## Lehigh University Lehigh Preserve

Theses and Dissertations

1-1-1980

# A study of two-dimensional effects in metal/ tunnel-oxide/ N/P+ silicon switching devices.

Umesh K. Mishra

Follow this and additional works at: http://preserve.lehigh.edu/etd Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Mishra, Umesh K., "A study of two-dimensional effects in metal/tunnel-oxide/ N/P+ silicon switching devices." (1980). *Theses and Dissertations*. Paper 2307.

This Thesis is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Lehigh Preserve. For more information, please contact preserve@lehigh.edu.

# A STUDY OF TWO-DIMENSIONAL EFFECTS IN METAL/TUNNEL-OXIDE/N/P<sup>+</sup> SILICON SWITCHING DEVICES

Umesh~K. Mishra

by

#### A Thesis

Presented to the Graduate Committee

of Lehigh University

In Candidacy for the Degree of

Master of Science

in

Electrical Engineering

Lehigh University

1980<sup>.</sup>

ProQuest Number: EP76583

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest EP76583

Published by ProQuest LLC (2015). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

> ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 - 1346

### CERTIFICATE OF APPROVAL

This thesis is accepted and approved in partial fulfillment of the requirements for the degree of Master of Science.

1\_

Date

Professor in Charge

Chairman of Department

#### ACKNOWLEDGEMENTS

I wish to express my most sincere thanks to Prof. J. G. Simmons, who not only suggested the project but also ably guided me, giving many invaluable suggestions during the course of the work.

I am extremely grateful to Dr. L. Faraone of R.C.A. Laboratories, Princeton, NJ, who painstakingly taught me silicon processing techniques and provided me with insight into device operation.

I would also like to thank Mr. Fu-Lung Hsueh for many helpful suggestions on device modeling, and Mr. A. K. Agarwal for his help in analysis.

Thanks are also due to Mr. K. Duncan of the University of Toronto for his helpful collaboration.

I would also like to thank all the graduate students and professors at Fairchild Laboratory for making my stay here a pleasant and informative one.

I wish to thank Ms. Jeanne Loosbrock for her patient and adept typing of this thesis.

Finally, I wish to acknowledge the National Science Foundation for its generous support of this research (under grant ECS-7908364) and the Sherman Fairchild Foundation for the fellowship awarded to me for the period January 1980

# TABLE OF CONTENTS

| /        |                                             | Page |

|----------|---------------------------------------------|------|

| List of  | Symbols                                     | vii  |

| Abstract |                                             | 1    |

| CHAPTER  | 1, INTRODUCTION                             | 2    |

| 1.1      | The Metal Insulator Semiconductor Switch    | 2    |

| 1.2      | The MISS:Historical Review                  | 6    |

| 1.3      | The Metal Insulator Semiconductor Thyristor | 11   |

| 1.4      | The Optical MIST (OMIST)                    | 13   |

| 1.5      | Two Dimensional Effects                     | 17   |

| 1.6      | The Objective and Outline of This Thesis    | 18   |

|          | References                                  | 20   |

| CHAPTER  | 2                                           | 22   |

| 2.1      | The Ideal Punch-through MISS                | 23   |

| 2.1.1    | High Impedance Characteristics              | 23   |

| 2.1.2    | The Negative Resistance Region              | 27   |

| 2.1.3    | Low Impedance ON State                      | 30   |

| 2.1.4    | The Switch-off Mode                         | 32   |

| 2.2      | The "Non-Ideal" Punch-through Mode          | 33   |

| 2.2.1    | The Regenerative Feedback Mechanism (RFM)   | 33   |

| 2.2.2    | The Negative Resistance Region              | 34   |

| 2.3      | Two-Dimensional Effects                     | 36   |

| 2.3.1    | The Effect of Device Area                   | 36   |

| 2.3.2    | Perimeter to Area Ratio (PAR) Effects       | 41   |

|          | References                                  | 44   |

iv

|   | •            |                                                    | Page |

|---|--------------|----------------------------------------------------|------|

|   | CHAPTER      | 3. EXPERIMENTAL TECHNIQUES                         | 45   |

|   | 3 <b>.</b> 1 | Fabrication Procedure                              | 45   |

|   | 3.1.1        | Masking Oxide Growth                               | 45   |

|   | 3.1.2        | Phosphorous Deposition                             | 47   |

|   | 3.1.3        | V-Groove Etching                                   | 48   |

|   | 3.1.4        | Pattern Definition for Tunnel-Oxide Areas          | 49   |

|   | 3.1.5        | Tunnel-Oxide Growth                                | 52   |

|   | 3.1.6        | First Metallization                                | 53   |

|   | 3.1.7        | Removal of the Thin Oxide over Contact Holes       | 54   |

|   | 3.1.8        | Second Metallization and Electrode Definition      | 55.  |

|   | 3.2          | Measurement Technique                              | 55   |

|   |              | References                                         | 59   |

|   | CHAPTER      | 4                                                  | 60   |

|   | 4.1          | Experimental Current-Voltage Characteristics       | 64   |

|   | 4.1.1        | Effect of Junction Area                            | 64   |

|   | 4.1.2        | Effect of Tunnel-Oxide Thickness                   | 66   |

| • | 4.2          | Discussion of the OFF State Characteristic         | 66   |

|   | 4.2.1        | Effect of Junction Area $A_j$                      | 66   |

|   | 4.2.2        | Effect of Tunnel-Oxide Thickness, dox              | 74   |

|   | 4.3          | The Switching Point                                | 75   |

|   | 4.3.1        | Effect of Junction Area on the Switching Current . | 75   |

|   | 4.3.2        | Effect of Oxide Thickness on the Switching         | 76   |

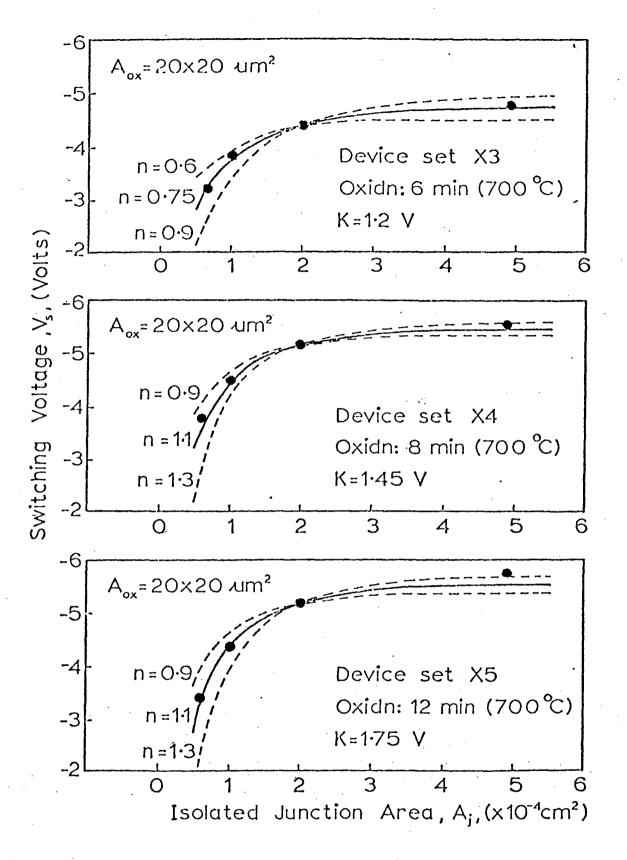

|   | 4.3.3        | The Switching Voltage                              | 77   |

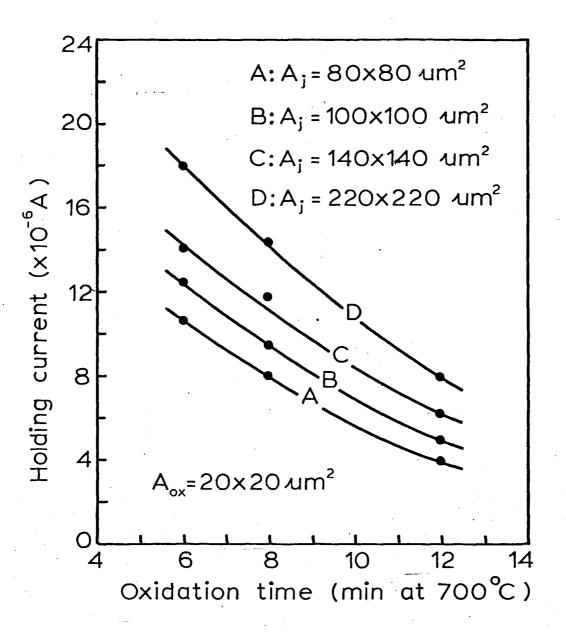

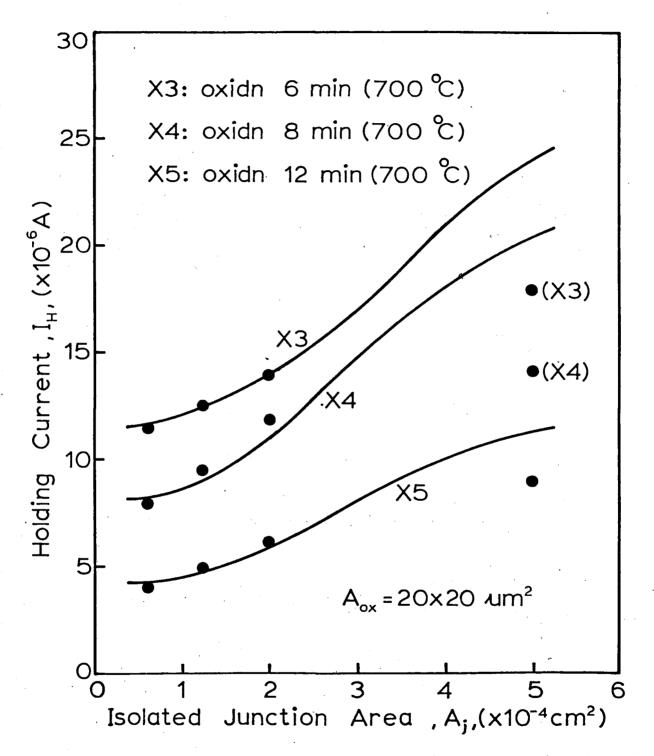

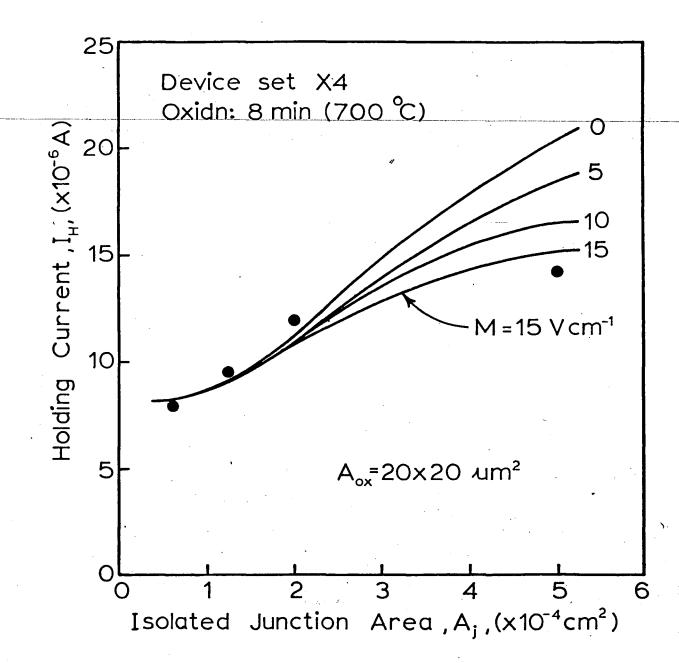

|   | 4.3.4        | The Holding Point                                  | 78   |

| • |              | References                                         | 81   |

|               |                                                                           | Page |

|---------------|---------------------------------------------------------------------------|------|

| CHAPTER       | 5                                                                         | 82   |

| 5.1           | Determination of the Switching Criterion                                  | 83   |

| 5.2           | Switching Current and Holding Current as<br>a Function of Oxide Thickness | 87   |

| 5.3           | Derivation of Relevant Equations for<br>Two-Dimensional Model             | 89   |

| 5.4           | Results and Discussion                                                    | 97   |

| 5.4.1         | The Switching Point                                                       | 97   |

| 5.4.1.ì       | Comparison between Calculated and Experi-<br>mental Results               | .98  |

| 5.4.2         | The Holding Point                                                         | 102  |

|               | References                                                                | 105  |

| CHAPTER       | 6. CONCLUSIONS AND RECOMMENDATIONS                                        | 106  |

| APPENDIC      | CES                                                                       |      |

| ,<br>Appendix | A. Pre-furnace Cleaning Procedure                                         | 111  |

| Appendix      | B. Shipley Photoresist (PR) Procedure                                     | 113  |

| Appendix      | c C. Cleaning Procedure for Aluminum                                      | 115  |

| Appendix      | CD. Physical and Experimental Parameters<br>Used in Calculation           | 116  |

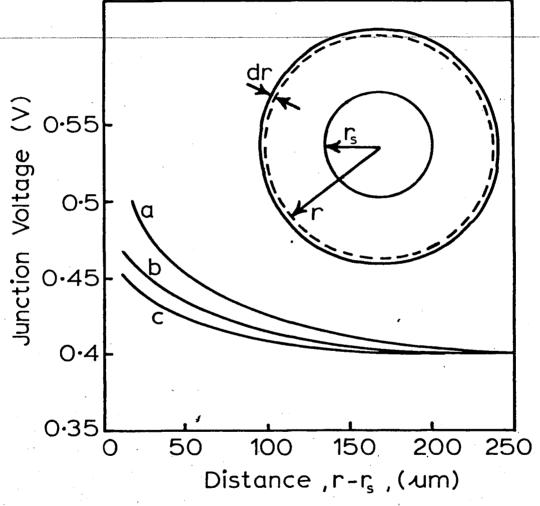

| Appendix      | K E. Junction Voltage as a Function of Radius                             | 117  |

| VITA          |                                                                           | 121  |

vi

# LIST OF SYMBOLS

| A*                  | Richardson constant, A cm <sup>-2</sup> $\kappa^{-2}$                |

|---------------------|----------------------------------------------------------------------|

| A <sub>1</sub>      | effective device area (= $L + 2X_d$ ) <sup>2</sup> , cm <sup>2</sup> |

| A, `                | isolated p <sup>+</sup> -n junction area, cm <sup>2</sup>            |

| Aox                 | tunnel-oxide area, cm <sup>2</sup>                                   |

| Cox                 | owide capacitance, F cm <sup>-2</sup>                                |

| d <sub>ox</sub>     | tunnel-oxide thickness, cm                                           |

| D                   | diffusion coefficient for holes, $cm^2 sec^{-1}$                     |

| -                   | silicon conduction band edge at Si-SiO2 interface, eV .              |

| E<br>Fm             | Fermi level of metal, eV                                             |

| E <sub>Fn</sub>     | quasi-Fermi level for electrons in neutral epi-layer, eV             |

| E <sub>Fn</sub> (0) | quasi-Fermi level for electrons at Si-SiO <sub>2</sub> interface, eV |

| E <sub>Fp</sub> (0) | quasi-Fermi level for holes at Si-SiO <sub>2</sub> interface, eV     |

| E <sub>FP</sub> +   | Fermi level of p <sup>+</sup> substrate, eV                          |

| Eg                  | silicon band-gap, eV                                                 |

| E <sub>v</sub> (0)  | silicon valence band edge at Si-SiO <sub>2</sub> interface, eV       |

| $E_v(X_d)$          | silicon valence band edge at $X = X_d$ , eV                          |

| . <b>I</b> .        | device current, A                                                    |

| Ig                  | generation current of the surface depletion region, A                |

| I.H.                | bolding current, A                                                   |

| I <sub>nj</sub>     | electron diffusion current, A                                        |

| Int                 | electron tunnel current from metal to silicon conduction band, A     |

| I p                 | total hole current, A                                                |

•

vii

| Ipi             | hole current reaching Si-SiO <sub>2</sub> interface, A                           |                                      |

|-----------------|----------------------------------------------------------------------------------|--------------------------------------|

| I<br>Pj         | hole diffusion current across the $p^+$ -n junction, A /                         |                                      |

|                 | pj2,I pj3) hole diffusion current in Region I (II,III), A                        |                                      |

| Ipt             | hole tunnel current from silicon valence band to metal, A                        |                                      |

| I<br>rj         | p <sup>+</sup> -n junction recombination current, A                              |                                      |

| ı,<br>rn        | recombination current in neutral epi-layer, A                                    |                                      |

| Is              | switching current, A                                                             | ••                                   |

| Jei             | injected electron current density, A cm <sup>-2</sup>                            | 4                                    |

| Jg              | generation current density of the surface depletion * region, A cm <sup>-2</sup> |                                      |

| J<br>nj         | electron diffusion current density, A cm <sup>-2</sup>                           |                                      |

| Jnt             | electron tunnel current density from metal to silicon conduction band, A cm $^2$ |                                      |

| J<br>Pj         | hole_diffusion current density across the $p^+$ -n junction, A cm                |                                      |

| J <sub>pt</sub> | hole tunnel current density from silicon valence band to metal, A cm             | nj :<br>:                            |

| J<br>rj         | $p^+$ -n junction recombination current density, A cm <sup>-2</sup>              |                                      |

| k               | Boltzman's constant, eV°K <sup>-1</sup>                                          |                                      |

| L ·             | tunnel-oxide side dimension, cm                                                  |                                      |

| L <sub>f</sub>  | fringing length of the electron tunnel current, cm                               | <b>.</b>                             |

| L p             | hole diffusion length, cm                                                        | <b>G</b>                             |

| M               | multiplication factor, dimensionless                                             |                                      |

| MISS            | metal insulator semiconductor switch                                             | алан <b>а</b> ла<br><sub>14</sub> ал |

| MIST            | metal insulator semiconductor thyristor                                          |                                      |

| OMIST           | optical metal insulator semiconductor thyristor                                  |                                      |

| N <sub>a</sub>  | acceptor concentration in $p^+$ substrate, $cm^{-3}$                             |                                      |

|                 | n an                                         | •<br>•                               |

viii.

|        | ,               |                                                                 |

|--------|-----------------|-----------------------------------------------------------------|

| · .    | Nd              | donor concentration in n epi-layer, cm <sup>-3</sup>            |

| ń      | n<br>i          | intrinsic carrier concentration, cm <sup>-3</sup>               |

|        | N <sub>v</sub>  | density of states at silicon valence band edge, $cm^{-3}$       |

|        | PAR             | perimeter to area ratio of device, $cm^{-1}$                    |

| • •    | p(0)            | hole density at Si-SiO <sub>2</sub> interface, cm <sup>-3</sup> |

| 7      | Pno             | equilibrium hole concentration in n epi-layer, $cm^{-3}$        |

| -<br>- | q               | electronic charge, $1.6 \times 10^{-19}$ coul                   |

|        | RFM             | regenerative <u>f</u> eedback mechanism                         |

|        | Q <sub>d</sub>  | depletion charge, coul $cm^{-2}$                                |

|        | Qg              | gate charge, coul $cm^{-2}$                                     |

|        | Q               | inversion charge, coul cm <sup>-2</sup>                         |

|        | Q <sub>ss</sub> | fixed interface charge density, coul $cm^{-2}$                  |

|        | r j             | equivalent radius of isolated $p^+$ -n junction area, cm        |

|        | ro              | equivalent radius of effective device area, cm                  |

|        | r <sub>s,</sub> | equivalent radius of short-base diode (Region II), cm           |

|        | Τ <sub>ι</sub>  | absolute temperature, °K                                        |

|        | v               | total voltage across the device, V                              |

|        | V <sub>bd</sub> | avalanche breakdown voltage, V                                  |

|        | v <sub>H</sub>  | holding voltage, V                                              |

|        | v <sub>j</sub>  | p <sup>+</sup> -n junction voltage, V                           |

|        | Vs              | switching voltage, V                                            |

|        | Vpt             | punch-through voltage, V                                        |

|        | v <sub>T</sub>  | thermal voltage (= kT/q), V                                     |

|        | Wj              | p <sup>+</sup> -n junction depletion width, cm                  |

|        | Wn              | width of neutral region, cm                                     |

| . 1    |                 | ix ,                                                            |

|        | •               |                                                                 |

epi-layer thickness, cm

$E_{\rm Fm} - E_{\rm c}(0), eV$

Xd

Х<sub>е</sub>

δ

ε<sub>ox</sub>

ε<sub>s</sub>

τg

τ<sub>o</sub>

τ1

${}^{\phi}{}_{\texttt{Bi}}$

<sup>¢</sup>ms

Ψs

Xn

х<sub>р</sub>

silicon dioxide dielectric constant, F cm<sup>-1</sup> silicon dielectric constant, F cm<sup>-1</sup>

generation lifetime in  $p^+$ -n junction, sec

hole recombination lifetime in bulk epi-layer, sec

hole recombination lifetime in  $p^+$ -n junction depletion region, sec

p<sup>+</sup>-n junction built-in potential, V

metal-semiconductor work function difference, V

semiconductor surface potential, V

tunnel-oxide barrier height for electrons, eV

tunnel-oxide barrier height for holes, eV

X

Effects of V-groove isolation on the two-terminal D.C. characteristics of the metal/tunnel-oxide/n/p<sup>+</sup> silicon switching devices have been studied.

Experimental results show that the switching characteristics of non-isolated devices are strongly dependent on area and the area-to-perimeter ratio of the device. To carry out a systematic investigation of this phenomenon, devices in this study were isolated using V-grooves of various areas. For a given tunneloxide thickness and area, it was found that the switching voltage,  $V_{\rm H}^{}$ , and holding current,  $I_{\rm H}^{}$ , is essentially independent of isolation area. Based on this experimental observation (I  $\simeq$  constant), a qualitative physical argument is presented which determines the switching criterion for the device, and concludes that the transition from the OFF to the ON state, and vice versa, is solely dependent on the properties of the MIS diode; in particular, the minority carrier concentration at the Si-SiO, interface. In agreement with experimental results, a decrease in switching current and holding current is predicted for an increase in tunnel-oxide thickness.

Finally a simple two-dimensional model has been derived which effectively explains the variation of switching voltage and holding current with changes in the p-n junction area.

#### INTRODUCTION

#### 1.1 THE METAL INSULATOR SEMICONDUCTOR SWITCH (MISS)

Recently, the Metal-Insulator-Semiconductor-Switch (MISS) has been the focus of considerable attention. This device has been received with increasing enthusiasm because of three primary reasons:

(i) Ease of fabrication

(ii) Compatibility with existing technologies and, most importantly,(iii) Performance of a function not hitherto obtained by an easily

integrable device (a bistable switch).

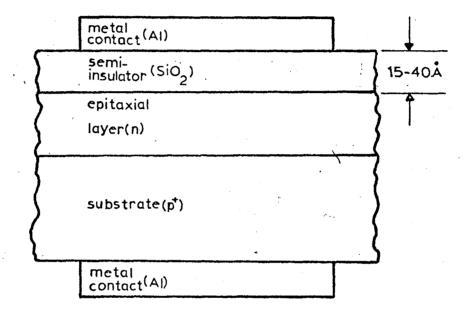

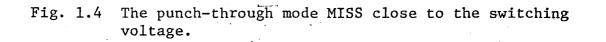

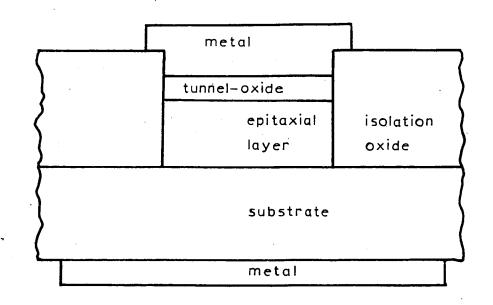

The basic structure of the MISS is shown schematically in Fig. 1.1. It consists primarily of a semi-insulating film of silicon dioxide grown on the surface of an n-epitaxial layer formed on a p<sup>+</sup> substrate wafer of <100> orientation, sandwiched between two electrodes. Neither the choice of the semi-insulating layer, nor of the metal electrodes is limited to those just mentioned, and a wide range of materials has been investigated. Yamamoto et al (1-1, 1-2), who first demonstrated the switching behaviour of the MISS, used a 20-30 Å tunnel-oxide (SiO<sub>2</sub>) for the semi-insulating film. Later Kroger and Wegener demonstrated the viability of Si<sub>3</sub>N<sub>4</sub> (1-3) and polycrystalline silicon (1-4). Results of an in-depth investigation carried out by them, on the effect of various other semi-insulating films on device characteristics is presented in Ref. (1-5). Various metals can be used as electrodes for the device. Aluminum (1-1), platinum (1-1), gold (1-2), molybdenum

Fig. 1.1 Schematic of basic MISS structure under study (not drawn to scale).

(1-3) and chromium (1-4) are a few examples of metals that have been researched thus far. However, most of the work done to date has been on devices using a tunnel-oxide (20-40  $\stackrel{\circ}{A}$  SiO<sub>2</sub>) as the semi-insulating film and aluminum as the metal electrode.

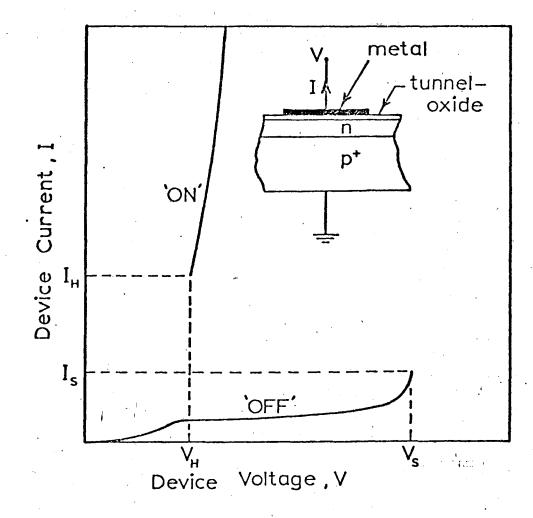

The MISS performs the function of an electronic switch, in that it exhibits two stable states, the ON and OFF states (see Fig. 1.2). The ratio of the resistance of the two states is  $\sim 10^6$ . As the applied voltage,  $V_A$ , is increased negatively from zero, the device exists in the high impedance or OFF state. The switching voltage,  $V_s$ , is the maximum voltage that can exist across the device before the MISS switches from the OFF to the ON state. The switching current, Is, is the current at the switching point. The holding current, I<sub>H</sub>, is the minimum current necessary to sustain the device in the low impedance ON state. The holding voltage,  $V_{\rm H}$ , is the voltage across the MISS at the holding point. Fig. 1.2 shows a schematic of the I-V characteristics of a MISS. The basic circuit configuration in which the device is operated is presented in the inset. It will be noted that the I-V characteristic of the MISS is similar to that of a 'pnpn' (Shockley) diode. However, there are important differences between the two:

(i) The MISS possesses a higher switching speed, measured as less than two nanoseconds (1-2).

(ii) Unlike the 'pnpn' diode, the fabrication of the MISS involves very few high temperature processes, making it a simpler device to fabricate.

(iii) The most important advantage of the MISS over the 'pnpn' diode

Fig. 1.2 Schematic of the I-V curve of a MISS device defining the parameters I, V, I<sub>H</sub> and V<sub>H</sub> that characterize the device.

INSET: Basic MISS structure.

is the case with which it can be integrated i.e. it is amenable to fabrication with standard IC technology.

#### 1.2 THE MISS: HISTORICAL REVIEW

In the first report of the switching phenomenon (1-1), it was speculated that the formation of an inversion layer under the oxide, caused by hole injection from the substrate, resulted in a very high voltage across the device, causing two electron currents to flow: (a) a hot electron tunnel current from the conduction band of the nSi to the metal (note that the electrons flow from the metal to the conduction band), and

(b) a current caused by the tunneling of electrons from the metal to the Si-SiO<sub>2</sub> interface states and their subsequent recombination with the holes present in the inversion layer.

Kroger and Wegener (1-3) recognised the OFF state to be a deeply-depleted state in the semiconductor. This was believed to be caused by the leaky insulator allowing a finite tunneling current to drain off excess minority carriers from the Si-SiO<sub>2</sub> interface. This minority carrier tunneling through the semi-insulator prevented the formation of an inversion layer, forcing the MISS to remain in the high-impedance state.

Yamamoto et al in a later publication (1-2) postulated a surface feedback mechanism based on current multiplication at the insulatorsemiconductor interface (1-6) as being responsible for the negative resistance behaviour of the MISS. Simmons and El-Badry (1-7)

presented a scmi-quantitative theory establishing two types of switching in the MISS: (a) the punch-through mode and (b) the avalanche mode. Those devices in which the surface depletion region extended through the lightly-doped ( $N_d < 10^{16} cm^{-3}$ ) epitaxial layer to the underlying p<sup>+</sup>-n junction, were recognised to be operating in the punch-through mode. On the other hand, the avalanche mode identified those devices in which avalanche breakdown in the higher doped epitaxial layer ( $N_d > 10^{16} cm^{-3}$ ) occurred before punch-through and was responsible for switching.

Most recently, Habib (1-8) has shown that the avalanche and punch-through modes are two subclasses of a more general switching mechanism, the <u>Regenerative Feedback Mechanism</u> (RFM). He identified the feedback loop in terms of the various current components in the system and eventually rigorously derived the I-V characteristics of the device. Both types of switching, avalanche and punch-through, depend on the RFM for switching. The key difference between the two modes of switching is the manner in which each is initiated.

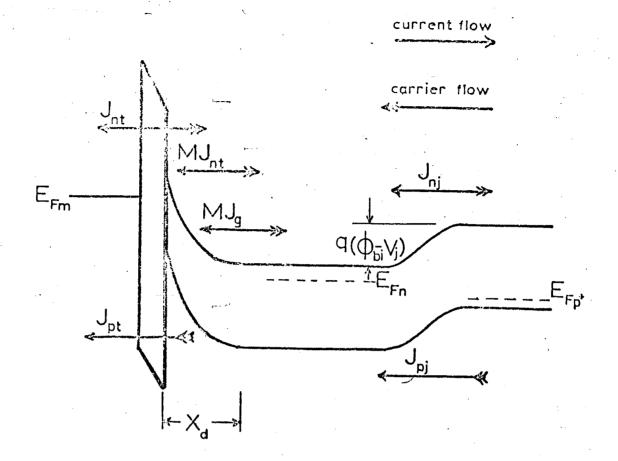

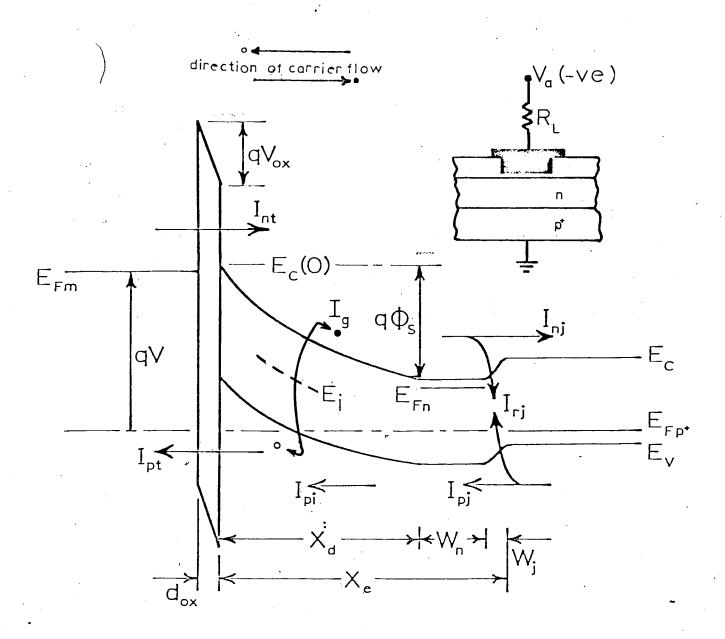

In the avalanche device, avalanche multiplication of the electron tunnel current,  $J_{nt}$  (see Fig. 1.3), and/or the generation current,  $J_g$ , in the high field depletion region,  $x_d$ , increases the electron current passing across the p<sup>+-n</sup> junction,  $J_{nj}$ . This injected electron current is given by

7

$J_{nj} = M(J_{nt} + J_g),$

where the multiplication factor  $M = 1 - \left(\frac{V}{V_{bd}}\right)^{-1}$ , and bd

τ.

Fig. 1.3 The avalanche mode MISS just prior to switching.

$V_a$  = voltage applied to the device,  $V_{bd}$  = the avalanche breakdown voltage.

The electron current biases the  $p^+$ -n junction, and once the junction is sufficiently biased, the feedback mechanism is initiated. The mechanism is described in detail in Section 2.2.1. The voltage at which switching occurs in the avalanche device is dependent on the avalanche breakdown voltage of the epitaxial layer, given by (1-9)

$$V_{bd} = 60 \left(\frac{E_g}{1.1}\right)^{3/2} \left(\frac{N_d}{10^{16}}\right)^{-3/4}$$

where  $E_g$  is the bandgap energy and  $N_d$  is the epitaxial layer doping concentration.

In the PT device of E1-Badry and Simmons (1-7) however, because of the relatively low doping of the epitaxial layer, the surface depletion region actually extends (i.e. punches through) to the  $p^+-n$ junction before the avalanche voltage,  $V_{\rm bd}$ , can be attained. Any increase in the applied voltage will thereafter cause a decrease in the barrier potential of the  $p^+-n$  junction and the same feedback mechanism (of Section 2.2.1) as in the avalanche mode of switching is initiated.

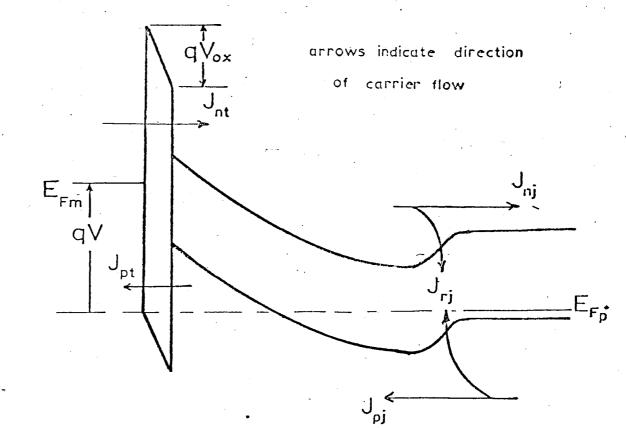

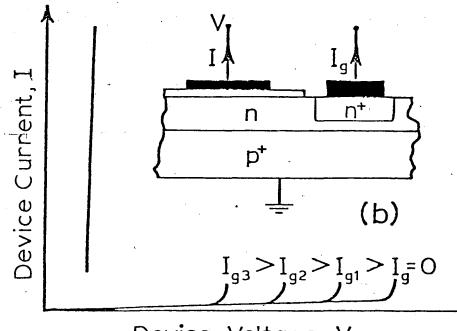

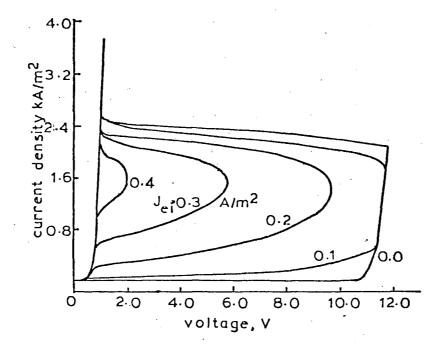

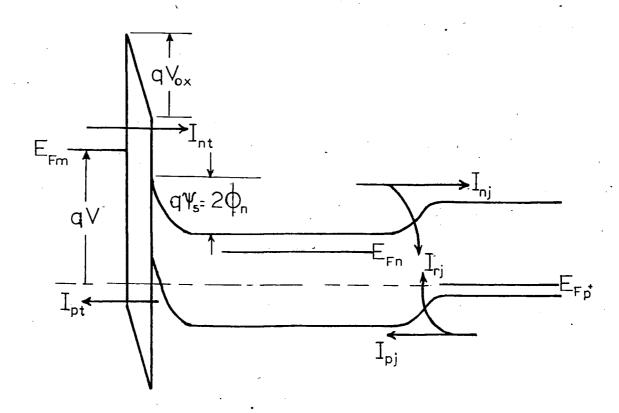

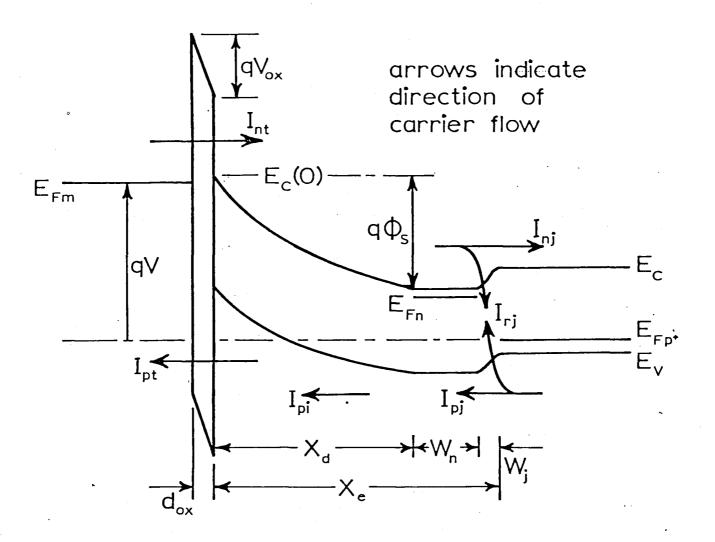

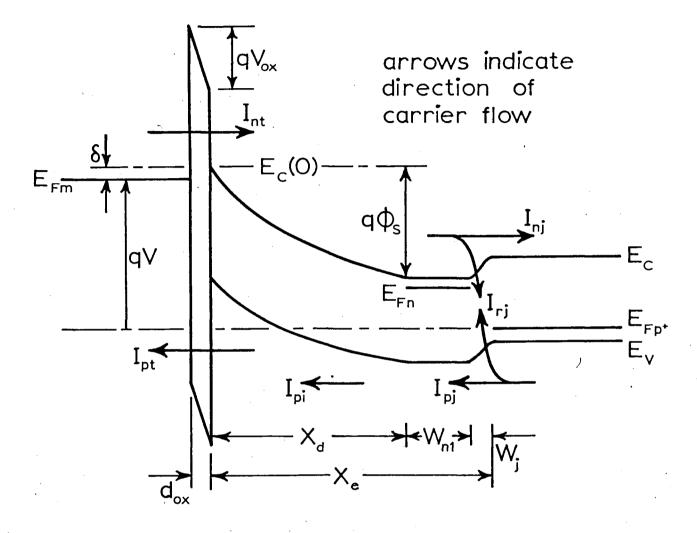

Figure 1.4 illustrates the energy diagram for a punch-through device close to switching. The feedback loop is established when the  $p^+$ -n junction is biased sufficiently such that a critical value of hole current is injected from the  $p^+$  substrate into the epitaxial

layer. This augmented hole diffusion current,  $J_{pj}$ , will be accompanied by an incremental increase in the free hole density p(o) at the Si-SiO<sub>2</sub> interface, causing an increase in the oxide voltage,  $V_{ox}$ . This increase in  $V_{ox}$  will enhance the flow of electron tunnel current,  $J_{nt}$ , from the semiconductor conduction band to the metal. This in turn causes a further increase in the  $p^+$ -n junction bias,  $V_j$ , which is accompanied by a further increase in the hole current,  $J_{pj}$ , injected into the epitaxial layer. In this manner, a positive feedback loop is established. When the gain of the feedback loop is equal to unity, the device switches.

Two mechanisms, PT and RFM, are of special importance since the devices studied during the course of this work behaved as predicted by these two mechanisms. Hence these two mechanisms deserve more attention and will be treated in detail in the next chapter.

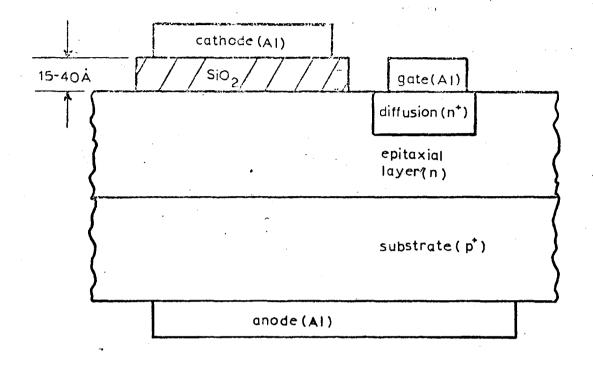

#### 1.3 THE METAL INSULATOR SEMICONDUCTOR THYRISTOR

Any mechanism that will reinforce the feedback action will facilitate the device switching. Conversely, any mechanism that weakens the positive feedback action will tend to inhibit switching. Thus, electronic carrier injection (or extraction) or the appropriate  $p^+-n$  junction biasing will strengthen (or weaken) the feedback mechanism i.e. reduce (or increase) the voltage required to switch the device. Desired junction biasing can be achieved through a third terminal or gate which is in ohmic contact with the n layer via an  $n^+$  diffusion (see Fig. 1.5). Since this device has

Fig. 1.5 The basic three terminal MIST structure. (not drawn to scale)

characteristics resembling those of a thyristor, it is designated the Metal-Insulator-Semiconductor-Thyristor (MIST).

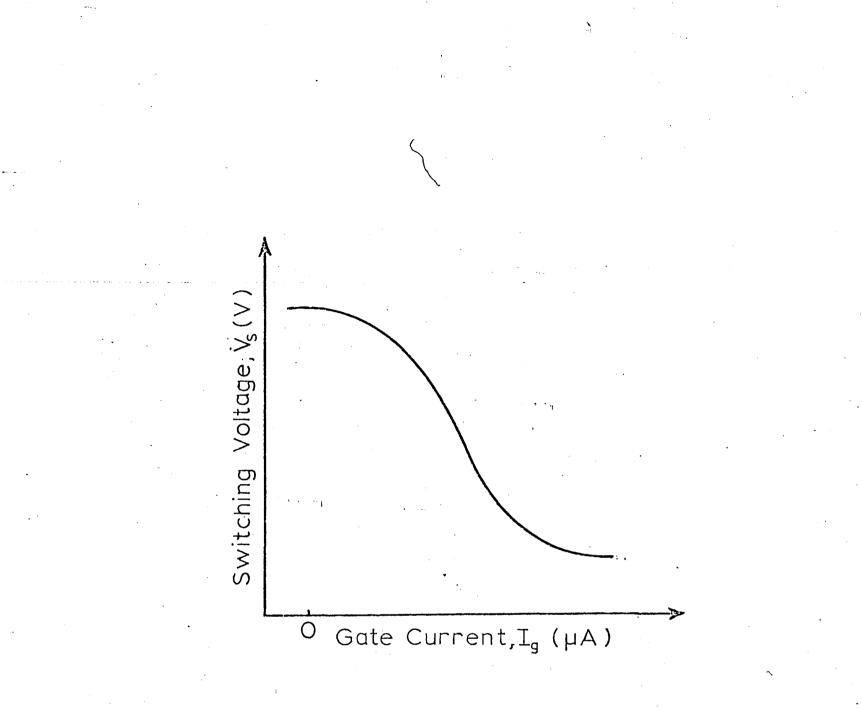

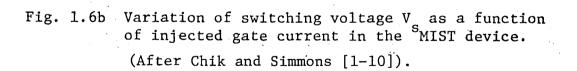

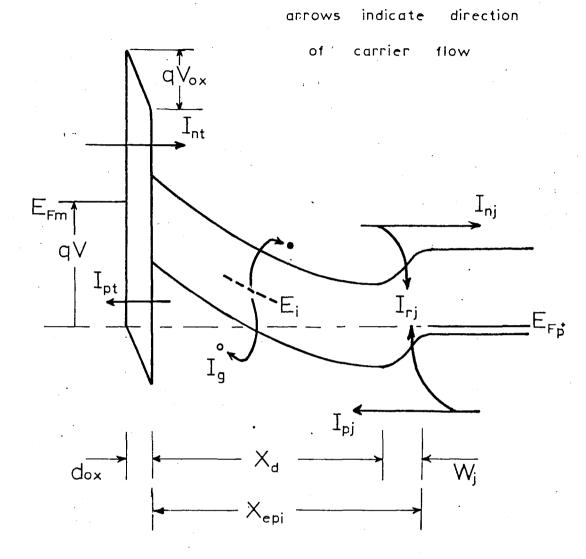

The MIST was first studied by Kroger and Wegener (1-4), who found that increasing the negative bias on the gate (or increasing the forward bias across the junction) decreased the switching voltage whereas decreasing the forward bias caused the switching voltage to increase. Yamamoto et al. (1-2) discovered that the switching voltage could be decreased with a proportionate increase in the gate terminal bias current. Chik and Simmons (1-10) carried out an extensive investigation of the dependence of the MIST I-V characteristics on gate bias (both current and voltage bias). Figure 1.6a shows the I-V characteristics of the MIST for various values of gate current, It is seen from the figure that the switching voltage,  $V_s$ , I<sub>a</sub>. decreases monotonically with increasing  $I_g$ . The variation of  $V_s$ with I that they observed is presented in Figure 1.6b. Habib and Simmons (1-11) have carried out a detailed theoretical analysis of the MIST, and the calculated I-V curves they obtained with gate current as parameter are presented in Figure 1.6c. This study is of particular interest because variation of the junction isolation area (see Chapter 4) manifests itself in a change in junction bias, which is what one achieves via the gate terminal of the MIST.

#### 1.4 THE OPTICAL MIST (OMIST)

Just as electronic minority carrier injection enhances the switching action, so does optically generated carrier injection.

-13

Device Voltage ,V

Fig. 1.6a MIST device I-V characteristics.

INSET: Basic structure.

(After Chik and Simmons [1-10]).

.

# Fig. 1.6c Calculated I-V curves of the MIST with gate current J as parameter.

(After Habib and Simmons [1-11]).

Nassibian, Calligaro and Simmons (1-12) developed theoretical expressions for the light induced hole current and correlated the experimentally observed change in the MIST switching voltage as a function of incident photon flux. They used a 150 Å thick, semitransparent aluminium film as the cathode so that the incidentlight could penetrate through the metal and generate electron-hole pairs in the n epi-layer. The transmittance of the film was measured to be 0.15.

The main drawback in the structure was the poor transmittance of the Al film, which reduced the quantum efficiency of the device. Adam and Dobos (1-13) recently investigated the optical dependence of the MISS characteristics using a 1000-2000 Å thick RF sputtered film of SnO<sub>2</sub> as the cathode. The advantage of using SnO<sub>2</sub> over Al is that it is a highly conductive ( $\rho \approx 10^{-2} \Omega cm$ ) n-type semiconductor which is virtually transparent to visible light (transmittance  $\approx$  90%).

#### 1.5 TWO DIMENSIONAL EFFECTS

All the theories presented to date to explain the observed I-V characteristics have been based on a one-dimensional analysis of the device. Other than the punch-through and avalanche models proposed by Habib and Simmons, there is a third model first proposed by Ya-mamoto et al. (1-2) and treated in greater detail by Sarrbayrouse et al. (1-14). In this model the switching is related to the formation of an inversion layer at the Si-SiO<sub>2</sub> interface. However erroncous interpretation of their experimental results led the authors

to conclusions different from those reached by Habib and Simmons. These anomalies have recently been explained by an investigation carried out by Duncan et al. (1-15).

In an extensive experimental study these authors have established that fabrication conditions, thickness of the field oxide employed and device geometry have a very strong effect on the switching charactersitics of the MISS. The experimental results obtained have been explained in a qualitative manner based on the strengthening and weakening of the regenerative feedback mechanism of Habib and Simmons (1-16).

#### 1.6 THE OBJECTIVE AND OUTLINE OF THIS THESIS

The main objective of this thesis is to provide a two-dimensional model to explain the two-terminal DC characteristics of the MISS. To adequately model the device, it is essential to know as accurately as possible the area of the  $p^+$ -n junction active in the functioning of the device. To effectively control the junction area, the devices were isolated by means of self-terminating V-grooves. Another motivation for isolating the devices is the theoretical analysis of the MIST by Habib and Simmons (1-11). The variation of the MISS characteristics with gate bias (or junction bias) that they calculated is what is effectively simulated by changing the V-groove area.

An important outcome of the study of the variation of the I-V characteristics with changes in junction area was the experimental determination of the switching criterion of the MISS. The effect

of the tunnel oxide thickness,  $d_{ox}$  on the DC behaviour has also been investigated.

To make the presentation lucid, the thesis is organised in the following fashion:

Chapter 2 presents the punch-through and regenerative feedback theories which are essential to understand the DC behaviour of the devices under study. Observed perimeter-to-area ratio effects on the I-V characteristics of the MISS are presented and the trends explained on the basis of the RFM.

Chapter 3 presents the procedure employed to fabricate the devices and the experimental technique used to measure the DC I-V characteristics of the MISS.

Chapter 4 presents physical arguments to explain the observed two-terminal DC behaviour of the isolated MISS and establishes the switching criterion for the device.

Chapter 5 details the two-dimensional model used in predicting the variation of device parameters with changes in oxide thickness and junction area.

Chapter 6 presents the conclusions that may be drawn from the discussions in the preceding chapters and design criteria for the device are developed, based on these discussions.

#### REFERENCES

- 1-1 T.Yamamoto and M.Morimoto: 'Thin M-I-S Structure Si Negative Resistance Diode', Appl. Phys. Lett., 20, 269 (1972).

- 1-2 T.Yamamoto, K.Kawamura & H.Shimuzu: 'Silicon-p-n-Insulator-Metal (p-n-I-M) Devices', Solid-St. Electron., 19, 701 (1976).

- 1-3 H.Kroger & H.A.R.Wegener: 'Bistable Impedance States in MIS Structures through Controlled Inversion', Appl.Phys.Lett., 23, 347 (1973).

- 1-4 H.Kroger & H.A.R.Wegener: 'Controlled Inversion Transistors', Appl.Phys.Lett., 27, 303 (1975).

- 1-5 H.Kroger & H.A.R.Wegener: 'Steady-State Characteristics of Two Terminal Inversion-Controlled Switches', Solid-St. Electron, 21, 643 (1974).

- 1-6 V.Temple, M.Green, J.Shewchun: 'Equilibrium to Non-Equilibrium Transition in MOS (Surface Oxide) Tunnel Diode", J.Appl.Phys., 45, 4934 (1974).

- 1-7 J.Simmons & A.El-Badry: 'Theory of Switching Phenomena in Metal/Semi-Insulator/n-p Silicon Devices', Solid-St. Electron., 20, 963 (1977).

- 1-8 S.E-D.Habib: 'DC Theory of Switching M-I (Tunnel)-n-p Silicon Devices', PhD Thesis, University of Toronto (1973).

- 1-9 S.M.Sze: 'Physics of Semiconductor Devices', J.Wiley (1969).

- 1-10 K.D.Chik & J.G.Simmons; 'Characteristics of Three-Terminal Metal-Tunnel Oxide-n/p Devices', Solid-St. Electron., <u>22</u>, 589 (1979)

- 1-11 S.E-D.Habib & J.G.Simmons: 'Theory of the Metal-Insulator-Semiconductor Thyristor', IEE Proc., Pt.I, 127, 176 (1980).

- 1-12 A.G.Nassibian, R.B.Calligaro & J.G.Simmons: 'Digital Optical Metal Insulator Silicon Thyristor (OMIST)', IEE J. Solid-St. & Electron Dev., 2, 149 (1978).

- 1-13 A.Adan & K.Dobos: 'New Types of Metal-Insulator-Semiconductor Switch', Solid-St.Electron, 23, 17 (1980).

1-14 G.Sarrabayrouse, J.Buxo, A.E.Owen, A.Munoz Yague & J-P.Sabaa: 'Inversion-Controlled Switching Mechanism of MISS Devices', IEEE Proc., Pt.I, 127, 119 (1980).

- 1-15 K. A. Duncan, P. D. Tonner, J. G. Simmons and L. Faraone, 'Characteristics of Metal/Tunnel-Oxide/ n/p Silicon Switching Devices: Part I: Effects of Device Geometry and Fabrication Processes,' (to be published).

- 1-16 S. E-D. Habib and J. G. Simmons: 'Theory of Switching in P-N-Insulator(Tunnel)-Metal Devices. Part I: Punch-through Mode,' Solid-St. Electron, 22, 181 (1979).

CHAPTER 2

In this chapter the DC theory essential to understanding the MISS is presented. The class of devices this theory models is those that do not depend on carrier multiplication in the surface depletion region to initiate the positive feedback mechanism (see section 1.2 for a simple treatment of avalanche devices). From now on we will refer to all such devices (i.e. other than avalanche devices) as punch-through devices. However, there are two subclasses of the punch-through device:

(1) the "ideal" punch-through device in which the surface depletion region extends through the epilayer to the junction depletion region before the positive feedback mechanism is initiated, and (ii) the "non-ideal" punch-through device in which the regenerative feedback is high enough to initiate switching before the surface depletion region punches through to the junction depletion edge.

Both these classes of devices will be dealt with separately and the arguments presented and used to explain, qualitatively, the area dependence of the MISS current-voltage characteristics.

#### 2.1 THE IDEAL PUNCH-THROUGH MISS

#### 2.1.1 High Impedance Characteristics

The switching mode of the metal-insulator-n-p<sup>+</sup> structure is with the metal biased negatively with respect to the p substrate. This effectively reverse-biases the MIS diode into deep-depletion and forward-biases the p<sup>+</sup>-n junction. As the bias on the metal electrode is increased negatively, the depletion region under the oxide grows toward the p-n junction. Electron-hole pairs are generated in the depletion region, the electrons being swept towards the  $p^{+-n}$  junction and holes towards the Si-SiO<sub>2</sub> interface. The electron-hole pair generation current  $I_g$  is depicted in Figure 2.1a. It is worthwhile to note that if the oxide were impervious to holes (i.e. a thick-oxide ( $\sim$ 1000 Å) MOS capacitor), the generated holes would accumulate at the Si-SiO2 interface, causing the n-Si to invert This would limit the depletion width, X<sub>d</sub>, to a maximum corresponding to a surface potential  $\psi_s = 2\phi_n$ . However, as the insulator is leaky, holes pass through the oxide at the rate that they are supplied to the interface; hence, the n-Si goes into deep-depletion (Fig. 2.1a).

For the typical values of generation lifetime encountered in bulk epitaxial silicon ( $\sim 10^{-6}$ Sec), the generation current is negligible compared to the magnitude of the OFF state current normally observed. The primary electron current flowing in the system is the electron tunnel current,  $I_{nt}$ , composed of electrons flowing from the metal to the conduction band of the n-Si. This current dominates  $I_{g}$  and will be shown in Section 2.2.1 to be the

Fig. 2.1a The MISS in the OFF state with component currents. INSET: Basic circuit configuration for the MISS.

triggering current component which initiates the RFM leading to switching.

However, the "ideal" punch-through device, by definition, is one in which the surface depletion region necessarily has to punchthrough before the switching process is initiated and so more insight into device operation is gained through the voltage rather than the current equations.

The voltage, V, across the device is given by

$$V = \phi_{MS} + V_{ox} + \psi_{s} + V_{j} \qquad (2.1)$$

The MISS is normally in the configuration shown in the inset of Figure 2.1a, where  $R_{\underline{I}}$  is the load resistor used to limit the current through the device.

The applied voltage,  $V_A$ , is given by

$$v_{A} = v + v_{R}$$

(2.2)

where  $V_{R}$  is the voltage across  $R_{L}$ .

In the OFF state, the current through the device is limited by the reverse biased MIS diode. The device exhibits a very high dynamic impedance in the OFF state ( $\sim 10^{7}\Omega$ ); hence the increase in  $V_{ox}$ and  $V_{j}$  needed to accommodate the small increase in current is negligible compared to the gate voltage, V. These arguments apply only after flat-band (see Chapter 4 for details), when any increase in the gate voltage, V, is absorbed in the surface depletion region. Hence, eqn. 2.1 may be rewritten as

where K is a constant, of the order of 1-2V, which incorporates the effects of  $\phi_{\rm MS}$ ,  $V_{\rm ox}$  and  $V_{\rm j}$  (see Chapter 4). The surface potential,  $\psi_{\rm s}$ , is related to the depletion width,  $X_{\rm d}$ , given by (2-1)

$V \simeq K + \psi_s$

$$x_{d} = \left(\frac{2\varepsilon_{s}\psi_{s}}{qN_{d}}\right)^{\frac{1}{2}}$$

(2.4)

Hence V can increase to a maximum value corresponding to the case when the depletion region extends up to the depletion edge of the  $p^+$ -n junction, or equivalently,

$$X_{d_{max}} = X_{epi} - W_j$$

(2.5)

where  $X_{epi}$  is the epilayer thickness and  $W_j$  is the junction depletion width.

Using eqns. 2.3 and 2.4 the following relation for the maximum voltage  $V_{\rm PT}$  than can be sustained across the MISS can be derived as,

$$V_{\text{PT}} = K + \psi_{\text{smax}}$$

$$= K - \frac{qN_{d}(X_{\text{epi}} - W_{j})^{2}}{2\varepsilon_{s}}$$

(2.6)

Any extra voltage,  $\Delta V$ , above  $V_{pT}$ , applied to the gate will cause a Schottky lowering of the p<sup>+</sup>-n junction barrier potential,  $V_{bi}$  (2-2), and an attendant increase in current. This sudden increase in the current across the device is what triggers the switching mechanism, leading to the observed negative resistance in the MISS I-V charac-

teristic. The physical processes responsible for the negative resistance behaviour are explained in the following section.

## 2.1.2 The Negative Resistance Region

As stated in the previous section, at sufficiently high bias  $(V=V_{\rm PT})$ , the depleted section of the epilayer reaches through to the p<sup>+</sup>-n junction. Any further increase in the gate voltage will appear across R<sub>L</sub>, the p<sup>+</sup>-n junction and V<sub>ox</sub>.

Consider a small incremental voltage increase,  $\Delta V$ , beyond  $V_s$ . Assume also that all the voltage increase appears across  $R_L$ . Hence, the current flowing through the MISS is given by

$$I \simeq \frac{v - v_{max}}{R_L}$$

(2.7)

In the OFF state, the current  $I_{off}$ , was typically around  $10^{-6}$ - $10^{-7}$  A (depending on device area). Now, however, for V - V<sub>max</sub> = 0.1V and R<sub>I</sub> = 1K $\Omega$ ,

$$I = \frac{0.1}{10^3} = 10^{-4} A$$

which is very much greater than  $I_{off}$ . This current flows into the device, across the oxide and  $p^+$ -n junction. However, the voltage drop across the resistor is a linear function of I, whereas the voltage drop across both the oxide and the  $p^+$ -n junction depend logarithmically on I. Hence the initial assumption of most of the voltage increase being absorbed across  $R_L$  after punch-through is

justified. The above empirical argument further strengthens the statement that  $V_{\text{PT}}$  as defined by eqn. 2.6 is truly the maximum voltage that can be sustained across the device.

After punch-through, any incremental voltage  $\Delta V$  causes a Schottky lowering of V causing a sudden increase in the injected hole current  $I_{pi}$  from the p<sup>+</sup> substrate towards the Si-SiO<sub>2</sub> interface (see Figure 2.1b). Just prior to punch-through the voltage across the tunnel-oxide was just enough to supply the small OFF state current. Hence the sudden increase in the rate of holes reaching the interface (or equivalently, the sudden rise in I ) cannot be accommodated by the oxide, i.e. the holes reach the Si-SiO<sub>2</sub> interface faster than the existing oxide voltage can drain them. This causes an increase in the hole concentration at the interface p(o), and an attendant increase in  $V_{ox}$ . This in turn increases the electron tunnel current, which further biases the  $p^{+}_{p}$ -n junction, causing a larger I to flow. The build-up of holes causes a redistribution of voltage across the device. The depletion region starts collapsing, the decrease in surface potential being taken up by the oxide, the p-n junction and  $R_{I}$ . However, because of the exponential dependence of current on V and V, very small changes in V and V can accommodate ox j large changes in current. Hence, most of the voltage drop across the device caused by the shrinking depletion region is absorbed in the series resistance. This voltage decrease across the device

28

accompanied by an increase in current leads to the negative resis-

Fig. 2.1b The MISS at punch-through with component voltages and currents.

tance characteristic observed and the device switches. The voltage at which switching occurs is hence the PT voltage,

$$V_s \equiv V_{PT} \simeq K - \frac{qN_d(X_{epi} - W_j)^2}{2\varepsilon_s}$$

(2.6a)

## 2.1.3 Low Impedance ON State

During switching, the depletion region keeps collapsing and  $\psi_{\rm s}$  continuously decreases. This contraction stops when  $\psi_{\rm s}$  reaches the equilibrium strong inversion value (2-3),

$$\psi_{\rm s} \simeq 2\phi_{\rm n} = 2\{\frac{E_{\rm G}}{2} - (E_{\rm c} - E_{\rm Fn})\}$$

(2.8)

Figure 2.1c shows the energy band diagram of the MISS in the ON state i.e. with  $\psi_s \simeq 2\phi_n$ . During switching, the current was limited by the rate at which holes could be transported through the oxide. In the ON state however, the field across the oxide is large (>10<sup>6</sup>Vcm<sup>-1</sup>) and the oxide can be considered essentially transparent to electrons and holes. Hence in this regime of operation the current through the device is limited by the p<sup>+</sup>-n junction and R<sub>T</sub>.

The holding voltage, V<sub>H</sub>, which is the minimum voltage required to keep the device in the ON state, is given by

$$V_{\rm H} = \phi_{\rm MS} + V_{\rm ox} + 2\phi_{\rm n} + V_{\rm j}$$

(2.9)

In the low-impedance state, the p<sup>+</sup>-n junction is fully turned on, i.e.  $V_j \approx 0.5V$  (see Chapter 5). Also  $q\psi_s = 2\phi_n \approx 0.47$  eV for a doping concentration  $N_d = 10^{14}$  cm<sup>-3</sup>. Assuming that the tunnel-oxide thickness.  $d_{ox}$ , is 30 Å and the oxide field,  $\varepsilon_{ox}$ , is  $10^6$  V cm<sup>-1</sup>, then the oxide voltage,  $V_{ox}$ , is given by 30

Fig. 2.1c The MISS at the holding point with component currents and voltages.

$$V_{\rm ox} = \epsilon_{\rm ox} \cdot d_{\rm ox} = 30 \times 10^{-8} \times 10^{6} = 0.3V$$

Hence  $V_{H}$  is of the order of

$$V_{\rm H} \simeq 0.3 + 0.5 + 0.47 + 0.34 \simeq 1.8V$$

It is also important to note that in the ON state, the I-V characteristic is determined by the  $p^+$ -n junction. In other words, it is almost identical to the familiar forward bias characteristic of a  $p^+$ -n junction with a voltage displacement due to  $\psi_s$  and  $V_{ox}$ .

### 2.1.4 The Switch-Off Möde

When the voltage across the device in the ON state is reduced, the current flowing through the device decreases. The decrease in the device current necessarily implies a decrease in the injected hole current,  $I_{pj}$ , from the  $p^+$  substrate to the Si-SiO<sub>2</sub> interface. When the rate of hole supply to the silicon surface drops below a critical value, i.e.  $I < I_H$ , then the existing voltage across the tunnel oxide drains the holes from the Si-SiO<sub>2</sub> interface faster than they are supplied by the  $p^+$ -n junction. The reduction of hole charge at the interface reduces the oxide voltage, which in turn reduces the electron tunnel current,  $I_{nt}$ . The reduction in  $I_{nt}$  lowers the bias across the  $p^+$ -n junction which causes a decrease in  $I_{pj}$ . This negative feedback mechanism drains all the inversion charge from the Si-SiO<sub>2</sub> interface, causing the depletion 'region to expand and the device reverts to the OFF state. Alternatively, the voltage drop

across  $R_L$ ,  $V_j$  and  $V_{ox}$  decrease now appearing across  $\psi_s$ . Furthermore, the current is again limited by the reverse-biased MIS diode and not the p<sup>+</sup>-n junction or the load resistor.

El-Badry and Simmons (2-4) have shown that there is excellent correspondence between the predictions of the "ideal" PT theory and the observed behaviour of MISS devices fabricated on n epilayers of relatively low doping ( $\sim 10^{14}-10^{15}$  cm<sup>-3</sup>).

## 2.2 THE "NON-IDEAL" PUNCH-THROUGH MODE

As stated earlier the class of devices that switch before the surface depletion region actually extends up to the  $p^+$ -n depletion edge, are said to be operating in the "non-ideal" punch-through mode, i.e.  $V_s < V_{PT}$ .

## 2.2.1 The Regenerative Feedback Mechanism (RFM)

Consider a MISS biased in the same manner as shown in the inset of Figure 2.1a, i.e. the metal biased negatively with respect to the  $p^+$  substrate, effectively reverse biasing the MIS diode and forward biasing the  $p^+$ -n junction. The feedback loop inherent in the system is established as follows: Let the voltage drop across the  $p^+$ -n junction,  $V_j$ , be incremented by a small amount. Extra holes are thus injected from the  $p^+$  region to the Si-SiO<sub>2</sub> interface. If the hole current is tunnel-limited, a build-up of the inversion charge takes place with a concomitant increase in the voltage drop across the in-sulator,  $V_{ox}$ , and, hence, in the electron-tunnel current,

.33

$I_{nt}$ . The augmented  $I_{nt}$  flows across the p<sup>+</sup>-n junction turning it still further on. The feedback loop is thus a regenerative one. Whether the process carries on until the device switches from the OFF to the ON state, or a steady state is reached in the OFF state itself is dependent on the strength of the RFM. In particular, Habib and Simmons (2-4) have identified the criterion for switching to be when the open loop gain (G) of the device equals unity where G is defined as follows,

$$G = \frac{\Delta I_{nt}}{\Delta I_{rj}}$$

= 1 at switching.

where  $\Delta I_{nt}$  = incremental change in electron tunnel current, and

$\Delta I_{rj}$  = resultant change in junction recombination current. The negative resistance region as explained by the RFM is the subject of discussion in the next section.

## 2.2.2 The Negative Resistance Region

Consider the feedback loop  $\Delta I_{nt_1} \rightarrow \Delta I_{rj} \rightarrow \Delta V_j \rightarrow \Delta I_{pj} (\simeq \Delta I_{pt}) \rightarrow \Delta p(o) \rightarrow \Delta V_{ox} \rightarrow \Delta I_{nt_2}$ , where  $\Delta I_{nt_1}$  is the initial increment in  $I_{nt}$  and  $\Delta I_{nt_2}$  is the increase in  $I_{nt}$  subsequently caused by the increase in the oxide voltage. If  $\Delta I_{nt_2}$  is less than  $\Delta I_{nt_1}$ , then the system tends to achieve a steady state in the OFF state itself, with the increments in  $I_{nt}$  caused by the regenerative feedback loop swiftly decaying to zero. However, if the increase in electron tunnel current,

$\Delta I_{nt_2}$ , caused by the RFM is larger than the initial increment  $\Delta I_{nt_1}$  then a"run-away" increase in current fuelled by the RFM occurs, increasing the voltage drops across  $R_L$  ( $V_R$ ), the tunnel-oxide ( $V_{ox}$ ) and the p<sup>+</sup>-n junction ( $V_j$ ). Since this voltage redistribution occurs at a fixed applied voltage ( $V_A$ ), the voltage across the device, V, has to decrease to satisfy the voltage relationship across the device. This decrease in V accompanied by an increase in current gives rise to the negative resistance behaviour observed. The decrease in the voltage, V, across the device is manifested in a decrease in the surface potential,  $\psi_s$ , the electrons necessary to fill the donor states being supplied by  $I_{nt}$ .

Summarising, switching occurs when  $\Delta I_{nt_2}$  is greater than  $\Delta I_{nt_1}$ . Neglecting recombination in the neutral epilayer one can write the following series of equations to derive the open loop gain of the system

$$\Delta I_{nt_{1}} = \Delta I_{rj}$$

$$\Delta I_{pt} = \Delta I_{pj}$$

$$\Delta I_{nt_{2}} = G_{ox}, \text{ the gain of the oxide}$$

$$\frac{\Delta I_{pj}}{\Delta I_{rj}} = G_{j}, \text{ the gain of the junction}$$

$$G \equiv \frac{\Delta I_{nt_{2}}}{\Delta I_{nt_{1}}} = \frac{\Delta I_{nt_{2}}}{\Delta I_{rj}}$$

$$= 1 \text{ at switching.}$$

The switch-off mode is identical to the mechanism explained in Section 2.1.4.

### 2.3 TWO-DIMENSIONAL EFFECTS

The punch-through theory and the more rigorous regenerative feedback theory of Habib and Simmons (2-4) adequately explain the observed I-V characteristics of large area MISS devices (>100 x  $100\mu^2$ ). However, as the tunnel-oxide areas get progressively smaller the MISS characteristics cannot be explained by either of the above models. The primary reason for the strong area dependence of the MISS characteristics is that as the device dimensions become comparable to the epilayer thickness current fringing plays a dominant role in determining device behaviour. Neither of the above-mentioned models take such two-dimensional effects into account and thus cannot account for the strong area

The following section will deal exclusively with explaining the variation of device characteristics with area.

### 2.3.1 The Effect of Device Area

To study the two-dimensional nature of the MISS, devices were fabricated on materials with the following specifications: Material: n epitaxial on p<sup>+</sup> substrate Crystal Orientation: <100> Epilayer resistivity: 10.8  $\Omega$ cm (N<sub>d</sub> = 42x10<sup>14</sup> cm<sup>-3</sup>) Substrate resistivity:  $\sim 0.005 \Omega$ cm (N<sub>g</sub> = 10<sup>19</sup> cm<sup>-3</sup>)

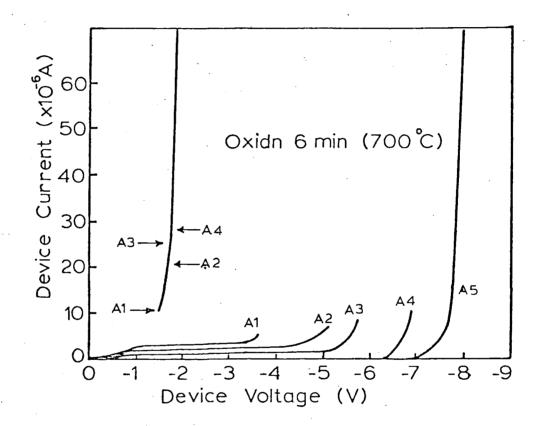

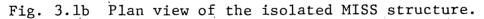

The field oxide employed was a  $\sim 5000$  Å SiO<sub>2</sub> film, thermally grown in wet oxygen at  $1100^{\circ}$ C. The tunnel-oxide was grown at  $700^{\circ}$ C in dry oxygen for 6 minutes. The tunnel oxide areas were 160 x  $160\mu m^2$ , 100 x 100  $\mu m^2$ , 80 x 80  $\mu m^2$ , 40 x 40  $\mu m^2$  and 20 x 20  $\mu m^2$ . Aluminium was the metal used for both the gate electrode and the back contact. Details of the fabrication techniques employed are presented in Chapter 3.3.

The DC characteristics of the devices differed substantially from one device area to the next. Whereas the largest area device A1, (160 x  $160\mu m^2$ ) switched at the low voltage of 3.5V (see Figure 2.2 ), the smallest area device, A5 (20 x  $20\mu m^2$ ) did not show any switching behaviour at all (Figure 2.2). It is also apparent from Figures 2.2 that the switching voltage of the devices monotonically increased as the tunnel oxide area decreased. This, we postulate, is due to the increased current fringing which occurs in smaller dimension devices.

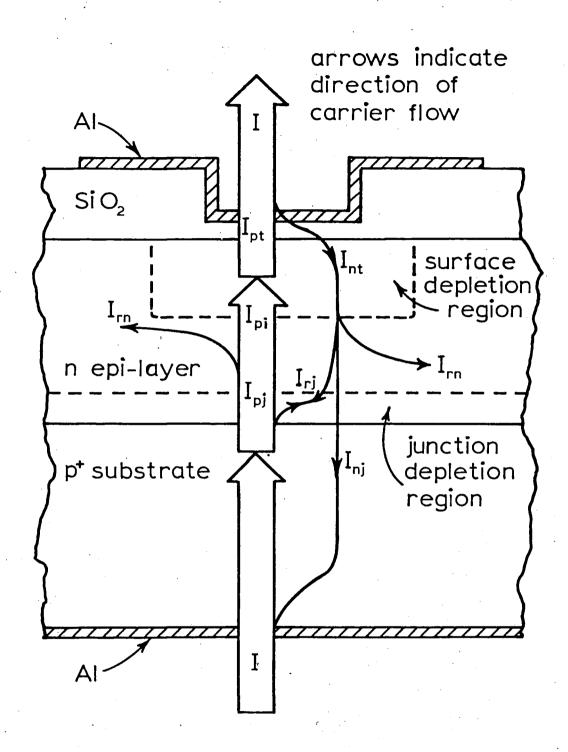

In Figure 2.3 a small tunnel oxide area device is shown schematically just prior to switching. The fringing effects are included as current lines intercepting an effective  $p^+-n$  junction area  $A_j$ . This effective junction area is larger than the tunnel oxide area,  $A_{ox}$ , by the additional fringing area,  $A_{f^\circ}$  Or, equivalently,

$$A_j = A_{ox} + A_f$$

(2.10)

| TUG | are | cas c | 116 | -           | ົ່              |

|-----|-----|-------|-----|-------------|-----------------|

| •   | A1  | 160   | x   | 160         | μm <sup>∠</sup> |

|     | A2  | 100   | x   | 100         | μm <sup>2</sup> |

|     | A3  |       |     | 80          |                 |

|     | A4  | 40    | x   | 40          | $\mu m^2$       |

|     | A5  | 20    | x   | 20 <u>.</u> | $\mu m^2$       |

|     |     |       |     |             |                 |

38

Ċ

Schematic diagram of small-area MISS, illustrating the effect of current fringing. Fig. 2.3

•

It is important to note that the extent of fringing is dependent mainly on the doping concentration,  $N_d$ , in the epilayer and the diffusion coefficient,  $D_n$ , of electrons, which are both constant for all the devices. Hence the fringing length is essentially constant from one device to the next.

The electron tunnel current,  $I_{nt}$ , is dependent on the tunnel oxide area,  $A_{ox}$ . Hence as the device area decreases, the tunnel current  $I_{nt}$  also decreases. Neglecting recombination in the neutral epilayer and the electron diffusion current across the junction (see Chapter 4 for details),  $I_{nt}$  is essentially absorbed in the p<sup>+</sup>-n junction as a recombination current. Equivalently,

$$I_{nt} \simeq I_{rj}$$

(2.11)

Hence the reduction in  $I_{nt}$  is equivalent to a decrease in  $I_{rj}$ . Furthermore,  $I_{rj}$  is related to the bias,  $V_j$ , across the junction by (2-1)

$$I_{rj} = \frac{qA_jn_iW_j}{2\tau_1} exp(\frac{qV_j}{2kT})$$

where  $A_j = A_{ox} + A_f$   $W_j = the p^+ - n$  junction depletion width and  $\tau_1 = the$  recombination lifetime in the  $p^+ - n$  junction.

For small area devices  $(A_{ox}^{<<}A_{f})$ ,  $A_{j}$  remains essentially unchanged from one device to the next. Hence the decrease in  $I_{rj}$ cannot be accounted for by the insignificant change in  $A_{j}$ . It

therefore has to manifest itself in a reduced bias across the junction. This decreased bias will weaken the RFM. Since the RFM is weakened, the gate has to be biased more strongly negative for the open loop gain to become unity, i.e. for the device to switch. In other words, the smaller the device area, the weaker is the RFM and hence higher the switching voltage,  $V_s$ , to a maximum of  $V_s \approx V_{PT}$ .

However, if the devices are sufficiently small, the RFM will be weakened to the point when the gain of the feedback loop can never reach unity which is necessary for switching (see section 2.2.2). Hence even after punch-through the MISS will remain in a deeply depleted state with the increase in current being mainly due to recombination, preventing the gain from ever reaching unity and thus not allowing the device to switch (device A4, Figure 2.2).

The above arguments adequately explain the area dependence of the device switching characteristics which are presented in Figures 2.2.

## 2.3.2 Perimeter to Area Ratio (PAR) Effects

Even though not explicitly stated, intrinsic in the arguments presented in the previous section is the fact that as the area of the devices decreased, the PAR of the devices increased, as is apparent from the following relation,

PAR =

$$\frac{4(A_{ox})^{\frac{1}{2}}}{A_{ox}} = \frac{4}{(A_{ox})^{\frac{1}{2}}}$$

Hence the switching voltage,  $V_s$ , of a device with a particular tunnel-oxide thickness,  $d_{ox}$ , increases as the PAR increases.

To identify that this indeed was the case, a set of devices (B1-B5) was fabricated on the same material as devices A in the same run, with the same tunnel oxide thickness. The area of these devices was kept constant (160 x  $160\mu m^2$ ) but the PAR was varied as listed below

| Device<br>No. | Device<br>Dimensions (µm <sup>°</sup> ) |   | PAR_1 (µm <sup>1</sup> ) |

|---------------|-----------------------------------------|---|--------------------------|

| B1            | 160 x 160                               |   | 0.025                    |

| B2            | 320 x 80                                |   | 0.032                    |

| B3            | 510 x 50                                |   | 0.044                    |

| B4            | 850 x 30                                |   | 0.069                    |

| B5            | 1280 x 20                               | • | 0.102                    |

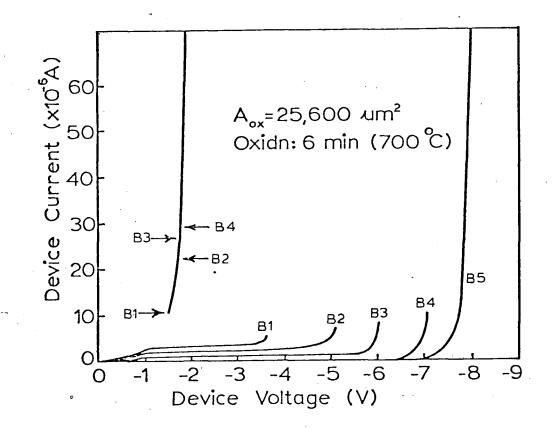

The I-V characteristics of these devices are presented in Figure 2.4. It can be seen that for devices with constant area and identical tunnel oxide thickness, the switching voltage does indeed increase with increasing PAR (indicative of a weakening RFM) until device B5 which does not exhibit any switching behaviour. This trend is what was predicted from the preceding arguments and demonstrates the need for a comprehensive two-dimensional model to adequately predict the behaviour of small area devices.

Fig. 2.4 I-V characteristics illustrating the effects of increasing tunnel-oxide perimeter for the 25,600  $\mu$ m<sup>2</sup> area device: (B1) 640  $\mu$ m, (B2) 800  $\mu$ m, (B3) 1120  $\mu$ m, (B4) 1760  $\mu$ m and (B5) 2600  $\mu$ m.

REFERENCES

- 2-1 A.S.Grove: 'Physics and Technology of Semiconductor Devices', J.Wiley (1967).

- 2-2 G.Persky: 'Thermionic Saturation of Diffusion Currents in Transistors', Solid-St. Electron., 15, 1345 (1972).

- 2-3 A.E1-Badry & J.G.Simmons: 'Experimental Studies of Switching in Metal Semi-Insulating n-p<sup>+</sup> Silicon Devices', Solid-St. Electron., 20, 963 (1977).

- 2-4 S.E-D Habib & J.G.Simmons: 'Theory of Switching in p-n-Insulator (Tunnel)-Metal Devices. Part I: Punch-Through Mode', Solid-St. Electron., 22, 181 (1979).

### CHAPTER 3

## EXPERIMENTAL TECHNIQUES

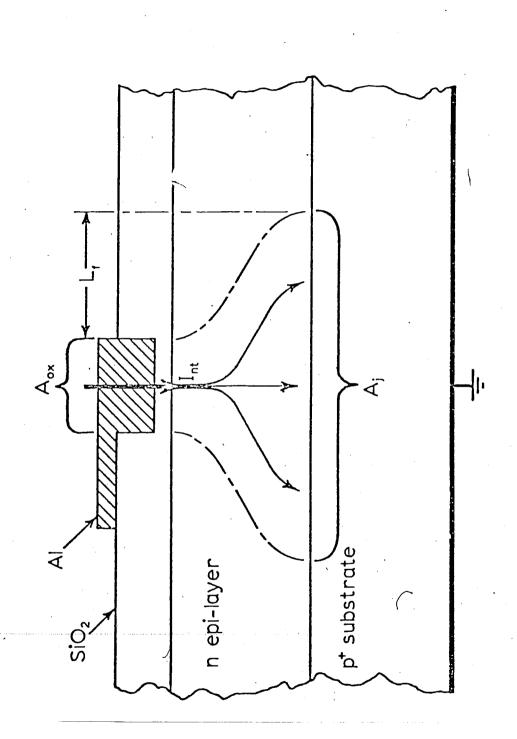

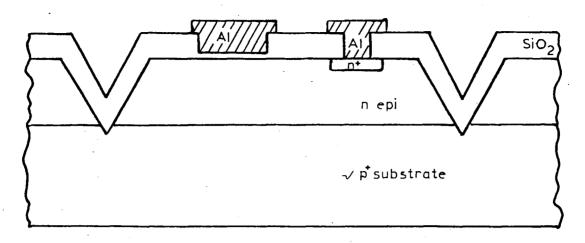

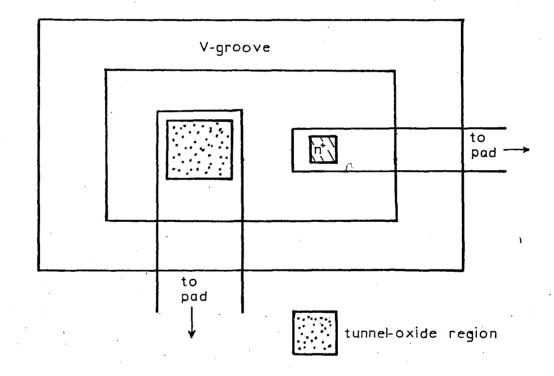

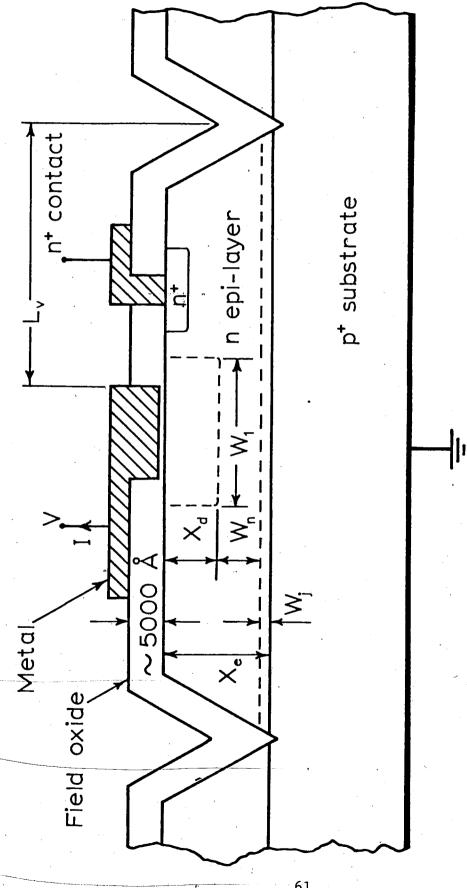

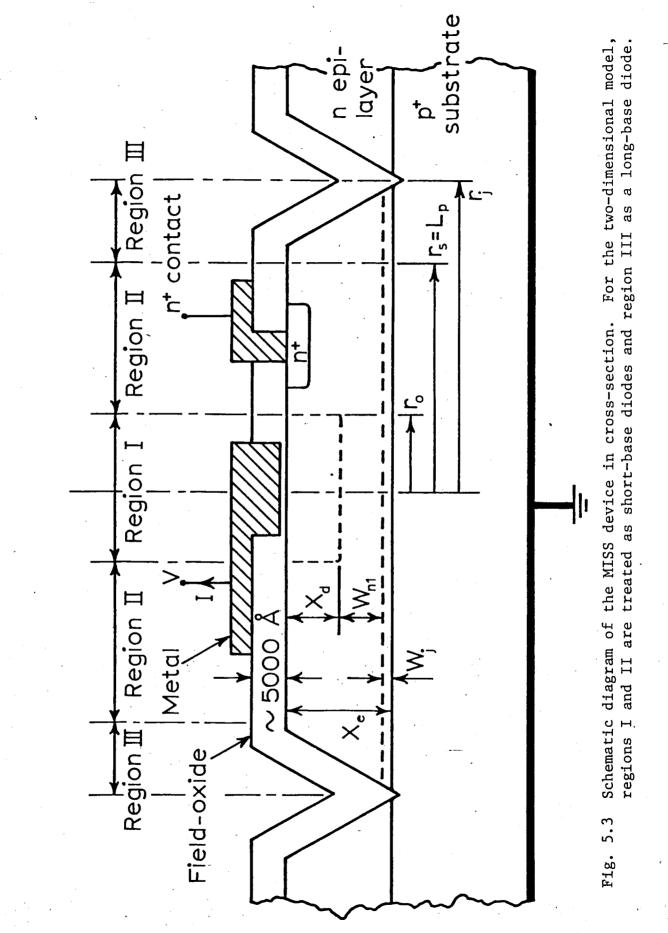

In this chapter the processes used to fabricate the MISS devices characterised during the course of this work are described in detail. The device structure fabricated is shown in cross-section in Figure 3.1a and the plan view in Figure 3.1b.

The devices were fabricated on two batches of silicon epitaxial wafers with the following specifications:

(i) n-epitaxial material of starting thickness 7.4 $\mu$ m and resistivity 10.8 $\Omega$ cm grown on a p<sup>+</sup><100> substrate of resistivity 0.005-0.01 $\Omega$ cm (Batch 'X').

(ii) n-epitaxial material of starting thickness 9.7 $\mu$ m and resistivity 18.0  $\Omega$ cm grown on a p<sup>+</sup><100> substrate of resistivity 0.06-0.12 $\Omega$ cm (Batch 'L').

Besides fabrication, also described in this chapter is the experimental set-up used to make the DC current-voltage measurements of the MISS.

## 3.1 FABRICATION PROCEDURE

## 3.1.1 Masking Oxide Growth

The wafers were given a standard RCA pre-furnace clean (3-1). The details of this process are listed in Appendix A. The masking

Fig. 3.1a Cross-sectional view of the isolated MISS structure.

oxides were thermally grown in a resistance-heated single-walled quartz tube in an ambient of wet oxygen under the following conditions:

1100°C Furnace temperature: 95<sup>°</sup>C Water temperature (bubbler): Oxygen flow rate: 1 l/min Oxidation time: 10 mins.

These conditions provided an oxide thickness of approximately A, which was sufficient to mask against any phosphorous 2500 diffusion during deposition and drive-in (3-2).

## 3.1.2 Phosphorous Deposition

The regions for phosphorous deposition were defined using the photolithographic techniques listed in Appendix B. The oxide was etched from these regions in a solution of buffered HF, comprising a mixture of HF reagent (49%) and NH<sub>4</sub>F reagent (40%), supplied by Ashland Chemicals. The photoresist was removed by boiling in acetone.

The wafers were then cleaned by process A. Next, phosphorous pre-deposition was carried out under the following furnace conditions:

950<sup>°</sup>C Furnace temperature: Furnace ambient: N<sub>2</sub> flow rate: 1 l/min. Phosphorous source:

Grade PH-1000 Planar Diffusion Source (Carborundum)

Deposition time:

47

20 mins.

<sup>N</sup>2

Four-point-probe measurements made on a test wafer diffused at the same time gave a sheet resistivity value of approximately  $20^{\Omega/\Box}$ . This agreed very well with the data sheets supplied by the Carborundum Company. Immediately after the deposition, the drive-in was done at 1100°C in  $O_2$  (flow rate 1  $\ell/min$ ) for 10 mins. All the oxide was then stripped off in a 30% HF solution.

### 3.1.3 V-Groove Etching

After etching the masking oxide, the wafers were rinsed in DI water and a masking oxide for the V-groove etching was grown under the same conditions as described in Section 3.1.1. The V-groove areas were defined photolithographically (Appendix B) and the oxide was etched from these regions in buffered HF.

Four V-groove geometries were used:  $0.64 \times 10^{-4} \text{ cm}^2$  (80 x 80µm<sup>2</sup>),  $10^{-4} \text{ cm}^2$  (100 x 100µm<sup>2</sup>), 1.96 x  $10^{-4} \text{ cm}^2$  (140 x 140µm<sup>2</sup>) and 4.8 x  $10^{-4}$  cm<sup>2</sup> (220 x 220µm<sup>2</sup>), designated as devices A, B, C and D respectively. A control epitaxial device was also prepared on the same slice (which was not isolated), labelled the N device.

The V-grooves were fabricated using an anisotropic etching solution composed of 40 gms. of KOH, 60 ml of DI H<sub>2</sub>O and 100 ml of propanol. The temperature of the etch was maintained at  $65^{\circ}C$ . Etching occurs along the <100> planes of silicon, resulting in the formation of an effectively self-terminating V-groove with the sides oriented at an angle of 54.7° with the surface. Since amorphous SiO<sub>2</sub> is etched by the solution at a much lower rate than

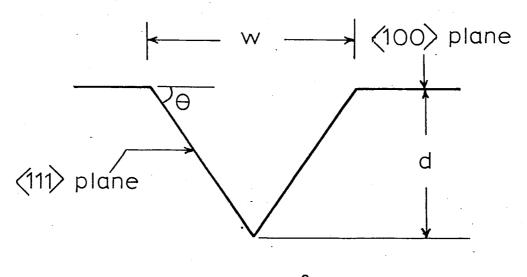

<100> silicon, a relatively thin (500-1000 Å) layer of oxide can act as a mask for the etching procedure. The direction of the V-groove must be aligned parallel or perpendicular to the <110> direction, on the surface of the slice. The depth to which the groove extends is determined by the width of the oxide window. The depth, d, is approximately 0.71 times the width, w, of the silicon surface exposed to the etchant, i.e.

$d = (\frac{w}{2}) \tan 54.7^{\circ}$

A schematic of a V-groove in cross-section, defining the parameters d and w is shown in Figure 3.2.

After the V-grooves were etched, the masking oxide was removed in a solution of 30% HF.

Note: The V-groove etch also etches  $\sqrt{7}\mu$  from the back of the silicon wafer, effectively removing the junction formed by phosphorous diffusing into the back. Hence the need for a separate process to remove the junction is eliminated.

3.1.4 Pattern Definition for Tunnel-Oxide Areas

Following the etching of the masking oxide, the wafers were given a pre-furnace clean (Appendix A). A field oxide of thickness  $\sim 5000$  Å was then thermally grown on the wafers under the same furnace conditions as detailed in Section 3.1.1 except for an increase in the oxidation time to 40 mins. It is essential that the field

θ=54.7°

Fig. 3.2 Schematic of a V-groove defining the depth d, and width w of the groove.

oxide be thick enough to give flat-band voltages ( $V_{FB} = \phi_{MS} - \frac{Q_{SS}}{C_{ox}}$ ) greater than the punch-through voltage of the device. This is to prevent premature switching of the device triggered by inversion under the field oxide, before the onset of positive feedback of holes from the p<sup>+</sup> substrate. A detailed study of the effect of field oxide fabrication conditions on device switching has been carried out by Duncan et al. (3-3). Test MOS capacitors fabricated during the same run yielded flat-band voltages of  $\sim$ 18V, much larger than the punch-through voltages of both the X( $V_{PT}$ ) = 6 V) and theL devices ( $V_{PT} = 10.5$ V).

While photoresisting the V-grooved surfaces, it was noticed that spinning the photoresist at the conventional 4000 rpm caused the resist to thin at the edges of the V-groove and even completely break in some cases. To improve the adhesion the photoresisting procedure (B) was altered in three ways:

(i) After field oxide growth the wafers were baked in a single-walled quartz tube furnace at 700°C in dry 0<sub>2</sub> (1 ½/min) for 15 mins. This treatment removed most of the water from the oxide surface that may have remained after the wet field oxide growth. It is well established that even traces of water (in particular OH<sup>-</sup> ions) on the wafer surface causes a drastic degradation in the adhesion properties of the resist. The post-oxidation "drying" just described improved the adhesion of the photoresist dramatically.

(ii) The photoresist spinning speed was reduced to 2000 rpm. This resulted in a thicker film of photoresist over the wafer. Conse-

quently, the thinning of the film that results at the V-groove edge did not lead to a break in the resist as seen before with films spun at 4000 rpm.

(iii) Because of the increase in resist film thickness, the exposure time was increased to 45 secs to ensure that the full depth of the resist film was exposed.

Finally, the oxide was etched away from the desired areas in buffered HF and the photoresist removed by boiling in acetone.

### 3.1.5 Tunnel-Oxide Growth

After etching the oxide, the wafers were given a standard prefurnace clean (Appendix A) with the following variation. After boiling in the peroxide-HCl solution (step IV), the wafers were rinsed in DI water and then blown dry in  $N_2$ , prior to the final HF etch. Secondly, before growing the tunnel-oxide, the wafers were baked in dry  $N_2$  (1  $\ell$ /min.) at 700°C for 10 mins. in a single-walled resistance heated quartz tube furnace. These two processes were found to be essential in the fabrication of satisfactory switching devices with reproducible characteristics.

The first process ensures that the thin oxide grown during the peroxide cleans, over the regions defined for tunnel oxide growth was completely removed by the final HF etch. Hence, a fresh silicon surface (save native oxide) was exposed for tunnel-oxide growth.

The main purpose of the N<sub>2</sub> bake-out was to remove residual water from the wafer surface after the DI water rinse. Traces of

water can critically affect the oxidation rate of the silicon surface especially when the oxide thickness is of the order of 20 Å. Hence, to have any control on the oxidation rate the silicon surface must be absolutely dry, and the N<sub>2</sub> bake-out seemed to accomplish the purpose satisfactorily. However, there were no detailed studies carried out during the course of this work to determine the exact effect the N<sub>2</sub> treatment had on the silicon surface.

The tunnel-oxide growth was done in a single-walled resistance heated furnace in dry  $0_2$ . The furnace conditions employed for the tunnel-oxide growth are listed below.

| Furnace temperature: | 700 <sup>°</sup> C                                  |

|----------------------|-----------------------------------------------------|

| Ambient:             | dry 0 <sub>2</sub>                                  |

| Flow rate:           | 1 l/min.                                            |

| Oxidation times:     | 6 mins. X3; L3<br>8 mins. X4; L4<br>12 mins. X4: L5 |

#### 3.1.6 First Metallization

In order to obtain reproducible switching characteristics, immediately after the tunnel-oxide growth, the wafers were loaded in a vacuum deposition system for aluminium deposition of the cathode electrode of the MISS device. However, as the metallization was done immediately after the tunnel-oxide growth, a thin oxide also covers the contact hole regions of the n<sup>+</sup> diffusion. Hence, the oxide has to be removed and another layer of aluminium deposited to obtain good ohmic contact. Thus, two metallizations are necessary

for the final fabrication of the device.

The aluminum used for evaporation was of 99.999% purity. Prior to loading into the filament the aluminum was cleaned using process C. Filament evaporation was the technique employed and the metallization was performed at a pressure of  $\sim 10^{-6}$  torr. The resultant Al film thickness was  $\sim 5000$  Å.

### 3.1.7 Removal of the Thin Oxide over Contact Holes

Immediately after metallization, the wafers were photoresisted in a manner similar to that described in Section 3.1.4. Aluminium was etched away from the contact hole areas by dipping the wafers in PAN etch, which was maintained at a temperature of 45°C. The composition of the etch is presented below. The percentages by volume are

| Phosphoric acid: | 80% |

|------------------|-----|

| Acetic acid:     | 5%  |

| Nitric acid:     | 5%  |

| DI water:        | 10% |

The phosphorous pre-deposition mask was used for exposing the n areas to the PAN etch. After the Al etch the wafers were rinsed in DI water and then etched in 10% HF for 10 secs to remove the tunneloxide grown over the contact areas. This etching was monitored from the back of the wafer (which also has a layer of tunnel-oxide) and is complete when the back surface becomes hydrophobic.

## 3.1.8 Second Metallization and Electrode Definition

After the HF etch, the wafers were rinsed in DI water, then boiled in acetone to remove the photo-resist and a second layer of aluminium evaporated in identical fashion to the process described in Section 3.1.7. Photoresist was applied to the wafers immediately after the evaporation, and the electrodes defined using the mask for the final electrode patterns. The aluminium etching conditions were the same as in the previous section.

After removal of the photoresist by boiling in acetone, Al was evaporated (Section 3.1.7) onto the back of the wafers to provide a good ohmic contact.

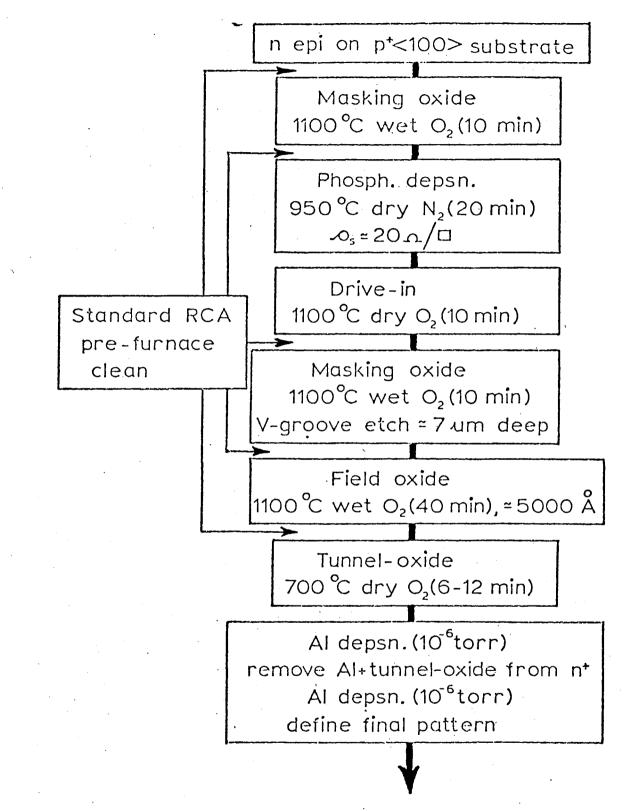

The complete fabrication procedure is presented as a flowchart in Figure 3. 3.

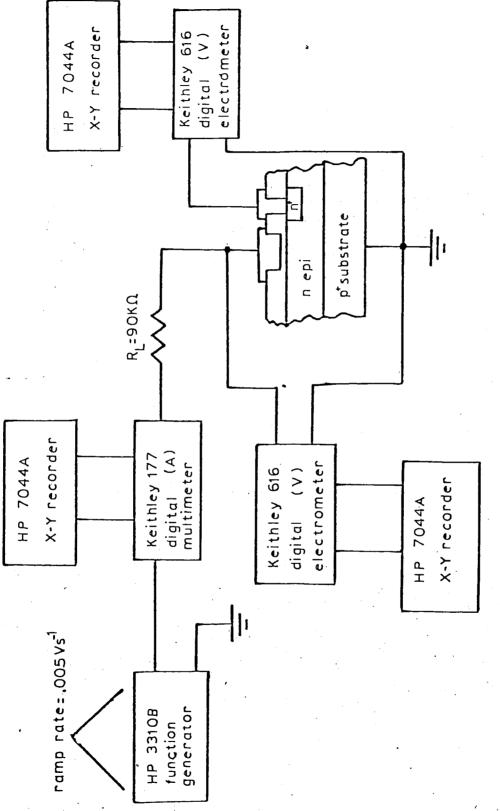

### 3.2. MEASUREMENT TECHNIQUE

The D.C. two-terminal I-V characteristics of the MISS were obtained by applying a very slow voltage ramp (0.005 V S<sup>-1</sup>) to the device via a HP 3310B function generator. A load resistor  $R_L$ =90K $\Omega$ was kept in series with the device to limit the current in the ON state. The measurement configuration used is shown in Fig. 3.4.

The voltage across the device was measured using a Keithley 616 digital electrometer with an input impedance  $R_{in} = 10^{14} \Omega$ . The high input impedance ensured that the electrometer would not shunt the MISS in the OFF state ( $R_{off} \approx 10^6 \Omega$ ) and hence lead to erroneous measurements. The current through the device was measured

via a Keithley 177 microvolt digital multimeter. A graphical plot of the I-V characteristics was obtained by feeding the analog outputs from the multimeter and electrometer to the input terminals of a HP 7044A X-Y recorder.

Fig. 3.3 Flow chart of the fabrication procedure employed for the isolated 3-terminal MISS, i.e. with an n diffusion.

# REFERENCES

| 3-1 | W. Kern and D. A. Poutinen, R.C.A. Rev. 31, 187 (1970).                                                                                                                                                                                 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-2 | H. F. Wolf, "Silicon Semiconductor Data," Pergamon<br>Press, 1969.                                                                                                                                                                      |

| 3-3 | K. A. Duncan, P. D. Tonner, J. G. Simmons and L.<br>Faraone, "Characteristics of Metal/Tunnel-oxide/n/p <sup>+</sup><br>Silicon Switching Devices: Part I: Effects of Device<br>Geometry and Fabrication Processes," (to be published). |

## CHAPTER 4

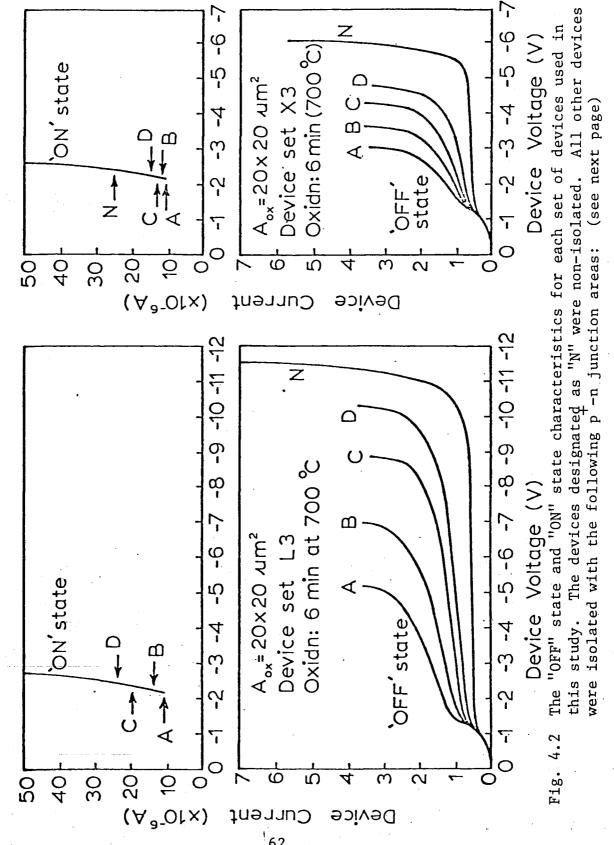

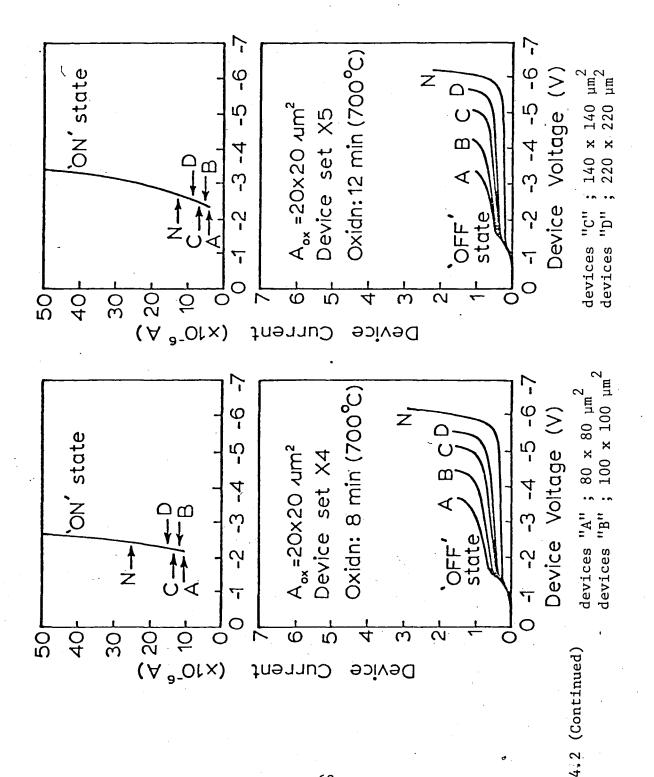

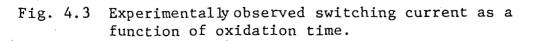

In this chapter the experimentally observed DC two-terminal characteristics of the isolated MISS is presented. The I-V characteristics of non-isolated devices, labeled "N," are also discussed to bring out their substantially different behaviour from the isolated MISS devices fabricated under exactly the same conditions (see Chapter 3 for fabrication details).

Figure 4.1 shows a schematic of the isolated MISS in crosssection defining the various parameters useful in qualitatively understanding the observed I-V characteristics. It is important to note that the device current is considered positive flowing <u>away</u> from the cathode as shown in Fig. 4.1. The reason for this convention is because the natural direction of current flow in the device is in this direction and adoption of the above convention helps eliminate a preponderance of negative signs in the writing of current-voltage equations.

· 60

Schematic diagram of the isolated MISS device in cross-section. Fig. 4.1

#### 4.1 EXPERIMENTAL CURRENT-VOLTAGE CHARACTERISTICS

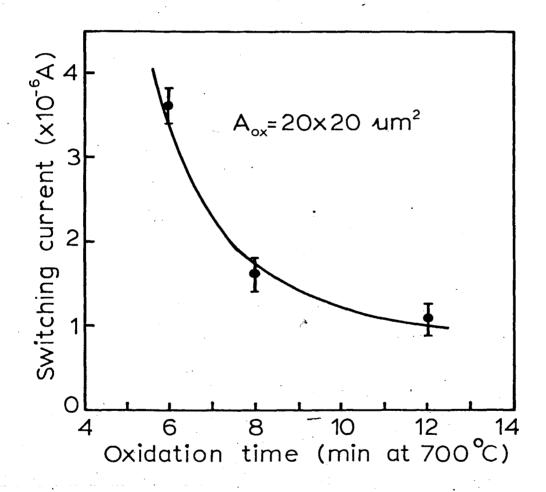

The experimental I-V curves for each set of devices are illustrated in Fig. 4.2. For ease of comparison, the characteristics are divided into ON state and OFF state.