## Lehigh University Lehigh Preserve

Theses and Dissertations

1-1-1976

# A survey of error-correcting codes for computer applications.

Dhriti Kapur

Follow this and additional works at: http://preserve.lehigh.edu/etd Part of the <u>Computer Sciences Commons</u>

## **Recommended** Citation

Kapur, Dhriti, "A survey of error-correcting codes for computer applications." (1976). Theses and Dissertations. Paper 2023.

This Thesis is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Lehigh Preserve. For more information, please contact preserve@lehigh.edu.

## A SURVEY OF ERROR-CORRECTING CODES

FOR

### COMPUTER APPLICATIONS

by

Dhriti Kapur

#### A Thesis

Presented to the Graduate Committee of Lehigh University in Candidacy for the Degree of Master of Science

in

Computer Science

Lehigh University

1976

16

ProQuest Number: EP76296

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest EP76296

Published by ProQuest LLC (2015). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

> ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 - 1346

This thesis is accepted and approved in partial fulfillment of the requirements for the degree of Master of Science.

lag 5, 1976 (Date)

# Professor in Charge

Chairman of the Department

٦

#### ACKNOWLEDGEMENT

The author wishes to express his gratitude to his advisor, Prof. Kenneth Kai-Ming Tzeng, for his most valuable suggestions and advice during the preparation of this thesis.

Appreciation is also expressed to Lehigh University and Prof. A. K. Susskind, Head of the Department of Electrical Engineering, for providing financial support and encouragement to pursue graduate study at Lehigh University.

## TABLE OF CONTENTS

| Chapter |              | • ×                                                                                                      | Page |

|---------|--------------|----------------------------------------------------------------------------------------------------------|------|

|         | Abst         | ract                                                                                                     | 1    |

| 1       | INTRO        | DDUCTION                                                                                                 | 3    |

| 2       | ERRO         | R-CORRECTING CODES FOR COMPUTER MEMORY SYSTEMS                                                           | 7    |

|         | 2.1          | Error Correction by Parity Checking                                                                      | 7    |

|         | 2.2          | Single-error-correcting, Double-error-<br>detecting Code for Single Bit per Card Memory<br>Configuration | 9    |

|         | 2.3          | Double-error-correcting, Triple-error-<br>detecting Code for Single Bit per Card Memory<br>Configuration | 15   |

|         | 2.4          | Error-correcting Codes for Multiple Bit per<br>Card Memory Configuration                                 | 18   |

|         | 2.5          | General Class of Maximal Codes                                                                           | 24   |

|         | 2.6          | Majority Logic Decodable Codes                                                                           | 31   |

|         | 2.7          | Summary                                                                                                  | 36   |

| 3       | ERRO<br>SYST | R-CORRECTING CODES FOR COMPUTER PERIPHERAL<br>EM                                                         | 38   |

|         | 3.1          | Single-track Correction of Magnetic Tape Unit<br>with Cyclic Redundancy Codes                            | 38   |

|         | 3.2          | Double-track Correction of Magnetic Tape<br>Unit with Cyclic Redundancy Codes                            | 45   |

|         | 3.3          | Single and Double Track Correction Using<br>Optimal Rectangular Codes                                    | 49   |

| •       | 3.4          | Error-correcting Codes for Single Channel<br>Disc Systems                                                | 57   |

|         | 3.5          | Error-correcting Schemes for Multi-Channel<br>Disc Systems                                               | 60   |

· -iv-

L

Chapter

4

5

| 3.6  | Error-correction in Photo Digital Storage<br>Systems                    | 65 <sup>-</sup> |

|------|-------------------------------------------------------------------------|-----------------|

| 3.7  | Summary                                                                 | 68              |

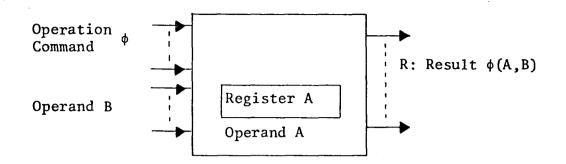

|      | R-CORRECTING CODES FOR COMPUTER ARITHMETIC<br>ESSORS                    | 69              |

| 4.1  | Nature of Errors in Arithmetic Processor                                | 69              |

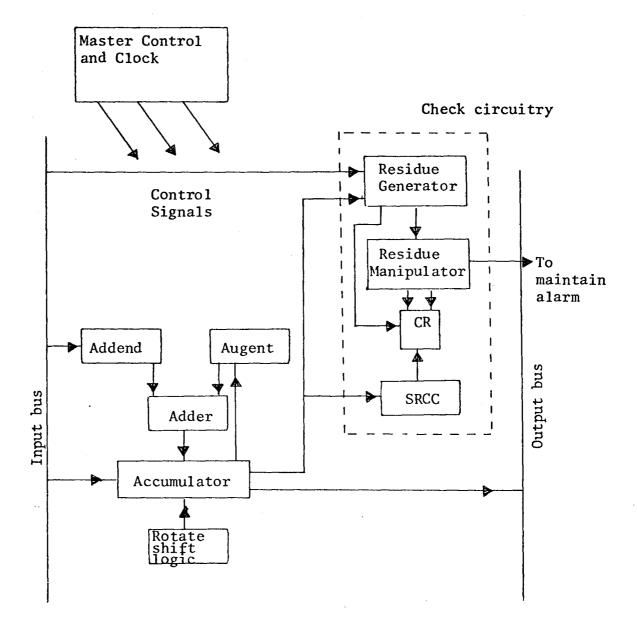

| 4.2  | Checking Arithmetic Operations Using Residue<br>Codes                   | 71              |

| 4.3  | Single Error-correction with AN Codes                                   | 74              |

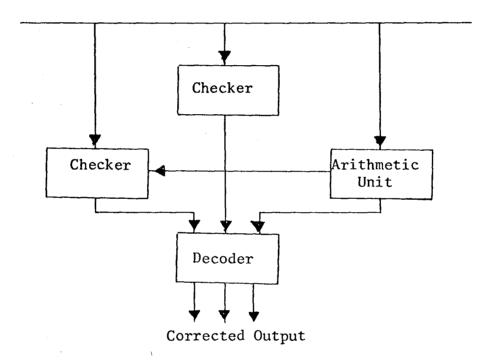

| 4.4  | Multiple-error-detection and Correction<br>with Mandelbaum Barrow Codes | 74              |

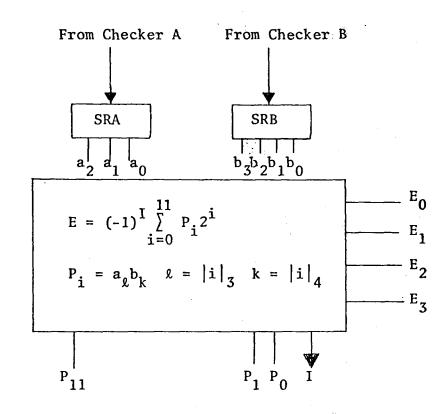

| 4.5  | Biresidue Codes for Single Error-Correction                             | 75              |

| 4.6  | Multiresidue Codes                                                      | 79              |

| 4.7  | Summary                                                                 | 84              |

| CONC | LUSIONS                                                                 | 85              |

| Refe | rences                                                                  | 86              |

| Vita |                                                                         | 88              |

Page

#### ABSTRACT

The thesis presents an investigative survey of Error-Correcting Codes suitable for application in computer environment. Errorcorrecting codes have been successfully utilized to improve reliability in transmitting information in communication systems. In recent years the phenomenol increase in information handled by digital computers has enhanced the need for computer system reliability. In the survey with respect to error-correction the overall computer system has been broadly classified into three sections, namely the computer memory system, the computer peripheral system and the central processing unit. Each section is discussed under a separate heading.

Error-correcting codes used in computer memory systems depend upon the configuration of memory. For those memories which are packaged on single bit per card basis, single error-correcting, double error-detecting Hamming type codes, double error-correcting, triple error-detecting BCH codes, and one step majority decodable codes play a useful role in increasing the reliability of memory. Byte error-correcting codes form the basis of correcting errors in memories configured as multiple bit per card. A general class of maximal codes was developed by Hong and Patel whose structure is not restricted to any homogeneous bit per card arrangement and is capable of correcting single random byte errors.

Cyclic codes formed the basis of the error-correcting scheme

-1-

in magnetic tape and disc drives which are part of the computer peripheral system. Cyclic Redundancy Code (CRC) and the Orthogonal Rectangular Code (ORC) were found applicable to magnetic tape units. In magnetic disc systems Fire codes with high speed decoding could be used for single channel. Recently Malhotra and Fisher have come up with a practical error-correcting scheme for multichannel disc systems. Reed-Solomon codes were best suited for photodigital mass storage systems. The decoding scheme employed a hybrid hardware-software technique to simplify the complexity of decoding the multiple character correcting code.

In the processing unit of the computer the error-correcting codes used are arithmetic codes. The best known among these which are suitable for computer arithmetic as well as easily implementable are the residue codes. The Biresidue code proposed by Rao involved circuit redundancy of the magnitude of 30-35 percent of the main processor which is definitely more economical than duplicating redundant schemes like Triple Modular Redundancy.

A desirable feature of the error-correcting codes used in computer systems is the fast and simple encoding and decoding procedure. To ensure efficient operation the speed of implementation of the code must be comparable to the speed of operation of the computer system. Most of the codes surveyed in this thesis have been found suitable in computer environment with existing trade-off between redundancy and decoding time.

-2-

#### CHAPTER 1. INTRODUCTION

Error-correcting codes are mathematical codes designed to encode information in such a manner that it can be decoded correctly at the receiving end in the presence of disturbance in the transmitting medium. Typical examples of transmission mediums are telephone lines, high frequency radio links, space communication links and magnetic tape units including writing and reading heads for storage systems. The codes are constructed in binary digits compatible with information handled in digital computers. Errorcorrecting codes have been used successfully in communication systems to improve reliability. The idea has been carried over to computer environment where the need for reliability in storing and processing information has assumed wide importance with increasing demand for more computer power.

The idea of increasing system reliability through hardware was first initiated by Von Neumann. In his scheme the original network was duplicated an odd number of times. If three identical copies of an original circuit are made and the output of each circuit is taken to a majority voter assumed to be perfect, then this scheme can tolerate error in one of the circuits. The introduction of extra copies required to improve reliability is called redundancy. In particular, the above scheme is known as Triple Modular Redundancy. This is equivalent to triplicating a binary digit (also called encoding) before transmission in a binary symmetric channel

- 3-

and ensuring safety of the information in the presence of single error due to disturbance in the transmitting medium or transmitting the same digit three times over certain intervals of time. The fact that some form of redundancy either in hardware, binary digits or time was needed is fundamental in the concept of system reliability.

In the field of error-correcting code the rules for encoding and decoding information can be specified a parity check matrix. For instance, if we desired to transmit 4 information binary digits  $x_1x_2x_3x_4$  we would transmit instead a binary code sequence  $y_1y_2y_3y_4y_5y_$  $y_5y_6y_7$ . This introduction of redundancy to the information digits is known as encoding. Only 2<sup>4</sup> out of the 2<sup>7</sup> possible encoded sequences would be acceptable. If two encoded output sequences differ in at least 3 positions, a single error will always be corrected. This is achieved by the following encoding rules.

$y_{i} = x_{i} \quad i = 1, 2, 3, 4$   $y_{5} = x_{2} \oplus x_{3} \oplus x_{4}$   $y_{6} = x_{1} \oplus x_{3} \oplus x_{4}$   $y_{7} = x_{1} \oplus x_{2} \oplus x_{4}$

where  $\oplus$  indicates mod 2 addition. The equations can be written in terms of y<sub>i</sub>

> $0y_1 \oplus 1y_2 \oplus 1y_3 + 1y_4 \oplus 1y_5 \oplus 06_6 \oplus 0y_7 = 0$   $1y_1 \oplus 0y_2 \oplus 1y_3 \oplus 1y_4 \oplus 0y_5 \oplus 1y_6 \oplus 0y_7 = 0$  $1y_1 \oplus 1y_2 \oplus 0y_3 \oplus 1y_4 \oplus 0y_5 \oplus 0y_6 \oplus 1y_7 = 0$

> > -4-

which can be compactly written as

$$\begin{bmatrix} 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 1 & 0 & 1 & 0 \\ 1 & 1 & 0 & 1 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} y_1 \\ y_2 \\ y_3 \\ y_4 \\ y_5 \\ y_6 \\ y_7 \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

It is easy to verify that each of the 16 possible encoded sequences is a solution to the above equations. The matrix of 0 and 1 is termed the parity check matrix and is usually denoted by the symbol H. It is the choice of this matrix which is important in designing Algebraic codes.

For decoding the output sequence is taken and the syndrome  $s_1s_2s_3$  is calculated

$$\begin{bmatrix} 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 1 & 0 & 1 & 0 \\ 1 & 1 & 0 & 1 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} y_1 \\ y_2 \\ y_3 \\ y_4 \\ y_5 \\ y_6 \\ y_7 \end{bmatrix} = \begin{bmatrix} s_1 \\ s_2 \\ s_3 \end{bmatrix}$$

. رست If the output sequence differs from a codeword in only one position then the vector  $[s_1s_2s_3]^T \neq 0$  and will be equal to one of the columns of the parity check matrix. Since all columns of the parity check matrix are distinct we will be able to identify the position of the error by observing the vector  $[s_1s_2s_3]^T$ . If an output

-5-

sequence 1001011 is received the syndrome vector is calculated as [111]<sup>T</sup> which indicates that the error was in the 4th position and thus we should decode to the codeword 1000011.

In general a code is represented as (n,k), where k is the number of information digits and n is the length of the code sequence. In the above example we used a (7,4) code. For a more detailed exposure to Coding Theory, the reader is referred to Peterson [1], Shu Lin [2].

Since a digital computer operates at ultra high speeds, the encoding and decoding process built in the computer system must be fast and simple. The code constructed should have minimum redundancy, maximum efficiency, and low cost to be a viable alternative in computer system reliability.

The survey deals with a large number of such codes which have been developed to meet specifically the requirements of reliability for computer memory systems, peripheral systems and Arithmetic processors. Each system is discussed under a separate heading.

#### CHAPTER 2. ERROR-CORRECTING CODES FOR COMPUTER MEMORY SYSTEMS

Capacity, access time, data transfer rate and cost/bit are basic performance considerations of mass storage devices. The demand for more storage capacity with high speed access appears as insatiable as the demand for more computer power. Improvement in capacity and access time cannot be at the expense of reliability because most users are placing their vital records under computer control.

In recent years basic technology has shifted from core memory towards monolithic memory and LSI technology decreasing random access cycle time from  $\mu$ s to ns range. However, batch fabricated or integrated memory elements are not as reliable as cores giving rise to permanent stuck type memory faults.

#### 2.1 Error Correction by Parity Checking

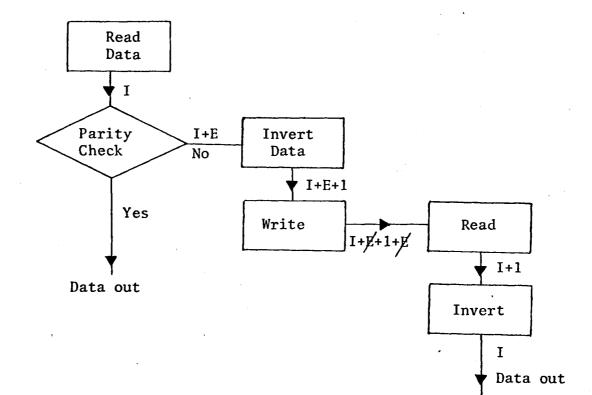

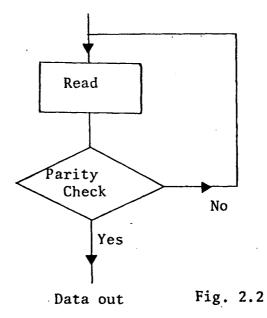

By successive read/write operation according to flow chart (fig. 2.1) odd number of errors are corrected by simple parity code. In most events economic considerations will dominate any decision to use the parity code versus reworking of components to obtain a perfect memory. On the other hand, temporary faults caused by the malfunction of the driver, sense amplifier circuits or random electromagnetic noise interference, where the errors are not reproducible, successive read operation with parity check can correct odd errors (fig 2.2). Even number of errors still remain undetected. It is here that random-error-correcting codes play an

-7-

i

-8-

important part in system reliability as compared with other techniques.

# 2.2 <u>Single-error-correcting</u>, <u>Double-error-detecting</u> <u>Code</u> for <u>Single Bit Per Card Memory</u> Configuration

The most widely used error-correcting codes in the computer memory environment are the single-error-correcting, double-errordetecting (SEC-DED) Hamming code [7] and double-error-correcting, triple-error-detecting BCH codes (DED-TED) [8]. These codes are suitable for single bit per card configuration proposed by Allen [5]. The memory is organized such that every bit of a code word appears in a single card. Errors in the card will therefore appear as single errors in the codeword.

SEC-DED Hamming codes have been used in IBM 7030 and IBM System/360 model 85, having 72 bits per word, 64 data bits and 8 check bits. These codes are slightly modified from the conventional single-error-correcting, double-error-detecting codes of distance 4 used in communication channels. The row of all 1's in the parity check matrix of the conventional code is not used. Instead the parity check matrix is constructed such that every column is of odd weight and distinct. Since any linear combination of three odd weight distinct columns of the parity check matrix is independent, i.e. they do not add to all zero, the minimum distance of the code becomes  $\geq 4$ , satisfying the condition for simultaneous detection of two errors and correction of single errors.

-9-

The syndrome

$S = eH^{T}$

(Eq.2.10)

is implemented using an Ex-OR network [7]. The number of inputs to each gate and the number of logic levels required are dependent on the number of 1's in each row of the parity check matrix. The code is therefore constructed such that the number of 1's in the parity check matrix is a minimum. It is for this reason that the overall parity check in the conventional Hamming code is avoided in the construction of SEC-DED via odd-weight-column parity check matrix, thus improving the speed of encoding and decoding. If r parity check bits are used to match the k data bits, the parity check matrix is constructed using the formula

$$\frac{\leq \mathbf{r}}{\sum_{\substack{i=1\\ \text{odd}}} {\mathbf{r} \choose i} \geq k + \mathbf{r}$$

(Eq.2.11)

where each term stands for the possible combinations of r columns of wt i. This code has minimum redundancy as the unshortened code requires the same number of check bits as the conventional Hamming code.

$$\sum_{\substack{i=1\\odd}}^{\leq r} {\binom{r}{i}} = \frac{1}{2} 2^{r} = 2^{r-1}$$

(Eq.2.12)

The syndrome corresponding to single error matches the particular column of the parity check matrix identifying its location. An

-10-

| Byte           | 1                  | 2                           | 3                             | 4                                                         | ъ                             | 9                             | 7                             | ∞                             | Check                         |

|----------------|--------------------|-----------------------------|-------------------------------|-----------------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

| Bit            | 0 1 2 3<br>4 5 6 7 | 8 9 10<br>11 12 13<br>14 15 | 16 17 18<br>19 20 21<br>22 23 | 24 25 26<br>27 28 29<br>30 31                             | 32 33 34<br>35 36 37<br>38 39 | 40 41 42<br>43 44 45<br>46 47 | 48 49 50<br>51 52 53<br>54 55 | 56 57 58<br>59 60 61<br>62 63 | 64 65 66<br>67 68 69<br>70 71 |

| s <sub>1</sub> | 1111111            | 00100110                    | 10010010                      | 00001000 00001001                                         |                               | 00010011                      | 00010011 00011100 11100000    | 11100000                      | 1000000                       |

| s <sub>2</sub> | 11100000111        | 1111111                     | 00100100                      | 00100110 01001001 10010000 0001000 0001001                | 10010000                      | 0001000                       | 11001000                      | 00111000                      | 0100000                       |

| s <sub>3</sub> | 00011100           | 11100000                    | 11111111                      | 00000 11111111 0010010 01001001 10010000 00010000 0001001 | 010010010                     | 10010000                      | 0001000                       | 11001000                      | 00000100                      |

| S <sub>4</sub> | 00010011           | 000111000 11000             | 11100000                      | 11100000 1111111 00100110                                 |                               | 010010010                     | 01001001 10010000             | 0001000                       | 0001000 0001000               |

| s<br>S         | 00010000 000       | 11001000                    | 00111000                      | 11111111 00000111 00111000                                | 1111111                       | 10010010 01100100             | 10010010                      | 10010000                      | 00001000                      |

| s <sub>6</sub> | 10010000 000       | 00001000                    | 00010011                      | 00010011 00011100 11100000 1111111 001001                 | 11100000                      | 1111111                       | 00100100                      | 10010010                      | 00100000                      |

| s <sub>7</sub> | 01001001 100       | 1001000                     | 0001000                       | 0001000 00010011 00011100 1110101111 001000               | 000111000                     | 11100000                      | 11111111                      | 01100100                      | 00000010                      |

| S <sub>8</sub> | 00100110           | 00100110 01001001           | 10010000                      | 10010000 00010000 00010011 00011100 11100000 111111       | 00010011                      | 00011100                      | 11100000                      | 1111111                       | 10000000                      |

Fig. 2.3

-11-

|       | 1                             |                    |                   |                   |           |          |               |                 | <b>1</b>                |

|-------|-------------------------------|--------------------|-------------------|-------------------|-----------|----------|---------------|-----------------|-------------------------|

| Check | 64 65 66<br>67 68 69<br>70 71 | 1000000            | 00000010          | 00000100          | 0001000   | 0001000  | 0010000       | 01000000        | 0000001                 |

| 8     | 56 57 58<br>59 60 61<br>62 63 | 1000000            | 0100000           | 00100110          | 001101000 | 11100111 | 00001100      | 11110000        | 1111111                 |

| ۷.    | 48 49 50<br>51 52 53<br>54 55 | 10001000 10001000  | 001000100         | 00100010 00100110 | 0001000   | 00000000 | 11110000      | 1111111 0000000 | 11110000 11110000 11111 |

| 9     | 40 41 42<br>43 44 45<br>46 47 | 10001000           | 0100010           | 00000010 00100000 | 0001000   | 00001111 | 1111111       | 00000000        | 11110000                |

| ю     | 32 33 34<br>35 36 37<br>38 39 | 00010110           | 01100100 01000100 | 00000010          | 00000001  | 1111111  | 11110000      | 11100111        | 00010110 00110000       |

| 4     | 24 25 26<br>27 28 29<br>30 31 | 00001111 000011000 | 0000000 111100111 | 11110000          | 1111111   | 10000000 | 0100000       | 01100100        | 00010110                |

| 3     | 16 17 18<br>19 20 21<br>22 23 | 00001111           |                   | 1111111           | 11110000  | 10001000 | 01000100      | 001000100       | 00010001                |

| 2     | 8 9 10<br>11 12 13<br>14 15   | 00001111           | 1111111           | 11110000          | 00000000  | 10001000 | 01000100      | 01000100        | 00010001                |

| -1    | 0 1 2 3<br>4 5 6 7            | 1111111 0000       | 11100000 111      | 000111000         | 00010011  | 00010000 | 10010000 0100 | 01001001 0010   | 00100110 0001           |

| Byte  | Bit                           | s1                 | s2                | s33               | S.<br>4   | s<br>5   | s<br>6        | s <sub>7</sub>  | °S<br>8                 |

Fig. 2.4

-12-

even number of 1's in the syndrome would suggest the existence of multiple even error including detection of double errors. Multiple odd error would be correctely detected if the syndrome pattern lies outside the codes parity check matrix. Otherwise a miscorrection would result. Since the probability of having one bit in error is low (of the order of  $10^{-5}$ ) the probability of having a large number of multiple error is even smaller.

#### Illustrative Example

The (72,64) code used in IBM 7030 and IBM 360 system Model 85 is the shortened version of (128,120) full length code. The 72 columns of the parity check matrix are constructed using Eq. 2.11.

$$72 = {\binom{8}{1}} + {\binom{8}{3}} + \frac{8}{5}$$

(Eq. 2.13)

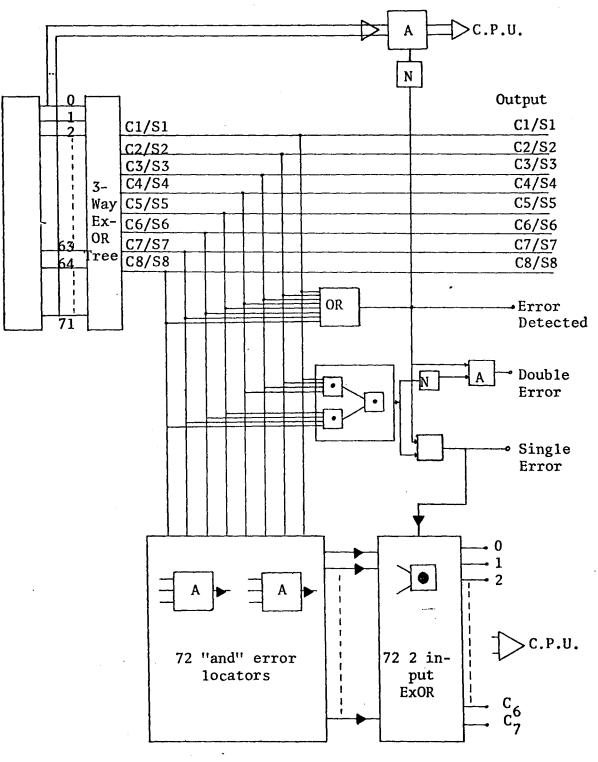

The stroke in Eq. 2.13 suggests that 8 columns of wt 5 of the possible  $\binom{8}{5}$  combinations are used. The total number of 1's in the H matrix is equal to 8 + 3 x 56 + 8 x 5 = 216. The average number of 1's in each row is equal to 216/8 = 27. This implies that if a 3-way ExOR gate is used, the number of logic levels required to generate S<sub>1</sub> is equal to 3. Two versions of the parity check matrix of the (72,64) SEC-DED codes are shown in Fig. 2.3 [7] and Fig. 2.4 [7]. A simple layout of the encoder and decoder is shown in Fig. 2.5.

The memory is assumed to be a binary symmetric channel and errors are statistically independent. The logic circuit is simple,

-13-

Fig. 2.5

-14-

fast and the code has minimum redundancy suitable for computer application.

## 2.3 Double-error-correcting, Triple-error-detecting Code for

Single Bit Per Card Memory Configuration

With a slight increase in the decoding complexity double error correction can be done, improving the reliability of the memory.

The code used is a DEC-TED BCH code. The generator polynomial is of the form  $g(x) = (1+x)g_1(x)$

$$g_1(x) = LCM(m_1(x), m_3(x))$$

(Eq. 2.14)

where  $m_i(x)$  are the minimum polynomial of  $\alpha^i$ ,  $\alpha$  being a primitive element of the Galois field  $GF(2^m)$ . The degree of  $g_1(x)$  is at most 2m. The minimum distance  $d \geq 5$ . The (1+x) factor in g(x) increases the distance of the code by one. This ensures that every column of the parity check matrix generated by  $X^i \mod g(x)$  is of odd weight. Odd weight syndromes then correspond to odd number of errors and an even weight syndrome tells that the error polynomial is of even weight. Also every code word is of even weight.

#### Example

Using the (79,64) DEC-TED BCH code for illustration, the code has 64 data bits and 15 check bits and is a shortened cyclic code of the full length code (127,112). The polynomial  $g_1(x)$  has root in GF(2<sup>7</sup>)

$$m_1(x) = 1 + x^3 + x^7$$

The roots of  $m_1(x)$  are  $\alpha$ ,  $\alpha^2$ ,  $\alpha^4$ ,  $\alpha^8$ ,  $\alpha^{16}$ ,  $\alpha^{32}$ ,  $\alpha^{64}$  $m_3(x) = 1 + x + x^2 + x^3 + x^7$

The roots of  $m_3(x)$  are  $\alpha^3$ ,  $\alpha^6$ ,  $\alpha^{12}$ ,  $\alpha^{24}$ ,  $\alpha^{48}$ ,  $\alpha^{96}$ ,  $\alpha^{65}$

$$g_{1}(x) = (1 + x^{3} + x^{7})(1 + x + x^{2} + x^{3} + x^{7})$$

$$= (1 + x + x^{2} + x^{4} + x^{5} + x^{6} + x^{8} + x^{9} + x^{14})$$

Since  $g(x) = (1+x)g_1(x)$

$= (1+x)(1+x+x^{2}+x^{4}+x^{5}+x^{6}+x^{8}+x^{9}+x^{14})$ = 1 + x<sup>3</sup> + x<sup>4</sup> + x<sup>7</sup> + x<sup>8</sup> + x<sup>10</sup> + x<sup>14</sup> + x<sup>15</sup>

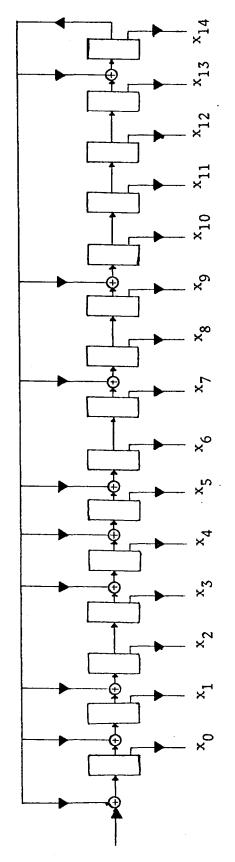

Each row of  $H^{T}$  can be generated by a feedback register characterized by g(x) (Fig. 2.6) with initial state 1000000000000. The other states are as follows:

00 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 17 1 1 0 0 1 1 0 0 1 1 0 1 0 0 0 01 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 18 0 1 1 0 0 1 1 0 0 1 1 0 1 0 0 02 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 19 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 03 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 20 0 0 0 1 1 0 0 1 1 0 0 1 1 0 1 04 21 1 0 0 1 0 1 0 1 0 1 1 0 1 1 1 05 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 22 1 1 0 1 0 0 1 1 0 0 0 1 0 1 0 06 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 23 0 1 1 0 1 0 0 1 1 0 0 0 1 0 1 07 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 24 1 0 1 0 1 1 0 1 0 1 1 0 0 1 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 08 25 1 1 0 0 1 1 1 1 0 0 0 1 0 0 0 09 0 0 0 0 0 0 0 0 0 1 0 0 0 0 26 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 10 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 27 0 0 1 1 0 0 1 1 1 1 0 0 0 1 0 11 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 28 0 0 0 1 1 0 0 1 1 1 1 0 0 0 1 12 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 29 1 0 0 1 0 1 0 1 0 1 0 1 0 0 1 13 0.0000000000000010 30 1 1 0 1 0 0 1 1 0 0 0 1 0 1 14 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 3111 1 1 1 0 0 0 0 0 0 1 0 0 1 1 15 1 0 0 1 1 0 0 1 1 0 1 0 0 0 1 32 1 1 1 0 0 0 0 1 1 0 1 1 0 0 0 16 1 1 0 1 0 1 0 1 0 1 1 1 0 0 1 33 0 1 1 1 0 0 0 0 1 1 0 1 1 0 0

-17-

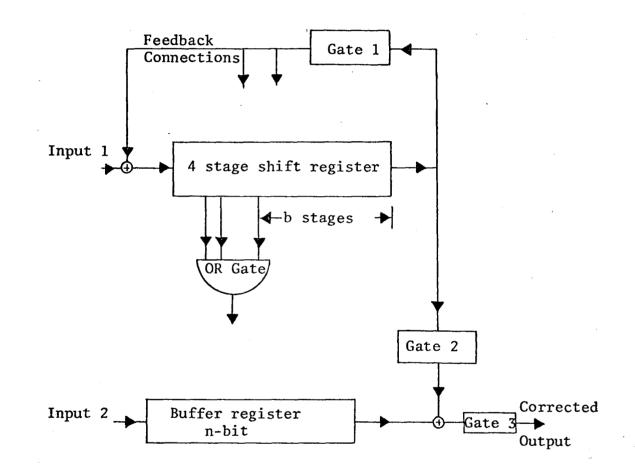

The syndrome bits are computed by Ex-OR tree. If S = 0 the data bits are sent to the CPU. When parity of S is odd it implies single or multiple odd errors. Single errors are corrected by the logic circuit similar to Fig. 2.5. Double error correction is done when parity of syndrome bits is even. The syndrome is loaded into the serial linear feedback register (Fig. 2.6) and the codeword in an n-bit register. Both registers are shifted simultaneously till the first error bit has shifted into the rightmost bit position. This is detected when the syndrome pattern matches any of possible 78 double error patterns stored in a ROM.

The leading bit in the n-bit register is inverted. The remaining error can be corrected by the single error correcting scheme.

# 2.4 <u>Error-correcting Codes for Multiple Bit Per Card Memory</u> Configuration

The error-correcting codes we have seen so far are suitable for single bit per card memory configuration. Increasing speed and system efficiency demands have pushed the idea of single bit per card to a cluster of bits per card type memory organization. A single fault in these systems would affect many bits within a byte. Consequently a byte-error-correcting ability is demanded of the codes. There are a number of known classes of error-correcting

-18-

$g(x) = 1 + x^{3} + x^{4} + x^{7} + x^{8} + x^{10} + x^{14} + x^{15}$

Fig. 2.6

-19-

codes that have this property. Best among these, suitable for high speed implementation, are the redundant residue polynomial code [9].

It is well known that the parity check matrix of the singleerror-correcting Hamming code can be constructed with each element being a symbol from a finite field  $GF(2^b)$ . Then any single error corresponds to a block of b bits in error.

As a simple example, if we consider  $GF(2)[x] \mod x^2 + x + 1$ , the residue classes are  $\{0\},\{1\},\{x\},\{x+1\}$ . They can be represented by powers of symbol  $\alpha$  where  $\alpha^2 + \alpha + 1 = 0$ . In vector form each symbol appears as a binary 2 tuple

| Symbol         | Vector Form |

|----------------|-------------|

| 0              | 0 0         |

| 1              | 0 1         |

| α              | 1 0         |

| α <sup>2</sup> | 11          |

The companion matrix T of the irreducible polynomial p(x) of degree b is a bxb nonsingular matrix described by

| T = | [] <sup>•</sup><br>α | <br>α <sup>2</sup> | <br>α <sup>3</sup> | • • • | μ<br>α <sup>b</sup> |  |

|-----|----------------------|--------------------|--------------------|-------|---------------------|--|

|     |                      | ł                  | <b>]</b> .         |       |                     |  |

where  $\alpha$  is the root of the irreducible polynomial in GF(2<sup>b</sup>). Other symbols in GF(2<sup>b</sup>) can be represented by the matrix

$T = \begin{bmatrix} | & | & | \\ \alpha^{i+1} & \alpha^{i+2} & \dots & \alpha^{i+b} \\ | & | & | \end{bmatrix}$

-20-

The zero and one symbols in  $GF(2^b)$  are the bxb zero matrix  $T_o$ and the bxb identity matrix  $T_1$  respectively. In our example

$$\mathbf{T}_{0} = \begin{bmatrix} 0 & 0 \\ 0 & 0 \end{bmatrix} ; \mathbf{T}_{1} = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix} ; \mathbf{T} = \begin{bmatrix} 1 & 1 \\ 0 & 1 \end{bmatrix} ; \mathbf{T}' = \begin{bmatrix} 1 & 0 \\ 1 & 1 \end{bmatrix}$$

The H matrix for single card correction code with 2-bit per card memory consisting of 64 data bits and 8 check bits is shown (Fig. 2.7). Each element is a bxb binary matrix.

An interesting subclass of these Hamming type codes is 2-redundant codes [9] having two check symbols and capable of single symbol correction in  $GF(2^b)$ . They always have the parity check matrix of the form

$$H = \begin{bmatrix} 1 & 1 & 1 & - - - - - - 1 & 1 & 0 \\ \alpha^{0} & \alpha & \alpha^{2} & - - - - \alpha^{2^{b} - 2} & 0 & 1 \end{bmatrix}$$

If  $\alpha$  is the root of the primitive polynomial in GF(2<sup>b</sup>) then all columns are distinct and the maximum number of information symbol is 2<sup>b</sup>-1.

#### Example

An (80,64) code over  $GF(2^8)$  packaged as 8 bit per card memory with 64 data bits and two check cards (16 bits) has the following parity check matrix

Each symbol is replaced by its corresponding T matrix to obtain the binary H matrix for purposes of implementation.

-21-

$\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{1}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}_{0}\mathbf{r}$  $\mathbf{T}^{\mathbf{T}} \mathbf{T}_{\mathbf{1}} \mathbf{T}_{\mathbf{0}} \mathbf{T}_{\mathbf{0}} \mathbf{T}_{\mathbf{0}} \mathbf{T}_{\mathbf{1}} \mathbf{T}$  $\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{1}\mathbf{T}_{1}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}_{0}\mathbf{T}$  $^{\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}} \operatorname{T}_{0}\mathrm{T}_{0}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{1}\mathrm{T}_{1}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}_{0}\mathrm{T}$

Fig. 2.7

The syndrome for H matrix is computed by the usual Ex-OR tree. Since the error pattern now corresponds to some symbol  $e_i \in GF(2^b)$ in block i of data bits the syndrome corresponding to this error has the value

$$\begin{bmatrix} S_1 \\ S_2 \end{bmatrix} = \begin{bmatrix} e_i \\ e_i \alpha^i \end{bmatrix}$$

where  $S_1$  and  $S_2$  are binary column vectors of length b. If the error occurs in the check symbol, the syndrome is either

$$\begin{bmatrix} S_1 \\ S_2 \end{bmatrix} = \begin{bmatrix} e_i \\ 0 \end{bmatrix} \text{ or } \begin{bmatrix} S_1 \\ S_2 \end{bmatrix} = \begin{bmatrix} 0 \\ e_i \end{bmatrix}$$

This case can be easily detected by And gates checking either  $S_1$  = all zeros or  $S_2$  = all zeros.

When error is in the information symbols,  $S_1 \neq 0$ ,  $S_2 \neq 0$  and  $S_2 = \alpha^i S_1$  or  $S_2 + \alpha^i S_1 = 0$  where + stands for bit by bit Ex-OR. To test the above condition a set of Ex-OR circuits can be set up for all possible values of  $\alpha^i$ ,  $i = 1, 2, \dots 2^b$ -1. This gives the location of the block in error. The error magnitude  $e_i = S_1$  can be added mod 2 to block i for error correction.

For K information symbols, the decoding circuit requires on an average K+2 And gates of b inputs and Kb Ex-OR gates with an average of b/2+1 inputs each.

The 2-redundant codes thus provide a simple means for correcting single bit error or b-adjacent bit error by treating it as a symbol in  $GF(2^b)$ . The check bit are integral multiples of b.

-23-

The redundant bits r = kb where k is an integer.

2.5 General Class of Maximal Codes

Hong and Patel [10] proposed a new class of codes whose structure does not depend on  $GF(2^b)$ . The byte is equated to a suitable cluster of bits and the check bits r = kb+c where  $0 \le C \le b$ . These codes are either perfect or maximal. Hence they are called the general class of maximal codes (GMC).

In general, the identity portion of H matrix looks like

$$I_{r} = \begin{bmatrix} I_{b} & & \\ & I_{b} & & \\ & & \ddots & \\ & & & \ddots & \\ & & & & 1_{b} \\ & & & & I_{b+c} \end{bmatrix} \begin{cases} (k-1)b \ I_{b} \ matrices \qquad (Eq.2.15) \end{cases}$$

or

$$I_r = \begin{bmatrix} I_b & & \\ & I_b & & 0 \\ & & & I_b \\ & & & & \ddots \\ & & & & & 1_b \end{bmatrix}$$

kb  $I_b$  matrices (Eq.2.16)

For the discussion on the code, the form appearing in Eq. 2.15 will be used. The non-identity portion of the parity check matrix

-24-

37.

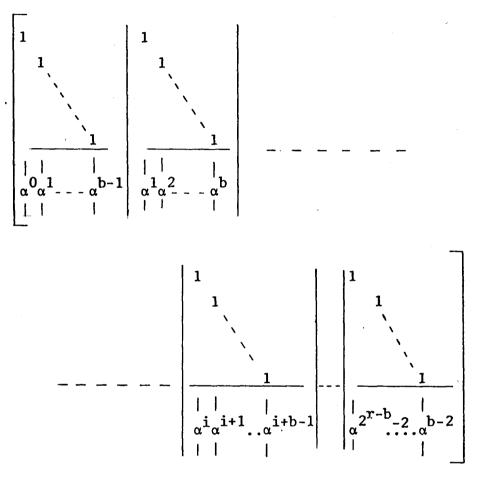

can be formed by successive iteration of the matrix  $H_{r,b}$  constructed as follows:

where  $\alpha$  is a primitive element from GF(2<sup>r-b</sup>). This can be conveniently represented as

$$\begin{bmatrix} I_{b} & I_{b} & I_{b} \\ \hline T^{0}_{r-b} \Phi_{r-b,b} & T^{1}_{r-b} \Phi_{r-b,b} & T^{i}_{r-b} \Phi_{r-b,b} \\ \hline T^{i}_{r-b} \Phi_{r-b,b} & T^{i}_{r-b} \Phi_{r-b$$

where  $T_{r-b}$  is the companion matrix of the primitive polynomial in GF(2<sup>r-b</sup>) and  $\Phi_{r-b,b}$  is a r-bxb matrix of the form

-25-

$\begin{bmatrix} I_b \\ 0_{r-2b,b} \\ matrix. I_b \text{ is a bxb identity matrix and } 0_{r-2b,b} \text{ is a r-2bxb zero matrix.}$

For  $r \ge 2b$  the parity check matrix formed as

$$H = [H_{r,b}|I_r]$$

(Eq.2.17)

is capable of correcting single byte errors.

The single byte correcting ability of this code can be proved by showing that a distinct syndrome exists for every single error pattern.

$$S = vH^{T} = [s_1 s_2 \dots s_k]^{T}$$

$S_i$  represents the syndrome byte corresponding to check byte  $C_i$ . The codeword consisting of information and check bytes is  $v = B_0 B_1 \dots B_{2^{r-b}-2^{l}} C_2 \dots C_k (C_k: \text{ special check byte of length}$ b+c). If an error pattern  $E \neq 0$  occurs in the i<sup>th</sup> information byte than  $S_1 = E \neq 0$

$$[S_2 S_3 \dots S_k]^T = [T_{r-b}^i \Phi_{r-b,b}]E \neq 0$$

If an error pattern  $E \neq 0$  occurs in the j<sup>th</sup> check byte

then

$$S_j = E$$

and  $S_{\lambda} = 0$   $\lambda \neq j$

All the errors yield distinct syndrome and therefore correctable. In case of the parity check matrix given in Eq. 2.17 both the syndromes  $S_1$  and  $[S_2...S_k] \neq 0$  for errors in the information section of the codeword.

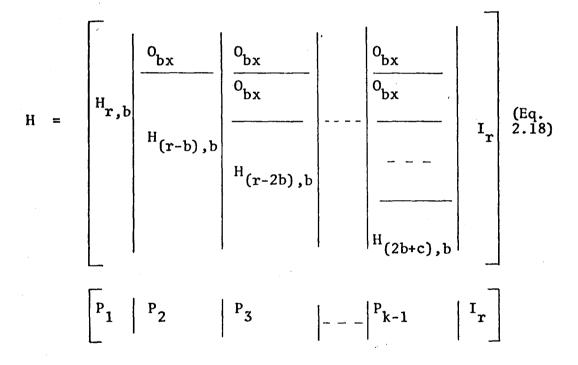

For  $r \ge 3b$  the GMC code is described by the matrix

$$H = \begin{bmatrix} H_{r,b} & \frac{O_{b,b(2^{r-2b}-1)}}{H_{(r-b),b}} & I_{r} \end{bmatrix}$$

$$\begin{bmatrix} P_{1} & P_{2} & I_{r} \end{bmatrix}$$

In general for  $r \ge kb$

Each partition  $P_j$  appears to be a single byte correcting code for information symbols in that particular section of the codeword as they all yield syndromes distinct from other partitions. A single error  $E \neq 0$  in the i<sup>th</sup> byte of partition  $P_j$  yields the syndrome

-27-

$$S_1 = S_2 = \dots = S_{j-1} = 0$$

$S_j = E \neq 0$

$[S_{j+1} \dots S_k]^T = [T^i_{(r-jb)} \Phi_{(r-jb),b}] \cdot E \neq 0$

Since  $H_{2b+c}$  is the smallest possible partition capable of correcting single byte error, there is a limit on the possible number of partitions which suggest the maximality of the code. The total number of distinct error patterns of this code is given by according to Eq. 2.18

$$Z = \begin{cases} k^{-1} \\ j = 1 \end{cases} (2^{b} - 1) (2^{(k-j)b+c} - 1) \} + (k-1) (2^{b} - 1) + (2^{b+c} - 1) + 1$$

$$= 2^{b} - 1\{\sum_{i=1}^{k-1} 2^{ib+c}\} + 2^{b+c}$$

$$= 2^{b-1} 2^{c} \{\sum_{i=1}^{k-1} 2^{ib}\} + 2^{b+c}$$

$$= 2^{b+c} (2^{b} - 1) \frac{2^{(k-1)b} - 1}{2^{b} - 1} + 2^{b+c}$$

$$= 2^{r}$$

This suggests that the code is perfect.

Example

Given  $r = 5 \times 1 + 0 \Rightarrow B = 1$ , c = 0

$$I_{r} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

-28-

The parity check matrix is structured according to Eq. 2.18

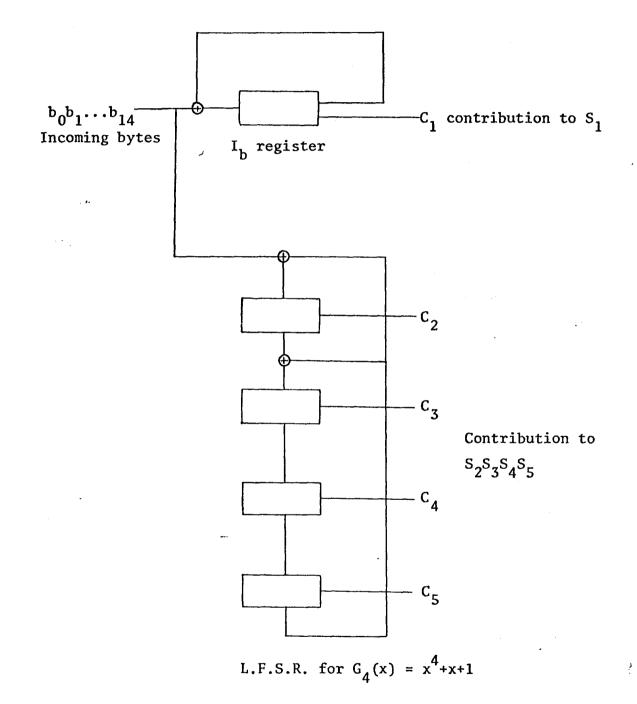

P1P2P3P4IrP1is constructed using primitive polynomial  $x^4 + x + 1$  in GF(2<sup>4</sup>)P2is constructed using primitive polynomial  $x^3 + x + 1$  in GF(2<sup>3</sup>)P3is constructed using primitive polynomial  $x^2 + x + 1$  in GF(2<sup>2</sup>)P4is constructed using primitive polynomial x + 1 in GF(2)

We see that the code length is increased in an iterative fashion and is maximal. Also this (31,26) GMC Code provides an alternate method for constructing single error correcting Hamming code and is perfect. A shortened version of the code could be constructed using a non-primitive irreducible polynomial in  $GF(2^{r-b})$ . In decoders using shift registers this saves decoding time due to the smaller exponent of the generating polynomial.

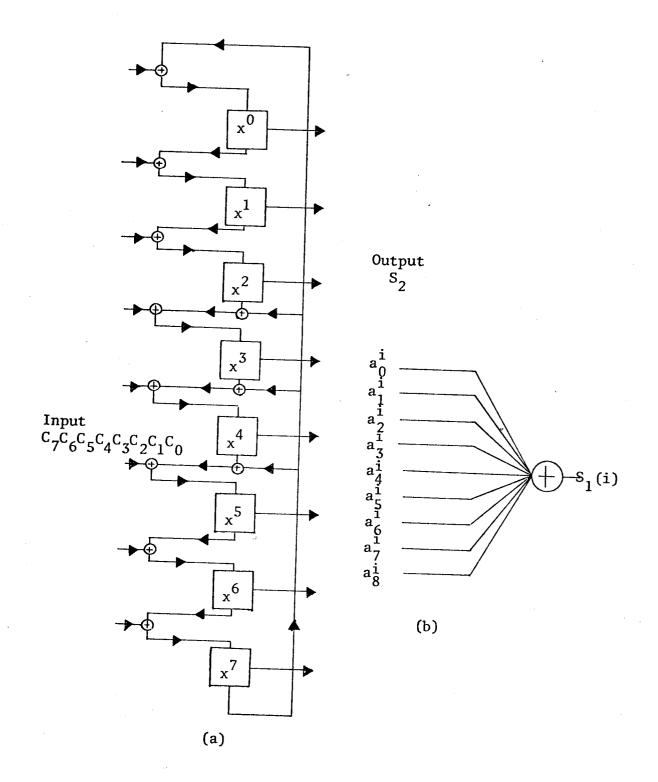

In the encoding and decoding circuitry each partition is processed in parallel. Shift register implementation for  $P_1$  in our example is shown in Fig. 2.8. The check bits of the information is available after  $2^4$ -1 cyclic shifts of the primitive polynomial  $g_4(x) = x^4 + x + 1$  of the largest partition. During decoding the syndrome is obtained by adding the check bits of the information

-29-

Fig. 2.8

mod 2 to the computed check bits. the  $I_b$  portion of the shift register contributes to the syndrome  $S_1$  which gives the error pattern. The linear feedback shift register contributes to the syndrome  $[S_2 S_3 S_4 S_5]$  which provides the location of the error. Let v be a codeword given by

The 5 most significant bits are the check bits of the codeword. Suppose a single error  $b_0 = 1$  occurs corresponding to the position  $P_1$  of the codeword. The received codeword becomes

Bits  $b_0 b_{\bar{1}} b_{14}$  are processed by the circuit (Fig. 2.8). The computed check bits  $C_1 = 1$ ,  $[C_2 C_3 C_4 C_5] = 1001$ . This is added mod 2 to the check bits of the codeword to give  $S_1 = 1$ ,  $[S_2 S_3 S_4 S_5] = 1000$ . The error pattern E = 1. The syndrome  $[S_2 S_3 S_4 S_5]$  matches the first column of the parity check matrix (Eq. 2.19) giving the location.

The GMC code thus provides us the flexibility of constructing a code to suit any byte arrangement of memory. Moreover, the code processing can be done in parallel, saving precious decoding time.

2.6 Majority Logic Decodable Code

At a time when integrated circuits are being developed rapidly and becoming cheaper, a class of codes which are one-step majoritylogic decodable are becoming likely candidates in competition with other codes for computer applications. Although bit is redundancy

-31-

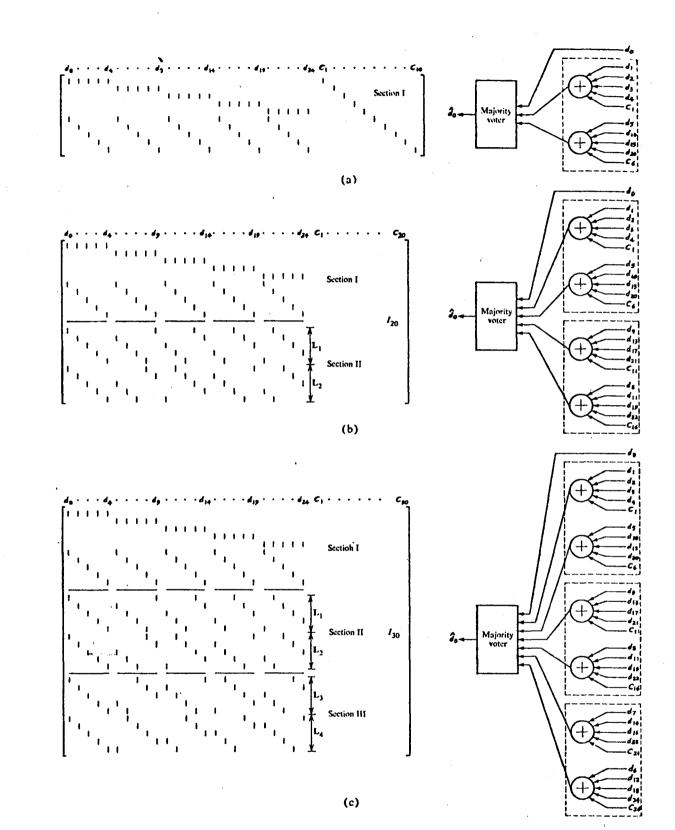

is higher compared to other codes the design of the decoder is simple and fast. A class of such codes derived from orthogonal Latin squares has been proposed by Bossen, Hsiao, Chien [11]. The orthogonal property provides a unique feature of adding redundancy systematically such that the decoder can be built in modules.

A code of distance d is said to be one step majority decodable if it is possible to construct 1-1 check sums orthogonal on every digit. This implies that there must be at least 2t 1's in each column of the parity check matrix for t-error correction. The parity check matrix constructed using Latin squares has exactly 2t 1's in each column corresponding to error in the data bits. The 2t parity check equations formed with any error in the data bit is orthogonal on that particular bit.

<u>Definition</u>: A Latin square of order m is an m x m square array of digits 0,1,...m-1 with each row and column a permutation of the digit 0,1,...m-1. Two Latin squares are orthogonal if when one Latin square is superimposed upon the other every ordered pair of elements appears only once.

<u>Theorem</u>: The maximum error correcting ability of the code constructed from Latin square  $t \leq \frac{m}{2}$ . Also these classes of codes have m<sup>2</sup> data bits and 2tm check bits.

Instead of the proof the construction of the parity check matrix is given with an illustrative example.

Given k = 25 m = 5the orthogonal Latin squares for m = 5 are

-32-

| L <sub>1</sub> = | 0 1 2 3 4<br>1 2 3 4 0<br>2 3 4 0 1                                         | L <sub>2</sub> = | 0 1 2 3 4<br>2 3 4 0 1<br>4 0 1 2 3 |

|------------------|-----------------------------------------------------------------------------|------------------|-------------------------------------|

| <b>.</b>         | 3       4       0       1       2         4       0       1       2       3 | 2                | 1 2 3 4 0<br>3 4 0 1 2              |

|                  | 0 1 2 3 4<br>3 4 0 1 2                                                      |                  | 0 1 2 3 4<br>4 0 1 2 3              |

| L <sub>3</sub> = | 1 2 3 4 0<br>4 0 1 2 3                                                      | L <sub>4</sub> = | 3 4 0 1 2<br>2 3 4 0 1              |

|                  | 2 3 4 0 1                                                                   |                  | 1 2 3 4 0                           |

The parity check matrix is described as

$$H = \begin{bmatrix} M_1 & & & \\ M_2 & & & \\ \vdots & & I_{2tm} \\ \vdots & & & \\ M_{2t} & & & \end{bmatrix}$$

$I_{2tm}$  is the identity matrix of order 2tm.  $M_1, M_2...M_{2t}$  are submatrices of size m x m<sup>2</sup>.

-33-

Since the maximum error correcting ability of this code  $t = \frac{5+1}{2} = 3$ .  $M_3, M_4, M_5, M_6$  are derived from the existing  $L_1, L_2, L_3, L_4$  Latin squares, respectively. The submatrix  $M_i$  derived from  $L_j$  is given by

$$M_{ij} = \begin{bmatrix} V_{1} \\ V_{2} \\ \vdots \\ V_{m} \end{bmatrix} \qquad i = 3,4,5,6 \\ j = 1,2,3,4$$

where  $V_k = 1, 2...m$  is a row vector of length  $m^2$  derived from  $L_i$

$$\mathbf{V}_{\mathbf{k}} = [\mathbf{q}_{11}^{\mu} \dots \mathbf{q}_{1m}^{\mu} \mathbf{q}_{21}^{\mu} \dots \mathbf{q}_{12m}^{\mu} \mathbf{q}_{31}^{\mu} \dots \mathbf{q}_{3m}^{\mu} \dots \mathbf{q}_{m1}^{\mu} \dots \mathbf{q}_{mm}^{\mu}]$$

If we pick any element  $\mu$  from the Latin square  $0 \le \mu \le m-1$ then  $1 \qquad \mu = \ell_{ij}$  i = 1, 2...m $q_{ij}^{\mu} = 0 \qquad \mu \ne \ell_{ij}$  j = 1, 2...m

ij are the elements of the Latin square.

The submatrices  $M_3$ ,  $M_4$ ,  $M_5$ ,  $M_6$  are shown in Fig. 2.9 [11] marked  $L_1$ ,  $L_2$ ,  $L_3$ ,  $L_4$  respectively. The single error correcting (35,25) code is constructed with submatrices  $M_1$  and  $M_2$  (Fig. 2.9a). The Decoder for data bit  $d_0$  is shown. The output of the majority

-34-

- 35-

Fig. 2.9

voter is 1 if  $d_0$  is correct and 0 of  $d_0$  is in error. The majority voters for other data bits can be constructed similarly. Referring to Fig. 2.9 the error correcting ability is increased to two by adding section II which includes submatrices  $M_2$  and  $M_3$ . Although the number of check bits doubles, the construction is very simple. The circuitry necessary for correcting the additional error is similar to the first and can be added in modular fashion without interfering its mechanization which makes this code a suitable candidate for implementation with I.C. Fig. 29c corresponds to the (55,25) triple error correcting code constructed by adding matrices  $M_5$  and  $M_6$ . Since there are no more Latin squares, this is the maximum error correcting capability of the code.

#### 2.7 Summary

In conclusion of this chapter, we have seen some of the errorcorrecting codes used in computer memory environment. For those memory configurations which are packaged on single bit per card basis, SEC-DED, DEC-TED and one step majority decodable codes were helpful in increasing the reliability of memory. Byte-errorcorrecting codes formed the basis of correcting errors in memories with multiple bit per card arrangement. Two-redundant codes and Reed-Solomon codes provided character-error-correcting ability. Reed-Solomon codes were not discussed in this chapter because its slow and complicated decoding scheme was a serious handicap. In the next chapter we shall see that this class of codes is not

-36-

best suited for photo digital mass memory. Also, we saw the flexibility of the general class of maximal codes whose construction did not depend upon any homogeneous bit arrangement of memory. Emphasis was based throughout on a simple and fast implementation scheme.

### CHAPTER 3. ERROR-CORRECTING CODES FOR COMPUTER PERIPHERAL SYSTEM

The storage medium in peripheral devices is generally a magnetic tape unit, drum or disc file or an optical unit. They form the bulk of the extended mass memory in computer environment. As more and more information is being placed in mass storage devices, the corresponding improvement in reliability cannot be ignored. Coding techniques are playing a vital role in achieving higher reliability and saving considerable time consuming corrective action in conventional read-write schemes.

## 3.1 <u>Single-track Correction of Magnetic Tape Unit with Cyclic</u> Redundancy Codes

The IBM/360 system 2400 series uses a standard 1/2" 9 track magnetic tape. Bits are recorded on this tape with a density of 800 bits/inch along the track. Spacing between bits in adjacent tracks is about 40 times larger than those between bits in the same track. This suggests that a single bit in error along any track is likely to affect other bits in the same track rather than those of adjacent tracks. Since bits are so closely packed within a track the probability of burst error patterns occurring simultaneously in one or more tracks is predominant. The errors are generally caused by foreign dust particles, imperfection in the surface coating of the tape and mechanical damage due to handling.

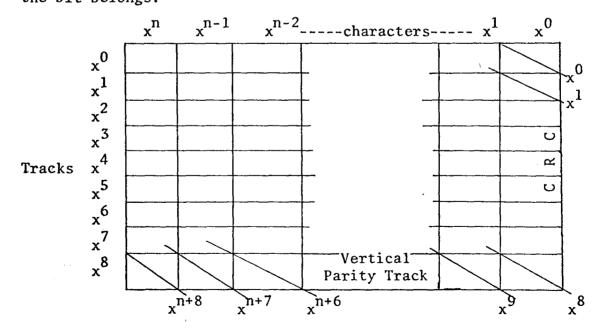

Information is recorded on the tape as characters of 9 bits

-38-

$\mathcal{A}$

across the tracks. The 9th bit is a parity on the other 8 bits and is written on the 8th track of the tape, also called the vertical parity track. The other 8 bits of the character are written from track 0-7. The position of the character along the tape is identified by associating it with a unique power of x. The highest power is attached to the first character in the record, and the lowest power of x is attached to a special character generated from all the previous characters in the track. It functions as a check on the previous characters written in the record. It is also called the cyclic redundancy check or the CRC character. The track positions are also associated with powers of x. In the 9 track tape the powers of x range from  $x^{0}-x^{8}$ . A record of n character on the tape looks like an array of  $9 \times n+1$  bits. Each bit in the record can therefore be associated with a power of x given by the sum of the track and character power of x to which the bit belongs.

<

-39-

The record is a sequence of n data characters, each 9 bits long consisting of 8 data bits and 1 parity bit. We can also represent the record as a polynomial

$p(x) = C_n x^n + C_{n-1} x^{n-1} + \dots + C_1 x^{n-1}$

where the coefficient  $C_i$  is a 9 bit character, polynomial

$C_{i}(x) = a_{0}^{i} + a_{1}^{i}x + a_{2}^{i}x^{2} + a_{3}^{i}x^{3}...a_{8}^{i}x^{8}$

and  $a_k^i$  is the bit associated with the i<sup>th</sup> character and k<sup>th</sup> track. The maximum degree of the polynomial p(x) is n+8. If we now consider a generator polynomial of degree nine, the remainder resulting from the division of p(x) by g(x) would be a polynomial of degree 8 or less which is equivalent to a 9-bit data character that can be added at the end of the information data characters to represent the CRC. The addition of the CRC to the data characters forms a polynomial codeword which is divisible by the generator polynomial g(x). Any burst error along the track will be detected if the code polynomial is not divisible by g(x) after the entire record has been read. If the burst error pattern is confined to a single track it can be corrected with the aid of the parity bits in the vertical parity track also called vertical redundancy check (VRC). Sometimes an undetectable error pattern divisible by g(x) may result. To account for this an additional check character called longitudinal redundancy check (LRC) is written on the record at the end of CRC character. Every bit in the LRC character is an even parity check of all the data bits in the corresponding track. The American National Standard

-40-

Institute has specified  $g(x) = (1+x)G_1(x)$  where  $G_1(x) = 1+x+x^2+x^4+x^6+x^7+x^8$  and  $g(x) = 1+x^3+x^4+x^5+x^6+x^9$ . This g(x) is a symmetric polynomial with (1+x) as a factor. The symmetric property facilitates the read backward mode of operation while the (1+x) factor predetermines the parity of the CRC character and makes error in the CRC character correctable. Also in systems where LRC is used the CRC can be altered by adding an odd wt character to it. This ensures that LRC has odd vertical parity, a desirable trait for identifying the start of the record in the read backward mode of operation. Asymmetric generator polynomials have also been specified. These have larger cycle length than symmetric polynomials and when used along with the symmetric generator polynomial on the data record helps to increase the range of checking ability, especially when bits are recorded at a higher density.

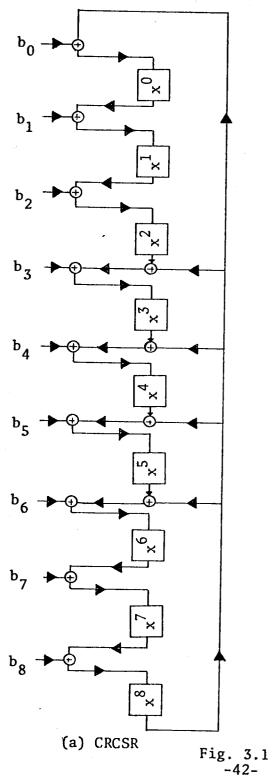

#### Working example

$g(x) = 1 + x^3 + x^4 + x^5 + x^6 + x^9$

The CRC character can be generated by the feedback shift register characterized by g(x) CRCSR (Fig. 31.a).

We will consider here a record of 3 characters written on the tape as shown, using even vertical parity for the data.

-41-

Write direction

$$p(x) = x^{2} + x^{3} + x^{5} + x^{8} + x^{9} + x^{10}$$

The CRC polynomial  $C_0(x)$  is given by the remainder of [p(x)|g(x)]

$$x^{9}+x^{6}+x^{5}+x^{4}+x^{3}+1 \overbrace{x^{10}+x^{9}+x^{8}+x^{5}+x^{4}+x^{2}}_{x^{9}+x^{8}+x^{7}+x^{6}+x^{4}+x^{3}+x^{2}+x}$$

$$\frac{x^{9}+x^{6}+x^{5}+x^{4}+x^{3}+x^{2}+x}{x^{9}+x^{6}+x^{5}+x^{4}+x^{3}+x^{2}+x}$$

$$\frac{x^{9}+x^{6}+x^{5}+x^{4}+x^{3}+1}{x^{8}+x^{7}+x^{5}+x^{2}+x+1}$$

In binary  $C_0 = 111001011$

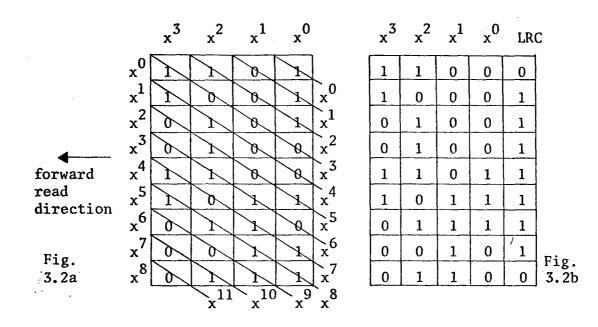

This is written after the last data character on the record. The tape now looks like Fig. (3.2a) below.

As (1+x) is a factor of g(x) there are even number of 1's in the record. Since the data has even vertical parity, the parity of  $C_0$  must be even. If an LRC character is written at the end of the record  $C_0(x)$  is modified by adding mod 2  $G_1(x)$  which is an odd wt vector.  $C'_0$  = 111001011 + 111010111 = 000011100. This ensures that the vertical parity of LRC character is odd (Fig. 3.2b) above. We shall now assume that all bits in track 3 are read as 1's. This corresponds to an error polynomial  $E(x) = x^6 + x^4 + x^3$  and the code polynomial  $v(x) = 1 + x + x^3 + x^7 + x^9 + x^{10}$ . The received polynomial  $r(x) = r(x) + e(x) = 1 + x + x^4 + x^6 + x^7 + x^9 + x^{10}$ . The division of v(x) by g(x) is performed by the feedback shift register of Fig. 3.1a. The content of the shift register after division is given by

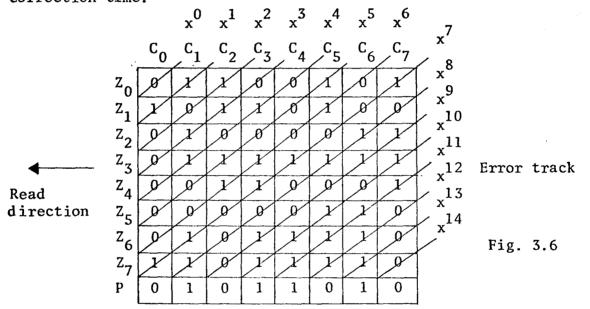

$$x^{9}+x^{6}+x^{5}+x^{4}+x^{3}+1 \boxed{x^{10}+x^{9}+x^{7}+x^{6}+x^{4}+x+1}_{x^{10}+x^{7}+x^{6}+x^{5}+x^{4}+x}_{x^{9}+x^{5}+1}_{\frac{x^{9}+x^{6}+x^{5}+x^{4}+x^{3}+1}{\frac{x^{9}+x^{6}+x^{5}+x^{4}+x^{3}+1}{\frac{x^{6}+x^{4}+x^{3}}{\frac{x^{6}+x^{4}+x^{3}}{\frac{x^{6}+x^{4}+x^{3}}{\frac{x^{6}+x^{4}+x^{3}}{\frac{x^{6}+x^{4}+x^{3}}{\frac{x^{6}+x^{4}+x^{3}}{\frac{x^{6}+x^{4}+x^{3}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{6}+x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{6}+x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{6}+x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{4}+x^{4}}{\frac{x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}+x^{6}$$

As the characters are being read they are checked for even parity. If an odd parity results a 1 is entered in the first bit position of an error pattern feedback shift register (EPSR) characterized by g(x) (Fig. 3.1b) and shifted in synchronism with CRCSR. In our case after 4 shifts the content of ERSR is equal to 110100000. Since the content of CRCSR is not all zero we have detected an error. The error pattern of burst length 9 is indicated in EPSR. The track in which the error occurred can be obtained by simply counting the shifts necessary for the content of EPSR to match that of CRCSR. For our example, after 3 shifts the contents of CRCSR and EPSR are identical, indicating error in the 3rd track. Error correction can now be performed by inverting the bit  $a_k^3$ for k = 1,3,4.

## 3.2 Double-track Correction of Magnetic Tape Unit with Cyclic Redundancy Codes

We have seen how the CRC polynomial code can correct random and burst error in single tracks. The idea has now extended to double track correction by Malhotra and Fisher [18] to increase reliability. Double channel correction is accomplished if a suitable hardware exists which identifies the two tracks in error. The format of the data recorded on the tape is slightly modified. The length of data characters in a record is limited to 7, and the characters 8 bits long are synbols from  $GF(2^8)$ . The 8th track is the parity track. In this case the check character is computed

-45-

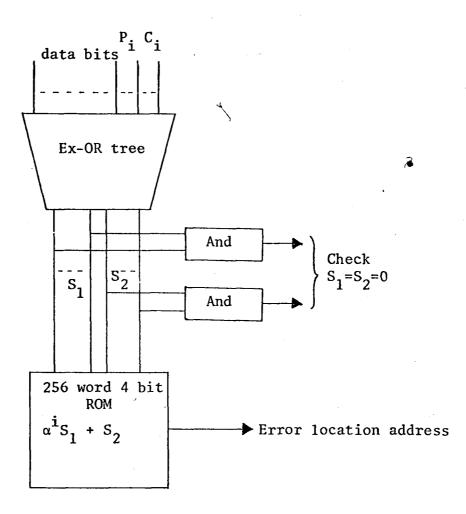

from data characters using an irreducible polynomial in GF(2<sup>8</sup>). When the record is read the parity track consisting of 8 bits and the check character of 8 bit length are treated as syndromes  $S_1$ and  $S_2$  of the record. Obviously, if  $E_i$  and  $E_j$  are the error patterns in tracks i and j respectively, then  $S_i = E_i + E_j$  and is computed as the mod 2 sum of the parity track written and read. The other syndrome  $S_2$  is computed by dividing the code polynomial by the generator polynomial using a feedback shift register similar to CRCSR.  $S_2 = [x^i E_i + x^j E_j] \mod g(x)$  where g(x) is the generator polynomial. From  $S_1$  and  $S_2$  the unknowns  $E_i$  and  $E_j$  can be calculated.

$$E_i = [AS_1 + BS_2] \mod g(x)$$

(Eq.3.1)

$$E_{j} = E_{i} + S_{1}$$

(Eq.3.2)

where A =

$$\frac{x^{j}}{x^{i}+x^{j}}$$

mod g(x) (Eq. 3.3); B =  $\frac{1}{x^{i}+x^{j}}$  mod g(x) (Eq. 3.4)

All possible solutions for A and B can be stored in a ROM.

Illustrative example.

<u>.</u>

-46-

Write direction

data polynomial  $p(x) = x+x^2+x^3+x^4+x^5+x^6+x^7+x^9+x^{10}+x^{13}$ . The check character is given by Remainder of p(x) divided by g(x)implemented a feedback shift register characterized by g(x).

$$x^{8} + x^{5} + x^{4} + x^{3} + 1$$

$$x^{13} + x^{10} + x^{9} + x^{7} + x^{6} + x^{5} + x^{4} + x^{3} + x^{2} + x$$

$$x^{13} + x^{10} + x^{9} + x^{8} + x^{5}$$

$$x^{8} + x^{7} + x^{6} + x^{4} + x^{3} + x^{2} + x$$

$$\frac{x^{8} + x^{5} + x^{4} + x^{3} + 1}{x^{7} + x^{6} + x^{5} + x^{2} + x + 1}$$

The check character  $C_0 = 11100111$  is now written at the end of the data characters to form a complete record.

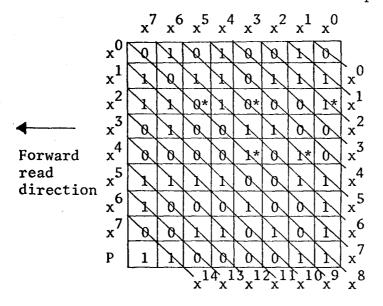

Error track

Error track

Assuming that error was detected in tracks 2 and 4 as a result of the bits marked with asterisk being inverted (i=2,j=4), the computed parity track during read is equal to 11100000,  $S_1 =$ 11000011 \*<sub>2</sub> 11100000 = 00100011. The received code polynomial  $r(x) = 1+x^2+x^3+x^4+x^9+x^{10}+x^{13}$ . The syndrome  $S_2$  is computed as follows:

-47-

$$x^{8}+x^{5}+x^{4}+x^{3}+1 \qquad x^{13}+x^{10}+x^{9}+x^{4}+x^{3}+x^{2}+1 \\ x^{13}+x^{10}+x^{9}+x^{8}+x^{5} \\ x^{8}+x^{5}+x^{4}+x^{3}+x^{2}+1 \\ \frac{x^{8}+x^{5}+x^{4}+x^{3}+1}{x^{2}} \\ x^{8}+x^{5}+x^{4}+x^{3}+1 \\ x^{2} \\$$

The coefficient A and B in Eq. 3.1 is computed using the formula in equations 3.3 and 3.4. In binary A = 01011001 and B = 00010110. During implementation these are the 8 bit addresses given by the ROM supplied with track pointers. Error pattern  $E_2$  is given by Eq. 3.1. The partial products and sums modulo g(x) is implemented by shift registers. The result Ex-ored with  $S_1$  gives the error pattern  $E_A$ .

$S_1 = 00100011$   $S_2 = 00000100$  A = 01011001 B = 00010110g(x) = 100111001

00100011 00010110 x 01011001 00000100 х <sup>BS</sup>2 00100011 01011000 Ξ 00100011000 AS<sub>1</sub> 001000110000 00101111001011 Ξ <sup>BS</sup>2 + 00100011000000 + 01011000 Ξ  $AS_1 + BS_2$ Ξ 00101111001011  $\equiv AS_1$ 00101110010011

where x and + stands for shift and addition mod 2.

L ...

$\mathbf{E}_{A} = 00100011 + 00101001 = 00001010$

When  $E_2$  and  $E_4$  are added to the tracks 2 and 4 of the record the correct information is restored. If errors occurred in more than 2 tracks, this scheme is unable to correct the errors. The capability to detect uncorrectable error can be extended by adding additional check characters generated by 9th degree polynomials similar to the generation of the CRC check character at the end of the record.

# 3.3 <u>Single and Double Track Correction Using Optimal Rectangular</u> <u>Codes</u>

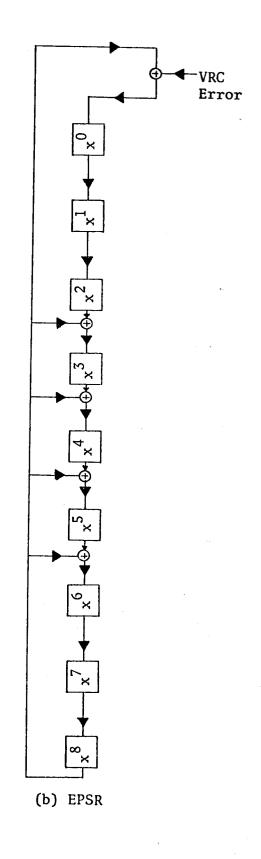

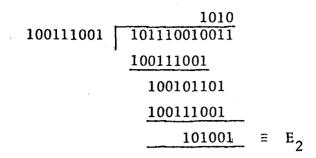

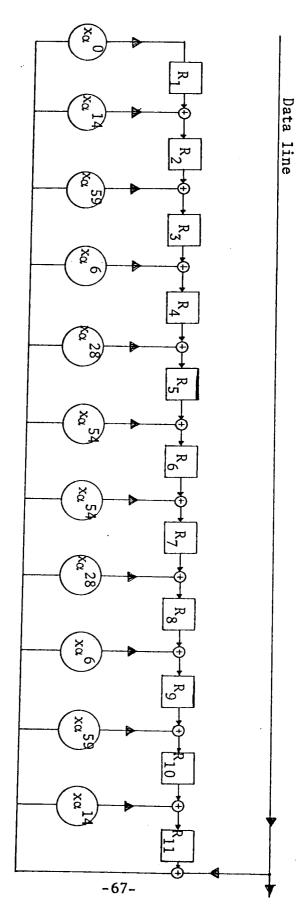

Another code capable of correcting single track error and double track errors with track pointers is the Optimal Rectangular code developed by Hong and Patel [17]. They are being used commercially in models 4, 6, 8 of the IBM 3420 series tape unit. The recording density on these standard  $\frac{1}{2}$  inch 9 track tapes is 6250 bits per inch. The code has a rectangular format of 9 rows and 8 columns. Information is recorded as 8-bit bytes along columns. There are 7 information bytes in the code word and a check byte generated from the information byte using an irreducible polynomial

-49-

in  $GF(2^8)$ . This is written on the first column of the rectangular array. Bits in track 0-7 in the array are treated as track bytes. The 8th track is the vertical parity track. Each bit in this track is a vertical parity of the upper 8 bits in the column.

Track Bytes

|                | с <sub>о</sub> | с <sub>1</sub> | с <sub>2</sub> | с <sub>3</sub> | с <sub>4</sub> | с <sub>5</sub> | с <sub>6</sub> | С <sub>7</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| z <sub>0</sub> | 2              | 1              | 2              | 3              | 4              | 5              | 6              | 7              |

| <sup>z</sup> 1 | 1              | X              | 3              | 4              | 5              | 6              | 7              | 8              |

| <sup>Z</sup> 2 | 2              | 3              | A              | 5              | 6              | 7              | 8              | 9              |

| Z <sub>3</sub> | 3              | 4              | 5              | Ø              | 7              | 8              | 9              | 10             |

| Z44            | •4             | 5              | 6              | 7              | 8              | 9              | 10             | 11             |

| Z <sub>5</sub> | 5              | 6              | 7              | 8              | 9              | N              | 11             | 12             |

| Z <sub>6</sub> | 6              | 7              | 8              | 9              | 10             | 11             | NZ             | 13             |

| Z <sub>7</sub> | 7              | 8              | 9              | 10             | 11             | 12             | 13             | 14             |

| Р              |                |                |                |                |                |                |                |                |

Fig. 3.3

Line of symmetry

If  $Z_i(j)$  is the j<sup>th</sup> bit in track i and  $C_i(j)$  the j<sup>th</sup> bit in i<sup>th</sup> character for  $0 \le i \le 7$  and  $0 \le j \le 7$ ,  $C_0(j)$   $0 \le j \le 7$  represents the check character and  $C_i(j)$   $0 \le j \le 7$ ,  $1 \le i \le 7$ , the information characters. If we associate  $Z_i(j)$  with the number x = i+j we observe that the array is symmetrical with respect to x (Fig. 3.3). This orthogonal symmetry is used to construct the parity check matrix of the code.

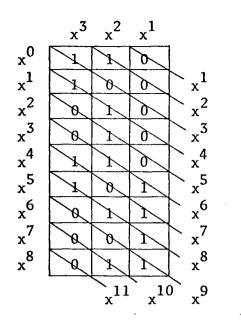

If we recall from the previous chapter Hong and Patel had developed a general class of maximal codes using matrix  $H_{r,b}$  for code construction. The ORC code can be represented by an H matrix (Fig. 3.4) which uses  $H_{2b,b}$  for code construction. This belongs to the shortened version of the maximal code as  $\alpha$  is the root of

-50-

= H

-51-

|          | $\alpha^7 \dots \alpha^{14}$ | $\alpha^{6} \dots \alpha^{13}$ $T^{6}$ | α5α <sup>12</sup><br>T <sup>5</sup> | $\alpha^4 \dots \alpha^{11}$<br>T <sup>4</sup> | α <sup>3</sup> α10<br>T <sup>3</sup> | $ \begin{array}{c c} & \alpha & \alpha^2 \dots & \alpha^2 \dots & \alpha^3 \dots & \alpha^1 \\ T & T^2 & T^2 & T^3 & T^4 & T^5 & T^6 & T^7 \end{pmatrix} \alpha^7 \dots & \alpha^{14} \\ \end{array} $ | α <sup>1</sup> α | $\alpha^{0}\alpha^{1}$ $\alpha^{7}$ $T^{0}$ |

|----------|------------------------------|----------------------------------------|-------------------------------------|------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------|

| 0000001  |                              | 10000000                               | 10000000                            | 00000000                                       | 00000001                             | 10000000                                                                                                                                                                                               | 10000000         | 10000000                                    |

| 00100000 | 00000100                     | 00000100                               | 00100000                            | 00000100                                       | 00100000                             | 00100000                                                                                                                                                                                               | 00100000         | 00100000                                    |