# Lehigh University Lehigh Preserve

Theses and Dissertations

1999

# Architectural design options for ATM switches

Navindra Yadav Lehigh University

Follow this and additional works at: http://preserve.lehigh.edu/etd

### Recommended Citation

Yadav, Navindra, "Architectural design options for ATM switches" (1999). Theses and Dissertations. Paper 603.

This Thesis is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Lehigh Preserve. For more information, please contact preserve@lehigh.edu.

# Yadov, Navindra Architectural design options for ATM switches

May 31, 1999

## **Architectural Design Options for ATM Switches**

Ву

### Navindra Yadav

### A Thesis

Presented to the Graduate and Research Committee

of Lehigh University

in Candidacy for the Degree of

Master of Science

in

Computer Science

Lehigh University

January 1999

This thesis is accepted and approved in partial fulfillment of the requirements for the Master of Science.

1/8/99 Date

Thesis Advisor

Chairperson of Department

### Acknowledgments

I would like to express my sincere gratitude to my advisor Professor Michael J. Schulte, for his support, encouragement and advice. It was a great experience working in the computer architecture and arithmetic (CAAR) laboratory.

I would especially like to extend my thanks to my CAAR lab friends and colleagues. They made the lab, one of the best places I have worked. I would like to extend my sincere thanks to James Stine ("James is the best!!!"), Ahmet Akkas and Vitaly Zelov. I do not know what I would have done without them.

Last but not the least, I would like to express my gratitude and love to my mother and father for their constant support throughout my life. I would like to extend my love to Moni, my wife, for her patience and for waking me every day, even though she was more than a thousand miles away from me.

# **Table of Contents**

| LIST OF TABLES                                | VII  |

|-----------------------------------------------|------|

| LIST OF FIGURES                               | viii |

| ABSTRACT                                      | 1    |

| 1. MOTIVATION                                 | 2    |

| 2. INTRODUCTION TO ASYNCHRONOUS TRANSFER MODE | 3    |

| 2.1 AN OVERVIEW OF ASYNCHRONOUS TRANSFER MODE | 3    |

| 2.2 BASIC PRINCIPLES OF ATM                   | 5    |

| 2.2.1 Information Transfer                    | б    |

| 2.2.2 Routing                                 | б    |

| 2.2.3 Resources                               | 6    |

| 2.2.4 ATM Cell Identifiers                    | 7    |

| 2.2.5 Throughput                              | 7    |

| 2.2.6 Signaling                               | 8    |

| 2.2.7 Flow Control                            | 8    |

| 2.3 VIRTUAL PATHS AND VIRTUAL CHANNELS        | 8    |

| 2.4 ATM CELL HEADER STRUCTURE                 |      |

| 2.5 Broadband Network Performance             | 13   |

| 2.6 ATM LAYER MODEL                           |      |

| 2.6.1 Physical Layer                          |      |

| 2.6.1.1 Physical medium sub-layer             | 15   |

| 2.7.1.2 Transmission convergence sub-layer    | 17   |

| 2.6.2 ATM Layer                               | 18   |

| 2.6.3 ATM Adaptation Layer                    |      |

| 3 ATM SWITCHES                                | 21   |

| 3.1 Introduction                              | 21   |

| 3.2 SWITCHING                                 | 21   |

| 3.3 CONCENTRATION / MULTIPLEXING              | 22   |

| 3.4 BASIC FUNCTION OF AN ATM SWITCH           |      |

| 3.5 SWITCHING REQUIREMENTS                    | 26   |

| 3.5.1 Information Rate                        | 26   |

| 3.5.2 Performance                                                                                         | 26 |

|-----------------------------------------------------------------------------------------------------------|----|

| 3.5.2.1 Connection blocking                                                                               | 27 |

| 3.5.2.2 Cell loss and cell miss-insertion probability                                                     | 27 |

| 3.5.2.3 Switching Delay                                                                                   | 28 |

| 3.6 Basic Architecture of an ATM Switch                                                                   | 28 |

| 3.7 SWITCHING ELEMENTS                                                                                    | 30 |

| 3.7.1 Input Queued Switching Element                                                                      | 31 |

| 3.7.2 Output Queued Switching Element                                                                     | 31 |

| 3.7.3 Central Queued Switching Element                                                                    | 33 |

| 3.8 SWITCHING FABRICS                                                                                     | 33 |

| 3.8.1 Single Stage Networks                                                                               | 35 |

| 3.8.2 Multi-Stage Networks                                                                                | 35 |

| 3.8.2.1 Single Path Networks                                                                              | 35 |

| 3.8.2.2 Multiple Path Networks                                                                            | 36 |

| 3.9 CELL HEADER PROCESSING IN SWITCHING FABRICS                                                           | 37 |

| 3.9.1 Self Routing Switching Elements                                                                     | 37 |

| 3.5.2.1 Connection blocking 3.5.2.2 Cell loss and cell miss-insertion probability 3.5.2.3 Switching Delay | 38 |

| 4. ATM SWITCH SIMULATION RESULTS                                                                          | 40 |

| 4.1 A GENERIC INPUT QUEUED SWITCHING ELEMENT                                                              | 40 |

| 4.2 OUTPUT QUEUED SWITCHING ELEMENT (KNOCKOUT SWITCHING ELEMENT)                                          | 41 |

| 4.3 CENTRAL QUEUED SWITCHING ELEMENT (COPRIN SWITCHING ELEMENT)                                           | 47 |

| 4.4 SWITCHING ELEMENTS SIMULATOR DESIGNS                                                                  | 52 |

| 4.4.1 Input Queued Switching Element                                                                      | 53 |

| 4.4.2 Output Queued Switching Element                                                                     | 54 |

| 4.4.3 Central Queued Switching Element                                                                    | 55 |

| 4.5 COMPUTER SIMULATION RESULTS FOR THE SWITCHING ELEMENTS                                                | 55 |

| 4.6 RESULTS                                                                                               | 58 |

| 4.7 Analysis of the results                                                                               | 62 |

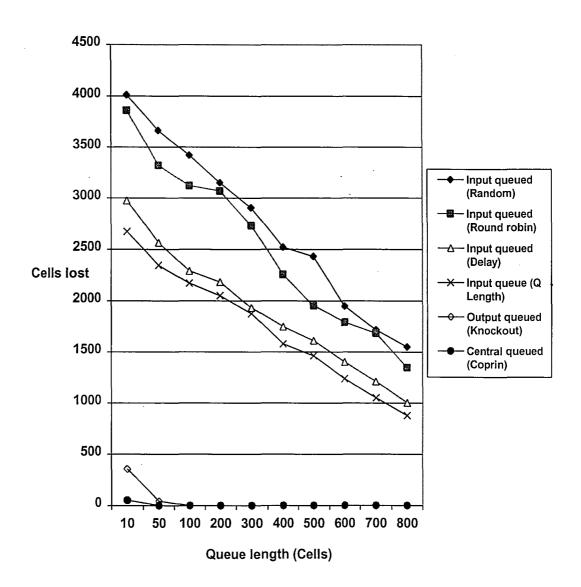

| 4.7.1 Cells dropped vs queue length                                                                       | 62 |

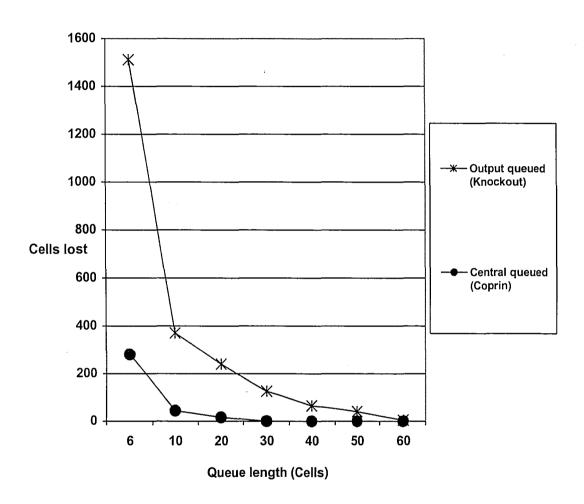

| 4.7.2 Cells dropped vs queue lengths for central and output queuing                                       | 63 |

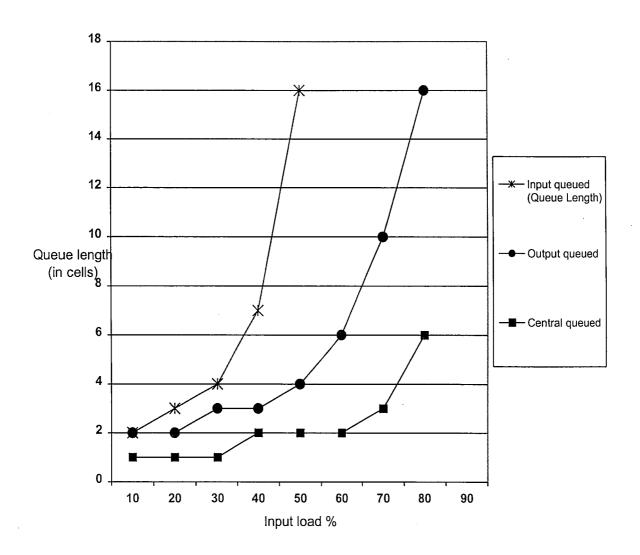

| 4.7.3 Queue length vs input load                                                                          | 63 |

| 4.8 QUEUE COMPLEXITY                                                                                      | 64 |

| 4.8.1 Input queuing                                                                                       | 65 |

| 4.8.2 Output queuing                                                                                      | 66 |

| 4.8.3 Central Queue                                                                                       | 67 |

|                                                                                                           |    |

| 5. | R    | OUTING IN ATM SWITCHING FABRICS                                               | 68 |

|----|------|-------------------------------------------------------------------------------|----|

|    | 5.1  | Banyan and Delta Networks                                                     | 68 |

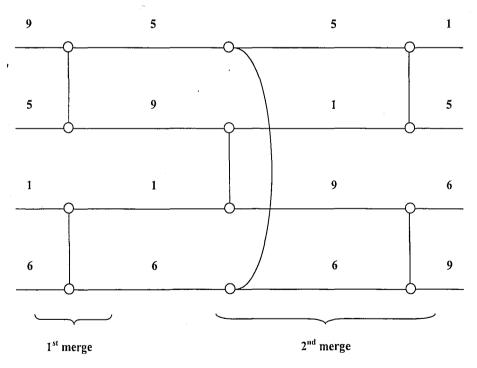

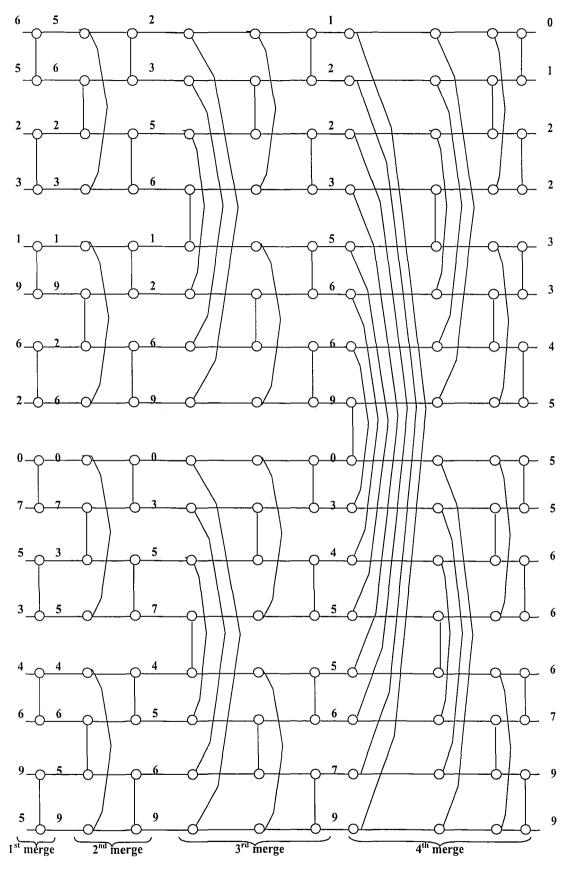

|    | 5.2  | ODD-EVEN MERGE SORT                                                           | 70 |

|    | 5.3  | Sorting Circuit of Depth $log_2(N)$ ( $log_2(N) + 1$ ) / 2                    | 71 |

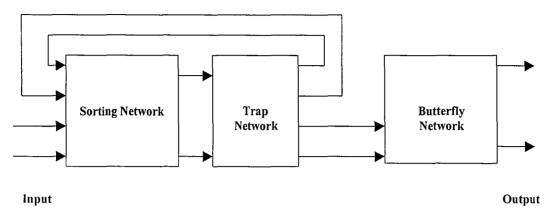

|    | 5.4  | REDUCING A ROUTING PROBLEM TO A SORTING PROBLEM                               | 74 |

|    | 5.5  | Solving the Routing Problem Using $\log_2(N)$ Stage Butterfly and a Balancing |    |

|    | NET  | WORK                                                                          | 75 |

| 6  | . (  | CONCLUSIONS                                                                   | 77 |

| A  | PPE  | NDIX - ABBREVIATIONS                                                          | 79 |

| F  | REFE | RENCES                                                                        | 81 |

| v  | /ITA |                                                                               | 85 |

# List of Tables

| TABLE 2-1: ATM PERFORMANCE PARAMETERS                                         | . 14 |

|-------------------------------------------------------------------------------|------|

| TABLE 2-2: ATM PROTOCOL REFERENCE MODEL SUB-LAYERS AND FUNCTIONS              | . 17 |

| TABLE 2-3: SERVICE CLASSES FOR ATM ADAPTATION LAYER                           | . 20 |

| TABLE 3-1: TRANSLATION TABLE                                                  | . 25 |

| Table 4-1: Routing table for a 2 X 2 switching element                        | . 55 |

| Table 4-2 A: Routing table for an 8 X 8 switching element (Input Ports 1 - 5) | . 56 |

| Table 4-2 B: Routing table for an 8 X 8 switching element (Input Ports 6 - 8) | . 57 |

| Table 4-3: Required memory access times for the three queuing schemes         | . 65 |

# List of Figures

| FIGURE 2-1: ATM CELL STRUCTURE                                                  |

|---------------------------------------------------------------------------------|

| FIGURE 2-2: SYNCHRONOUS TRANSFER MODE 4                                         |

| FIGURE 2-3: ASYNCHRONOUS TRANSFER MODE                                          |

| FIGURE 2-4: RELATIONSHIP BETWEEN A VIRTUAL PATH AND VIRTUAL CHANNEL             |

| FIGURE 2-5: VIRTUAL PATH SWITCH                                                 |

| FIGURE 2-6: VIRTUAL CHANNEL / VIRTUAL PATH SWITCH                               |

| FIGURE 2-7: ATM CELL HEADER (NETWORK-NETWORK INTERFACE)                         |

| FIGURE 2-8: ATM Protocol Reference Model                                        |

| FIGURE 3-1: A SPACE SWITCH                                                      |

| FIGURE 3-2: A TIME SWITCH                                                       |

| FIGURE 3-3: ATM SWITCHING PRINCIPLE                                             |

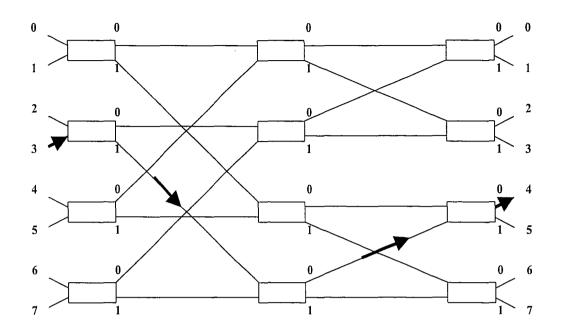

| FIGURE 3-4: BUTTERFLY SWITCHING FABRIC WITH SWITCHING ELEMENTS AT THE ITS NODES |

| FIGURE 3-5: SWITCHING ELEMENT WITH INPUT QUEUES                                 |

| FIGURE 3-6: SWITCHING ELEMENT WITH OUTPUT QUEUES                                |

| FIGURE 3-7: SWITCHING ELEMENT WITH CENTRAL QUEUING                              |

| FIGURE 3-8: CLASSIFICATION OF SWITCHING NETWORKS                                |

| FIGURE 3-9: SELF-ROUTING SWITCHING ELEMENTS                                     |

| FIGURE 3-10: BLOCK DIAGRAM OF A SELF-ROUTING CENTRAL MEMORY SWITCHING ELEMENT   |

| FIGURE 3-11: TABLE CONTROLLED SWITCHING ELEMENTS                                |

| FIGURE 4-1: INPUT QUEUED SWITCHING ELEMENT SIMULATOR SCHEMATIC                  |

| FIGURE 4-2: KNOCKOUT SWITCHING ELEMENT SIMULATOR                                |

| FIGURE 4-3: KNOCKOUT BUS INTERFACE UNIT                                         |

| FIGURE 4-4: EIGHT INPUT LINE SHIFTER UNIT, FIRST TIMESLOT                       |

| FIGURE 4-5: EIGHT INPUT LINE SHIFTER UNIT, SECOND TIMESLOT                      |

| FIGURE 4-6: COPRIN SWITCHING ELEMENT                                            |

| FIGURE 4-7: STAGE 2 FOR A SUPER MULTIPLEXING BLOCK IN A COPRIN SWITCH ELEMENT   |

| FIGURE 4-8: FOUR STAGES OF THE SPACE SWITCH                                               | 49    |

|-------------------------------------------------------------------------------------------|-------|

| FIGURE 4-9: BUFFER MEMORY AND DE-MULTIPLEXING                                             | 51    |

| FIGURE 4-10: CONTROL BLOCK OF A COPRIN SWITCH                                             | 52    |

| FIGURE 4-11: SIMULATOR DESIGN AND CLASS INTERACTION DIAGRAM                               | 53    |

| FIGURE 4-12: CELLS LOST VS. QUEUE LENGTH FOR AN 8 X 8 SWITCHING ELEMENT WITH AN INPUT LOA | ND .  |

| of 90% and 10 <sup>8</sup> ATM cell timeslots                                             | 59    |

| FIGURE 4-13: CELLS LOST VS. QUEUE LENGTHS FOR A 2 X 2 OUTPUT AND CENTRAL QUEUED SWITCHIN  | IG    |

| elements with an input load of 90% and $10^8\mathrm{ATM}$ cell timeslots                  | 60    |

| FIGURE 4-14: QUEUE LENGTH VS. INPUT LOAD FOR A 2 X 2 SWITCHING ELEMENT, WITH A CELL LOSS  |       |

| RATE OF 10 <sup>-3</sup>                                                                  | 61    |

| Figure 5-1: Butterfly: A banyan, delta and bidelta network                                | 69    |

| FIGURE 5-2: A FOUR-INPUT SORTING CIRCUIT OF DEPTH THREE.                                  | 72    |

| FIGURE 5-3: A SIXTEEN ITEM SORTING CIRCUIT OF DEPTH TEN                                   | 73    |

| <br>FIGURE 5-4: A SORTING-TRAP-BUTTERFLY ROUTING NETWORK                                  | 75    |

| FIGURE 5-5: STACKED-BANYAN-BALANCING NETWORK                                              | 76    |

|                                                                                           |       |

|                                                                                           | · · · |

|                                                                                           |       |

|                                                                                           |       |

### **Abstract**

Asynchronous transfer mode (ATM) is rapidly becoming the primary transfer mode for implementing broadband integrated services digital networks (B-ISDN). These ISDN networks carry data, full motion video, audio, etc. Nowadays, networks with transfer rates of 100 mega bits per second (MBPS) to 622 MBPS are common, with users demanding even high transfer rates. Giga bits per second (GBPS) and tera bits per second (TBPS) networks are being designed and tested, to satisfy the increased bandwidth requirements.

ATM networks consist of two major parts; transfer medium and switches. The medium typically used is optical fiber, which can theoretically support infinite bandwidth. Hence, it is not the limiting factor, but rather ATM switches are the bottleneck to achieving high transfer rates. An ATM switch consists of two main components; switching elements and a switching fabric. The switching fabric is composed of identical switching elements, which are interconnected in a specific topology.

In this thesis, various ATM switch architectures are evaluated. Switching elements are classified as input queued, central queued, or output queued. Simulators are developed for the three different categories. The results generated from the simulators are analyzed and conclusions are drawn. Output queued switching elements, which are faster than central queued elements (because of less memory control overhead) can match the cell loss rate of central queued switching elements at the expense of a small increase in the amount of memory available.

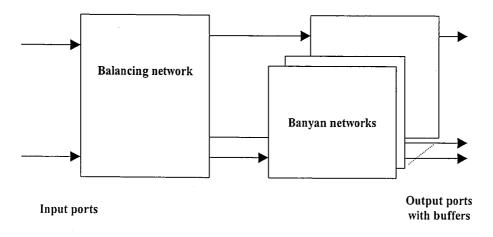

A theoretical analysis of a multistage interconnection network, without internal cell loss based on stacked banyan-balancing networks, indicates that it is better than a sorting-trap-butterfly network by a factor of  $log_2(N)$  in terms of the number of switching elements each cell has to pass through.

### 1. Motivation

With the rapid growth of the Internet, the role of computer networks is becoming extremely important. Currently the drive in the computer industry is for computer hardware and software to achieve higher performance with greater reliability. In the design of high-speed networks, fast response time and high data bandwidth are critical.

Computer networks consist of two main components: media to transfer information and network elements. To meet the increased bandwidth requirements, the performance of both these components has to be improved. After the advent of fiber optical cables, which are theoretically capable of supporting infinite bandwidth, network elements have become the limitation in the attempt to increase the bandwidth of computer networks.

One of the most promising technology for high-speed data, voice and video transfer is asynchronous transfer mode (ATM). Within ATM networks, ATM switches have been identified to be the bottleneck [12]. Currently, several ATM switches exists that use different architectural design concepts. To make faster ATM switches, operating in the tera-bits per second range, the switch architecture needs to use the right design decisions.

The currently available technology has also considerably improved, for instance the capacity of dynamic random access memory (DRAM) improves by four times in every three years. If in the design of a switch a few years ago a design decision was taken because the size of the DRAM was not sufficient, then the same restriction may not hold today. In this thesis, various ATM switch architectural design concepts are evaluated by developing simulators for different switches. The performance of two switching fabrics is also evaluated.

### 2. Introduction to Asynchronous Transfer Mode

This chapter provides a brief introduction to the concept of asynchronous transfer mode. It describes the basic principles of ATM networks, parameters used to evaluate the performance and traffic control in ATM networks, and the ATM protocol layer stack.

### 2.1 An Overview of Asynchronous Transfer Mode

Asynchronous Transfer Mode (ATM) is the transfer mode for implementing Broadband Integrated Service Digital Networks (B-ISDN). The term transfer includes both transmission and switching aspects, so a transfer mode is a specific way of transmitting and switching information in a network. In ATM, all information to be transferred is packed into fixed size slots called cells, which are 53 bytes long. The first 5 bytes form the header and the next 48 bytes form the information field. Figure 2-1 shows the structure of an ATM cell. The term asynchronous, in the context of multiplexed connections means that cells allocated to the medium may exhibit an irregular recurrence pattern as they are inserted into the medium according to the actual bandwidth of the connection.

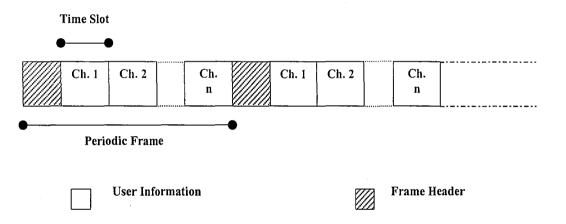

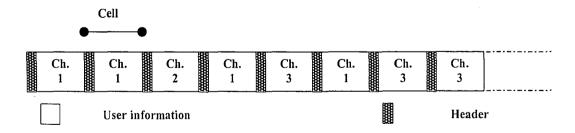

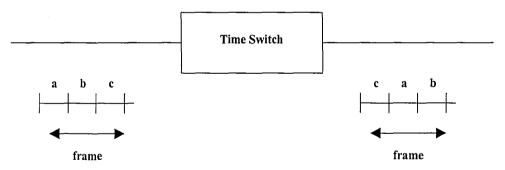

Examples of a synchronous transmission mode (STM) and an ATM transmission pattern are shown in Figure 2-2 and Figure 2-3, respectively. In STM, a data unit associated with a given channel is identified by its position in the transmission frame, while in ATM a cell associated with a specific virtual channel may occur at any position. This property provides ATM flexibility in allocation of bit-rate (i.e. bandwidth) to a specific connection or channel. Bit-rates in STM are restricted to a set of predefined channel bit-rates.

Networks are commonly categorized as circuit switched or packet switched networks.

In circuit switched networks a connection is established between the source and the destination before any information is transferred. In packet switched networks every packet

| Header  | Information field |

|---------|-------------------|

| 5 bytes | 48 bytes          |

|         |                   |

Figure 2-1: ATM cell structure.

Figure 2-2: Synchronous Transfer Mode

Figure 2-3: Asynchronous Transfer Mode

contains the address of the destination and is routed independently. Each of these techniques has their own advantages. ATM combines the advantages of both circuit and packet switched techniques. Circuit switched networks require a low processing overhead once a circuit is established, and the transfer delay of the information being carried is low and constant. Packet switched networks have more processing overhead while routing each packet, and the transfer delay of the packets is also not constant. However, packet switched networks can utilize the bandwidth of the network more efficiently, and are much more flexible in terms of the bit-rate assigned to individual connections.

ATM combines the advantages of both switching techniques by using the concept of virtual channels, which are connection-oriented channels. A connection-oriented channel is like a telephone call, because it involves a connection setup phase, an information transfer phase and a connection tear down phase. A connection within the ATM layer consists of one or more links, each of which is assigned an identifier. These identifiers remain unchanged for the duration of the connection. Also, cell routing is done in hardware to achieve low transfer delays.

ATM specifications guarantee cell sequence integrity under fault free conditions. Maintaining cell sequence integrity means that nowhere in the network can a cell belonging to a specific virtual channel connection overtake another cell belonging to the same virtual channel connection that was sent earlier.

### 2.2 Basic Principles of ATM

This section briefly describes the basic principles put forward by the International Telecommunication Union – Telecommunication (ITU-T) in [1].

### 2.2.1 Information Transfer

ATM is considered a packet oriented transfer mode based on asynchronous time division multiplexing and the use of fixed length cells. Each cell consists of an information field and a header. The header is primarily used to identify cells belonging to the same virtual channel within the asynchronous time division multiplex and to perform the appropriate routing. Cell sequence integrity is preserved on each virtual channel. The information field of ATM cells is carried transparently through the network. No processing, such as error control, is performed on the information field in the network. To accommodate various services such as voice, video, and data, several types of ATM Adaptation Layers (AAL) have been defined.

### 2.2.2 Routing

ATM is connection oriented. The header values are assigned to each section of a connection for the complete duration of the connection, and translated when switched from one section to another. Signaling information is carried on a separate virtual channel. Two sorts of connections are possible, virtual channel connections (VCC) and virtual path connections (VPC). A VPC can be considered to be an aggregate of VCCs. When switching, it must first be done based on the VPC and then on the VCC. For more details, refer to Section 2.3.

### 2.2.3 Resources

Since ATM is connection oriented, connections are established either semipermanently or for the duration of the call in the case of switched services. This establishment includes not only allocation of a virtual channel identifier (VCI) or/and virtual path identifier (VPI), but also the allocation of the required resources for the user access and inside the network. These resources are expressed in terms of throughput (bit-rate) and quality of service (QOS). They maybe negotiated between the user and the network for switched connections, during the call setup phase or possibly during the call.

### 2.2.4 ATM Cell Identifiers

ATM cell identifiers, which include virtual path identifiers (VPI), virtual channel identifiers (VCI) and payload type identifiers (PTI), support recognition of an ATM cell on a physical transmission medium. Recognition of the cell is the basis for all further operations. VPI and VCI values are unique for cells belonging to the same virtual connection on a shared transmission medium. Within a particular virtual circuit, cells may be further distinguished by their PTI, which cannot be allocated freely, but depends on the type of payload carried by the cell. This field indicates whether the cell is carrying user information to be delivered transparently through the network or special network information. In case the field indicates network information, part of the information field indicates the type of network control, and the rest of the information field may be processed inside the network.

A number of pre-assigned ATM cell identifiers have been chosen in the ATM layer for particular cell streams. They are necessary for enabling communication with the network and performing network management. Other pre-assigned values define meta-signaling cells, point-to-point signaling cells and general-broadcast cells.

### 2.2.5 Throughput

Bandwidth has to be reserved in the network for each virtual connection. ATM offers the possibility to realize resource savings in the total bandwidth needed when multiplexing traffic for many variable bit-rate connections. The amount that can be saved, however, depends heavily on the number of multiplexed connections, on the burstiness of the traffic they carry, on the correlation between them, and on the quality of service (QOS) required. Peak cell rate (PCR) and sustainable cell rate (SCR) are used as throughput parameters. PCR

is the maximum cell rate of the connection for the duration of the call. SCR is the maximum, mean cell rate measured over a period shorter than the duration of the call but longer than the cell inter-arrival interval.

### 2.2.6 Signaling

The negotiation between the user and the network with respect to the resources (e.g. VPI/VCI, throughput, QOS) is performed over a separate signaling virtual channel. The signaling protocol used over this channel is described in [2], [3], and [4].

### 2.2.7 Flow Control

There are three ATM layer service classes with respect to the bandwidth usage, i.e. constant bit-rate (CBR), variable bit-rate (VBR) and available bit-rate (ABR). An application requests for CBR, if its bandwidth needs are constant. A VBR application requires a variable amount of bandwidth. The bandwidth available in the network at any given time may not be completely allocated. ABR applications make use of this unallocated bandwidth. ABR applications can handle varying throughput and the possibility of increased delay.

To effectively manage the network bandwidth resource a fast signaling and control flow mechanism is used. There are two types of flow control mechanisms used in ATMs; generic flow control and resource management cells. More details about flow control can be found in [5].

### 2.3 Virtual Paths and Virtual Channels

Virtual channel (VC) is a unidirectional transport of ATM cells associated by a common unique identifier value. This identifier is called the virtual channel identifier (VCI) and is a part of the cell header. Virtual Path (VP) is a unidirectional transport of cells belonging to virtual channels that are associated by a common identifier value. This identifier

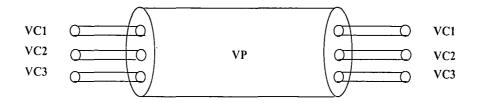

is called the virtual path identifier (VPI) and is a part of the cell header. The relationship between virtual channels and a virtual path is show in Figure 2-4. A virtual path may carry one or more virtual channels.

A virtual channel link provides a means for unidirectional transport of ATM cells between the point where a VCI value is assigned and the point where it is translated or removed. The points where a VPI is assigned and translated terminate a virtual path link. A concatenation of VC links is called a virtual channel connection (VCC) and a concatenation of VP links is called a virtual path connection (VPC).

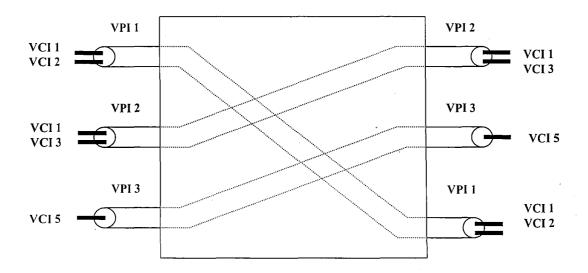

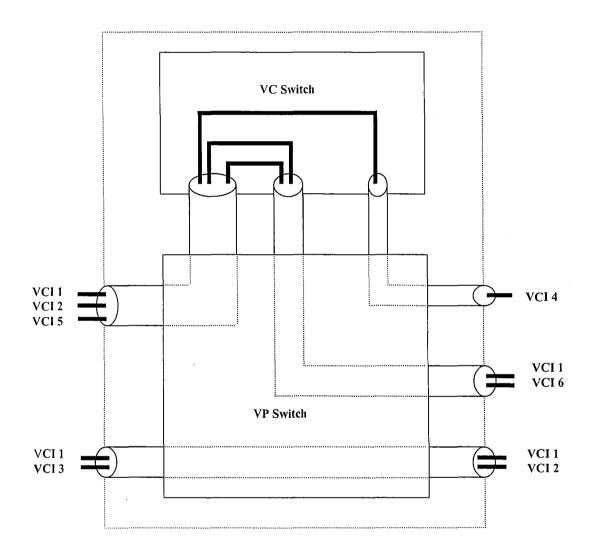

Switching of virtual channel connections / virtual path connections is achieved by translating one or both of the values of VCI/VPI in a VC/VP switching entity. VP switches terminate VP links and therefore have to translate incoming VPIs to the corresponding outgoing VPIs, according to the destination of the VP connection. The VCI values remain unchanged. Figure 2-5 shows a VP switch. A VC switch terminates both VC links and VP links and performs VPI and VCI translation. Figure 2-6 shows a VC switch.

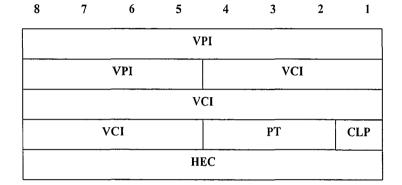

### 2.4 ATM Cell Header structure

Figure 2-7 shows the structure of an ATM cell header at the network node interface. The first field is the routing field, which is subdivided into twelve-bit and sixteen-bit fields. The twelve-bit field holds the VPI and the sixteen-bit field holds the VCI. The payload type identifier (PTI) is coded in three bits. The cell loss priority (CLP) field consists of one-bit and indicates whether the cell has a higher priority (CLP=0) or is subject to discarding by the network (CLP=1). Finally, the header error check (HEC) field consists of eight bits and is used for error detection and correction on the header.

Figure 2-4: Relationship between a virtual path and virtual channel.

Figure 2-5: Virtual path switch

Figure 2-6: Virtual channel / Virtual path switch

VPI: Virtual Path Identifier (12 bits) VCI: Virtual Channel Identifier (16 bits)

PT: Payload Type (3 bits) CLP: Cell Loss Priority (1 bit) HEC: Header Error Check (8bits)

Figure 2-7: ATM Cell header (Network-Network Interface)

### 2.5 Broadband Network Performance

Broadband networks based on ATM cell transfer must meet certain performance requirements. ATM performance parameters and measures need to be specified in addition to the performance parameters of existing networks. These parameters are knows as quality of service parameters. When a connection establish request is made, a set of minimum acceptable quality of service (QOS) parameters is also specified. A connection is established only if the network can guarantee the QOS parameters. Assume 'A' and 'B' are the two endpoints of a virtual channel in an ATM network. Cells belonging to the virtual connection are delivered from 'A' to 'B'. Because there is some transfer delay, the cell sent from 'A' arrives at 'B' within some time  $\delta > 0$ . A cell exit event occurs at 'A' when the first bit of the cell leaves 'A' and a cell entry event occurs at 'B' when the last bit of the cell reaches B.

In order to adequately describe the quality of ATM cell transfer, the following outcome categories are defined [6]:

- 1. Successfully Transferred Cell: If  $\delta$  is less than a maximum allowed time T and the cell is not affected by bit errors, then the cell has been successfully transferred.

- 2. Erroneous Cell: If the cell arrives in due time but there are one or more bit errors in the received cell information field, the cell is erroneous.

- 3. **Lost Cell**: A lost cell outcome occurs if the cell arrives after time T or never reaches 'B'. Errors in the ATM cell header that cannot be corrected or cell buffer overflows in the switches lead to lost cells.

- 4. **Misinserted Cell:** If a cell that has not been sent from 'A' on the virtual channel to 'B', arrives at 'B' on the 'A' to 'B' virtual channel, then this miss-delivered

- cell produces a misinserted cell outcome. Header errors that are not detected or are erroneously corrected may produce miss-inserted cells.

- 5. Severely Erroneous Cell Block: A severely erroneous cellblock occurs if more than M erroneous cells are observed in a block of N cells transmitted consecutively on a given connection.

By making use of the above considerations, performance parameters for the network are defined. The parameters and their definitions are listed in Table 2-1.

| Parameter                           | Definition                                                                                                             |  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|

| Cell loss ratio                     | Ratio of lost cells to transmitted cell                                                                                |  |

| Cell misinserted rate               | Number of misinserted cells per connection per second                                                                  |  |

| Cell error ratio                    | Ratio of erroneous cells to the number of delivered (successful + erroneous) cells                                     |  |

| Severely erroneous cell block ratio | Ratio of the number of severely erroneous cell blocks to total number of cell blocks (fixed number of cells)           |  |

| Mean cell transfer delay            | Arithmetic average of a specified number of cell transfer delays                                                       |  |

| Cell delay variation                | Difference between a single observation of cell transfer delay and the mean cell transfer delay on the same connection |  |

Table 2-1: ATM performance parameters

Bit errors in erroneous cells can be corrected to a certain extent by error correction methods. Lost or misinserted cells can cause severe problems if they are not detected. For example, when using a constant bit-rate, the real time services synchronism between sending and receiving terminals may be disturbed. This can be overcome by using sequence numbers. Cell transfer delay and cell delay variation must be kept within a limited range in order to meet service requirements. Cell transfer delay and ATM switches, due to buffering introduce cell delay variation.

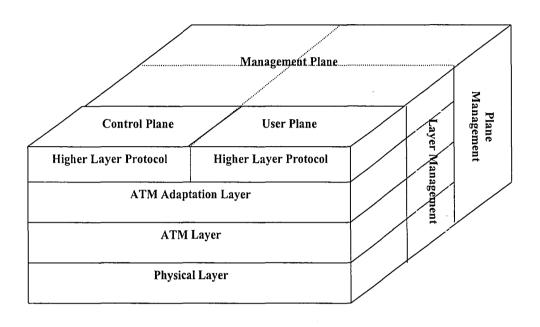

### 2.6 ATM Layer Model

ATM has three layers; the physical layer (PL), the ATM layer and ATM adaptation layer (AAL). It contains three planes: a user plane to transport user information, a control plane mainly composed of signaling information, and a management plane used to maintain the network. In addition, a third dimension is added to the protocol reference model (PRM), called the plane management, which is responsible for the management of different planes. Figure 2-8 shows the PRM. ITU-T recommendation I.321 describe the PRM for ATM [7].

The physical layer (PHY) transports information (bits and cells). The ATM layer mainly performs switching, routing and multiplexing. The AAL is mainly responsible for adapting service information to the ATM stream. Each of the layers can be further subdivided into sub-layers. Each sub-layer performs a number of functions, as shown in Table 2-2.

### 2.6.1 Physical Layer

The Physical layer is further sub-divided into the physical medium (PM) sub-layer which supports medium dependent bit functions, and the transmission convergence (TC) sub-layer which converts the ATM cell stream into bits to be transported over the physical medium. The physical layer for the UNI is described in [8].

### 2.6.1.1 Physical medium sub-layer

The physical medium sub-layer is responsible for the correct transmission and reception of bits on the appropriate physical medium. This sub-layer must guarantee a proper bit timing reconstruction at the receiver. The transmitter is responsible for inserting the required bit timing information and line coding.

Figure 2-8: ATM Protocol Reference Model

| Layer | Sub Layer                                   | Function                                         |  |

|-------|---------------------------------------------|--------------------------------------------------|--|

| AAL   | Convergence Sub-layer (CSL)                 | Message identification and time/clock recovery   |  |

|       | Segmentation and Reassembly Sub-layer (SAR) | Segment and re-assemble higher layer information |  |

| ATM   |                                             | Generic flow control                             |  |

|       |                                             | Cell VPI / VCI translation                       |  |

|       |                                             | Cell multiplex / de-multiplex                    |  |

|       |                                             | Cell rate de-coupling (with unassigned cells)    |  |

| PHY   | Transmission                                | Cell rate de-coupling (with idle cells)          |  |

|       | Convergence                                 | Header error check (HEC) generation /            |  |

|       |                                             | verification                                     |  |

|       |                                             | Cell scrambling / de-scrambling                  |  |

|       |                                             | Cell delineation (using HEC)                     |  |

|       |                                             | Path signal identification                       |  |

|       |                                             | Frequency justification                          |  |

|       |                                             | Frame scrambling / de-scrambling                 |  |

|       |                                             | Frame generation / recovery                      |  |

|       | Physical Medium                             | Bit timing                                       |  |

| ļ     |                                             | Line coding                                      |  |

|       |                                             | Physical medium dependent scrambling / de-       |  |

|       |                                             | scrambling                                       |  |

Table 2-2: ATM protocol reference model sub-layers and functions

### 2.7.1.2 Transmission convergence sub-layer

The first function performed by this sub-layer is the adaptation to the transmission system used, such as synchronous digital hierarchy (SDH), plesiochronous digital hierarchy (PDH) or cell based. The second function of the sub-layer is generation of the header error check (HEC) for each cell at the transmitter and its validation at the receiver. During startup, to detect the proper cell boundary, an ATM network element needs to validate a number of HEC values for each cell. If it can successfully perform this check on a specific number of cells it means that the correct cell boundary has been detected. Once cell delineation has been found, an adaptive mechanism uses the HEC for correction and detection of cell header errors. Isolated single bit errors are corrected, but as soon as multiple consecutive cells show header errors, correction is given up for higher precision detection and elimination of cells

with errors. To avoid the slipping of cells with undetected multiple header errors during periods of bit error bursts. Such errors may go undetected by the correction algorithm. Finally, this sub-layer must ensure insertion and suppression of unassigned cells to adapt the useful cells to the available payload.

### 2.6.2 ATM Layer

The ATM layer is independent of the physical medium used to transport the ATM cells. The ATM layer is responsible for performing the following functions.

- The multiplexing and de-multiplexing of cells of different connections identified by different VCI and VPI values, into a single cell stream on a physical layer.

- Translating the cell identifier, which is required in most cases when switching a

cell from one physical link to another in an ATM switch. This translation can be

performed on the VCI, the VPI, or both.

- Providing the user of a VCC or VPC with one QOS class, out of a number of

classes supported by the network. Some services may require a certain QOS for

one part of the connection, and a lower QOS for the remainder. The distinction

within the connection is made by means of the CLP bit in the cell header.

- Performing management functions, such as setting the PTI field in the cell header

to indicate congestion. When the PTI does not indicate user information, more

information related to layer management is present in the information field of the

cell.

- Extracting of the cell header before the cell is delivered to the adaptation layer and adding the cell header after the cell is delivered from the adaptation layer to be transmitted.

• Implementing a flow control mechanism on the user network interface using the generic flow control bits in the cell header.

### 2.6.3 ATM Adaptation Layer

The ATM adaptation layer enhances the service provided by the ATM layer to a level required by the next higher layer. It performs functions for the user, control, and management planes, and supports the mapping between the ATM layer and the next higher layer. The functions performed by the AAL layer depend on the higher layer requirements.

The AAL layer is divided into two sub-layers: the segmentation and re-assembly (SAR) sub-layer and the convergence sub-layer (CS). The main function of the SAR sub-layer is to segment the higher layer information into suitable size payloads for the consecutive ATM cells of a virtual connection on the transmit side. On the receiver side re-assembly of the contents of the cells is performed. The convergence sub-layer performs functions like message identification, time/clock recovery, etc. If an application finds the service provided by the ATM layer sufficient, then the AAL layer may be empty.

There are four classes of AAL layers. To obtain these four classes the services are classified according to three basic parameters.

- Time relation between source and destination: Some services have a time relation between the source and destination, while for others there is no such time relation. For instance, in 64 KBPS PCM voice, there is a clear time relation between the source and destination. Information transfer between computers has no time relation. Services with a time relation are also called real time services.

- Bit-rate: Some services have a constant bit-rate, while others have a variable bit-rate.

Connection mode: Services can be either connectionless or connection oriented.

Connectionless mode is similar to packet switching, whereas connection oriented mode is similar to circuit switching. In connection oriented mode, all the information is sent through the same path decided upon during connection setup.

In connectionless mode this is not true.

Only four of the theoretical eight combinations of the three parameters yield existing services. For details refer to ITU-T 's I.362 recommendation [9]. Table 2-3 gives a quick reference.

- In Class A, a time relation exists between source and destination. The bit-rate is constant and the service is connection oriented. Typical examples include a 64 KBPS voice transmission and a fixed bit-rate video transmission.

- In Class B, again a time relation exists between the source and the destination, for a connection oriented services. However, the difference from class A is that Class B sources have a variable bit-rate. Examples of this include variable bit-rate audio and video.

- In Class C there is no time relation between the source and the destination and the bit-rate is variable. The service is connection oriented. Examples of this include connection oriented data transfer and signaling.

- Class D differs from Class C in that it is connectionless. An example of such a service is connectionless data transport, such as video broadcast.

|                 | Class A  | Class B                            | Class C | Class D   |

|-----------------|----------|------------------------------------|---------|-----------|

| Timing relation | Ex       | Exists Does not a                  |         | not exist |

| between source  |          |                                    |         |           |

| and destination |          | <u></u>                            |         |           |

| Bit-rate        | Constant | Variable                           |         |           |

| Connection      |          | Connection oriented Connectionless |         |           |

| mode            |          |                                    |         |           |

Table 2-3: Service classes for ATM adaptation layer

### 3 ATM Switches

### 3.1 Introduction

In the past, various switching architectures were developed for different applications, such as voice and data, based on transfer modes like synchronous transfer mode (STM) and packet transfer mode (PTM). The switching architectures developed for STM and PTM are not directly applicable to broadband ATM [10].

The two main factors that have a large impact on the implementation of broadband ATM switching architectures are

- The high speeds at which the switch has to operate (from 150 to 600 MBPS)

- The statistical behavior of the ATM streams passing through the ATM switch

In addition, the small fixed cell size and a limited functionality cell header have an important influence on the definition of an optimal ATM switching architecture. A number of ATM switches are commercially available from various telecommunication companies ranging from very small (four inputs and outputs) to very large (thousands of inputs and outputs).

In an ATM switch, the ATM cells are transported from an input port (out of N input ports) to one or more output ports (out of M output ports). This switching from input port to output port might be combined with concentration, expansion, multiplexing and demultiplexing of ATM traffic.

### 3.2 Switching

Switching is the transportation of information from an incoming ATM channel to an outgoing logical channel. A logical channel is characterized by

• A physical input port / output port having a physical port number

• A virtual channel identifier (VCI) and virtual path identifier (VPI)

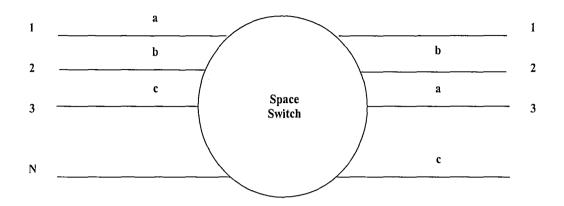

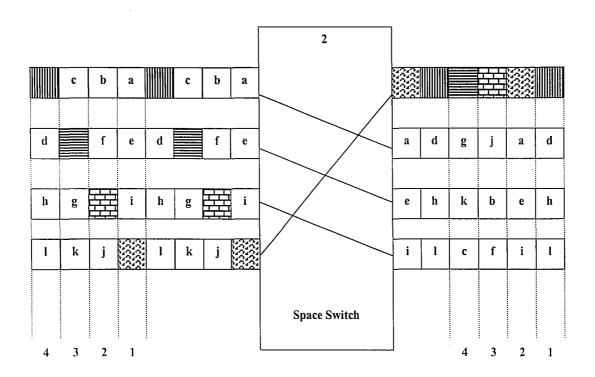

To perform switching, both the input port and incoming virtual channel/path identifier have to be related to the output port and outgoing virtual channel/path identifier. In any ATM switching system these two functions have to be implemented and can be compared to functions applied in classical STM switching systems, as described in [11]. Relating the ports is comparable to a space switching function (S), as shown in Figure 3-1. Information from input port 1 is transported to output port 3, whereas information from input port 3 is transported to output port M. An important aspect of space switching is routing. Relating virtual channel/path identifiers is comparable to a time slot interchange (T) in a time switch as shown in Figure 3-2. Information from time slot i is switched to time slot j, whereas information from time slot k is transported to time slot 1.

Modern STM switches are often composed of these S and T stages, in different sorts of combinations like STSTS, STSSTS, or TSTTST. In ATM switching systems, however, the time identification in a fixed frame is replaced by logical channel identification. Since the pre-assigned time slot concept disappears in ATM switching systems, contention problems arise if 2 or more logical channels contend for the same time slot. This can be solved by temporarily queuing the ATM cells before sending them out. This queuing function is the second important aspect of ATM switching systems.

### 3.3 Concentration / multiplexing

In ATM, the distinction between multiplexing and concentration is rather vague. Multiplexing is used when the emphasis is put on the statistical merging of different ATM virtual channels (cell streams) on a single ATM stream. Concentration is used when the stress is on the reduction of a number of input ports to a smaller number of output ports.

Figure 3-1: A Space Switch

Figure 3-2: A Time Switch

### 3.4 Basic Function of an ATM Switch

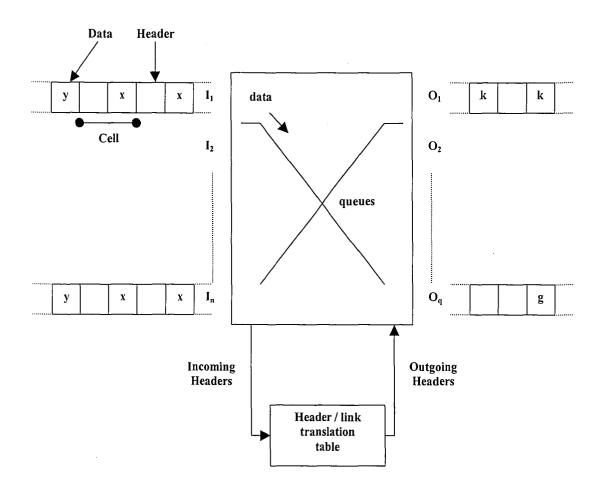

The basic function of an ATM switch is shown in Figure 3-3 and described in detail in [12]. Incoming ATM cells are physically switched from an input port  $I_i$  to an output port  $O_j$ , and at the same time their header value is translated from an incoming value of  $\alpha$  to an outgoing value of  $\beta$ . On each incoming and outgoing link, the values of the header are unique, but identical headers can be found on different links. For example, in Figure 3-3 and Table 3-1, x appears on two input ports  $I_1$  and  $I_n$ . All cells which have a header equal to y on incoming link  $I_1$  are switched to output port  $O_q$  and their header value is changed to m. All cells with a header x on link  $I_n$  are switched to output port  $O_1$  and their header value is set to n.

Two main tasks that need to be performed by an ATM switch are:

- VPI / VCI translation

- Cell transport from its input to its dedicated output

An ATM switch performs VPI / VCI translation by modifying the cell header. Cell transport from its input to its dedicated output is achieved by space switching. It is possible for two cells arriving simultaneously from different input ports of the ATM switch, destined for the same output port (O<sub>1</sub>). To prevent the two cells destined for the same output port from colliding and corrupting each other, either one of them has to be dropped or queued. Since a low cell loss rate is desired for ATM switches, cells are dropped only as a last resort. Buffers are incorporated into the design of an ATM switch to queue the cells that cannot be routed.

Figure 3-3: ATM switching principle

| Incoming link | Header | Outgoing link  | Header |

|---------------|--------|----------------|--------|

| $I_1$         | X      | O <sub>1</sub> | K      |

|               | Y      | $O_q$          | M      |

|               | Z      | O <sub>2</sub> | L      |

|               |        |                | ,      |

|               |        |                |        |

| $I_n$         | X      | O <sub>1</sub> | N      |

|               | Y      | $O_2$          | I      |

|               | S      | Oq             | G      |

Table 3-1: Translation table

To conclude, an ATM cell performs the following three functions: routing (space switching), queuing and header translation. The way these functions are implemented and where in the switch these functions are located distinguishes one switch from another.

### 3.5 Switching Requirements

Broadband networks must be capable of transporting all kinds of information, ranging from voice to high quality video. These services have different requirements in terms of bit-rate (from a few KBPS up to hundreds of MBPS), behavior in time (constant bit-rate or variable bit-rate), semantic transparency (cell loss rate and bit error rate) and time transparency (delay and delay jitter). These different service requirements have to be met by broadband ATM switches.

#### 3.5.1 Information Rate

Since the information rates of the different services are very diverse, a large number of information rates must be supported in broadband switches. These rates range from a few KBPS (e.g. for voice) up to values of 150 MBPS (e.g. for: high definition television (HDTV)). If an ATM switch operates at 150 MBPS, it does not mean that the switch internally operates at 150 MBPS. Its internal operating speed may be lower or greater than 150 MBPS depending on its architecture. For example, switching can be realized over parallel wires resulting in a lower internal speed, or several 150 MBPS input ports can be multiplexed on a single link resulting in a higher internal speed.

## 3.5.2 Performance

The performance of classical STM switches is mainly characterized by the switch's throughput, connection blocking probability, bit error rate and switching delay, as described in [13]. In an ATM environment, however, two other parameters are important, namely the

cell loss or cell miss-insertion probability and the delay jitter. In ATM switches, as in STM switches, the fabrication technology and dimension of the switch mainly determine the throughput and the bit error rate [14] [15]. The effect of connection blocking, cell loss / miss-insertion probability and switching delay are different in ATM switches and are described below.

#### 3.5.2.1 Connection blocking

Since ATM is connection oriented during the connection set-up phase, a logical connection needs to be established between a logical input port and output port. The probability of not finding enough resources between the input and output ports of the switch to guarantee the quality of all existing connections and the new connection is defined as connection blocking.

Some switch implementations do not have internal connections. This means that if enough resources (i.e. bandwidth and header values) are available on the input port and the output port of the switch, no new connection is blocked. Thus, a new connection is always accepted if enough resources are available on the external links, without an explicit check of the internal switch resources. Other switch implementations that have internal connections exhibit internal connection blocking. Internal connection blocking occurs when there are not enough resources for the new connection that can be allocated within the switch. Their dimension, the number of existing internal connections, and the load on those connections determine the blocking probability of internal connection blocking switches.

## 3.5.2.2 Cell loss and cell miss-insertion probability

In ATM switches, it is possible for many cells to be destined for the same link (this link can be internal or external to the switch). This may cause more cells than the queue's capacity to compete for the queue's storage space, resulting in cells being dropped or lost.

The probability of losing a cell must be kept within limits to ensure a high semantic transparency (clear communication between the transmitting and receiving application). Typical values for cell loss probability for ATM switches range between 10<sup>-8</sup> and 10<sup>-11</sup>.

Some switch architectures are designed in such a way that they do not suffer from cells competing for the same resource internally (e.g. a queue). These architectures do not lose ATM cells internally, but may lose cells only at their input and output ports. These switches are called internally non-blocking switches.

Sometimes cells in an ATM switch may be misrouted only to arrive erroneously on another logical connection. This occurs when the cell header gets corrupted during transmission and it goes undetected through the error checking stage. The probability of this cell miss-insertion must be kept within limits. Typical, cell miss-insertion values are a factor of 1000 times less than the cell loss rate.

#### 3.5.2.3 Switching Delay

Switching delay is the time to transmit an ATM cell through the switch. Typical values for the switching delay of ATM switches range between 10 and 1000 micro-seconds with a jitter of few 100 micro-seconds or less, described in [6]. Jitter is determined by the probability that the delay of the switch will exceed a certain value. For example a jitter of 100 microseconds for 10<sup>10</sup> cells, means that the probability that the delay in the switch is larger than 100 microseconds is smaller than 10<sup>-10</sup>.

#### 3.6 Basic Architecture of an ATM Switch

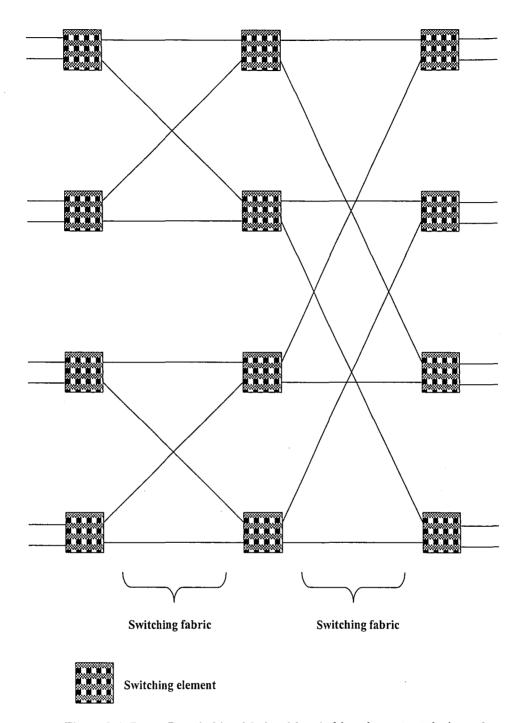

The basic architecture of a butterfly based ATM switch is shown in Figure 3-4. In general an ATM switch consists of two parts: switching elements and switching fabric.

Figure 3-4: Butterfly switching fabric with switching elements at the its nodes

The switching element is the generic building block used to construct an ATM switching fabric. Switching elements are also called basic switching blocks [16]. A switching fabric is composed of identical basic switching elements interconnected in a specific topology. Thus, a switching fabric is defined when its topology is determined and when the switching elements are defined.

### 3.7 Switching Elements

ATM switching elements have a small number of input and output ports. Typical sizes for switching elements are 2 by 2 to 16 by 16. The operating speed of most switching elements ranges from 150 MBPS to 2.4 GBPS or greater. The size (number of input and output ports) and speed depend on the fabrication technology and the level of integration used.

This section discusses the queuing problems of a switching element. If two ATM cells arrive at two input ports of the switching element for the same output during the duration of one cell, one of them has to be queued for a later cell time. Depending on the particular architecture of the switching element and the required internal speed, it is possible to queue cells at the input port, output port, or internally in the switching element [17]. There are some switching element architectures which have a fully non-blocking (per cell) switch fabric. Such architectures do not need to maintain internal queues. This contention-free characteristic guarantees that if all incoming cells of the switch architectures are destined for a different output port, no internal contention will arise. Switching elements which buffer cells destined for the same output port can be categorized into three categories determined by the physical location of the buffers: at the input, at the output, or central in the switching element [18].

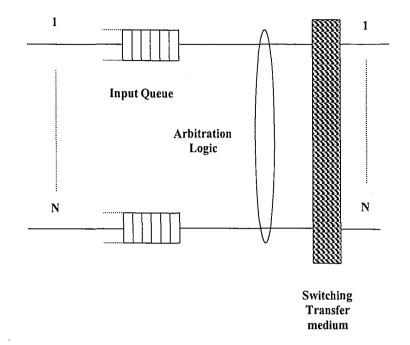

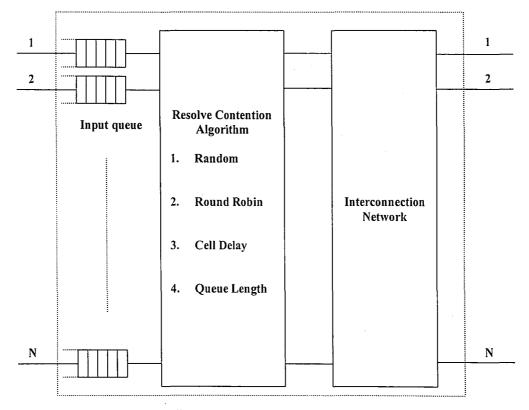

## 3.7.1 Input Queued Switching Element

The block diagram of a switching element with input queuing is shown in Figure 3-5. In an input queued switching element all incoming cells are queued in a buffer at the input port. The arbitration logic determines which cell to serve in case of contention. The switching transfer medium then transfers the ATM cells from the input queues to the output port without internal contention. The arbitration logic which decides which input port to serve can range from very simple, such as round robin to quite complex, such as, taking into account the input buffer filling levels, delays of cells, etc.

Input queued switching elements have a major disadvantage called head of the line (HOL) blocking. Suppose that the cell of input port i is selected to be transferred to output port p. If input port j also has a cell destined for output port p, this cell will be stopped, together with all following cells. Suppose that the second cell in the queue of input port j is destined to an output port q for which there is currently no cell waiting in the other queues. Then this cell cannot be served, since the cell in front of it in the queue is blocking the transfer.

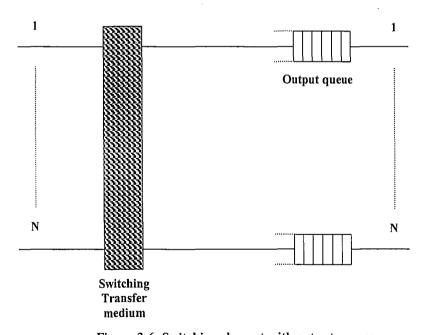

#### 3.7.2 Output Queued Switching Element

The block diagram of a switching element with output queuing is shown in Figure 3-6. In the output queued switches, cells of different input ports destined to the same output port are transferred during one cell time to their corresponding output port. Only a single cell is served at the output port. If there are more than one cells destined to the same output port, a contention problem arises, which is solved by having a separate queue for each output port.

In principle, cells can arrive simultaneously at all input ports destined to a single output port. To ensure that no cells is lost in the switching transfer medium before it arrives at the output queue, the cell transfer must be performed at N times the speed of the input ports.

Figure 3-5: Switching element with input queues

Figure 3-6: Switching element with output queues

The system must be able to write N cells in the queues during one cell times. In the switching transfer medium, no arbitration logic is required. The control of the output queues is based on a simple first in first out (FIFO) discipline to ensure that cells remain in the correct sequence.

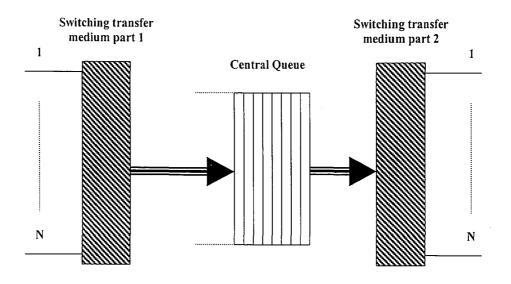

## 3.7.3 Central Queued Switching Element

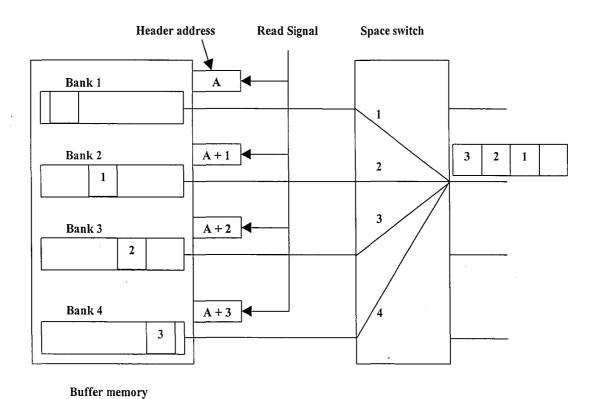

The block diagram of a switching element with central queuing is shown in Figure 3-7. In the central queued approach, the buffers are not dedicated to a single input port or output port, but shared between all input and output ports. Each incoming cell is directly stored in the central queue. Every output port selects the cells destined for it from the central memory in a FIFO discipline.

Internally, provisions are made to ensure that the output ports know which cells are destined for them. The read and write discipline of the central queue is not a simple FIFO discipline, since cells for different destinations are all merged in to a single queue. This means that the central memory is addressed in a random manner. The logical queues apply the FIFO discipline. Since cells can be written and read at random memory locations, a rather complex memory management system has to be used.

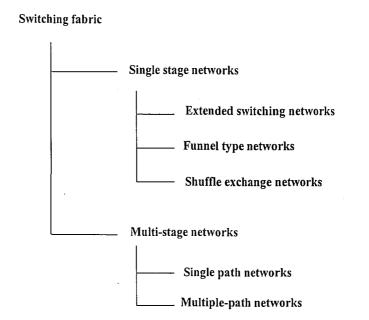

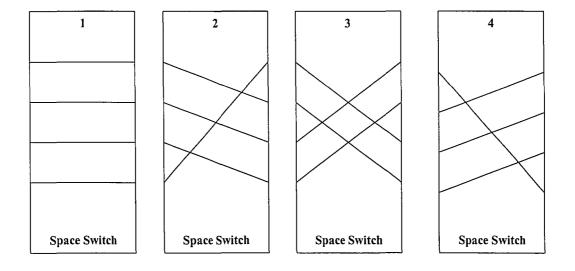

#### 3.8 Switching Fabrics

This section gives a general classification of switching networks [19]. A survey of various switches can be found in [20], [21], [22]. Figure 3-8 gives a classification of switching networks. Switching fabrics are categorized into two general categories depending on the number of stages. A switching fabric is also known as a switching network.

Figure 3-7: Switching element with central queuing

Figure 3-8: Classification of switching networks

## 3.8.1 Single Stage Networks

A single stage network is characterized by a single stage of switching elements connected to the inputs and output ports of the switching network / fabric. Categories of single stage fabrics are extended switching matrices, funnel type networks and shuffle-exchange networks. Single stage fabrics are useful for constructing smaller switches. With the increase in the number inputs, the number of switching elements also has to be increased, which in turn increases the delay in switching cells. To construct switches with 128 or more input / output ports, multi-stage fabrics are preferred.

## 3.8.2 Multi-Stage Networks

Multi-stage networks are built from several stages which are interconnected in a certain link pattern. According to the number of paths available for reaching a destination output port from a given input port, these fabrics are classified into two groups called single-path and multiple-path networks.

#### 3.8.2.1 Single Path Networks

In single path networks, there is only one path to the destination from a given input. These networks are also called Banyan networks [23]. Since there is only one path to the destination port, routing is simple. The disadvantage is that internal blocking can occur as an internal link can be used simultaneously by different groups. Banyan networks can further be classified into sub groups.

In L level Banyan networks, only the switching elements of adjacent stages are interconnected. Each path in the network passes through exactly L stages. L level Banyan networks are further subdivided into regular and irregular Banyan networks. Regular Banyan networks are constructed from identical switching elements, whereas irregular Banyan

networks use different types of switching elements. Regular Banyan networks have an advantage that they can be implemented easily because of they are constructed from identical elements.

#### 3.8.2.2 Multiple Path Networks

In multiple-path networks, a multiplicity of alternative paths exists to the destination output from a given input port. This property has the advantage that internal blocking can be reduced or avoided altogether [24]. In most multiple-path networks, the internal path is determined during the connection setup phase. All cells on the connection use the same internal path. As all cells follow the same path, switching elements can uses a FIFO policy without worrying about cell sequence integrity.

Multiple path networks are further subdivided into folded and unfolded networks. In folded networks, all inputs and outputs are located at the same side of the switching network and the network's internal links operate in both directions. Folded networks have the advantage that the paths are short [25] [26]. For example, if the input and output ports are connected to the same switching element, cells can be reflected at the switching element and need not be passes to the last stage. The number of switching elements that the cells of a connection have to pass through depends on the location of the input and output lines.

In unfolded networks, the inputs are located on one side and the outputs on the opposite side of the network. Internal links are unidirectional and all cells have to pass through the same number of switching elements.

Multiple-path networks can also be realized by using several planes of Banyan networks in parallel. [27]. This is called vertical stacking. All cells belonging to the same connection pass through the same plane. The plane and the path within the plane are determined during the connection setup phase. An incoming cell is switched to its appropriate

plane by a distribution unit located at each input port. In [24], it is shown that even with two planes in parallel a virtually non-blocking switching structure can be achieved. Adding a number of stages of a Banyan network, one after the other, yields a horizontal stack.

#### 3.9 Cell Header Processing in Switching Fabrics

Switching fabrics need to perform VPI / VCI translation and route the cells to the correct output port. In order to fulfil these tasks, two approaches can be used

- Self-routing principle

- Table-controlled routing principle

Studies have been made to decide which principle is superior [28]. For large multistage switching networks the self-routing principle is preferred because it is superior in terms of control complexity and failure behavior. The need for a higher internal bit rate because of the cell extension in self-routing networks is not critical.

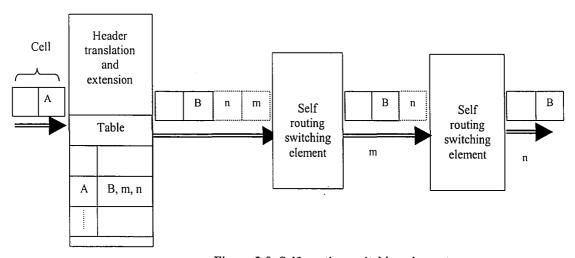

## 3.9.1 Self Routing Switching Elements

When using self-routing elements, VPI/VCI translation only has to be performed at the input port of the switching network. After the translation, a switching network internal header is added to the cell. This header precedes the cell header. Because of the cell header extension an increased internal network speed has to be maintained.

In a network with k stages, the internal header is subdivided into k sub-fields. Sub-field i, contains the destination output port number of the switching element in stage i of the switching fabric. Figure 3-9 shows the cell header processing in a switching network built up of self-routing switching elements.

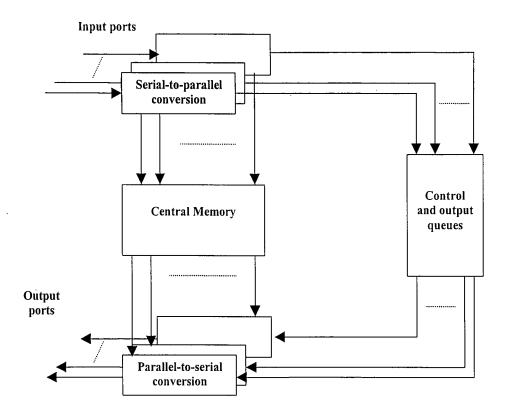

Figure 3-10 shows a generic block diagram of a self-routing switching element [29]. It contains a central memory with logical output queues and is controlled by the routing

information included in the internal cell header. In order to keep the buffer access speed within a realistic range a wide parallel memory interface is used requiring serial-to-parallel conversion at the input and parallel-to-serial conversion at the output.

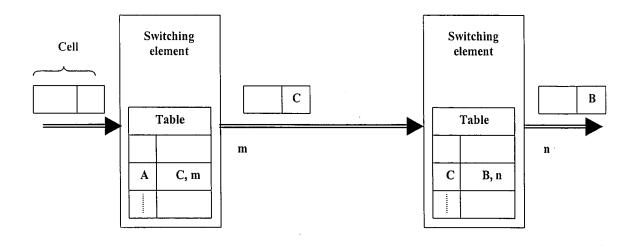

## 3.9.2 Table Controlled Switching Elements

In table controlled switching elements, the VPI / VCI of the cell header is translated into a new identifier in each switching element. Therefore, the cell length does not need to be altered. Figure 3-11 shows the header processing in a switching network which consists of table controlled switching elements. The contents of the table are updated during the connection setup phase. Each table entry consists of the new VPI / VCI and the number of the appropriate output link.

Figure 3-9: Self-routing switching elements

Figure 3-10: Block diagram of a self-routing central memory switching element

Figure 3-11: Table controlled switching elements

## 4. ATM Switch Simulation Results

This chapter describes the simulators developed for the three different categories of switching elements. Simulators described are for a regular input queued switching element, an output queued switching element (i.e. Knockout switching element [30], [31] [32]), and a central queued switching element (i.e. Coprin switching element [33]).

## 4.1 A Generic Input Queued Switching Element

Figure 4-1 shows a block diagram of an input queued switching element. The input buffers of an input queued switching element do not need to have very fast access times compared to an output or central buffered switching element. This is because the input buffers need to be written and read only once during one timeslot. However, all input queued switches have a major disadvantage called head of the line (HOL) blocking, explained in the previous chapter.

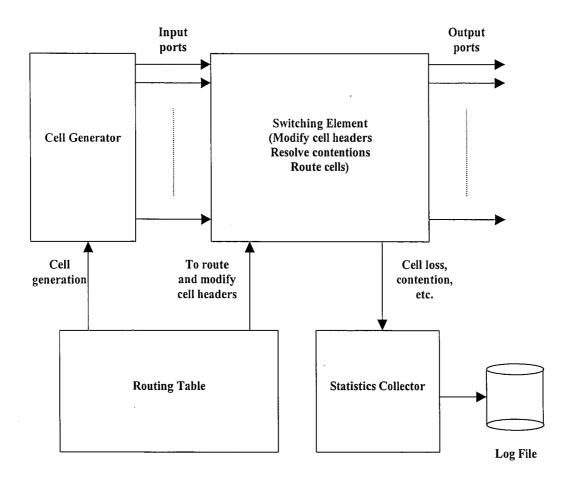

Figure 4-1: Input queued switching element simulator schematic

The input queued switching element has a generic architecture. More details about it can be found in the previous chapter and [18].

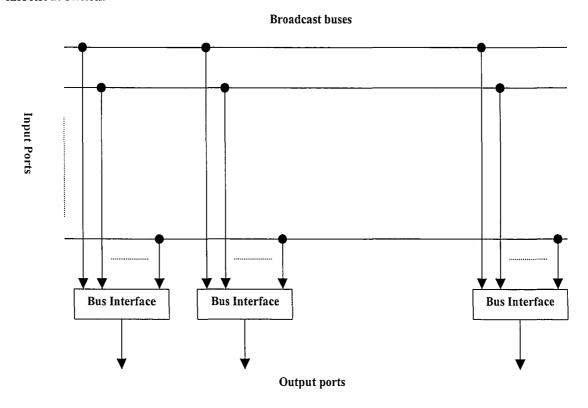

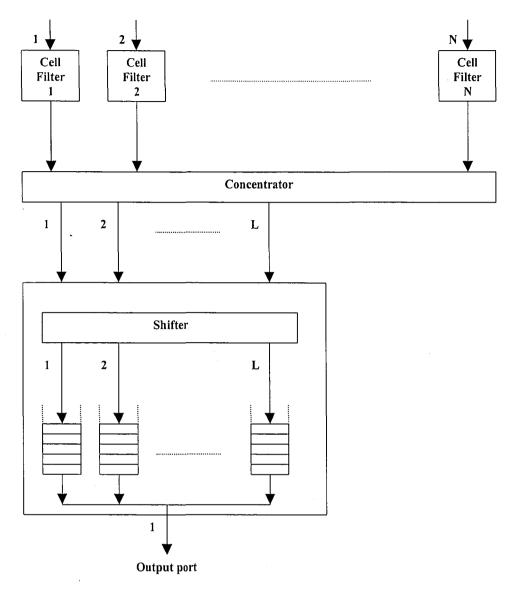

## 4.2 Output Queued Switching Element (Knockout Switching Element)

A Knockout switch is an example of an output queued switching element and is describe in detail in [30] [31] [34]. In a knockout switching element, the access time for an output memory has to be very fast, because for a N X N output queued switch it is possible for all the cells from the input port to be destined to the same output port. Therefore, the memory should be able to support N writes and 1 read (the cell to read out of the queue and sent out on the output link). In order to decrease the operating speed and complexity, the knockout switch, has more than one-output buffers at each output port. Figure 4-2 shows the schematic of a knockout switch and Figure 4-3 shows the details of a bus interface unit of a knockout switch.

Figure 4-2: Knockout switching element simulator

Figure 4-3: Knockout Bus Interface unit

Figure 4-2 shows a knockout switch with N input ports and N output ports, each operating at an equal speed. Fixed length ATM cells arrive on each input port in a regular time frame. The transfer medium is composed of N broadcast buses, one for each input port, each output port has access to cells arriving on all inputs, via a bus interface connected to each individual broadcast bus. As shown, each of the N input ports puts its cells on a separate broadcast bus, which is accessible to each of the output ports through a bus interface unit.

Because of this property the transfer medium is non-blocking and no cells are lost at the input ports of the knockout switch.

Cells may contend for a single output port in a bus interface of the Knockout switch.

A major advantage of the bus structure is that each bus is driven by only one input port, allowing a simple implementation and high transmission rate compared with a bus shared by multiple input ports. If the bus has to be shared between input ports, timing has to maintained between all inputs.

In a knockout switch, since each the buses may have cells, not all of which are destined to the same output port, the bus interface units should only select cells destined to its output port. Cell filters perform the role of selecting cells. These cell filters examine the address of each incoming cell. If the cell is destined for that specific output port, the cell is passed to the concentrator, otherwise the cell is discarded. Each bus interface unit has N cell filters connected to one of the N broadcast buses on one side and a concentrator on the other side.

At a bus interface, several cells may arrive simultaneously. In the worst case, all N cells are destined for a single output port. Thus, the bus interface requires cell buffers somewhere. If zero cell loss has to be guaranteed in the transfer phase to the cell buffer, the memory must write at N times the speed of each input port. In a knockout switch this operating speed is reduced, by an intelligent bus interface, which acts as a concentrator, with a non-zero cell loss probability. The next part of the bus interface is the concentrator from N inputs to L intermediate outputs ( $L \le N$ ). If K cells arrive simultaneously all destined for the same output port, then after passing through the concentrator, these K cells will arrive on inputs 1 to K of the concentrator, if  $K \le L$ . If K > L, then all L outputs of the concentrator will have cells, and K - L cells will be lost in the concentrator.

In [30], it is shown that L is not very sensitive to input load or the number of input ports, but is mainly influenced by the required cell loss probability. Hence, if L is selected to be 12, a cell loss probability of  $10^{-10}$  can be achieved for any load and any value of N. This cell loss probability is only for the concentration stage of the knockout switching element. To get the complete cell loss probability of the switching element, the cell loss probability of the output queue also needs to be taken into account. Of the N input lines into the concentrator, it randomly selects L of the input lines with cells and transmits the cells on in its first L output lines. If there are cells on less than L of the input lines of the concentrator all the cells get select.

A concentrator is constructed using one or more 2 by 2 contention switches to form a tournament, with N players (inputs) and L winners (outputs). An L output tournament is constructed by having L trees, with a 2 by 2 switch used to construct each node of the L trees. The first tree has N leaf nodes, the cell that makes it through the root of this tree is sent out on the concentrator's first output line. The N - 1 losing cells are passed as inputs to a second tree with N - 1 leaves, the winner on this tree forms the second output of the concentrator and so on. Hence for a concentrator with N inputs and L outputs, there are L sections of competition, one for each output. A cell entering the concentrator is given L opportunities to exit successfully through a concentrator output. A cell losing L times is knocked out of the competition and is discarded by the concentrator. However, in all cases, cells are only lost if more than L arrive in a single cell timeslot. The knockout switch gets its name from these knockout tournaments.

The next part of the bus interface is the cell buffer responsible for storing the cells successfully passed by the concentrator, but which cannot be served simultaneously by the single output port. Since the buffers are located at the output of each bus interface, the option

taken in the knockout switch for the cell buffer is the output queuing solution, the number of memory accesses during one cell time equals N+1 for a single ported memory.

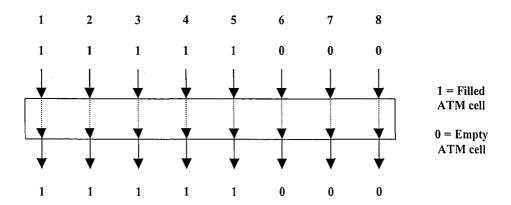

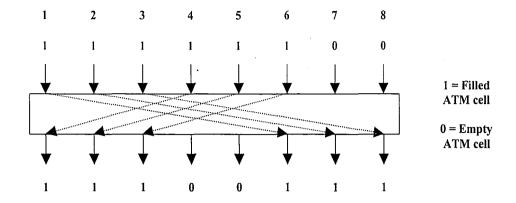

In the knockout switch this number is reduced to L+1, since the concentrator has reduced the number of inputs from N to L. The implementation of this output queue is realized by L separate queues each of which need only two memory accesses (i.e. one for reading and one for writing) per cell time, instead of L+1. However, in order to distribute the load over all queues and to obtain the same cell loss performance as an output queue, the L separate queues must be shared, and operate virtually as a single queue. To achieve this, a shifter stage is provided which guarantees that all buffers are equally loaded and optimally used, but also that the cell sequence is guaranteed. This shifter is required since without it all P "winning" cells from the concentrator would arrive at the left queues (if P < L).

Figure 4-4: Eight input line shifter unit, first timeslot

Figure 4-5: Eight input line shifter unit, second timeslot

The shifter provides a circular shift of the L inputs to the L outputs so that the L buffers are filled in acyclic way. Figure 4-4 and 4-5 shows the first and the second cell timeslots for an eight input line shifter. In the example, at the first cell time, five filled cells arrive at the first five inlets of the shifter. During this cell time the five cells are directly shifted through to the first five output lines. During the next cell time, six filled cells arrive, again at the first six inlets of the shifter. This is because the concentrator always concentrates on its first outputs. During the second cell time, the first cell will be shifted to output port six, the second to output port seven, etc. During the next cell time, the first cell will be shifted to the fourth buffer. With this technique, all cells buffers are filled uniformly.

A shifter can guarantee cell sequence, by cyclically reading out buffers. Formally, the shifter is described as follows. If  $S_i$  describes the number of positions the shifter has to shift to the right during cell time i, then

$$S_{i+1} = (S_i + K_i) \mod L$$

Where,  $K_i$  represents the number of filled cells arrived during cell time i and  $S_l$  is zero.

Total buffer memory of the output switching element = # concentrator outputs \* # output ports \* # cell locations

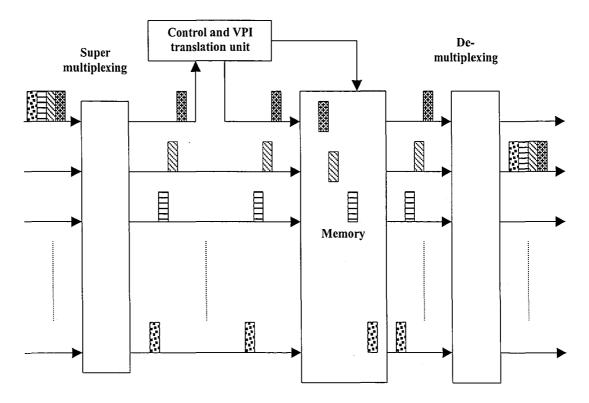

## 4.3 Central Queued Switching Element (Coprin Switching Element)

A Coprin switching element is an example of a central queued switching element and is described in detail in [33] [35]. The Coprin switch was originally designed for an experimental set-up called Prelude, to which data, voice and video sources were connected. It was designed and realized by the French Center National d'Etudes des Telecommunications (French CNET).

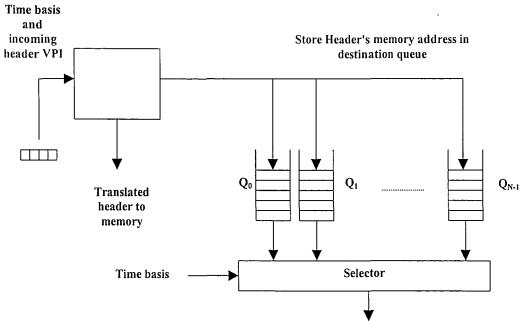

Like all other ATM switches, routing in the Coprin switching element is based on the header of the cell. Each ATM cell header contains a VPI, which is pre-set for each connection. The VPI is used in the Coprin switch to determine the physical output port; at the same time it is translated to an appropriate value for the outgoing link.

Figure 4-6: Coprin switching element