#### Lehigh University Lehigh Preserve

Theses and Dissertations

1992

## A modular approach to designing software for realtime actuator control for destructive testing

Poulomi Bharatkumar Damany Lehigh University

Follow this and additional works at: http://preserve.lehigh.edu/etd

#### **Recommended** Citation

Damany, Poulomi Bharatkumar, "A modular approach to designing software for real-time actuator control for destructive testing" (1992). *Theses and Dissertations*. Paper 62.

This Thesis is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Lehigh Preserve. For more information, please contact preserve@lehigh.edu.

# AUTHOR: Damany, Poulomi Bharatkumar

# TITLE:

A Modular Approach to Designing Software for Real-Time Actuator Conrtol For Destructive Testing

# DATE: May 31, 1992

# A MODULAR APPROACH TO DESIGNING SOFTWARE FOR REAL-TIME ACTUATOR CONTROL FOR DESTRUCTIVE TESTING

BY

## **POULOMI BHARATKUMAR DAMANY**

A Thesis

Presented to the Graduate Committee

of Lehigh University

in Candidacy for the Degree of

Master of Science

in

**Computer Science**

Lehigh University June 1992

### **CERTIFICATE OF APPROVAL**

This thesis is accepted and approved in partial fulfillment of the requirements for the degree of Master of Science.

April 29, 1992

Date

Advisor

Chairman of Department

### ACKNOWLEDGEMENTS

The author would like to express her gratitude to her advisor, Professor Stephen P. Pessiki, for taking a chance on a female, non-Civil Engineer teetering on the brink of financial insolvency. This work would not have been possible without his constant encouragement and guidance throughout this past year. I would be remiss if I did not thank Mark Kaczinski, research engineer at ATLSS, for all his help, insights and patience, CE graduate students John Abruzzo, Alain Nussbaumer and Guy Decorges for seeing that I did not kill myself or anyone else while on the test floor and Dave Scott for rescuing me everytime my program threatened to self-destruct.

Finally, my special thanks to the ATLSS - Engineering Research Center for funding me for my graduate studies and for introducing me to the world of hard hats, steel beams and lean, mean pounding machines - I hope the work I did when not trying to single-handedly destroy all the computers on the floor, will be of some use in the future.

## TABLE OF CONTENTS

|    | ABS  | TRACT                                | 1  |

|----|------|--------------------------------------|----|

|    |      |                                      |    |

| 1. | INTF | RODUCTION                            | 3  |

|    | 1.1  | Introduction                         | 3  |

|    | 1.2  | Objective                            | 5  |

|    | 1.3  | Outline of the Report                | 5  |

| 2. | DES  | CRIPTION OF A SERVO LOOP CONTROLLER  | 7  |

|    | 2.1  | Introduction                         | 7  |

|    | 2.2  | General Description of a Servo Loop  | 7  |

|    | 2.3  | The Vickers DCI Servo System         | 9  |

|    | 2.4  | The Vickers Servo Valve Operation    | 12 |

| 3. | GEN  | IERAL DESCRIPTION OF PROGRAM MODULES | 14 |

|    | 3.1  | Introduction                         | 14 |

|    | 3.2  | Program Structure                    | 14 |

|    | 3.3  | Installation                         | 15 |

|    | 3.4  | Initialization and Start-up          | 15 |

|    | 3.5  | Setup                                | 16 |

|    | 3.6  | Run <sup>°</sup>                     | 25 |

| 4. | PAR  | ALLEL INPUT-OUTPUT                   | 30 |

|    | 4.1  | Introduction                         | 30 |

iv

|    | 4.2  | The Burr-Brown PIO Board                                | 30 |

|----|------|---------------------------------------------------------|----|

| 5. | PRO  | GRAMMING GUIDE                                          | 32 |

|    | 5.1  | Introduction                                            | 32 |

|    | 5.2  | Program Organization                                    | 32 |

|    | 5.3  | Program Files                                           | 32 |

|    | 5.4  | Linking User Test-Control (run) Programs                | 33 |

|    |      | 5.4.1 Linking the setup module with the user program    | 33 |

|    |      | 5.4.2 Linking individual routines with the user program | 34 |

| 6. | INIT | IALIZATION                                              | 36 |

|    | 6.1  | Introduction                                            | 36 |

|    | 6.2  | Communication Port Initialization                       | 36 |

|    |      | 6.2.1 async_init()                                      | 36 |

|    |      | 6.2.2 async_mode()                                      | 38 |

|    |      | 6.2.3 async_clear_errors()                              | 40 |

|    |      | 6.2.4 async.h                                           | 41 |

|    | 6.3  | Parallel I/O Initialization                             | 41 |

|    |      | 6.3.1 pio_init()                                        | 41 |

|    |      | 6.3.2 pio_read()                                        | 43 |

|    |      | 6.3.3 pio_write()                                       | 44 |

| 7. | SET  | ŪP                                                      | 45 |

• 7

7.1Introduction45

| 7.2  | Scr_setup()                | 45 |

|------|----------------------------|----|

|      | 7.2.1 chk_parameter_type() | 48 |

|      | 7.2.2 dcl_boot()           | 49 |

|      | 7.2.3 read_saved_setup()   | 50 |

|      | 7.2.4 read_parameter()     | 50 |

|      | 7.2.6 read_eqn()           | 51 |

|      | 7.2.6 write_parameter()    | 52 |

|      | 7.2.7 write_eqn()          | 53 |

|      | 7.2.8 blocks()             | 54 |

| 7.3  | Limits()                   | 55 |

|      | 7.3.1 chk_tbk_limits()     | 57 |

|      | 7.3.2 switch_fdbks()       | 58 |

|      |                            |    |

| RUN  |                            | 59 |

| 8.1  | Introduction               | 59 |

| 8.2  | Run_dcl()                  | 59 |

|      | 8.2.1 check_chn_faults()   | 62 |

|      |                            |    |

| GRAF | PHICS                      | 63 |

| 9.1  | Introduction               | 63 |

| 9.2  | Initialize()               | 63 |

| 9.3  | Menu()                     | 63 |

|      | 9.3.1 box()                | 66 |

|      | 9.3.2 itemiz <i>e</i> ()   | 66 |

8.

9.

|      | 9.3.3 clear_window() | 67   |

|------|----------------------|------|

|      | 9.3.4 cursor()       | 67   |

| 8.3  | Printing             | 68   |

|      | 8.3.1 intprint()     | 68   |

|      | 8.3.2 numprint()     | * 69 |

|      | 8.3.3 longprint()    | 70   |

|      | 8.3.4 strprint()     | 70   |

|      |                      |      |

| FUT  | URE WORK             | 72   |

| 10.1 | Introduction         | 72   |

| 10.2 | Tasks Ahead          | 72   |

| REF  | ERENCES              | 73   |

| APPI | ENDIX A              | 74   |

| APPI | ENDIX B              | 83   |

| APPI | ENDIX C              | 91   |

10.

| VITA | 111 |

|------|-----|

|      |     |

ŧ

## LIST OF FIGURES

| FIGURE 1.1  | Schematic Diagram Of A Computer Controlled Test System | 4  |

|-------------|--------------------------------------------------------|----|

| FIGURE 2.1  | Schematic Diagram Of A Control System                  | 9  |

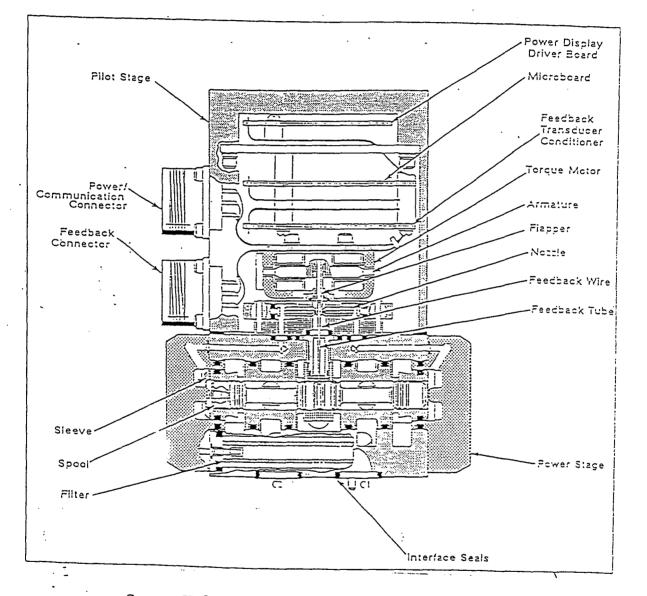

| FIGURE 2.2  | Servo Valve Construction                               | 11 |

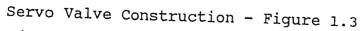

| FIGURE 2.3  | Controller Switches                                    | 12 |

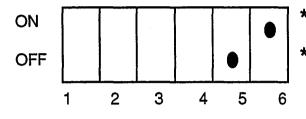

| FIGURE 3.1  | Main Menu                                              | 14 |

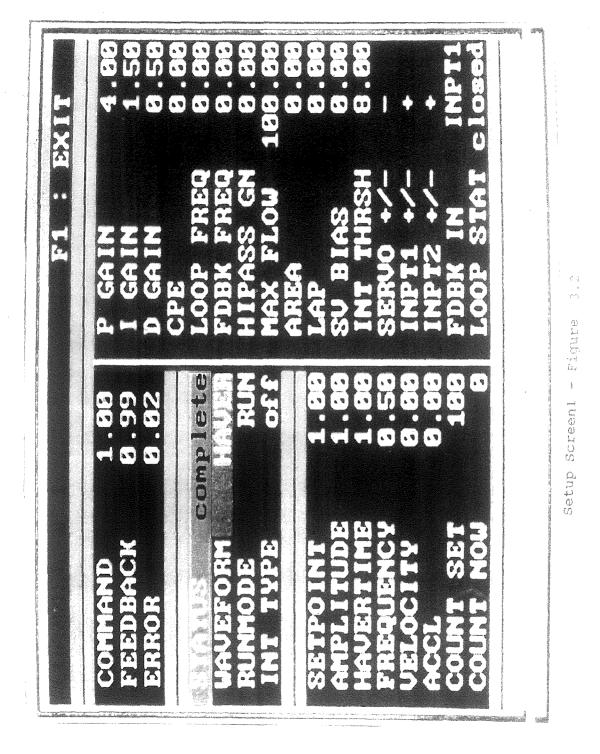

| FIGURE 3.2  | Setup Screen1                                          | 18 |

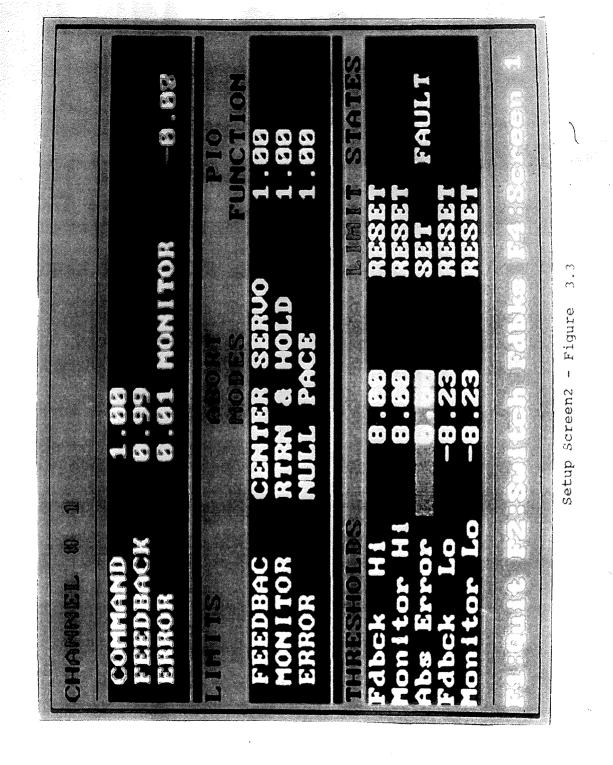

| FIGURE 3.3  | Setup Screen2                                          | 19 |

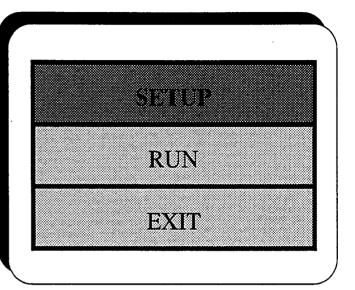

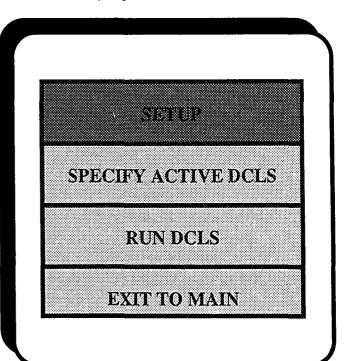

| FIĠURE 3.4  | Run Menu                                               | 25 |

| FIGURE 3.5  | Run Screen1                                            | 28 |

| FIGURE 3.6  | Run Screen2                                            | 29 |

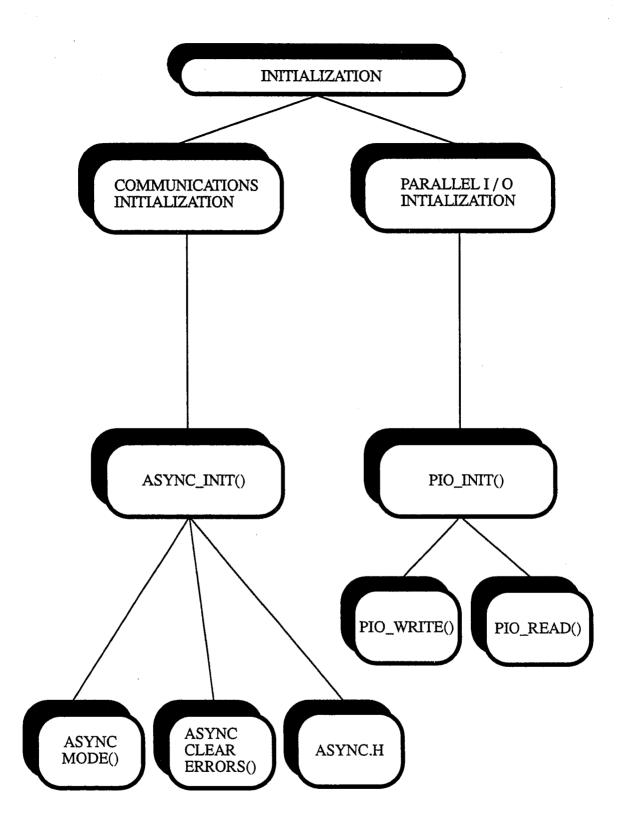

| FIGURE 6.1  | Initialization Module                                  | 37 |

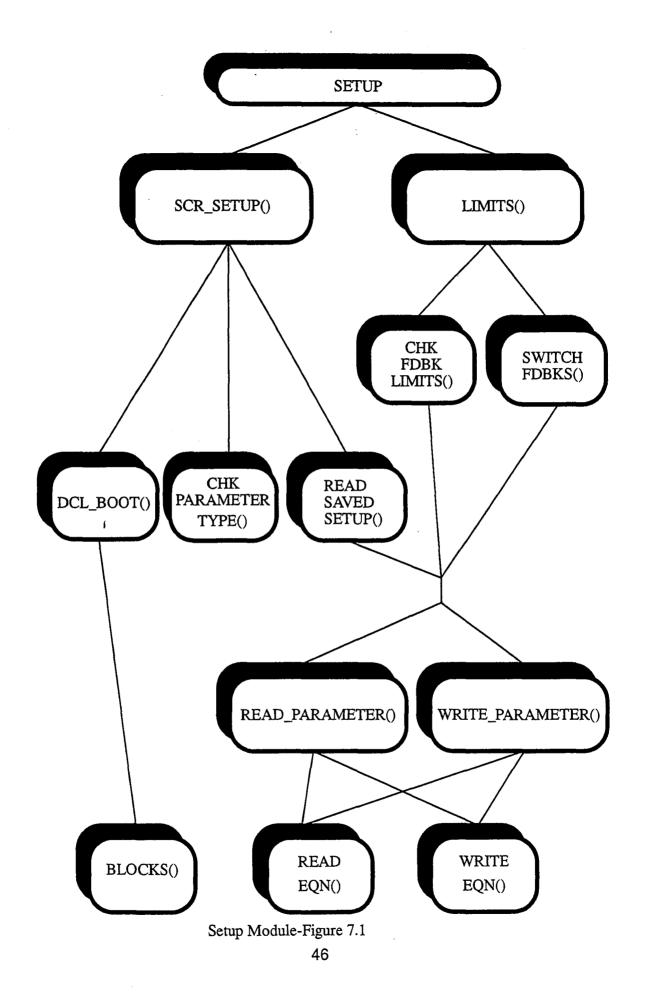

| FIGURE 7.1  | Setup Module                                           | 46 |

| FIGURE 7.3. | Tuned Signal                                           | 52 |

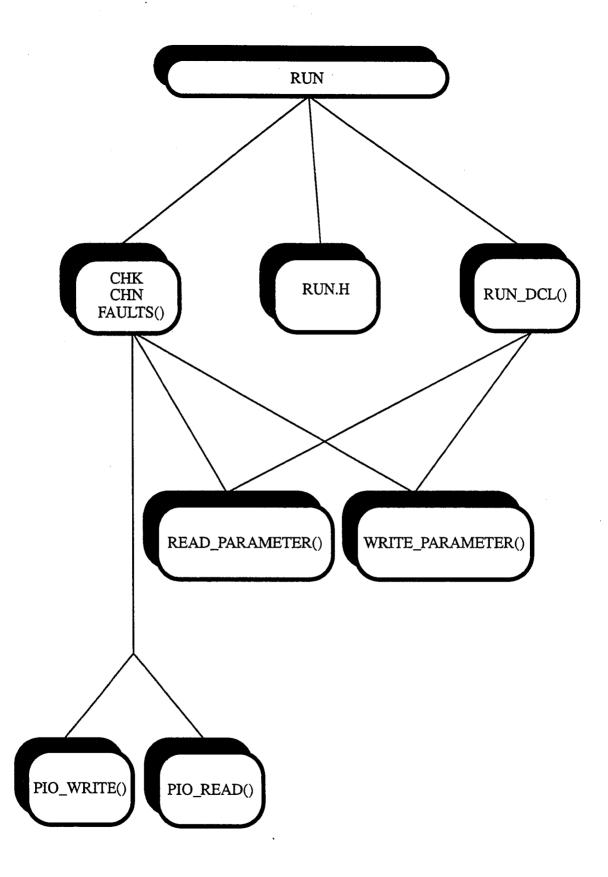

| FIGURE 8.1  | Run Module                                             | 60 |

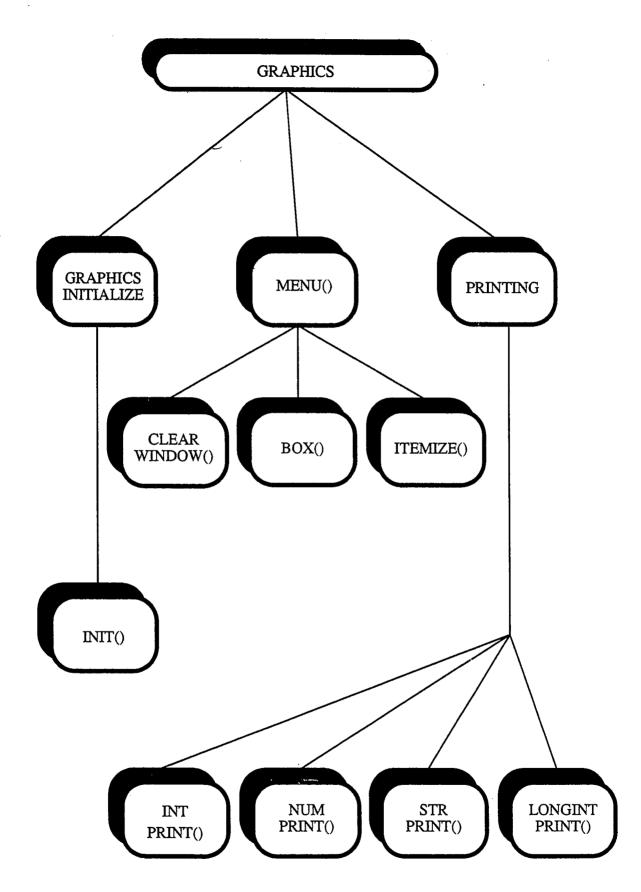

| FIGURE 9.1  | Graphics Module                                        | 64 |

. \

#### ABSTRACT

The laboratories for the Center for Advanced Technology for Large Structural Systems (ATLSS) conduct a wide range of experiments (fatigue, quasistatic and dynamic tests) on structures, which have different requirements for actuator control, data acquisition, and data display. Project D2- Computer Controlled and Integrated Experimentation involves developmental work to expand the experimental testing capabilities of ATLSS.

In a computer-controlled test, all aspects of actuator control and data acquisition are controlled by commands issued from a single test computer, with information about the current system state being displayed to the operator. The purpose of the actuator control software is to generate an interface between the Vickers X8700 Digital Closed Loop (DCL) servo controller and the end-user so that the user can easily communicate with the servo controller and send force or motion control parameters, while having information about the actuator on the monitor.

At present, ATLSS is using software written by Test Systems & Simulation, Inc. (TS&S) for actuator control. The software works well in isolation for fatigue testing but imposes limitations on other tests. This is because the software does not communicate easily with other test hardware/software. Actuator control is the primary task of the TS&S software while the actual test is viewed as a sub-task.

The efforts of this project have been towards the development of a software package for actuator control, which can be called within the user-specific test control program as a sub-task. This allows the user to modify the test control program while leaving the basic actuator communication shell intact. In addition to this actuator control software, one user-specific test control program for constant amplitude fatigue testing was also developed.

The software is written in Borland Turbo C to run under MS-DOS version 3.2 or 3.3 on an IBM PC AT with a clock speed of at least 8 MHz. It requires the following minimum hardware configuration:

| 640K Memory       | 20 MB Hard Drive          |

|-------------------|---------------------------|

| EGA Color Monitor | EGA Graphics Adaptor Card |

| Math Co-processor |                           |

The memory address map used by the software:

Interrupt vector table - 00000H BIOS data area - 00400H

Video buffer - B8000H Burr-Brown I/O-D0000H, CD000H, C0000H

The I/O port addresses used:

Serial I/O to controllers - 3F8H, 2F8H, 3E8H, 2E8H (any one of 4 COM ports).

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Introduction

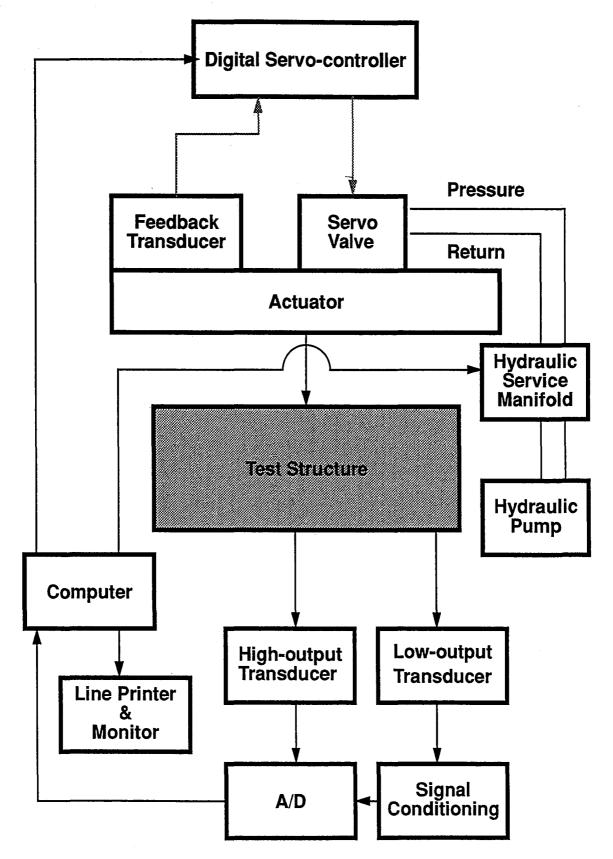

To obtain true "computer-controlled testing" it is necessary to integrate the separate activities of actuator control and data acquisition, as well as other aspects of a test such as data manipulation and display. Figure 1.1 is a schematic diagram of such an integrated test system. In this system, all aspects of actuator control and data acquisition are controlled by the commands issued by the test computer.

It is not essential to have just one computer as shown in Figure 1.1. What is essential is that the information about actuator control and data acquisition are available in some common environment so that their activities can be coordinated, and so that information about the current state of a test are available for manipulation and for presentation to the test operator. This is a key requirement.

At present, ATLSS is using software written by Test Systems & Simulation, Inc. (TS&S) to achieve control of the hydraulic actuators. The TS&S software works well for actuator control in constant amplitude fatigue testing. In theory, the desired command signal, consisting of an amplitude (force or displacement) and frequency, is issued by the computer to the actuator controller, and the computer is then available to perform other tasks. Application of the TS&S software to variable amplitude fatigue testing is somewhat more complicated because of the need to constantly update the command signal. Nonetheless, the software has been used to control variable amplitude fatigue tests.

Use of the TS&S software has imposed severe limitations on tests other than fatigue tests. This is because the software does not easily communicate with other test hardware/software (such as data acquisition hardware/software). Rather than have actuator control as just one task in a computer-controlled test, use of the TS&S software forces all other tasks (such as data acquisition) to be sub-tasks of the activity of actuator control.

The forgoing is not intended to suggest that combined hardware/software test packages are in all aspects undesirable. For example, as noted above, the TS&S software works well for constant amplitude fatigue tests, particularly if data acquisition is not necessary and the test can be monitored with a separate standalone data acquisition unit. In addition, there may be many tests performed in

Schematic Diagram Of A Computer Controlled Test System - Figure 1.1

which integration of actuator control and data acquisition is not needed. It can be argued, however, that the sole reliance on packaged test systems (hardware and software) which teat only one component of a test (actuator control or data acquisition) impedes efforts to obtain true integration of a test. Communication between stand-alone software/hardware packages has proved to be an extremely difficult task.

#### 1.2 Objective

The work described in this report was performed as part of the ATLSS project D2 - Computer Controlled and Integrated Experimentation. The objective of the project was the development of a modular software package for actuator control which could be called within the user-specific test control program as a sub-task. This actuator control software would allow the user to modify the test control program while leaving the basic actuator communication shell intact. The modularity of the software would allow inclusion of needed modules only thereby significantly reducing memory requirements and improving overall speed of execution.

#### **1.3** Outline Of The Report

This report combines two manuals- one intended as a users' guide and the other as a programmers' guide. Chapter 2 gives a brief description of a servo feedback controller and the issues involved in using it for position or force control. Chapters 3 and 4 describe the basic structure of the software package, along with a description of all the user display screens and how to operate in them. Chapters 5 through 9 are a programmers' guide to the software and are intended as documentation and reference for future revisors of the code. The following is a brief listing of the contents of each chapter:

5

Chapter 2 **DESCRIPTION OF A SERVO LOOP CONTROLLER:** This chapter describes a Digital Closed Loop Controller and its various elements.

Chapter 3 **GENERAL DESCRIPTION OF PROGRAM MODULES:** This chapter is intended to give an overview of the software, showing the relationships between the program modules. The modules are described in order of appearance in the system menus.

5

Chapter 4 **PARALLEL INPUT-OUTPUT**: This chapter describes the Parallel I/O option that allows the user to control external hardware such as panel switches, service manifolds, etc. through computer control of parallel I/O. This feature is most useful in case of an error condition in the control loop that requires the automatic shut down of hydraulic pressure, display warning lights, etc.

Chapter 5 **PROGRAMMING GUIDE**: The next four chapters describe in detail, each module and the lower level routines it calls. The description format is topdown, starting with the main module and going down to the component routines and the functions they call.

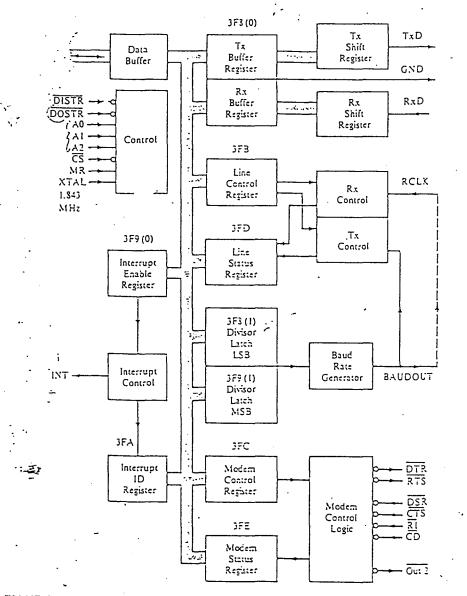

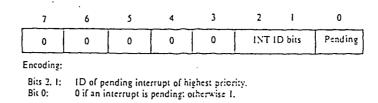

Chapter 6 **INITIALIZATION:** This chapter describes the routines executed during start-up. Two separate entities need to be initialized - the serial communication port (8250 UART chip-Appendix A) and the parallel input/output board (Burr-Brown PIO board-Appendix B).

Chapter 7 **SETUP:** This chapter describes the routines which interface between the controller parameters and the user display (screens 1 & 2). They read and write the controller parameters, convert between engineering units and controller counts and display the information onto the screens for the user's benefit.

Chapter 8 **RUN:** In addition to the general purpose software for actuator control, a user-specific program for constant amplitude fatigue testing was also written. This user-specific program is described in this chapter.

Chapter 9 **GRAPHICS:** This chapter describes the routines that have to do with drawing menus, borders and boxes, changing the background and foreground colors, writing to specific portions of the screens and all other screen entity manipulations.

Appendix A **INTEL 8051 UART HARDWARE DESCRIPTION:** This is a pullout from the INTEL Peripheral Components manual and presents a complete description of the hardware and programming features of a NS16450 type Asynchronous Serial Communications controller through which the computer can "talk" to the servo controller on the valve.

Appendix B **PROGRAMMING THE BURR-BROWN PIO BOARD:** This deals with the programming of the PC20001C parallel I/O board in more detail and also expands on the memory addressing scheme of the board.

6

Appendix C **CONTROLLER PARAMETERS:** This is a listing of the controller parameters along with some information about their engineering units-counts conversion equations and scaling factors, the registers assigned to them and the amount of memory (in bytes) they occupy.

#### **CHAPTER 2**

#### DESCRIPTION OF A SERVO LOOP CONTROLLER

#### 2.1 Introduction

This chapter provides a general description of the operation of closed-loop servo hydraulic control systems such as those used for structural testing in the ATLSS laboratories. This chapter also presents some of the details of the Vickers Xpert DCL servo system, which is the particular system in wide use in the ATLSS laboratories.

#### 2.2 General Description of a Servo Loop:

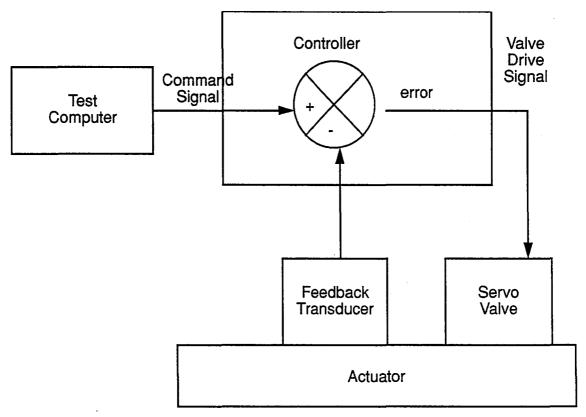

A servo system is a feedback system in which the output or some function of the output is fed back for comparison with the input and their difference (error) is used to control a source of power<sup>1</sup>. In the ATLSS laboratories, such servo systems are used to control the displacements or forces applied by the hydraulic actuators used in structural tests.

Figure 2.1 is a schematic diagram of a generic control system for the operation of a hydraulic actuator. The main components of this system include the test computer, controller, actuator and feedback transducer. Briefly, the operation of the system is as follows. The test computer issues a command to the controller. The command is the desired force or displacement which is to be implemented by the actuator. The controller also receives from the feedback transducer. Also input to the controller is a feedback signal which is an indication of the current force or displacement applied to the structure by the actuator. The controller computes an error signal which is the difference between the command and feedback signals. The error signal gives rise to a drive signal to the servovalve. The servovalve is a mechanical device used to adjust the flow of oil in to the actuator. The servovalve adjusts this flow of oil in response to the drive signal, porting oil to the actuator in a manner that causes the error signal to reduce to zero, thus implementing the commanded force or displacement.

One end of the hydraulic actuator is normally attached to the test structure, and the other end reacts against the reaction wall, strong floor, or other similar reaction point. The hydraulic actuators are usually operated in one of two modes: load control or displacement control. In the case of load control, the command signal is the desired force, and the feedback signal is the force currently applied by the actuator. The feedback transducer in this case is a load cell. In displacement control, the command signal is the desired displacement, and the feedback signal is the current displacement of the actuator, i.e. how far the piston is currently extended. The feedback transducer in this case is a displacement transducer. This displacement transducer is often mounted internally in the body of the actuator, but may also be external to the actuator. Other type of control are also possible, such as acceleration control or strain control. Finally, the actuators are operated in a closed loop manner, i.e. the valve command is sent automatically without intervention by the test operator.

r.,

#### 2.3 The Vickers DCL Servo System

The rest of this chapter is condensed from the Vickers Xpert DCL User's Manual <sup>2</sup> and is included here for completeness. The Vickers Xpert DCL system is a force and motion control system. It consists of a display board, a microboard containing the software for bi-directional serial communication between the computer and the Controller, a digital closed loop servo valve and a feedback transducer. The servo valve consists of a polarized electrical servo motor and two stages of hydraulic power applications - a pilot flapper/nozzle arrangement and a

Schematic DIagram of a Control System - Figure 2.1

power sliding spool arrangement (See Figure 2.2). The servo motor converts low level electrical input signals from an amplifier to a mechanical force and motion. When the command signal is applied, the motor is activated and the servo valve provides flow to the actuator proportional to the electrical current applied. The direction of the flow is dependant on the polarity of the DC command signal. Flow from the valve controls actuator movement. Actuator movement is measured by the feedback transducer. The feedback signal from the transducer is compared with the command signal, the difference amplified and a new electrical current sent to the servo valve. The actuator will continue to move until the actuator position approaches that called for by the command.

#### **Controller:**

The Vickers controller contains the power display drive board to control the valve driver and the display lights and address switches, the microboard holding the on-board software and the feedback transducer conditioner which converts the signal from the feedback sensor to a digital signal for computer access.

#### Servo Motor:

The Vickers motor consists of two coils surrounding an armature. Lead wires from the coils are connected to the power display drive board. A flexible tube supports the armature and also acts as a fluid seal between the hydraulic and electronic areas of the valve.

#### **Pilot Stage:**

Attached at the center of the servo motor armature is a flapper with a nozzle on each side, that extends down inside the flexible tube. Flapper movement between the nozzles creates pressure variations, which act on the ends of the power stage spool. Attached to the flapper is a feedback spring which engages into a hole at the center of the spool. When the spool moves, the feedback spring senses the spool movement and a force proportional to this movement is fed back to the flapper.

#### **Power Stage:**

Actual flow in the valve is controlled by a four-way spool that slides within a sleeve. The porting system is arranged so that the spool movement in one direction opens fluid supply to control port #1 and opens port #2 to return. Movement in the opposite direction opens fluid supply to port #2 and opens port #1 to return.

#### **Address Switches:**

A given application can contain up to 16 of the above described DCL Controllers on one serial port. To distinguish one from the other, each is assigned an address. This is done by setting the address switches (1-4) on each individual valve. Another setting to be made is that of the baud rate which is the speed with which communication takes place between the valve and the computer. Switches 5 and 6 on each valve have to be set to the desired rate. For example, for a baud rate of 38400 the setting is as shown below in Figure 2.3:

\*(Power Indicator Light-Green)

\*(Communicating Indicator Light-Yellow)

**Controller Switches-Figure 2.3**

#### 2.4 The Vickers Servo Valve Operation

- 1. An electrical input current is applied to the servo motor.

- 2. The coils in the motor magnetize the armature.

- 3. The armature moves clockwise or counterclockwise, depending on the polarity of the current applied.

- 4 This causes the flapper to move between the nozzles creating a change in fluid pressure at the ends of the power stage spool.

- 5. As a result of the pressure change, the spool moves away from the high pressure end of the valve.

- 6. Depending on the direction of spool movement, the pressurized fluid will then flow from either port.

- 7. As the spool moves, it causes the feedback spring to deflect. This creates a force on the pilot stage flapper opposing the motion caused by the armature.

- 8. When the force from the feedback spring equals the magnetic force of the armature, the flapper returns to center between the nozzles.

- 9. The power stage spool stops moving and remains in that position until the input current changes to a new level.

#### **CHAPTER 3**

#### **GENERAL DESCRIPTION OF PROGRAM MODULES**

#### 3.1 Introduction

This chapter is intended to give an overview of the software, showing the relationships between the program modules. The modules are described in order of appearance in the system menus.

#### 3.2 **Program Structure**

The software is a menudriven collection of modules with

Main Menu- Figure 3.1

15

each module performing one aspect of the total controller communication task. The three main modules are *Initialization, Setup and Run.* The Initialization and Setup are constant, general routines which can be used without any changes to establish communication with any controller. The Initialization module is executed as soon as the program starts up and is not a user choice from the main menu (see Figure 3.1). The Run program is intended to be a user test-control program which can use the other two routines for controller communication while running the test at a higher level. The Run program described here is a sample constant-amplitude fatigue test-control program.

The Initialization routine does exactly that - it establishes the communication channel, resets the parallel I/O logic board (for more details see Appendix B) and reads in the current values of the controller parameters. The Setup module is similar to the TS&S Multi-scan program in that it is used to facilitate the storage of controller parameters and to manipulate the controller during setup. Data about the controller can also be saved from this module. The Run module is a sample fatigue test control program with 16-channel configuring capability. The controllers can be run as a group from this routine while still maintaining individual starting/stopping capabilities.

#### 3.3 Installation

To install the package on the hard drive of the host computer, first create a new directory of any name. Copy the following files to the directory - note that all the files must be in the same directory - do not attempt to divide the program files among sub-directories.

The header files are:

| 1. Async.h                                | 2. Run.h 3. Params.h        |  |  |

|-------------------------------------------|-----------------------------|--|--|

| The data files are:                       |                             |  |  |

| 1. Chn11.lst                              | 3. Chn21.lst 5. Pioasgn.wgd |  |  |

| 2. Chn12.Ist                              | 4. Chn22.lst                |  |  |

| The object files are:                     |                             |  |  |

| 1. Menu.obj                               | 3. Run.obj 5. Async.obj     |  |  |

| 2. Setup.obj                              | 4. Pio.obj                  |  |  |

| The graphics drivers are: (TURBO C files) |                             |  |  |

1. EGAVGA.BGI 2. EGA.BGI 3. BGIOBJ.BGI

The executable files are:

1. DCL.PRJ 2. DCL.EXE

#### 3.4 Initialization And Start-up

To enter the system from DOS, type: DCL <ENTER>

The initialization routine is then activated which sets the following parameters as

| ENTRY    | DATA FILE   | VALUE                |

|----------|-------------|----------------------|

| Channels | Params.h    | 0-16                 |

| PIO      | Pioasgn.wgd | BOI (parallel ports) |

15

| Parallel Interface | Params.h     | CD00 (Hex address) |

|--------------------|--------------|--------------------|

| Serial Port        | Async.h      | COM1               |

| Serial Port Type   | Pioasgn.wgd  | l (input)          |

| Baud Rate          | User config. | (9600,19200,38400) |

At present, these default values are stored in data files as listed above and cannot be viewed by the user while in the program. The values can be changed by editing these data files from DOS.

The main menu will then appear and the user can select the module to execute from here. If the user choice is *setup*, control is transferred to the setup module (controlling routine scr\_setup - see Section 7.2) and if the user selects *run dcls*, the run module is stepped into (controlling routine run\_dcl - see Section 8.2).

#### 3.5 Setup

This is a User Interface program that provides the capability to communicate with the controller. The main use of this routine is to setup and tune a channel. It allows communication with only one channel at a time. This module reads and displays all the controller user-configurable and status-only parameters on two screens (toggle between screens using F4). The user is allowed to select the channel to be displayed at the start of the routine (it is assumed that each channel has been assigned with a controller address and the identification switches have been set to the corresponding address). Channels beyond the selected range will cause the routine to routine to quit and go back to the main menu.

When a valid channel is selected, the screen will show all the values as currently present in the controller for that channel. If the channel has been previously backed up, a file will be present on the hard drive that can be used to recall the data and send it to the controller. When first communicating with the controller, to ensure no erroneous setup parameters are present, it is a good idea to *re-boot* the controller.

All user configurable values can be edited by merely moving the field indicator (using the 4 arrow keys-up, down, right & left), inserting the numeric

value or letter (for non-numerical parameters, the first letter of the desired option) and confirming with the **ENTER** key. The new value is communicated to the controller *as soon as* the value is set, that is, <u>the controller will be immediately</u> <u>affected by the changes that the user makes</u>.

The setup screens also have Function key (F1-F10) definitions displayed at the bottom of each screen. These are used to call initialization routines, recover saved parameter values and other desirable activities.

Screen1 is associated with most of the numerical parameters of the controller (See Figure 3.2). For example, the Proportional Gain may be modified from Screen 1 to improve performance. If the channel is sluggish, one can increase the P GAIN from this screen, if it is unstable, decrease P GAIN. Polarities of the servo loop or the feedback signal can be reversed from here for proper loop closure. Again, to change a value, the user must press the ENTER key after entering the value and before moving onto another menu selection. Alt-F4 from this screen will operate the PIO function. Screen1 toggles to screen2 when F4 is pressed.

Screen2 displays controller limits and abort modes (see Figure 3.3). These are three separate controller monitored limit conditions: the signals that can have limits assigned are the feedback signal, the monitor signal and the control loop error signal. These signals can have thresholds assigned (in the engineering units of the signal being monitored) to set the boundaries for the feedback signal, the monitor signal and the error window. The status of these limit boundaries is also shown (SET if limit exceeded). The user can also assign PIO modules to a limit here by entering a PIO function number in the appropriate column. The PIO functions are used to control hydraulic power units, service manifolds or blocking manifolds. If a PIO function entry is "0" the function will be ignored.

17

|           |              | F 1 : }   | SH I T |

|-----------|--------------|-----------|--------|

| COMMAND   | 1.88         | PGAIN     | 4.00   |

| FEEDBACK  | 0.99         | IGAIN     | 1.56   |

| ERROR     | 8.62         | DGAIN     | 6.50   |

|           |              | CPE       | ย.ยอ   |

| STATUS    |              | LOOP FREQ | 0.00   |

| WAVEFORM  | ROUR         | FDBK FREQ | 0.00   |

| RUNMODE   | RUN          | HIPASS GN | 0.00   |

| INT TYPE  | off          | MAX FLOW  | 100.00 |

|           |              | AREA      | 0.00   |

| SETPOINT  | 1.00         | LAP       | 0.00   |

| AMPLITUDE | 1.00         | SV BIAS   | 0.00   |

| HAVERTIME | 1.00         | INT THRSH | 8.00   |

| FREQUENCY | 0.50         | SERVO +/- |        |

| VELOCITY  | 0.00         | INPT1 +/- | ◆      |

| ACCL      | 0.00         | INPT2 +/- | •      |

| COUNT SET | <b>` 100</b> | FDBK IN   | INPT1  |

| COUNT NOW | 8            | LOOP STAT | closed |

|                                                                                                  | 5 6 6<br>5 6 6<br>7                      | FaultT                                                        | F4:Screen 1  |

|--------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------------------------|--------------|

| MONLTOR                                                                                          | <b>←</b> ┥ <b>←</b> ┥ <b>←</b> ┥         | RESET<br>RESET<br>SET<br>RESET<br>RESET                       | Fdbks F4:Se  |

| 9<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | CENTER SERUO<br>RTRN & HOLD<br>NULL PACE |                                                               | F2:Suitch Fd |

| ( OMMAND<br>FEEDBACK<br>ERROR                                                                    | FEEDBAC<br>MONITOR<br>ERROR              | Fdbck Hi<br>Monitor Hi<br>Abs Error<br>Fdbck Lo<br>Monitor Lo | F1:Quit F2:  |

The following parameters are displayed on Screen1:

| STATUS ONLY:                                |                                                                                                                                                                                                                                 |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Channel #:                                  | This is the current channel that is being addressed.                                                                                                                                                                            |

| Command:                                    | This is the current output of the internal signal generator for the desired force or motion (The controller does not receive the entire force/motion command; rather it is sent small incremental steps - this is the command). |

| Feedback:                                   | This is the current output from the controlling transducer (force/motion- See parameter Fdbk In). It is the actual load/position of the actuator.                                                                               |

| Error:                                      | This is the difference between command and feedback.                                                                                                                                                                            |

| Waveform Status:                            | This displays the status of the internal waveform generator (either in process or complete).                                                                                                                                    |

| Counter Now:                                | This displays the current number of cycles (on Sines).                                                                                                                                                                          |

| Fdbk In:                                    | Displays the active (controlling) feedback (1 or 2).                                                                                                                                                                            |

| USER CONFIGURABLE:                          |                                                                                                                                                                                                                                 |

| Waveform Type:<br>(Non-numerical S/R/H)     | The controller has 3 options for its internal waveform generator: (S)ine, (R)amp and (H)aversine.                                                                                                                               |

| <b>Run Mode:</b><br>(Non-numerical R/A/Z/H) | There are 4 options: Run, Abort, Zero (return) & Hold.                                                                                                                                                                          |

| Integrator Type:<br>(Non-numerical S/R/H/O) | This is the integrating function to the feedback loop. There are 4 options:                                                                                                                                                     |

| (S)ines (On):                               | This continuously sums the integrator term of the loop into the loop output).                                                                                                                                                   |

(R)amp (Threshold): This zeroes the integrator term in the loop output if error is greater than the integrator threshold.

(H)old: Sends a constant value for the integrator to the loop output.

No integral action - zero for the integrator term to the loop.

This is the endpoint (Haver/Ramp) or the mean value (Sine) of the waveform.

This is the desired amplitude for a Sine waveform.

For a Haversine, this is the desired length of time in seconds; for a Sine it is the period.

This is the desired frequency of the Sine waveform in Hz.

The desired velocity to set the ramp rate for a Ramp.

The desired acceleration for a Ramp waveform.

The proportional loop gain.

The integral loop gain.

The derivative loop gain.

The feed-forward compensation to adjust the phase shift between command and feedback at a given frequency.

Desired loop output frequency (3db) in Hertz for the output low-pass filter (zero-filter off).

Desired feedback cutoff frequency (3db) in Hertz for the output low-pass filter (zero-filter off).

(numerical)

Set Point:

(O)ff :

Amplitude: (numerical)

Havertime: (numerical)

Frequency: (numerical)

Velocity: (numerical)

Acceleration: (numerical)

**P Gain:** (numerical)

I Gain: (numerical)

**D Gain:** (numerical)

**CPE:** (numerical)

Loop Freq: (numerical)

Fdbk Freq: (numerical) Hipass Gn: (numerical)

Return Time: (numerical)

Lap: (numerical)

SV Bias: (numerical)

Max Flow: (numerical)

Int Thresh: (numerical) Desired feedback cutoff frequency (3db) in Hertz for the output high-pass filter (zero-filter off).

Haversine time for a profile return.

The servo valve lap compensation value.

The servo valve electrical null bias value.

The maximum allowable flow limit in percent (0-100)

The threshold value in controller counts of the integrator function to the loop output.

Fdbk1 +/-: (non-numerical +/-)

Sets the polarity of feedback 1.

| Fdbk2 +/-:          | Sets the polarity of feedback 2. |

|---------------------|----------------------------------|

| (non-numerical +/-) |                                  |

Servo +/-: Sets the servo valve polarity.

(nonnumerical+/-)

Loop Status: (non-numerical O/C) Set to open or close loop.

At the bottom of screen1 are the Function key assignments:

- **F1:** Exit from the screen return to main menu.

- F2: Recall previously saved backup of controller parameters.

- **F3:** Save current setup to disk.

- F4: Toggle to Screen 2.

- F5: Boot controller- clear present parameter values and reset limits.

The following parameters are displayed on Screen2: (F4 to toggle between

screens1 & 2)

#### STATUS ONLY:

**Command:** Same as screen 1.

Feedback: Same as screen 1.

**Error:** Same as screen 1. **Monitor:** The non-controlling feedback value.

At the bottom of screen2 are the Function key assignments:

**F1:** Exit from screen 2 - return to main menu.

F2: Switch controlling feedbacks. Only works if the controller is not in process.

**F4:** Toggle to screen 1.

#### USER CONFIGURABLE:

Abort Modes: (Non-numerical O/N/R/S)

Off:

Null Pace:

**Return & Hold:**

There are 3 definable controller monitored limit conditions for the user; the signals that can have limit actions assigned are the *feedback*, the *monitor* and the *control loop error* signals. Four independent limit actions can be set for each of these.<sup>3</sup>

Limits are checked and fault displayed but not acted on.

The internal command generator is turned off while the fault exists. Thus the command value at the time of the fault is held until the feedback falls back within set limits. It then **resumes** command sequence unlike the other abort modes. (useful when running Sines between defined limits. **Not** available with monitor/noncontrolling feedback).

When a fault is detected, the controller generates a haversine to the previous setpoint with a havertime equal to the Return time (on screen 1).

Center Servo: When a fault is detected, the controller immediately centers the servo valve. The servo valve mechanical null should be adjusted so that the actuator does not drift. (Not available with monitor/non-controlling feedback).

Parallel I/O: (numerical 1-32) PIO can be defined for each of the three signals (feedback, monitor and error).These are used to allow the controller to operate the parallel functions when a limit threshold has been exceeded. (see Appendix B for PIO definitions). The PIO functions can be used to control hydraulic power units, service manifolds, panel lights, etc. It this entry is less than or equal to zero or greater than 32, it will be ignored.

The feedback and monitor inputs each have limit threshold window defined by a Hi and Lo value. Abort action is taken if the signal strays outside this window. The error signal only has an absolute threshold (or a Hi value), the crossing of which leads to an abort action specified in the abort mode.

Indicates the state of the corresponding threshold for the 3 signals- can be manually SET and RESET. These are automatically updated to reflect the true state of each of the five limits.

#### 3.6 Run

The purpose of this routine is to demonstrate the method in which user test-specific programs will link with the general controller setup and initialization routines and be able to call the screens and routines of the former from within the test program. It is also a valid fatigue test control program. The basic idea was to

free the user from the low-level I/ O and communication protocols (which are repetitive for every test) by providing easy-to-use commands and means for accessing all parameters. This allows the user to spend time on designing the test sequence instead of having to write the code communicate with the to controllers. The communication mechanism is thus subordinate to the test (Run) program. This module is a constant-amplitude fatigue test control program.

A constant-amplitude

#### Run Menu- Figure 3.4

#### Thresholds: (numerical)

Threshold Status: (Non-numerical S/R) fatigue test involves running 1 or more actuators as a group in continuous sinewave mode with either force or displacement as the controlling feedback. The number of sine waves performed by each actuator (counts) have to be constantly monitored and it is desirable to be able to start and stop each actuator individually without affecting the others in the group. The routine first pops up a menu (see Figure 3.4) with four choices: Setup, Specify, Run andExit. The following is a brief description of each.

#### Setup Individual DCLS:

This allows access to individual channels (setup screen1)

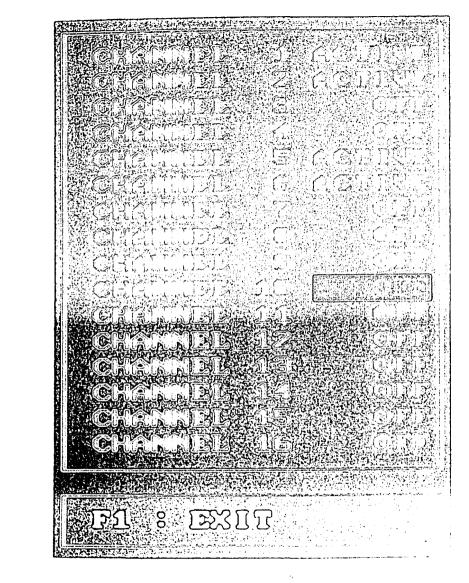

### Specify Active DCLS:

This pops another menu shown in Figure 3.5, which allows the user to configure controllers for groups. Up to 16 channels can be specified as (A)CTIVE or (O)FF.

The function key defined is:

F1: Exit to the main RUN menu.

### Run DCLS:

Starts the test. This displays another screen with the following information for each active channel: (See Figure 3.6)

| Channel #:   | Number of the active channel.                           |

|--------------|---------------------------------------------------------|

| Count:       | Total number of sines sent to the controller-constantly |

|              | updated.                                                |

| Limit Modes: | Abort modes for feedback, monitor and error (setup      |

|              | screen 2)                                               |

| PIO:         | The PIO function for the 3 signals (setup screen 2).    |

The function keys defined are:

F1: Exit to the main RUN menu.

Counts will be backed up in a file COUNT. IFT on the hard drive.

- F2: Modify counts (only if controllers are not running).

- F3: Start/Stop the test-all actuators.

Exit:

1

Return to the main menu.

|                                         | 12. 12<br>12. 12 | 1 <u>4.</u><br>10. (0) | <u> </u>                                                                                                                                                                                                                   |                                                        |    | 64, 64, 6<br>194, 64, 6<br>194, 64, 6<br>194, |        |

|-----------------------------------------|------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| الم |                  |                        | हत हत<br>जुने उटा रहे                                                                                                                                                                                                      | - <u>5</u> (5) (5)                                     |    | e<br>A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                         | 1 11 11<br>16 11 |                        | $ \begin{array}{c c} \hline (c_1) & [c_2] & [c_3] \\ \hline \hline (c_1) & [c_2] & [c_3] \\ \hline \hline \hline (c_1) & [c_3] & [c_3] \\ \hline \hline \hline (c_1) & [c_3] & [c_3] \\ \hline \hline \hline \end{array} $ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | δι | 12 12 1<br>1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 : EX |

Run Screenl - Figure 3.5

| Edb (ENTER SERVO B) 2 B Edd (C)                                                                                                                                                                                  | • ENTER SERVO 8              RTRN 8 HOLD       1       mov             RTRN 8 HOLD       1       mov              NULL PACE       1       mov              0FF       8       6       6       8       f.db       0F       0F         0FF       8       mov       0FF       enr       0FF       enr       0FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>ENTER SERVO 8</li> <li>ETRN &amp; HOLD</li> <l< th=""><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></l<></ul> |  |             |                 |   |             |                 |     |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|-----------------|---|-------------|-----------------|-----|------|

| RTKN & HOLD     1     no.     1       NULL PACE     1     rrr     01       OFF     0     5     0     6.4h     0.FF       OFF     0     6     mon     0FF       OFF     0     err     0FF                                                             | RTKN & HOLD     1     no.     0       NULL PACE     1     err     01       NULL PACE     1     err     01       OFF     0     6     0     6.4h     0FF       OFF     8     non     0FF     0FF       OFF     8     err     0FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RTRN & HOLD1numNULL PACE1errNULL PACE1errOFF050OFF00errOFF050TATEVITE FOLONING FOR TOTEErr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  | ENTER SERUC | Ŕ               |   | 6- <b>4</b> | 4 <del>-</del>  |     | •.   |

| NULL PACE         1         Fr         0           0FF         0         6         0         6Ab         0FF           0FF         0         6         0         6Ab         0FF           0FF         0         6         0         6Ab         0FF | NULL PACE         1         FF         0         5         8         6 (d)         (i)         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         F         0         0         F         0         0         F         0         0         F         0         0         F         0         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0         F         0 | NULL PACE         1         Free           0FF         8         6         8         6.4b           0FF         8         6.00         000           0FF         8         6.00         6.00           0FF         8         6.50         6.00           0FF         8         6.50         6.50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  | RTKN & HOLD | \$**** <b>5</b> |   |             | <b>M</b> t 25 - |     | ₹.   |

| 0FF 0 6 0 (dt 0FF<br>0FF 0 mon 0FF<br>0FF 0 err 0FF                                                                                                                                                                                                  | 0FF 8 6 8 f.dt 0FF<br>0FF 8 mon 0FF<br>0FF 8 err 0FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0FF 8 6 6 8 6.46<br>0FF 8 8 mon<br>0FF 8 8 err                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  | NULL PACE   | \$ <b>\$</b>    |   |             | الحمر ل         |     | F.a. |