0

Б

C

U

$\boldsymbol{\sigma}$

0

### SpaceCube v3.0 Mini NASA Next-Generation Data-Processing System for Advanced CubeSat Applications

Cody G. Brewer Science Data Processing Branch Software Engineering Division NASA - Goddard Space Flight Center Greenbelt, MD, USA

The Twelfth Space Computing Conference

July 2019

www.nasa.gov

# Acronyms

| Acronym | Definition                                 |  |

|---------|--------------------------------------------|--|

| BL-TMR  | BYU-LANL TMR                               |  |

| cFE     | Core Flight Executive                      |  |

| cFS     | Core Flight System                         |  |

|         | Center for High-performance Reconfigurable |  |

| CHREC   | Computing                                  |  |

| CPU     | Central Processing Unit                    |  |

| CSP     | CHREC/CubeSat Space Processor              |  |

| DSP     | Digital Signal Processor                   |  |

| ELC     | ExPRESS Logistics Carrier                  |  |

| EM      | Engineering Model                          |  |

| FF      | Flip-Flop                                  |  |

| FLT     | Flight                                     |  |

| FPGA    | Field Programmable Gate Array              |  |

| FSM     | Finite State Machine                       |  |

| GMSEC   | Goddard Mission Services Evolution Center  |  |

| GOPS    | Giga-Operations Per Second                 |  |

| ISA     | Instruction Set Architecture               |  |

| LEO     | low-Earth Orbit                            |  |

| MGT     | Multi-Gigabit Transceiver                  |  |

| MIPS    | Million instructions per second            |  |

| NSF     | National Science Foundation                |  |

| ORS     | Operationally Responsive Space             |  |

| РСВ     | Printed Circuit Board                      |  |

| RE      | Recuring Engineering                       |  |

| SBC     | Single-Board Computer                      |  |

| SEL    | Single-Event Latchup                          |  |

|--------|-----------------------------------------------|--|

| SEM    | Soft Error Mitigation                         |  |

|        | Spacecraft Supercomputing for Image and Video |  |

| SSIVP  | Processing                                    |  |

| STP-Hx | Space Test Program Houston                    |  |

| TID    | Total Ionizing Dose                           |  |

| TMR    | Triple Modular Redundancy                     |  |

| TRL    | Technology Readiness Level                    |  |

| UVSC   | Ultraviolet Spectro-Coronagraph               |  |

# Outline

1

2

#### Introduction and Background

#### SpaceCube Mini

- SpaceCube Introduction

- SpaceCube Approach

- Mini Design Philosophy

- SmallSat CubeSat Challenges

4

5

#### Fault-Tolerant Design

- Xilinx Space-grade Devices

- Kintex UltraScale

- Soft-Core Processors

- Configuration Schemes & Operation

#### Software and Deployment Examples

Conclusion

- cFE/cFS

- Deployment Configurations

- Specifications

# INTRODUCTION AND BACKGROUND

# Science Data Processing Branch Embedded Processing Group (EPG)

### **EPG Group Specializes in Embedded Development**

- Hardware acceleration of algorithms and applications

- Intelligence, autonomy, and novel architectures

- Flight software integration for development platforms

- Advanced architectures and research platforms

### **Advanced Platforms for Spaceflight**

- SpaceCube v2.0 and v2.0 Mini

- SpaceCube v3.0, v3.0 Mini

- SpaceCube Mini-Z and Mini-Z45

### **Key Tools and Skills**

- Flight Software: cFE/cFS, driver integration, flight algorithms

- **GSE**: COSMOS, GMSEC, system testbeds

- FPGA Design: Hardware acceleration, fault-tolerant structures

- Mission Support: Supporting flight cards, algorithm development

- On-board Autonomy and Analysis: deep-learning frameworks, unique architectures

cube H

Uata

SpaceCube v2.0

# **SpaceCube Introduction**

### What is SpaceCube?

A family of NASA developed space processors that established a hybridprocessing approach combining radiation-hardened and commercial components while emphasizing a novel architecture harmonizing the best capabilities of CPUs, DSPs, and FPGAs

High performance reconfigurable science / mission data processor based on Xilinx FPGAs

- Hybrid processing ...

CPU, DSP, and FPGA logic

- Integrated "radiation upset mitigation" techniques

- SpaceCube "core software" infrastructure (cFE/cFS and "SpaceCube Linux" with Xenomai)

- Small "critical function" manager/watchdog

- Standard high-speed (multi-Gbps) interfaces

# SpaceCube is Hybrid Processing..

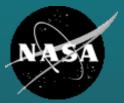

# **SpaceCube Heritage**

Closing the gap with commercial processors while retaining reliability

57+ Xilinx device-years on orbit

26 Xilinx FPGAs in space to date (2019)

11 systems in space to date (2019)

# SpaceCube is Mission Enabling...

SpaceCube v2.0-FLT RRM3, STP-H6 (NavCube)

SpaceCube v2.0 Mini STP-H5, UVSC-GEO

### SpaceCube on the ISS

(Past and Present)

Image Credit: DoD Space Test Program

## SpaceCube Approach

01

The traditional path of developing radiationhardened flight processor **will not work** ... they are always one or two generations behind

02

Use latest radiation-tolerant\* processing elements to achieve massive improvement in "MIPS/Watt" (for same size/weight/power)

03

Accept that radiation induced upsets may happen occasionally and just deal with them appropriately ... any level of reliability can be achieved via smart system design!

\*Radiation tolerant – susceptible to radiation induced upsets (bit flips) but not radiation-induced destructive failures (latch-up)

# **SPACECUBE MINI**

# Goals, Motivations, Challenges

### Goals

Develop reliable, high-speed hybrid processor using SpaceCube design approach to enable next-generation instrument and CubeSat capability

### **Motivations**

Many commercial CubeSat processor offerings primarily target benign LEO orbits and do not strongly address radiation concerns and parts qualification

Need exceptional capability to support complex applications such as artificial intelligence

SpaceCube v3.0 Mini - NASA Goddard Space Flight Center – June 2019

### Challenges

Managing PCB area restrictions for rad-hard components, balancing cost, educating mission designers for key reliability differences

# SpaceCube v2.0 Mini

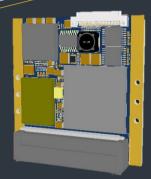

### **Overview of SpaceCube v2.0 Mini**

- TRL9 flight-proven processing system, miniaturized version of SpaceCube v2.0 Processor Card for CubeSats

- 1U CubeSat (10 × 10 × 10 cm) size

- Typical power draw: <10 W</li>

- Scalable design allows daisy-chaining of Mini cards with Gigabit interface

#### SpaceCube v2.0 Mini Unfolded

#### Flight Deployment

### **Missions and Heritage**

- Launched Feb 2017 to ISS on STP-H5/ISEM as mission manager card for several DoD experiments

- Instrument processor for Ultraviolet Spectro-Coronagraph (UVSC) Pathfinder to be launched to GEO on STPSat-6

# SpaceCube Mini-Z (CSPv1)

### **Overview of SpaceCube Mini-Z**

- Collaborative development with NSF CHREC at University of Florida for Zynq-based 1U Board

- Selective population scheme between commercial and rad-hard components

- Rapid deployment prototyping

- Convenient pre-built software packages with cFS

- Re-Envisioned to support quality-of-life upgrades and enable specific NASA mission needs

### **Missions and Heritage**

- Launched Feb 2017 to ISS on STP-H5/CSP featuring 2 CSPv1 cards performing image processing

- Launched May 2019 to ISS on STP-H6/SSIVP featuring 5 CSPv1 for massive parallel computing

- Featured on many more...

Original CSPv1

CSPv1 Development Board

STP-H5/CSP Flight Unit

NASA SpaceCube Mini-Z

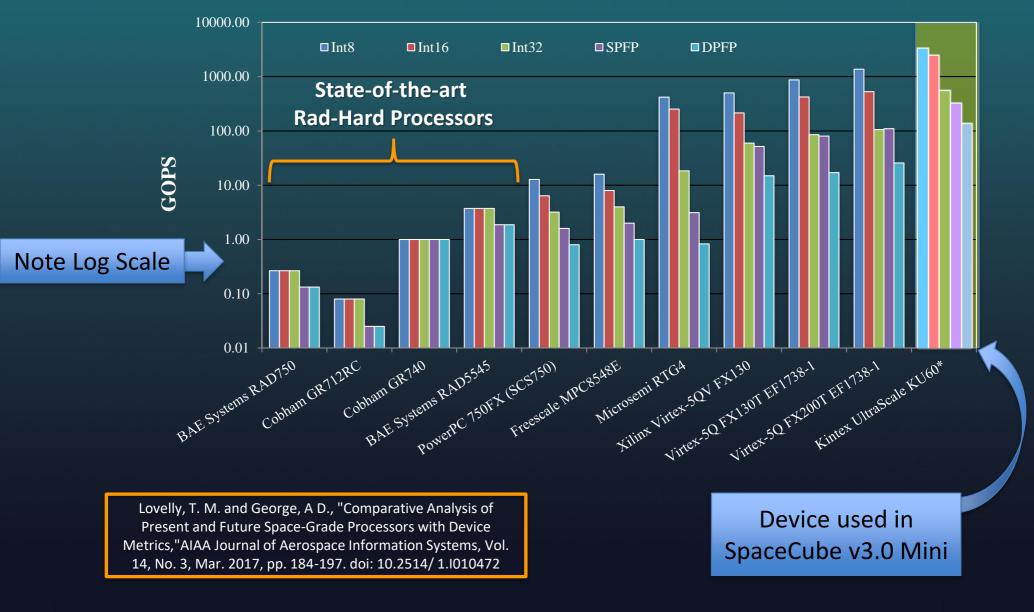

## Performance

\*UltraScale results are an estimate based off of existing data, new metrics are in progress but not currently available

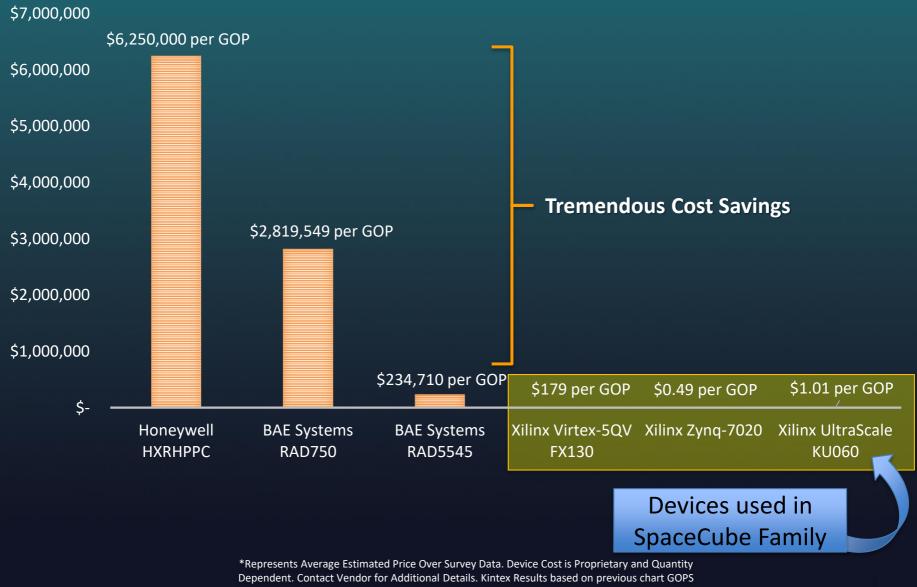

# Affordability

#### COST TO ACHIEVE '1' GOP\*

assumption and industrial-grade device

# **Mini Design Philosophy**

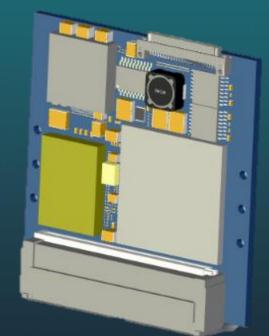

#### SpaceCube v3.0 Processor Card

### SpaceCube v3.0 Mini

220.00 mm

### Same Approach, Smaller Size

SpaceCube design approach applied to smaller form-factor

#### **Key Design Reused**

Much of UltraScale design and interface remain same between cards including DDR Pinout

### **Supervision Requested**

Radiation-hardened monitor architecture and code reusable

### Trade in, Trade Out

EEE parts trades, analysis, and circuits extensively leveraged from main card design

# **Mini Form Factor Lessons Learned**

SpaceCube v2.0 Mini Lessons Learned

CSPv1 Lessons Learned

#### Manufacturability

Difficult to manufacture due to rigidflex and laser-drilled microvias. Tied to single vendor design.

#### **Monitor Design**

Aeroflex rad-hard monitor was effective, however, limited by FPGA resources preventing more robust design

#### **CubeSat Connector**

Samtec SEARAY connector provided flexibility and performance, same connector used with SpaceVNX (VITA 74.4)

#### **Backplane Advantage**

Backplane allows swapping of individual card as advances/ improvements are made and can easily incorporate new components

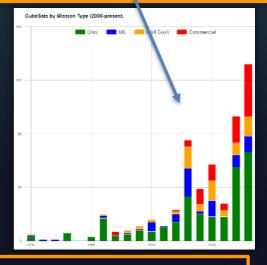

### SmallSat/CubeSat Processor Challenge

#### **Massively Expanding Commercial Market for SBCs**

Tons of commercial vendors in CubeSat Market (e.g. Pumpkin, Tyvak, GomSpace, ISIS, Clyde Space, etc...)

#### **Mission Developers Seeking Commercial Hardware**

- Under pressure from cost-cap missions, and reducing costs in general

- Reduced RE for constellation mission concepts

- Attractive all-commercial solutions provided integrating several CubeSat "Kit" types of cards

#### **Not Designed With Harsh Orbit Considerations Beyond LEO**

- Many vendors have performed limited radiation testing and largely support missions in more benign LEO orbits

- Mission is radiation test approach

- Little-to-no additional radiation testing or parts qualification

- No recommendations for fault-tolerant configurations of offered SBCs

"2019 Nano/Microsatellite Forecast, 9th Edition," SpaceWorks Enterprises, Inc., Jan 2019.

M. A. Swartwout @ The CubeSat Database

# **FAULT-TOLERANT DESIGN**

# Xilinx Space Devices Compared

|                          | SpaceCube v1.0      |            | SpaceCube v2.0                   | SpaceCube v3.0                                |              |

|--------------------------|---------------------|------------|----------------------------------|-----------------------------------------------|--------------|

|                          | XQR4V<br>(RT, 1.2V) |            | XQR5V<br>(RHBD, 1.0V)            | XQRKU060<br>(RT, 1.01V)                       | KU060 vs. V5 |

| Resource                 | FX60                | FX140      | FX130                            | KU060                                         |              |

| Logic Cells              | 56,880              | 142,128    | 131,072                          | 726,000                                       | 5.54x        |

| CLB FF                   | 50,560              | 126,336    | 81,920                           | 663,360                                       | 8.10x        |

| Max Distributed RAM (Kb) | 395                 | 987        | 1,580                            | 9,180                                         | 5.81x        |

| Total Block RAM (Kb)     | 4,176               | 9,936      | 10,728                           | 38,000                                        | 3.54x        |

| BRAM/FIFO ECC (36 Kb)    |                     |            |                                  | 1,080                                         | N/A          |

| DSP Slices               | 128                 | 192        | 320                              | 2,760                                         | 8.63x        |

| MGT                      |                     |            | 18 @ 4.25 Gbps                   | 32 @ 12.5 Gbps                                | 5.23x        |

| TID (krad)               | 300                 | 300        | 1,000                            | 120                                           | (0.12)       |

| SEL                      | >125                | >125       | >125                             | ~80                                           | (0.64)       |

| Flow                     | V-Flow (QML-V)      |            | B-Flow (QML-Q)<br>V-Flow (QML-V) | B-Flow (QML-Q)<br>Y-Flow (QML-Y<br>Compliant) | N/A          |

| Package                  | 35 x 35 mm          | 40 x 40 mm | 45 x 45 mm                       | 40 x 40 mm                                    | (0.78)       |

"Xilinx's Adaptive FPGAs for Space Applications" White Paper

# Xilinx Kintex UltraScale XQRKU060

### First 20 nm FPGA for Space

- Designed for SEU mitigation (>40 patents)

- Deploys same commercial silicon mask set

- Uses Vivado UltraFast Development

- Ruggedized 1509 CCGA

- 40 mm x 40mm package

- Footprint compatible A1517

- Product Space Test Flows

- B-Flow (QML-Q Equiv.) and Y-Flow (QML-Y Compliant)

- Commercial Radiation Testing Results

- Improved Xsect compared to 7 series

- No observed classical SEL signatures

Lee, D., Allen, G., Swift, G., Cannon, M., Wirthlin, M., George, J. S., Koga, R., and K. Huey, "Single-Event Characterization of the 20 nm Xilinx Kintex UltraScale Field-Programmable Gate Array under Heavy Ion Irradiation," IEEE Radiation Effects Data Workshop, July 13-17, 2015.

Berg, M., Kim, H., Phan, A., Seidleck, C., Label, K., and M. Campola, "Xilinx Kintex-UltraScale Field Programmable Gate Array Single Event Effects (SEE) Heavy-ion Test Report," NASA Electronic Parts and Packaging, 2017.

# **Fault-Tolerant Soft-Core Processing**

### Xilinx TMR MicroBlaze<sup>1</sup>

- Built-in Xilinx TMR solution for newer FPGAs

- Includes TMR SEM IP Core

- Vivado IP integrator for easy project creation

#### **BL-TMR MicroBlaze<sup>2</sup>**

- BYU-LANL TMR Tool (BL-TMR) provides automated TMR application

- Fault Injection on MicroBlaze performed for SpaceCube v2.0

### **BL-TMR RISC-V<sup>3</sup>**

- RISC-V is a promising new ISA processor gaining popularity for Intel and Xilinx FPGAs

- Neutron radiation test of Taiga RISC-V

- 27% decrease in operational frequency, for 33x improvement in cross section

Resource Utilization of TMR Designs on KU040

| Resource                     | Unmitigated<br>MicroBlaze | Xilinx TMR<br>MicroBlaze | BL-TMR<br>MicroBlaze | BL-TMR<br>RISC-V <sup>3</sup> |

|------------------------------|---------------------------|--------------------------|----------------------|-------------------------------|

| LUTs                         | 3.29%                     | 9.81%                    | 15.58%               | 0.80 %                        |

| CLB FF                       | 1.63%                     | 4.77%                    | 4.89%                | 0.20 %                        |

| BRAM/FIF<br>O ECC (36<br>Kb) | 12.50%                    | 37.50%                   | 37.50%               | 1.00 %                        |

| DSP Slices                   | 0.31%                     | 0.94%                    | 0.94%                | 0.20 %                        |

| FMax                         |                           | 0.95x                    | 0.88x                | 0.73x                         |

BL-TMR v6.3, MicroBlaze v11, 32-bit 5-stage, FPU, 32 Kb I/D, Vivado 2019.1,

<sup>1</sup>Microblaze Triple Modular Redundancy (TMR) Subsystem v1.0, https://www:xilinx:com/support/documentation/ip documentation/tmr/v1 0/pg268-tmr:pdf, Xilinx, 10 2018.

<sup>2</sup>http://reliability.ee.byu.edu/edif/

<sup>3</sup>A. Wilson and M. Wirthlin, "Neutron Radiation Testing of Fault Tolerant RISC-V Soft Processors on Xilinx SRAM-based FPGAs," 12<sup>th</sup> Space Computing Conference, July 30 – August 1, 2019.

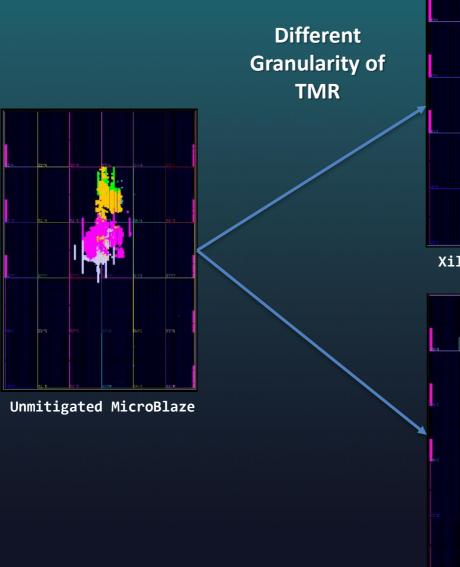

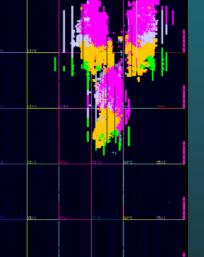

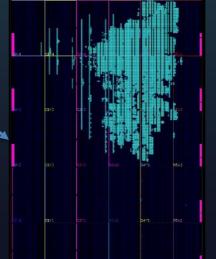

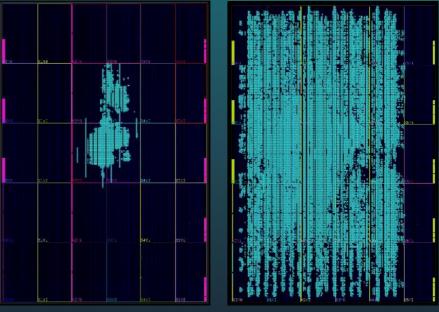

# **TMR Floorplan Design on KU060**

Microblaze

Interconnects/AXI

Caches

Local memory

Xilinx TMR MicroBlaze

BL-TMR tool completely flattens design and removes hierarchical information about the design

BL-TMR MicroBlaze

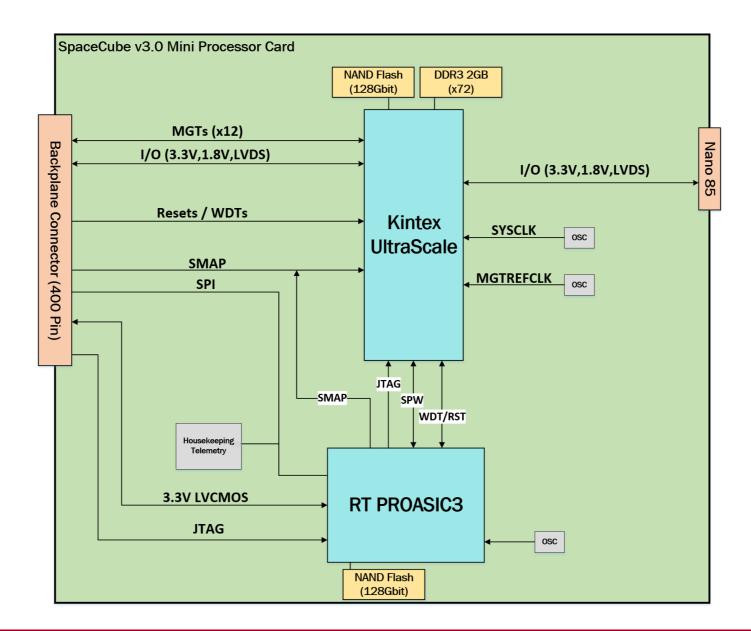

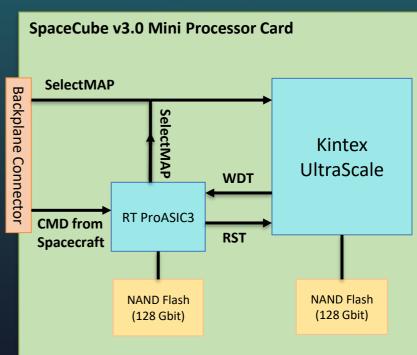

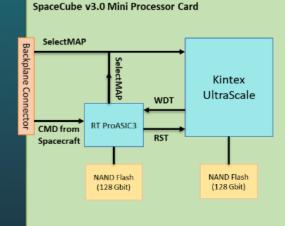

# **SCv3.0 Mini Booting Configuration**

### **Selectable Configuration**

- Kintex configured via SelectMAP from

backplane or on-board RTProASIC3 supervisor

- Dozens of configuration files stored with redundant copies across multiple internal dies

### **Robust RTProASIC Monitor**

- Verifies configuration files are valid via pagelevel CRC checks

- Can reconstruct valid configuration file from several corrupted ones

- Internal FSM ensures Kintex programming and boot sequence is completed correctly

- Automatic program retry

### **Flexible Configuration**

- Can be reconfigured via command from spacecraft to RTProASIC

- Can change configurations in-flight to support dynamic mission requirements

### SCv3.0 Mini Fault-Tolerant Architecture

### Stand-Alone Operation (RT-ProASIC)

- Scrubs Kintex configuration during operation via either:

- Blind scrubbing (consistent time interval)

- Smart scrubbing (readback scrubbing to check configuration and correct errors as they are detected)

- Scrubs configuration files in NAND flash memory

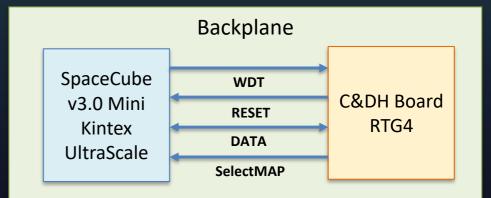

### **Companion-Card Operation (GSFC CubeSat Bus)**

- Combines reliability of RTG4 with high performance of SCv3Mini to form flexible, reusable SmallSat/CubeSat bus

- RTG4 configures and monitors Mini over the backplane

# SOFTWARE AND DEPLOYMENT EXAMPLES

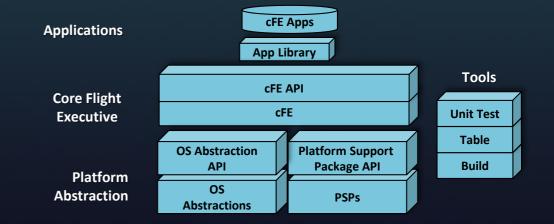

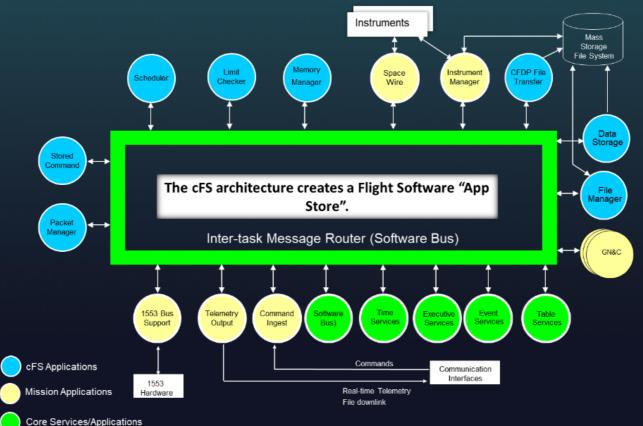

# **Core Flight System (cFS) Overview**

- SpaceCube includes software packages supporting cFS

- cFS is NASA multi-center configuration controlled open source flight software framework

- Layered architecture with standards-based interfaces

- Provides development tools and runtime environment for user applications

- Reusable Class A lifecycle artifacts: requirements, design, code, tests, and documents

- Framework is ported to platforms and augmented with applications to create cFS distributions

- Highly reliable software with more than decade of flight heritage

- Worldwide community from government, industry, and academia

## **Benefits of cFS**

- Portable: Write once, run anywhere cFS framework has been deployed

- Framework has been ported to many popular hardware platform/operating system platforms including MUSTANG, SpaceCube, and CSPv1

- Open Source: 15 Goddard apps released as open source that provide common command and data handling

- Stored command management and execution

- Onboard data storage file management

- Lowers Risk: Reduces project cost and schedule risks

- High quality flight heritage applications

- Focus resources on mission-specific functionality

- Framework provides seamless application transition from technology demonstration efforts to flight projects

# **cFS** Integration

- SpaceCube v2.0 is currently flying with cFE 6.4 with the Linux OSAL

- Many open source applications have been used on the SpaceCube (including SC, SCH, LC, HK, HS, FM)

- Platform support packages exist for SpaceCube v2.0 and SpaceCube Mini

- cFS applications exist to control the SpaceCube Mini Aeroflex, SpaceCube v2.0 Aeroflex, SpaceCube v2.0 Analog Card

## **SpaceCube Development Kit**

# SpaceCube provides software packages for mission development

SpaceCube includes support for several popular OS (Linux, RTEMS, FreeRTOS) and allows for end-to-end flatsat testing with ground station software such as Ball Aerospace's COSMOS and NASA's IRC

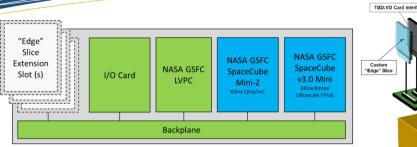

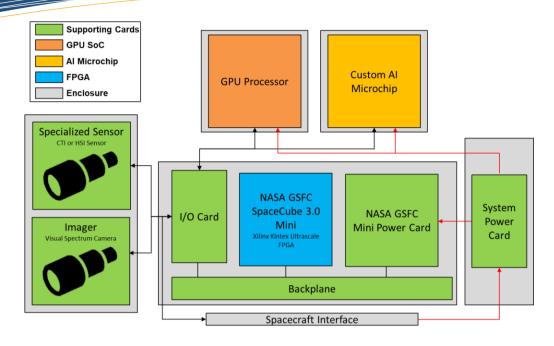

# **Deployment Configurations**

Small form factor makes SpaceCube Mini versatile for many use cases and multiple mission classes

### **Instrument Processing Unit**

- Provides high-speed interface to instruments supporting 12 Multi-Gigabit Transceivers and over 70 LVDS pairs

- Convenient small enclosure for tight integration

#### **High-Performance Processor**

- Featured as the high-performance processor on NASA GSFC's highly reliable CubeSat Bus DellingrX

- Supports latest Xilinx FPGA development tools including high-level synthesis, reVISION, and Partial Reconfiguration

#### AI "Edge Node" System

Can combine SCv3.0 Mini with Mini-Z or Mini-Z45 to provide on-board autonomy and analysis dedicated co-processing node

XILINX

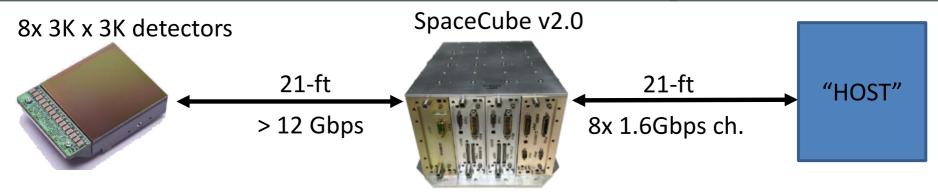

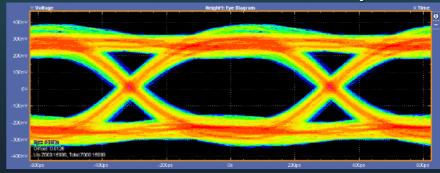

# **NEODaC Instrument Example**

- Near Earth Objects Detection and Characterization (NEODaC)

- SerDes output drivers over 21-ft

- SpaceCube FPGAs being used to interface with detectors, host on-board data processing and compression

- Successful multi-detector readout with SpaceCube completed during TVAC

- SpaceCube Mini can be used in similar role, but supporting faster rates

Xilinx GTX Driver: 1.6Gbps

#### **SerDes Link Test Results**

| Transmitter<br>Swing (mV) | Transmitter %<br>Pre-emphasis | Test Duration | Bit Error<br>Count | BER (*) |

|---------------------------|-------------------------------|---------------|--------------------|---------|

| 500                       | 0                             | 6hr           | 32                 | 9.2E-13 |

| 500                       | 8                             | 18hr          | 0                  | 9.6E-15 |

| 800                       | 0                             | 4hr           | 4                  | 1.7E-13 |

| 800                       | 25                            | 20hr          | 0                  | 8.7E-15 |

| 1300                      | 17                            | 20hr          | 0                  | 8.7E-15 |

| 1300                      | 0                             | 19hr          | 52                 | 4.7E-13 |

• Note: BER calculation assumes at least 1 error 32

58-hours of error-free transmission

# Al "Edge Node" System

#### Artificial intelligence co-processors for on-board autonomy or analysis

- Run machine-learning models on flight-qualified single-board computers networked together for fault tolerance, flexibility, and performance

- Currently deep learning models and applications rely on HPC resources like GPUs not broadly for spaceflight

- State-of-the-art radiation-hardened computers are unable to run modern neural networks

- Published research for running deep learning models on flight systems

### SpaceCube AI Co-Processor

SpaceCube v3.0 Mini combined with SpaceCube Mini-Z or Mini-Z45

AI Co-Processor 1U Box

Expandable Design

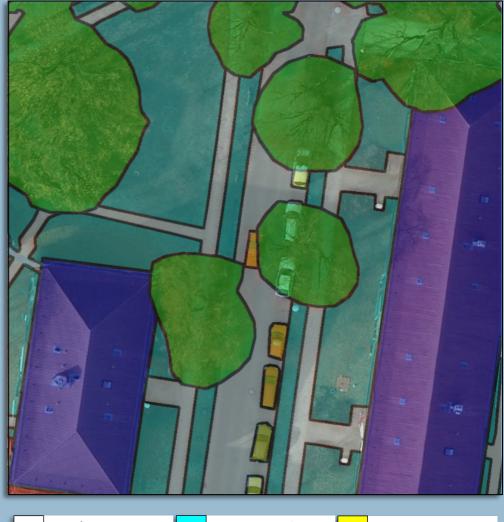

# Advanced Applications Example: Semantic Segmentation

- Computer Vision / Machine Learning Process

- Learns to assign label to all pixels of image

- Pixels with same label share semantic characteristics

- Output roughly resembles input

- Space Applications

- Science: Earth observations and remote sensing

- Defense: reconnaissance and intelligence gathering

S. Sabogal, A. D. George, and G. Crum, "ReCoN: Reconfigurable CNN Acceleration for Space Applications A Framework for Hybrid Semantic Segmentation on Hybrid SoCs," 12<sup>th</sup> Space Computing Conference, July 30 – August 1, 2019.

| Roads     | Low Vegetation | Automobiles |

|-----------|----------------|-------------|

| Buildings | Trees          | Clutter     |

### **SpaceCube for Advanced Applications**

### **Resource-Intensive Applications**

Advanced deep-learning algorithms, such as semantic segmentation, are computationally expensive and prohibitive on traditional rad-hard processors

# **ReCoN (Reconfigurable CNN accelerator)**

- ReCoN is designed for scalability and parameterization of CNNs and used for semantic segmentation demonstration

- Generated using Vivado High Level Synthesis (HLS)

- Parallel computations are scalable, and certain accelerator sizes can only be supported on larger devices such as the Kintex UltraScale in SpaceCube Mini

MicroBlaze

**ReCoN** Accelerator

#### **Resource Utilization of TMR Designs on KU060**

| Resource                 | MicroBlaze<br>Stand Alone<br>Reference | ReCoN <sub>16</sub> |

|--------------------------|----------------------------------------|---------------------|

| LUTs                     | 2.41%                                  | 18.85%              |

| CLB FF                   | 1.19%                                  | 21.61%              |

| BRAM/FIFO<br>ECC (36 Kb) | 6.94%                                  | 6.11%               |

| DSP Slices               | 0.22%                                  | 84.64%              |

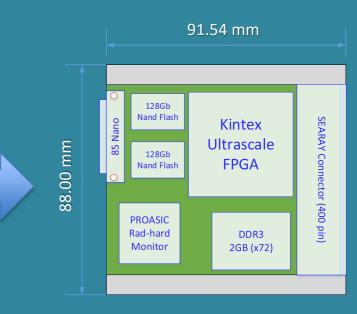

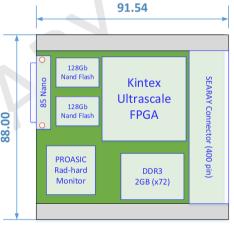

# **SpaceCube v3.0 Mini Specification**

#### Overview

- Apply SpaceCube design approach to provide next-generation processor in CubeSat form-factor

- Maintain compatibility with SpaceCube v3.0

- High-performance processor of Goddard's modular CubeSat spacecraft bus Dellingr-X

### **High-Level Specifications**

#### 1x Xilinx Kintex UltraScale

- 1x 2GB DDR3 SDRAM (x72 wide)

- 2x 16GB NAND Flash

- Radiation-Hardened Monitor

- External Interfaces

- 12x Multi-Gigabit Transceivers

- 48x LVDS pairs or 96x 1.8V single-ended I/O

- 30x 3.3V GPIO

- 2 RS-422/LVDS

- SelectMAP Interface

- (Front Panel) 24x LVDS pairs or 48x 1.8V single-ended I/O

- Debug Interfaces

- 2x RS-422 UART (external transceivers)

- JTAG

# **SpaceCube Mini-Z45 Specification**

## Overview

- Apply SpaceCube design approach to provide next-generation processor in CubeSat form-factor

- Maintain compatibility with SpaceCube v3.0 Mini and Mini-Z designs

- **Upgrade** capabilities of Mini-Z (CSPv1) to provide MGTs, more FPGA resources and more memory

## **High-Level Specifications**

## 1x Xilinx Zyng 7000 System-on-Chip

- 1GB DDR3 SDRAM for ARM Processors

- 2GB DDR3 SDRAM for Programmable Logic

- 16GB NAND Flash

- Radiation-Hardened Watchdog

- External Interfaces

- 8x Multi-Gigabit Transceivers

- 31x LVDS pairs or 62x single-ended I/O (Voltage Selectable)

- 28x Single-ended PS MIO

- Debug Interfaces

- 1x RS-422 UART (external transceivers)

- JTAG

**SEARAY Connector (400 pin)**

91.54

88.00

Zynq 7000

CREDIT CARD

4768 0989 8978 2378

VALID 07/2014 EXP 08/202

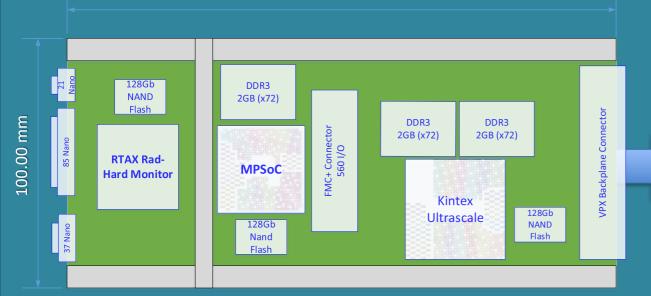

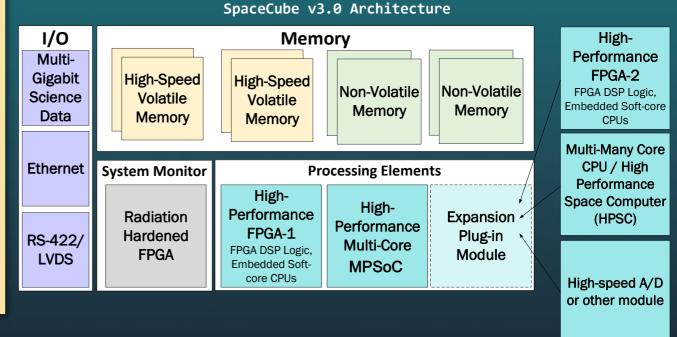

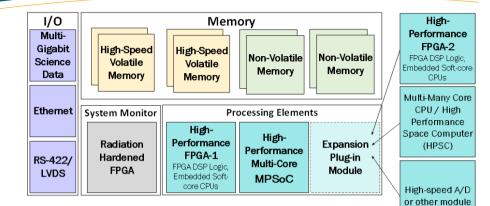

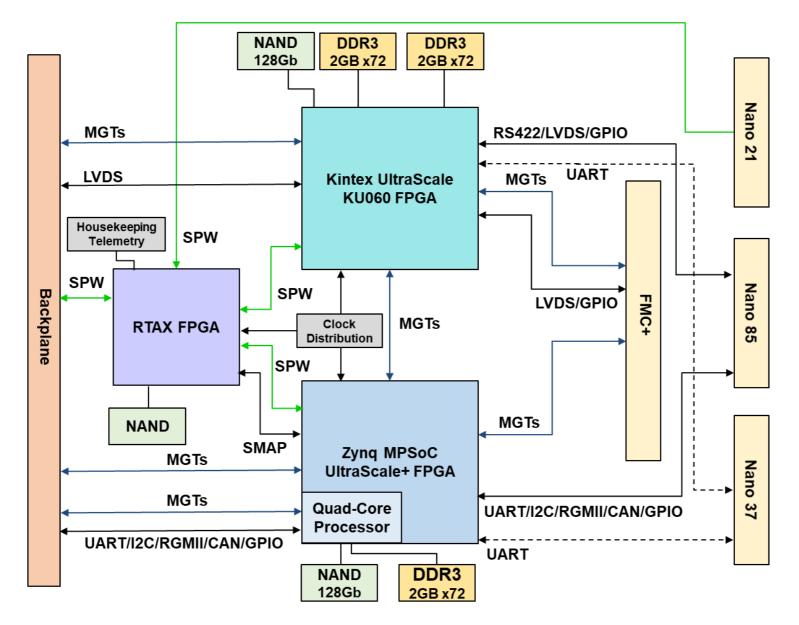

# SpaceCube v3.0 Processor Card

## Overview

- Next-Generation SpaceCube Design

- Prototype demonstration 9/19

- 3U SpaceVPX Form-Factor

- Ultimate goal of using High-Performance Space Computer (HPSC) paired with the high-performance FPGA

- HPSC will not be ready in time for the prototype design

- Special FMC+ Expansion Slot

## **High-Level Specifications**

## 1x Xilinx Kintex UltraScale

- 2x 2GB DDR3 SDRAM (x72 wide)

- 1x 16GB NAND Flash

- External Interfaces

- 24x Multi-Gigabit Transceivers

- 82x LVDS pairs or 164x 1.8V single-ended I/O

- 30x 3.3V single-ended I/O,

- 4x RS-422/LVDS/SPW

- Debug Interfaces

- 2x RS-422 UART / JTAG

## 1x Xilinx Zynq MPSoC

- Quad-core Arm Cortex-A53 processor (1.3GHz)

- Dual Arm R5 processor (533MHz)

- 1x 2GB DDR3 SDRAM (x72 wide)

- 1x 16GB NAND Flash

- External Interfaces

- I2C/CAN/GigE/SPIO/GPIO/SPW

- 12x Multi-Gigabit Transceivers

- Debug Interfaces:

- 10/100/1000 Ethernet (non-flight)

- 2x RS-422 UART / JTAG

## Rad-Hard Monitor FPGA

- Internal SpaceWire router between Xilinx FPGAs

- 1x 16GB NAND Flash

- Scrubbing/configuration of Kintex FPGA

- Power sequencing

- External Interfaces:

- SpaceWire

- 2x 8-channel housekeeping A/D with current monitoring

# SpaceCube "Spin-offs" and Technology Infusion

# SpaceCube designs have expanded to support variety of missions and projects

9 Mission-Unique SpaceCube I/O Cards in various stages of integration and test

- SSCO Video Distribution Unit

- GRSSLi (Code 590)

- NavCube (Code 590)

- GEDI Digitizer design

- Complex PWB design using 1mm pitch CCGAs

- TESS, GEDI, Mustang, OSIRIS-REx

- Proposal development

- CycloPPS (Code 550 and Code 600)

- DTN (Code 450)

- DFB (Code 600)

- Various others

- NICER/GEDI Ethernet Circuitry

- NSF CHREC Space Processor

'NavCube'

GRSSLi Lidar

# Conclusion

# SpaceCube is a MISSION ENABLING technology

Delivers exceptional computing power in number of form factors

Cross-cutting technology for Comm/Nav, Earth and Space Science, Planetary, and Exploration missions

Being reconfigurable equals **BIG SAVINGS**

Past research / missions have proven viability

Designs support AI applications for autonomy and analysis onboard

Successful technology transfer to industry through commercialization

# **SpaceCube Publications**

- A. Geist, C. Brewer, M. Davis, N. Franconi, S. Heyward, T. Wise G. Crum, D. Petrick, R. Ripley, C. Wilson, and T. Flatley, "SpaceCube v3.0 NASA Next-Generation High-Performance Processor for Science Applications," 33rd Annual AIAA/USU Conf. on Small Satellites, SSC19-XII-02, Logan, UT, August 3-8, 2019.

- A. Schmidt, M. French, and T. Flatley, "Radiation hardening by software techniques on FPGAs: Flight experiment evaluation and results," IEEE Aerospace Conference, Big Sky, MT, March 4-11, 2017.

- A. Schmidt, G. Weisz, M. French, T. Flatley, C. Villalpando, "SpaceCubeX: A framework for evaluating hybrid multi-core CPU/FPGA/DSP architectures," IEEE Aerospace Conference, Big Sky, MT, March 4-11, 2017.

- D. Petrick, N. Gill, M. Hassouneh R. Stone, L. Winternitz, L. Thomas, M. Davis, P. Sparacino, and T. Flatley, "Adapting the SpaceCube v2.0 data processing system for mission-unique application requirements," IEEE Aerospace Conference, Big Sky, MT, June 15-18, 2015.

- T. Flatley, "Keynote 2 SpaceCube A family of reconfigurable hybrid on-board science data processors," International Conference on ReConFigurable Computing and FPGAs (ReConFig14), Cancun, Mexico, Dec 8-10, 2014.

- D. Petrick, A. Geist, D. Albaijes, M. Davis, P. Sparacino, G. Crum, R. Ripley, J. Boblitt, and T. Flatley, "SpaceCube v2.0 space flight hybrid reconfigurable data processing system," IEEE Aerospace Conference, Big Sky, MT, March 1-8, 2014.

- D. Petrick, D. Espinosa, R. Ripley, G. Crum, A. Geist, and T. Flatley, "Adapting the reconfigurable spacecube processing system for multiple mission applications," IEEE Aerospace Conference, Big Sky, MT, March 1-8, 2014.

- T. Flatley, "Keynote address I: SpaceCube: A family of reconfigurable hybrid on-board science data processors," NASA/ESA Conference on Adaptive Hardware and Systems (AHS), June 25-28, 2012.

- M. Lin, T. Flatley, A. Geist, and D. Petrick, "NASA GSFC Development of the SpaceCube Mini," 25th Annual AIAA/USU Conf. on Small Satellites, SSC11-X-11, Logan, UT, August 8-11, 2011.

# **SmallSat / CubeSat Publications**

- J. Manning, E. Gretok, B. Ramesh, C. Wilson, A. D. George, J. MacKinnon, G. Crum, "Machine-Learning Space Applications on SmallSat Platforms with TensorFlow," 32nd Annual AIAA/USU Conference on Small Satellites, SSC18-WKVII-03, Logan, UT, Aug 4-9, 2018.

- S. Sabogal, P. Gauvin, B. Shea, D. Sabogal, A. Gillette, C. Wilson, A. D. George, G. Crum, and T. Flatley, "Spacecraft Supercomputing Experiment for STP-H6," 31st Annual AIAA/USU Conf. on Small Satellites, SSC17-XIII-02, Logan, UT, Aug 5-10, 2017.

- C. Wilson, J. MacKinnon, P. Gauvin, S. Sabogal, A. D. George, G. Crum, T. Flatley, "µCSP: A Diminutive, Hybrid, Space Processor for Smart Modules and CubeSats," 30th Annual AIAA/USU Conf. on Small Satellites, SSC16-X-4, Logan, UT, August 6-11, 2016.

- C. Wilson, J. Stewart, P. Gauvin, J. MacKinnon, J. Coole, J. Urriste, A. D. George, G. Crum, A. Wilson, and M. Wirthlin, "CSP Hybrid Space Computing for STP-H5/ISEM on ISS," 29th Annual AIAA/USU Conf. on Small Satellites, SSC15-III-10, Logan, UT, August 8-13, 2015.

- B. LaMeres, S. Harkness, M. Handley, P. Moholt, C. Julien, T. Kaiser, D. Klumpar, K. Mashburn, L. Springer, G. Crum, "RadSat – Radiation Tolerant SmallSat Computer System, "29th Annual AIAA/USU Conf. on Small Satellites, SSC15-X-8, Logan, UT, August 8-13, 2015.

- S. Altunc, O. Kegege, S. Bundick, H. Shaw, S. Schaire, G. Bussey, G. Crum, J. Burke, S. Palo, D. O'Conor, "X-band CubeSat Communication System Demonstration," 29th Annual AIAA/USU Conf. on Small Satellites, SSC15-IV-8, Logan, UT, August 8-13, 2015

- D. Rudolph, C. Wilson, J. Stewart, P. Gauvin, G. Crum, A. D. George, M. Wirthlin, H. Lam, "CSP: A Multifaceted Hybrid System for Space Computing," Proc. of 28th Annual AIAA/USU Conference on Small Satellites, SSC14-III-3, Logan, UT, August 2-7, 2014.

- S. Palo, D. O'Connor, E. DeVito, R. Kohnert, G. Crum, S. Altune, "Expanding CubeSat Capabilities with a Low Cost Transceiver," Proc. of 28th Annual AIAA/USU Conference on Small Satellites, SSC14-IX-1, Logan, UT, August 2-7, 2014.

# Thank you! Questions?

## alessandro.d.geist@nasa.gov spacecube.nasa.gov

Special thanks to our sponsors: NASA/GSFC IR&D, NASA Satellite Servicing Programs Division (SSPD), NASA Earth Science Technology Office (ESTO), DoD Space Test Program (STP), DoD Operationally Responsive Space (ORS)

Icons courtesy https://www.flaticon.com/packs/marketing-management-2

## Artificial Intelligence CubeSat Co-Processor

Experimental ISS Testbed in CubeSat Form-Factor

New Computing Frontier GPUs and custom AI devices have vast potential for accelerating applications in the artificial intelligence domain, however, many have not been evaluated for flight (FPGA will serve as baseline/control)

#### New Mission Enabling

Develop key software functions for adaptive machine learning, multi-point measurements, constellation management, and collaborative satellite ecosystems

#### Key Scenarios

Demonstrate autonomy, decision making, inter-platform collaboration, detection / identification and tracking

For more information on any of our solutions please visit us on the web at: spacecube.nasa.gov

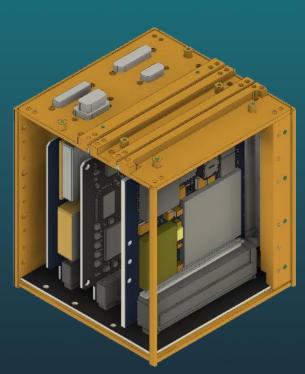

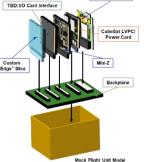

SpaceCube Mini

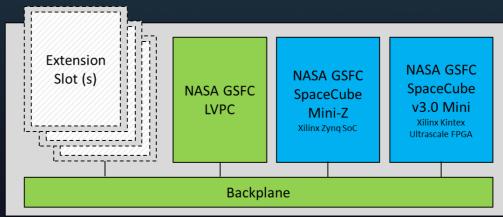

The ISS Artificial Intelligence (AI) and Machine Learning (ML) CubeSat Co-Processor baseline system features the NASA Goddard SpaceCube v3.0 Mini (Kintex UltraScale FPGA), the NASA Goddard SpaceCube Mini-Z (Zynq SoC), the GSFC Low Voltage Power Converter, and customizable I/O card to support mission and instrument unique interfaces. The backplane is extendable for "Edge" processor slices which can feature the Cubic Aerospace Edge Processor (NVIDIA TK1 CPU/GPU SoC), Lucid Circuit Astrum (AI Microchip), or Intel Movidius Myriad X (VPU). Combined with a high-resolution imager, dynamic vision sensor, or other state-of-the-art instruments, this platform would be able to act as an in-flight AI processing unit to execute new AI algorithms in a space environment.

Dual-Core ARM-Cortex A9

## **Baseline Specification**

Processing

- Processing System (PS)

- L1 Cache 32KB I / D per core, L2 Cache 512 KB, onchip Memory 256KB Up to 667 MHz (-1) and 866 MHz (-3) Softcore MicroBlaze(s) 3 Preset Configurations Microcontroller (400 MHz / 540 DMIPS) Real-Time Processor (302 MHz / 405 DMIPS) Application Processor (256 MHz / 232 DMIPS) 811K (726K + 85K) System Logic Cells **FPGA Programmable Logic** 42.9Mb (38 Mb + 4.9 Mb) Block RAM 2,980 (2,760 + 220) DSP Slices Supported Interfaces **External Interfaces** 12x Multi-Gigabit Transceivers 48x LVDS pairs or 96x 1.8V single-ended I/O 24x LVDS pairs or 48x 1.8V, 2.5V, or 3.3V single-ended I/O 30x 3.3V GPIO 12x 1.8V, 2.5V, or 3.3V GPIO 2x RS-422/LVDS 1x SpaceWire Port I2C/CAN/GigE/SPIO/GPIO/SPW 2x RS-422 UART **Debug Interfaces** JTAG Memory 2x 16 GB + 1x 4 GB NAND Flash 1x 2 GB + 1x 1 GB DDR3 SDRAM Mechanical CubeSat 1U (105 mm × 95 mm × 170 mm w/ 1 "Edge" slice) Up to 2.19 kg (depending on Edge Slice) Thermal Conduction cooled **Power Consumption** 24.46 W (Baseline), 50 W (K1 Slice), 26 W (Astrum Slice)

\*Values presented are notional estimates, baseline configuration does not include additional features of "edge" slices

Science Data Processing Branch Gary Crum / Embedded Group Lead

ode 58

## Artificial Intelligence Testbed for ISS

Experimental ISS Testbed To Evaluate AI/ML Technology Platforms

New Computing Frontier GPUs and custom AI devices have vast potential for accelerating applications in the artificial intelligence domain, however, many have not been evaluated for flight (FPGA will serve as baseline/control)

#### New Mission Enabling

Develop key software functions for adaptive machine learning, multi-point measurements, constellation management, and collaborative satellite ecosystems

#### Key Scenarios

Demonstrate autonomy, decision making, inter-platform collaboration, detection / identification and tracking

For more information on any of our solutions please visit us on the web at: spacecube.nasa.gov

The ISS Artificial Intelligence (AI) and Machine Learning (ML) Testbed features the NASA Goddard SpaceCube v3.0 Mini (Kintex UltraScale FPGA), the Cubic Aerospace Edge Processor (NVIDIA TK1 CPU/GPU SoC), and the Lucid Circuit Astrum (AI Microchip). Combined with a high-resolution imager, the platform would be able to act as an in-flight AI testbed to prototype new algorithms in a space environment.

## System Requirements

- Run the state-of-the-art AI algorithms on all three platforms, and show comparisons in performance, power, and resiliency to radiation effects

- Provides flight heritage and verification for three technologies that may be included in future NASA solicitations

3. Provide the capability to upload new software applications to use the in-flight experiment time to test additional applications of interest and scenarios. This upload feature would be convenient to make

adjustments and modifications to code when investigating autonomy reacting to ground commands (Operator's Intent) and experimental prototyping for conveying decisions (Human-readable, decision-making understanding of AI decisions)

Science Data Processing Branch

Tom Flatley / Principal Investigator thomas.p.flatley@nasa.gov

o ground sions

## SpaceCube v3.0 Mini

Next-Generation Data-Processing System for Advanced CubeSat Applications

Apply SpaceCube design approach to provide next-generation processor in CubeSat form factor

Maintains compatibility with main line SpaceCube v3.0

NASA GSFC's new CubeSat framework is under development as the DellingrX mission, where the SpaceCube v3.0 Mini assumes the role of the highperformance processor

For more information on any of our solutions please visit us on the web at: spacecube.nasa.gov

## In order to provide a high-performance processor to perform onboard data analysis, conduct fault mitigation and management, and provide spacecraft autonomy for future missions, the Science Data Processing Branch at NASA GSFC has developed a new CubeSat-sized processor named SpaceCube v3.0 Mini.

The SpaceCube family consists of cross-cutting, in-flight reconfigurable hybrid data processing systems. The Mini is another addition to the SpaceCube family, a series of NASA developed space processors that established a hybrid-processing approach combining radiationhardened and commercial components while emphasizing a novel architecture harmonizing the best capabilities of CPUs, DSPs, and FPGAs. Just as its predecessor card the v2.0 Mini, the design methodology for the SpaceCube Mini series leverages the design of the larger processor card in the SpaceCube family, and reduces the core functionality to fit within a CubeSat form-factor design.

CubeSat Size Comparison to Phone

In "Achieving Science with CubeSats," the Space Studies Board at the National Academies emphasized that NASA must assign a high priority to develop the capability to implement large-scale constellation missions for multi-point science measurements and expanded spatial and temporal coverage. To enable these types of multi-satellite missions, high-performance onboard computing is necessary to provide autonomous behavior to reduce operations cost, as well as, provide robustness, fault management, and resource conservation of the entire constellation. There are many proposals to apply the benefits of groundbased artificial intelligence (AI) algorithms to space autonomy, however, Al structures are too computationally intensive to run on current CubeSat platforms. To enable the next CubeSat revolution, advanced CubeSat applications and complex formation-flying missions need CubeSat processors to offer higher-performance processing while remaining affordable and highly reliable.

## Specification

## Xilinx Kintex UltraScale

- 1x 2GB DDR3 SDRAM (x72 wide)

- 1x 16GB NAND Flash

- Radiation-Hardened Monitor

- External Interfaces

- 12x Multi-Gigabit Transceivers 48x LVDS pairs or 96x 1.8V single-ended I/O

- 30x 3.3V GPIO

- 2x RS-422/IVDS

- 1x SpaceWire Port

- SelectMAP

- (Optional) 24 LVDS pairs or 48x 1.8V single-ended I/O

- Debug Interfaces

- 2x RS-422 UART

- JTAG

Alessandro Geist / Principal Engineer alessandro.d.geist@nasa.gov

## SpaceCube v3.0 Mini

Next-Generation Data-Processing System for Advanced CubeSat Applications

About SpaceCube v3.0 Mini The SpaceCube family consists of cross-cutting, in-flight reconfigurable hybrid data processing systems. The Mini is another addition to the SpaceCube family, a series of NASA developed space processors that established a hybrid-processing approach combining radiationhardened and commercial components while emphasizing a novel architecture harmonizing the best capabilities of CPUs, DSPs, and FPGAs. Just as its predecessor card the v2.0 Mini, the design methodology for the SpaceCube Mini series leverages the design of the larger processor card in the SpaceCube family, and reduces the core functionality to fit within a CubeSat form-factor design.

For more information on any of our solutions please visit us on the web at: spacecube.nasa.gov

#### Contact Us

Science Data Processing Branch

Alessandro Geist / Principal Engineer alessandro.d.geist@nasa.gov

## Specifications

| Processing                                                                  |                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Softcore MicroBlaze(s)</li> <li>FPGA Programmable Logic</li> </ul> | <ul> <li>3 Preset Configurations</li> <li>Microcontroller (400 MHz / 540 DMIPS)</li> <li>Real-Time Processor (302 MHz / 405 DMIPS)</li> <li>Application Processor (256 MHz / 232 DMIPS)</li> <li>100 MHz CLK</li> </ul>  |

|                                                                             | 726K System Logic Cells<br>9,180 KB Block RAM<br>2,760 DSP Slices                                                                                                                                                        |

| Supported Interfaces                                                        |                                                                                                                                                                                                                          |

| External Interfaces                                                         | 12x Multi-Gigabit Transceivers<br>48x LVDS pairs or 96x 1.8V single-ended I/O<br>30x 3.3V GPIO<br>2x RS-422/LVDS<br>1x SpaceWire Port<br>SelectMAP Interface<br>(Front Panel) 24 LVDS pairs or 48x 1.8V single-ended I/O |

| Debug Interfaces                                                            | 2x RS-422 UART<br>JTAG                                                                                                                                                                                                   |

| Memory                                                                      | 2x 16 GB NAND Flash<br>2 GB DDR3 SDRAM                                                                                                                                                                                   |

| Radiation Performance TID:                                                  | Est. 60+ krads (Si)                                                                                                                                                                                                      |

| SEE:                                                                        | TBD Upsets/Day (LEO) TBD (GEO)                                                                                                                                                                                           |

|                                                                             | Radiation-Hardened Monitor                                                                                                                                                                                               |

| Development Tools                                                           |                                                                                                                                                                                                                          |

| Mini Evaluation Board*                                                      | JTAG programming support<br>10/100/1000 Ethernet<br>GPIO breakout<br>4x SpaceWire breakouts<br>2x Camera Link breakout                                                                                                   |

| Software BSP                                                                | Basic SCv3 Mini BSP includes FPGA Cores for all board<br>interfaces, as well as, light-weight Linux supporting CFS                                                                                                       |

| Mechanical                                                                  | 1U CubeSat form factor (< 10 cm x 10 cm)<br>250 grams max weight<br>29mm thickness with populated parts                                                                                                                  |

| Thermal                                                                     | Conduction cooled                                                                                                                                                                                                        |

| Power Consumption                                                           | 10-17 Watts<br>(Application/Utilization Dependant)                                                                                                                                                                       |

| Temperature Ratings <sup>+</sup>                                            | SCv3-EM Operational: 0 to 70 °C<br>SCv3-Flight Operational: -35 °C to +85 °C<br>SCv3-Flight Survival / Storage: -35 °C to +85 °C                                                                                         |

## SpaceCube v3.0

Next-Generation High-Performance Processor for Science Applications

#### Next Generation Design

SpaceCube v3.0 features the latest cutting-edge processing technology for space systems including the new Xilinx Ultrascale and Zynq Ultrascale+

#### **3U SpaceVPX**

SpaceCube v3.0 is built around the new industry standard SpaceVPX form factor. This design ensures compatibility with more vendors and reduces costly vendor lock-in.

#### Expandable

The FMC+ expansion slot is designed to seamlessly integrate new devices with the core processing elements, such as, high-speed ADC/DAC cirucits, GPU's and more!

#### **HPSC** Compatible

Ready for the High-Performance Space Computer (HPSC). SpaceCube v3.0 includes highspeed interfaces, power, and thermal solutions to pair the HPSC with our high-performance FPGA's to meet the most extreme performance and relaiability needs.

For more information on any of our solutions please visit us on the web at: spacecube.nasa.gov This Datasheet is Subject to Change Without Notice

The SpaceCube family consists of cross-cutting, in-flight reconfigurable hybrid data processing systems. In order to provide a robust solution to a variety of missions and instruments, the Science Data Processing Branch at NASA GSFC has pioneered a hybrid-processing approach that combines radiation-hardened and commercial components while emphasizing a novel architecture harmonizing the best capabilities of CPUs, DSPs, and FPGAs. This approach provides anywhere from 10x to 100x improvements in onboard computing capability while lowering relative power consuption and cost. The SpaceCube v3.0 is the next generation SpaceCube design and functions as the next evolutionary step for upcoming missions while providing a flexible and mature architecture to adopt HPSC upon release.

## Specification

## Xilinx Kintex UltraScale

- 2x 2GB DDR3 SDRAM (x72 wide)

- 1x 16GB NAND Flash

- External Interfaces

- 24x Multi-Gigabit Transceivers

82x LVDS pairs or 164x 1.8V single-ended I/O

- 30x 3.3V single-ended I/O.

- 4x RS-422/LVDS/SPW

- Debug Interfaces

- 2x RS-422 UART / JTAG

#### Xilinx Zyng MPSoC

- Quad-core Arm Cortex-A53 processor (1.3GHz)

- Dual Arm R5 processor (533MHz)

- 1x 2GB DDR3 SDRAM (x72 wide)

- 1x 16GB NAND Flash

- External Interfaces

- I2C/CAN/GigE/SPIO/GPIO/SPW

- 12x-16x Multi-Gigabit Transceivers

- Debug Interfaces:

- 2x RS-422 UART / JTAG

#### Rad-Hard Monitor FPGA

- Internal SpaceWire router between Xilinx FPGAs

- 1x 16GB NAND Flash

- Scrubbing/configuration of Kintex FPGA

- Power sequencing

- External Interfaces:

- SpaceWire

- 2x 8-channel housekeeping A/D with current monitoring

## Mezzanine Card

- FMC+ compatible

- 1.8V, 3.3V, 12V power rails Multi-Gigabit interfaces, LVDS, and GPIO

ancerumer

#### Applications

Real-Time instrument processing Autonomous Operations / Robotic Servicing Mission-critical computing Real-time Event / Feature Detection Gigabit interfacing

- On-board classification

- Intelligent data compression

- Real-time situational awareness

- Data volume reduction

- Inter-platform collaboration

- High speed data routing

- Multi-processor computing

- Adaptive processing applications

- Science Data / Image Segmentation

- Software Degined Radio

- Deep Learning / Convolutional Neural Networks

Alessandro Geist / Principal Engineer alessandro.d.geist@nasa.gov

Next-Generation High-Performance Processor for Science Applications

# anarcune I

About SpaceCube v3.0

The SpaceCube family consists of cross-cutting, in-flight reconfigurable hybrid data processing systems. The v3.0 is the next main design in the SpaceCube family, a series of NASA developed space processors that established a hybrid-processing approach combining radiationhardened and commercial components while emphasizing a novel architecture harmonizing the best capabilities of CPUs, DSPs, and FPGAs.The SpaceCube v3.0 functions as the next evolutionary step for upcoming missions while providing a flexible and mature architecture to adopt HPSC upon release.SpaceCube v3.0 features the latest cutting-edge processing technology for space systems including the new Xilinx Ultrascale and Zynq Ultrascale+

For more information on any of our solutions please visit us on the web at: spacecube.nasa.gov

#### Contact Us

Science Data Processing Bra<u>nch</u>

Alessandro Geist / Principal Engineer alessandro.d.geist@nasa.gov

## Specification

| Processing                                                                 |                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processing System (PS)                                                     | <ul> <li>Quad-Core ARM Cortex-A53 Processor (1.3GHz)</li> <li>L1 Cache 32KB I / D per core, L2 Cache 1MB, on-<br/>chip Memory 256KB (ECC)</li> <li>Dual-Core ARM Cortex-R5 processor (533MHz)</li> <li>L1 Cache 32KB I / D per core, Tightly Coupled<br/>Memory 128KB per core (ECC)</li> </ul> |

| Softcore MicroBlaze(s)                                                     | <ul> <li>3 Preset Configurations</li> <li>Microcontroller (400 MHz / 540 DMIPS)</li> <li>Real-Time Processor (302 MHz / 405 DMIPS)</li> <li>Application Processor (256 MHz / 232 DMIPS)</li> </ul>                                                                                              |

| FPGA Programmable Logic                                                    | 1,230K (726K + 504K) System Logic Cells<br>49Mb (38 Mb + 11 Mb) Block RAM<br>27 Mb UltraRAM<br>4,488 (2,760 + 1,728) DSP Slices                                                                                                                                                                 |

| Supported Interfaces                                                       | 4,400 (2,700 + 1,720) 051 511005                                                                                                                                                                                                                                                                |

| External Interfaces                                                        | 36x (24x + 12x) Multi-Gigabit Transceivers<br>82x LVDS pairs or 164x 1.8V single-ended I/O<br>30x 3.3V GPIO<br>4x RS-422/LVDS<br>1x SpaceWire Port                                                                                                                                              |

| Mezzanine Card                                                             | I2C/CAN/GigE/SPIO/GPIO/SPW<br>2x 8-ch Housekeeping ADC<br>FMC+ Compatible<br>1.8V, 3.3V, 12V Power Rails<br>24 Multi-Gigabit Transceivers<br>58x LVDS pairs or 116x 1.8V single-ended I/O<br>20x 3.3V GPIO                                                                                      |

| Debug Interfaces                                                           | 26x Configurable MIO<br>4x (2x + 2x) RS-422 UART<br>JTAG                                                                                                                                                                                                                                        |

| Memory                                                                     | 3x 16 GB NAND Flash<br>3x 2 GB DDR3 SDRAM                                                                                                                                                                                                                                                       |

| Radiation Performance TID:                                                 | Est. 60+ krads (Si)                                                                                                                                                                                                                                                                             |

| SEE:                                                                       | TBD Upsets/Day (LEO) TBD (GEO)                                                                                                                                                                                                                                                                  |

| Rad-Hard Monitor FPGA                                                      | Performs Scrubbing and Power Sequencing                                                                                                                                                                                                                                                         |

| Development Tools                                                          |                                                                                                                                                                                                                                                                                                 |

| Evaluation Card*                                                           | JTAG programming support<br>10/100/1000 Ethernet<br>MIO breakout<br>TBD SpaceWire breakouts                                                                                                                                                                                                     |

| Software BSP                                                               | Camera Link breakout<br>Basic SCv3 BSP includes FPGA Cores for all board interfaces,<br>as well as, light-weight Linux supporting CFS                                                                                                                                                           |

| Mechanical                                                                 | SpaceVPX 3U-220                                                                                                                                                                                                                                                                                 |

|                                                                            | 250 grams max weight<br>29 mm thickness with populated parts                                                                                                                                                                                                                                    |

| Thermal                                                                    | Conduction cooled                                                                                                                                                                                                                                                                               |

| Power Consumption                                                          | 23-55 Watts                                                                                                                                                                                                                                                                                     |

| Temperature Ratings <sup>+</sup>                                           | SCv3-EM Operational: 0 to 70 °C                                                                                                                                                                                                                                                                 |

|                                                                            | SCv3-Flight Operational: -35 °C to +85 °C                                                                                                                                                                                                                                                       |

| *SpaceCube v3.0 Eval Board Still In Development<br>† Pending Finalized BOM | SCv3-Flight Survival / Storage: -35 °C to +85 °C                                                                                                                                                                                                                                                |

+ Pending Finalized BOM

Goddard Space Flight Center

Goddard Space Flight Center