# SINGLE-EVENT TRANSIENTS IN INDIUM GALLIUM ARSENIDE MOSFETS FOR SUB-10 NM CMOS TECHNOLOGY

By

Huiqi Gong

Dissertation

Submitted to the Faculty of the Graduate School of Vanderbilt University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

September 30, 2018

Nashville, Tennessee

Approved:

Ronald D. Schrimpf, Ph.D. Daniel M. Fleetwood, Ph.D. Robert A. Reed, Ph.D. Michael L. Alles, Ph.D. Enxia Zhang, Ph.D. Sokrates T. Pantelides, Ph.D. Copyright © 2018 by Huiqi Gong

All Rights Reserved

#### ACKNOWLEDGEMENT

First and foremost, with my much gratitude, I thank my advisor, Prof. Ronald D. Schrimpf for his kind guidance and tremendous support. His semiconductor classes lighted up my deep interests in semiconductor devices. I was not just impressed by the scientific knowledge he conveyed to us, but also his inspiring teaching method which set up a teaching model to me all my life. As an advisor, he offers me opportunities to lead various research projects, which broadens my insight in this research area, helps me build strong connections with various research groups all over the world, and helps settle my most interested research as this dissertation work. I am also grateful for his insightful discussions and advice, which teach me the way to use scientific methods to conduct research works and benefits all my life.

My sincere thanks also go to Prof. Daniel M. Fleetwood for his continuous guidance and support in my research. His radiation effects class gave me a systematic overview on the radiation effects. He is energetic with broad scientific views. He always helps sort puzzles by recommending the right references when I get confused with previous research works. I learned how to be a good researcher from him. I would also like to thank Prof. Robert A. Reed for guiding me through the single-event effects and laser characterization techniques. His insightful suggestions and discussions strengthen my understanding of the dissertation work. I would also like to thank Prof. Michael L. Alles for his helpful discussions on my research works, especially for the support and guidance through my radiation effects study on MEMS. I would also like to thank Prof. Sokrates T. Pantelides for helpful discussions on optical phenomena. I would also like to thank Prof. Sharon M. Weiss for helpful discussions on my research on MEMS.

I am grateful for my collaborators for providing state-of-art devices. I would like to thank our partners from MIT, Dr. Alon Vardi, Xiaowei Cai, and Prof. Jesús A. del Alamo for providing very advanced III-V MOSFETs. Prof. del Alamo provides valuable academic discussions on my works, which benefits me greatly. I would also like to thank our partners from imec, Niamh Waldron, Bernardette Kunert, and Dr. Dimitri Linten for providing the silicon substrate III-V MOSFETs. I would also like to thank our partners from CERN, Giulio Borghello, and Dr. Federico Faccio for providing the CMOS devices. I would also like to thank our partners from the University of Louisville, Pranoy Deb Shuvra, Dr. Ji-Tzuoh Lin, Prof. Shamus McNamara, Prof. Kevin M. Walsh, and Prof. Bruce W. Alphenaar for providing the MEMS.

I would also like to thank other professors and faculty in the Radiation Effects and Reliability group, with a special mention to Dr. Enxia Zhang for her kind guidance and endless support on semiconductor characterization techniques and helpful discussions on my research topics. Her tremendous support improves my research efficiency greatly. I would also like to thank Dr. Andrew L. Sternberg and Dr. John A. Kozub for their help in the laser tests. Andrew's excellent real-time data processing skill helps improve the laser test efficiency greatly. I would also like to thank Michael W. McCurdy for his help in the proton tests. I would also like to thank Dr. Dennis R. Ball for helpful discussions on TCAD simulations.

A very special gratitude goes out to all my fellow graduate students in the Radiation Effects and Reliability group. It has been a happy working environment with valuable discussions, insights and support during the experiments. These are the best memories I cherish for my whole life. Specially, I thank Kai Ni for his help and insightful discussions on single-event transient characterization and TCAD simulations. I also thank Wenjun Liao for his help and insightful discussions on MEMS. I also thank Pan Wang for her help and insightful discussions on low frequency noise techniques.

In addition, I am grateful for the generous financial support for my studies provided by the Defense Threat Reduction Agency and the Hi-REV program of the Air Force Research Laboratory and Air Force Office of Scientific Research.

Last but not the least, I would like to thank my wife Zhihua Zhu for her infinite support and endless love. She is always the strongest support, which encourages me to keep moving on with my research and all my life. I would also like to thank my parents, my brother and sister for their endless support and love in all my pursuits.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTi                                              | ii |

|---------------------------------------------------------------|----|

| LIST OF TABLES                                                | ii |

| LIST OF FIGURES                                               | ii |

| Chapter                                                       |    |

| 1 Introduction                                                | 1  |

| 2 Background                                                  | 4  |

| 2.1 MOSFET scaling                                            | 4  |

| 2.2 III-V MOSFETs                                             |    |

| 2.3 Radiation environments                                    |    |

| 2.4 Single-Event Effects                                      |    |

| 2.4.1 Charge deposition                                       |    |

| 2.4.2 Charge collection mechanism                             |    |

| 2.4.3 Shunt effect                                            |    |

| 2.4.4 Single-event transient in silicon MOSFETs               |    |

| 2.4.5 Bipolar amplification effect                            |    |

| 2.4.6 Plasmonic effect                                        |    |

| 3 Scaling effects on single-event transient in InGaAs FinFET2 | 1  |

| 3.1 Introduction                                              | 1  |

| 3.2 Device structure and experimental setup                   |    |

| 3.3 Experimental results and discussion                       |    |

| 3.3.1 Pulsed-laser induced charge generation                  |    |

| 3.3.2 Heavy-ion induced charge generation                     |    |

| 3.4 TCAD Simulations                                          |    |

| 3.4.1 Geometric effect                                        |    |

| 3.4.2                                                      | 2 Channel modulation by the substrate                                                                                                                                                                                         | ••••••••••••••••••••••••••••••••••••••• |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 3.5                                                        | Optical Simulations                                                                                                                                                                                                           |                                         |

| 3.6                                                        | Conclusion                                                                                                                                                                                                                    |                                         |

| 4                                                          | Plasmonics enhanced charge deposition in InGaAs FinFETs                                                                                                                                                                       |                                         |

| 4.1                                                        | Introduction                                                                                                                                                                                                                  |                                         |

| 4.2                                                        | Device structure and experimental setup                                                                                                                                                                                       |                                         |

| 4.3                                                        | Experimental results and discussion                                                                                                                                                                                           |                                         |

| 4.4                                                        | Plasmonic effect in InGaAs FinFETs                                                                                                                                                                                            |                                         |

| 4.5                                                        | TCAD simulation                                                                                                                                                                                                               |                                         |

| 4.6                                                        | Conclusion                                                                                                                                                                                                                    |                                         |

| 5<br>5.1                                                   | Pulsed-laser induced single-event transients in InGaAs FinFET                                                                                                                                                                 |                                         |

|                                                            | -                                                                                                                                                                                                                             |                                         |

|                                                            | Introduction                                                                                                                                                                                                                  |                                         |

| 5.1                                                        | -                                                                                                                                                                                                                             |                                         |

| 5.1<br>5.2                                                 | Introduction<br>Experimental details                                                                                                                                                                                          |                                         |

| 5.1<br>5.2<br>5.3<br>5.4                                   | Introduction<br>Experimental details<br>Experimental results and discussion                                                                                                                                                   |                                         |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.4.1                          | Introduction<br>Experimental details<br>Experimental results and discussion<br>TCAD simulations                                                                                                                               |                                         |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.4.2                          | Introduction<br>Experimental details<br>Experimental results and discussion<br>TCAD simulations<br>Parasitic bipolar amplification                                                                                            |                                         |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.4.2                          | Introduction<br>Experimental details<br>Experimental results and discussion<br>TCAD simulations<br>Parasitic bipolar amplification<br>2 Hole collection by the substrate                                                      |                                         |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.4.2<br>5.4.2                 | Introduction<br>Experimental details<br>Experimental results and discussion<br>TCAD simulations<br>Parasitic bipolar amplification<br>2 Hole collection by the substrate<br>3 Reduced carrier lifetime in GaAs                |                                         |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.4.2<br>5.4.2<br>5.4.2<br>5.5 | Introduction<br>Experimental details<br>Experimental results and discussion<br>TCAD simulations<br>Parasitic bipolar amplification<br>2 Hole collection by the substrate<br>3 Reduced carrier lifetime in GaAs<br>Conclusions |                                         |

# LIST OF TABLES

| Table                                                                                        | Page |

|----------------------------------------------------------------------------------------------|------|

| 3.1. Charge generation mechanism for 1260 nm laser                                           |      |

| 3.2. Ions that comprise the LBNL 10 MeV/u cocktail                                           |      |

| 4.1. Charge generation mechanism in InGaAs FinFETs and planar MOSFETs                        |      |

| 5.1. Charge generation mechanism for 1260 nm laser                                           | 63   |

| 6.1. Summary of single-event transients on sub-10 nm node III-V MOSFETs is this dissertation |      |

# LIST OF FIGURES

| Figure                                                                                                                                                                                                                 | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1. Trend in state-of-the-art high performance (HP) CMOS transistor innovation. Transformative changes in materials (high-k dielectric, Ge, III-V channel) and the transistor architecture (3D,                       |      |

| Tunnel FET) being implemented and explored to maintain historical rate of performance, density and power scaling [20]                                                                                                  | 4    |

| 2.2. TEM images of an NMOS GAA Si NWFET ( $L_G = 70$ nm): (a) overview of the Si NW array,                                                                                                                             |      |

| and (b) detailed view of two stacked Si NWs. The rounded NW shape, the narrow NW size                                                                                                                                  |      |

| distribution, and the conformally deposited HK/MG layers are clearly visible [28]                                                                                                                                      | 5    |

| 2.3 (a) Electron and hole mobility of group III-V compound semiconductors. Electron mobility is marked red and hole mobility is in blue. The arrow indicates the increase of biaxial                                   |      |

| compressive strain. (b) Electron injection velocity in III-V compound semiconductors [4]                                                                                                                               | 6    |

| 2.4. Performance comparison of inversion-type InGaAs MOSFETs and HEMTs (with InAs                                                                                                                                      | 0    |

| composition between 0 and 1) vs. year: (a) transconductance, (b) ON resistance [36]                                                                                                                                    | 8    |

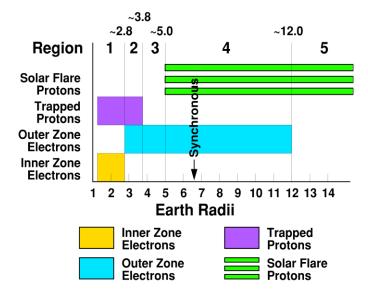

| 2.5. The charged particles trapped by the Earth's magnetosphere [38].                                                                                                                                                  |      |

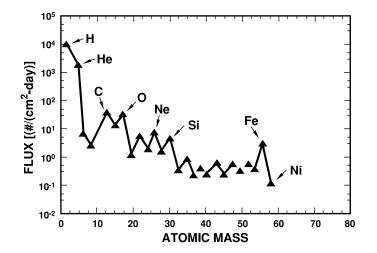

| 2.6. Relative abundance of the elements from hydrogen to the iron group [39]                                                                                                                                           | 9    |

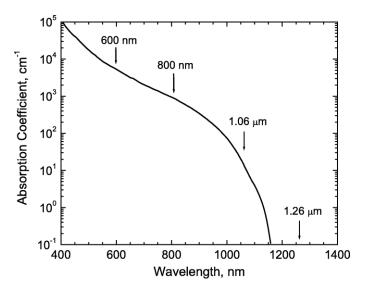

| 2.7. Room temperature absorption spectrum of silicon in the visible and near-infrared region of the                                                                                                                    |      |

| spectrum illustrating the common laser wavelengths used for above-bandgap single-event                                                                                                                                 |      |

| effects measurements and also that for the subbandgap experiment [44]                                                                                                                                                  | 11   |

| 2.8. Charge generation and collection phases in a reverse-biased junction and the resultant current                                                                                                                    | 10   |

| pulse caused by the passage of a high-energy ion [47]                                                                                                                                                                  |      |

| 2.9. Illustration of ion track shunt effect in two-junction experimental structure [49].                                                                                                                               | 14   |

| 2.10. Transient drain currents induced by pulsed laser irradiation in 0.25 μm NMOS and 50 nm NMOS transistors [58].                                                                                                    | 15   |

| 2.11. Drain current induced by heavy ion irradiation in bulk FinFETs with different contact type.                                                                                                                      | 15   |

| Solid (black) curve is the largest transient curve that was recorded in a FinFET ( $W_f/L = 20/70$ )                                                                                                                   |      |

| with dumbbell contacts. The dashed (red) curve is the largest current transient recorded in a                                                                                                                          |      |

| FinFET ( $W_f/L = 20/60$ ) with saddle contacts [53].                                                                                                                                                                  | 15   |

| 2.12. Schematic diagram illustrating (a) the bipolar gain and (b) channel-modulation charge                                                                                                                            |      |

| enhancement mechanisms that contribute to the charge collection processes of GaAs FETs                                                                                                                                 |      |

| [63]                                                                                                                                                                                                                   | 16   |

| 2.13. Peak drain current along a line scan for different gate lengths. The laser wavelength $\lambda = 1260$                                                                                                           |      |

| nm. The shadow represents the standard deviation among the 50 transients recorded at each                                                                                                                              | 1.5  |

| position. $V_G - V_{\text{TH}} = 0$ V. $W_{\text{FIN}} = 30$ nm. Laser pulse energy is 0.65 ± 0.01 nJ [54]                                                                                                             | 1 /  |

| <ul><li>2.14. (a) Schematic of surface plasmons at the interface between a metal and a dielectric material.</li><li>(b) The field component perpendicular to the surface being enhanced near the surface and</li></ul> |      |

| decaying exponentially with distance away from it [67]                                                                                                                                                                 | 18   |

| 2.15. Plasmonic tandem solar-cell geometry. Semiconductors with different bandgaps are stacked                                                                                                                         | 10   |

| on top of each other, separated by a metal contact layer with a plasmonic nanostructure that                                                                                                                           |      |

| couples different spectral bands of the solar spectrum into the corresponding semiconductor                  |

|--------------------------------------------------------------------------------------------------------------|

| layer [71]                                                                                                   |

| 2.16. FinFETs evolution in Intel from 22 nm node to 10 nm node [78]                                          |

| 3.1. (a) 3D qualitative representation of the fin structure of the InGaAs double-gate FinFETs, (b)           |

| cross-section along the fin width direction, and (c) 3D schematic diagram of 11 fin InGaAs                   |

| double-gate FinFETs. Gate (G), drain (D), and source (S) are labeled on the diagram. (Not                    |

| drawn to scale)                                                                                              |

| 3.2. Band diagrams cut through the fin structure along the (a) fin width direction and (d) fin height        |

| direction23                                                                                                  |

| 3.3. A simplified block diagram of TPA test setup. In the figure, 'L' stands for lens, 'M' stands for        |

| mirror, 'S' stands for shutter, 'P' stands for polarizer, 'BS' stands for beam splitter, 'PD' stands         |

| for photodiode, and "BB" represents the broadband light source. The red line indicates the                   |

| optical path traveled by the laser beam. The blue line indicates the reflected light that is                 |

| imaged by the near infrared camera [54]24                                                                    |

| 3.4. Schematic diagram of the heavy-ion experiment setup. Two Keithley 2410 working as SMUs                  |

| for gate and drain terminals. The source terminal is grounded by 50 $\Omega$ terminator                      |

| 3.5. Brass high-speed packages for pulsed-laser experiments (top) and heavy-ion experiments                  |

| (bottom)                                                                                                     |

| 3.6. SET captured during TPA testing for an InGaAs FinFET. $L_G = 100$ nm, $W_f = 40$ nm                     |

| 3.7. Peak drain current (a) and drain collected charge (b) along a line scan for InGaAs FinFETs of           |

| different fin widths during TPA testing                                                                      |

| 3.8. Drain current transients for InGaAs FinFETs of different fin widths during TPA testing (peak            |

| drain current is taken as absolute value). The laser strike is at the center of the gate                     |

| 3.9. Peak drain current along a line scan at different drain bias during TPA testing. $W_f = 40$ nm, $L_G =$ |

| 100 nm                                                                                                       |

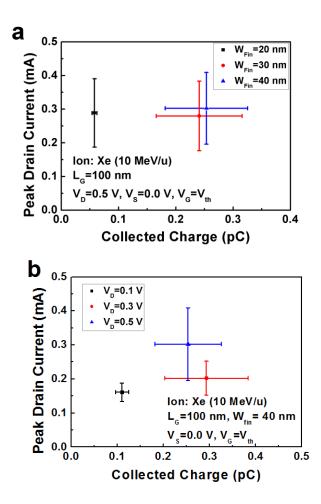

| 3.10. SET captured during heavy ion testing for an InGaAs FinFET. $L_G = 100$ nm, $W_f = 40$ nm              |

| 3.11. Collected charge and peak drain current during Xe irradiation for devices with different fin           |

| width (a) and drain bias (b). Each data point is averaged from 50 transient events                           |

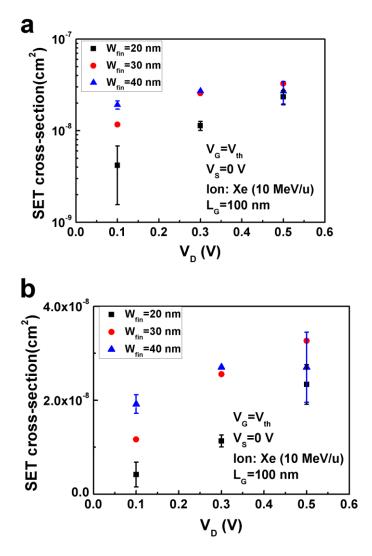

| 3.12. SET cross-section vs. $V_{DS}$ for InGaAs FinFETs with different fin widths (a) log scale and (b)      |

| linear scale. Each data point is averaged from 50 transient events                                           |

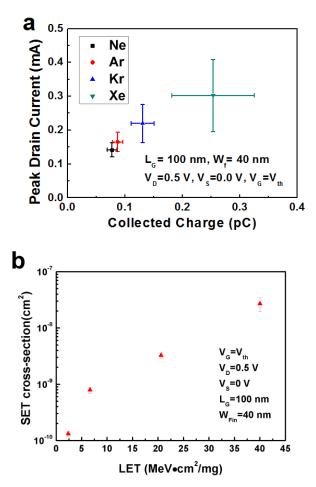

| 3.13. (a) Collected charge, peak drain current and (b) SET cross-section for a 40 nm device with             |

| heavy-ion irradiation at different LET in In <sub>0.53</sub> Ga <sub>0.47</sub> As                           |

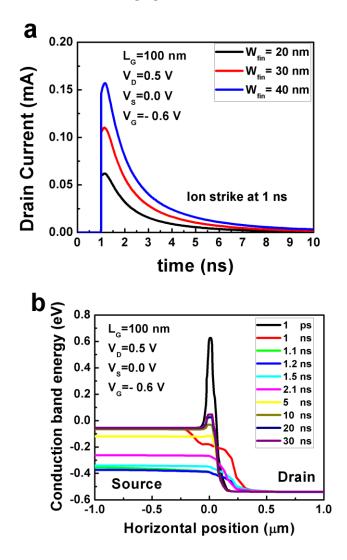

| 3.14. (a) Drain current transients for InGaAs FinFETs of different fin widths from TCAD                      |

| simulation, (b) conduction band energy evolution along the channel after charge deposition                   |

| 3.15. Electron density distribution (b,c,d) for 20 nm fin-width devices with different doping in the         |

| red region (a). $V_G = 0.6 \text{ V}, V_D = 0.5 \text{ V}, V_S = 0 \text{ V}.$ 37                            |

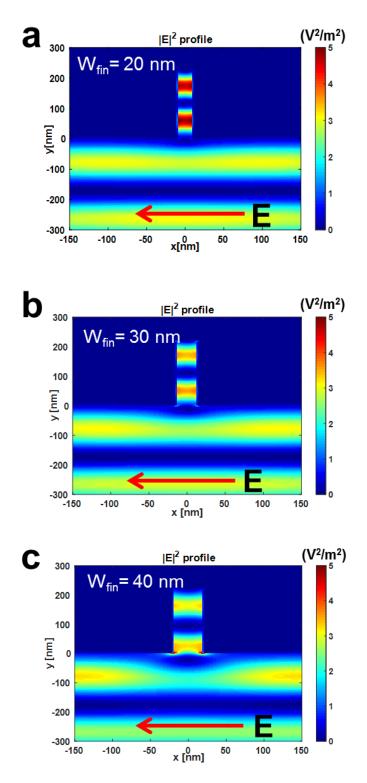

| 3.16. Optical $(E^2)$ field distribution calculated by 2D Lumerical simulations for simplified silicon       |

| FinFETs with different fin width                                                                             |

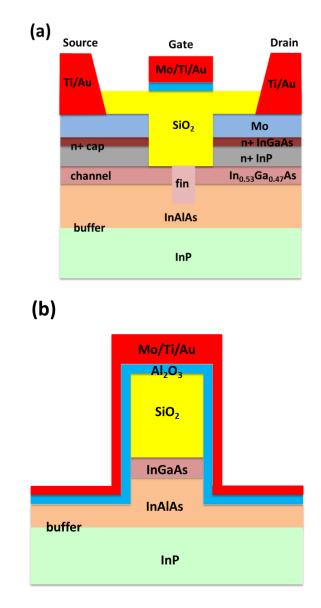

| 4.1. (a) Schematic cross section and (b) side-view of an InGaAs double-gate FinFET (not drawn to             |

| scale)                                                                                                       |

|                                                                                                              |

| 4.2. (a) Schematic cross section and (b) side-view of an InGaAs planar MOSFET (not drawn to                     | 11         |

|-----------------------------------------------------------------------------------------------------------------|------------|

| scale).                                                                                                         | 44         |

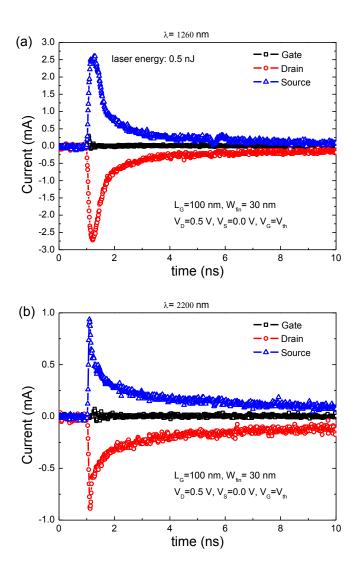

| 4.3. SET captured during pulsed-laser testing for an InGaAs FinFET with wavelength at (a) 1260                  |            |

| nm and (b) 2200 nm. The strike point is at the center of the device. $W_{fin} = 30$ nm, $L_G = 100$ nm.         |            |

| $V_G - V_{th} = 0 \text{ V}; V_{DS} = 0.5 \text{ V}.$                                                           | 46         |

| 4.4. SET captured during pulsed-laser testing for an InGaAs planar MOSFET with wavelength at (a)                |            |

| 1260 nm and (b) 2200 nm. The strike point is at the center of the device. $W/L = 10 \ \mu m/200 \ nm$ .         |            |

| $V_G - V_{th} = 0 \text{ V}; V_{DS} = 0.5 \text{ V}.$                                                           | 47         |

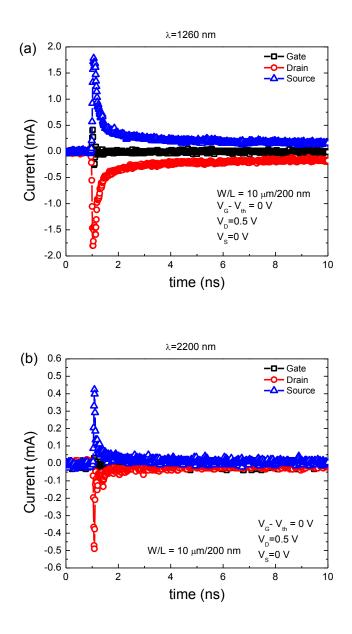

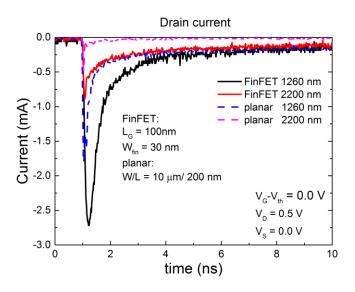

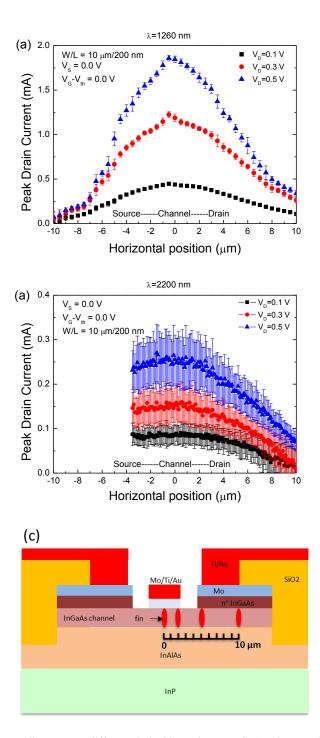

| 4.5. Drain current comparison for an InGaAs FinFET (solid lines) and planar MOSFET (dashed                      |            |

| lines). The strike point is at the center of the device. $V_G - V_{th} = 0$ V; $V_{DS} = 0.5$ V                 | 48         |

| 4.6. Peak drain current along a line scan at different drain biases for an InGaAs FinFET with                   |            |

| wavelength at (a) 1260 nm and (b) 2200 nm. The error bars represent the standard deviation of                   |            |

| the mean. (c) The cross-section view of an InGaAs FinFET with scale shows the line scan area                    |            |

| w.r.t. the device geometry. Geometry on vertical direction is not scaled                                        | 49         |

| 4.7. Peak drain current along a line scan at different drain biases for an InGaAs planar MOSFET                 | 77         |

|                                                                                                                 |            |

| with wavelength at (a) 1260 nm and (b) 2200 nm. The error bars represent the standard                           |            |

| deviation of the mean. (c) The cross-section view of an InGaAs planar MOSFET with scale                         |            |

| shows the line scan area w.r.t. the device geometry. Geometry on vertical direction is not                      | -0         |

| scaled.                                                                                                         | 50         |

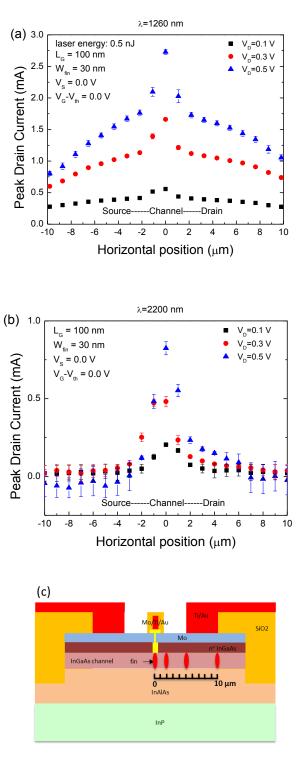

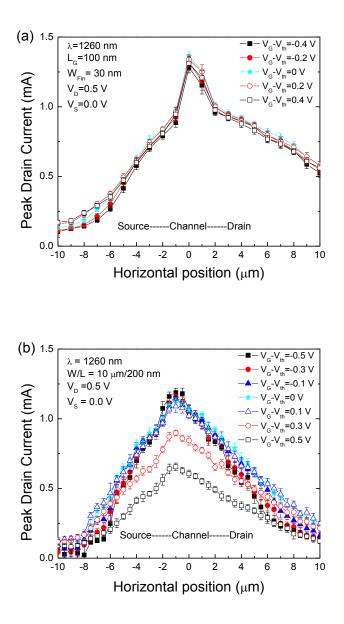

| 4.8. Peak drain current along a line scan at different gate bias for InGaAs (a) FinFET and (b) planar           |            |

| MOSFET. The error bars represent the standard deviation of the mean                                             | 51         |

| 4.9. Peak drain current area mapping for an InGaA FinFET with wavelength at (a) 1260 nm and (b)                 |            |

| 2200 nm. The peak current is normalized to the maximum peak current in both figures. The                        |            |

| black box in each figure marks the sensitive area at different wavelength. The corresponding                    |            |

| cross-section view of the device is also shown in each figure                                                   | 53         |

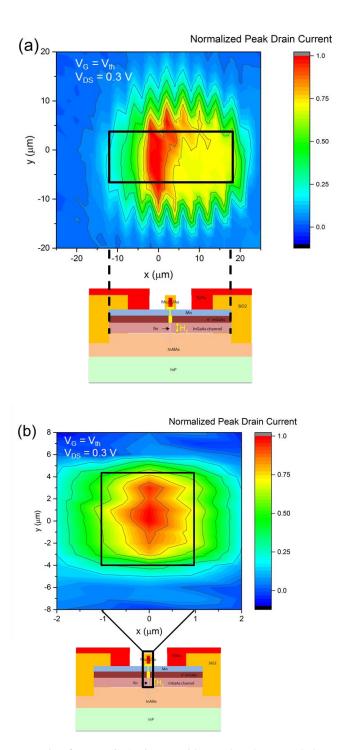

| 4.10. Optical (E <sup>2</sup> ) field propagation calculated by 2-D Lumerical simulations for simplified FinFET |            |

| structure.                                                                                                      | 54         |

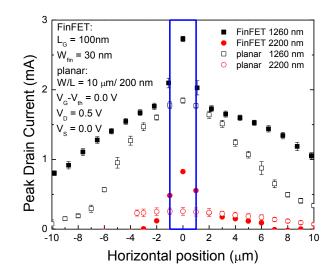

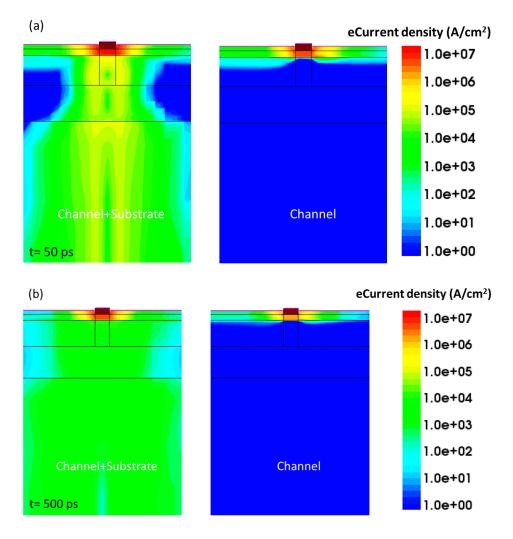

| 4.11. Peak drain current comparison along a line scan between an InGaAs FinFET (solid symbols)                  |            |

| and an InGaAs planar MOSFET (open symbols) with wavelength at 1260 nm (black) and 2200                          |            |

| nm (red). The blue box marks the fin dimension for the InGaAs FinFET. The error bars                            |            |

| represent the standard deviation of the mean. $V_G - V_{th} = 0$ V; $V_{DS} = 0.5$ V                            | 55         |

| 4.12. Peak drain current comparison along a line scan between an InGaAs FinFET with fin height                  |            |

| of 220 nm (black box) and 40 nm (red circle) [56] at wavelength of 1260 nm. The error bars                      |            |

| represent the standard deviation of the mean. $V_G - V_{th} = 0$ V; $V_{DS} = 0.5$ V                            | 55         |

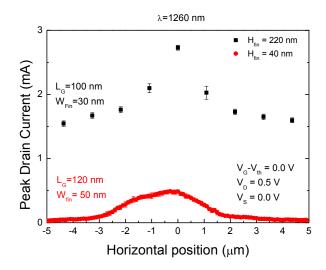

| 4.13. (a) Charge injection schematic in SET simulations. (b) Drain current transients for charge                | 00         |

| injection only in channel (red) and both channel and substrate (black)                                          | 57         |

|                                                                                                                 | 51         |

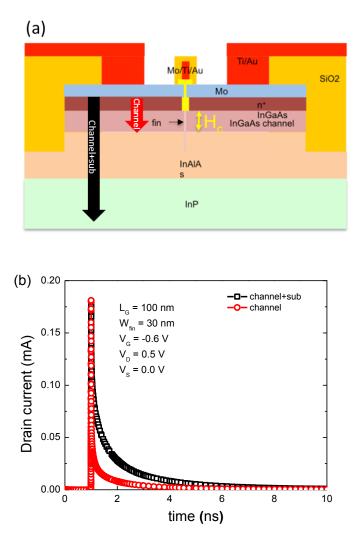

| 4.14. Electron current density for charge deposition in both channel and substrate (left) and channel           | <b>5</b> 0 |

| only (right) (a) 50 ps after charge deposition, and (b) 500 ps after charge deposition.                         | 38         |

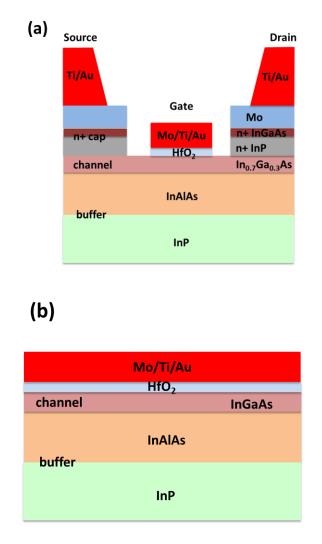

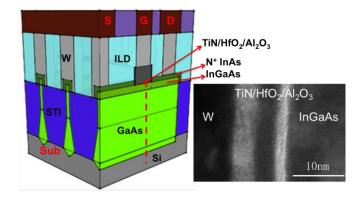

| 5.1. 3-D diagram of InGaAs FinFET on bulk silicon. Gate (G), drain (D), source (S), and substrate               |            |

| (Sub) are labeled in red. The inset shows a TEM image of the gate stack [49]                                    | 62         |

|                                                                                                                 |            |

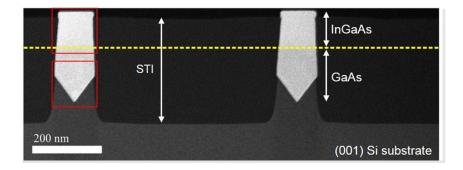

| 5.2. HAADF-STEM images of an InGaAs/GaAs hetero-structure. The yellow dashed line visualizes the interface between InGaAs and GaAs [108]                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

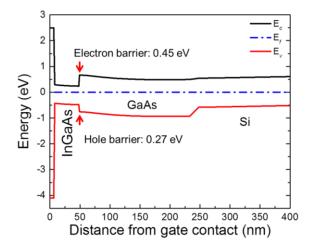

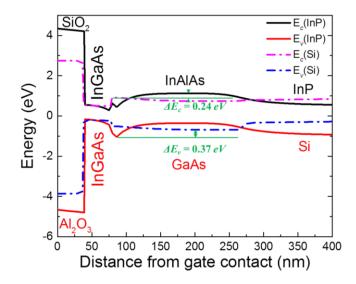

| 5.3. Energy band diagram for a Si-based InGaAs FinFET for a cut line (red dashed line in Fig. 1)<br>through the gate to substrate                                                                                                                                                                |

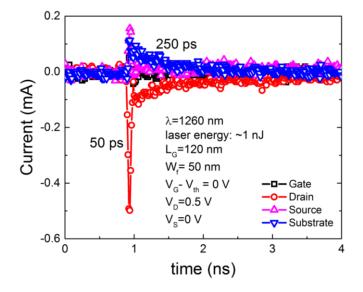

| 5.4. SET captured during pulsed-laser testing for an InGaAs FinFET on bulk silicon. $W_{fin} = 50$ nm,<br>$L_G = 120$ nm. $V_G - V_{th} = 0$ V; $V_{DS} = 0.5$ V. The strike point is at the center of the device                                                                                |

| 5.5. Normalized (to fin number) peak drain currents between an InGaAs FinFET on silicon (black) and previous results for an InGaAs FinFET on InP (red) [55]. Devices are irradiated at the                                                                                                       |

| same pulsed-laser energy                                                                                                                                                                                                                                                                         |

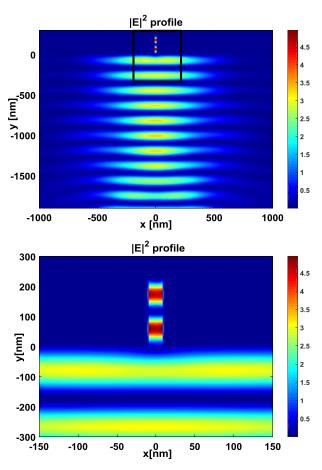

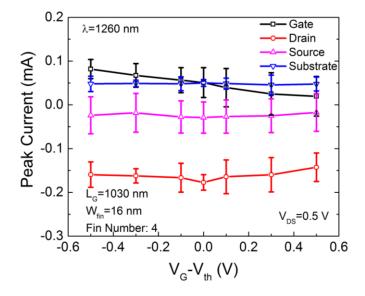

| represent the standard deviation of the mean. $W_{fin} = 16$ nm, $L_G = 1030$ nm. $V_{DS} = 0.5$ V                                                                                                                                                                                               |

| 5.7. Peak drain current along a line scan at different drain biases for an InGaAs FinFET on silicon<br>(a) and an InGaAs FinFET on InP (b) [55]. Solid symbols correspond to $V_s = 0$ V; open<br>symbols correspond to $V = V$                                                                  |

| symbols correspond to $V_S = V_D$                                                                                                                                                                                                                                                                |

| gate region. $L_G = 100$ nm, $W_{fin} = 50$ nm                                                                                                                                                                                                                                                   |

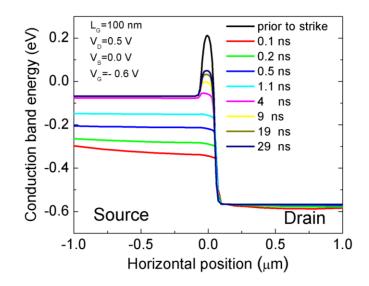

| 5.9. Conduction band energy evolution along the channel after charge deposition for InGaAs FinFETs on silicon substrate. $V_G - V_{th} = -0.6 \text{ V}$ ; $V_{DS} = 0.5 \text{ V}$ . $L_G = 100 \text{ nm}$ , $W_{fin} = 50 \text{ nm}$                                                         |

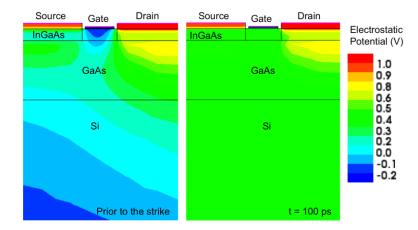

| 5.10. Constant electrostatic potential contours for an InGaAs FinFET prior to the laser strike (left)<br>and 100 ps after the strike $V = 0.6 V$ ; $V = 0.5 V L = 100 \text{ pm}$ $W = 50 \text{ pm}$                                                                                            |

| and 100 ps after the strike. $V_G - V_{th} = -0.6 \text{ V}$ ; $V_{DS} = 0.5 \text{ V}$ . $L_G = 100 \text{ nm}$ , $W_{fin} = 50 \text{ nm}$                                                                                                                                                     |

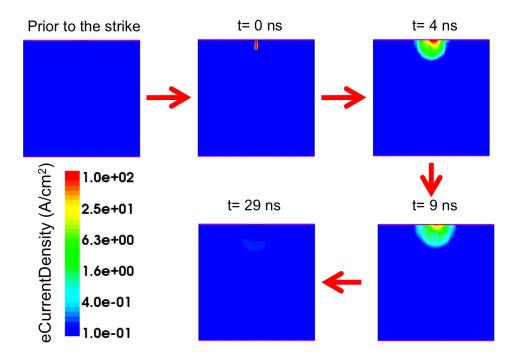

| Substrate contact is at bottom. $V_G - V_{th} = -0.6 \text{ V}$ ; $V_{DS} = 0.5 \text{ V}$ . $L_G = 100 \text{ nm}$ , $W_{fin} = 50 \text{ nm}$ 70<br>5.12. Temporal evolution of hole current density in the substrate after charge deposition. The                                             |

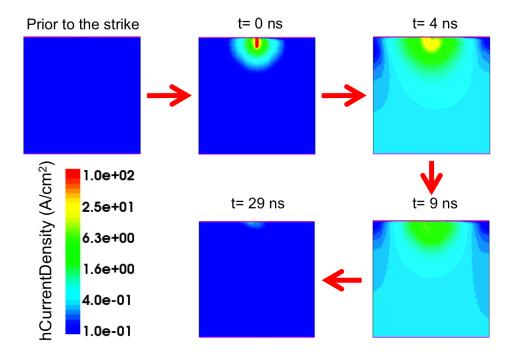

| substrate contact is at the bottom. $V_G - V_{th} = -0.6 \text{ V}$ ; $V_{DS} = 0.5 \text{ V}$ . $L_G = 100 \text{ nm}$ , $W_{fin} = 50 \text{ nm}$                                                                                                                                              |

| 5.13. Energy band diagrams for an InP-based InGaAs FinFET (solid lines, corresponding stack material is shown in black text, SiO <sub>2</sub> /InGaAs/InAlAs/InP) and a Si-based InGaAs FinFET (dot                                                                                              |

| dashed lines, corresponding stack material is shown in red text, Al <sub>2</sub> O <sub>3</sub> /InGaAs/GaAs/Si). The cut line is through the gate to substrate. The barrier difference between these two devices is                                                                             |

| also shown in the figure. $V_G - V_{th} = -0.6 \text{ V}; V_{DS} = 0.5 \text{ V}$                                                                                                                                                                                                                |

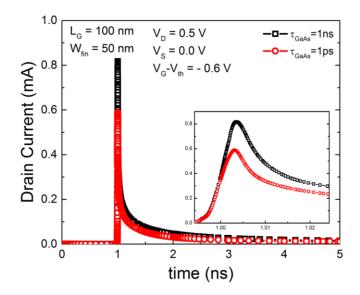

| 5.14. Drain current transients for Si-based InGaAs FinFETs. The carrier lifetime is varied in the GaAs buffer layer. Black squares show transients with carrier lifetime of 1 ns, and the red circles show transients with carrier lifetime of 1 ps. The inset shows the detail of the transient |

| peaks. $V_G - V_{th} = -0.6 \text{ V}; V_{DS} = 0.5 \text{ V}. L_G = 100 \text{ nm}, W_{fin} = 50 \text{ nm}$                                                                                                                                                                                    |

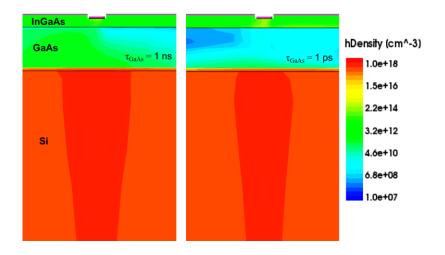

| 5.15. Hole density distribution 50 ps after the strike for InGaAs FinFETs on silicon substrate. The carrier lifetime is varied in the GaAs buffer layer. $V_G - V_{th} = -0.6$ V; $V_{DS} = 0.5$ V. $L_G = 100$ nm, $W_{fin} = 50$ nm                                                            |

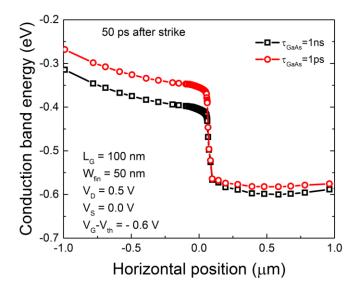

| 5.16. Conduction band energy along the channel 50 ps after the strike for InGaAs FinFETs on silicon substrate. The carrier lifetime is varied in the GaAs buffer layer. $V_G - V_{th} = -0.6$ V; $V_{DS}$                                                                                        |

| $= 0.5 \text{ V}. L_G = 100 \text{ nm}, W_{fin} = 50 \text{ nm}.$ 73                                                                                                                                                                                                                             |

# Chapter 1 Introduction

MOSFETs are the building blocks of modern electronics. A modern microprocessor contains billions of transistors. The microelectronics revolution can be characterized by the motto 'smaller is better', due to its cost reduction, enhanced performance and greater efficiency [1]. There are various energetic particles existing in the space, atmospheric and terrestrial radiation environments [2]. These energetic particles generate excess electron-hole pairs while passing through semiconductor devices. The excess carriers then move inside devices through either drift or diffusion process, resulting in a transient current at the device terminals [3]. This transient current, called a single-event transient (SET), may produce soft errors in microelectronic circuits in space applications. As technology scales, soft errors in terrestrial integrated circuits (IC) emerge as one of the most important reliability issues. Many technical conferences, such as the International Reliability Physics Symposium (IRPS), now include sessions on soft errors and single-event effects (SEE) [3].

III-V FinFETs are promising candidates for the sub-10 nm technology due to their effective gate control and superior transport properties [4]. However, obtaining high performance III-V MOSFETs is challenging because of the lattice mismatch between III-V materials and silicon. Most III-V MOSFETs are still integrated on semi-insulating III-V substrates to improve the electronic performance [5]-[14]. To be compatible with current CMOS technology, III-V MOSFETs must be integrated on silicon substrates. Recently, successful integration of III-V FinFETs on 300 mm silicon wafers has been demonstrated, representing significant progress towards application in next generation logic transistors [15]-[18].

The objective of this work is to explore the SET response and charge collection mechanisms of III-V FinFETs on semi-insulating and silicon substrates. Both pulsed laser and heavy-ion irradiation were used to examine the SET sensitivities in these devices. The heavy-ion experiments are of particular interest to the radiation-effects community, because of their analogy to space environments. There is growing interest in pulsed-laser experiments because they are less expensive than heavy-ion experiments, and are non-destructive to semiconductor devices. By changing the pulsed-laser focus position with respect to the devices under test, sensitive area information can be extracted from either peak current or total collected charge.

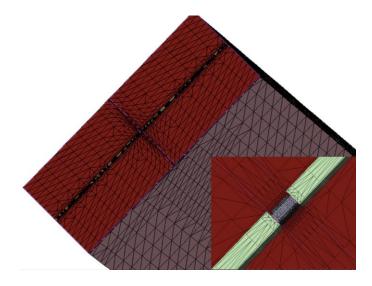

Comparisons of SET sensitivity between FinFETs with various fin widths, FinFETs and planar devices, semi-insulating substrate and silicon substrate devices, and various charge injection locations provide systematic understanding of the charge collection mechanisms in III-V FinFETs. Shunt effects and parasitic bipolar amplification effects typically contribute to charge collection in III-V FinFETs. Device level technology computer aided design (TCAD) simulations were used to provide further insight into the charge collection mechanisms. For pulsed-laser irradiation, plasmonic effects resulting from the nanoscale metal-dielectric-metal geometry of the fin structures may play an important role in the most advanced FinFET technologies and future nanowire technologies. Optical simulations were carried out using the Lumerical optical design tool with finite-difference time-domain (FDTD) analysis. This thesis is organized as follows:

Chapter 2 provides brief background information on relevant topics including MOSFET scaling, III-V MOSFETs, radiation environments, and single-event effects. The basic charge collection mechanisms and shunt effects are discussed in this chapter. Previous SETs investigations on both silicon and III-V MOSFETs are reviewed. Parasitic bipolar amplification effects in III-V MOSFETs are discussed in detail. Plasmonic effects on charge generation are introduced. These background topics provide the foundation to understand the work in the following chapters.

Chapter 3 describes the single-event transient response of InGaAs FinFETs with different fin widths. Both pulsed-laser and heavy-ion irradiation were used to study the scaling effects of InGaAs FinFETs. Devices with wider fins collect more charge in both environments. Quantum-well structures confine charge collection in the channel, and determine the sensitive volume. Simulations show that the charge density produced by irradiation is similar for devices with different fin widths, but more charge is collected by wider fin devices due to the larger channel volume. Charge accumulated in the buffer and substrate layers modulates the body potential, altering the degree of backgate control, leading to additional effects associated with charge accumulation in wider fin devices. Optical simulations for a model system suggest that optical phenomena in the fins should be considered for laser testing. These include optical interference, plasmonic enhancement at the metal–dielectric interfaces, and enhanced electron-hole pair recombination due to multiple reflections in nonplanar devices with nanoscale dimensions.

Chapter 4 describes the plasmonic effect in pulsed-laser induced single-event transients in InGaAs FinFETs. The transient currents in FinFETs and planar MOSFETs with similar stack materials are compared. Enhanced charge collection in the fin region is observed in FinFETs. Plasmonic effects may improve SET sensitivity in the fin region, even with low charge generation efficiency. 3-D TCAD simulations show the transient peaks are mainly due to charge deposition in the channel. The substrate charge collection contributes to the tail current. Optical simulation shows that the enhanced charge deposition in the fin channel is likely due to plasmonic effects. Plasmonic effects may play an important role for pulsed-laser SET characterization of modern CMOS technologies.

Chapter 5 describes the pulsed-laser single-event transient response of InGaAs FinFETs on bulk silicon substrates. Charge collection due to a source-drain shunt effect and drain-to-substrate junction charge collection contribute to the observed transients. The transient response of these silicon substrate devices is compared to that of InGaAs FinFETs on semi-insulating substrates. Faster transients with reduced peak currents and peak widths are observed on the silicon substrate devices. Simulations show hole collection by the silicon substrate. This reduces the amount of source-barrier lowering and bipolar-amplification relative to other III-V devices. Moreover, the reduced hole lifetime in the GaAs buffer layer also contributes to the relative reduction of the bipolar amplification in these devices.

Chapter 6 summarizes the conclusions of the dissertation.

## Chapter 2

## Background

## 2.1 MOSFET scaling

MOSFET scaling is best described by Moore's law that the transistor density and performance of integrated circuits doubles every year [1], which was revised to doubling every two years later [19].

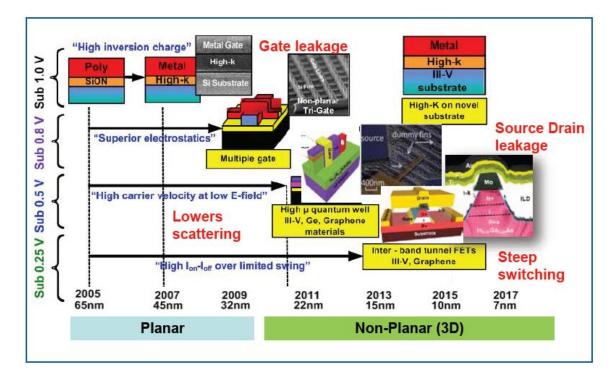

Fig. 2.1. Trend in state-of-the-art high performance (HP) CMOS transistor innovation. Transformative changes in materials (high-k dielectric, Ge, III-V channel) and the transistor architecture (3D, Tunnel FET) being implemented and explored to maintain historical rate of performance, density and power scaling [20].

However, it is becoming more and more challenging to follow the roadmap as the transistor feature size moves to the nanometer region. Several transformative changes in materials and transistor architecture have been implemented and explored to maintain MOSFET scaling, as shown in Fig. 2.1 [20]. Strain engineering was introduced in the 90 nm node to increase both electron and hole mobility [21],

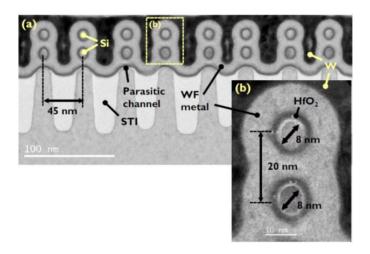

[22]. Metal-gate/high-k gate stacks were introduced in the 45 nm node to reduce the gate leakage and eliminate poly-silicon depletion [23], [24]. The FinFET technology was introduced in the 22 nm node for combating short channel effects [25]-[27]. Vertically stacked gate-all-around (GAA) Si nanowire MOSFETs with excellent short channel characteristics have been developed for the 5 nm node [28]-[30]. GAA architectures offer optimal electrostatic control, thereby enabling ultimate CMOS device scaling [31]. Functional ring oscillators based on GAA MOSFETs have also been manufactured by imec [32]. Fig. 2.2 shows the cross-sectional TEM images of a GAA MOSFET [28]. The devices show excellent short-channel characteristics (SS = 65 mV/dec, DIBL = 42 mV/V) at performance levels comparable to finFET reference devices [28].

Fig. 2.2. TEM images of an NMOS GAA Si NWFET ( $L_G = 70$  nm): (a) overview of the Si NW array, and (b) detailed view of two stacked Si NWs. The rounded NW shape, the narrow NW size distribution, and the conformally deposited HK/MG layers are clearly visible [28].

## 2.2 III-V MOSFETs

MOSFET scaling has progressed for decades, but is now limited by power constraints as the power density dissipated by logic chips hits around 100 W/cm<sup>2</sup> [33]. Power density cannot increase much further without incurring substantial packaging and cooling costs. Continued MOSFET scaling will require a reduction in the operating voltage, but this will compromise switching speed [4]. The III-V compound

semiconductors with superior transport properties provide a promising solution to the continued scaling.

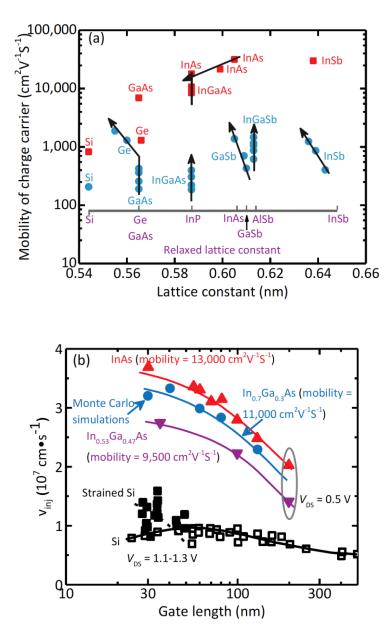

Fig. 2.3 (a) Electron and hole mobility of group III-V compound semiconductors. Electron mobility is marked red and hole mobility is in blue. The arrow indicates the increase of biaxial compressive strain. (b) Electron injection velocity in III-V compound semiconductors [4].

The low field carrier mobility and electron injection velocity of III-V compound semiconductors are shown in Fig. 2.3 [4]. In InGaAs or InAs, the electron mobility is more than 10 times higher than in

silicon at a comparable sheet charge density. For sub-10 nm technology, transistors are operating in the quasi-ballistic region, where carriers experience few scattering events [34]. The drive current,  $I_{on}$ , is affected by the injection velocity,  $v_{inj}$  [35]:

$$I_{on} \propto v_{inj} Q_i \approx v_{inj} C_i (V_{gs} - V_t)$$

(2.1)

$Q_i$  gives the inversion layer charge, and  $V_{gs}$ - $V_t$  is the gate overdrive. The injection velocity of III-V materials is more than twice that of comparable silicon MOSFETs at less than half the voltage. As a result, III-V compound semiconductors are promising materials for sub-10 nm technology.

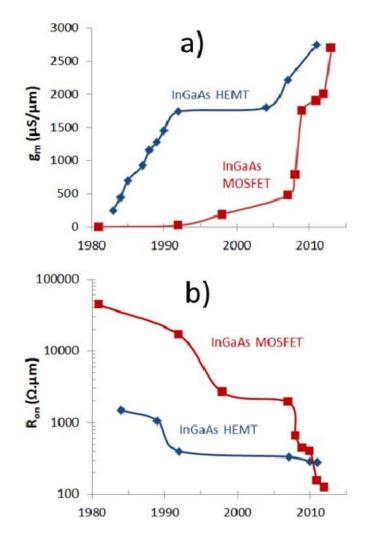

Two main architectures of III-V FETs have been developed, High-Electron Mobility transistors (HEMTs) and MOSFETs. HEMTs made persistent progress since their invention, and have also been turned into a successful transistor technology [36]. Unlike the commercialized silicon MOSFETs and III-V HEMTs, there little progress was made on III-V MOSFETs before the mid-2000s. The initial attempt to fabricate III-V MOSFETs goes back to the 1960s [37]. Unlike the nearly perfect interface between SiO<sub>2</sub> and Si, there are no ideal native oxides for III-V compounds. Recent advances in atomic layer deposition (ALD) of high  $\kappa$  dielectric materials have provided the technology to address this challenge [5],[6]. In order to obtain high quality interfaces to reduce scattering, InGaAs or InAs channels sandwiched between barriers forming high performance quantum-well MOSFETs have been developed [7]. Similar to silicon technology, both InGaAs FinFETs [8]-[11] and InGaAs gate-all-around nanowire transistors [12]-[14] have been developed to reduce short channel effects. InGaAs MOSFETs have now matched transconductance and better ON-resistance compared with InGaAs HEMTs as shown in Fig. 2.4 [36].

Fig. 2.4. Performance comparison of inversion-type InGaAs MOSFETs and HEMTs (with InAs composition between 0 and 1) vs. year: (a) transconductance, (b) ON resistance [36].

#### 2.3 Radiation environments

Typical radiation environments can be divided into space environments, atmospheric environments, and nuclear reactor environments. Detailed discussions on radiation environments can be found in [2], [38]. All studies in this dissertation are within the scope of space and atmospheric radiation environments; nuclear reactor environments are not discussed in this dissertation.

One of the main source of energetic particles in space environments are particles trapped in the Earth's radiation belts, including electrons, protons, and heavy-ions and cosmic rays, including protons

and heavy-ions. For space applications, devices have to withstand radiation exposure. SEEs are one of the most important issues need to be considered for modern technologies. SEEs are caused when highly energetic particles (e.g., protons, neutrons, alpha particles, or other heavy ions) strike sensitive regions of a microelectronic circuit [3]. They may cause nondestructive effects such as single-event upset (SEU), single-event transients (SET) or potential destructive effects such as single-event latchup (SEL). The physical origin of SEE comes from the charge released by ionizing radiation.

Fig. 2.5. The charged particles trapped by the Earth's magnetosphere [38].

Fig. 2.6. Relative abundance of the elements from hydrogen to the iron group [39].

The particle distributions in the Earth's belts are shown in Fig. 2.5 [38]. Cosmic rays including the galactic cosmic rays and solar cosmic rays include protons and heavy ions. The galactic cosmic ray flux consists mostly of protons and alpha particles. Fig. 2.6 shows the abundance distribution of the elements of the galactic cosmic rays [39]. The solar cosmic rays show similar distributions [39].

As cosmic rays enter the top of Earth's atmosphere, they interact with nitrogen and oxygen atoms and produce a "shower" of secondary particles including protons, electrons, neutrons, heavy-ions, muons, and pions [2], among which neutrons are the most important product. Neutrons can affect avionics through SEEs due to nuclear interactions. The neutron induced SEE rate increases with altitude and latitude [40].

Even for terrestrial level applications, SEEs can play an important role in microelectronic circuits. The energetic particles can interact with back end of line (BEOL) materials, which leads to secondary particles through nuclear reactions [41], [42]. The secondary particles can produce single-event upset in a hardended SRAM [42]. This may produce serious reliability issues for modern technologies, even for terrestrial applications.

#### **2.4 Single-Event Effects**

#### 2.4.1 Charge deposition

When an energetic particle passes through a semiconductor device, it will lose energy through Coulomb scattering. The energy loss per unit path for a particle is described by linear energy transfer (LET) [3]:

$$LET = \frac{1}{\rho} \frac{dE}{dx}, \quad MeV \cdot cm^2 / mg$$

<sup>(2.2)</sup>

where  $\rho$  is the material density. In silicon, an LET of 97  $MeV \cdot cm^2 / mg$  corresponds to a charge deposition of 1  $pC / \mu m$ . The energy loss generates excess electron-hole pairs in semiconductor

materials.

Another efficient way to inject excess electron-hole pairs in a semiconductor is through single-photon absorption (SPA) if the photon energy is above the bandgap [43], or two-photon absorption (TPA) if the photon energy is subbandgap [44]. Semiconductor devices are usually irradiated from the backside to avoid the reflections from metal contacts on top. The sensitive area is typically located near the channel region at the surface. The substrates are usually hundreds of µm thick, which produces a serious absorption problem for SPA. Fig. 2.7 shows the room temperature absorption spectrum of silicon in the visible and near-infrared regions [44]. There is very low absorption in the subbandgap region. At sufficiently high intensities, the material can absorb two photons simultaneously to generate a single electron-hole pair.

Fig. 2.7. Room temperature absorption spectrum of silicon in the visible and near-infrared region of the spectrum illustrating the common laser wavelengths used for above-bandgap single-event effects measurements and also that for the subbandgap experiment [44].

In TPA, the energy deposited in materials is quadratically dependent on the laser irradiance [45], [46]. Therefore, the carrier generation occurs only in the focused region with high irradiance. This enables 3-D mapping of the SEE sensitivity for a device or a circuit. The following equations show the pulse propagation and charge deposition in a semiconductor material [45], [46]:

$$\frac{dI(r,z)}{dz} = -\alpha I(r,z) - \beta_2 I^2(r,z) - \sigma_{ex} NI(r,z)$$

(2.3)

$$\frac{d\Phi(r,z)}{dz} = \beta_1 I(r,z) - \gamma_1 N(r,z)$$

(2.4)

$$\frac{dN(r,z)}{dz} = \frac{\alpha I(r,z)}{\hbar\omega} + \frac{\beta_2 I^2(r,z)}{2\hbar\omega}$$

(2.5)

where *I* is the laser intensity, *N* is the density of free carriers,  $\Phi$  is the phase,  $\alpha$  is the single-photon absorption coefficient,  $\beta_2$  is the two-photon absorption coefficient which is proportional to the imaginary part of  $\chi^{(3)}$  (the third-order nonlinear-optical susceptibility),  $\sigma_{ex}$  is the absorptivity of generated free carriers,  $\beta_1$  is proportional to the real part of  $\chi^{(3)}$ ,  $\gamma_1$  describes the refraction due to free carriers, and *z* is the depth in the material.

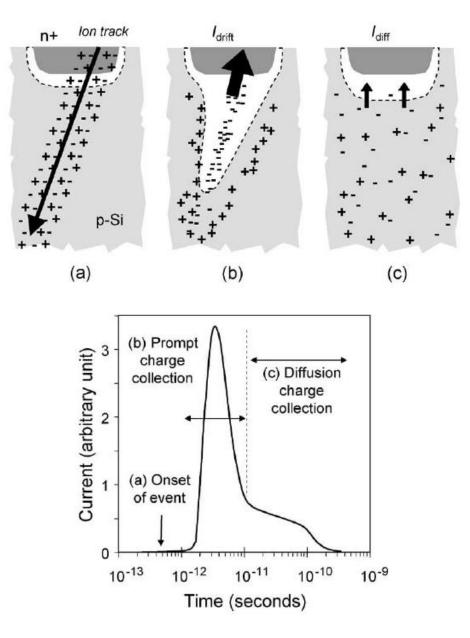

#### 2.4.2 Charge collection mechanism

Once the free carriers are generated either by energetic particles or photons, they can be collected by the terminals at specified bias conditions. The most sensitive regions are reverse-biased p-n junctions due to the high electric field presented in the depletion region. Fig. 2.8 shows the single-event transient by high energy ions and the subsequent charge collection through drift and diffusion in a reverse biased p-n junction [47]. The figure also shows a typical time-dependent current at a struck p-n junction. The figure shows clearly a short-term charge collection process dominated by drift, which contributes to the peak, and a relatively slow process dominated by diffusion, which contributes to the tail.

It is worthwhile to mention that in Fig. 2.8 (b), the electrostatic field is disturbed by the free carriers generated along the ion path, which was termed a "field funnel" [48]. This funneling effect extends the sensitive region from the initial depletion region deep into the substrate, and more carriers will be collected.

Fig. 2.8. Charge generation and collection phases in a reverse-biased junction and the resultant current pulse caused by the passage of a high-energy ion [47].

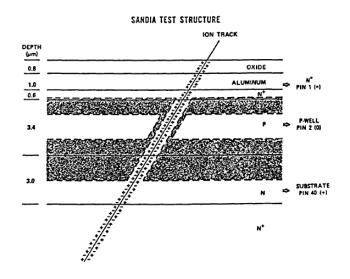

## 2.4.3 Shunt effect

As technology scales, transistor size reduces such that multiple junctions can be disturbed by energetic particles and photons. A transient conductive path may connect two adjacent junctions due to the high density of free carriers, which was termed a "shunt effect" [49]. Fig. 2.9 shows the schematic of

an ion track shunt effect in a multilayer structure. The high density ion track penetrates both junctions, forming a highly conductive ohmic-like region, and the junction charge collection cannot be considered independently. For most advanced technologies, the shunt effect will form a conductive path along the channel, forming a source-drain conduction current, which contributes to the transient current [50]-[57].

Fig. 2.9. Illustration of ion track shunt effect in two-junction experimental structure [49].

#### 2.4.4 Single-event transient in silicon MOSFETs

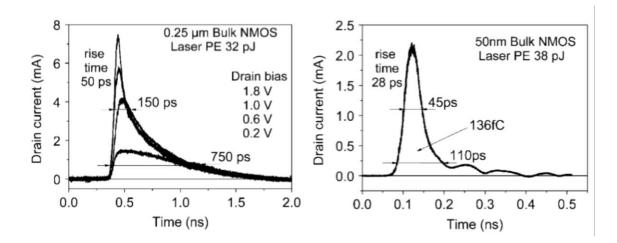

As technology scales, modern IC's vulnerability to SEE increases as the sensitive volume decreases dramatically. Fig. 2.10 shows the transient drain currents induced by pulsed laser irradiation in 0.25 µm NMOS and 50 nm NMOS transistors [58]. With comparable pulsed laser irradiation, the smaller device shows smaller peak current with narrower peak width.

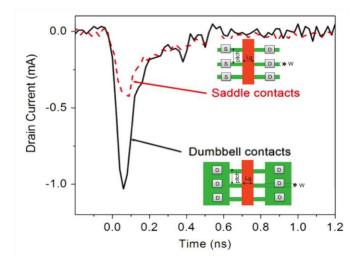

The transient response of silicon FinFETs has been explored with both laser and heavy ion experiments [50]-[53]. As the active channel volume decreases, the charge collection in the drain region masks the contributions of the fins [52], [53]. Fig. 2.11 shows the transient drain current with different contact type [53]. A device with larger contact area shows larger drain current. The drain (or source) to substrate junction charge collection contributes significantly in modern technologies. Improving the drain region design provides an effective radiation hardening technique for future technologies.

Fig. 2.10. Transient drain currents induced by pulsed laser irradiation in 0.25 µm NMOS and 50 nm NMOS transistors [58].

Fig. 2.11. Drain current induced by heavy ion irradiation in bulk FinFETs with different contact type. Solid (black) curve is the largest transient curve that was recorded in a FinFET ( $W_f/L = 20/70$ ) with dumbbell contacts. The dashed (red) curve is the largest current transient recorded in a FinFET ( $W_f/L = 20/60$ ) with saddle contacts [53].

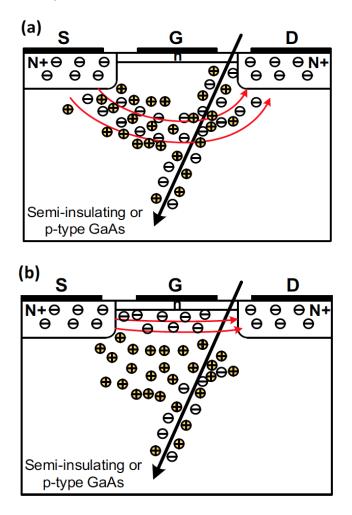

#### 2.4.5 Bipolar amplification effect

A significant amount of research focused on SEEs in III-V FETs has been reported [54], [55], [59]-[66]. III-V MOSFETs are found to be more sensitive to SEE compared with Si counterparts. One important reason is the charge enhancement in III-V FETs. Fig. 2.12 illustrates the charge enhancement

mechanism in a GaAs FET [63]. During an ion strike, a high density of e-h pairs is generated along the ion track. The electrons are quickly collected, while holes remain in the active region due to larger effective mass. Holes accumulated near the source reduce the conduction barrier from source to substrate, causing electron injection from source to substrate, and are collected by the drain, which is similar to a bipolar transistor biased at forward active condition. In addition, holes beneath the channel act as a back gate, creating a source-drain current path as long as the excess hole density is present. These charge enhancement effects, unknown as bipolar amplification effects, result in amplification, causing more charge to be collected than was generated.

Fig. 2.12. Schematic diagram illustrating (a) the bipolar gain and (b) channel-modulation charge enhancement mechanisms that contribute to the charge collection processes of GaAs FETs [63].

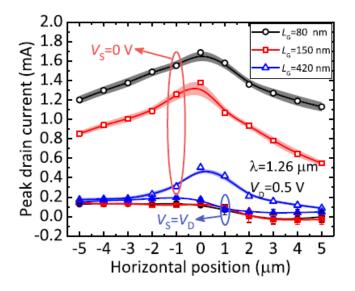

Charge enhancement has been observed in all different kinds of III-V FETs, including III-V MESFETs and HEMTs [63], surface-channel GaAs MOSFETs [66], planar quantum-well InGaAs MOSFETs [65], and quantum-well InGaAs FinFETs [54], [55]. Fig. 2.13 shows the SEE sensitivity dependence on gate length scaling of InGaAs FinFETs [54]. The peak drain current is inversely proportional to the gate length due to the suppressed bipolar amplification effect in long channel devices.

Fig. 2.13. Peak drain current along a line scan for different gate lengths. The laser wavelength  $\lambda = 1260$  nm. The shadow represents the standard deviation among the 50 transients recorded at each position.  $V_G - V_{TH} = 0$  V.  $W_{FIN} = 30$  nm. Laser pulse energy is 0.65 ±0.01 nJ [54].

#### 2.4.6 Plasmonic effects

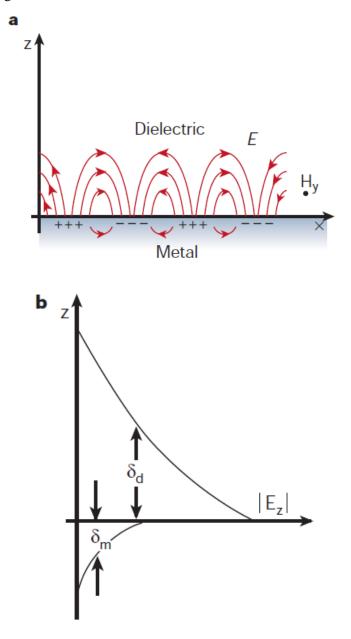

Plasmonic effects have been widely investigated in the nano-photonic community, while it has not attracted much attention from the radiation community. As MOSFETs move from planar to 3-D FinFET structures starting from the 22 nm technology node, the plasmonic effect in the narrow fin structures during pulsed-laser experiments may not be ignored. When a pulsed-laser irradiates a nanoscale metal-dielectric interface, the free electrons at the interface between the metal and dielectric medium will oscillate, typically known as "surface plasmons" [67]. Fig. 2.14 shows a surface plasmon at the interface between a metal and a dielectric material [67]. As shown in Fig. 2.14 (a), the electric field component is

normal to the surface. The electric field is maximum at the surface and decays exponentially into both the metal and dielectric material, as shown in Fig. 2.14 (b). The decay length of the field is of the order of half the wavelength of light involved.

Fig. 2.14. (a) Schematic of surface plasmons at the interface between a metal and a dielectric material. (b) The field component perpendicular to the surface being enhanced near the surface and decaying exponentially with distance away from it [67].

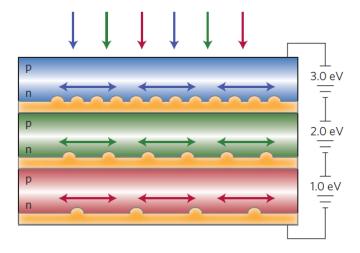

In nanostructures, such as fins in a FinFET, the field is enhanced as the decay length is large compared with the nanostructures. Strong enhanced electric field will be observed in the nanostructures. This plasmonic enhancement effect has been widely used in nanoscale photonic waveguides [68], [69], modulators [70], photovoltaics [71], [72], Raman spectroscopy [73], [74], and biosensing[75], [76]. Fig. 2.15 shows plasmonic solar-cell design [71]. The plasmonic scattering and coupling by the nanostructure helps improve the solar-cell efficiency. These nano-structures are very similar to fin structures in a FinFET.

Fig. 2.15. Plasmonic tandem solar-cell geometry. Semiconductors with different bandgaps are stacked on top of each other, separated by a metal contact layer with a plasmonic nanostructure that couples different spectral bands of the solar spectrum into the corresponding semiconductor layer [71].

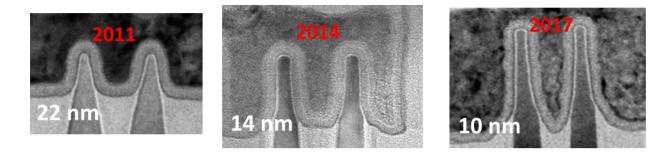

Fig. 2.16. FinFETs evolution in Intel from 22 nm node to 10 nm node [78].

The FinFET technology was first introduced in 2001 by Hu, et al. from the University of California, Berkeley [77]. It is now the mainstream technology. Fig. 2.16 shows the FinFET structure in Intel from 22 nm node to 10 nm node [78]. It is a metal/dielectric/metal stack along the fin width direction. Surface plasmons may be generated along the metal dielectric interface during pulsed-laser SET experiments. The fin width in Intel's 10 nm technology is 7 nm, which is much smaller compared with the electric field decay length. Strong electric field enhancement due to surface plasmons may enhance the charge deposition inside the narrow fin region.

There has been much effort to convert measurable pulsed-laser energy to equivalent LET in order to make comparisons with heavy-ion experiments [79]. One efficient way is to compare the transient shapes from pulsed-laser and heavy-ion irradiation experimentally. The correlation between these two types of experiments strongly depends on the facilities and the experiment conditions. The other path is to use theoretical calculations to predict the pulsed-laser induced carrier generation, and convert the charge deposition to equivalent LETs [80], [82]. Optical effects, such as plasmonic effects, may be incorporated into the calculations to improve the accuracy.

#### Chapter 3

#### Scaling effects on single-event transients in InGaAs FinFETs

## **3.1 Introduction**

Incorporation of compound semiconductors is a promising candidate to address scaling challenges beyond the 7 nm node due to their outstanding electron transport properties [4]. Their high electron mobility and high frequency response make these devices an ideal option for many space applications [4], [59], [60]. A significant amount of research focuses on single-event effects in these devices [59]-[66]. Most of these works consider III-V planar MESFETs and HEMTs. Only limited work describing the SEE response of III-V FinFETs has been reported. InGaAs and Ge complementary FinFET technology is promising for next generation NMOS/PMOS FETs. Recent work suggests that SEE in circuits built in this technology are likely to be dominated by ion strikes on the InGaAs FinFET [54].

Fin geometry is optimized for device electrical performance and manufacturability of a given process. Dimensions can scale as process generations scale, and vary among manufacturers and even within a single process [4]. From the 22-nm technology node to the 10-nm technology node, fin height increases while fin width decreases [78]. The gate length dependence of the single-event transient response of InGaAs FinFETs has been evaluation by Ni et al. using a high-speed pulsed-laser system [54]. The peak drain current was found to increase as the gate length decreased, which suggests that parasitic bipolar action is fully suppressed in longer channel devices [54]. In this chapter, we evaluate the impact of fin width on the SET response of InGaAs FinFETs via pulsed-laser and heavy-ion irradiation. Over all, the trends observed in pulsed-laser irradiation are consistent with those of heavy-ion irradiation. However, there are a few differences. In both situations, devices with wider fins collect more charge, due to their greater sensitive volumes. Charge accumulated in the buffer and substrate modulates the body potential, leading to additional charge collection in wider fin devices. Finite-difference time-domain simulations for a model system carried out using Lumerical [83] show that optical intensity is modulated inside narrow fins during laser irradiation. As technology scales, this optical modulation is important to consider.

## 3.2 Device structure and experimental setup

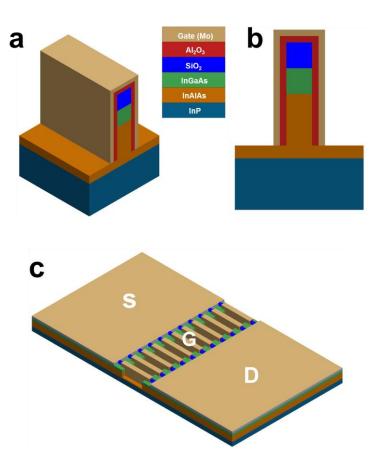

Fig. 3.1. (a) 3D qualitative representation of the fin structure of the InGaAs double-gate FinFETs, (b) cross-section along the fin width direction, and (c) 3D schematic diagram of 11 fin InGaAs double-gate FinFETs. Gate (G), drain (D), and source (S) are labeled on the diagram. (Not drawn to scale)

The device under test is a double-gate InGaAs FinFET [84]. A 3D qualitative view of the device is shown in Fig. 3.1c; layers are not drawn to scale. Details of the fin structure are shown in Fig. 3.1a. Fig. 3.1b shows a cross-sectional diagram along the fin width direction of a single fin structure. There are 11 fins in parallel for each device, with 0.8  $\mu$ m pitch between fins. The height of each fin is 220 nm, with a 40 nm thick In<sub>0.53</sub>Ga<sub>0.47</sub>As channel layer, and the gate length is 100 nm for all devices reported here. Under the channel, a 0.4- $\mu$ m In<sub>0.52</sub>Al<sub>0.48</sub>As buffer layer is grown on a 600- $\mu$ m semi-insulating InP substrate. 40 nm of SiO<sub>2</sub> serves as a hard mask, which electrostatically decouples the top gate from the

channel. As a result, devices are only controlled by the two side gates. A 5-nm Al<sub>2</sub>O<sub>3</sub> gate dielectric is deposited by atomic layer deposition. A silicon delta doping layer 5 nm below the channel is used to enhance channel electron density. The detailed fabrication process is described in [10]. Fig. 3.2a and b show the energy band diagrams in the fin width and fin height directions, respectively.

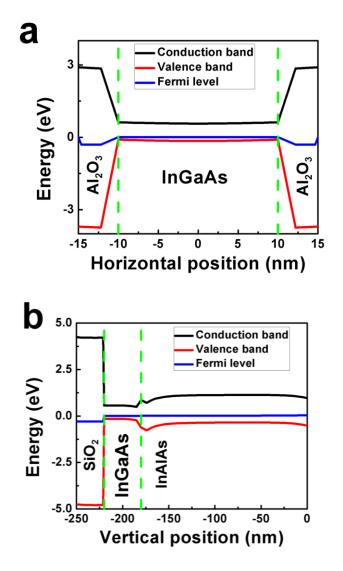

Fig. 3.2. Band diagrams cut through the fin structure along the (a) fin width direction and (d) fin height direction.

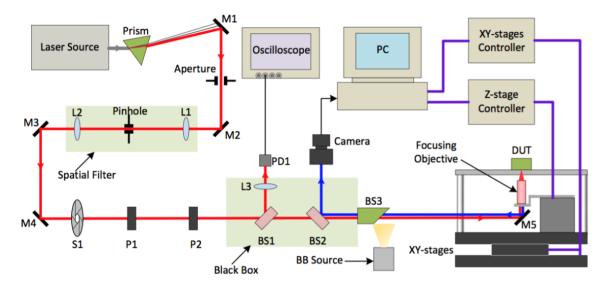

Fig. 3.3. A simplified block diagram of TPA test setup. In the figure, 'L' stands for lens, 'M' stands for mirror, 'S' stands for shutter, 'P' stands for polarizer, 'BS' stands for beam splitter, 'PD' stands for photodiode, and "BB" represents the broadband light source. The red line indicates the optical path traveled by the laser beam. The blue line indicates the reflected light that is imaged by the near infrared camera [54].

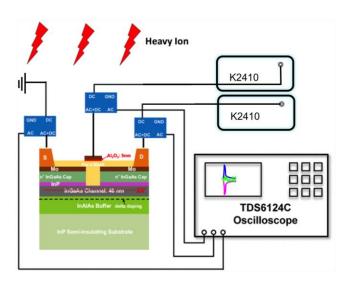

Fig. 3.4. Schematic diagram of the heavy-ion experiment setup. Two Keithley 2410 working as SMUs for gate and drain terminals. The source terminal is grounded by a 50  $\Omega$  terminator.

Devices with different fin widths were tested with both pulsed-laser and heavy-ion irradiations. A tunable wavelength laser system and high resolution transient capture system are used for laser testing.

The pulsed-laser testing experiments were performed at Vanderbilt University. The laser system setup is shown in Fig. 3.3. The laser system generates 150 fs pulses with 1 kHz repetition rate. The laser wavelength in this experiment is 1260 nm with spot size of approximately 1.2  $\mu$ m [85]. As shown in Fig. 3.3, the devices under test (DUTs) are irradiated from the backside by focusing the pulsed-laser spot such that the channel region is contained within the charge generation region from the laser pulse. The heavy-ion experiments were performed with the 88 inch cyclotron at Lawrence Berkeley National Laboratory (LBNL). Fig. 3.4 shows the schematic diagram of the experiment setup.

Fig. 3.5. Brass high-speed packages for pulsed-laser experiments (top) and heavy-ion experiments (bottom).

Transients are captured using a Teledyne Lecroy LabMaster 10-36Zi-A oscilloscope with 36-GHz front-end bandwidth and 80 GS/s sampling rate for pulsed-laser experiments and a Tektronix TDS6124C oscilloscope with 12 GHz front-end bandwidth and 20 GS/s-sampling rate for heavy-ion experiments. The DC bias is supplied with a semiconductor parameter analyzer, HP 4156A, for pulsed-laser experiments

and Keithley 2410 for heavy-ion experiments, through bias tees with 50-GHz bandwidth. The DUTs are mounted and bonded in a brass high-speed package with RF connectors [86]. Fig. 3.5 shows the InGaAs FinFETs mounted on high-speed packages used in the pulsed-laser experiments and heavy-ion experiments.

## 3.3 Experimental results and discussion

#### 3.3.1 Pulsed-laser induced charge generation

The pulsed-laser wavelength used in the experiment is 1260 nm, corresponding to a photon energy of 0.98 eV, which is above the band gap of  $In_{0.53}Ga_{0.47}As$ . Table 3.1 lists the charge generation mechanisms in the materials used in the devices. Both two-photon absorption (TPA) and single-photon absorption (SPA) mechanisms contribute to charge generation in the InGaAs channel, while only TPA contributes to charge generation in the InAlAs and InP layers.

| Material                                 | Band gap (eV) | Photon absorption |  |

|------------------------------------------|---------------|-------------------|--|

|                                          |               | mechanism         |  |

| In <sub>0.53</sub> Ga <sub>0.47</sub> As | 0.75          | SPA/TPA           |  |

| $In_{0.52}Al_{0.48}As$                   | 1.46          | TPA               |  |

| InP                                      | 1.35          | TPA               |  |

Table 3.1. Charge generation mechanism for 1260 nm laser

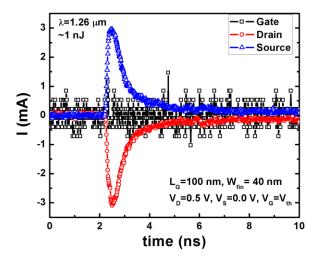

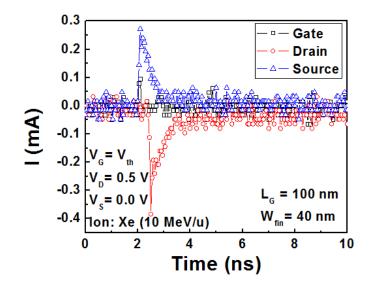

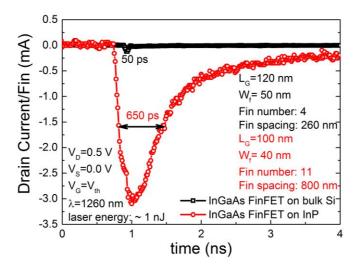

Fig. 3.6 shows a typical laser-induced transient for a pulse delivered to the center of a device with fin width of 40 nm under a bias condition of  $V_D = 0.5$  V,  $V_S = 0$  V, and  $V_G = V_{th}$ , where  $V_{th}$  is the threshold voltage of the devices with initial value in the range of -0.1 ±0.1 V. The spot size of the incident Gaussian beam is approximately 1.2 µm, as determined via a typical knife-edge measurement at the beam waist [85]. The maximum peak current is achieved when the center (maximum intensity) of the laser spot is located on the fin. The radius of the spot (0.6  $\mu$ m) is smaller than the fin pitch (0.8  $\mu$ m), which localizes the irradiation on a single fin. Transient signals are recorded mainly on the drain and source; the peak gate current is negligible. This occurs because, across the fin width direction, the InGaAs channel and  $Al_2O_3$ gate dielectric form a deep type-I quantum-well. Along the fin height direction, the InGaAs channel, InAlAs buffer, and SiO<sub>2</sub> also form a type-I quantum-well, as shown in Fig. 3.2a and b. Thus, carriers generated by irradiation are confined in the channel layer once they have been collected. This makes the channel layer critical to the charge collection. The transients on drain and source are symmetric for various strike locations, which suggests the transient current comes mainly from channel collection. There is a tail (compared with the prompt peak current) on the transient signal, which is consistent with previous work on planar III-V MOSFETs [65] and FinFETs [54]. The tail current in Fig. 3.6 is mainly caused by charge collection from the substrate. Charge generated more deeply within the substrate leads to a longer time for carriers to transport into the channel. This response differs significantly from bulk Si FinFETs, where no tail current is observed within the transient signal [52]. This is because most deposited charge in the substrate of a Si bulk FinFET is collected by the substrate contact through the conductive substrate, instead of the source or drain. All peak drain currents in this chapter are reported as absolute values. For both laser and heavy ion tests, the total collected charge is based on integration of current vs. time beginning and ending at 10% of the peak value.

Fig. 3.6. SET captured during TPA testing for an InGaAs FinFET.  $L_G = 100$  nm,  $W_f = 40$  nm.

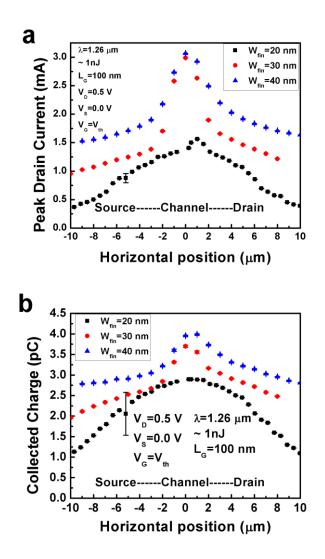

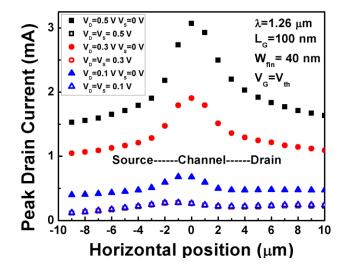

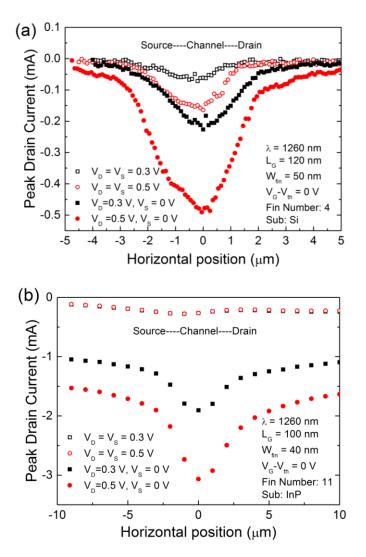

Figs. 3.7a and b show peak drain current and collected charge along a line scan from source to drain for devices with different fin widths. There is some spatial asymmetry; the peak drain current is higher when the laser is on the drain side, due to the higher electric field on the drain side. Both the peak drain currents and collected charge for narrower fin devices ( $W_{fin} = 20$  nm) are much smaller compared with wider fin devices ( $W_{fin} = 30$  nm and 40 nm).

Fig. 3.7. Peak drain current (a) and drain collected charge (b) along a line scan for InGaAs FinFETs of different fin widths during TPA testing.

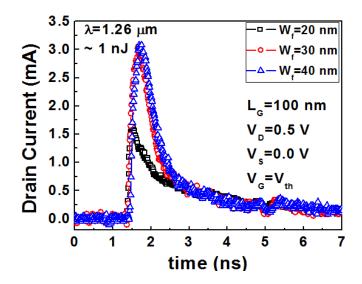

Fig. 3.8. Drain current transients for InGaAs FinFETs of different fin widths during TPA testing (peak drain current is taken as absolute value). The laser strike is at the center of the gate.

Fig. 3.9. Peak drain current along a line scan at different drain bias during TPA testing.  $W_f = 40$  nm,  $L_G = 100$  nm.

A comparison of drain current transients for devices with different fin widths is shown in Fig. 3.8. For the 20 nm fin width device, peak currents are much smaller than for 30 nm or 40 nm fin widths. The tails of the transients overlap for all three devices, because all devices have the same substrate material and geometry, leading to similar charge collection from the substrate in all cases. Charge collection of the charge injected in the channel produces the prompt increase in current. Even though all transients have similar tails, the integrated collected charge is much smaller for the 20 nm devices due to the lower peak current.