# IMPACT OF DESIGNER-CONTROLLED PARAMETERS ON SINGLE-EVENT RESPONSES FOR FLIP-FLOP DESIGNS IN ADVANCED TECHNOLOGIES

By

# Hangfang Zhang

#### Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

### DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

May 11, 2018

Nashville, Tennessee

## Approved:

Bharat L. Bhuva, Ph.D.

Lloyd W. Massengill, Ph.D.

Ronald D. Schrimpf, Ph.D.

Daniel M. Fleetwood, Ph.D.

Marcelo M. Disconzi, Ph.D.

Copyright © 2018 by Hangfang Zhang

All Rights Reserved

#### **ACKNOWLEDGMENTS**

With a long way coming here, I am really grateful to many people, without whom the completion of this work would not have been possible.

First of all, I would like to express my thanks to advisor, Dr. Bharat L. Bhuva. He has been a responsible and valued advisor throughout my graduate years. His availability, guidance, patience and encouragement during research are vitally important for my progress and discoveries. I would also like to thank my other committee members for their time and effort for reviewing papers and providing insightful advices to my dissertation. Dr. Massengill has always been provides fresh perspectives for my research work which allows improvement for all the work. Dr. Schrimpf has helped me get deeper understanding of underlying mechanisms for devices with profound knowledge. Dr. Fleetwood has been a valued academic advisor and instructed me with patience and carefulness during my first academic year. Dr. Disconzi has provided insightful thoughts for my dissertation and has been so kind to shuffle schedule for my defense.

I would also like to express my thanks to the faculty and students in RER group of Vanderbilt University for their valuable discussions, insights and instructions on theories, simulations and experiments. The friendship and happy moments are precious memories and I really appreciate your company.

At last, I would like to thank my family, who have always been supportive for me. My parents and husband trust me and respect all my decisions, letting me pursuing my goal without worries behind. Their love, support and encouragement have provided me with inexhaustible motivations for my graduate studies.

# TABLE OF CONTENTS

|                                                                                   | Page  |

|-----------------------------------------------------------------------------------|-------|

| ACKNOWLEDGMENTS                                                                   | . iii |

| LIST OF TABLES                                                                    | . vii |

| LIST OF FIGURES                                                                   | . ix  |

| 1 Introduction                                                                    | . 1   |

| 1.1 Key Research Contributions                                                    | . 2   |

| 1.2 Dissertation Organization                                                     | . 4   |

| 2 Background                                                                      | . 6   |

| 2.1 Single-Event Mechanism                                                        | . 6   |

| 2.1.1 Charge Deposition                                                           | . 6   |

| 2.1.2 Charge Collection                                                           | . 8   |

| 2.1.3 Circuit Response                                                            | . 9   |

| 2.2 Threshold Voltage                                                             | . 10  |

| 2.2.1 Previous Results                                                            | . 11  |

| 2.2.2 Theoretical Analysis                                                        | . 12  |

| 2.3 Dual-Well and Triple-Well Structures                                          | . 14  |

| 2.3.1 Previous Results                                                            | . 14  |

| 2.3.2 Charge-Collection Mechanism with Different Well Structures                  | . 16  |

| 2.4 Summary                                                                       | . 19  |

| 3 Effects of Threshold Voltage Variations on Single-Event Upset Responses for Ad- |       |

| vanced Technologies                                                               | . 20  |

| 3.1 Test Circuits and Data Analysis                                               | . 20  |

| 3.1.1 Test Circuits and Setup                                                     | . 20  |

| 3.1.2 SEU Cross-Section and Failure in Time Analysis                              | . 23  |

|   |      | 3.1.3 Simulation Uncertainty                                                   | 24 |

|---|------|--------------------------------------------------------------------------------|----|

|   | 3.2  | Heavy-ion Irradiation                                                          | 26 |

|   |      | 3.2.1 Experimental Details                                                     | 26 |

|   |      | 3.2.2 Experimental Results                                                     | 27 |

|   | 3.3  | Alpha Particle Irradiation                                                     | 29 |

|   |      | 3.3.1 Experimental Details                                                     | 29 |

|   |      | 3.3.2 Experimental Results                                                     | 29 |

|   | 3.4  | Simulations and Discussion                                                     | 31 |

|   | 3.5  | Proton, High-Energy Neutron and Thermal Neutron Irradiation                    | 34 |

|   |      | 3.5.1 Experimental Details                                                     | 34 |

|   |      | 3.5.2 Experimental Results                                                     | 36 |

|   | 3.6  | Frequency Dependence                                                           | 37 |

|   |      | 3.6.1 Experimental Details                                                     | 38 |

|   |      | 3.6.2 Experimental Results for DFF Designs                                     | 39 |

|   |      | 3.6.3 Experimental Results for Logic Circuits                                  | 41 |

|   | 3.7  | Design Guidelines                                                              | 42 |

|   |      | 3.7.1 Simulations for Power Consumption and Gate Delay                         | 43 |

|   |      | 3.7.2 SEU Cross-Sections for DFF with Different $V_T$ options                  | 44 |

|   |      | 3.7.3 Case Study                                                               | 44 |

|   | 3.8  | Summary                                                                        | 47 |

| 4 | Effe | ects of Well Structure on Single-Event Upset Responses for FinFET Technologies | 48 |

|   | 4.1  | Test Circuits                                                                  | 48 |

|   | 4.2  | Heavy-ion Irradiation                                                          | 49 |

|   |      | 4.2.1 Experimental Details                                                     | 49 |

|   |      | 4.2.2 Experimental Results                                                     | 50 |

|   | 4.3  | Alpha Particle Irradiation                                                     | 53 |

|   |      | 4.3.1 Experimental Details                                                     | 53 |

| 4.3.2 Experimental Results                                                       | 53 |

|----------------------------------------------------------------------------------|----|

| 4.4 Simulations and Discussion                                                   | 54 |

| 4.4.1 3D TCAD Simulations for 14/16-nm Bulk FinFET Technology                    | 54 |

| 4.4.2 Comparison between Planar and FinFET technologies                          | 59 |

| 4.5 Summary                                                                      | 60 |

| 5 Stability of Designer-Controlled Parameter Effects against Temperature and An- |    |

| gular Incidence                                                                  | 62 |

| 5.1 Temperature Effects                                                          | 62 |

| 5.1.1 Background                                                                 | 63 |

| 5.1.2 Simulations and Implications                                               | 64 |

| 5.1.3 Experimental Details                                                       | 68 |

| 5.1.4 Experimental Results                                                       | 69 |

| 5.2 Angular Effects                                                              | 72 |

| 5.2.1 Background                                                                 | 73 |

| 5.2.2 Angular Effects Analysis from Geometry View                                | 74 |

| 5.2.2.1 Angular Effects on a planar transistor                                   | 74 |

| 5.2.2.2 Angular Effects on a FinFET transistor                                   | 76 |

| 5.2.3 Simulations and Discussion                                                 | 78 |

| 5.2.4 Experimental Details                                                       | 81 |

| 5.2.5 Experimental Results                                                       | 81 |

| 5.3 Summary                                                                      | 86 |

| 6 Conclusion                                                                     | 88 |

| BIBLIOGRAPHY                                                                     | 91 |

# LIST OF TABLES

| Table |                                                                                            | Page |

|-------|--------------------------------------------------------------------------------------------|------|

| 3.1   | 10 MeV/nucleon Cocktail Components                                                         | . 26 |

| 3.2   | 16 MeV/nucleon Cocktail Components                                                         | . 27 |

| 3.3   | Percentage Change in SET PW and FD relative to ULVT Design for 20-nm                       |      |

|       | Node                                                                                       | . 32 |

| 3.4   | Percentage Change in SET PW and FD relative to ULVT Design for 14/16-                      |      |

|       | nm Node                                                                                    | . 33 |

| 3.5   | Thermal Neutron Flux and Fluence in Tests                                                  | . 36 |

| 3.6   | Normalized FIT for DFF with Different $V_T$ Options with Exposure to Pro-                  |      |

|       | tons, High-Energy Neutrons and Thermal Neutrons                                            | . 37 |

| 3.7   | Normalized Slope of SEU Cross-Section Curve of DFFs                                        | . 39 |

| 3.8   | Normalized Slope of SEU Cross-Section Curve of Comparator Logics                           | . 41 |

| 3.9   | Power Consumption (nW) for DFF with Different $V_T$ Options across Sup-                    |      |

|       | ply Voltage and Frequency                                                                  | . 43 |

| 3.10  | Gate Delay (ps) for DFF with Different $V_T$ options across Supply Voltage                 | . 44 |

| 3.11  | Alpha-Particle-Induced SEU cross-Section ( $\times 10^{-11}~cm^2/FF$ ) for DFF with        |      |

|       | Different $V_T$ Options across Supply Voltage at 2.5 MHz                                   | . 45 |

| 3.12  | $^{124}Xe^{+43}$ -Induced SEU cross-Section ( $\times 10^{-9}~cm^2/FF$ ) for DFF with Dif- |      |

|       | ferent $V_T$ Options across Frequency at Nominal Supply Voltage                            | . 45 |

| 3.13  | Case Study 1                                                                               | . 45 |

| 3.14  | Case Study 2                                                                               | . 46 |

| 3.15  | Case Study 3                                                                               | . 46 |

| 4.1   | 10 MeV/nucleon Cocktail Components                                                         | . 49 |

| 4.2   | Charge Collection of Dual- and Triple-Well OFF-State NMOS Inverters                        |      |

| 4.3 | Charge Collection of Dual- and Triple-Well OFF-State NMOS Inverters for                        |    |

|-----|------------------------------------------------------------------------------------------------|----|

|     | Three Technologies with A Particle Strike (LET = $1 \text{ MeV} \cdot \text{cm}^2/\text{mg}$ ) | 60 |

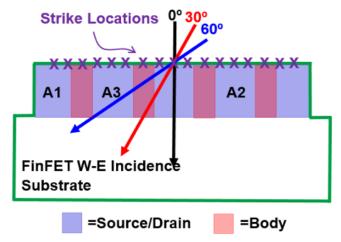

| 5.1 | Upset at Different Strike Locations for W-E Incidence                                          | 80 |

| 5.2 | Upset at Different Strike Locations for N-S Incidence                                          | 80 |

| 5.3 | 10 MeV/nucleon Cocktail Components                                                             | 81 |

# LIST OF FIGURES

| Figu | re                                                                           | Pa | age |

|------|------------------------------------------------------------------------------|----|-----|

| 2.1  | Generation of electron-hole pairs due to an energetic particle strike [30]   | •  | 7   |

| 2.2  | Charge generation and collection phases in a reverse-biased junction and     |    |     |

|      | the resultant current pulse caused by the passage of a high-energy ion [10]. | •  | 8   |

| 2.3  | Simulation of a 5 $MeV \cdot cm^2/mg$ ion strike for a 130-nm SOI off-state  |    |     |

|      | NMOS transistor, either device alone or integrated in a CMOS inverter        |    |     |

|      | chain with mixed-mode simulation. The left axis shows the current drive      |    |     |

|      | and the right axis shows the output inverter voltages of the struck node     |    |     |

|      | [33, 34]                                                                     |    | 9   |

| 2.4  | Schematic design of a conventional D-latch, with an SET pulse caused by      |    |     |

|      | a particle hit and defined feedback loop delay                               |    | 10  |

| 2.5  | Impact of threshold voltage variations on the relative upset probability for |    |     |

|      | a FF design in a 65-nm bulk CMOS technology [43]                             | •  | 12  |

| 2.6  | Impact of threshold voltage variations on DFF SER in a 28-nm bulk CMOS       |    |     |

|      | technology [44]                                                              | •  | 12  |

| 2.7  | Normalized cross-section versus LET for dual-well and triple-well SRAMs      |    |     |

|      | for normal incidence irradiation with a checkerboard pattern in 65-nm, 40-   |    |     |

|      | nm, 28-nm bulk CMOS technologies [51]                                        |    | 15  |

| 2.8  | Normalized alpha-particle-induced MCU SER as a function of voltage for       |    |     |

|      | dual- and triple-well SRAMs in a 28-nm bulk CMOS technology [53]             |    | 16  |

| 2.9  | Structures of dual- and triple-well planar NMOS transistors                  |    | 17  |

| 3.1  | CREST block level design used for evaluating SEU response of FF cells,       |    |     |

|      | after [58]                                                                   |    | 21  |

| 3.2  | C-CREST block level design used for evaluating SEU response of FF and        |    |

|------|------------------------------------------------------------------------------|----|

|      | logic circuits [60]                                                          | 22 |

| 3.3  | SEU characterization test setup                                              | 23 |

| 3.4  | Heavy-ion-induced SEU cross-section as a function of particle LET for 20-    |    |

|      | nm DFF with different $V_T$ values                                           | 28 |

| 3.5  | Heavy-ion-induced SEU cross-section as a function of particle LET for        |    |

|      | 14/16-nm DFF with different $V_T$ values                                     | 28 |

| 3.6  | Flux-Energy Spectrum of 5.4 MeV 10 $\mu$ Ci <sup>241</sup> Am source         | 29 |

| 3.7  | Alpha-particle-induced SEU cross-section as a function of supply voltage     |    |

|      | for 20-nm DFF with different $V_T$ values                                    | 30 |

| 3.8  | Alpha-particle-induced SEU cross-section as a function of supply voltage     |    |

|      | for 14/16-nm DFF with different $V_T$ values                                 | 31 |

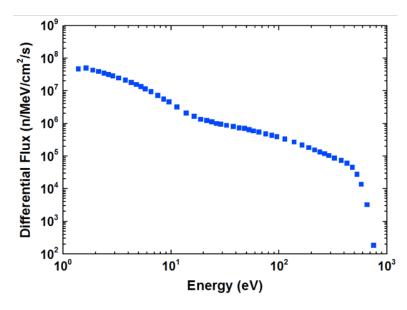

| 3.9  | High-Energy-Neutron Test Setup in LANSCE                                     | 35 |

| 3.10 | High-Energy-Neutron Beam Spectrum in LANSCE                                  | 35 |

| 3.11 | Thermal-Neutron Beam Spectrum in MURR                                        | 36 |

| 3.12 | Master-Slave Configuration for a Conventional DFF Design                     | 38 |

| 3.13 | Heavy-ion induced SEU cross-section as a function of frequency for the       |    |

|      | 14/16-nm DFF with different $V_T$ values                                     | 40 |

| 3.14 | Heavy-ion induced SEU cross-section as a function of frequency for 14/16-    |    |

|      | nm 4-bit comparator logic circuit with different $V_T$ values                | 42 |

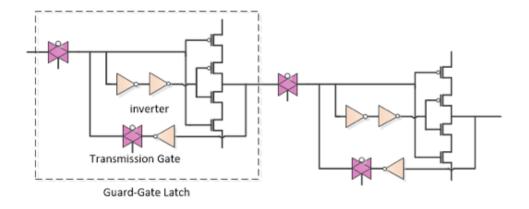

| 4.1  | Schematic design of a Guard-Gate FF [58]                                     | 49 |

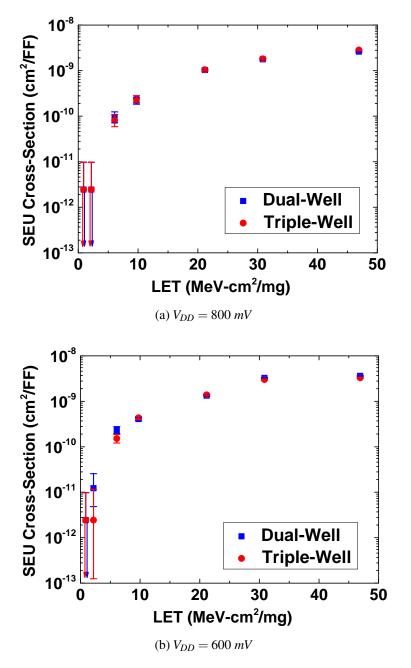

| 4.2  | Heavy ion-induced SEU cross-sections of dual-well and triple-well FF de-     |    |

|      | signs with guard-gates as a function of LET values for different voltage     |    |

|      | operations                                                                   | 50 |

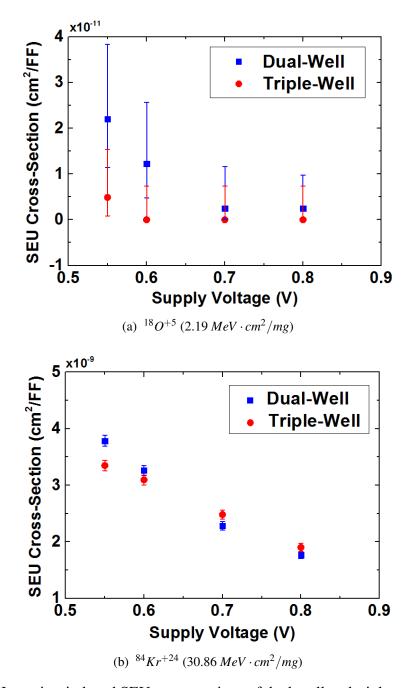

| 4.3  | Heavy ion-induced SEU cross-sections of dual-well and triple-well FF de-     |    |

|      | signs with guard-gates as a function of voltage for particles with different |    |

|      | LET values                                                                   | 52 |

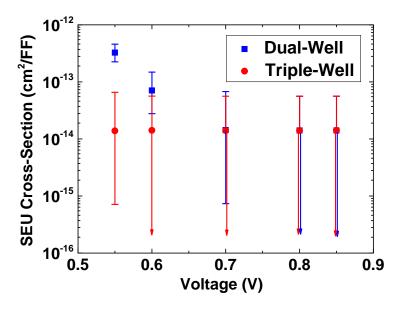

| 4.4 | Alpha particle-induced SEU cross-sections of dual-well and triple-well guard-                           |    |

|-----|---------------------------------------------------------------------------------------------------------|----|

|     | gate FF designs as a function of supply voltage                                                         | 53 |

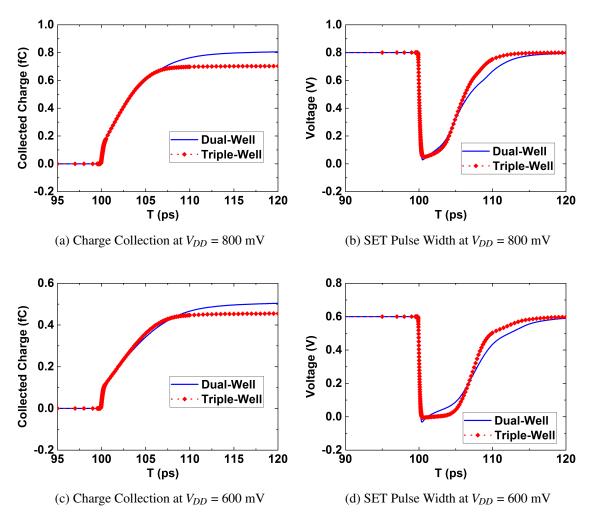

| 4.5 | Collected charge and SET pulse width for dual-well and triple-well designs                              |    |

|     | when a particle with LET = $1 \text{ MeV} \cdot \text{cm}^2/\text{mg}$ strikes the drain of an inverter |    |

|     | with OFF-state NMOS                                                                                     | 55 |

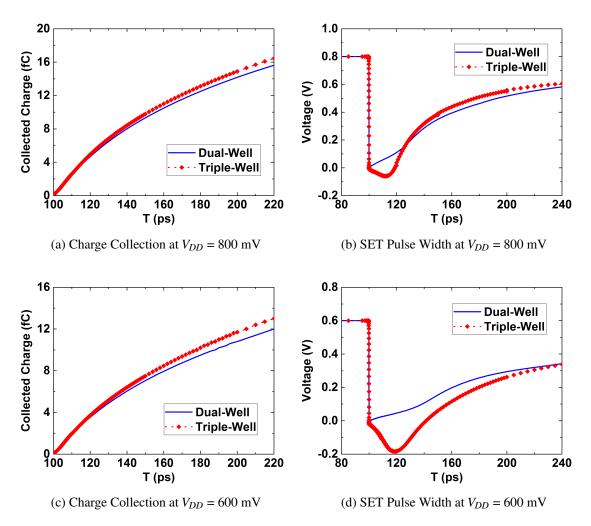

| 4.6 | Collected charge and SET pulse width for dual-well and triple-well designs                              |    |

|     | when a particle with LET = $60  MeV \cdot cm^2/mg$ strikes the drain of an inverter                     |    |

|     | with OFF-state NMOS                                                                                     | 57 |

| 4.7 | Schematic design of a conventional D-latch                                                              | 58 |

| 5.1 | Circuit-level simulation results for transistor currents at different tempera-                          |    |

|     | tures for the 20-nm node with nominal supply voltage of 850 mV                                          | 64 |

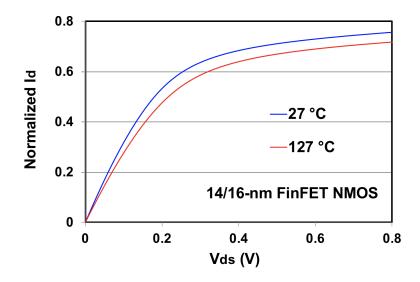

| 5.2 | Circuit-level simulation results for transistor currents at different tempera-                          |    |

|     | ture for the 14/16-nm node with supply voltage of 800 mV                                                | 65 |

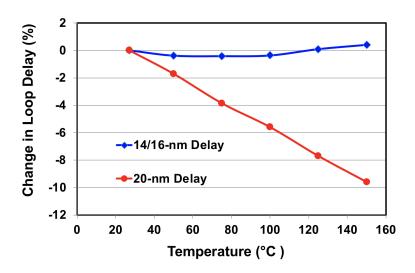

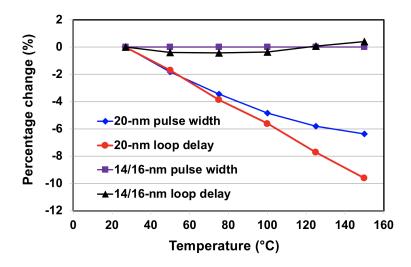

| 5.3 | Circuit-level simulation results showing variations in feedback loop delay                              |    |

|     | for a conventional DFF design for 20-nm planar ( $V_{DD}$ = 850 mV) and 14/16-                          |    |

|     | nm FinFET ( $V_{DD}$ = 800 mV) technology nodes                                                         | 65 |

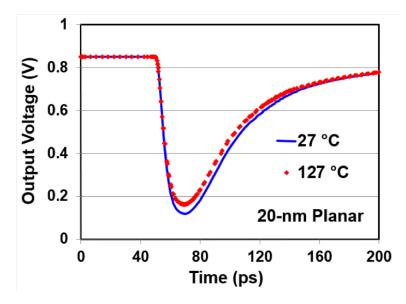

| 5.4 | Circuit-level simulation results for SET pulse widths at different tempera-                             |    |

|     | tures for a low-LET particle striking an inverter design on a 20-nm node                                |    |

|     | with a supply voltage of 850 mV                                                                         | 66 |

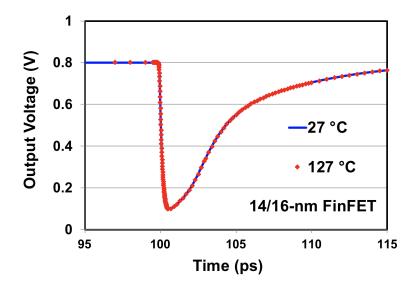

| 5.5 | 3D-TCAD simulation results for SET pulse widths at different temperatures                               |    |

|     | for a low-LET particle striking an inverter design on a 14/16-nm node with                              |    |

|     | a supply voltage of 800 mV                                                                              | 67 |

| 5.6 | Circuit-level simulations showing variation comparison of feedback loop                                 |    |

|     | delay and SET pulse width for the 20-nm and the 14/16-nm nodes at nom-                                  |    |

|     | inal supply voltages                                                                                    | 67 |

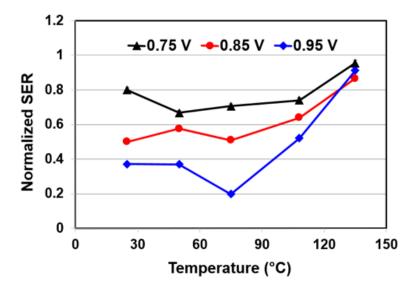

| 5.7 | Normalized SER as a function of temperature with different supply voltages                              |    |

|     | for the 20-nm conventional DFF                                                                          | 69 |

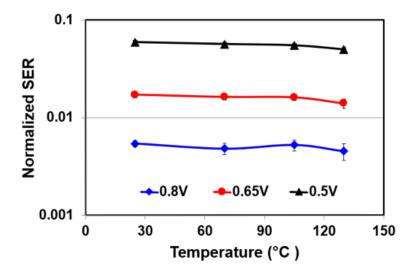

| 5.8  | Normalized SER as a function of temperature with different supply voltages    |    |

|------|-------------------------------------------------------------------------------|----|

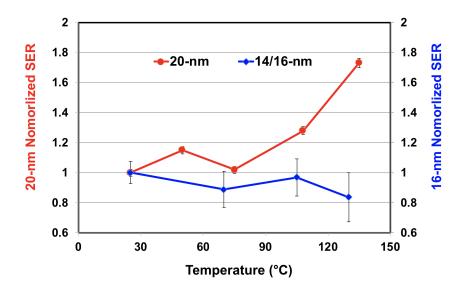

|      | for the 14/16-nm conventional LVT DFF                                         | 70 |

| 5.9  | Normalized SER as a function of temperature showing changes for 20-nm         |    |

|      | planar and 14/16-nm FinFET LVT DFF designs at norminal supply voltages.       | 71 |

| 5.10 | Normalized alpha-induced SER as a function of temperature of conven-          |    |

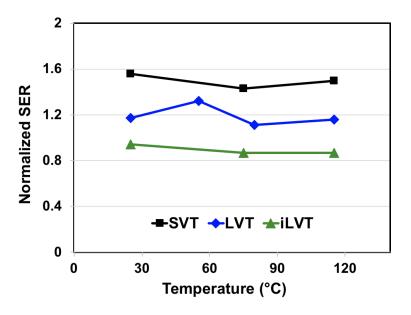

|      | tional DFF with different $V_T$ options at $V_{DD} = 570 \text{ mV}.$         | 71 |

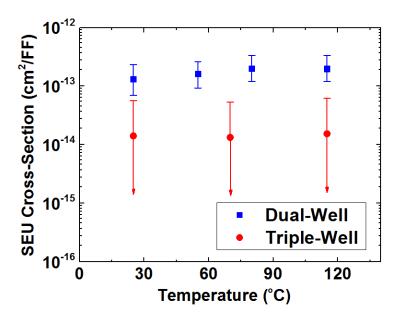

| 5.11 | Alpha particle-induced SEU cross-sections of dual-well and triple-well guard- |    |

|      | gate FF designs as a function of temperature at $V_{DD}$ = 570 mV             | 72 |

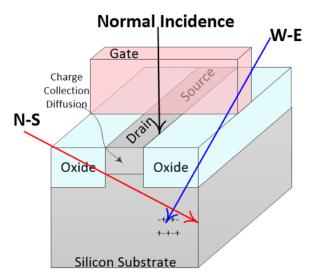

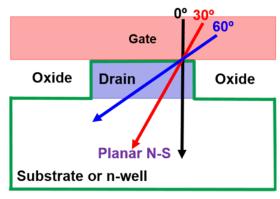

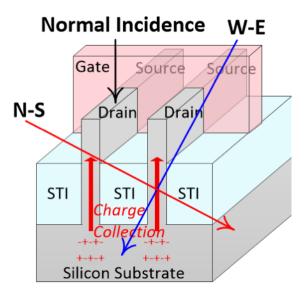

| 5.12 | Incident ions from N-S, W-E directions and normal incidence on a transis-     |    |

|      | tor in a planar technology, after [107]                                       | 74 |

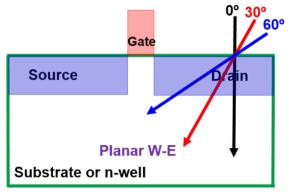

| 5.13 | Cartoon cross-section views of a planar transistor from different aspects     |    |

|      | with particles incident from different directions                             | 75 |

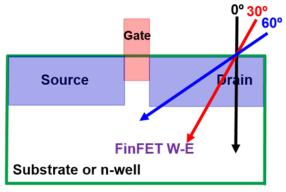

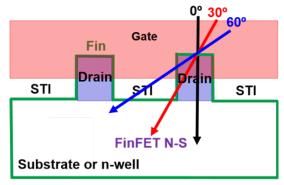

| 5.14 | Incident ions from N-S, W-E directions and normal incidence on a transis-     |    |

|      | tor in a FinFET technology, after [107]                                       | 76 |

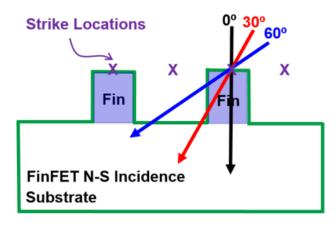

| 5.15 | Cartoon cross-section views of a FinFET transistor from different aspects     |    |

|      | with particles incident from different directions                             | 77 |

| 5.16 | Schematic design of the 14/16-nm bulk FinFET D-latch                          | 79 |

| 5.17 | Cartoon cross-section views of strike locations in TCAD simulation. Strike    |    |

|      | location varies every 20-nm. Nodes are identified to match the nodes in the   |    |

|      | schematic                                                                     | 79 |

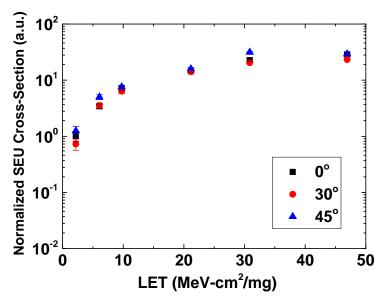

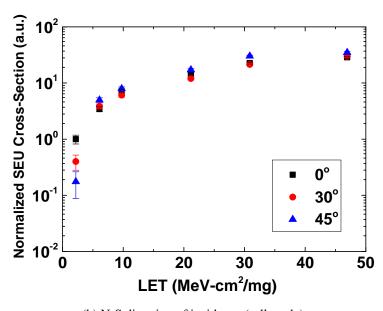

| 5.18 | Normalized SEU cross-sections as a function of LET with different angular     |    |

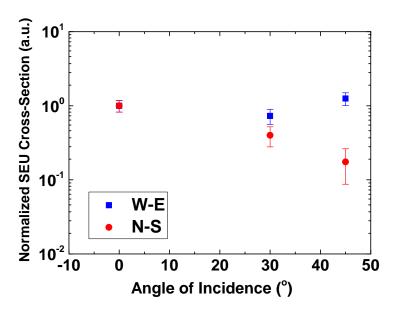

|      | incidence for conventional DFF                                                | 82 |

| 5.19 | Normalized SEU cross-sections as a function incident angle when $^{18}O^{+5}$ |    |

|      | hit on DFF (LET = $2.19 \ MeV \cdot cm^2/mg$ )                                | 83 |

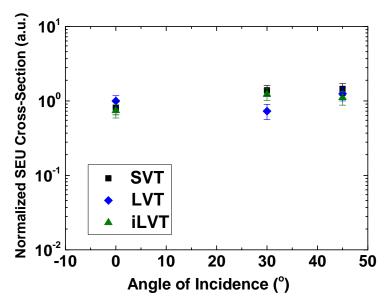

| 5.20 | Normalized SEU cross-sections as a function incident angle when $^{18}O^{+5}$ |    |

|      | hit on DFF with different $V_T$ options (LET = 2.19 $MeV \cdot cm^2/mg$ )     | 85 |

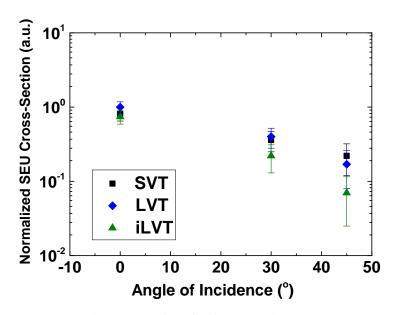

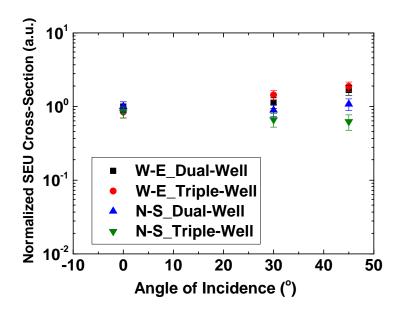

5.21 Normalized SEU cross-sections as a function incident angle when  $^{29}Si^{+8}$  hit on dual- and triple-well guard-gate FF (LET =  $6.09~MeV \cdot cm^2/mg$ ). . . 86

### Chapter 1

#### Introduction

The semiconductor industry has maintained technology scaling at the pace of Moore's Law for the past 50 years [1, 2]. The feature size of transistors scales by a factor of 0.7 every three years, enabling increasing number of transistors per integrated circuit (IC) associated with improved speed and system performance.

A traditional planar transistor establishes an electrical field and forms conducting channel from the source to the drain when the gate electrode is energized [3]. As the length of the gate is reduced, the control of the gate over the channel region is also reduced and short channel effects arises [4]. The threshold voltage, subthreshold slope and leakage current become sensitive to the gate length and are significantly degraded. New controlling methods or transistor structures were in prompt need to suppress short channel effects. One effective device structure named "FinFET" has been proposed to enhance the gate control over the channel region by rapping the gate electrode around the channel [5, 6, 7]. Methods to fabricated devices in FinFET processes have been developed and simplified [5, 8]. The FinFET devices have shown promising performance and scalability.

Along with scaling down of CMOS technology and improved system performance, single-event effects (SEEs) have become a serious reliability concern for advanced technology nodes due to decreased transistor current and nodal capacitance [9, 10]. An SEE is a circuit or system response to a single-event (SE), which refers to a single ionizing particle interacting with a semiconductor device. For space radiation, the common sources of single events (SEs) include heavy-ions and cosmic rays. For terrestrial environment, the radiation components include alpha particles, high-energy neutrons and protons, thermal neutrons, muons and electrons. SEEs include radiation-induced soft errors and hard errors in microelectronic circuits caused by ionizing particles striking the sensitive region of semicon-

ductor devices. When an energetic particle strikes a semiconductor device, electron-hole pairs will be generated along the striking track and charge can be collected through drift and diffusion processes. The collected charge modifies the potential of struck nodes and produces transient voltage spikes called single-event transients (SETs) in circuits. When a SE strike occurs and deposits enough charge in a storage cell, such as SRAM cells or flip-flops (FFs), a data state change will occur. This bit flip is called a single-event upset (SEU). SETs generated in combinational logic parts may also be latched into receiving FFs to cause soft errors in integrated circuits (ICs).

Efforts have been put into evaluating and mitigating soft errors in ICs for advanced technology nodes. Nowadays, commercial fabrication houses have successfully transitioned to FinFET structure for their advanced semiconductor processes. For FinFET technologies, since the physical structure changes significantly compared to planar technologies, the charge collection mechanism at a circuit node will be affected by the thin fin region (narrow active Silicon region) and the narrow connection to the substrate. The differences in physical transistor structure for planar technologies and FinFET technologies are significant enough that most SEEs will need to be reevaluated for FinFET technologies. Previous experimental and simulation results have reported the sensitive cross-section area for individual transistors fabricated on a range of FinFET processes to be reduced, resulting in less charge collection and better SEU performance for each bit in memory cells compared to that for planar processes, especially for nominal supply voltage operations [11, 12, 13, 14].

### 1.1 Key Research Contributions

Modern ICs need to be designed to meet requirements of power, speed and SEU performance, etc. under different environment and operating conditions. Flip-flops are basic storage elements in sequential logic circuits and fundamental building blocks in digital electronic systems. Proper designer-controllable factors can be chosen to meet performance requirements for flip-flop (FF) designs in different applications. This work char-

acterizes the SEU performance for FF designs in a commercial 14/16-nm bulk FinFET technology from a designer's perspective. For the first time, effects of designer-controlled parameters related to fabrication processes, such as threshold voltage, dual- and triple-well structures, on SEU performance and power consumption have been investigated in FinFET technologies. Theoretic analysis, simulation and experimental results are used to understand the effects of threshold voltage and well structure on SEU responses. Effects of these designer-controlled parameters on SEU performance against temperature and incident angle of radiation particles are also evaluated for stability of SEU responses. By comparing with former planar technologies, this work will provide designers with better understanding of how SE mechanism evolves from planar to FinFET technologies, better idea of SEU performance for FF designs with different designer-controlled parameters and environment conditions, and provide design guidelines for choosing proper designer-controlled parameters for specific applications in the 14/16-nm bulk FinFET technology.

1. Threshold voltage (V<sub>T</sub>): Increased integration density and operating frequency with technology scaling have led to significant increase in power density on ICs, increasing the need for power efficient design techniques. Fabrication houses have proposed to design low-power circuits by using different threshold voltages for individual transistors or employ multi-V<sub>T</sub> design techniques for different sub-circuits [15, 16, 17, 18]. Since it has become a standard practice to improve power requirements for a circuit by adjusting V<sub>T</sub> values, evaluating SEU vulnerability of circuits designed with different V<sub>T</sub> options is necessary. In this work, V<sub>T</sub> dependence of alpha-particle and heavy-ion-induced SEU cross-section at different supply voltages for a conventional D-flip-flop (DFF) design in a 14/16-nm bulk FinFET technology will be characterized. The SEU cross-sections for the 20-nm bulk planar DFF with different V<sub>T</sub> options will also be provided for comparison. Theory analysis and simulations will be carried out to understand the underlying mechanism for V<sub>T</sub> dependence of SEU cross-section for both the 20-nm bulk planar and the 14/16-nm bulk

FinFET technology. Design guidelines will be derived from case study to improve power, speed and SEU performance of specific circuits. Additionally,  $V_T$  effects on SEU responses against temperature variations and angular strikes will also be studied to ensure the selected  $V_T$  options remain efficient in real applications that face different operation conditions.

2. Dual- and triple-well structures: Triple-well technology has been widely used to provide better isolation of transistors from the substrate, which reduces substrate noise coupling as well as enable easier body bias and threshold voltage control [19, 20, 21]. With presence of the deep n-well, SEU response of circuits will be affected since the deep nSEU vulnerability-well alters the charge-collection mechanism. In order to take advantage of the triple-well technique at advanced FinFET technology nodes, evaluation of the SEU performance of dual- and triple-well structures in FinFET technologies are required. In this work, the dual-well and triple-well based 14/16-nm bulk FinFET FF designs will be irradiated with alpha particles and heavy-ions over a wide range of supply voltage to show the effect of the deep n-well on SEU performance. 3D TCAD (Technology Computer-Aided Design) simulations of transient currents, charge collection and SET pulse generation will be carried out for both planar and FinFET processes to explain the difference of underlying SE mechanism and how this alters the SEU performance. Similarly, SEU responses of dual- and triplewell FF designs will also be studied across wide ranges of temperature and particle incident angle to ensure proper choice of well-structure for system applications.

### 1.2 Dissertation Organization

The dissertation is organized as follows:

1. Chapter 1 first gave the general introduction to technology scaling, advantages of FinFET technologies, SEE, SEU and SE mechanism. After that, the objective and

- planned investigation of this proposed work was presented. Finally, the organization of the area paper is listed.

- 2. Chapter 2 includes background information of SE mechanism, effects of the variations to be investigated (i.e. threshold voltage, dual- and triple-well structure) on SEU performance for previous technologies, theory analysis of how these parameters affect SEU vulnerability, and whether the variations affect SEU performance differently in the new FinFET structure.

- 3. Chapter 3 presents experimental and simulation results for  $V_T$  effects on SET pulse width, feedback loop delay and overall SEU responses for the 20-nm bulk planar and the 14/16-nm bulk FinFET DFF designs, which shows how  $V_T$  effects alters for different technologies. Frequency dependence of the 14/16-nm DFF with different  $V_T$  options is also provided, followed by power, speed and SEU performance analysis and design guidelines.

- 4. Chapter 4 provides experimental and simulation results for effects of well structure on charge collection, SET pulse and overall SEU responses for the 14/16-nm bulk FinFET dual- and triple-well FF designs. Additional simulations have been carried out for designs with different well options in 40-nm and 28-nm CMOS technologies to show how SE mechanism evolves from planar to FinFET technologies.

- 5. Chapter 5 shows temperature and incident-angle dependence of SEU response for the 14/16-nm DFF and investigates the underlying mechanisms. Temperature and angular test results for FF designs with different  $V_T$  and well options have also been provides to show  $V_T$  and well-structure effects on SEU responses for the 14/16-nm FF designs across a wide range of temperature and incident angle.

- 6. Chapter 6 summarizes the major finding and research contributions of this work.

### Chapter 2

#### Background

Microelectronic circuits are operated in systems for both space and terrestrial applications. For space applications, ICs are exposed to radiation particles from trapped "belts" as well as from galactic cosmic rays and solar events, resulting in significant SEEs in circuit systems [22]. Early evidence of SEEs occurred in 1975 and heavy-ion-induced upsets in space was observed in satellite operation [23]. Shortly after the first observation of SEU in space, soft errors in terrestrial operations were reported that alpha-particle contaminants in package materials led to significant alpha-particle-induced error rates in DRAMs [24]. Researchers also reported soft errors due to proton and neutron indirect ionization effects [25, 26], which revealed the large abundance of SE radiation sources. As technologies have scaled, the problem of soft errors has been exacerbated for both space and terrestrial applications. More recently, experimental results have shown that particles like muons and electrons can also be the cause of soft errors [27, 28].

#### 2.1 Single-Event Mechanism

When a single radiation particle strikes a semiconductor device on an IC, it may cause an SE soft error in the circuit node, mainly through three processes: charge deposition, charge collection and circuit response [9].

### 2.1.1 Charge Deposition

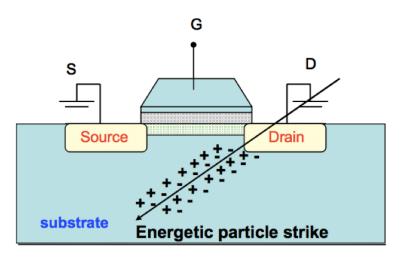

An energetic particle can induce charge in a semiconductor device either through direct ionization or indirect ionization [29]. When an ionizing particle, like a heavy ion or an alpha particle, passes through a semiconductor material, direct ionization happens, as shown in Figure 2.1. Atoms in material can be ionized by the coulombic forces between

Figure 2.1: Generation of electron-hole pairs due to an energetic particle strike [30].

the moving charged particle and the electrons of the nearby atoms, leading to energy transfer from the particle to bound electrons. This ionization of the material generates a dense track of electron-hole pairs (EHPs) along the striking track. The rate of energy loss is often expressed in terms of stopping power (STP) or linear energy transfer (LET) [31]. STP is the incremental rate of energy loss along the ion's path with a unit of energy per unit length (e.g. MeV/cm). LET normalizes out the material density from STP and usually has a unit of  $MeV \cdot cm^2/mg$ . The distance traveled by the incident particle inside the semiconductor is defined as the particle's range in this particular material. Along the striking track, the charge created by the strike can be calculated by [31]:

$$dQ[pC] = L(x)[pC/\mu m] \cdot dX[\mu m]$$

$$= \frac{LET(x)[MeV \cdot cm^2/g] \cdot \rho[g/cm^3] \cdot 1.6 \times 10^{19}[C]}{G[eV]} \cdot dX[\mu m]$$

(2.1)

For particles like protons or neutrons, production of the secondary charged particles is necessary before significant generation of EHPs occurs. These particles are considered to deposit charge through indirect ionization. The secondary particles deposit charge through the same mechanism as described above.

## 2.1.2 Charge Collection

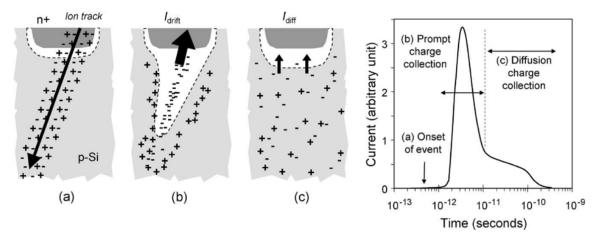

After charge deposition, charge within specific region can be collected through drift and diffusion processes [31]. Figure 2.2 shows the drift and diffusion processes for charge collection in a reverse-biased junction and the resultant current pulse caused by the high-energy ion strike [10]. For electrons and holes passes the depletion region, presence of

Figure 2.2: Charge generation and collection phases in a reverse-biased junction and the resultant current pulse caused by the passage of a high-energy ion [10].

electrical field helps effectively collect charge through drift process. In addition, the generated charge track can perturb the depletion region and distort the potential gradients along the track length significantly, leading to enhanced drift charge collection, which is called field funneling. Charge generated outside the funnel region but within a diffusion length of a junction may diffuse to the depletion region, leading to increased charge collection. Charge collection through diffusion is delayed since carriers need to move to the depletion region to be collected. In advanced CMOS technologies, charge collection may also be enhanced by bipolar transistor effect caused by the charge confinement within a well or body region [9]. Confined charge can modify the well potential, leading to additional injection of electrons into the channel [9, 32].

### 2.1.3 Circuit Response

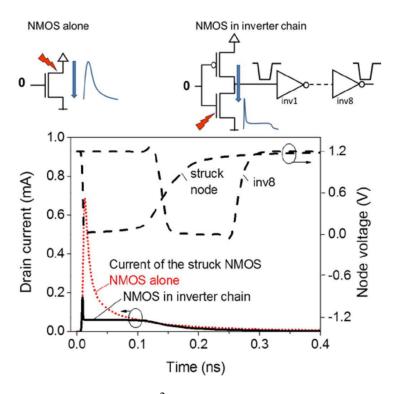

The charge collected modifies the voltage of struck nodes and the restoring transistor current helps restore the struck node to its initial state, leading to a transient voltage spike or an SET pulse. Figure 2.3 shows an example of SET pulse generation when a particle strikes a 130-nm SOI NMOS transistor. The SET pulse width greatly depends on the amount of charge collection and the strength of restoring current drive.

Figure 2.3: Simulation of a  $5 \text{ MeV} \cdot \text{cm}^2/\text{mg}$  ion strike for a 130-nm SOI off-state NMOS transistor, either device alone or integrated in a CMOS inverter chain with mixed-mode simulation. The left axis shows the current drive and the right axis shows the output inverter voltages of the struck node [33, 34].

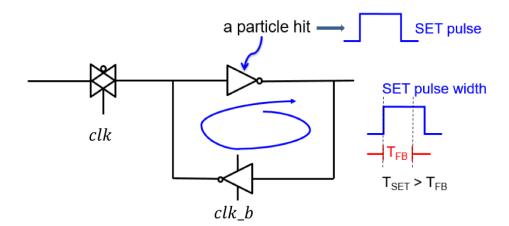

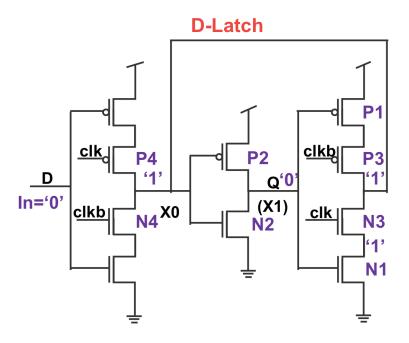

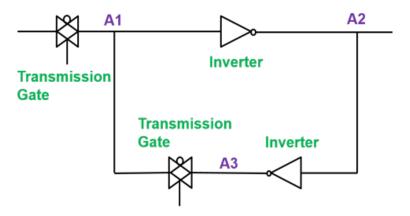

If the SET happens at the sensitive node of a flip-flop design or an SRAM design and is wide enough to transmit through the feedback circuit, an SEU will occur. SE upsets (SEUs) are non-destructive soft errors caused by ionizing particle strikes and normally appear as bit flips in SRAMs or FFs. Figure 2.4 shows the schematic design of a conventional D-latch, with an SET pulse generated by a particle hit. The D-latch consists of a transmission gate

Figure 2.4: Schematic design of a conventional D-latch, with an SET pulse caused by a particle hit and defined feedback loop delay.

(outside the loop), an inverter (hit by a particle in the figure) and a clocked inverter (an inverter with clock control). Feedback loop delay is defined as the time needed for a signal to transmit through the whole loop. For example, the feedback loop delay for the D-latch in Figure 2.4 is the sum of one inverter delay and one clocked-inverter delay. If the SET pulse width is longer than the feedback loop delay of the D-latch, the state change will be latched and transmitted to the next stage, thus an SEU will be recorded.

#### 2.2 Threshold Voltage

With scaling down of CMOS technology, increased integration density and operating frequency have led to significant increase in power density on ICs, increasing the need for power efficient design techniques. The preferred technique for reducing power consumption is to use reduced supply voltages since dynamic power is directly proportional to the square of supply voltage and standby power is proportional to supply voltage. However, reduction in supply voltage leads to lower operating frequency and increased vulnerability to single-event upsets [35, 36]. A alternate option provided by fabrication houses to design low-power circuits is to use different threshold voltages for individual transistors or employ multi- $V_T$  design techniques for different sub-circuits [15, 16, 17, 18]. There are

several  $V_T$  options available in commercial process design kits (PDK) for power-saving purposes for each advanced technology node. While dynamic power is approximately independent of threshold voltage, standby power can be decreased by increasing threshold voltage [37, 38, 39]. Since the use of different  $V_T$  options has become a standard practice to improve power requirements for a circuit, it is important to evaluate SEU vulnerability of circuits designed with different  $V_T$  options.

#### 2.2.1 Previous Results

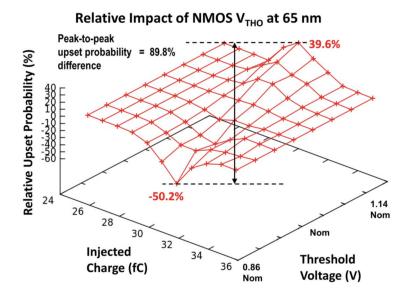

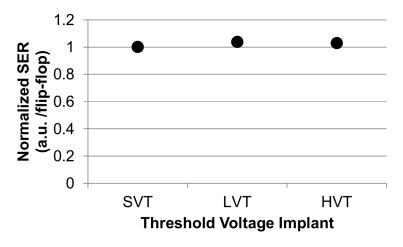

Much previous work has been done to evaluate different effects of  $V_T$  variations on critical charge, SEU probability or SEU cross-section in previous technologies [40, 41, 42, 43, 44]. Simulation results using 70-nm Berkeley predictive technology have been presented to show that increasing  $V_T$  reduces soft error rates (SER) of transmission-gatebased FFs but increases SER for combinational logic circuits [39]. The spread in critical charge due to  $V_T$  fluctuations of PMOS and NMOS transistors for 130-nm, 90-nm and 65-nm CMOS technologies have also been reported [40, 41]. The impact of  $V_T$  variations on the SEU vulnerability for specific SRAM and FF designs in 90-nm and 65-nm CMOS processes has been evaluated [42, 43]. Figure 2.5 shows the SEU probability changes caused by  $V_T$  variations for the 65-nm FF designs, which indicates that an increase in  $V_T$ significantly increases the SEU probability. However, a different dependence of SER on  $V_T$  for DFF designed in a 28-nm bulk planar process has been reported, as shown in Figure 2.6 [44]. For the 28-nm bulk planar technology, the SER of DFF with different  $V_T$  options have been shown to be very similar. As a result, the power consumption of DFF designs at this technology node can be easily reduced by increasing  $V_T$  without affecting the SEU vulnerability. These contradicting results have necessitated the need for reevaluating effects of  $V_T$  variations on SEU cross-section for each new advanced technology node to find out the tradeoff between power consumption and SEU vulnerability.

Figure 2.5: Impact of threshold voltage variations on the relative upset probability for a FF design in a 65-nm bulk CMOS technology [43].

Figure 2.6: Impact of threshold voltage variations on DFF SER in a 28-nm bulk CMOS technology [44].

## 2.2.2 Theoretical Analysis

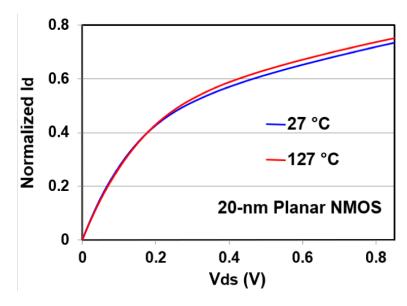

Transistor current is an important factor that affects SET pulse width and feedback loop delay. As mentioned earlier, transistor current drive is largely responsible for dissipating the deposited charge by the ion hit and leading to voltage recovery at the struck node. As transistor current decreases, SET pulse width will increase since it takes longer for a node

to restore to its original state with smaller currents. The gate delay is the length of time which starts when the input of a logic gate becomes stable and valid to change, to when the output of the logic gate is stable and valid to change. The length of time is equal to the time for charging or discharging the output node with capacitance  $C_{out}$  to a desired state with current drive  $I_D$  at a supply voltage of  $V_{DD}$ ,  $T_d = (C_{out} * V_{DD})/I_D$  [45]. So the gate delay is inversely proportional to transistor current and the feedback loop delay is simply the sum of several gate delays. A decrease in transistor current results in an increase in feedback loop delay. The two competing factors (SET pulse width and feedback loop delay) determine the overall SER for a given FF design. General equations for NMOS and PMOS transistor currents in linear region are shown as follows:

$$NMOS: I_{DS} = \mu_{n}C_{ox}\frac{W}{L}[(V_{GS} - V_{T})V_{DS} - \frac{1}{2}V_{DS}^{2}], C_{ox} = \frac{\varepsilon_{0}\varepsilon_{ox}}{t_{ox}}$$

$$PMOS: I_{SD} = \mu_{p}C_{ox}\frac{W}{L}[(V_{SG} - |V_{T}|)V_{SD} - \frac{1}{2}V_{SD}^{2}], C_{ox} = \frac{\varepsilon_{0}\varepsilon_{ox}}{t_{ox}}$$

(2.2)

From the equation set, the transistor current will be affected by carrier mobility, nodal capacitance, transistor length, transistor width and threshold voltage. As  $V_T$  increases, transistor current decreases. Reduced transistor current leads to an increase in SET pulse width and feedback loop delay. If the SET pulse width augment outweighs that of the feedback loop delay, then the SEU probability will increase; if the feedback loop delay increases faster than the SET pulse width, a decrease in SEU probability is expected. As  $V_T$  decreases, transistor current will increase. An increase in transistor current leads to a decrease in SET pulse width and feedback loop delay. If the pulse width reduction outweighs that of the feedback loop delay, a decrease in SEU probability is expected; if the feedback loop delay decreases more, the SEU probability increases.

Since SET pulse width is also closely related to the charge collection speed and amount, which is different for different technologies, varying currents caused by adjusting  $V_T$  will lead to different percentage changes in SET pulse width relative to gate delay for each technology. For FinFET structure, the charge collection efficiency (from substrate) and the

charge available for collection are both reduced by the new structure [11]. Effects of  $V_T$  on SEU performance for FinFET FF designs still wait to be investigated.

#### 2.3 Dual-Well and Triple-Well Structures

Triple-well technology has been widely used for better isolation of transistors from the substrate to reduce substrate noise coupling [19, 20, 21]. With the deep n-well design, each NMOS transistor built in the p-well is separated from the substrate. In addition to noise isolation, triple-well structures also enable easier  $V_T$  adjustment than dual-well structures through p-well bias for optimum performance and/or for controlling the power consumption without reducing supply voltage. In the presence of the deep n-well, SEU responses of circuits will be affected since the deep n-well alters the charge-collection mechanism and increases charge sharing between NMOS transistors [46].

#### 2.3.1 Previous Results

Dual-well and triple-well designs for older technologies showed inconsistent SEU performance. Triple-well SRAMs fabricated in the 0.5- $\mu$ m BiCMOS technology showed lower alpha-particle-induced SER compared to dual-well designs [47]. Triple-well SRAMs in a single-poly 0.15- $\mu$ m process was also investigated and a significant degradation in the alpha particle-induced FIT rates was observed [48]. For triple-well SRAMs fabricated in a 130-nm technology node and a 90-nm technology node, the alpha-particle-induced SER were shown to decrease by  $\sim$ 25% and  $\sim$ 41% compared to the dual-well designs [49]. For the BISER and BCDMR FF designs in a 65-nm CMOS technology, triple-well design showed superior or inferior SEU performance than the dual-well design depending on operating frequency [50].

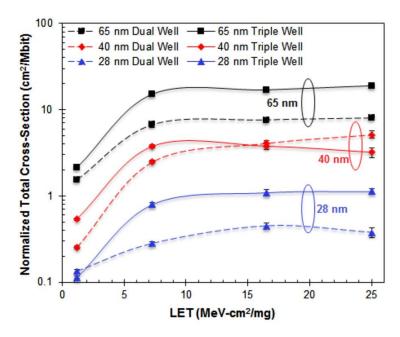

For recent planar technology generations, different behaviors of heavy-ion-induced upset cross-sections for triple-well and dual-well SRAMs designed in 65-nm, 40-nm and 28-nm technologies have been reported [51]. Results, presented in Figure 2.7, show over-

all SEU cross-section data (single-bit upsets as well as multi-cell upsets) for the 65-nm, 40-nm, and 28-nm SRAM designs. All three technology nodes show inferior performance for the triple-well designs for particle irradiation with low LET values. The 65-nm and

Figure 2.7: Normalized cross-section versus LET for dual-well and triple-well SRAMs for normal incidence irradiation with a checkerboard pattern in 65-nm, 40-nm, 28-nm bulk CMOS technologies [51].

28-nm nodes kept showing inferior SEU performance for triple-well designs compared to dual-well designs for all particle LET values. However, the 40-nm technology node showed better SEU performance for the triple-well design compared to the dual-well design for particles with high LET values due to single-event upset-reversal (SEUR) mechanism [51, 52].

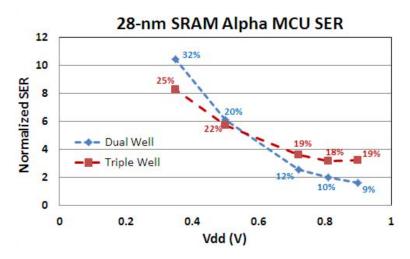

Triple-well SRAMs were also found to have improved multi-cell upset (MCU) cross-sections at reduced supply voltages due to the dominance of SEUR at low voltage operations [53]. The results of alpha-particle exposure for the 28-nm planar dual-well and triple-well SRAM designs as a function of supply voltage are shown in Figure 2.8. For the nominal supply voltage  $V_{DD} = 850$  mV, the dual-well design shows superior performance. At reduced supply voltages, the triple-well design shows lower SEU cross-section compared to the dual-well design. These different trends are the result of competition be-

Figure 2.8: Normalized alpha-particle-induced MCU SER as a function of voltage for dual-and triple-well SRAMs in a 28-nm bulk CMOS technology [53].

tween the charge-confinement mechanism and minimum spacing between sensitive regions at each technology node [51]. From these previous investigation, influence of well structure on SEU vulnerability highly depends on technology, which is difficult to predict for new technologies (especially for FinFET technologies when the physical structure have altered significantly).

#### 2.3.2 Charge-Collection Mechanism with Different Well Structures

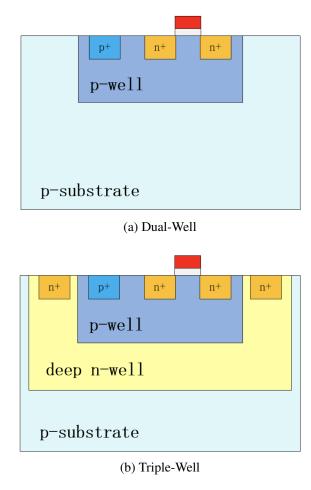

Figure 2.9 shows the two-dimension view of structures of dual- and triple-well planar NMOS transistors. Compared to the dual-well design, the triple-well NMOS comprises a buried deep-n-well that isolates the p-well from the p-substrate. Charge collection mechanism is altered in the triple-well structure by the third-well and has been discussed in [48]. Assume a simple application condition that source, p-well and p-substrate are connected to ground potential while drain, gate and deep-n-well are connected to high potential. For the dual-well design, generated electrons caused by ion hit in the p-well are collected by the drain region. Since the holes generated by ion hit spreads over the p-well and the p-substrate, the majority of holes inside p-well caused by trapped holes is not siSEU vulnerabil-

Figure 2.9: Structures of dual- and triple-well planar NMOS transistors.

itygnificant. Only small voltage perturbations exist in the p-well and the additional charge collection induced by bipolar transistor effect will not be significant. For the triple-well design, when a particle strikes, generated electrons in the p-well can be collected by the drain area and the deep-n-well. With presence of the deep-n-well, the majority of holes generated by ion hit are trapped in the p-well by the electric field between p-well and deep-n-well, leading to large voltage perturbation in p-well. Increasing p-well potential results in forward bias of the p-well to the source, leading to the source injecting additional electrons into the p-well, which may increase charge collection (bipolar transistor effect). However, the additional path for electrons from the p-well to the deep-n-well reduces charge collection (additional charge sink). If the bipolar transistor effect outweighs the effect of the

additional charge sink, enhanced charge collection will be found in the triple-well structure, leading to higher SEU vulnerability for the triple-well design than the dual-well design. If the p-well contact removes holes with such an efficiency (depending on the size and location of the p-well contact) that the bipolar transistor effect is not significant in the triple-well design, or the deep-n-well collects charge in a higher speed than the drain area, charge collection will be less for the drain region, leading to reduced SEU vulnerability compared to the dual-well design. Therefore, the SEU performance of triple-well designs compared to that of dual-well designs will depend both on hole removal efficiency of the p-well contact and charge collection efficiency of the drain and the deep-n-well.

The phenomenon of SEUR was also reported in previous work, which is similar to "pulse quenching" or "reinforcing charge collection" mechanism observed in combinational logics [51, 53, 54]. Charge confinement in the triple-well design may lead to higher numbers of multi-cell upsets within the same p-well [55]. The potential change in the second cell can form a feedback path to enhance the restoring current drive strength and restore the directly stricken cell to the original state, causing SEUR in the design and reducing overall SER.

The physical transistor structure for the FinFET transistors changes significantly compared to planar transistors. With the narrow connection between the well/substrate and the drain region, the charge collection efficiency of drain area may be further reduced, leading to the deep-n-well collecting more charge than the drain region. Besides, reduced charge-sharing effect at a FinFET node has been seen in SRAM cells where MCU size was used to show the extent of charge sharing between adjacent cells [56], which reduces charge collection and the possibility of SEUR. These differences further necessitate the need to reevaluate the SEU performance of dual- and triple-well designs in FinFET technologies in order to take advantage of the triple-well technique at advanced FinFET technology nodes.

## 2.4 Summary

In this chapter, the fundamental SE mechanism have been presented to show how soft errors can be caused by radiation particles in microelectronic systems. Threshold voltage and well structure are important designer-controllable variations that can be used for power-saving techniques or better isolation devices. Modifications on these parameters affect charge deposition, charge collection and circuit response processes, thus affecting the SEU vulnerability of advanced circuits. Previous investigations on the effects of  $V_T$  and well structure on SEU responses have shown inconsistent behaviors for different technology nodes. Qualitative analysis has been presented in this chapter, which shows that impact of these factors is technology dependent. Along with significant changes in physical structure of FinFET technologies, the effects will be more unpredictable, necessitating reevaluation of  $V_T$  and well-structure effects on SEU vulnerability for advanced FinFET circuits in order to take advantage of these benefits.

### Chapter 3

Effects of Threshold Voltage Variations on Single-Event Upset Responses for Advanced

Technologies

With increased use of  $V_T$  options for power-saving techniques, investigation of  $V_T$  effects on SEU responses for advanced circuits has come into the picture of product performance evaluation. It is crucial to understand the underlying mechanisms of  $V_T$  effects on SEU performance for advanced technology nodes and the tradeoffs between power, speed and SEU performance when  $V_T$  changes. This chapter mainly characterizes and compares the SEU responses of sequential circuits with different  $V_T$  options in a 20-nm bulk planar technology and a 14/16-nm bulk FinFET technology. With circuit-level simulations and theoretical analysis, this work provides better understanding of how  $V_T$  effects vary with technology and case study for design guidelines to achieve better overall performance to meet power, speed and SEU performance requirements for new technologies.

### 3.1 Test Circuits and Data Analysis

#### 3.1.1 Test Circuits and Setup

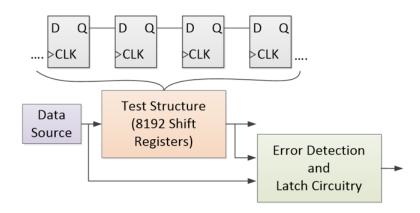

Test chips were fabricated in both 20-nm bulk planar and 14/16-nm bulk FinFET technology at a commercial foundry. FF chains with different FF designs were implemented in Circuit for Radiation Effects Self-Test (CREST) configuration [57]. The test structure consists of 8K shift-register stages for each FF chain, with supplemental clock generation, error detection and latch circuits, as shown in Figure 3.1. All sub-circuits other than shift registers were designed with Triple Modular Redundancy (TMR) to eliminate all errors from support circuits.

The conventional master-slave DFF design with inverter and clocked inverter was used. For the 20-nm node, DFF with high (HVT), low (LVT) and ultra-low (ULVT)  $V_T$  options

Figure 3.1: CREST block level design used for evaluating SEU response of FF cells, after [58].

$(V_T: HVT > LVT > ULVT)$  were designed in three different CREST blocks. For the 14/16-nm technology, all four available  $V_T$  implants, which are standard (SVT), low (LVT), intermediate-low (iLVT) and ultra-low (ULVT)  $V_T$  options ( $V_T: SVT > LVT > iLVT > ULVT$ ), were used to design four different CREST blocks.

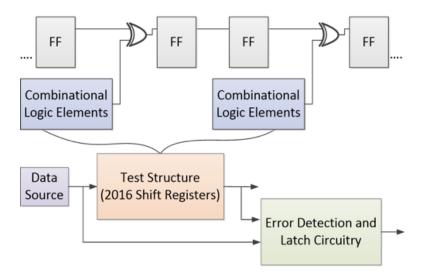

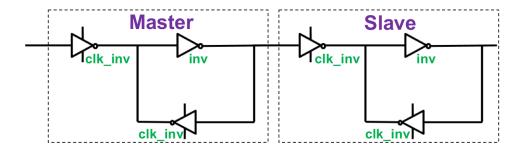

For further evaluating  $V_T$  effects on SEU responses for advanced circuits, the 14/16-nm bulk FinFET DFF designs are operated at high frequencies to measure the logic SEU cross-sections. These DFF designs consist of master and slave stages, with one being on-hold stage and another being transparent stage. The transparent stage acts like logic circuits and SET-induced errors become an important portion as frequency increases. Additionally, identical logic circuits were designed with different  $V_T$  options (SVT, LVT and iLVT) for the 14/16-nm combinational logic circuits. These logic SE measurement circuits were implemented in Combinational Circuit for Radiation Effects Self-Test (C-CREST) configuration [59] with 2K stages per block, as shown in Figure 3.2. Each stage consists of logic elements interleaved with flip-flops, which captures upsets from FFs and logic circuits. Similar to CREST blocks, C-CREST blocks also employed TMR for support circuits to eliminate all errors except those from the FFs and logic circuits.

To further reduce the number of errors from FF cells (and to increase the visibility of logic errors), Dual-Interlocked Storage Cell (DICE) FFs [61, 62] were used in the C-

Figure 3.2: C-CREST block level design used for evaluating SEU response of FF and logic circuits [60].

CREST blocks. A separate CREST block for the same DICE FF was used to estimate the SEU cross-section of the DICE FF design. The logic structure inserted between each DICE FF was a 4-bit comparator circuit. Three different C-CREST blocks were designed, each using a different  $V_T$  option (SVT, LVT, ULVT) for all transistors in the logic block.

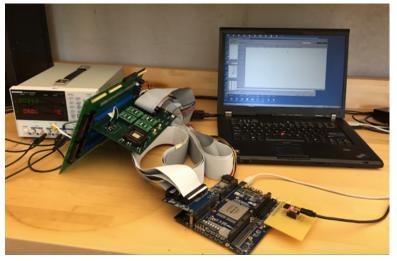

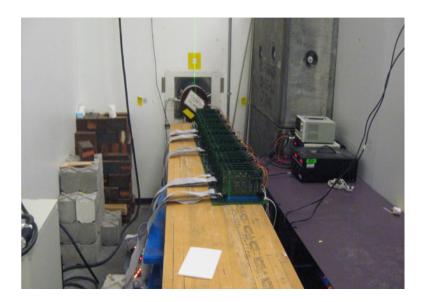

The size of test ICs is  $2 \, mm \times 2 \, mm$  and the packaged die is of  $2 \, cm \times 2 \, cm$ , which can fit into properly designed IC socket, as shown in Figure 3.3(a). Figure 3.3(b) shows the test setup, including equipment for testing, test boards, and the connections for the setup. Altera DE2-115 or DE3 [63] are used to control the signal and data transmission through ribbon cables for test ICs. Printed Circuit Boards (PCBs) were designed and fabricated for convenient connection and control of signal and data transmission from FPGA (Field Programmable Gate Array) boards to test ICs. Either the shift-register outputs or the error detection results can be read. When tested with radiation sources and SEUs are generated inside FF designs, errors will be counted on IC. Data will transmit out through the PCB and be stored in FPGA, and finally be shown on the control terminal of the laptop. Data analysis can be done with stored file for SEU performance.

(a) A socket holds the packaged die with alpha source sitting above. Blue block shows the position of IC under alpha source

(b) Test equipments, parts and connections.

Figure 3.3: SEU characterization test setup.

## 3.1.2 SEU Cross-Section and Failure in Time Analysis

SEU cross-section for FF designs were measured with CREST circuits (Figure 3.1). The equation used to calculate FF SEU cross-section is:

$$Cross - Section/FF[cm^{2}] = \frac{\# \ of \ Errors}{(\# \ of \ FFs) \times Total \ Fluence}$$

(3.1)

When number of errors is no less than 100, standard errors are used for error bars:

$$ErrorBarFF = \frac{\sqrt{\# of Errors}}{(\# of FFs) \times Total Fluence}$$

(3.2)

When number of errors is less than 100, error bars were calculated with a confidence level of 95%, as expressed in [64]. Failure in time (FIT) is the number of failures that can be expected in one billion  $(10^9)$  device-hours of operation. FIT rates and error bars are calculated for mega FFs as follows:

$$FIT/MFF = Cross - Section/FF[cm^{2}] \times 10^{9}[hours] \times 10^{6}[/MFF] \times (\# of \ particles)[/cm^{2}/hour]$$

$$ErrorBarFIT = ErrorBarFF \times 10^{9}[hours] \times 10^{6}[/MFF] \times (\# of \ particles)[/cm^{2}/hour]$$

$$(3.3)$$

SEU cross-section for logic circuits were measured with C-CREST circuits (Figure 3.2). Similarly, the equations used to calculate logic SEU cross-section and error bars (or based on reference [64]) are:

$$Cross - Section/stage[cm^{2}] = \frac{(Total \# of \ Errors) - (\# of \ Errors \ from \ FFs)}{(\# of \ stages) \times Total \ Fluence}$$

$$ErrorBarLogic = \frac{\sqrt{(Total \# of \ Errors) - (\# of \ Errors \ from \ FFs)}}{(\# of \ stages) \times Total \ Fluence}$$

$$(3.4)$$

#### 3.1.3 Simulation Uncertainty

Compared to results from real circuit tests, there will be uncertainties in simulation results for transistor current, charge collection, SET pulse width and gate delay. In this section, the sources for simulation uncertainty will be discussed.

Circuit-level simulations were carried out in Cadence tool suite with commercial 20-nm and 16-nm PDKs or 16-nm Arizona State University Predictive Technology Models (ASU PTM) [65, 66]. The uncertainty for transistor current and gate delay mainly comes from the accuracy of PDK/PTM. For example, PDK provides transistor models for different  $V_T$

options with nominal  $V_T$  values. However, process variations in real circuits may shift the real  $V_T$  values and induce differences in simulation results and experimental results. Other process variations, such as variations in transistor length, width, oxide thickness, doping density, may also induce differences. Besides, accuracy of temperature models in PDK and PTM affects simulation results for transistor current and gate delay as temperature changes.

The above variations also contribute to the uncertainty for SET pulse width simulation in Cadence. Other sources for uncertainty includes the current model used for particle strikes, particle LET values and hit locations. The bias-dependent single-event compact model developed in [67] was used to strike sensitive nodes in circuits. The model is capable of capturing the bias-dependent effects, recombination and parasitic bipolar effects and shows good agreement with 3D mixed-mode TCAD simulations. The model parameters were developed and calibrated with high-LET particles, and then for low-LET particles, which may induce additional uncertainty in SET pulse width. The LET value used for particle strikes in simulations and experiments may also differ, resulting in differences between simulation and experimental results. Lastly, particles may hit a specific node in circuits but the exact hit location may not be precisely known (i.e. how far from the center of the drain area) during experiments. All these factors can induce uncertainty for the SET pulse width values.

For 3D TCAD simulations, the uncertainty of charge collection and SET pulse width mainly comes from model calibration. Electrical characteristics of transistor, inverter and latch models are calibrated to 20-nm PDK or 28-nm PDK or 40-nm PDK or 16-nm PTM, so the variations in PDK and PTM will also be reflected in TCAD simulations. Besides, some of the detailed information, such as structure, doping density, carrier mobility, lifetime, recombination, gate stack, metal stack, layout, is not precisely known. With electrical characteristic calibration and sensitivity study, the accuracy of the TCAD models can be increased, but these parameters still induce uncertainties. The characteristics of striking particle, such as model of heavy-ion tracks, characteristic radius and deposition time, also

affect charge collection and SET pulse width values. These factors may induce additional uncertainty for TCAD simulations of charge collection and SET pulse width.

Quantitative error-bar analysis for simulation results can be done with additional information for fabrication processes, transistors, layouts, PDK and PTM variations and simulation models.

### 3.2 Heavy-ion Irradiation

### 3.2.1 Experimental Details

Heavy-ion tests were carried out at Lawrence Berkeley National Laboratory (LBNL) with  $10\,MeV/nucleon$  cocktail for the 20-nm test ICs and  $16\,MeV/nucleon$  cocktail for the 14/16-nm test ICs [68]. The LET values of heavy-ions were between  $0\sim 60\,MeV\cdot cm^2/mg$ , as listed in Table 3.1 and Table 3.2. All heavy-ion tests were conducted in vacuum, at room temperature and at normal incidence, with total fluence running up to  $5\times 10^7/cm^2$ . For the 20-nm DFF designs, static tests (clock set at "0") were carried out at 900 mV. For the 14/16-nm DFF designs, tests were carried out at 800 mV with a low operating frequency at 2.5 MHz.

Table 3.1: 10 MeV/nucleon Cocktail Components

| Ion              | Energy  | LET                   | Range     |

|------------------|---------|-----------------------|-----------|

| 1011             | (MeV)   | $(MeV \cdot cm^2/mg)$ | $(\mu m)$ |

| $^{11}B^{+3}$    | 108.01  | 0.89                  | 305.7     |

| $^{18}O^{+5}$    | 183.47  | 2.19                  | 226.4     |

| $^{22}Ne^{+6}$   | 216.28  | 3.49                  | 174.6     |

| $^{40}Ar^{+11}$  | 400.00  | 9.74                  | 130.1     |

| $51V^{+14}$      | 508.27  | 14.59                 | 113.4     |

| $^{65}Cu^{+18}$  | 659.19  | 21.17                 | 108.0     |

| $^{84}Kr^{+24}$  | 885.59  | 30.86                 | 109.9     |

| $^{124}Xe^{+34}$ | 1232.55 | 58.78                 | 90.0      |

Table 3.2: 16 MeV/nucleon Cocktail Components

| Ion              | Energy  | LET                   | Range     |

|------------------|---------|-----------------------|-----------|

| 1011             | (MeV)   | $(MeV \cdot cm^2/mg)$ | $(\mu m)$ |

| $^{20}Ne^{+7}$   | 321.00  | 2.39                  | 347.9     |

| $^{40}Ar^{+14}$  | 642.36  | 7.27                  | 255.6     |

| $^{63}Cu^{+22}$  | 1007.34 | 16.53                 | 190.3     |

| $^{78}Kr^{+27}$  | 1225.54 | 24.98                 | 165.4     |

| $^{124}Xe^{+43}$ | 1954.71 | 49.29                 | 147.9     |

#### 3.2.2 Experimental Results

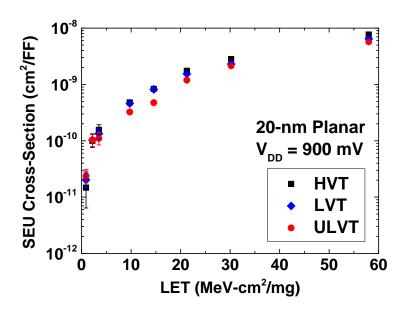

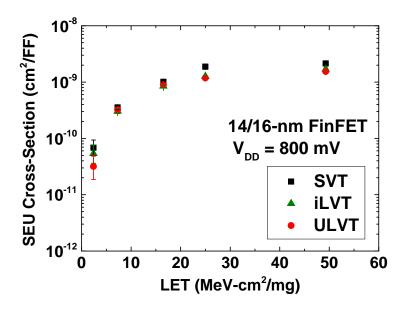

Heavy-ion test results for two technology nodes are shown in Figure 3.4 and Figure 3.5. For the 20-nm node, the influence of threshold voltage on SEU cross-section is not significant for high-LET heavy-ion irradiations. For low-LET particles, the ULVT DFF design shows slightly higher SEU cross-sections than those with HVT and LVT options. However, the differences are not significant. With very low critical charge values for these FF designs, differences in cross-sections are magnified near the LET threshold. For incident particles with LET significantly higher than the LET threshold, all these designs will show similar cross-sections because the underlying circuit design and layout are identical and the collected charge is large enough to cause upsets.

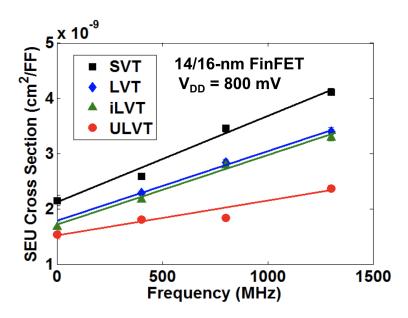

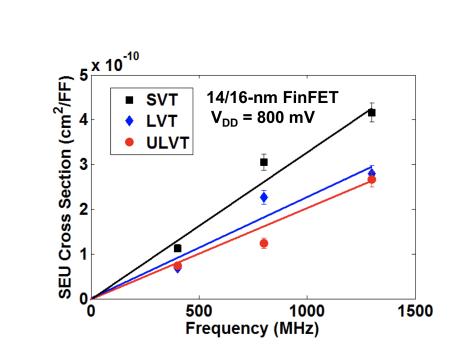

Similar to the DFF designs in the 20-nm technology node, high-LET heavy-ion irradiation results do not show significant differences among different  $V_T$  options for the 14/16-nm FinFET node, as is shown in Figure 3.5. For heavy-ion particles with low-LET values, some differences among the SEU cross-sections of these DFF designs can be observed (not significant and within error bars). For this node, the ULVT design shows the lowest SEU cross-section and the SVT design shows the highest SEU cross-section, which is completely opposite to what was observed for the 20-nm technology node. The different trends in SEU cross-section compared to that of 20-nm DFF relate to the different changing rate of SET pulse width and feedback loop delay as  $V_T$  changes for two technologies.

Figure 3.4: Heavy-ion-induced SEU cross-section as a function of particle LET for 20-nm DFF with different  $V_T$  values.

Figure 3.5: Heavy-ion-induced SEU cross-section as a function of particle LET for 14/16-nm DFF with different  $V_T$  values.

#### 3.3 Alpha Particle Irradiation

# 3.3.1 Experimental Details

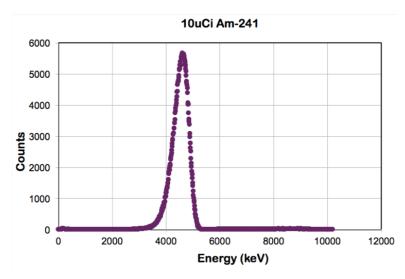

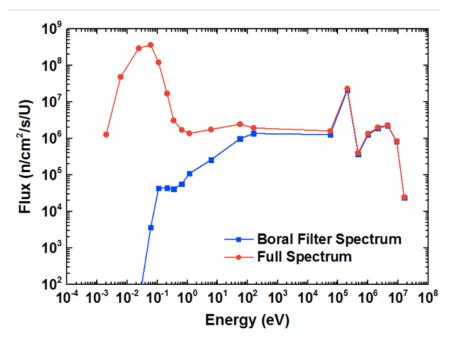

Alpha tests were carried out at Vanderbilt University at room temperature, with a 1  $cm \times$  1 cm size 5.4 MeV 10  $\mu Ci$  <sup>241</sup>Am foil button source to test FF SEU cross-section. Figure 3.6 shows the spectrum of the alpha source. The air gap between the Americium source and

Figure 3.6: Flux-Energy Spectrum of 5.4 MeV 10  $\mu$ Ci <sup>241</sup>Am source.

the die was less than 1 mm, leading to the particle LET less than 1  $MeV \cdot cm^2/mg$  when it reaches the active Silicon region. The alpha particle flux from the source was  $\sim 1000$   $alpha/mm^2/s$ . Supply voltage was varied from 750 mV to 950 mV (nominal  $V_{DD}$  is 850 mV) for the 20-nm DFF designs and 550 mV to 850 mV (nominal  $V_{DD}$  is 800 mV) for the 14/16-nm DFF designs. During testing, the shift registers were clocked at a low frequency of 2.5 MHz with logic input "0".

#### 3.3.2 Experimental Results

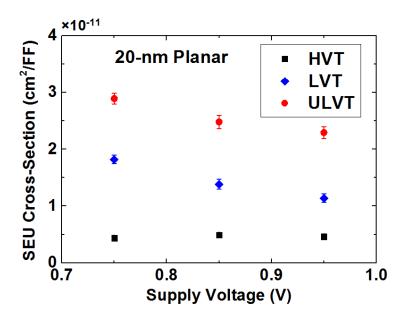

Experimental results are shown in this section. All curves contain error bars (some of them are too small to see). Figure 3.7 shows the experimental results of the SEU cross-sections for DFF designs with different  $V_T$  options for the 20-nm planar technology. The

ULVT design shows  $\sim 5x$  higher SEU cross-section than HVT design at 950 mV. This difference increases further to  $\sim 6x$  and  $\sim 7x$  when supply voltage is reduced to 850 mV and 750 mV. As  $V_T$  increases from ULVT to LVT to HVT, the transistor saturation current decreases, reducing the restoring current drive at a circuit node. This reduction in restoring

Figure 3.7: Alpha-particle-induced SEU cross-section as a function of supply voltage for 20-nm DFF with different  $V_T$  values.

current drive leads to lengthening of SET pulse generated at the circuit node. Additionally, the reduction in transistor currents also leads to an increase in feedback loop delay of an FF. A larger SET pulse width increases the upset probability while a longer feedback loop delay decreases it. These two competing factors determine the overall response of DFF.

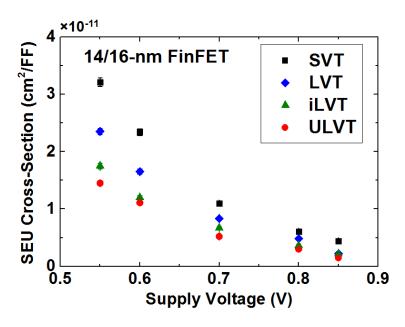

Alpha test results for the 14/16-nm DFF designs with varying threshold voltages are shown in Figure 3.8. As supply voltage decreases from 850 mV to 550 mV, the SEU cross-section increases by  $\sim$ 7x to  $\sim$ 10x for these DFF designs at this technology node. For this technology node, SEU vulnerability increases as  $V_T$  increases within a supply voltage range of 550 mV to 850 mV. As  $V_T$  increases from ULVT to SVT, the alpha-particle-induced SEU cross-section increases by  $\sim$ 2x. For the 14/16-nm DFF designs, decrease in transistor current caused by increasing  $V_T$  also results in an increase in SET pulse width

and feedback loop delay for the DFF designs. The different trends in SEU cross-section compared to that of the 20-nm DFF are similar to what has been observed for heavy-ion low-LET particle irradiations, which is mainly due to different changing rate of SET pulse width and feedback loop delay. Detailed simulations and analysis will be done in the next section.

Figure 3.8: Alpha-particle-induced SEU cross-section as a function of supply voltage for 14/16-nm DFF with different  $V_T$  values.

#### 3.4 Simulations and Discussion

Simulations were carried out in Cadence tool suite, with a bias-dependent model striking an OFF-state NMOS in the DFF designs [67, 65]. For the 20-nm bulk planar technology, simulated SET pulse width (PW) and feedback loop delay (FD) were obtained using a commercial 20-nm process design kit (PDK) (shown in Table 3.3) to show the percentage increase in SET pulse width and feedback loop delay as  $V_T$  increases at nominal supply voltage ( $V_{DD} = 850 \text{ mV}$ ). A low-LET particle (with the LET value close to that of alpha particles, about 1  $MeV \cdot cm^2/mg$ ) was used to strike inverters with OFF-state NMOS to generate SET pulses for these simulations. The percentage changes were calculated with

respect to the SET pulse width and feedback loop delay of the ULVT design. For the 20-nm

Table 3.3: Percentage Change in SET PW and FD relative to ULVT Design for 20-nm Node

|        | HVT   | LVT   | ULVT |

|--------|-------|-------|------|

| SET PW | 39.7% | 15.3% | 0    |

| FD     | 51.8% | 18.2% | 0    |

technology node, the increase in feedback loop delay is higher than that for the SET pulse width as  $V_T$  increases from ULVT to HVT, resulting in lower upset probability for HVT and LVT designs. This will lead to lower SEU cross-sections for higher  $V_T$  designs with low-LET particle irradiations. Therefore, for this 20-nm DFF design under low-LET particle irradiations, increasing  $V_T$  can effectively reduce static power consumption without any penalty in SEU vulnerability. According to Figure 3.7, this conventional DFF design with HVT option operating at a reduced supply voltage provides better performance for alphaparticle-induced SEU cross-section and power consumption than lower  $V_T$  options. It must be kept in mind that this may vary with different FF designs. These results are a strong function of SET pulse width and feedback loop delay. Depending on the FF design (individual transistor sizes and circuit topology), the changes in SET pulse width and feedback loop delay for different  $V_T$  options may be different, resulting in a different SEU response, as was observed for the 14/16-nm DFF designs. For high-LET particle irradiations, the SEU cross-section for designs with three  $V_T$  options are not significantly different since the SET pulse width becomes significantly larger than the feedback loop delay, which also leads to HVT option as the best choice for tradeoff between power and SEU responses.

For the 14/16-nm bulk FinFET node, a commercial 14/16-nm PDK was used to simulate the SET pulse width (strikes with a low-LET particle with the LET value close to that of alpha particles, about  $1 \text{ MeV} \cdot \text{cm}^2/\text{mg}$ ) and feedback loop delay for the DFF design at nominal supply voltage ( $V_{DD}$ = 800 mV). Similarly, the percentage changes were calculated with respect to the SET pulse width and feedback loop delay of the ULVT design. Table 3.4 shows simulation results of the percentage change in SET pulse width and feedback

loop delay when  $V_T$  increases from ULVT to SVT for the 14/16-nm bulk FinFET technology. For this technology node, SET pulse width increases faster than feedback loop delay, Table 3.4: Percentage Change in SET PW and FD relative to ULVT Design for 14/16-nm

**SVT** LVT iLVT **ULVT SET PW** 116.5% 61.6% 37.0% 0

Node

FD 78.9% 36.0% 15.6% 0