# DESIGN OF SOFT-ERROR-AWARE SEQUENTIAL CIRCUITS WITH POWER AND SPEED OPTIMIZATION

By

Hui Jiang

Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

# DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

May 11, 2018

Nashville, Tennessee

Approved:

Bharat L. Bhuva, Ph.D. Lloyd W. Massengill, Ph.D. Ronald D. Schrimpf, Ph.D. William H. Robinson, Ph.D. Aniruddha Gokhale, Ph.D. Copyright © 2018 by Hui Jiang All Rights Reserved To my husband, Zach, with whom all things are possible and without whom none of this would have been possible

#### ACKNOWLEDGMETNS

This work would not have been completed without the support of others. Therefore, I would like to acknowledge those who made this possible.

To begin with I would like to thank my advisor, Dr. Bharat Bhuva, for his relentless encouragement, unending patience, continued guidance and advice throughout my work. I also would like to thank Dr. Lloyd Massengill providing key insights that has allowed the conclusion of this work.

I also would like to thank the professors from the Radiation Effects and Reliability Group for their feedback over this research, usually provided during group meetings. I would like to thank you all for the friendship and great moments at school to the student members of the Radiation Effects and Reliability group.

Last, I would like to thank my parents who taught me the importance of an education, my family-in-law for their encouragement and finally, my husband, Zach, for his unending love and support that got me through from the dark and into the light.

# TABLE OF CONTENTS

| DEDICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | iii                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | iv                                                                                                             |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | viii                                                                                                           |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ix                                                                                                             |

| Chapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |

| I. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                              |

| <ul><li>1.1 Contribution</li><li>1.2 Summary of Document</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |

| II. BACKGROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9                                                                                                              |

| <ul> <li>2.1 Overview of Single-Event Effects in ICs</li> <li>2.1.1 SEUs in Logic</li> <li>2.1.2 SEUs in FFs</li> <li>2.1.3 Radiation Environments Overview</li> <li>2.1.3.1 The Van Allen Belts</li> <li>2.1.3.2 Galactic Cosmic Rays (GCRs)</li> <li>2.1.3.3 Terrestrial Environment</li> <li>2.2 Previous Approaches to Sequential Logic SEU Analysis</li> <li>2.3 Sources of Power Consumption</li> <li>2.3.1 Switching Power of the Circuits</li> <li>2.3.2 Short-Circuit Component of Power</li> <li>2.3.3 Leakage Component of Power</li> <li>2.3.3.1 Diode Leakage</li> <li>2.3.3.2 Sub-Threshold Leakage</li> <li>2.4 Low-Power Design Methodologies</li> <li>2.4.1 Device-driven voltage scaling</li> <li>2.4.2 Energy-delay minimum based voltage scaling</li> <li>2.4.4 Voltage Scaling Through Optimal Transistor Sizing</li> <li>2.4.4 Voltage Scaling Using Threshold Reduction</li> </ul> | 10<br>11<br>11<br>12<br>13<br>13<br>13<br>13<br>14<br>14<br>16<br>17<br>17<br>18<br>18<br>18<br>18<br>19<br>20 |

| 2.4.5 Leakage Power Reduction Approaches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 22                                                                                                           |

| III. CHARACTERIZATION OF LOGIC SEES FOR ADVANCED TECHNOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 24                                                                                                           |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .24                                                                                                            |

| 3.2 Test Circuit Description & Experiments                                   |          |

|------------------------------------------------------------------------------|----------|

| 3.2.1 Circuit Description.                                                   |          |

| 3.2.2 Test Details                                                           |          |

| 3.2.3 Experimentally Measuring Logic Cross-Section                           |          |

| 3.3 Experimental Results                                                     |          |

| 3.4 Discussion                                                               |          |

| 3.5 Conclusions                                                              |          |

| IV. AN EMPIRICAL MODEL FOR PREDICTING SE CROSS-SECTION FOR                   |          |

| COMBINATIONAL LOGIC CIRCUITS IN ADVANCED TECHNOLOGIES                        |          |

| 4.1 Introduction                                                             | 35       |

| 4.2 Background                                                               |          |

| 4.3 Proposed Empirical Approach                                              |          |

| 4.4 Test IC Designs and Experimental Details                                 |          |

| 4.4.1 Circuit Description                                                    |          |

| 4.4.2 Test Details                                                           |          |

| 4.4.3 Experimentally Measuring Logic Cross-Section                           |          |

| 4.5 Conclusions                                                              |          |

| V. CHARACTERIZATION OF FFS SEES FOR ADVANCED TECHNOLOGY .                    |          |

| 5.1 Introduction                                                             |          |

| 5.2 SE Analysis of Conventional DFF and three RHBD FF Designs                |          |

| 5.2.1 Schematic of FF Designs                                                |          |

| 5.2.2 Simulation Results                                                     |          |

| 5.2.3 Test Details                                                           |          |

| 5.2.4 Irradiation Test Results                                               |          |

| 5.3 SE Analysis of Sense-Amplifier Based FF Design                           | 64       |

| 5.3.1 Introduction                                                           |          |

| 5.3.2 SE Vulnerability of SAFF Design                                        |          |

| 5.3.2.1 First Phase: Data Sampling Phase                                     |          |

| 5.3.2.2 Second Phase: SRAM-Cell Like Phase & Third Phase: SR Latc            |          |

| 5.3.3 Data Phase                                                             |          |

| 5.3.3.1 Three Separate Phases of SAFF Comparison                             |          |

| 5.3.3.2 SEU Response of the SAFF as A Function of Temperature                |          |

| 5.3.4 Test IC Design and Experimental Details                                |          |

| 5.3.5 Experimental Results & Analyses                                        |          |

| 5.3.5.1 Heavy-Ion Experimental Results                                       |          |

| 5.3.5.2 Alpha Particle Experimental Results<br>5.3.6 Conclusions             |          |

| 5.4 Summary                                                                  |          |

| J. + Summary                                                                 |          |

| VI. An Empirical Model Based Approach to Explore Design Space for Sequential | Circuits |

|                                                                              |          |

| 6.1 Introduction                                  | 80  |

|---------------------------------------------------|-----|

| 6.2 Design Methodology and Empirical Models       |     |

| 6.3 Experimental Details and Results              |     |

| 6.3.1 Circuit Description and Test Results        |     |

| 6.3.2 Proposed Model for FF Designs               |     |

| 6.3.2.1 Quantitative Modeling Results             |     |

| 6.3.2.2 Discussion                                |     |

| 6.3.3 Proposed Model for Logic Circuits           |     |

| 6.3.3.1 Quantitative Modeling and Assessment Step | 94  |

| 6.3.3.2 Discussion                                |     |

| 6.4 Conclusions                                   |     |

| VII. Conclusions                                  | 104 |

| REFERENCES                                        |     |

# LIST OF TABLES

| Table Page                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IV.I. Number of gates, gates type, and transistor count for logic circuits                                                                                                                                            |

| IV.II.Parameters Value As Needed To Solving $t_{pw}$ Based on (IV.3) And the Logic<br>Circuit Used for the Empirical Model.45                                                                                         |

| IV. III. The Number of the Sensitive Gates for Different Logic Circuits Designs at Input Conditions $A_3A_2A_1A_0 = 1000$ and $B_3B_2B_1B_0 = 0110$                                                                   |

| IV.IV. The SEU Cross-Section Ratio Between the Measured Logic Cross-Section and<br>Estimated Cross-Section for LVT Designs                                                                                            |

| IV.V. The SEU Cross-Section Ratio Between the Measured Logic Cross-Section and<br>Estimated Cross-Section for SVT Designs                                                                                             |

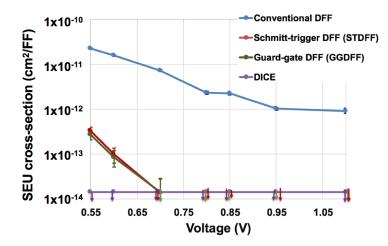

| V.I. Power (at 0% and 100% data activity), clk-to-q delay, total number of transistors, and IC area of the three representative RHBD FFs and the conventioanl DFF (@16-nm bulk FinFET & <i>Vdd</i> =0.8 V and 0.55 V) |

| <ul><li>V.II. Critical Charge for All Three Stages of Operation for The SAFF as A Function of Differential Input Voltage at Node <i>In1</i> and <i>In2</i></li></ul>                                                  |

| V.III. Critical Charge for The SAFF as A Function of Temperature With $In1 = 0.95$ V and $In2 = 0$ V                                                                                                                  |

| V.I. Fitting parameters ( $\alpha_{@V}$ , $\beta_{@V}$ , $\gamma_{@f}$ , $\delta_{@f}$ , and $\eta_{@f}$ ) for DFF design with SVT, LVT, iLVT, and uLVT implants                                                      |

| V.II. Fitting parameters ( $\alpha_{@V}$ , $\beta_{@V}$ , $\gamma_{@f}$ , $\delta_{@f}$ , and $\eta_{@f}$ ) for conventional DFF design and three RHBD FF Designs with LVT implant                                    |

| VI.III. Four different design specifications with the minimized power consumption design after applying the proposed analytical method90                                                                              |

| VI.IV. Four different design specifications with the minimized power consumption design after applying the proposed analytical method                                                                                 |

| VI.V. Fitting parameters ( $\alpha_{@V}$ and $\beta_{@V}$ ) for three logic circuits                                                                                                                                  |

| VI.VI. Fitting parameters ( $\gamma_{@f}$ , $\delta_{@f}$ , and $\eta_{@f}$ ) for three logic circuits                                                                                                                |

| VI.VII. Average number of N <sub>transistor</sub> for different logic gates                                                                                                                                           |

# LIST OF FIGURES

| Figure Page                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

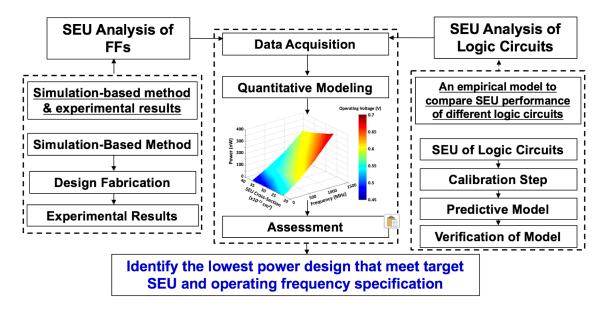

| I.1. Summary of the main research objectives of this work7                                                                                                                                                                                                                                                                                                                                      |

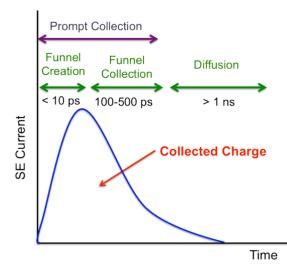

| II.1. Shape of a representative single event pulse measured at a struck p-n junction [5]. 10                                                                                                                                                                                                                                                                                                    |

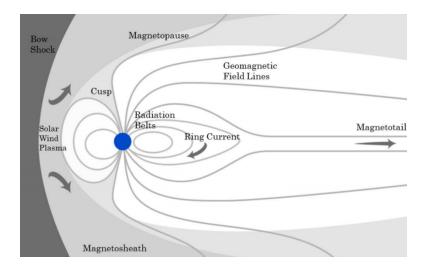

| II.2. The Earth's magnetosphere including the solar wind (pictured to the left), bow shock, magnetosheath and magnetopause [16]                                                                                                                                                                                                                                                                 |

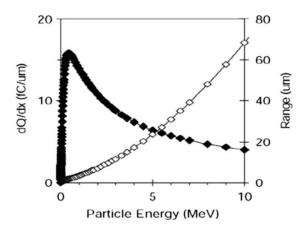

| II.3. Charge transfer ( <i>solid boxes</i> ) and range ( <i>open boxes</i> ) of alpha particles in silicon [24]                                                                                                                                                                                                                                                                                 |

| II.4. Circuit model for computing the dynamic power of a CMOS gate                                                                                                                                                                                                                                                                                                                              |

| II.5. Delay comparison at different $V_{dd}$ for FinFET and planar circuits. After [38]19                                                                                                                                                                                                                                                                                                       |

| II.6. Energy-delay product of a 20-stage inverter chain versus supply voltage at different<br>activities factors (af) for FinFET 7-nm. After [40]                                                                                                                                                                                                                                               |

| II.7. Compromise between dynamic and leakage power dissipation through $V_t$ variation.<br>After [34]                                                                                                                                                                                                                                                                                           |

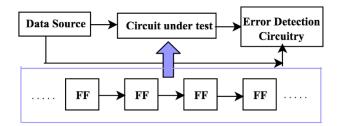

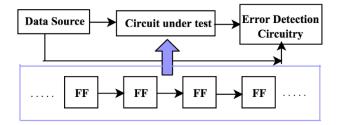

| III.1. CREST block diagram for the test circuit to evaluate SEU effects on flip-flops, after<br>[64]                                                                                                                                                                                                                                                                                            |

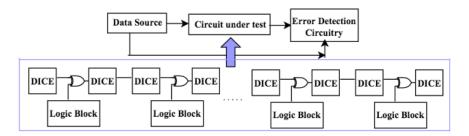

| III.2. C-CREST block diagram for the test circuit to evaluate SEU effects on flip-flops and<br>logic circuits, after [65]                                                                                                                                                                                                                                                                       |

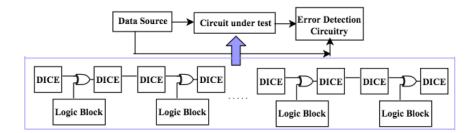

| III.3. Expreimental cross-section for LC-1 with inputs A = '1000' and B = '0110' and $600/700/800 \text{ mV}$ at (a) 58.78 (Xe) MeV-cm <sup>2</sup> /mg and (b) 21.17 (Cu) MeV-cm <sup>2</sup> /mg as a function of frequency; (c) Cross-section of LC-1 for two different LET particles as a function of supply voltage at 500 MHz. For the other operating frequency, the trends are similar. |

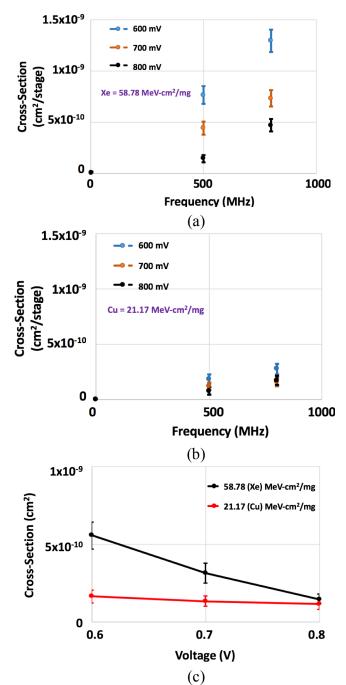

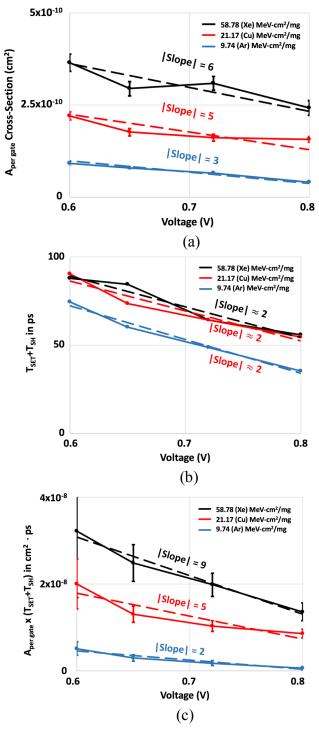

| <ul><li>III.4. Sensitive area of an inverter, average SET pulse widths, and setup-and-hold time as a function of supply voltage for different LET values (a) Sensitive area of an inverter;</li><li>(b) Sum of average SET pulse widths and setup-and-hold time; (c) Sensitive area of an inverter times the sum of average SET pulse widths and setup-and-hold time</li></ul>                  |

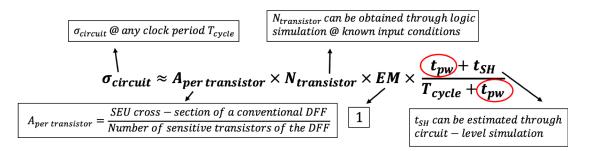

| IV.1. The process for obtaining the necessary parameters for Eqn. (IV.3) to solve $t_{pw}$ 41                                                                                                                                                                                                                                                                                                   |

| IV.2. CREST block diagram for the test circuit to evaluate SEU effects on flip-flops, after [64]                                                                                                                                                                                                                                                                                                |

| IV.3. C-CREST block diagram for the test circuit to evaluate SEU effects on flip-flops and logic circuits, after [65]                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

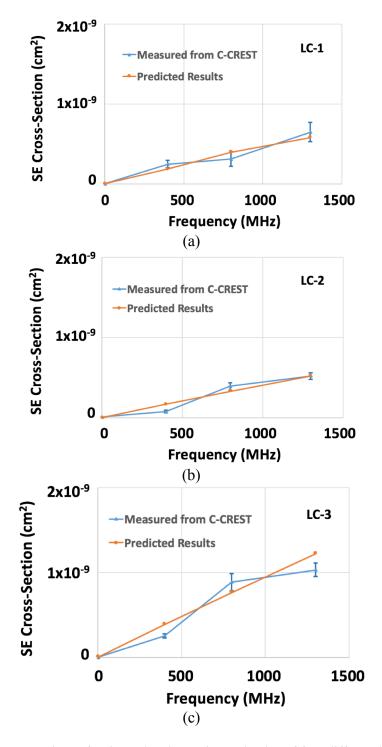

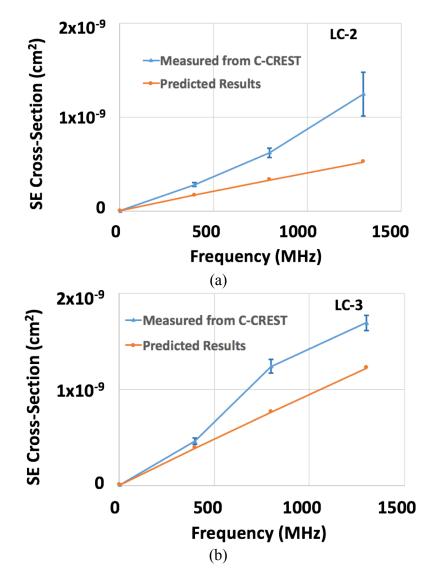

| IV.4. Comparison of estimated and experimental value of four different logic circuit.<br>Comparison of estimated and experimental value for (a) LC-2, (b) LC-3, and (c) LC-4<br>circuits. The same scale on Y-axis is used to show the relative hardness for these<br>circuits      |

| IV.5. Comparison of estimated and experimental value of two different logic circuit with<br>SVT designs. Comparison of estimated and experimental value for (a) LC-3 and (b)<br>LC-4 circuits. The same scale on Y-axis is used to show the relative hardness for these<br>circuits |

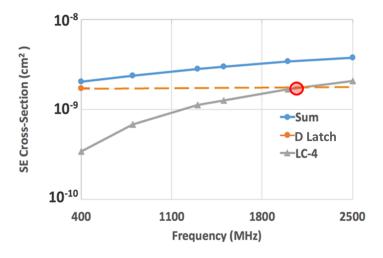

| IV.6. SE cross-section as a function of frequency for measured D latch SEUs and estimated LC-4 logic errors as well as their sum for Xe (LET~49.29 MeV-cm <sup>2</sup> /mg) with supply voltage of 800 mV (nominal)                                                                 |

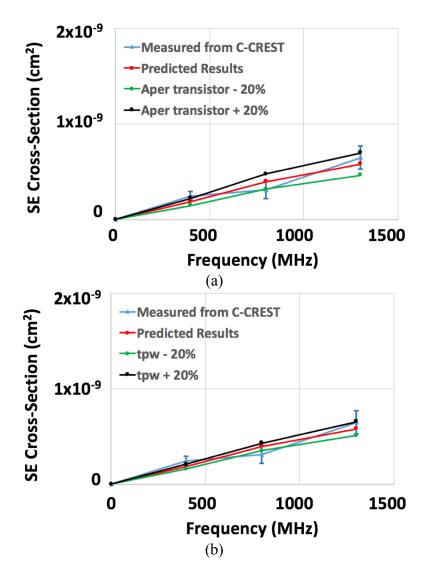

| IV.7. Sensitivity of $A_{per \ transistor}$ and $t_{pw}$ on predicting SE cross-section of logic circuit <i>LC-1</i> . 52                                                                                                                                                           |

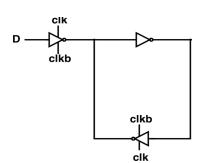

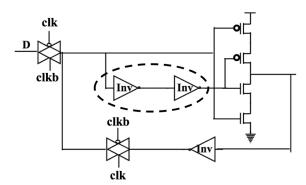

| V.1. A conventional D-latch design                                                                                                                                                                                                                                                  |

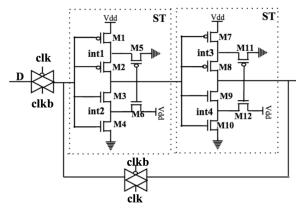

| V.2. Schmitt-trigger-based latch design                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                     |

| V.3. Guard-gate-based latch design                                                                                                                                                                                                                                                  |

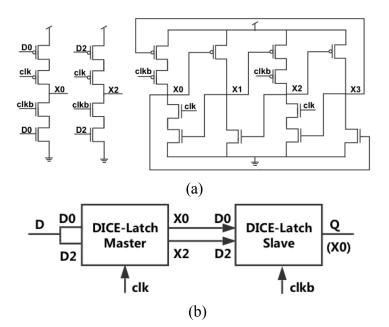

| <ul> <li>V.3. Guard-gate-based latch design.</li> <li>V.4. (a) Schematic design of the DICE-latch containing four storage nodes. (b) The master-slave connections for the DICE flip-flop.</li> </ul>                                                                                |

| V.4. (a) Schematic design of the DICE-latch containing four storage nodes. (b) The master-                                                                                                                                                                                          |

| <ul> <li>V.4. (a) Schematic design of the DICE-latch containing four storage nodes. (b) The master-slave connections for the DICE flip-flop</li></ul>                                                                                                                               |

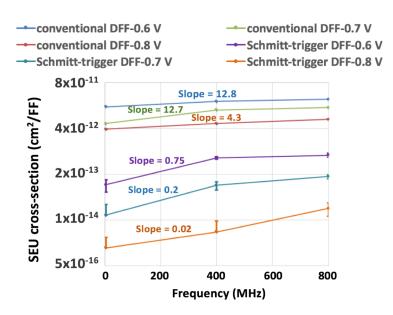

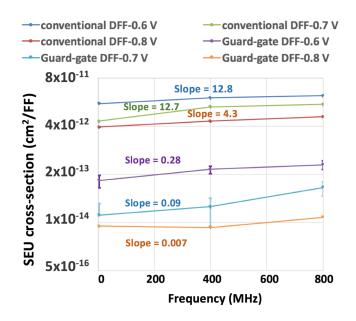

| <ul> <li>V.4. (a) Schematic design of the DICE-latch containing four storage nodes. (b) The master-slave connections for the DICE flip-flop</li></ul>                                                                                                                               |

| <ul> <li>V.4. (a) Schematic design of the DICE-latch containing four storage nodes. (b) The master-slave connections for the DICE flip-flop</li></ul>                                                                                                                               |

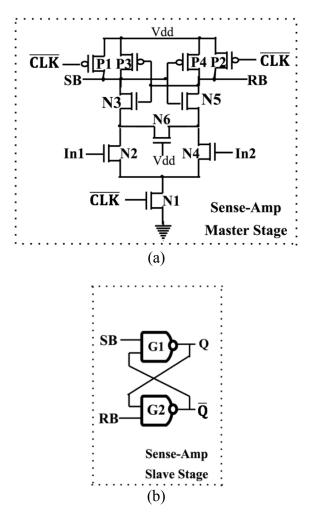

| V.10. Schematic of a SAFF with NAND SR slave latch. (a) Master stage of a SAFF. (b)<br>Slave stage of a SAFF                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

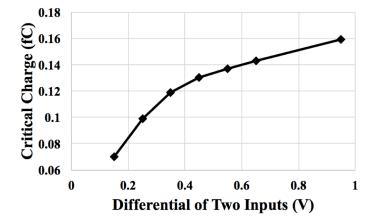

| V.11. Critical charge of the data sampling phase of SAFF as a function of differential input voltage                                                                                                                                                                                                                                                                    |

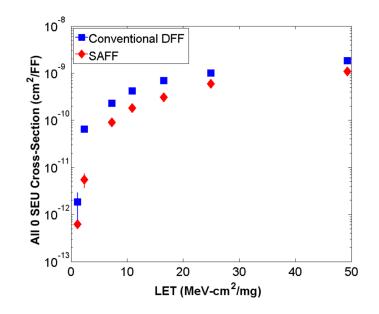

| V.12. SEU cross-section for heavy-ions as a function of particle LET for conventional DFF<br>and SAFF at 0.95 V                                                                                                                                                                                                                                                         |

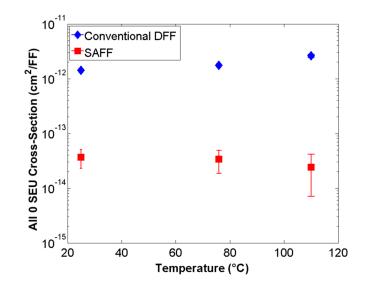

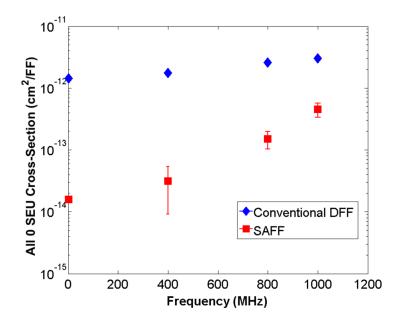

| <ul> <li>V.13. SE cross-section for alpha particle exposures as a function of temperature for<br/>conventional DFF and SAFF at 0.95 V.</li> </ul>                                                                                                                                                                                                                       |

| V.14. SE cross-section for alpha particle exposures as a function of frequency for<br>conventional DFF and SAFF at 1.1 V                                                                                                                                                                                                                                                |

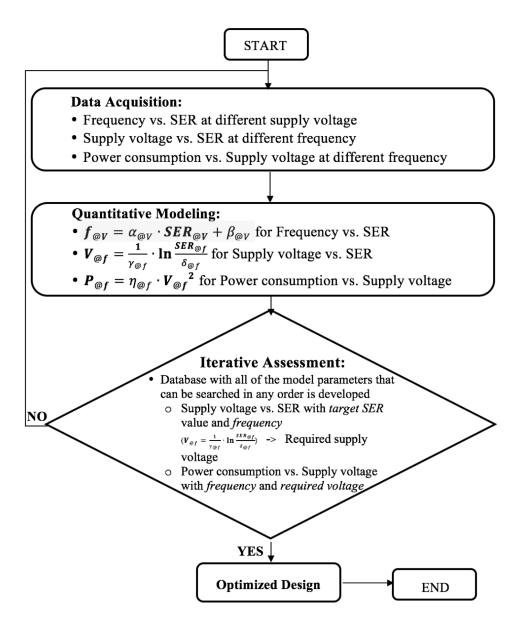

| VI.1. Flowchart of the proposed analytical method                                                                                                                                                                                                                                                                                                                       |

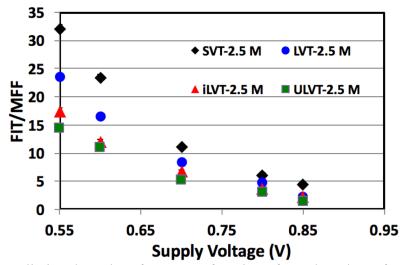

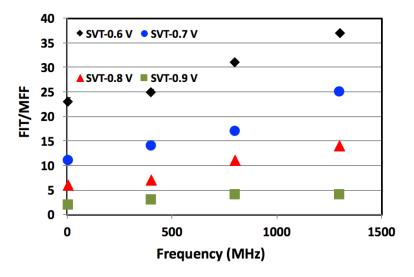

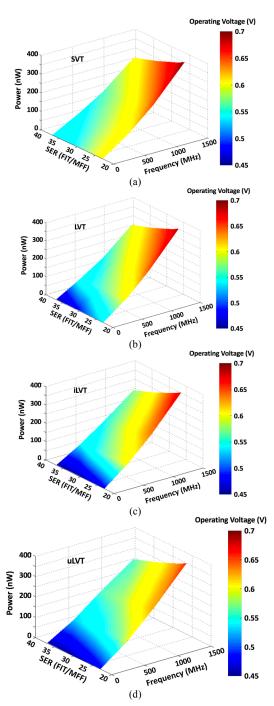

| <ul><li>VI.2. Data set with four numerical dimensions for the DFF (SER, frequency, power, and voltage) are generated by using the proposed analytical method (a) DFF design with SVT options; (b) DFF design with LVT options; (c) DFF design with LVT options; (d) DFF design with LVT options.</li></ul>                                                              |

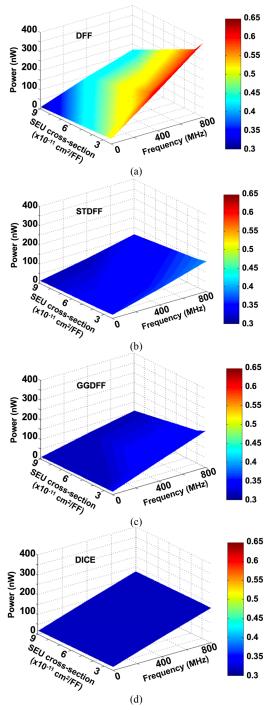

| VI.3. Data set with four numerical dimensions for the DFF and three RHBD FF designs<br>(SER, frequency, power, and voltage) are generated by using the proposed analytical<br>method (a) DFF; (b) STDFF; (c) GGDFF; (d) DICE                                                                                                                                            |

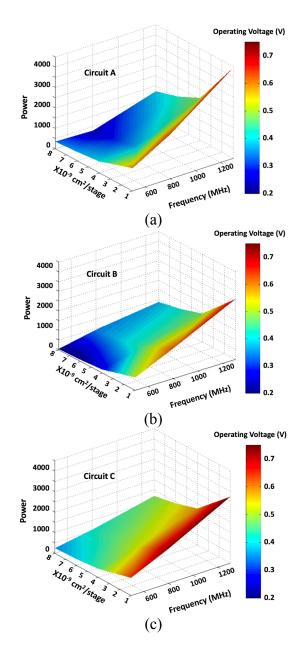

| <ul><li>VI.4. Data set with four numerical dimensions for the logic circuit (SE cross-section, frequency, power, and voltage) are generated by using the proposed model (a) Circuit A; (b) Circuit B; (c) Circuit C.</li></ul>                                                                                                                                          |

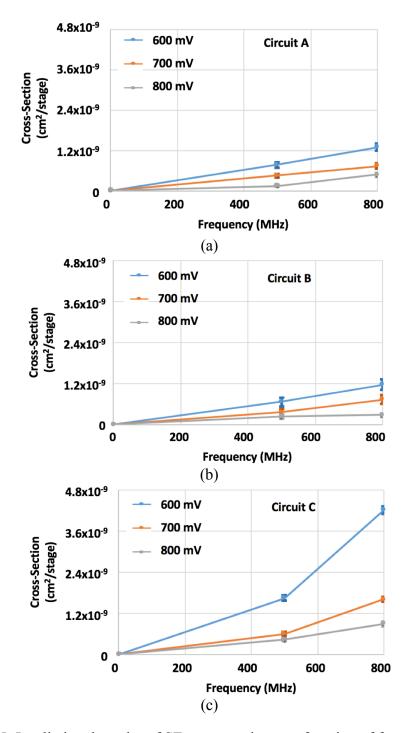

| <ul><li>VI.5. Irradiation data plot of SE cross-section as a function of frequency for (a) Circuit A;</li><li>(b) Circuit B; (c) Circuit C logic circuits at 600 mV, 700 mV, and 800 mV97</li></ul>                                                                                                                                                                     |

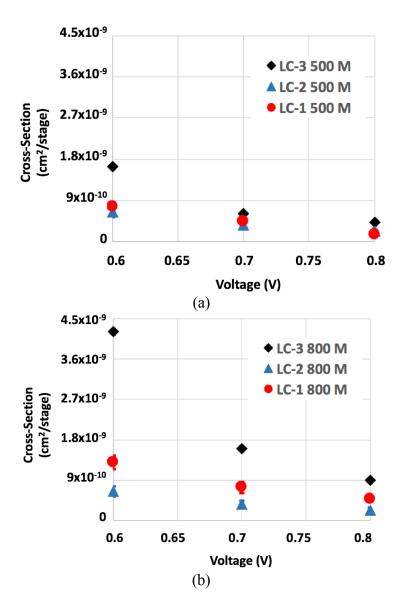

| <ul><li>VI.6. Irradiation data plot of SE cross-section as a function of supply voltage for (a) Circuit A; (b) Circuit B; (c) Circuit C logic circuits at 500 MHz and 800 MHz</li></ul>                                                                                                                                                                                 |

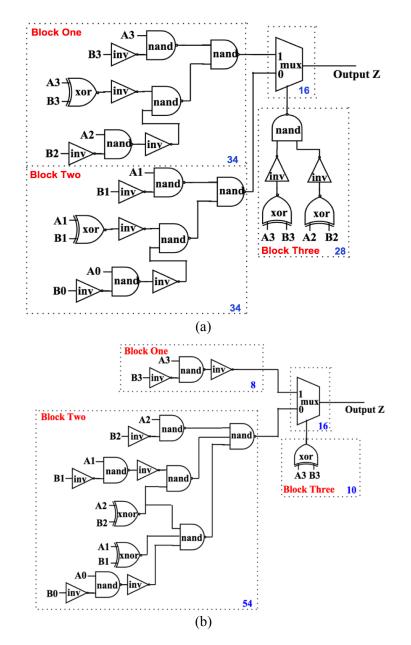

| VI.7. Circuit design of second hardened four-bit comparator. (a) CMP1, It consists a total of 112 transistors. The number at right bottom corner of each block is the total number of transistors in each block. (b) CMP2, It consists a total of 88 transistors. The number at right bottom corner of each block is the total number of transistors in each block. 101 |

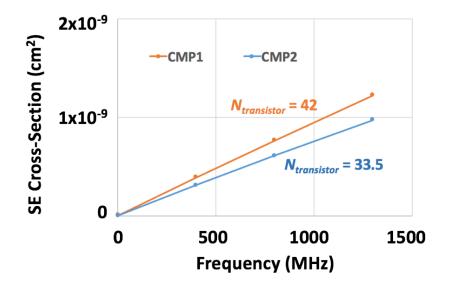

| VI.8. Estimated SE cross-section of CMP1 and CMP2 by using the average number of $N_{transistor}$ with the empirical model that developed in chapter 4                                                                                                                                                                                                                  |

### CHAPTER I

#### INTRODUCTION

The increasing demand of mobile, battery-powered electronic systems (e.g., lap-top computers, cellular phones, etc.) has been a major driving force for the design of microelectronic circuits with low power dissipation. More generally, as density, speed, and complexity of the digital chips continue to increase, the cost associated with cooling and heat removal such chips are becoming prohibitive. In addition to cost, there is the issue of reliability that points to the need for low power design [1]. Apparently, there is a high need for designing of high-throughput, low-power digital systems. For the low-power design techniques, it ultimately come down to a fundamental set of concepts: power is reduced by lowering either the supply voltage, the voltage swing, the physical capacitance, the switching activity or a combination of the above [2]. A single-event effect (SEE) of circuits is however strongly dependent on the supply voltage and the physical capacitance. Reduction in supply voltage as well as technology scaling trends (smaller nodal capacitances) may result in dramatically increased sensitivity of the circuits to radiation. For this reason, SEE induced errors of the low power design has very high demanding to be taken into account especially when designing circuits for applications require high reliability.

A SEE occurs when an ionizing particle that travels through silicon producing electron-hole pairs in an integrated circuit (IC). If the SE ion strike deposits charge near a transistor, the deposited charge may potentially lead to a voltage change of the circuit node associated with that transistor. The voltage change of the circuit node may result in a singleevent upset (SEU) in memory storage elements or a single-event transient (SET) in combinational logic that may be latched into memory [3]. A SEU occurs when the deposited charge ( $Q_{coll}$ ) is greater than the critical charge ( $Q_{crit}$ ). The  $Q_{crit}$  are based upon both the node capacitance and the restoring current (i.e., drive strength) of the logic cell. As the operating voltages and the dimensions of ICs are reduced to satisfy the ever-increasing demand for low power and higher density, the  $Q_{crit}$  has decreased dramatically.  $Q_{coll}$  was not shrinking as fast as  $Q_{crit}$  have made deep submicron low power ICs increasingly susceptible to radiation induced errors [4]. A SET in combinational logic result in an error is a strong function of three masking factors: electrical masking (SET pulse have insufficient amplitude to propagate through logic gates), logic masking (SET pulse can not get latched in to a latch).

In this proposed research, a methodology for evaluating SEE performance of sequential logic circuits have been developed. A study of the relationship between circuit SEE tolerance and power consumption is performed using this methodology. The purpose is to provide a figure-of-merit (FOM) for designers to make informed decisions on meeting power, speed, and SE specifications. To comprehensively comment on the design parameters of different sequential logic circuits, a FOM is defined as the inverse of the product of power and SE cross-section (PCSP<sup>-1</sup>). Since minimization of power and SE cross-section is desirable, a lower PCSP value and thus a higher FOM value can be considered to be an indicator of an optimized design. This work focuses on the study of both power consumption and SEE tolerance at device and circuit-level. Sequential circuits are used as circuit examples in this proposed research. The ultimate goal of the work is to provide designers with capabilities and FOM to choose the suitable low power and SEE tolerance design for different targeted design specifications and operating environment.

#### 1.1 Contribution

Upon completion of this work, some of the novel contributions of this dissertation include:

- An empirical model for evaluating SEE performance of logic circuits have been developed. Computing power can be reduced compare to previous simulation-based approaches. In additional, the proposed approach is easy to obtain and characterize compare to previous experimental-based approaches.

- SE characterization of different FFs fabricated in a 16-nm bulk FinFET CMOS technology have been performed for designing soft-error-aware circuits with power and speed optimization. First time differential FF have been detailed analyzed for SE performance at 16-nm bulk FinFET technology node.

- 3. A framework of designing soft-error-aware sequential circuits with power and speed optimization have been developed. This framework allows designers to expand sequential circuit designs of choice in terms of the low power designs for meeting target SER and speed specifications. Usually there is a target SER value (protection level) that needs to be met by designers. Therefore, instead of traditional analysis (SER as a function of supply voltage, frequency, temperature, etc.) comparative analysis (FF/logic designs, supply voltage, and frequency yielding identical SER values) is carried out to identify the best performing (lowest power) designs for meeting SER specifications. By analyzing the test results based on such an approach, designers will have access to data that will allow them to optimize a circuit design along multiple dimensions (such as SER, power, and operating frequency). Such an analysis may also

yield significant power savings while meeting SER and speed specifications.

# 1.2 Summary of Document

The dissertation is composed of six additional chapters. **Chapter 2**, Background, provides a background on radiation effects in digital integrated circuits (ICs) and sequential circuits in particular. In this chapter, the fundamentals of power consumption in CMOS circuits, as well as literature review materials to understand the various power minimization techniques are presented.

Logic SER, similar to FF SER are a strong function of particles LET values, supply voltage and operating frequency. If designers focus on hardening FF cells only, unmitigated logic errors may not reduce overall SER to required specifications (especially if operating frequencies are in GHz range). Hence, characterization and mitigation of logic SER is necessary to determine the optimized approach for meeting SER specifications for sequential circuits. Chapter 3, Characterization of Logic SEEs for Advanced Technology, presents experimental results that characterize logic SEEs as a function of LET and supply voltage for 16-nm bulk FinFET technology node. Although the SER performance of logic circuits at low-LET particles is well studied for planar bulk CMOS nodes, characterization for FinFET nodes has been done only for frequency and not for particle LET's or supply voltages. In this work, the impact of supply voltage, operating frequency, and particle LET's on the logic SER for the 16-nm bulk FinFET node is experimentally characterized. It was observed that only mitigate the SET pulse-width may not necessarily be effective to reduce the strong impact of the supply voltage on the logic SER for the high-LET particles. In addition, results indicate that particle LET strongly affects logic SEU cross-section and reducing the operating voltages, used for reducing power consumption, will significantly increase SEU cross-section for high-LET particles. Therefore, accurate and efficient estimation of combinational logic SEU cross-section at different circuit parameters and control variables (different LET particles, operating frequency, temperature, and supply voltage) is necessary for designers to identify best hardening design approaches. **Chapter 4**, An Empirical Model for Predicting SE Cross-Section for Combinational Logic Circuits in Advanced Technologies, develops a novel approach for evaluating SEE performance of logic circuits at different circuit parameters and control variables. An empirical method that uses experimental data from simple test structures for estimating SE vulnerability of any combinational logic circuit is presented. The estimated logic SE cross-section results obtained with the proposed method are within 2X average error when compared to the experimentally measured logic SE cross-section.

The primary goal of this work is to build a framework of designing soft-error-aware sequential circuits with power and speed optimization. A model for predicting SEU cross-section for any arbitrary logic circuit developed in Chapter 4 has been used to explore design space for logic circuits. In order to create a model for FF cells that will allow designers to identify the best performing (lowest power) designs for meeting SER specifications, comprehensive study on the SEU of different FF designs have been carried out in this work. **Chapter 5**, Characterization of FFs SEEs for Advanced Technology, details the process to characterize SEU of different FFs. Effects of operating frequency, supply voltage, particle LET, and temperature on SEU cross-section for different FFs are evaluated and actual experimental data are reported. The results are used to create a model that will allow designers to identify optimum design and operating parameters to meet multiple design constraints.

Designers have access to a library containing a wide variety of FF cells and logic circuits with varying levels of performance penalty and radiation hardness. Traditional SE analysis for these FF designs and logic circuits usually compares SE performance for a given set of conditions (supply voltage, speed, temperature, particle LET, etc.). Designers need to identify the best performing (the lowest power requirement) FF designs and logic circuits for meeting SER specifications. Since design library dose not contain such comparative analysis (SER as a function of power), designers have to carry out additional analysis and test. **Chapter 6**, An Empirical Model Based Approach to Explore Design Space for Sequential Circuits, explains a design methodology employing empirical models for identifying the optimum combination of topology, supply voltage, and frequency for a given SEU crosssection specification. By analyzing the sequential circuits based on such an approach, designers will have access to data that will allow them to optimize a circuit design along multiple dimensions (such as SER, power, and operating frequency). Such an analysis may also yield significant power savings while meeting SER and speed specifications.

Chapter 7, Conclusions, summarizes the major contributions of the research.

Fig I.1 is used to summarize the research objectives of this work discussed above. This work main objective is to develop a framework of designing soft-error-aware sequential circuits with power and speed optimization for designers to identify the lowest power designs for meeting SEU and frequency specifications. SEU analysis of sequential circuits in this work has been divided into SEU analysis of FFs and logic circuits. In order to explore designs space of power, SEU, and operating frequency for FFs and logic circuits, SEU analysis of FFs and logic circuits as a function of supply voltage and frequency are carried out in this work. For SEU analysis of FFs, simulation-based method and experimental results are

Figure I.1: Summary of the main research objectives of this work.

discussed in this work (Chapter 5). Experimental results have been used in this work for improving accuracy of the framework. A method to compare SEU performance of different logic circuits for early design phase is presented (Chapter 4). The method is used to created the design space of logic circuits that will allow designers to identify the lowest power designs for meeting SEU and operating frequency specifications. After analyzing the SEU of FFs and logic circuits, the data are imported to the Data Acquisition step. Results from Data Acquisition step are used to calculate the fitting parameters that will allow designers estimate the necessary parameters (e.g., power, frequency, and SEU) quickly and easily during Assessment step. During Assessment step, different logic designs and FFs are evaluated as a function of supply voltage, frequency, power, and SEU with the fitting parameters developed in Quantitative Modeling step. A multi-dimensional chart for all designs is then generated to allow designer to identify the lowest power designs for meeting SEU and operating sections.

Each chapter corresponds to a published paper, and contains expanded detail not included in the paper publication.

#### CHAPTER II

#### BACKGROUND

The overview of radiation effects in digital ICs and radiation environment are summarized in this chapter. In addition, previous methods to predict the SEU at the sequential circuits level are discussed. The fundamentals of power consumption in CMOS circuits, as well as literature review materials to understand the various power minimization techniques are also presented.

# 2.1 Overview of Single-Event Effects in ICs

Electron-hole pairs are created when an energetic particle pass through a semiconductor material. The electron-hole pairs are generated mainly via three mechanisms: coulomb scattering [5], ion-nuclei [6-8], and spallation [9]. When the electron-hole pairs generated in or in the neighborhood of a p-n junction, the charge is collected in the depletion region of the p-n junction, producing a measurable transient photocurrent [10]. The charge collection in IC junctions takes place via drift collection [10], funneling [10-12], and diffuse [5]. In summary, a typical time-dependent current at a struck p-n junction as shown in Fig. II.1. The charge collected  $(Q_{coll})$  in the junction is the integral of the illustrated pulse. The figure illustrates that the rise times are controlled by the drift and the funnel mechanisms, which lasts up to a few hundred picoseconds. The slow component or the tail of the transient is a result of the carriers collected from outside the depletion region of the p-n unction (via diffusion). When electrons or holes released by a particle strike are confined to a well or body region in which a transistor is located, a somewhat similar but distinct mechanism exists. A potential raise in the channel (body) region, for instance for the NMOS transistor, can lower the source/well potential barrier leading to the source injects electrons into the channel [13-15]. The drain collects these electrons, thus increasing the total amount of charge

Figure II.1: Shape of a representative single event pulse measured at a struck p-n junction [5].

collected by the drain region during the radiation event. At circuit-level, this charge will be represented as a transient current and causing a transient voltage glitch. The deposition of the charge in a circuit relate to the particle LET and location of the strike. If the glitch occurs in a combinational node, one or more downstream state elements can be latched due to the glitch. If the glitch occurs in a state holding element, the stored bit can be flipped in the element feedback structure.

# 2.1.1 SEUs in Logic

Three masking factors can prevent the glitch from causing an upset in state, depending upon the input vector applied to the circuit when the strike occurs [25]: 1) Electrical Masking occurs if a SET pulse is not of sufficient magnitude to propagate through logic gates, 2) Logic Masking occurs if a SET pulse dose not have a logically sensitized path through the circuit, 3) Temporal Masking occurs if erroneous SET pulse is not get stored in to a downstream state element.

# 2.1.2 SEUs in FFs

Data loss of FF occurs when the  $Q_{coll}$  exceeds the critical charge ( $Q_{crit}$ ) that is stored in the sensitive node [3].  $Q_{crit}$  is the minimum amount of charge required to flip the nodal value of a feedback structure. It depends on the output capacitance of the struck node, supply voltage, restoring drive, and the feedback delay.

#### 2.1.3 Radiation Environments Overview

Different regions of the magnetosphere including the bow shock, magnetopause, and radiation belts are shown in Fig. II.2 [16]. In space, the main sources of energetic particles

Figure II.2: The Earth's magnetosphere including the solar wind (pictured to the left), bow shock, magnetosheath and magnetopause [16].

(space radiation) are 1) protons and electrons trapped in the Van Allen radiation belts, 2) cosmic or galactic ray protons and heavy ions (from outside the solar system), 3) protons and heavy ions from solar flares, 4) heavy ions trapped in the magnetosphere. Energy to generate the ionization required to cause SEEs are not sufficient for the trapped heavy ions. Also, low-energy electrons are not known to cause SEEs. Therefore, the energetic particles causing

SEU include trapped protons in the radiation belts, cosmic solar particles (heavily influenced by solar flares), and galactic cosmic rays. Some protons undergo nuclear spallation reaction with nuclei (mainly oxygen and nitrogen nuclei) in the atmosphere to produce a number of light particles including neutron, photons, electrons, muons, pions, protons and neutrons, when the energetic protons enter the atmosphere (troposphere and stratosphere) of the Earth.

## 2.1.3.1 The Van Allen Belts

The Inner Van Allen Belt traps high energy protons (energies < 1 GeV) and energetic electrons (less than 0.8 MeV) [17]. High-energy protons can damage spacecraft microelectronics [18]. For example, total dose problems, SEUs, and solar panel degradation can be caused by energetic proton events. Low-energy electrons do not possess enough energy to penetrate shielding materials [19]. At the South Atlantic Anomaly (SAA) the Inner Van Allen Belt dips closest to the Earth's surface and causes an increase in particle flux [20]. Hundreds of satellites operating in low earth orbit (LEO) at the Inner Van Allen Belt. The outer radiation belt in calm solar wind activity traps energetic electrons with energies up to ~10 MeV [21]. High-energy electrons are capable of penetrating spacecraft shielding and contribution to internal charging. Geostationary orbit moves in and out of the outer radiation belt. A region dominated by high-energy electrons and bombarded with energetic protons from solar events [18].

# 2.1.3.2 Galactic Cosmic Rays (GCRs)

GCRs consist mostly of proton (84% hydrogen), alpha particles (15% helium), and less than 1% of heavier nuclei (e.g. C, N, O, Fe) [22]. Major SEUs in electronics are caused by GCRs (>  $10^{14}$  MeV), which in combination with the heavy ions (ions of any element heavier than helium). GCRs are capable of reaching the Earth's magnetosphere at solar

minimum, when the solar wind is low. However, at solar maximum when the high-speed solar wind speeds towards the earth act as a shield, GCRs are prohibited from entering a trajectory towards the magnetosphere. Therefore, the radiation from GCRs peaks at solar minimum and reaches a minimum at solar maximum.

# 2.1.3.3 Terrestrial Environment

The most important product of the cosmic ray showers is the neutrons in terms of SEEs in the atmosphere [23]. An other important contribution of SEEs comes from alpha particles (helium nucleus built with two neutrons and two protons) [24]. Three natural decay chains called Thorium, Radium, and Actinium decay chains cause alpha emitters. Alpha particles lose energy as they penetrate through the package and device. Fig. II.3 shows the LET measured in charge per unit distance (fC/um) in silicon as a function of alpha energy.

Figure II.3: Charge transfer (*solid boxes*) and range (*open boxes*) of alpha particles in silicon [24].

2.2 Previous Approaches to Sequential Logic SEU Analysis

This section reviews several of the SEU model methods that incorporate various masking factors (i.e. electrical, logic, and temporal) that affect whether a fault ultimately appears as an upset in the sequential logic circuits or not.

Analytical model using binary decision diagrams (BDD) and algebraic decision diagrams (ADD) for a unified symbolic analysis for circuit SEU performance is discussed in [26]. SEU\_Tool uses parameterized closed-form circuit models for transient pulse generation, a structural VHDL logic-level simulation for pulse attenuation and propagation, a probabilistic model for transient capture, and a second high-level VHDL logic simulation for bit-error observability [27]. Serfert et al. uses SPICE-level simulation to investigate temporal masking of sequential circuits [28]. Mukherjee et al. have developed a performance model that is accepted for calculating architectural vulnerability factor (AVF) [29]. In [29], AVF is the probability that a fault in a processor structure will result in a visible error in the final output of a program. Other simulation-based approaches that are used to calculate impact of SEU in sequential circuits are [30-33].

#### 2.3 Sources of Power Consumption

Following equation are summarized three sources of power dissipation in digital CMOS circuits:

$$\boldsymbol{P}_{avg} = \boldsymbol{P}_{switching} + \boldsymbol{P}_{short-circuit} + \boldsymbol{P}_{leakage} \tag{II.1}$$

$P_{switching}$  represents the switching power of the circuits.  $P_{short-circuit}$  is due to the directpath short circuit current, which arises when both the NMOS and PMOS transistors are simultaneously active, conducting current directly from supply to ground. Finally,  $P_{leakage}$  is due to the leakage current, which can arise from reverse bias diode currents, sub-threshold effects, gate-oxide tunneling, punchthrough leakage current, and gate induced drain leakage. Each of these components are described in detail below.

2.3.1 Switching Power of the Circuits

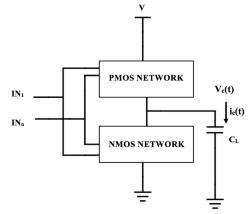

Switching power dissipation occurs when the output of a gate changes states. Fig.

II.4 shows a circuit model for computing the dynamic power. The switching power dissipation is relatively independent of the rise or fall times for the input signals of the CMOS gate and the function being performed (i.e. the interconnection network of the NMOS and PMOS transistors). Referring to the figure, V is an ideal constant voltage source. According to the laws of physics, the voltage  $v_c(t)$  and the current  $i_c(t)$  of a capacitance  $C_L$  at time t are given by [34]

$$i_c(t) = C_L \frac{dv_c(t)}{dt}$$

(II.2)

During the charging cycle from time  $t_0$  to  $t_1$ , the energy  $E_s$  drawn from the voltage source is [34]

$$E_s = \int_{t_0}^{t_1} Vi_c(t) dt \tag{II.3}$$

Figure II.4: Circuit model for computing the dynamic power of a CMOS gate.

Initially the voltage across the capacitor contains no charge, i.e.  $v_c(t_0) = 0$ . Assume that at the end of the charging cycle, the capacitor is fully charged, we have  $v_c(t_1) = V$ . Substituting Equation (II.2) into (II.3), we have [34]

$$E_{s} = C_{L}V \int_{t_{2}}^{t_{1}} \frac{dv_{c}(t)}{dt} dt = C_{L}V \int_{0}^{V} dv_{c} = C_{L}V^{2}$$

(II.4)

Half of this is dissipated immediately in the PMOS network, while the other half is stored on the load capacitance. Then, when the capacitance is discharged, its energy being dissipated in the NMOS network. In summary, an energy of  $C_L V^2$  is consumed when every time a capacitive node switches from ground to V (and back to ground).

This leads to the conclusion that the switching activity of the signals is related to the CMOS power consumption. In this context, the node transition-cycle activity ( $\alpha$ ) is the number of up transitions a circuit node traverses in one period of the clock. If we charge and discharge the capacitance at the frequency of *f* cycles per seconds, for average CMOS power consumption [34,35]:

$$P_{switching} = \alpha C_L V^2 f \tag{II.5}$$

This classical result illustrates that the switching power is proportional to switching activity, capacitive loading, and the square of the supply voltage.

#### 2.3.2 Short-Circuit Component of Power

A direct current path between power supply and ground are turned on for a short period of time during switching when the input waveforms are finite rise and fall times. This causes a short-circuit current from power source to ground and dissipates power. The shape of the short-circuit current curves is mainly dependent on three factors: the duration and slope of the input signal, the I-V curves of the P and N transistors (depend on their sizes, process technology, temperature, etc.), and the output loading capacitance of the inverter [34]. Shortcircuit current can be computed quite accurately using circuit simulators such as SPICE. In the case with no capacitive load, the short-circuit power can be given by [34,35]:

$$P_{short-circuit} = I_{sc} \cdot V = \frac{\beta}{12} (V - 2V_t)^3 \frac{\tau}{T_{clk}}$$

(II.6)

where  $I_{sc}$  arises when both the NMOS and PMOS transistors are simultaneously active, conducting current directly from supply to ground. *V* is the supply voltage value. Let  $\beta$  is the size of the transistors and  $\tau$  is the duration of the input signal. Let  $V_t$  be the threshold voltage of both PMOS and NMOS transistors.  $T_{clk}$  is the operating frequency of the system. The duration of short-circuit current depends on the transition period of the input signal and the output loading capacitance [36].

# 2.3.3 Leakage Component of Power

Two mainly sources of leakage current are described in detail below: reverse-bias diode leakage at the transistor drains, and sub-threshold conduction current. M. Haataja et al. described gate-oxide tunneling, punchthrough leakage, and gate induced drain leakage in detail [47].

# 2.3.3.1 Diode Leakage

When a transistor is turned off and other active transistor charges up/down the drain with respect to the off transistor's bulk potential, there is a diode leakage. The leakage current for the diode is given by [34,35]

$$I_{reverse} = I_s(e^{\frac{V}{V_{th}}} - 1)$$

(II.7)

where  $I_s$  is the reverse saturation current, V is the diode voltage,  $V_{th} = KT/q$  is the thermal voltage (V<sub>th</sub> = 25.9 mV at room temperature). Due to the exponential dependence, the leakage current will be relatively independent of the diode voltage and will equal to the

reverse saturation current. Diode leakage could be significant for a system application which spends much of the time in standby operation.

# 2.3.3.2 Sub-Threshold Leakage

There is a non-zero leakage current through the channel at the microscopic level, even though a transistor is logically turned off. Sub-threshold conduction current is given by [34,35]

$$I_{sub} = I_0 e^{(V_{gs} - V_t)/(\eta V_{th})}$$

(II.8)

where  $V_t$  is the device threshold voltage;  $V_{th} = KT/q$  is the thermal voltage as defined in Equation II.7; and  $I_0$  is the current when  $V_{gs} = V_t$ . The parameter  $\eta$  is a constant depending on the device fabrication process.  $I_{sub}$  drops exponentially as  $V_{gs}$  decreases, since the exponent factor ( $V_{gs} - V_t$ ) has a negative value. At room temperature, the typical values for the sub-threshold slope (the amount of voltage required to drop the sub-threshold current by one decade) lie between 60 to 90 mV/(decade current), with 60 mV/dec being the lower limit.

# 2.4 Low-Power Design Methodologies

In this section, various low-power design techniques will be reviewed which span from the device-level to the circuit-level.

# 2.4.1 Device-driven voltage scaling

One approach to the selection of an optimal power supply voltage for deep-submicron technologies has been proposed based on considering the effects of device level properties involving velocity saturation. As feature sizes shrink below 1 um, carrier velocity saturation under high electric fields needs to be considered for the delay characteristics as a function of lowering the supply voltage. The current drive is significantly reduced due to the carrier velocity saturation and is approximately given by

$$I = WC_{ox}(V_{dd} - V_t)v_{max}$$

(II.9)

where  $v_{max}$  is the maximum velocity. Delay for submicron circuits is relatively independent of supply voltage at high electric fields when consider the equation for delay as  $C_L V/I$ .

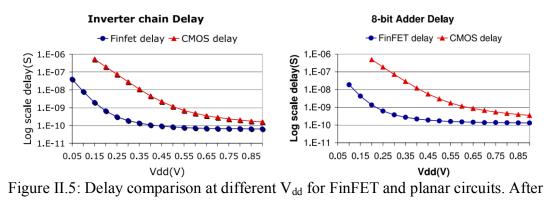

The power supply voltage based on maintaining the speed performance for a given submicron technology is a "technology" based approach [37]. Kakumu et al. yielding the concept of a "critical voltage" which provides a lower limit on the supply voltage [37]. Very little penalty in speed performance when the voltage dropped to some extent for a velocity-saturated device. X. Wu et al. investigated the delays for FinFET and planar CMOS circuits at different voltages in Fig. II.5 [38]. One can observe that for FinFET/planar technology, the lower limit on supply voltage (critical voltage) was found to be about 0.355 V/0.85 V.

2.4.2 Energy-delay minimum based voltage scaling

Another approach for voltage reduction involves minimizing the energy-delay product [39]. Due to a lower supply voltage, there is reduced energy per computation and increased circuit delays for the ICs. The power-delay product (PDP) is used to measure the

[38].

average energy consumed per switching event. The energy-delay product (EDP) unifies a measure of performance and energy. The equation of EDP is given by:

# $EDP(Js) = PDP(J) \times Propagation Delay$

# $= \textit{Propagation Delay} \times \textit{Average Power Dissipation} \times$

# **Propagation Delay** (II.9)

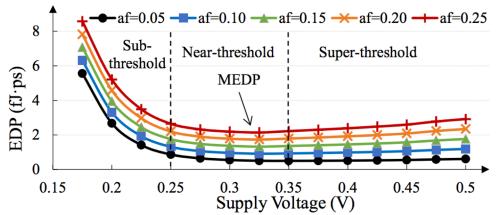

Q. Xie et al. studied the EDP results of a 20-stage inverter chain synthesized by using 7-nm FinFET devices as shown in Fig. II.6 [40]. One can see that the minimal EDP point (MEDP) is in the near-threshold voltage regime ( $V_{MEDP} \approx 0.3$  V).

Figure II.6: Energy-delay product of a 20-stage inverter chain versus supply voltage at different activities factors (af) for FinFET 7-nm. After [40].

# 2.4.3 Voltage Scaling Through Optimal Transistor Sizing

Transistor sizing has been shown to be one of the most effective methods for reducing power consumption in CMOS digital circuits, independent of the choice of circuit topology. There are two issues of to what extent the (W/L) ratios should be used: logic-path gate sizing and gate-transistor sizing [41]. Logic-path gate sizing determines the sizes of the individual gates in relation to each other. On the contrary, gate-transistor sizing decides the best actual transistor sizes of each gate to attain the required performance. S. Turgis et al. investigated the lowest power consumption of a chain of inverters (logic-path gate sizing) is when the tapering ratio equal to 4.25 [42]. However, when we are not allowed to restructure the transistor network, the gate-transistor sizing to attain the required performance needs to be estimated. For a path with general gates, H. Q. Dao et al. studied the minimal energy solution can be obtained by numerically solving a set of equation which was resulted from LaGrang method (different gate efforts) [43]. Inversely, A. Kabbani proposed the equal gate efforts to minimize the switching power dissipation [44]. Equal delay effort with scaled supply voltage technique provides a better power-delay product saving than only equal effort delay technique [45].

# 2.4.4 Voltage Scaling Using Threshold Reduction

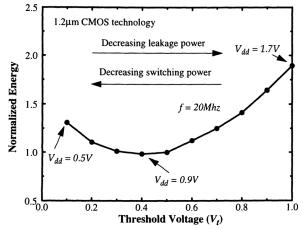

In modern power optimization schemes, the gates on the critical path operate at lower threshold voltage to meet the performance requirements, and the gates on the noncritical paths operate at the higher threshold voltage to reduce the overall power consumption without performance degradation. Also, supply voltage can be scaled down (therefore lower switching power) without loss in speed by reducing the threshold voltage of the device. However, there are two main reasons that threshold voltage cannot be decreased unlimited [46]. The first reason is that the sub-threshold leakage current of the device increases exponentially as the threshold voltage decreases. The second reason is that the process variation the threshold voltage dose not scale accordingly. Moreover, the optimum threshold voltage must compromise between the control of the sub-threshold leakage and improvement of current drive at low supply voltage operation. For example, Fig. II.7 shows energy vs.

Figure II.7: Compromise between dynamic and leakage power dissipation through  $V_t$  variation. After [34].

threshold voltage for a fixed through-put for a 16-bit data path ripple carry adder [34]. The optimum threshold voltage of the 16-bit data path ripple carry adder is around 0.4 V.

# 2.4.5 Leakage Power Reduction Approaches

Various leakage power reduction techniques at circuit level have been investigated [48-52]. These techniques include sleep, stack and sleepy stack, and power gating or MTCMOS for leakage power reduction. P. Oldiges et al. investigated the SEE performance of stacked devices on SOI. The paper shows that stacked devices have the potential to provide SEU immune design [53]. Moreover, it is obvious that most of the leakage power reduction techniques will not significant increase the SEE performance of the ICs. Therefore, in this paper, the SEE performance of leakage power reduction techniques will not be discussed.

#### 2.5 Summary

The fundamentals of power consumption in CMOS circuits has been presented. Equations (II.5), (II.6), (II.7), and (II.8) express the fundamental modes of power dissipation in CMOS ICs. Several basic principles of low power design techniques have been discovered by examining the equations. Since power is proportional to the square of the supply voltage, lowering the power supply voltage is the key to power reduction. However, lowering supply voltage comes at the cost of increased the sensitivity of the circuits to radiation. Since ICs dissipate most of the power when they are switching, an other major focus of low power design is to reduce the power switching activity and the effective switched capacitance. Decreasing capacitance comes at the cost of increased the sensitivity of the circuits to radiation as well. Therefore, design suggestions to the assurance that both the power consumption and SEE performance specifications are not violated are demanding.

In addition, being able to estimate any sequential logic circuits SEUs at different circuit parameters and control variables is necessary for designers to identify best hardening design approaches and confirm to the SEE performance specifications. Most previous approaches for modeling and/or predicting sequential logics SEUs are simulation-based approaches. An approach to couple experimental results and predictive models for SEE performance of logic circuits have been developed in this dissertation. The advantages and disadvantages of the proposed empirical method are compared to the previous approaches.

#### CHAPTER III

#### CHARACTERIZATION OF LOGIC SEES FOR ADVANCED TECHNOLOGY

The following content is an expanded version of a paper that is © 2018 IEEE. Reprinted, with permission, from:

H. Jiang, H. Zhang, R. C. Harrington, J. A. Maharrey, J. S. Kauppila, L. W. Massengill, and B. L. Bhuva, "Impact of supply voltage and particle LET on the soft error rate of logic circuits," *IEEE IRPS*, March 2018.

Logic SER, similar to FF SER are a strong function of particles LET values, supply voltage and operating frequency. If designers focus on hardening FF cells only, unmitigated logic errors may not reduce overall SER to required specifications (especially if operating frequencies are in GHz range). Hence, characterization and mitigation of logic SER is necessary to determine the optimized approach for meeting SER specifications for sequential circuits. This chapter presents experimental results that characterize logic SEEs as a function of LET and supply voltage for 16-nm bulk FinFET technology node. It was observed that only mitigate the SET pulse-width may not necessarily be effective to reduce the strong impact of the supply voltage on the logic SER for the high-LET particles. In addition, the chapter results indicate that particle LET strongly affects logic SEU cross-section and reducing the operating voltages, used for reducing power consumption, will significantly increase SEU cross-section for high-LET particles.

# 3.1 Introduction

Even though soft errors are a major threat to reliability, designers still need to focus

on power consumption first and foremost. Therefore, minimizing power consumption is the primary objective for all designers [54-56]. Reduced supply voltages are used to save power at the expense of increased soft-error rate (SER) [57]. Increased SER is mitigated through the use of hardened flip-flop (FF) cells. Experimental SER data for such FF cells as a function of supply voltage are used to ensure compliance with SER requirements. Such an approach worked very well for old technologies where FF SER dominated the overall SER and logic SER was minimal.

At GHz range of operating frequencies, contribution of logic SER to overall SER is significant [57]. Logic SER, similar to FF SER, are a strong function of particle LET values, supply voltage and operating frequency. If designers focus on hardening flip-flop cells only, unmitigated logic errors may not reduce overall SER to required specifications (especially if operating frequencies are in the GHz range). Hence characterization and mitigation of logic SER is necessary to determine the optimized approach for meeting SER specifications for sequential circuits [58].

Although the SER performance of logic circuits at low-LET particles is well studied for planar bulk CMOS nodes [58], [59-61], characterization for FinFET nodes has been done only for frequency and not for particle LET's or supply voltages [62-63]. In this work, the impact of supply voltage, operating frequency, and particle LET's on the logic SER for the 14/16-nm bulk FinFET node is experimentally characterized. Conventional SER models for logic errors along with experimental SET data are used to explain combined effects of particle LET, supply voltage, and frequency on logic SER.

## 3.2 Test Circuit Description & Experiments

## 3.2.1 Circuit Description

Multiple test ICs containing FF designs and three different logic circuits (*LC-1/2/3*) were fabricated in a 14/16-nm bulk FinFET CMOS technology node from a commercial foundry for SER characterization. The test circuits for DFF and DICE-like FF designs were implemented in CREST [64] configuration with an 8K-stage shift registers. Fig. III.1 shows the block diagram of the CREST circuit. Logic circuit designs were implemented using C-CREST approach [65]. C-CREST design consisted of a shift register design with logic circuits interspersed with DICE-based FF as shown in Fig. III.2. One DICE-based FF along

Figure III.1: CREST block diagram for the test circuit to evaluate SEU effects on flipflops, after [64].

Figure III.2: C-CREST block diagram for the test circuit to evaluate SEU effects on flip-flops and logic circuits, after [65].

with the associated logic circuit comprises a single stage. The fabricated design consists of 2K of such stages to improve the error statistics. NMOS and PMOS transistors in each logic

gate were sized to yield equal sinking/sourcing currents. A separate test IC for autonomously capturing SETs at reduced supply voltages was also designed in a 14/16nm bulk FinFET technology generation. Similar to previous SET test chips, it consists of target logic, a propagation network and an SET capture circuit. Inverter design is utilized (3 fin and low V<sub>t</sub> design). The target logic is constructed by utilizing short logic chains combined in parallel by a balanced OR tree. This test IC used vernier method for measuring SET pulses for different logic gates [66].

#### 3.2.2 Test Details