# SINGLE-EVENT CHARGE COLLECTION AND UPSET IN 65-NM AND 40-NM DUAL- AND TRIPLE-WELL BULK CMOS SRAMS

By

Indranil Chatterjee

Thesis

Submitted to the Faculty of the Graduate School of Vanderbilt University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

Electrical Engineering

May, 2012

Nashville, Tennessee

Approved by:

Professor Bharat L. Bhuva

Professor Ronald D. Schrimpf

#### ACKNOWLEDGMENTS

I am grateful to the Almighty for all the blessings. I would like to thank my parents, who have always been supportive of my endeavors. I would especially like to thank my mom (Ma) without whom I would not have been anywhere near this. She has always been my friend, philosopher and guide. I owe everything I have achieved, to her.

I am indebted to my advisor, Dr. Bhuva. He believed in me and has been the constant source of motivation, pushing me to do things, encouraging me through my failures and inspiring me to achieve more. I am thankful to Dr. Schrimpf for his support and patience during my troubled moments. I would also like to thank Dr. Reed, Dr. Witulski and Dr. Mendenhall for all their help pertaining to my research.

Another person who deserves a special mention is Dr. Balaji Narasimham of Broadcom. Without his support, this work would have been incomplete. I would like to thank Sandeepan and Tania for taking time off their research to teach me TCAD. Sincere thanks to Jon who had been my first point of contact for any problem whatsoever, Nelson and Sri for various technical suggestions. I am thankful to all my friends, especially Nihaar, Akash, Sayan, Jugantor and Satabdi who have been with me through thick and thin.

Lastly, I would like to thank Dr. Kiki Minoglou and Dr. Koen De Munck at IMEC for various technical discussions. I am indebted to Dr. Shi-Jie Wen at Cisco Systems, Inc., Broadcom Corporation and Defense Threat Reduction Agency (DTRA), for supporting and sponsoring this work.

## TABLE OF CONTENTS

| 1.       | Acknowledgments                                                                                                                                                                                            | ii                         |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2.       | List of Figures                                                                                                                                                                                            | iii                        |

| 3.       | List of Tables                                                                                                                                                                                             | viii                       |

| 4.       | Chapter I: Introduction                                                                                                                                                                                    | 1                          |

|          | Single Event Effects: A Brief Overview<br>Triple-well technology<br>Single Event Response of Triple Well Devices: Literature Review<br>Charge-Sharing at advanced technology nodes<br>Overview of the work | 1<br>4<br>5<br>7<br>7      |

| 5.       | Chapter II: 3-D TCAD Simulations                                                                                                                                                                           | 9                          |

|          | Simulation Setup<br>TCAD Structure<br>Mixed Mode Simulation Setup<br>Heavy Ion Simulations<br>Summary                                                                                                      | 9<br>9<br>12<br>12<br>13   |

| 6.       | Chapter III: Mechanisms Behind the SE Response of Dual- & Triple-Well SRAM Cells.                                                                                                                          | 14<br>14                   |

|          | Heavy Ion Simulations<br>Mechanisms behind the Single Event Response                                                                                                                                       | 14                         |

|          | Overview of the Charge Collection Mechanisms                                                                                                                                                               | 16                         |

|          | Charge confinement in triple-well structures                                                                                                                                                               | 18                         |

|          | Very High LET Particle Strike                                                                                                                                                                              | 25                         |

|          | Angular Incidence                                                                                                                                                                                          | 28                         |

|          | Summary                                                                                                                                                                                                    | 33                         |

| 7.       | Chapter IV: Alpha, Neutron and Heavy Ion Simulations                                                                                                                                                       | 24                         |

|          |                                                                                                                                                                                                            | 34                         |

|          | Alpha Particle Irradiation                                                                                                                                                                                 |                            |

|          | Alpha Particle Irradiation                                                                                                                                                                                 | 34                         |

|          | Alpha Particle Irradiation<br>Neutron irradiation<br>Heavy-ion Irradiation                                                                                                                                 |                            |

| 8.       | Neutron irradiation                                                                                                                                                                                        | 34<br>37                   |

| 8.<br>9. | Neutron irradiation<br>Heavy-ion Irradiation                                                                                                                                                               | 34<br>37<br>39             |

|          | Neutron irradiation<br>Heavy-ion Irradiation<br>Chapter V: General Discussion and Conclusion                                                                                                               | 34<br>37<br>39<br>51       |

| 9.       | Neutron irradiation<br>Heavy-ion Irradiation<br>Chapter V: General Discussion and Conclusion<br>Chapter VI: Summary                                                                                        | 34<br>37<br>39<br>51<br>53 |

| Figure |                                                                                                                                                                                                                                                                                                                                   | Page No. |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1      | An illustration showing the generation of electron hole pairs caused by a single event ion strike.                                                                                                                                                                                                                                | 2        |

| 2      | Triple Well NMOS transistors                                                                                                                                                                                                                                                                                                      | 4        |

| 3      | 2D cross-section of the (a) Triple-well and (b) Dual-well 40 nm NMOSFETs                                                                                                                                                                                                                                                          | 10       |

| 4      | 1-D slice showing the doping concentration along a vertical cutline taken through the source of the dual- and triple-well NMOSFETs                                                                                                                                                                                                | 10       |

| 5      | $I_D$ - $V_D$ and $I_D$ - $V_G$ curves a dual-well/triple-well NMOSFET                                                                                                                                                                                                                                                            | 11       |

| 6      | $I_D$ - $V_D$ and $I_D$ - $V_G$ curves a PMOSFET                                                                                                                                                                                                                                                                                  | 11       |

| 7      | Simulation setup (a) Circuit Schematic, 2D cut of a (b) dual well and (c) triple-<br>well NMOSFETs of an SRAM circuit in 3D TCAD and PMOSFETs in<br>Compact Models                                                                                                                                                                | 12       |

| 8      | Cross section of a triple-well NMOSFETs. The dotted arrow shows the location of the ion strike. Doping density and carrier concentrations in p-well (b) prior to ion strike, (c) 10 ps after an ion strike of LET = $1 \text{ MeV-cm}^2/\text{mg}$ , and (d) 10 ps after an ion strike of LET = $35 \text{ MeV-cm}^2/\text{mg}$ . | 15       |

| 9      | Overview of the physical mechanisms responsible for charge collection in triple-well NMOSFETs.                                                                                                                                                                                                                                    | 17       |

| 10     | Potential in the p-well in the (a) dual-well and (b) triple-well device 50 picoseconds after being struck with a particle of LET of 20 MeV-cm <sup>2</sup> /mg. The potential of the p-well is higher in the triple-well device than in the dual-well device.                                                                     | 19       |

| 11     | A schematic of a standard SRAM cell illustrating the upset reversal mechanism observed in a triple-well SRAM cell.                                                                                                                                                                                                                | 20       |

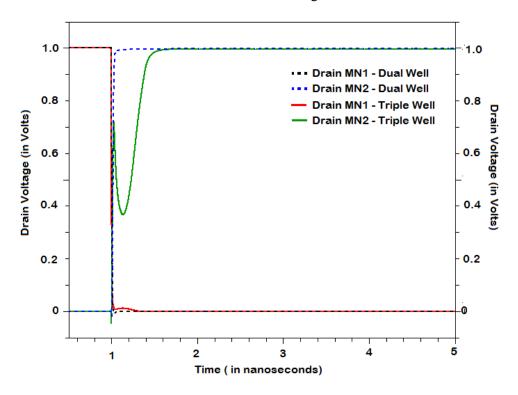

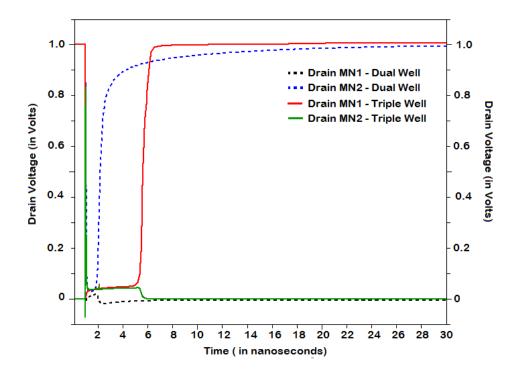

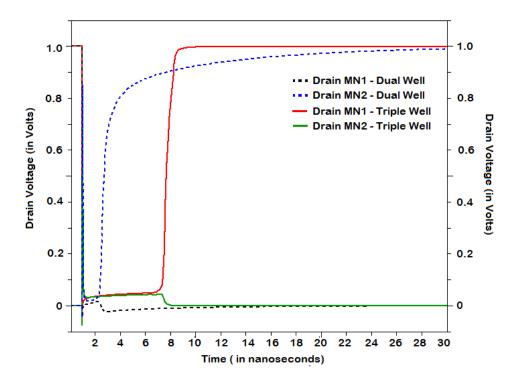

| 12     | Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 5 MeV-cm <sup>2</sup> /mg                                                                                                                                                                             | 21       |

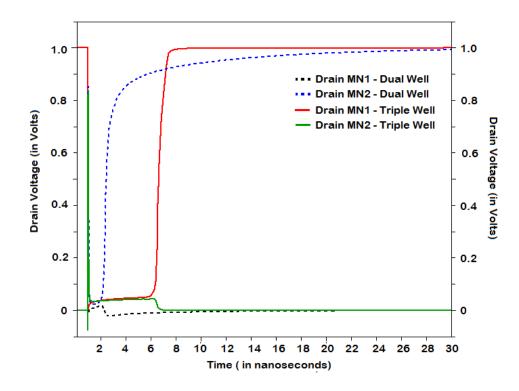

| 13     | Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 10 MeV-cm <sup>2</sup> /mg                                                                                                                                                                            | 21       |

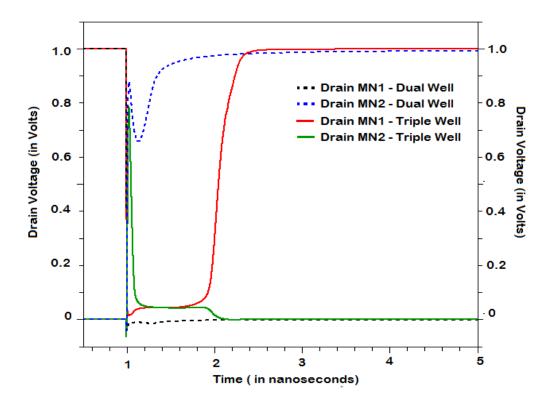

| 14     | Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 20 MeV-cm <sup>2</sup> /mg                                                                                                                                                                            | 22       |

| 15     | Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 35 MeV-cm <sup>2</sup> /mg                                                                                                                                                                            | 22       |

## LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                                     | Page No. |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

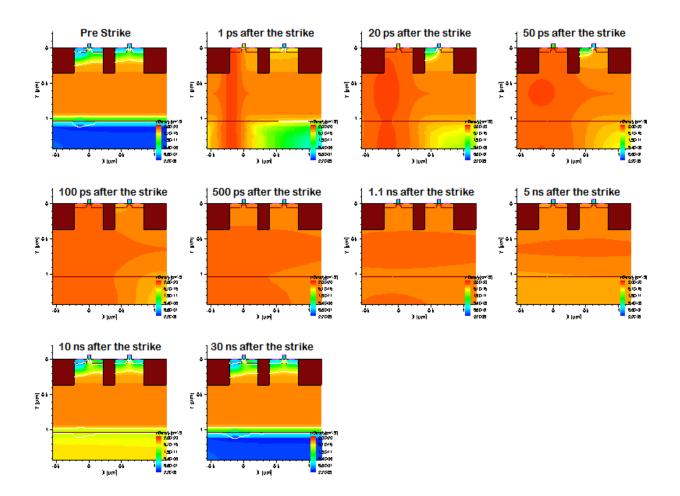

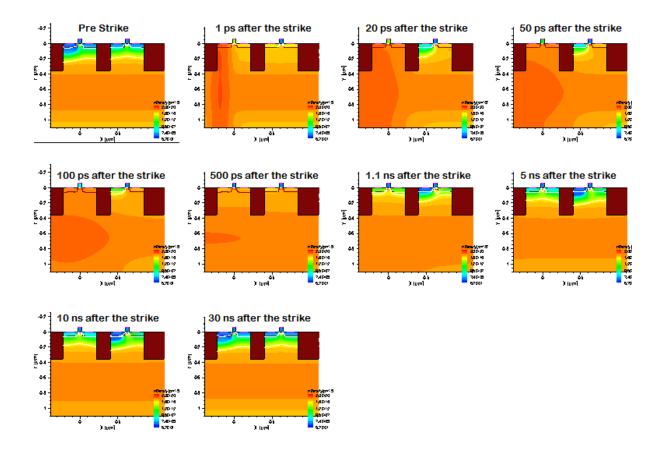

| 16     | Carrier (Hole) concentration in the p-well of the triple-well SRAM cell at various time instants after the drain of transistor MN1 is hit with an ion of LET: 25MeV-cm <sup>2</sup> /mg                                                                                             | 23       |

| 17     | Carrier (Hole) concentration in the p-well of the dual-well SRAM cell at various time instants after the drain of transistor MN1 is hit with an ion of LET: 25MeV-cm <sup>2</sup> /mg.                                                                                              | 24       |

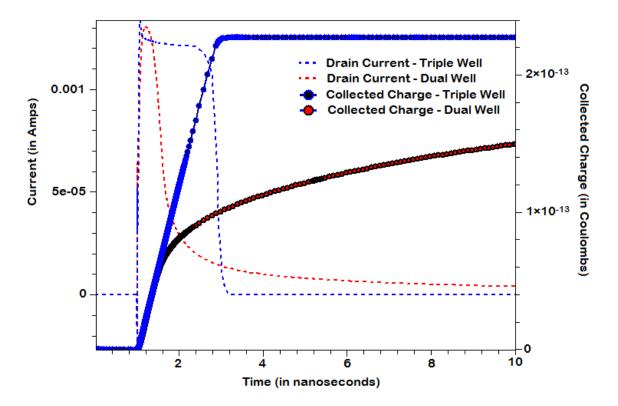

| 18     | Current pulse and charge collected by the second NMOS transistor (MN2) in a dual- and triple-well SRAM cell after the drain of the NMOSFET MN1 is struck with an ion of LET 20 MeV-cm <sup>2</sup> /mg.                                                                             | 25       |

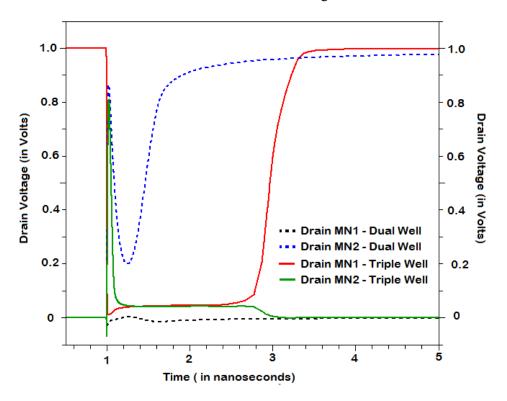

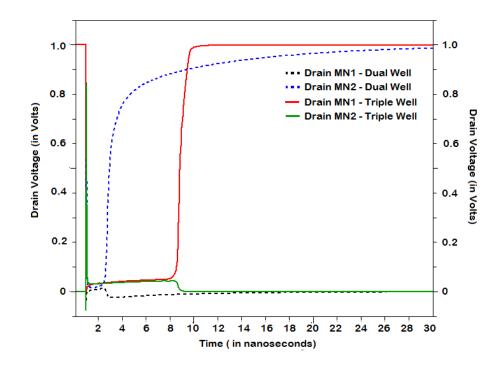

| 19     | Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 45 MeV-cm <sup>2</sup> /mg                                                                                                                              | 26       |

| 20     | Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 55 MeV-cm <sup>2</sup> /mg                                                                                                                              | 26       |

| 21     | Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 65 MeV-cm <sup>2</sup> /mg                                                                                                                              | 27       |

| 22     | Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 75 MeV-cm <sup>2</sup> /mg                                                                                                                              | 27       |

| 23     | 2D cross-section of the dual- and triple-well NMOSFETs belonging to two different SRAM cells                                                                                                                                                                                        | 28       |

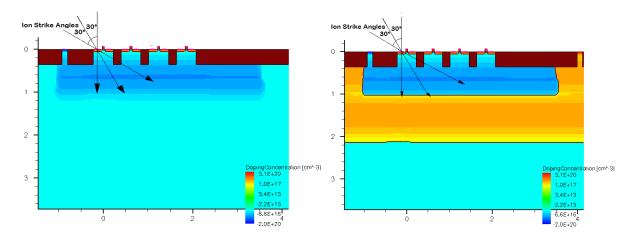

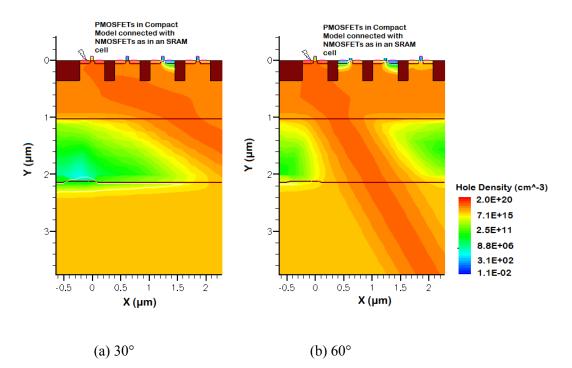

| 24     | Charge cloud in the p-well of a dual-well SRAM cell for a) $60^{\circ}$ and b) $30^{\circ}$ angle of incidence 50 ps after the ion-hit. It is seen that the charge cloud for the $60^{\circ}$ angle of incidence is larger compared to that for the $30^{\circ}$ angle of incidence | 29       |

| 25     | Charge cloud in the p-well of a dual-well SRAM cell for a) 60° and b) 30° angle of incidence 50 ps after the ion-hit. It is seen that the charge cloud affects the SRAM cells in the same well more for the 30° angle of incidence                                                  | 29       |

| 26     | Drain Voltage in both dual-well NMOSFETs when the drain of NMOSFET MN1 of SRAM 1 is struck with an ion of LET 5 MeV-cm <sup>2</sup> /mg at an angle of 30°                                                                                                                          | 30       |

| 27     | Drain Voltage in both dual-well NMOSFETs when the drain of NMOSFET MN1 of SRAM 1 is struck with an ion of LET 15 MeV-cm <sup>2</sup> /mg at an angle of 30°                                                                                                                         | 31       |

| 28     | Drain Voltage in both dual-well NMOSFETs when the drain of NMOSFET MN1 of SRAM 1 is struck with an ion of LET 35 MeV-cm <sup>2</sup> /mg at an angle of 30°                                                                                                                         | 32       |

| 29     | SBU and MBU in the dual- and triple-well SRAM cells after being irradiation with alpha particles                                                                                                                                                                                    | 35       |

| Figure |                                                                                                                                                                                                  | Page No. |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

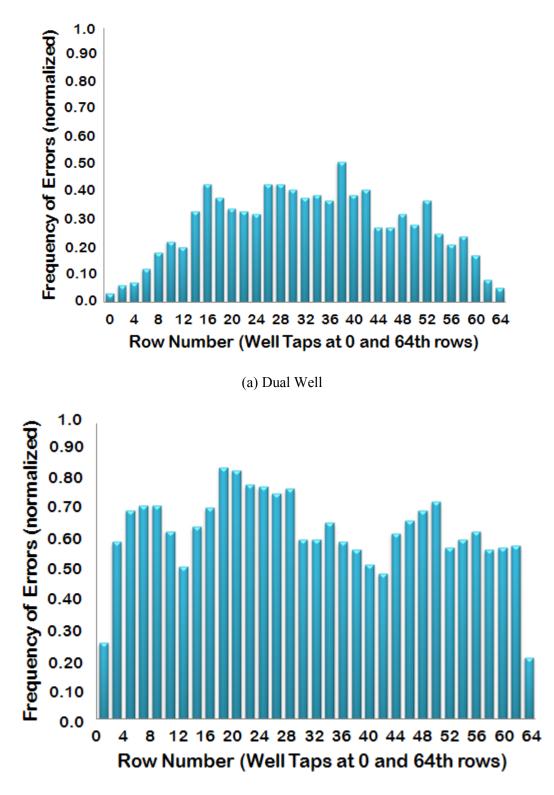

| 30     | Frequency of errors with respect to location for alpha particle irradiation for (a) dual-well and (b) triple well SRAM cells for checkerboard pattern                                            | 36       |

| 31     | Energy spectrum of the LANSCE neutron beam. This spectrum closely resembles the energy spectrum of terrestrial neutrons                                                                          | 37       |

| 32     | Secondary particles generated when a high energy neutron interacts with silicon                                                                                                                  | 38       |

| 33     | Soft error rate in 65 nm dual- and triple-well SRAM cells after being irradiated with high energy neutrons                                                                                       | 39       |

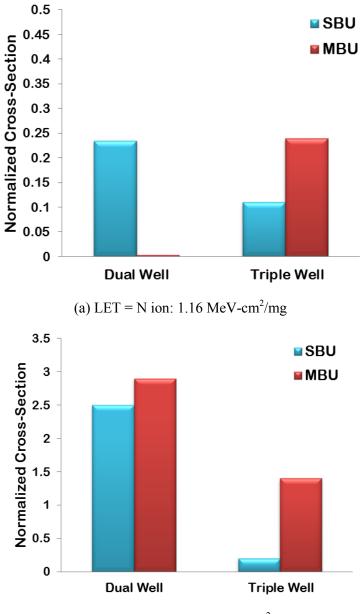

| 34     | Normalized cross section vs. LET for dual-well and triple-well devices for normal incidence irradiation with a (a) checkerboard pattern and (b) ALL-0 pattern.                                   | 41       |

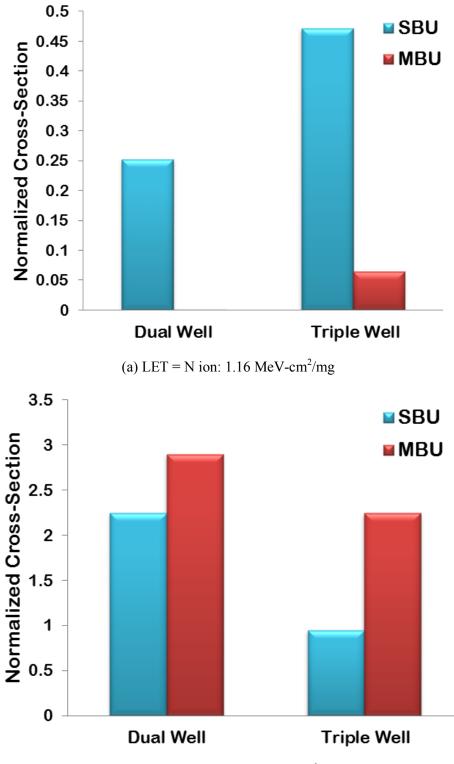

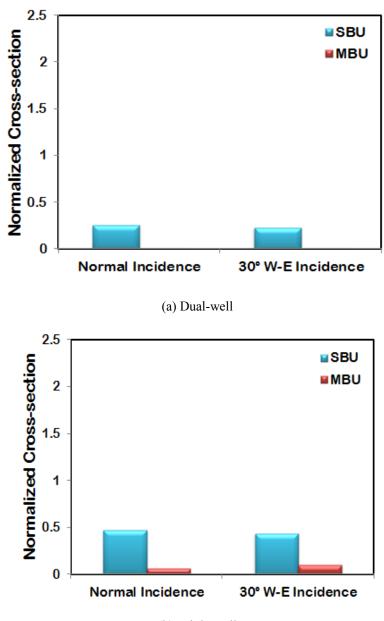

| 35     | SBU and MBU for normal strikes for (a) low LET and (b) high LET for the checkerboard pattern.                                                                                                    | 42       |

| 36     | SBU and MBU for normal strikes for (a) low LET and (b) high LET for the ALL-0 pattern.                                                                                                           | 43       |

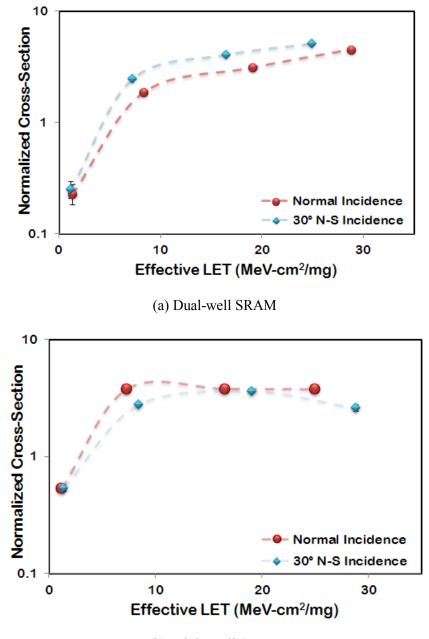

| 37     | Normalized cross section vs. Effective LET for a) dual-well and b) triple-well devices for normal and 30°W-E incidence irradiation with a checkerboard pattern.                                  | 44       |

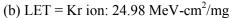

| 38     | SBU and MBU for normal and 30°W-E incidence at low LET (N ion: 1.16 MeV-cm <sup>2</sup> /mg) for a) dual-well and b) triple-well SRAM cells                                                      | 45       |

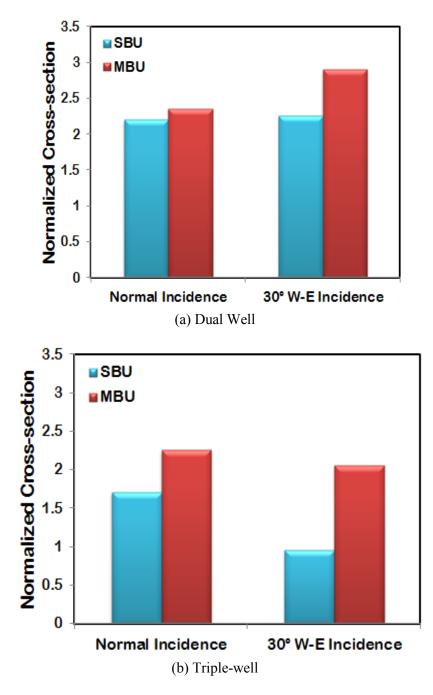

| 39     | SBU and MBU for normal and 30°W-E incidence at high LET (Kr ion: 24.98 MeV-cm2/mg) for a) dual-well and b) triple-well SRAM cells                                                                | 46       |

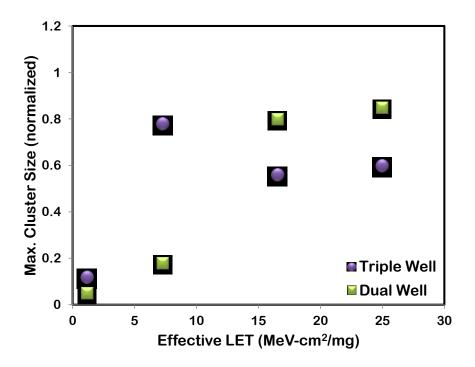

| 40     | Maximum cluster size of recorded errors (checkerboard pattern) for dual-well<br>and triple-well SRAM cells for normal incidence                                                                  | 47       |

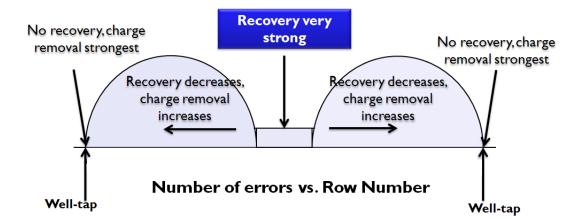

| 41     | Schematic showing the frequency of errors vs. well tap in the SRAM cell                                                                                                                          | 48       |

| 42     | Frequency of errors with respect to location for Ar ion (LET: 8.34 MeV-<br>cm <sup>2</sup> /mg) for (a) dual-well and (b) triple well SRAM cells for checkerboard<br>pattern.                    | 49       |

| 43     | Frequency of errors with respect to location for Ar ion (LET: 8.34 MeV-<br>cm <sup>2</sup> /mg) for (a) dual-well and (b) triple well SRAM cells for checkerboard<br>pattern.                    | 50       |

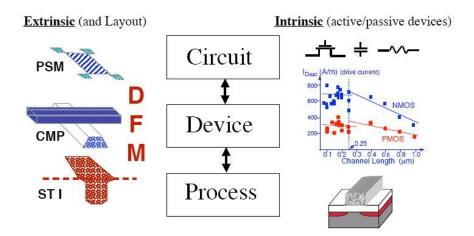

| A1     | Hierarchy of technology CAD tools building from the process level to circuits.<br>Left side icons show typical manufacturing issues; right side icons reflect MOS scaling results based on TCAD. | 59       |

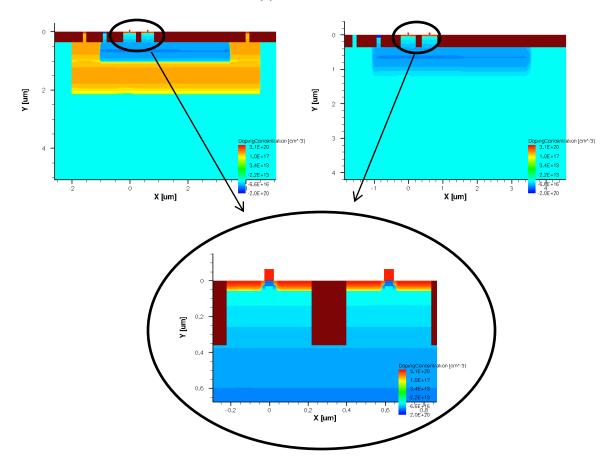

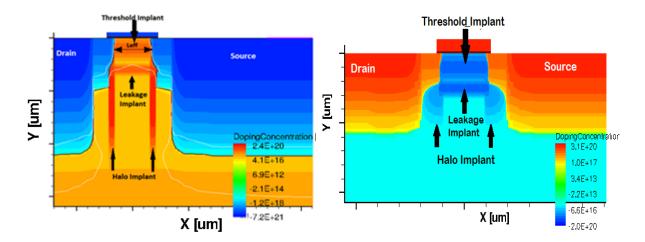

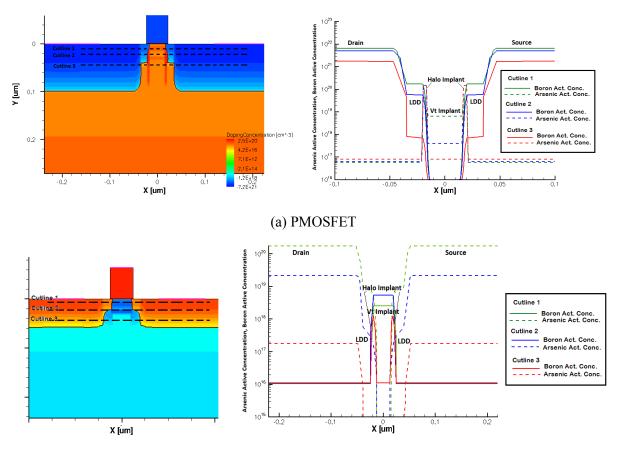

| Figure<br>A2 | 2D Cross-sections of the TCAD Models                                                    | Page No.<br>61 |

|--------------|-----------------------------------------------------------------------------------------|----------------|

| A3           | Close-up view of Source, Drain and the various implants of a) PMOSFET and b) NMOSFET    | 62             |

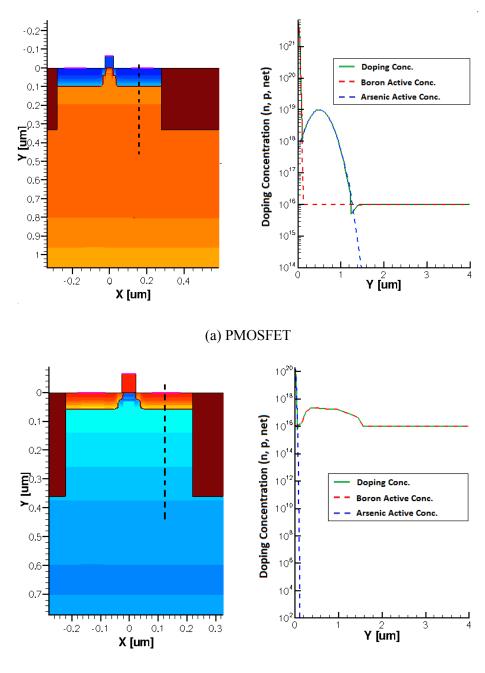

| A4           | 1-D doping cuts showing the well and substrate profiles for the PMOS and NMOS devices   | 63             |

| A5           | 1-d doping cuts showing channel and LDD doping fine structure of a PMOS and NMOS device | 64             |

## LIST OF TABLES

| 1. | Experimental Setup For Neutron Irradiation Tests | 38 |

|----|--------------------------------------------------|----|

| 2. | 16 MeV/Nucleon Heavy Ion Cocktail Components     | 40 |

## **CHAPTER I**

### INTRODUCTION

#### **1.1 Single Event Effects: A Brief Overview**

Since the discovery of May and Woods [1], considerable effort was spent by the semiconductor community to deal with the problem of errors from alpha particles emanating from packaging, metallization and other materials. Similar efforts were made to study the soft error mechanisms arising from protons, neutrons and heavy ions impinging on semiconductor devices. Single-Event Effects (SEE) in microelectronic devices results from highly energetic particles impinging on sensitive regions in a semiconductor device. These particles (e.g., protons, neutrons, alpha particles, or other heavy ions) are present in the natural space environment and they may also be a significant reliability issue for terrestrial applications. Depending on several factors, the particle strike may cause no observable effect, a transient disruption of circuit operation (Single Event Transient, SET), a change of logic state (Single Event Upset, SEU), or even permanent damage (Single Event Gate Rupture, SEGR & Single Event Burnout) to the device or integrated circuit (IC) [2].

There are two primary methods by which ionizing radiation releases charge in a semiconductor device: direct ionization by the incident particle itself and ionization by secondary particles created by nuclear reactions between the incident particle and the struck device. Both mechanisms can lead to integrated circuit malfunction.

**Direct Ionization:** When an energetic nuclear particle strikes a semiconductor material, it loses its energy through Rutherford scattering (Coulombic interactions) with the semiconductor lattice structure. The energy creates electron-hole pairs. When all of its energy is lost, the particle comes to rest in the semiconductor, having traveled a total path length referred to as the particle's range. Direct ionization is

the primary charge deposition mechanism for upsets caused by heavy ions (Heavy Ion: Ion with atomic number greater than or equal to two i.e., particles other than protons, electrons, neutrons, or pions).

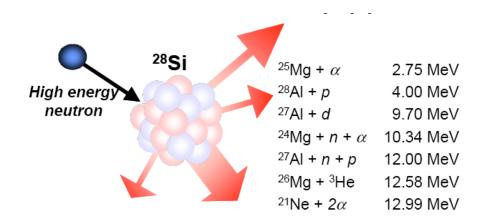

**Indirect Ionization:** As a high-energy proton or neutron enters the semiconductor, it may undergo a collision with a target nucleus. Possible reactions include: 1) elastic collisions that produce Si recoils; 2) the emission of alpha or gamma particles and the recoil of a daughter nucleus (e.g., Si emits alpha-particle and a recoiling Mg nucleus); and 3) spallation reactions, in which the target nucleus is broken into two fragments (e.g., Si breaks into C and O ions), each of which can recoil. The secondary particles, thus generated, deposit charge along the path they traverse by direct ionization, thereby resulting in an upset.

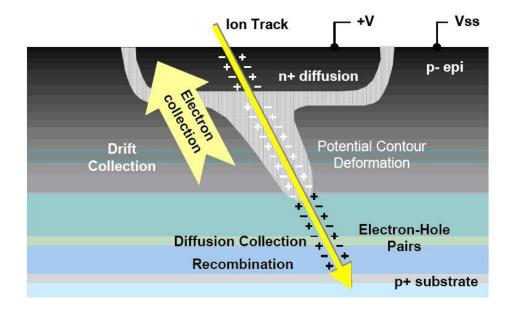

Ions can also lose energy by non-ionizing energy loss (NIEL) where the ion has elastic or inelastic collisions with the atoms of the material. This work focuses only on direct ionization processes. In case of ionizing energy loss, the particle slows down inside the semiconductor through predominantly Compton interactions with the nuclei of the crystalline structure and transfers energy to the lattice and leaves an ionization trail of free electron-hole pairs, as shown in Fig. 1.

Fig. 1: An illustration showing the generation of electron hole pairs caused by a single event ion strike [3]( **R. Baumann**, *IEEE NSREC Short Course*, 2005)

Within an integrated circuit, these excess carriers may come under the influence of an electric field, leading to current transients across device junctions and voltage transients on the circuit nodes. These current and voltage transients may cause loss of data stored in storage cells, such as latches or SRAM cells, resulting in single-event soft errors. These errors are called soft errors because the functionality of the storage cell is not affected. At the next clock cycle (or at the next write cycle at that address in SRAM), the cells accept new data and function normally without any permanent damage.

Direct ionization energy transfer can be quantified by calculating the linear energy transfer (LET) value. LET is defined as the energy loss per unit path length of the particle, typically given in units of MeV-cm<sup>2</sup>/mg after dividing by the density of the target material. Using the LET of the ion, the average energy needed to create an electron-hole pair (EHP) for the material, and the density of the material a calculation of charge deposited per unit length can be done. As a reference, in silicon an ion with an LET of 97 MeV-cm<sup>2</sup>/mg corresponds to a charge deposition of 1 pC/µm [12]. Traditionally heavy ions and alpha particles (heavier nuclei) have been responsible for causing SEE in circuits. However, with technology scaling, particles like muons etc. are also causing substantial effect in devices. In modern electronics the single-event soft error rate (SER) is expected to be higher than the combined failure rate due to device degradation issues, during the lifetime of a product [3]. SRAM cell topology and layout significantly affect the SRAM SER. The inherent feedback in the cell topology amplifies and strengthens the transient effects of the particle strike. SRAM cell layouts are designed to be as small as possible (both to increase density and to increase the frequency of operation). This approach results in decreased critical charge due to reduced transistor currents and nodal capacitances as compared to conventional logic gate designs. On the other hand, decreased cell layout footprint decreases the cell cross-section, resulting in decreased SER. Along with traditional methods of charge collections, new mechanisms such as parasitic bipolar charge injection, Multiple Cell Upsets (MCUs) and multiple-node charge collection have also resulted in a significant increase in the Soft Error Rate (SER) of circuits [4].

Various techniques have been proposed to mitigate the effects of soft errors in electronic circuits, namely error correcting codes [5], Guard Rings [6], Silicon-on-Insulator (SOI) technology [7], DICE latches [8], etc. Triple-well technology (described below) has a lot of electrical advantages compared to dual-well technology. However, the single-event response of such devices is not without ambiguity. While some published literature has reported cases of single-event hardening using triple-well structures, others have reported the opposite. In this work, the underlying mechanisms of the single event response have been studied to understand in detail the response of triple-well devices to ionizing radiation.

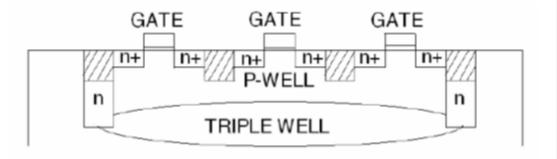

## **1.2 Triple Well Technology**

The aggressive scaling of CMOS technologies has enabled the realization of monolithic systems that integrate high-speed digital circuits with high performance analog circuits [9], [10], and thereby the integration of wireless RF circuitries as well. In such mixed-mode systems, substrate noise coupling has been identified as a major problem [11], [12], [13]. This paved the way for the use of triple-well technology in CMOS manufacturing process. The triple-well technology comprises a buried n-well layer that isolates the p-well from the p-substrate.

Fig. 2: Triple Well NMOS transistors

Triple-well technology is widely used in SRAM cells to improve the isolation of transistors from the substrate [14]. It has several other electrical advantages compared to a twin (dual)-well technology.

For analog circuits, triple well is used for reducing noise and cross-talk. In digital CMOS circuits, triple well technology enables low threshold voltage NMOS transistors to improve the frequency of operation. It may also be used to reduce power locally by modifying the threshold voltage using well bias. A modification of the triple-well technology, described as "merged triple-well' technology, reduces CMOS latchup susceptibility [15]-[16]. However, the implantation of the deep n-well causes damage (interstitials, vacancies, amorphous clusters, and amorphous layers) to the silicon lattice, as shown in [17] which increases the leakage current by a considerable margin. The damage produced is dependent on the dose of the dopants and at higher doses, the damage production rate increases to the extent of initiating amorphization of silicon. The threshold voltage of a triple-well NMOS device, similarly, increases first with increasing implant dose, and then decreases due to amorphization of the substrate bias condition. This is an advantage for noise isolation, mixed signal and dynamic threshold MOSFET applications. Additionally, allowing independent biasing of the substrate allows for biasing of the channel region in the isolated region, and providing a different back-bias condition, or dynamic threshold MOS (DTMOS) devices [18].

## 1.3 Single Event Response of Triple Well Devices: Literature Review

There have been conflicting reports about the single event performance of triple-well devices. One of the earliest references that discuss the influence of triple-well structures on the radiation response of devices was by Burnett et al. The paper showed that the use of a triple-well technology resulted in a reduction in the alpha-particle-induced soft error rate (SER) in 0.5-µm BiCMOS technology [19]. A 4Mb SRAM was fabricated in a triple well, and also in a p-well/p-substrate with a p+ buried layer. A standard BiCMOS process exhibited ~7X higher SER than a standard CMOS process. The authors attributed this difference to the p-well/n-substrate junction under the array for the CMOS process. The presence of the p+ buried layer or a deep n-well in a BiCMOS process was observed to reduce the charge collection [20]. The best results were obtained using a triple-well structure that reduces SER by ~600%. Roche et al.

showed that triple wells brought about a 40% decrease in alpha-particle-induced SER for SRAMs fabricated in a 130 nm technology and a 25% decrease in a 90 nm technology [21]. It was observed that triple-well structures reduce the SER sensitivity as the electrons generated deep inside the substrate are more efficiently collected by the extended n buried zone and then better evacuated through n-well ties. Similar observations were made by Kishimoto *et al.*, Noda *et al.*, and Sato *et al.* [22]-[23]. In 0.25 $\mu$ m technology, a shallow triple well and 4T SRAM cell with stacked capacitor were used to improve the soft error rate by 3.5X compared to a conventional SRAM cell [24]. In this 0.25  $\mu$ m process, Sato *et al.* demonstrated an increase of storage node capacitance from 8fC to 25fC by using a stacked-type capacitor with a two-layer polysilicon. Alpha and neutron irradiation was performed on the 64K × 36 bit SRAM. It was observed that the increased storage capacitance prevented the particle-generated charge from overwhelming the stored data, thereby exponentially improving the soft error immunity. It was hypothesized in this paper that a shallow triple-well structure reduces the possibility for charge to be generated because of the shallow depth of the p-type well through which the ion strike passes. The effect of the deep n-well was used along with the effect of increased storage node capacitance to obtain low soft error rate (SER).

While some of the published literature reports that the use of triple-well structures is beneficial to reducing error rates, many report the opposite. Puchner et al. found that using a triple-well increases the Failure-in-Time (FIT) rate for heavy ions in a 90 nm CMOS technology [25]. In this case, a triple-well scheme has been implemented on an 18-Mb fast synchronous SRAM by using a high energy implant to evaluate its impact on the alpha-particle-induced accelerated soft error rate. It was observed that because of the collection of holes in the p-well of the triple-well structure, the well gets de-biased. The excess holes can be removed by recombination with minority carriers or through the well contacts. The recombination rate is much lower than the generation rate of the free carriers by the particle hit and thus results in greater charge collection by the transistors, which increases the overall error rates by as much as 3x. Later in this thesis we will observe how charge confinement in the p-well will affect the single event

response of triple-well structures on a positive note. Roy et al. showed that the use of a triple-well technology results in greater transient pulse-widths in 90 nm inverter circuits [26]. They detailed the charge collection mechanisms in a 90 nm triple-well inverter circuit and it was observed that primarily because of the p-well de-bias, the pulse-widths were larger compared to dual-well structures. Combinational-logic circuits fabricated in a 65 nm technology showed a similar trend [27]. Mostly, these results were obtained using separated transistors so that only a single transistor collected charge due to an ion hit. Because of these apparently conflicting results for triple-well structures, it is important to understand the single-event response of triple-well transistors more thoroughly over a wide range of particle LETs.

#### 1.4 Charge-Sharing at advanced technology nodes

With greater packing density at advanced technology nodes, multiple node charge collection becomes important. Black et al. showed that at 65 nm SRAM cells can recover from upset because of well collapse source injection mechanism arising from charge-sharing at high LETs [28]. Ahlbin et al. showed that for 90 nm and 130 nm technologies, single event transient pulse-widths in combinational logic may decrease for irradiation with particles that have high LETs [29]. Seifert et al. demonstrated reinforcing charge collection between nMOS transistors using dummy gates [30]. While Black et al. focused on charge-sharing between nMOS and pMOS transistors in SRAM cells, Ahlbin et al. and Seifert et al. described multiple node charge collection between similar transistors in combinational and sequential circuit elements. Thus the charge collection mechanisms in a triple-well structure are bound to be affected by charge sharing between adjacent transistors. This work focuses on the effects of multiple node charge collection between nMOS transistors in triple-well SRAMs.

### 1.5 Overview of the work

In this work, a detailed analysis of the single-event response of dual-well and triple-well structures is reported over a wide range of particle LETs. Simulations were performed over a wide range

of deposited charge to observe the effects of charge-sharing in these structures. From these simulations, it was observed that triple-well technologies are more vulnerable than dual-well technologies for particles with low LET values, whereas for particles with moderate and high LET values, dual-well designs are more vulnerable. Chapter II details the 3D TCAD simulation setup used to understand the mechanisms of charge collection while Chapter III reports the underlying mechanisms of charge collection in dual- and triple-well structures. It was found that charge confinement and multiple node charge collection triggers the "Single Event Upset Reversal" in triple-well structures that lowers the soft error rate compared to dual-well structures at high LETs. Alpha, neutron and heavy-ion tests were carried out on SRAM designs built in both dual-well and triple-well technologies at 65 nm and 40 nm technology nodes in order to verify the simulation results obtained. Results for heavy-ion exposure are reported in Chapter IV. Chapter V briefly discusses the effects of various process parameters on the single-event upset reversal mechanism. The calibration of a 40 nm commercial NMOS and PMOS transistor is described in Appendix A and the Structure Editor and Sdevice scripts used in the simulations are included in Appendix B.

### **CHAPTER II**

## **3-D TCAD SIMULATIONS**

#### 2.1 Simulation Setup

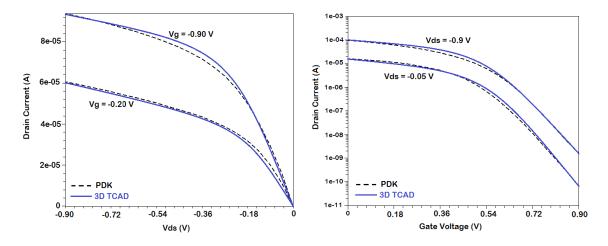

Simulations are used to analyze the single-event performance of dual- and triple-well NMOSFETs. Simulation results in the form of electrostatic potential and carrier concentration plots are used to explain the physical mechanisms of charge collection in triple-well devices. The device structures simulated using 3D TCAD are described in this chapter. Two NMOSFETs are constructed in 3-D TCAD in dual and triple well technology to simulate single event upsets caused by ion strikes on or near the drain of the NMOSFETs. The drains of the NMOSFETs are loaded with PMOSFETs and connected to simulate an SRAM cell, so that circuit effects on the behavior of the devices can be obtained. The aspect ratio of the PMOSFET simulated by means of a compact model is detailed in this chapter. Also, the parameters of the ion strikes are mentioned.

#### **2.2 TCAD Structure**

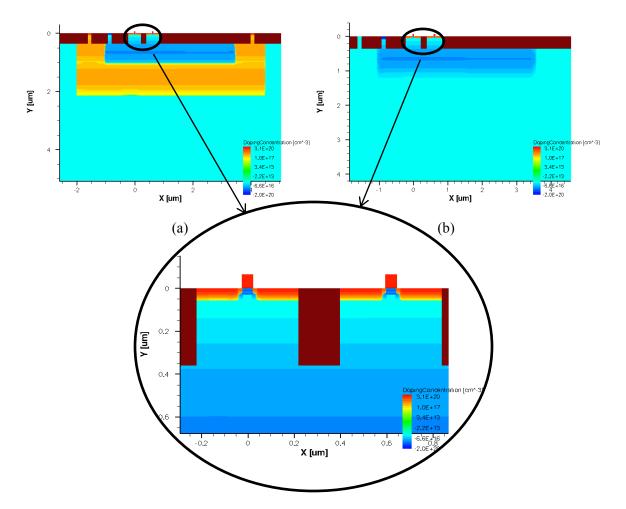

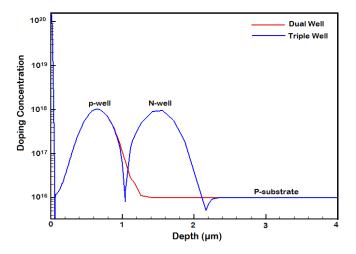

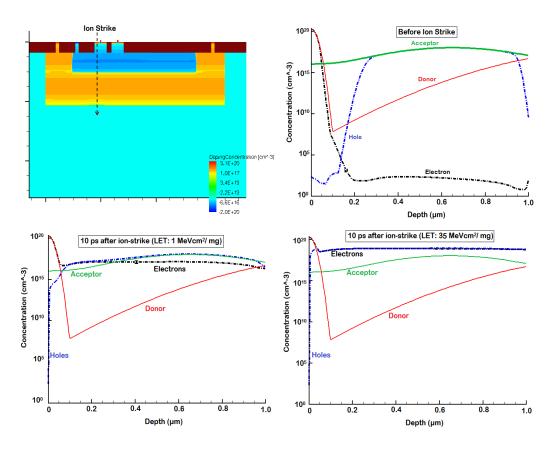

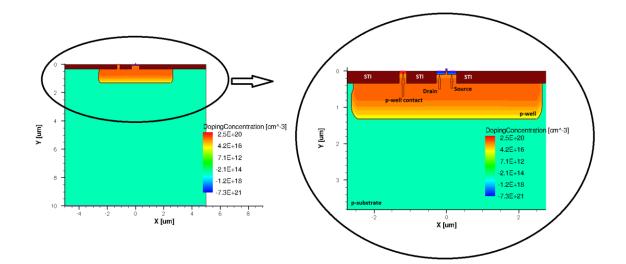

Synopsys® Sentaurus Structure Editor is used to create the 3-D NMOS transistors in order to study the single event effects on these devices. The devices belong to the 45 nm technology nodes. Figs. 3(a) and 3(b) show the 2D cross-sections of the dual- and triple-well NMOS transistors respectively while Fig. 4 shows a 1-D cut showing the doping concentration along a vertical cutline taken through the source of the dual- and triple-well NMOSFETs. On a p-substrate having a constant doping of  $1 \times 10^{16}$  cm<sup>-3</sup>, a buried n-well is made having a Gaussian doping profile. The p-well enclosed by the n-well has a Gaussian doping profile that peaks at  $1 \times 10^{18}$  cm<sup>-3</sup>. The doping and dimensions for the dual-well NMOS system were obtained after iterative simulations in order to match the commercial 45nm PDK. The n-well doping was adjusted so that the net doping at the surface where the NMOS device was built remained the same

Fig.3: 2D cross-section of the (a) Triple-well and (b) Dual-well 40 nm NMOSFETs

Fig. 4: 1-D slice showing the doping concentration along a vertical cutline taken through the source of the dual- and triple-well NMOSFETs

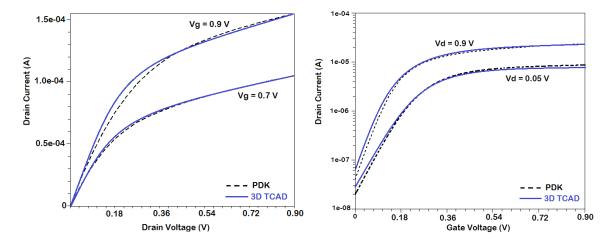

for both the dual- and triple-well systems. The TCAD transistors were calibrated to match the DC and AC electrical characteristics of the Process Design Kit (PDK). The DC characteristics curves are shown in Figs. 5 and 6.

Fig. 5:  $I_D$ - $V_D$  and  $I_D$ - $V_G$  curves a dual-well/triple-well NMOSFET. The dashed lines are from the PDK while the solid lines are of the calibrated devices.

Fig. 6:  $I_D$ - $V_D$  and  $I_D$ - $V_G$  curves a PMOSFET. The solid lines are from the PDK while the dashed lines are of the calibrated devices.

The simulation shows a close match with the PDK curves. The threshold voltage and the drive current are very similar in both cases. The block of silicon used for the simulations was  $10 \ \mu\text{m} \times 10 \ \mu\text{m} \times 10 \ \mu\text{m}$ .

Fig. 7: Simulation setup (a) Circuit Schematic, 2D cut of a (b) dual well and (c) triple-well NMOSFETs of an SRAM circuit in 3D TCAD and PMOSFETs in Compact Models.

## 2.3 Mixed Mode Simulation setup

The TCAD NMOS transistors described in the previous section are connected to PMOS devices. A calibrated BSIM3 compact model of the PMOS transistor is used. The simulations are carried out on a SRAM cell thus formed. The mixed mode simulations are performed to obtain the effect of an active load on the struck node, and to observe the circuit effects on the voltage and current at the struck node.

## 2.4 Heavy Ion Simulations

The charge deposited by the incident ions was modeled using a Gaussian radial profile with characteristic 1/e radius of 50 nm, and a Gaussian temporal profile with a characteristic time of 2 ps. It

may be noted that a Gaussian radial profile is not the best estimate for a single-event ion track profile [31], [32]. It has been observed that a realistic ion track may which conforms to the Kobetich and Katz (KK) theory [33], has a greater charge density in the track core compared to the Gaussian profile, often used in TCAD simulations. It was observed that the actual ion-track profile resembled more of an exponential function, rather than a Gaussian approximation. However, simulations carried out with both Gaussian and a realistic ion-track structure showed saturation in SET pulse widths for 90 nm inverters [32]. In the simulations carried out in this paper, the Gaussian ion-track has been used in conjunction with SRH and Auger recombination mechanisms that would provide a realistic trend from the simulations in terms of charge density in the track. Additionally, the total charge deposited is the same with both Gaussian and realistic tracks, corresponding to the incident particle LET. In this work, the charge deposited by the incident ion is important as that would determine whether the "single-event upset reversal" would trigger or not and the ion track profile would not influence the underlying mechanisms described here.

The circuit was simulated in an initial state with the output of inverter I1 HIGH and that for I2 LOW, which results from transistors MN1 and MP2 being in the OFF state and transistors MP1 and MN2 being in the ON state. The ion was incident on (or near) the drain region of transistor MN1, as shown in Fig. 7(a).

### 2.5 Summary

The device structure and the setup used for the simulation of single event effects in dual-well and triple-well devices are described in this chapter. The following chapters describe the result of simulating ion strikes on the devices described here. The mechanisms of charge collection in these devices are developed based on the results obtained from the simulations.

## CHAPTER III

## MECHANISMS BEHIND THE SINGLE EVENT RESPONSE OF DUAL- AND TRIPLE-WELL SRAM CELLS

In this chapter, an SRAM cell is simulated and the drain of the OFF NMOSFET is struck with ions. Ion strikes of different LET values are considered. The p-well contacts of the dual-well and triple-well devices are of comparable sizes. The upset pulses at drain of an NMOSFET built in a triple well are compared with those in a dual well. The single-event upset voltage and current pulses are shown here.

#### **3.1 Heavy Ion Simulations**

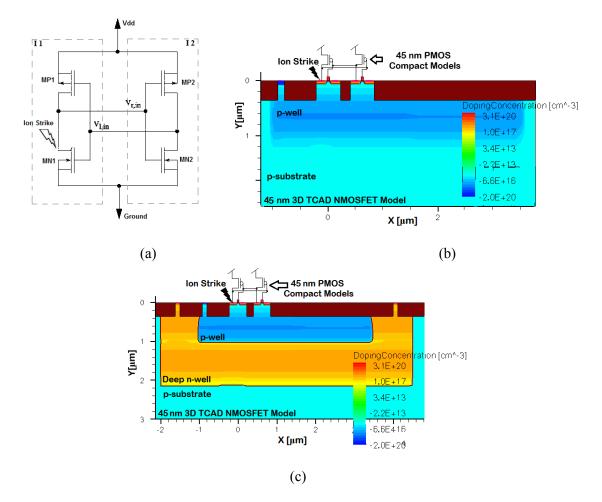

Ion strikes that deposit a maximum initial charge density lower than the background doping of the substrate are classified here as low-LET ion strikes. Fig. 8 shows the acceptor and donor concentrations and the free carrier densities before and 10 ps after the peak of the carrier generation occurs for an ion strike of LET 1 and 35 MeVcm<sup>2</sup>/ mg.

It can be seen that the charge density deposited by an ion strike of LET =  $1 \text{ MeVcm}^2/\text{ mg}$  at the peak of the Gaussian temporal profile (time t = 1 ns) hardly surpasses the background doping, while that deposited by an ion having LET =  $35 \text{ MeV-cm}^2/\text{mg}$  deposits a charge density two orders of magnitude greater than the background doping density at the peak of the Gaussian temporal profile (time t = 1 ns. The difference in the physics of these two cases shall be explained in the following section.

The upset pulse width depends on the LET of the ion. The following section shows the voltage and current characteristics of dual- and triple-well NMOS drains when struck by ions having different energies. First the simulated results for normal incidence are presented for LETs of 5, 10, 20 and 30 MeV-cm<sup>2</sup>/mg, followed by angled hits. Angular strikes have been simulated for LETs of 5, 15 and 25 MeV-cm<sup>2</sup>/mg for 30° and 60° angle of incidence. Further simulations for very high LETs (> 40 MeV- $\frac{1}{2}$

cm<sup>2</sup>/mg) are presented. The physics behind the single event response of dual- and triple-well SRAM cells are discussed in the following section.

Fig. 8: (a) Cross section of a triple-well NMOSFETs. The dotted arrow shows the location of the ion strike. Doping density and carrier concentrations in p-well (b) prior to ion strike, (c) 10 ps after an ion strike of LET =  $1 \text{ MeV-cm}^2/\text{mg}$ , and (d) 10 ps after an ion strike of LET =  $35 \text{ MeV-cm}^2/\text{mg}$ .

#### 3.2 Mechanisms behind the Single Event Response

In this section, the fundamental mechanisms of charge collection in dual- and triple-well structures are described. The simulation results obtained in the previous chapter are discussed in detail and the physical mechanisms behind the results are investigated. We discover a new phenomenon described as the **SINGLE EVENT UPSET REVERSAL MECHANISM**, which explains the single event response of triple-well structures at moderate to high LETs.

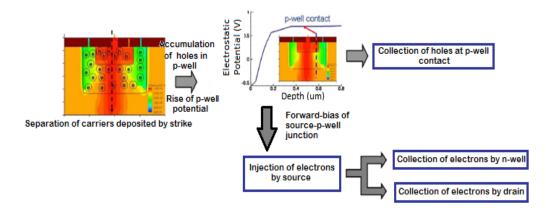

#### 3.3 Overview of the Charge Collection Mechanisms

The differences in mechanisms related to charge collection and removal in both the technologies are discussed below. The mechanisms have been discussed in detail in [26]. In this section, it is necessary to recapitulate the mechanisms.

The major difference between dual-well and triple-well technologies arises due to the presence of deep n-well structure in triple-well devices. The differences in collected charge for these technologies is affected by the amount of charge collected by a p-well, amount of charge injected by a source region, presence or absence of parasitic bipolar transistors, and the charge removal through p-well contact. Each of these mechanisms is briefly discussed for both technologies below. Fig 9 shows a summary of the charge collection mechanism in triple-well technology.

### A) Charge Collection in the p-well

In dual-well technology, when a strike occurs, the electrons generated in the p-well are collected by the source and drain of the NMOSFET. The holes are removed from the well by the p-well contact. The majority of the holes generated by the strike get distributed over the well and the substrate. Thus, there is just a slight increase in the p-well potential. In the case of a triple well technology, the electrons generated in the p-well due to the ion strike are collected by the n-well. The electric field in the p-well/n-well depletion region confines the holes to the p-well. This causes a large potential increase in the well, which is much greater than the p-well potential rise in dual-well.

## B) Electron Injection from the Source

The sources of NMOSFETs in both the technologies are tied to the ground potential. The large potential perturbation in the p-well in a triple-well technology due to an ion hit, forward biases the p-well—source junction of the NMOSFET. Thus the electric field at this junction injects electrons from the source of the NMOSFET into the p-well. In the dual well, the source–p-well junction is not forward biased as the p-

well-potential perturbation is small, resulting in very little electron injection into the p-well from the NMOSFET source region.

#### C) Parasitic Bipolar Action

In a triple-well device, the electrons that are injected into the p-well, need to find an n-doped region to go into. This is provided by two n-doped regions, the drain of the NMOSFET and the n-well. Thus here are two parasitic bipolar paths in this technology. One is the source--p-well--n-well path and the second is the source--p-well—drain path. Both of these parasitic transistors play a role in charge collection and the resultant voltage perturbations. These parasitic bipolar transistors are absent in dual-well technologies due to smaller well-potential perturbations.

## D) Charge Removal through p-well Contact

For a triple-well technology, the n-well--p-well junction is reverse-biased and this allows electrons to drift into the n-well region. As long as the charges are not completely removed from the p-well, it stays at a higher potential, thereby forward biasing the source–p-well junction causing more electrons to be injected into the p-well and collected by the drain. Thus, the key point for faster recovery of the system lies in the faster removal of holes from the p-well, which is thus dependent on the size and location of the p-well contact.

Fig. 9: Overview of the physical mechanisms responsible for charge collection in triple-well NMOSFETs. [26]

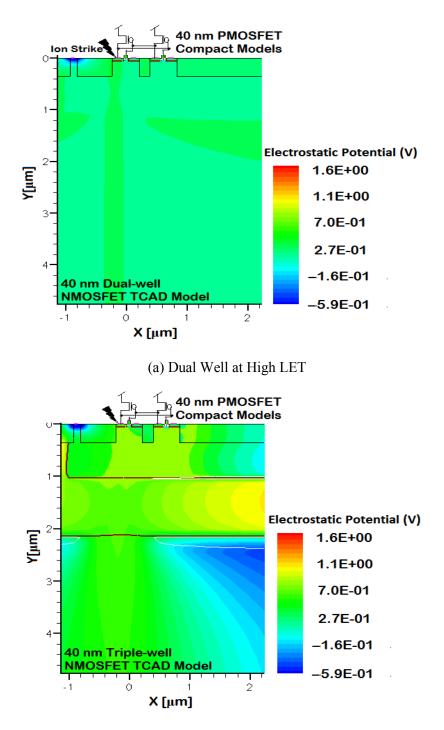

#### 3.4 Charge confinement in triple-well structures

Soft error rates for SRAMs depend on the critical charge of the circuit and the amount of charge collected by sensitive circuit nodes. The collected charge depends on the charge generation and transport processes. In a triple-well structure, the deep n-well–p-well junction is reverse-biased. This causes the electrons to drift into the n-well, leaving the holes behind in the p-well. In a dual-well technology, the holes spread throughout the p-substrate, while in a triple-well technology, majority of the holes are confined within the p-well. This may be termed as "charge confinement". Thus, the electrostatic potential perturbation in the p-well of a p-substrate dual-well technology is less than that in the p-well of a triple-well technology (Fig. 10).

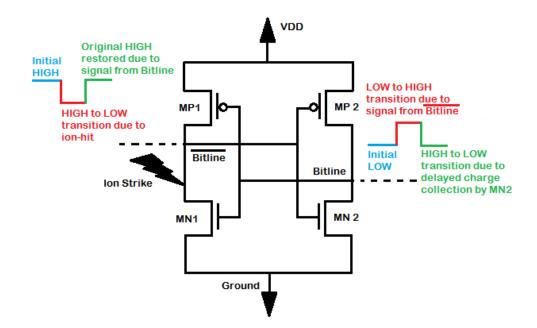

The parasitic bipolar effect is reduced in the dual-well technology, decreasing the collected charge. Also, charge confinement in the triple-well structure may lead to a higher number of multiple-cell errors within a single p-well [4]. This is why dual-well technology is sometimes considered to be superior to triple-well technology from a soft-error point of view. As shown in Fig. 10, the change in substrate potential under the NMOS transistors is much less in the dual-well technology than in the p-well of the triple-well technology for high LET ion strikes. The charge confinement in the well affects other OFF transistors in the same well. When the ion hit occurs, the nMOS transistor (MN1) is OFF and when it collects charge, the output of inverter I1 goes from HIGH to LOW. This turns the nMOS transistor (MN2) in the opposite inverter (I2) OFF and the pMOS transistor (MP2) ON. The output of the inverter 12 goes from LOW to HIGH and the OFF nMOS transistor (MN2) collects the residual charge in the pwell of the triple-well system. As MN2 collects charge, it turns ON and the output of the inverter I2 goes from HIGH to LOW and subsequently the feedback mechanism inherent in the SRAM cell changes the output of the inverter I1 from LOW to HIGH. Thus the original state of the cell is restored. The entire process is shown schematically in Fig. 11. We term this phenomenon "Single Event Upset Reversal" which is similar to the "Pulse Quenching" mechanism observed in combinational logic, also known as "Reinforcing Charge Collection" [30].

(b) Triple Well at High LET

Fig. 10: Potential in the p-well in the (a) dual-well and (b) triple-well device 50 picoseconds after being struck with a particle of LET of 20 MeV-cm<sup>2</sup>/mg. The potential of the p-well is higher in the triple-well device than in the dual-well device.

Fig. 11: A schematic of a standard SRAM cell illustrating the upset reversal mechanism observed in a triple-well SRAM cell.

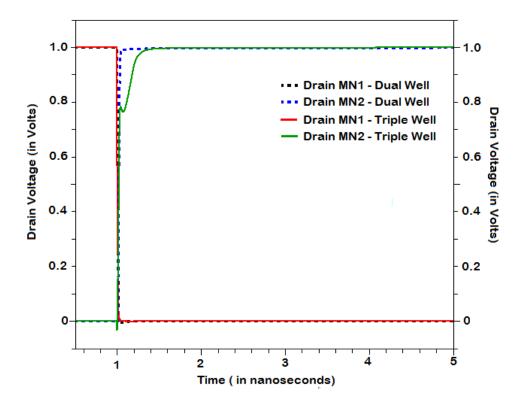

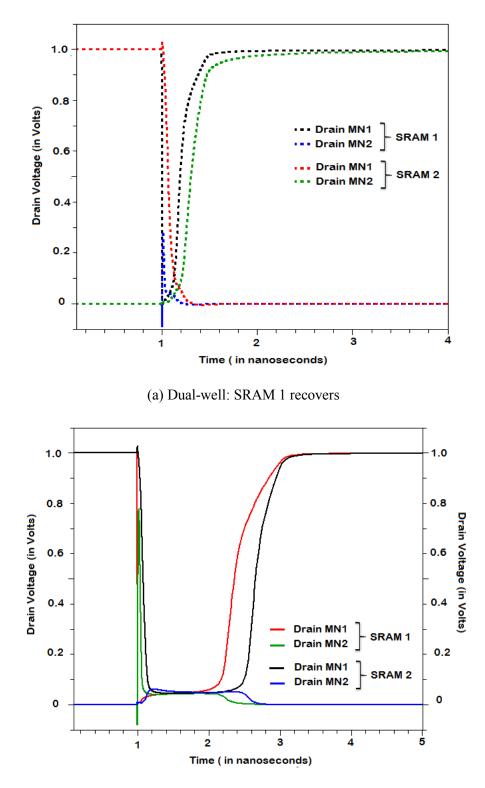

Figs. 12-15 show the drain voltage perturbations of both nMOS transistors (MN1 and MN2) after an ion hit. For a low-LET particle hit (5MeV-cm<sup>2</sup>/mg, in this case), both the dual-well nMOS transistors upset, but the triple-well transistor shows the signs of a delayed charge collection (Fig. 12). This effect is more pronounced in Fig. 13. In the triple-well system, the second nMOS transistor (MN2) tries to recover due to residual charge collection, but there is not enough charge available for the drain voltage to recover fully to its original value. On the other hand, for a high-LET particle strike (typically above 15 MeVcm<sup>2</sup>/mg), the amount of charge available for the second triple-well NMOS transistor (MN2) to collect is sufficient to reverse the upset. Fig. 14 shows this effect where the drain of the transistor MN1 was struck with an ion of LET 20 MeV-cm<sup>2</sup>/mg. Here, the drain voltage of MN2 fully recovers to its original state. The mechanism described above is actually two upsets in sequence happening within an SRAM cell. Fig. 13 shows the drain voltages for an ion hit of LET 35 MeV-cm<sup>2</sup>/mg. It shows that the system recovery time now increases to a few nanoseconds.

Fig. 12: Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 5 MeV-cm<sup>2</sup>/mg

Fig. 13: Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 10 MeV-cm<sup>2</sup>/mg

Fig. 14: Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 20 MeV-cm<sup>2</sup>/mg

Fig. 15: Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 35 MeV-cm<sup>2</sup>/mg

Although the dual-well system shows signs of delayed of charge collection, there is never enough charge in the system to trigger the upset reversal mechanism.

Figs. 16 and 17 show the carrier concentration in the p-well of a dual- and triple-well system for a particle strike of LET 25 MeV-cm<sup>2</sup>/mg. The concentration of the holes in the p-well determines whether the p-well is de-biased. Thus, as long as there are excess carriers in the system, the OFF transistors can collect charge. In the dual well, the hole concentration of the well 1.1 ns after the ion-strike is similar to the pre-strike condition, while in the triple well, enough charge is left in the system for the OFF nMOS transistor to collect and turn ON.

Fig. 16: Carrier (Hole) concentration in the p-well of the triple-well SRAM cell at various time instants after the drain of transistor MN1 is hit with an ion of LET: 25MeV-cm<sup>2</sup>/mg.

In the dual-well system, 5 ns after the strike, almost all of the deposited charge has moved out of the system while in the triple-well, the well is still de-biased. Charge collection by the second NMOS transistor is less in dual-well SRAM cells.

Fig. 17: Carrier (Hole) concentration in the p-well of the dual-well SRAM cell at various time instants after the drain of transistor MN1 is hit with an ion of LET: 25MeV-cm<sup>2</sup>/mg.

Fig. 18 shows the current pulse and the charge collected by NMOSFET MN2 in both the dualand triple-well systems for an ion-strike of LET =  $20 \text{ MeV-cm}^2/\text{mg}$ . As a result of this delayed multiple node charge collection, the SRAM cell restores back to its original state, thereby nullifying the effects of the ion-strike. This phenomenon may decrease the overall soft error rates for SRAM cells at high LETs in a triple-well process.

Fig. 18: Current pulse and charge collected by the second NMOS transistor (MN2) in a dual- and triple-well SRAM cell after the drain of the NMOSFET MN1 is struck with an ion of LET 20 MeV-cm<sup>2</sup>/mg.

## 3.5 Very High LET Particle Strike

The simulations were extended for very high LETs (>40 MeV-cm<sup>2</sup>/mg) for both dual- and triplewell structures. It was seen in Fig. 15 that the second transistor in the dual-well system showed effects of delayed charge collection. For higher LETs, the dual-well systems show more pronounced effects of multiple node charge collection, but the system never recovers, unlike triple-wells. Figs. 19-22 show the drain voltages of the SRAM cell on being struck with ions of LETs 45, 55, 65 and 75 MeV-cm<sup>2</sup>/mg. It is observed that the cell recovery time increases with increasing LET for triple-well structures. Delayed charge collection is observable in dual-well structures as well, but the SRAM cells never recover to their original states.

Fig. 19: Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 45 MeV-cm<sup>2</sup>/mg

Fig. 20: Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 55 MeV-cm<sup>2</sup>/mg

Fig. 21: Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 65 MeV-cm<sup>2</sup>/mg

Fig. 22: Drain Voltage in both dual-well and triple-well NMOSFETs devices when the drain of NMOSFET MN1 is struck with an ion of LET 75 MeV-cm<sup>2</sup>/mg

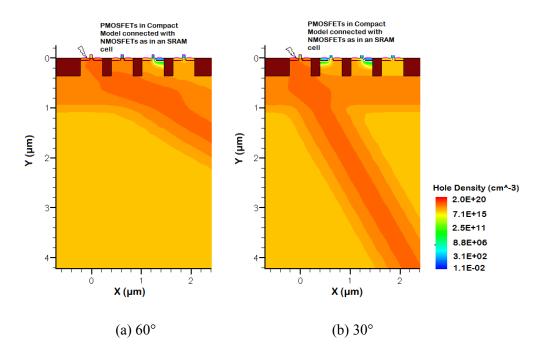

#### **3.6 Angular Incidence**

The previous section dealt with ion strikes at normal incidence. In this section, we explore ion strikes occurring at certain angles. Two angles of incidence ( $30^\circ$  and  $60^\circ$ ) are discussed for three different LETs (10, 25 and 35 MeV-cm<sup>2</sup>/mg.). Two SRAM cells were simulated using TCAD in an ALL-1 pattern. The 2D cross-section of the structure is shown in Fig. 23.

Fig. 23: 2D cross-section of the dual- and triple-well NMOSFETs belonging to two different SRAM cells.

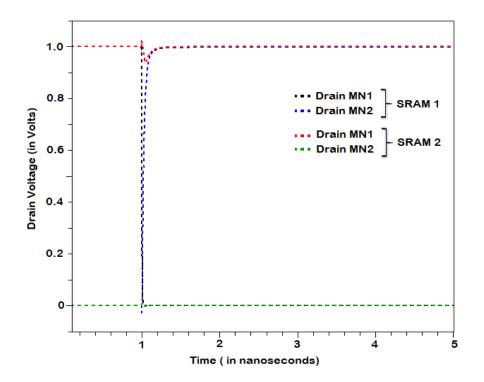

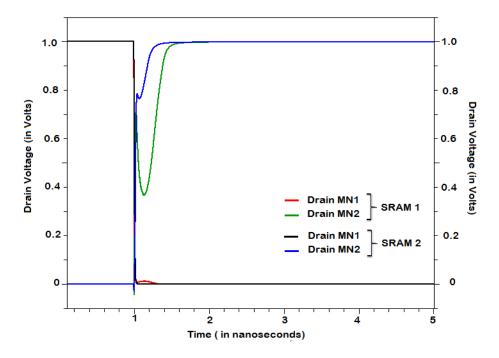

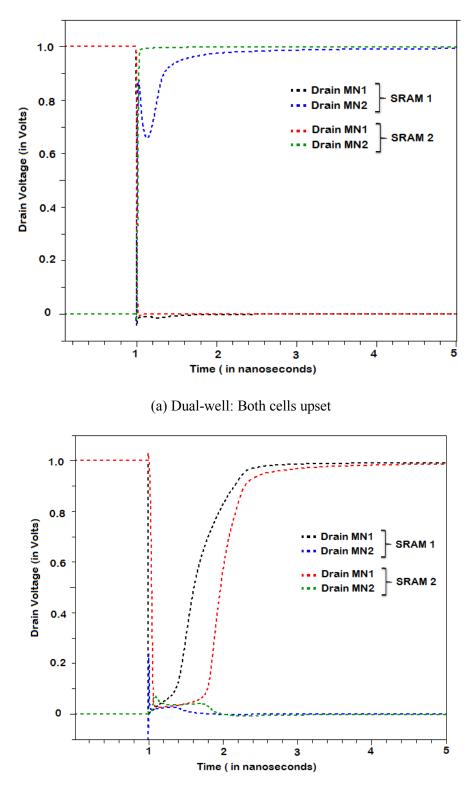

It is observed that strikes at 30° or 60° angle of incidence create a larger charge cloud compared to that of normal incidence. This is shown in Figs. 24 and 25. Thus, greater numbers of SRAM cells are affected by the charge cloud. Because of the charge confinement in triple-well systems, the charge cloud impacts transistors much more severely than it does in dual-well systems. The voltage characteristics of the NMOS transistors of both the SRAM cells are shown in Figs. 26-28 for 30° angle of incidence. It is seen that for low LET (5 MeV-cm<sup>2</sup>/mg) for 30° angle of incidence, both the SRAM cells upset in case of the dual-well system while one of the triple-well SRAM cell (the one hit) upsets. However, for moderate to high LETs (15 MeV-cm<sup>2</sup>/mg and 35 MeV-cm<sup>2</sup>/mg), the struck SRAM cell recovers its original state because of the single event upset reversal mechanism. However, the second cell still upsets whereas in triple-well systems, both the SRAM cells recover.

Fig. 24: Charge cloud in the p-well of a dual-well SRAM cell for a)  $60^{\circ}$  and b)  $30^{\circ}$  angle of incidence 50 ps after the ion-hit. It is seen that the charge cloud for the  $60^{\circ}$  angle of incidence is larger compared to that for the  $30^{\circ}$  angle of incidence.

Fig. 25: Charge cloud in the p-well of a dual-well SRAM cell for a)  $60^{\circ}$  and b)  $30^{\circ}$  angle of incidence 50 ps after the ion-hit. It is seen that the charge cloud affects the SRAM cells in the same well more for the  $30^{\circ}$  angle of incidence.

(a) Dual-well: SRAM 1 upsets, SRAM 2 does not

(b) Triple-well: Both SRAMs upset

Fig. 26: Drain Voltage in both dual-well NMOSFETs when the drain of NMOSFET MN1 of SRAM 1 is struck with an ion of LET 5 MeV-cm<sup>2</sup>/mg at an angle of  $30^{\circ}$

(b) Triple-well: SRAM 1 recovers

Fig. 27: Drain Voltage in both dual-well NMOSFETs when the drain of NMOSFET MN1 of SRAM 1 is struck with an ion of LET 15 MeV-cm<sup>2</sup>/mg at an angle of  $30^{\circ}$

(b) Triple-well: Both cells recover

Fig. 28: Drain Voltage in both dual-well NMOSFETs when the drain of NMOSFET MN1 of SRAM 1 is struck with an ion of LET 35 MeV-cm<sup>2</sup>/mg at an angle of  $30^{\circ}$

For 60° angle of incidence, the effects of multiple node charge collection are even more predominant. While for low and moderate LETs, the trend was similar to as shown in Figs. 24-25, for high LET ion strikes (30 MeV-cm<sup>2</sup>/mg), both the SRAM cells in the dual-well system upset.

### 3.7 Summary

This chapter dealt with the simulation results of heavy ion irradiation on dual- and triple-well SRAM cells over a wide range of particle LETs. Simulations were done for normal and angular incidence. It was observed that nMOS transistors in a triple-well usually collect more charge during a single event strike than those in a dual-well due to charge confinement within the well. For high LET values, however, charge collection at more than one node in a triple-well technology may restore the original state of the SRAM cells in the vicinity of the strike. Thus, for high-LET particles (typically above 15 MeV-cm<sup>2</sup>/mg), the triple-well SRAMs do not always upset. We describe this phenomenon as "single-event upset reversal". This phenomenon decreases the soft-error rate in certain circumstances, particularly those dominated by ions with high LET values. Dual-well nMOS transistors collect less charge for low LET strikes and thus typically have a lower error rate for environments in which low LET particles dominate.

For angled strikes, it was seen that for moderate and high LETs, the single event upset reversal was observed in dual-well NMOSFETs as well. However, the effect was much more pronounced in case of triple-well structures. In the following chapter, the experimental results for alpha, neutron and heavy ion irradiation on 40 nm dual- and triple-well SRAM cells are discussed as a verification of the theory developed in this chapter.

### **CHAPTER IV**

### ALPHA, NEUTRON AND HEAVY ION IRRADIATION

4MB SRAM chips were fabricated using two different process technologies. The design and layouts were similar, with the only difference being that one chip was fabricated in a dual-well CMOS process and the other in a triple-well process technology. The chips were subjected to alpha-particle, neutron, and heavy-ion irradiations. The thickness of the back-end-of-line overlayers at this technology node is approximately 10 µm.

### 4.1 Alpha-Particle Irradiation

## 4.1.1 Experimental Setup

Alpha-particle soft error testing was conducted using Americium-241at Vanderbilt University. The source was deposited as a liquid on a thin foil and allowed to dry. The source spot size was 20 mm in diameter and the deposited activity level was 300 nCi. The flux measured at the surface of the source was 6.4x10<sup>6</sup> hr<sup>-1</sup>cm<sup>-2</sup>. All parts were opened to expose the die face and the <sup>241</sup>Am source was mounted at a distance of 15 mm above the SRAM. The test procedure was compliant with the JEDEC SER test standard labeled JESD89A [34]. The tests were carried out for the Checkerboard, ALL-0 and ALL-1 patterns.

#### 4.1.2 Results

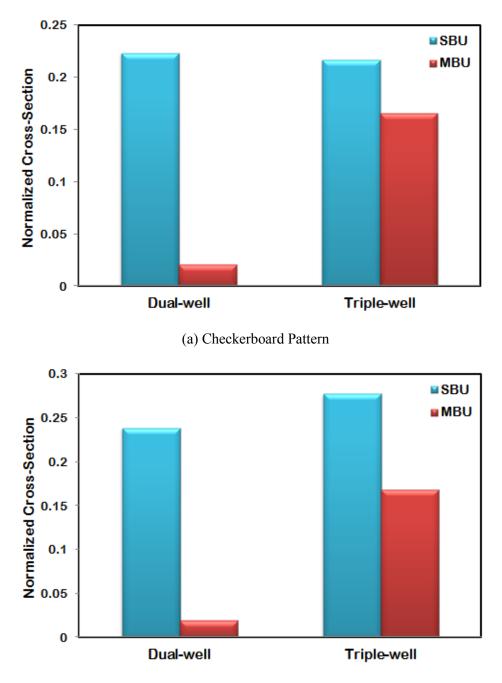

The simulation results for low-LET ion strikes indicated that dual-well transistors collect less charge and are less vulnerable to upsets. The experimental results from alpha irradiation showed a similar trend. Fig. 30 shows the Single Bit Upsets (SBUs) and Multiple Bit Upsets (MBUs) observed in the dualand triple-well systems on alpha particle irradiation while Fig. 31 shows the location of errors with respect to the well-taps.

(b) ALL-0 Pattern / ALL-1 Pattern

Fig. 29: SBU and MBU in the dual- and triple-well SRAM cells after being irradiation with alpha particles

(b) Triple-well

Fig. 30: Frequency of errors with respect to location for alpha particle irradiation for (a) dualwell and (b) triple well SRAM cells for checkerboard pattern.

It is seen that the number of errors is much less in dual-well systems compared to triple-well structures. The concentration of errors does not vary a lot with respect to the location. However, near the

well taps, the triple-well cells records the least number of errors as the charges are quickly removed from the system. Alpha particle energy deposition is in the same range as low-LET ions. The results show that dual-well SRAM cells perform better compared to the triple-well systems for low energy deposition. This is similar to the simulation results for low LET ions.

### **4.2 Neutron Irradiation**

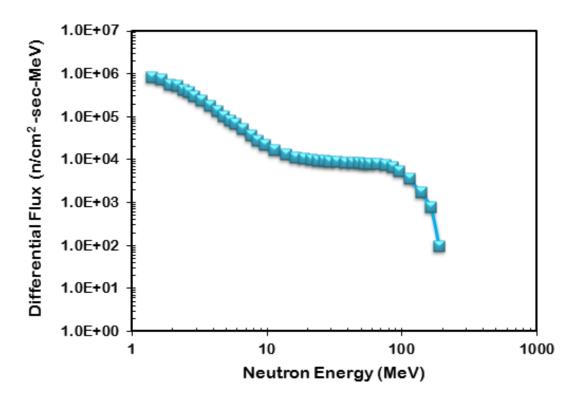

## 4.2.1 Experimental Setup

SRAM circuits fabricated in dual-well and triple-well 65-nm technologies were irradiated with high-energy neutrons at the Weapon Neutron Research test facility, Los Alamos Neutron Science Center (LANSCE). This neutron energy spectrum, shown in Fig. 31, closely resembles the sea-level neutron spectrum for energies from 10 to 500 MeV. The exposure was carried out at room temperature and with a

Fig 31: Energy spectrum of the LANSCE neutron beam. This spectrum closely resembles the energy spectrum of terrestrial neutrons.

checkerboard pattern over a wide range of supply voltages and temperature. The range of LETs of the secondary particles generated by the neutrons is 2-12 MeVcm<sup>2</sup>/mg, as shown in Fig. 32.

Fig. 32: Secondary particles generated when a high energy neutron interacts with silicon

The experimental conditions are listed in the following table.

TABLE I: EXPERIMENTAL SETUP FOR NEUTRON IRRADIATION TESTS

| Test Conditions | Voltage (in Volts) | Temperature (in °C) |                    |

|-----------------|--------------------|---------------------|--------------------|

| 1               | 1.2                | 35                  |                    |

| 2               | 1.1                | 35                  | Voltage Dependence |

| 3               | 1.3                | 35                  | Test               |

### 4.2.2 Experimental Results

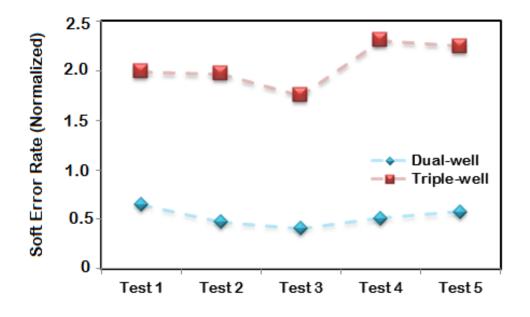

The results show that for triple-well technology, the error rates are much higher compared to dual-well technology, as shown in Fig. 33 below. In highly scaled technologies, multiple-cell upsets contribute significantly to the total error rate due to charge-sharing between adjacent transistors. The number of multiple-bit upsets was also higher in case of triple-well SRAM cells.

Fig. 33: Soft error rate in 65 nm dual- and triple-well SRAM cells after being irradiated with high energy neutrons

### 4.3 Heavy Ion Irradiation

### 4.3.1: Experimental Setup

Heavy-ion tests were performed over a wide range of LETs at Lawrence Berkley National Laboratory (LBNL) at  $V_{DD} = 1.2$  V with the SRAMs in either a checkerboard or an ALL-0 pattern. The design and layout for the dual- and triple-well structures were similar and both were fabricated in a commercial 40 nm bulk CMOS process. The total thickness of the back-end-of-line overlayers at this technology node is approximately 10  $\mu$ m. A 16 MeV/nucleon cocktail was used for the tests. The tests were carried out with four heavy ions (N, Ar, Cu and Kr) at normal incidence, 60° N-S (along bitlines) and 60° W-E (along wordlines). The range of particle LETs used was 1–30 MeV-cm<sup>2</sup>/mg. Table I lists the ion beams, the corresponding energy, LET values and the ranges.

#### TABLE II

| Ion                             | Energy<br>(MeV) | LET<br>(MeV/mg/cm <sup>2</sup> ) | Range <sub>Bragg</sub><br>(µm) | Range <sub>final</sub><br>(µm) |

|---------------------------------|-----------------|----------------------------------|--------------------------------|--------------------------------|

| <sup>14</sup> N <sup>+5</sup>   | 234             | 1.16                             | 505                            | 508                            |

| $^{40}{\rm Ar}^{+14}$           | 642             | 8.34                             | 243                            | 256                            |

| <sup>63</sup> Cu <sup>+22</sup> | 1007            | 16.53                            | 169                            | 190                            |

| <sup>78</sup> Kr <sup>+27</sup> | 1226            | 24.98                            | 142                            | 163                            |

### 16 MEV/NUCLEON COCKTAIL COMPONENTS

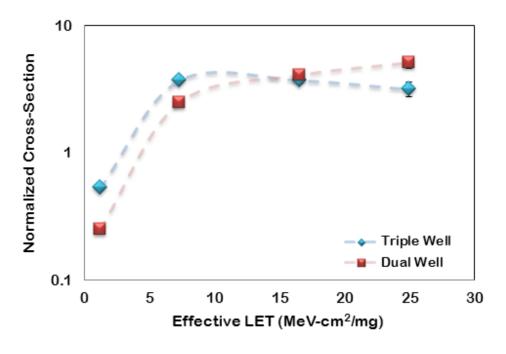

### 4.3.2: Experimental Results: Normal Incidence

The test results for normal incidence are shown in Fig 34. The data in the figure are normalized with a single factor for effective presentation. Based on the number of events measured, the error bars for these data are less than 10% of the mean value across all LETs. For particles with low LET, the triple-well structures have a greater soft-error cross-section. As the LET of the incident particles increases, the dual-well designs become more vulnerable compared to the triple-well designs. For SRAMs built in advanced-technology nodes, multiple-bit upsets (MBUs) are predominant [10]. Figs. 35 and 36 show the single-bit upset (SBU) and MBU cross-sections for dual- and triple-well SRAM cells at low and high LETs. For low-LET particle strikes, the MBU cross section is higher for triple-well structures compared to dual-well structures, whereas for particles with higher LETs, MBUs increase significantly in dual-well designs. Both SBU and MBU events are lower for triple-well devices compared to dual-well devices for high-LET particle strikes.

(a)

Fig 34: Normalized cross section vs. LET for dual-well and triple-well devices for normal incidence irradiation with a (a) checkerboard pattern and (b) ALL-0 pattern.

Fig.35: a) SBU and MBU for normal strikes for (a) low LET and (b) high LET for the checkerboard pattern.

(b) LET = Kr ion:  $24.98 \text{ MeV-cm}^2/\text{mg}$

Fig.36: a) SBU and MBU for normal strikes for (a) low LET and (b) high LET for the ALL-0 pattern.

The results show that at low LETs dual-well transistors collect less charge, thus they are less vulnerable to upsets. However, at moderate to high LETs, multiple node charge sharing triggers the single event upset reversal mechanism observed in the previous chapter to lower the overall error rates of the triple-well NMOS transistors.

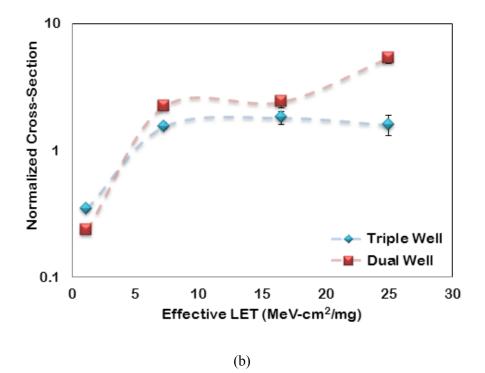

4.3.3 Experimental Results: Angular Incidence

It was noted in the previous chapter that the single event upset reversal mechanism is more pronounced for angular strikes. Fig. 37 below shows the responses of the dual- and triple-well for angled strikes. This verifies that the mechanism is effective for tilted strikes.

(b) Triple-well SRAM

Fig 37: Normalized cross section vs. Effective LET for a) dual-well and b) triple-well devices for normal and 30°W-E incidence irradiation with a checkerboard pattern.

(b) Triple-well

Fig. 38: SBU and MBU for normal and  $30^{\circ}$ W-E incidence at low LET (N ion: 1.16 MeV-cm<sup>2</sup>/mg) for a) dual-well and b) triple-well SRAM cells.

At moderate to high LETs, the soft error rates of the dual-well system increase dramatically, while for triple-well systems the error rate remains fairly constant or decreases compared to normally incident strikes. Similar behavior is observed in the simulations where at moderate or high LETs, both the SRAM cells are restored to their original state because of delayed collection of the confined charge in the p-well. Figs. 38 and 39 show the SBUs and MBUs for the angled ion-hits.

Fig.39: SBU and MBU for normal and 30°W-E incidence at high LET (Kr ion: 24.98 MeV-cm2/mg) for a) dual-well and b) triple-well SRAM cells.

The above results show that at high LETs, for angled strikes, the triple-well structures are more resistant to soft errors compared to dual-well structures. This is in contradiction to the common idea that devices exhibit more errors when exposed to ions impinging at an angle other than normal incidence.

4.3.4 Cluster Size

Maximum cluster size is defined as the product of the maximum number of errors in the horizontal (word-lines) and vertical (bit-lines) directions. Such a number will yield a measure of the spread of error across multiple rows and columns. The cluster size of the MBUs is lower for the triple-

Fig 40: Maximum cluster size of recorded errors (checkerboard pattern) for dual-well and triple-well SRAM cells for normal incidence.

well SRAMs compared to the dual-well SRAMs at high LETs for both angles of incidence. Further, the cluster size decreases for an angular strike from that for a normally incident ion. Fig. 40 shows the maximum cluster size of recorded errors for dual and triple-well structures.

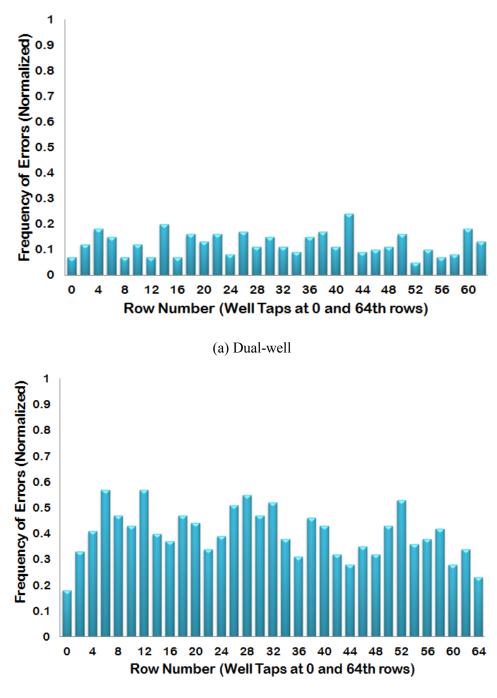

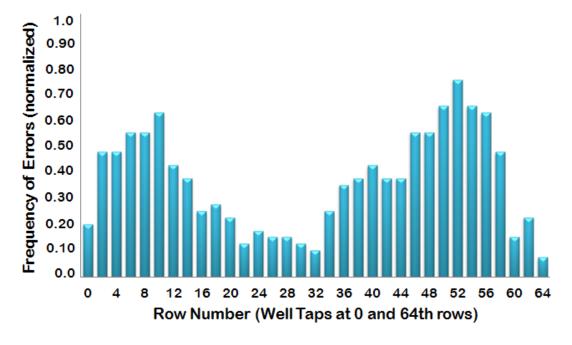

## 4.3.5 Location of Errors

The theory developed in the previous chapter makes use of the confined charge to reverse the upset in triple-well SRAM cells. Thus, the process is facilitated by not allowing the deposited charge to drain off the system faster than the electrical signal propagation time. Thus it should be more dominant in areas farther away from well taps. Figs. 41 and 42 show the total number of errors (normalized) vs. cell

location. In this case, as well, the data are normalized with a single factor. The n-wells run in the vertical direction and the well taps are placed every 64 rows. Word-lines run in the horizontal direction and bit-lines in the vertical direction.

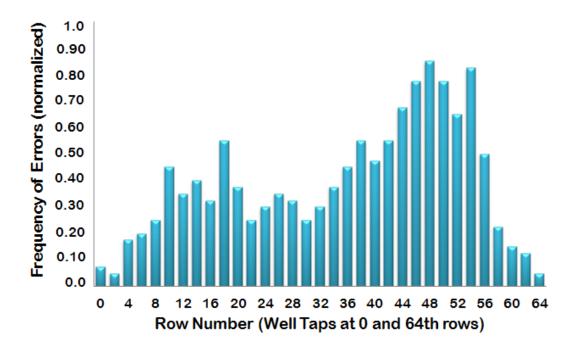

Two distinct patterns are observed, one for low LET particles and the other for high LET particles. For the dual-well technology, for low LET particles (Ar ion: LET =  $8.34 \text{ MeV-cm}^2/\text{mg}$ ), the concentration of errors farthest from the well taps is up to 82% higher than the average number of errors. However, it is around 90% lower than the average closer to the well taps, but the variation with location is much less for the triple-well technology (Fig. 42). A similar trend was observed by Gasiot et al. [4]. However, a higher number of errors are observed in the triple-well SRAM cells because of the charge confinement which has been explained in the following section. For high LET particles (Kr ion: LET = 24.98 MeV-cm<sup>2</sup>/mg), however, the triple-well cells show fewer errors far away from the well tap (~27% of the average number of errors) compared to the dual-well structures (~76% of the average number of errors)(Fig. 43). This is because near the well taps, the charges are quickly removed. This does not create an environment favorable for the upset-reversal mechanism. In areas farther away, charge confinement favorable for the upset-reversal mechanism. In areas farther away, charge confinement favorable for the upset-reversal mechanism. In areas farther away, charge confinement favorable for the upset-reversal mechanism. In areas farther away, charge confinement favorable for the upset-reversal mechanism. In areas farther away, charge confinement favorable for the upset-reversal mechanism. In areas farther away, charge confinement favorable for the upset-reversal mechanism. In areas farther away, charge confinement favorable for the upset-reversal mechanism. In areas farther away, charge confinement favorable for the upset-reversal mechanism. In areas farther away, charge confinement favorable for the upset-reversal mechanism. In areas farther away, charge confinement favorable for the upset-reversal mechanism.

Fig. 41: Schematic showing the frequency of errors vs. well tap in the SRAM cell

(b) Triple Well

Fig. 42: Frequency of errors with respect to location for Ar ion (LET:  $8.34 \text{ MeV-cm}^2/\text{mg}$ ) for (a) dual-well and (b) triple well SRAM cells for checkerboard pattern.

(a) Dual Well

<sup>(</sup>b) Triple Well

Fig. 43: Frequency of errors with respect to location for Kr ion (LET: 24.98 MeV-cm<sup>2</sup>/mg) for (a) dual-well and (b) triple well SRAM cells for checkerboard pattern.

## **CHAPTER V**

### GENERAL DISCUSSION

In SRAMs, multiple cells are associated with a single well. If enough charge is collected by transistors in the vicinity of the strike to flip the state of a cell twice, no upset will be observed in those cells. For cells distant from the struck node or near the well taps, however, this effect may not occur because the amount of confined charge is lower. Thus, for high-LET particles, there is a greater probability that cells close to the strike will revert back to their original state, with no upset occurring. The reversal effect will not, however, be observed for low LETs. In dual-well technologies, this effect does not occur in nMOS transistors because the collected charge is spread over the entire substrate as there is no deep n-well to confine the charges.