# A GENERALIZED SINGLE-EVENT ANALYSIS AND HARDENING OPTIONS FOR MIXED-SIGNAL PHASE-LOCKED LOOP CIRCUITS

By

Thomas Daniel Loveless

Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

## DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

December, 2009

Nashville, Tennessee

Approved:

Professor Lloyd W. Massengill Professor Bharat L. Bhuva Professor W. Timothy Holman Professor Robert A. Reed Professor Mark N. Ellingham

# DEDICATION

This dissertation is dedicated to my late grandmothers Beverly Loveless, who always knew I would grow up to be an engineer, and Katherine Landry, who always wanted a doctor in the family.

#### ACKNOWLEDGMENT

First and foremost, I would like to thank my wife Mary who has been more supportive than I could ever have hoped. Mary provides me with so much valuable input and I can't thank her enough. I would also like to thank the rest of my family for being there no matter what, for the sacrifices they have made to ensure I went to excellent schools, and for the guidance they have provided me over the years. Next, I would like to thank Dr. Lloyd Massengill for his continual support, confidence, and guidance throughout this project. Dr. Massengill has been a tremendous source of assistance and encouragement. More importantly, he has helped me identify and develop my talents, allowing for creativity in my research.

I would also like to thank Dr. Bharat Bhuva, whose words have been a source of patience and guidance. Additionally, I would like to thank Drs. Tim Holman, Robert Reed, and Mark Ellingham for serving on my committee. This process has been enjoyable because of them.

Special thanks are also deserved for Drs. Art Witulski, Younes Boulghassoul, Wole Amusan, Ron Schrimpf, and Dan Fleetwood, (soon to be Drs.) Megan Casey, Sarah Armstrong, Brian Olson, Matt Gadlage, and Jon Ahlbin. They have directly or indirectly provided valuable input to this work. I would also like to thank Dale McMorrow, Joe Melinger, Phil Jenkins, and Jeff Warner from the Navy Research Lab for the testing support, and Craig Hafer from Aeroflex Colorado Springs for the excellent collaboration. Recognition is also deserved for my friends in the Radiation Effects group. Finally I would like to show appreciation to the Defense Threat Reduction Agency Rad-Hard Microelectronics Program for the financial support of this research.

# TABLE OF CONTENTS

| DED  | ICATION                                                    | ii  |

|------|------------------------------------------------------------|-----|

| ACK  | NOWLEDGEMENT                                               | iii |

| LIST | OF FIGURES                                                 | ix  |

| LIST | OF TABLES                                                  | xix |

| Chap | oter                                                       |     |

| I.   | INTRODUCTION                                               |     |

| II.  | PHASE-LOCKED LOOPS                                         |     |

|      | Introduction                                               | 7   |

|      | Basic PLL Topology                                         | 7   |

|      | A Linear PLL Model                                         | 11  |

|      | Open and Closed Loop Analyses                              | 12  |

|      | Linear VCO Model                                           | 16  |

|      | PLL Locking Characteristics                                | 17  |

|      | PLL Lock Time Estimator                                    | 20  |

|      | Charge Pump PLLs                                           | 25  |

|      | The Phase-Frequency Detector                               |     |

|      | The Charge Pump and Loop Filter                            | 30  |

|      | The Voltage-Controlled Oscillator                          |     |

|      | The Frequency Divider                                      |     |

|      | Conclusion                                                 |     |

| III. | RADIATION ENVIRONMENTS AND SINGLE-EVENT PHENOMENA          |     |

|      | Introduction                                               |     |

|      | Radiation Environments and Single-Event-Inducing Particles |     |

|      | Galactic Cosmic Rays                                       |     |

|      | Solar Flares and Coronal Mass Ejections                    |     |

|      | The Trapped Radiation Environment                          |     |

|      | Single-Event Mechanisms                                    |     |

|      | Charge Generation                                          |     |

|      | Charge Collection                                          |     |

|      | Single-Event Effects                                       |     |

|      | Conclusion                                                 | 61  |

| IV.  | SINGLE-EVENT TRANSIENTS                                        | 63  |

|------|----------------------------------------------------------------|-----|

|      | Introduction                                                   | 63  |

|      | Modeling Single-Event Transients                               | 63  |

|      | Circuit Level Simulations                                      | 65  |

|      | Mixed-Mode Simulations                                         | 66  |

|      | Analog Single-Event Transients                                 | 69  |

|      | Digital Single-Event Transients                                |     |

|      | Conclusion                                                     |     |

| V.   |                                                                |     |

|      | Introduction                                                   |     |

|      | PLL Circuit Description                                        |     |

|      | Charge Pump Designs                                            |     |

|      | Simulation Study of Single-Event Transients in the PLL         |     |

|      | Laser Two-Photon Absorption Experimental Details               |     |

|      | Description of the DUT                                         | 80  |

|      | TPA-Induced SEU Mapping                                        | 84  |

|      | SET Characterization                                           |     |

|      | Experimental Results                                           | 88  |

|      | TPA-Induced SEU Mapping                                        | 88  |

|      | PLL Error Signature Characterization                           | 94  |

|      | Conclusion                                                     | 99  |

| VI.  | MITIGATION AND MODELING OF SETS IN                             |     |

|      | VOLTAGE-CONTROLLED OSCILLATORS                                 |     |

|      | Introduction                                                   |     |

|      | The Current-Starved Voltage-Controlled Oscillator              | 102 |

|      | Description of VCO Circuit Topology                            |     |

|      | Single-Event Response of the VCO                               |     |

|      | Modeling SETs in the VCO                                       | 106 |

|      | SET Simulations and Modeling                                   | 111 |

|      | Design Tradeoffs                                               | 115 |

|      | Conclusion                                                     | 118 |

| VII. |                                                                |     |

|      | RADIATION-HARDENED-BY-DESIGN VOLTAGE-CONTROLLED                |     |

|      | OSCILLATOR FOR MIXED-SIGNAL PHASE-LOCKED LOOPS                 |     |

|      | Introduction                                                   |     |

|      | VCO Circuit Description                                        |     |

|      | The Current-Starved VCO Topology                               | 120 |

|      | VCO Electrical Specifications                                  |     |

|      | Definition of Phase Jitter                                     |     |

|      | The Radiation-Hardened-by-Design Voltage-Controlled Oscillator |     |

|      | Single-Event Transient Simulation Parameters                   |     |

|      | Single-Event Transient Response                                |     |

|      | Quantification of Single-Event Transients                      | 129 |

|       | Maximum Phase Displacement                                           | 130   |

|-------|----------------------------------------------------------------------|-------|

|       | A Probabilistic Comparison of the Unhardened and RHBD VCOs           |       |

|       | Experimental Validation of Analysis Technique                        |       |

|       | Design Tradeoffs                                                     | 143   |

|       | Conclusion                                                           | .144  |

|       |                                                                      |       |

| VIII. |                                                                      |       |

|       | INTEGER-N FREQUENCY DIVIDERS AND IMPACTS ON                          |       |

|       | PHASE-LOCKED LOOP PERFORMANCE                                        |       |

|       | Introduction                                                         |       |

|       | Integer-N Frequency Divider Topology                                 |       |

|       | Single-Event Transient Simulations and Measures                      |       |

|       | Single-Event Transient Response of a Stand-Alone Divide-by-2 Circuit |       |

|       | Phase Transients in a Divide-by-2 Circuit                            | .148  |

|       | A Probabilistic Analysis of Single-Event Phase Transients in a       | 1 5 0 |

|       | Divide-by-2 Circuit                                                  | .150  |

|       | Impacts of Frequency Dividers on the SET Response of the             | 1.7.4 |

|       | Phase-Locked Loop                                                    |       |

|       | General PLL Topology                                                 | .154  |

|       | SET Propagation through a Stand-Alone Divide-by-N Circuit            | 150   |

|       | (I/O Frequency Divider)                                              |       |

|       | 1) Theoretical and Simulation Analyses<br>2) Experimental Analysis   |       |

|       | Impacts of the Feedback Divider on the SET Propagation in the PLL    |       |

|       | 1) Theoretical and Simulation Analyses                               |       |

|       | (a) Strikes in the PFD:                                              |       |

|       | (b) Strikes in the CP:                                               |       |

|       | (c) Strikes in the VCO:                                              |       |

|       |                                                                      |       |

|       | (d) Strikes in the Frequency Divider:                                |       |

|       | 2) Implications of PLL Feedback Factor                               |       |

|       | 3) Experimental Analysis                                             |       |

|       | Conclusion                                                           | .16/  |

| IX    | A GENERALIZED LINEAR MODEL FOR SINGLE TRANSIENT                      |       |

| 12 1. | PROPAGATION IN PHASE-LOCKED LOOPS AND GUIDELINES FOR                 |       |

|       | ERROR REDUCTION                                                      |       |

|       | Introduction                                                         |       |

|       | Transient Propagation                                                |       |

|       | Loop Recovery                                                        |       |

|       | Voltage Transient Generation                                         |       |

|       | Output Phase Displacement                                            |       |

|       | The PLL Critical Time Constant                                       |       |

|       | Principles for Transient Reduction                                   |       |

|       | Model Validation                                                     |       |

|       | Simulation Results                                                   |       |

|       | Experimental Results                                                 |       |

|       |                                                                      |       |

| Conclusion                                                                                                               | 196 |

|--------------------------------------------------------------------------------------------------------------------------|-----|

| X. CONCLUSION                                                                                                            | 197 |

| Appendix                                                                                                                 |     |

| A. DERIVATIONS FOR THE GENERALIZED LINEAR MODEL FOR<br>SINGLE TRANSIENT PROPAGATION IN PHASE-LOCKED LOOPS                | 200 |

| B. BASIC SPICE NETLIST FOR THE UNITY GAIN PHASE-LOCKED<br>LOOP CIRCUIT LOCKED LOOPS                                      | 210 |

| C. 2D TRANSIENT-SENSITIVITY MAPS OF CONVENTIONAL CHARGE<br>PUMP OBTAINED FROM LASER TWO-PHOTON ABSORPTION<br>EXPERIMENTS | 216 |

| REFERENCES                                                                                                               | 218 |

# LIST OF FIGURES

| Figure | Pag                                                                                                                                                                                                                                                                                       | ge |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| II-1.  | Diagram of a basic PLL consisting of a phase detector (PD), low-pass filter (LPF), and voltage-controlled oscillator (VCO)                                                                                                                                                                | 8  |

| II-2.  | Diagram of a PLL for reducing the clock skew associated with clock distribution. Buffers are included internal to the closed-loop                                                                                                                                                         | 9  |

| II-3.  | Diagram of a PLL for high-frequency clock generation                                                                                                                                                                                                                                      | 10 |

| II-4.  | Linear model for a PLL (adapted from [Be98])                                                                                                                                                                                                                                              | 11 |

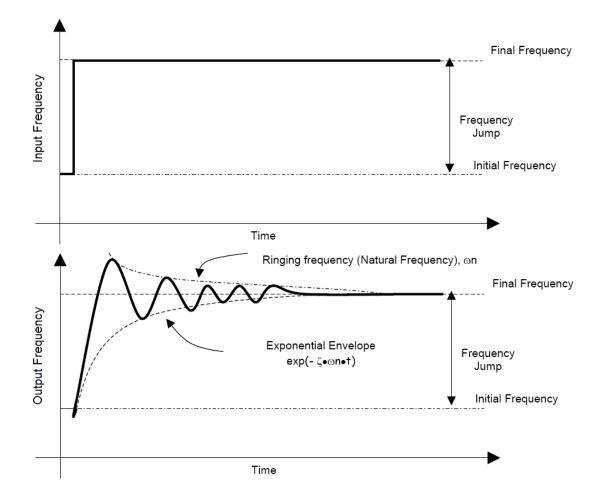

| II-5.  | Underdamped response of a PLL to a unit frequency step at the input (adapted from [Ra01] and [Ba06])                                                                                                                                                                                      | 15 |

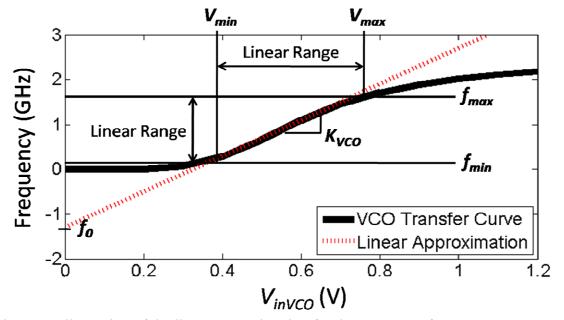

| II-6.  | Illustration of the linear approximation for the VCO transfer curve                                                                                                                                                                                                                       | 17 |

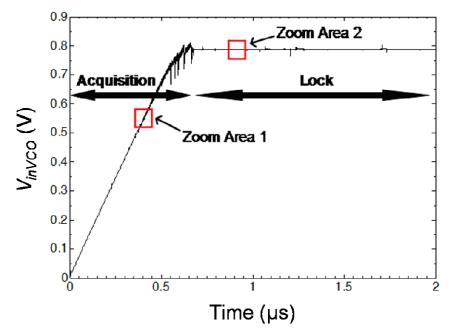

| II-7.  | Acquisition and lock curve: $V_{inVCO}$ versus time at 700 MHz operation.<br>The reference and output signals represented by the highlighted boxes ( <i>Zoom Area 1</i> and <i>Zoom Area 2</i> ) are displayed in Fig. II-8 and Fig. II-9 [Lo07a]                                         | 19 |

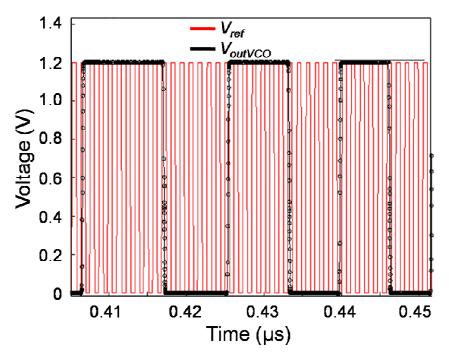

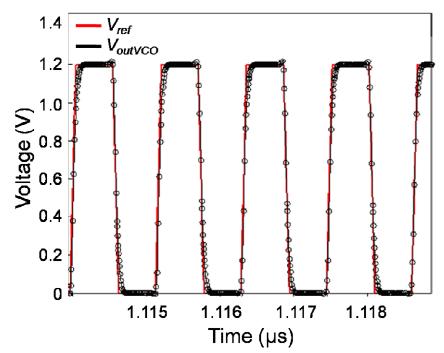

| II-8.  | $V_{ref}$ and $V_{outVCO}$ during the acquisition period, as indicated by Zoom Area 1 in Fig. II-7 [Lo07a]                                                                                                                                                                                | 19 |

| II-9.  | $V_{ref}$ and $V_{outVCO}$ during the lock period, as indicated by Zoom Area 2 in Fig. II-7 [Lo07a]                                                                                                                                                                                       | 20 |

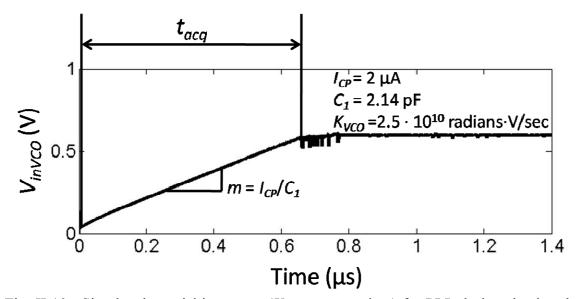

| II-10. | Simulated acquisition curve ( $V_{inVCO}$ versus time) for PLL designed using<br>the IBM 9SF PDK at a center frequency of 1.1 GHz. Calculated acquisition<br>time is 607 ns, whereas the simulated acquisition time is approximately<br>650 ns (ignoring the final settling time)         | 22 |

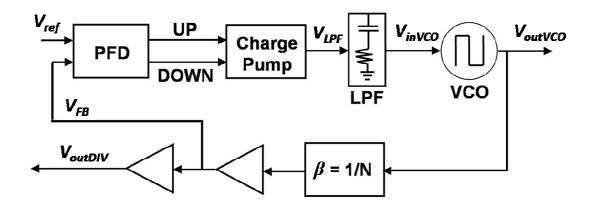

| II-11. | Block diagram of the charge pump PLL including the phase-frequency detector (PFD), charge pump (CP), low-pass filter (LPF), voltage-controlled oscillator (VCO), and frequency divider ( $\beta$ ). Additionally, "e-graded" buffers are included in order to account for loading effects | 26 |

| II-12. | Simplified block diagram of the phase-frequency detector [Ba08]                                                                                                                                                                                                                           | 27 |

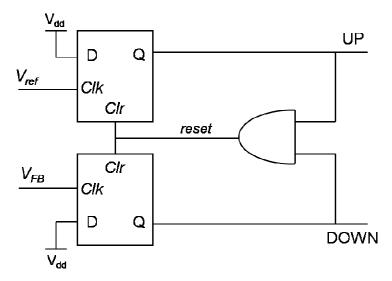

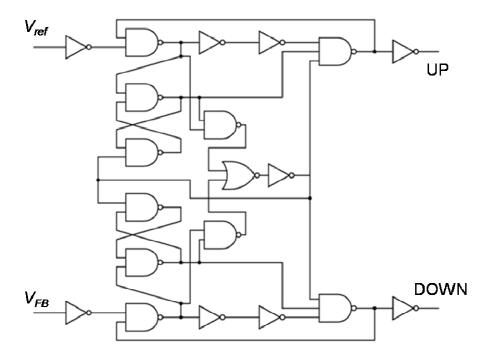

| II-13. | CMOS implementation of the phase-frequency detector used in this work [Ba08]                                                                                                                                                                                                              | 28 |

| II-14. | PFD inputs and outputs for (a) $V_{FB}$ lagging $V_{ref}$ , (b) $V_{FB}$ leading $V_{ref}$ , and (c) $V_{FB}$ in phase lock with $V_{ref}$ (adapted from [Ba08])                                                                                                                                                              | .30 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

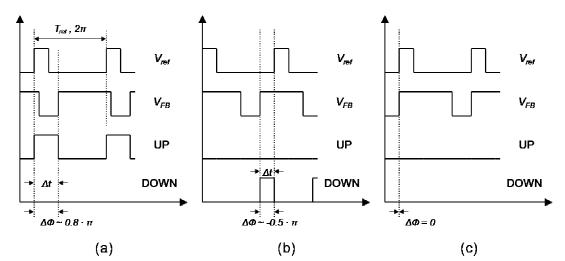

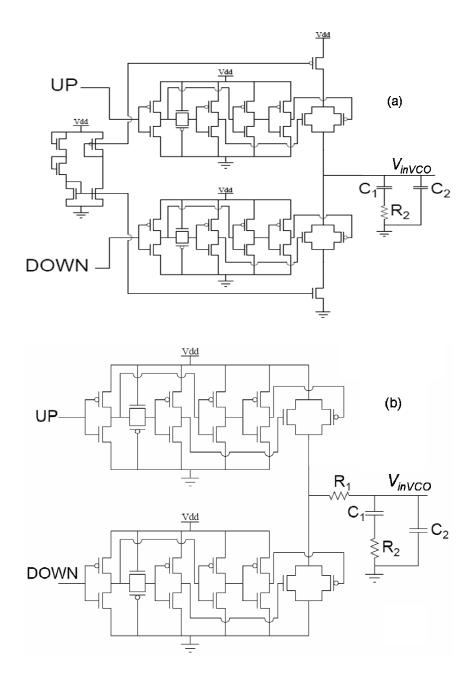

| II-15. | Basic schematic of the (a) current-based charge pump and (b) voltage-based charge pump (tri-state)                                                                                                                                                                                                                            |     |

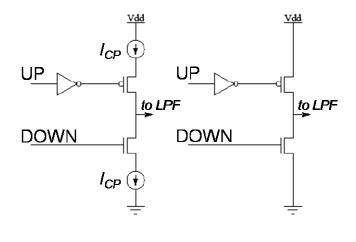

| II-16. | Basic loop filters for the (a) current-based and (b) voltage-based charge pumps                                                                                                                                                                                                                                               | .32 |

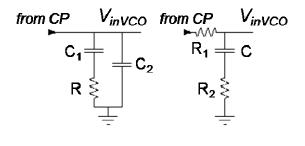

| II-17. | Practical implementations of the (a) current- and (b) voltage-based charge pumps and respective loop filters                                                                                                                                                                                                                  | .34 |

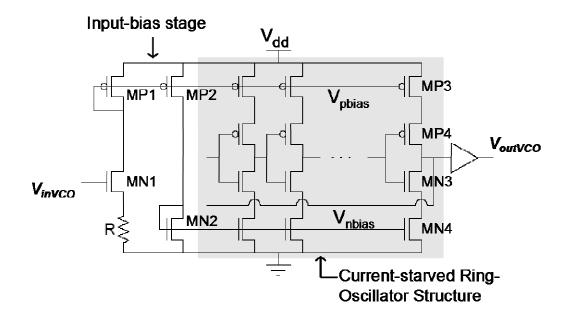

| II-18. | Schematic of the current-starved VCO                                                                                                                                                                                                                                                                                          | .36 |

| II-19. | Simplified schematic of a single current-starved stage in the VCO                                                                                                                                                                                                                                                             | .37 |

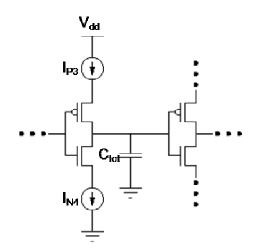

| II-20. | Current-starved VCO gain characteristics illustrating an example of a poor VCO design where the frequencies $f_c$ and $(f_{max} + f_{min})/2$ are far apart, to be contrasted with a desirable design example where the frequencies are within 10% of each other [Bo05].                                                      | .38 |

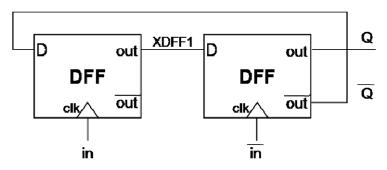

| II-21. | Diagram of a single divide-by-2 frequency divider (after [Le04a])                                                                                                                                                                                                                                                             | .40 |

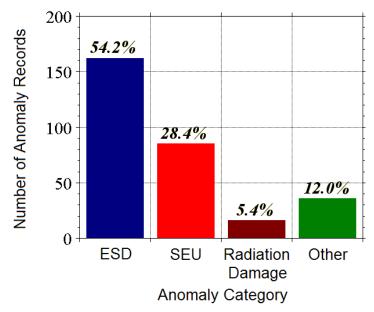

| III-1. | Distribution of spacecraft anomaly records versus anomaly type (ESD: electrostatic discharge; SEU: single event upset) [Ma02] (data from [Ko99])                                                                                                                                                                              | .43 |

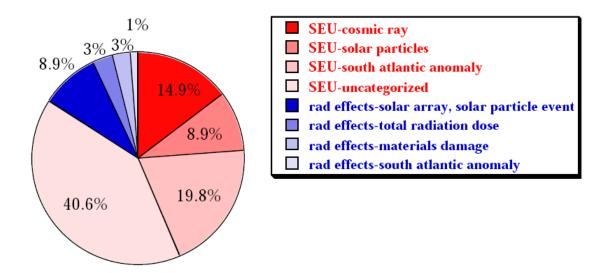

| III-2. | Breakdown of SEU and radiation damage anomaly records [Ma02]<br>(data from [Ko99])                                                                                                                                                                                                                                            | .43 |

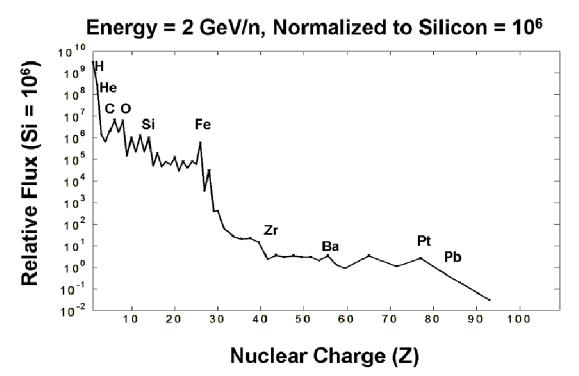

| III-3. | Galactic cosmic ray particle spectrum as a function of atomic number (adapted from [Me74] and [Ba98])                                                                                                                                                                                                                         | .44 |

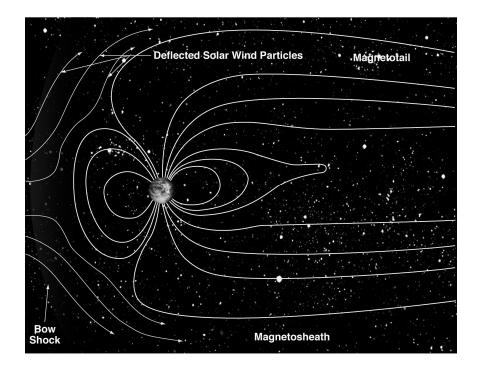

| III-4. | The Earth's magnetosphere [Xa06]                                                                                                                                                                                                                                                                                              | .45 |

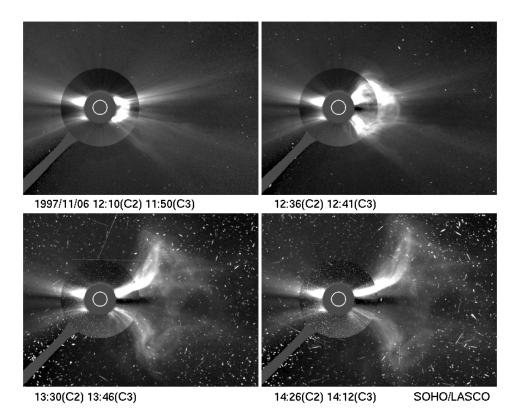

| III-5. | The most energetic solar flare ever recorded, Monday, April 2, 2001.<br>Coronagraphs from the SOHO satellite follow the evolution of a coronal<br>mass ejection. Protons from the event reach the instrument's charge coupled<br>devices (CCD) and "pepper" the image with transients in the lower two<br>panels [Ma99, SOHO] |     |

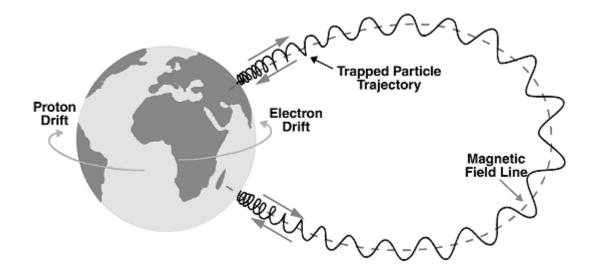

| III-6. | Motion of trapped charged particles in the Earth's magnetic field [St88b, Xa06]                                                                                                                                                                                                                                               | .48 |

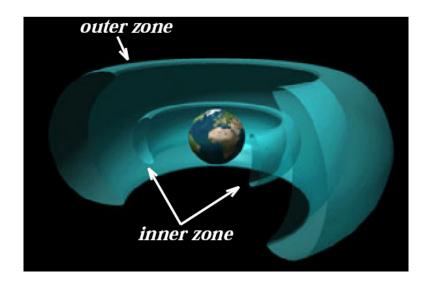

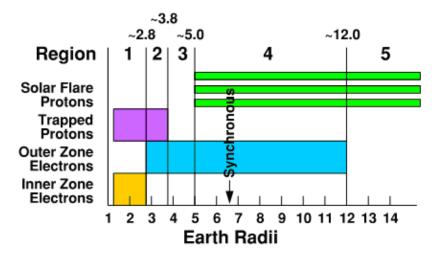

| III-7. | Diagram of the Earth's Van Allen radiation belts [Ma02]                                                                                                                                                                                                                                                                       | .49 |

| III-8.  | The proton and electron domains within the two primary Van Allen belts [St88b]                                                                                                                                                                                                                                                     | .49 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

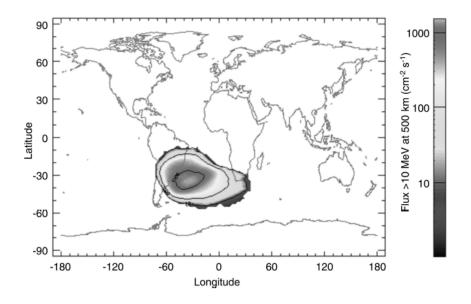

| III-9.  | Contour plot of proton fluxes > 10 MeV in the SAA at a 500 km altitude during solar maximum [Xa06]                                                                                                                                                                                                                                 | .50 |

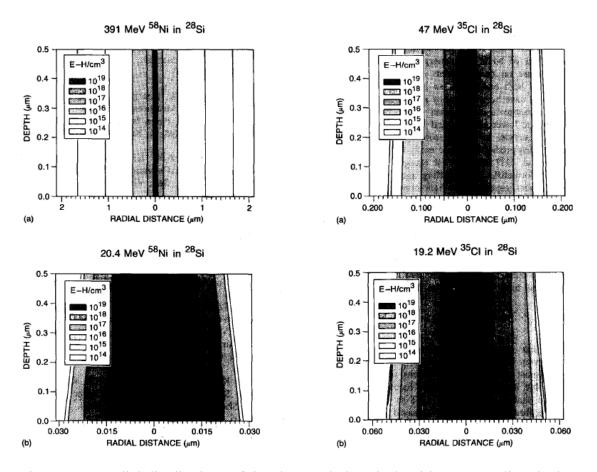

| III-10. | Radial distributions of the electron-hole pair densities surrounding the ion path (after [St88a])                                                                                                                                                                                                                                  | .52 |

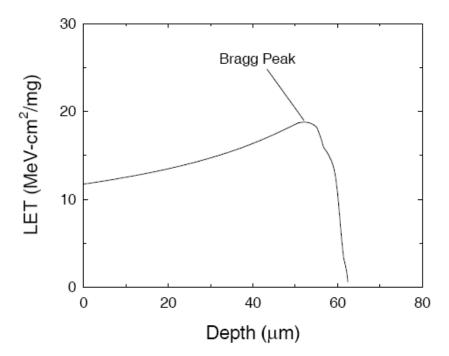

| III-11. | Linear energy transfer (LET) vs. depth curve for 210 MeV chlorine ions in silicon [Do99]                                                                                                                                                                                                                                           | .54 |

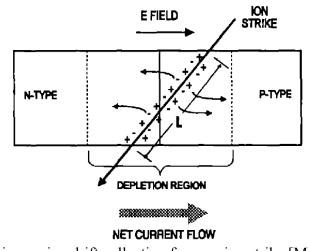

| III-12. | Depletion region drift collection from an ion strike [Ma93]                                                                                                                                                                                                                                                                        | .54 |

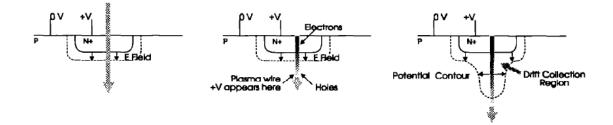

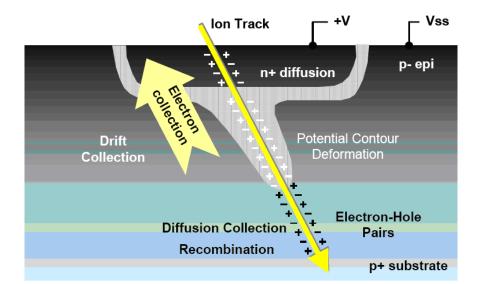

| III-13. | Qualitative view of the funnel effect: a) creation of the ion-induced plasma track, b) movement of electrons toward the positive bias, and c) potential drop along the track and redistribution of equipotential lines down the track [Ma93].                                                                                      | .56 |

| III-14. | Illustration of an ion strike on a reverse-biased n+/p junction [Ba05]                                                                                                                                                                                                                                                             | .57 |

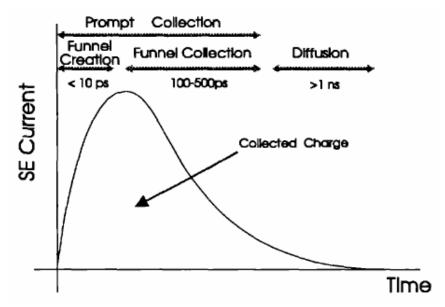

| III-15. | Typical shape of the SE current at a junction. The total collected charge corresponds to the area under the curve [Me82]                                                                                                                                                                                                           | .58 |

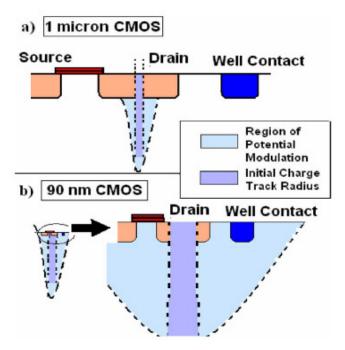

| III-16. | Relative range of the electron-hole cloud in a 1 $\mu$ m and a 90 nm technology. Top figure (a) shows the electron-hole cloud creating a potential perturbation only on a small portion of the drain. Bottom figure shows a strike with the same radius covering the source, drain and well contact [Da07a].                       | .59 |

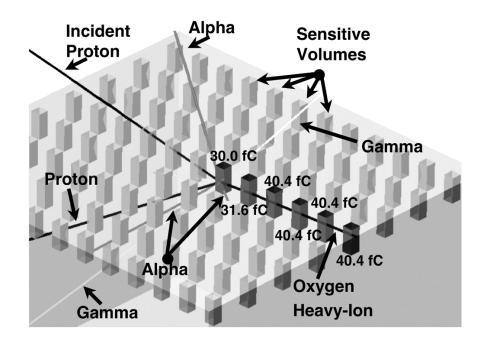

| III-17. | Simulated nuclear event with a 63 MeV incident proton. Proton interacts with a silicon nucleus producing secondary particles including a 14 MeV oxygen ion, a proton, gamma rays, and alpha particles. The heavy oxygen ion transverses six sensitive volumes, which collect between 30 fC and 40 fC each [Ti06]                   | .60 |

| IV-1.   | The double-exponential current pulse model used for circuit-level simulations of radiation-induced photocurrents. Also shown are the piece-wise equations directly compatible with SPICE-level circuit simulators. The total charge ( $Q$ ) delivered by the current pulse is obtained by integrating $I(t)$ over time, $t$ [Ma93] | .65 |

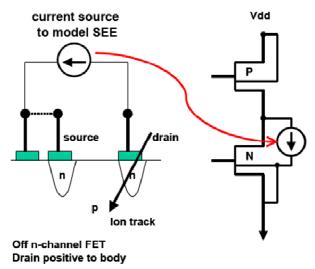

| IV-2.   | Placement of current sources to model the radiation-induced photocurrents (after [We02])                                                                                                                                                                                                                                           | .66 |

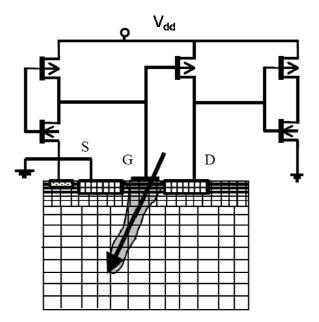

| IV-3.   | Mixed mode device/circuit simulation (after [Bu01])                                                                                                                                                                                                                                                                                | .68 |

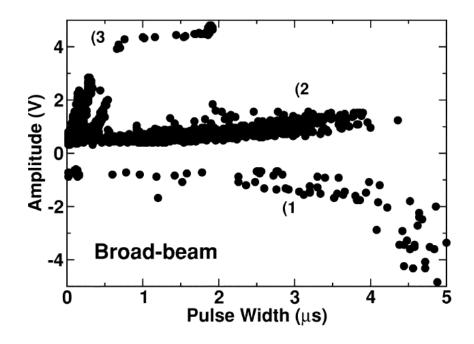

| IV-4. | Amplitude versus time-width (at full-width at half-maximum of amplitude) of an SET observed at the LM124 output. The ions used during the broad-beam experiment are 100 MeV Br, 150 MeV Mg, and 210 MeV Cl. The corresponding LET values of the ions used are 38.6, 6.25, and 11.5 MeV-cm <sup>2</sup> /mg, respectively. [Bo02]                          |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

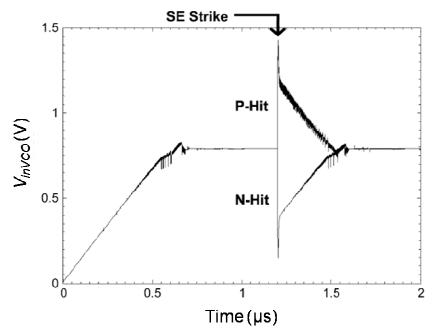

| IV-5. | Input of VCO ( $V_{inVCO}$ ) vs. time for PLL at 700 MHz operation.<br>Simulated SE strikes occur at 1.2 $\mu$ s and span over approximately<br>280 clock cycles, lasting over 500 ns. The P-Hit curve represents<br>the response of a strike on a pMOS device, whereas the N-Hit curve<br>represents the response of a strike on an nMOS device [Lo06]70 |

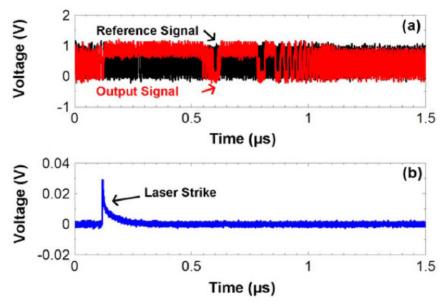

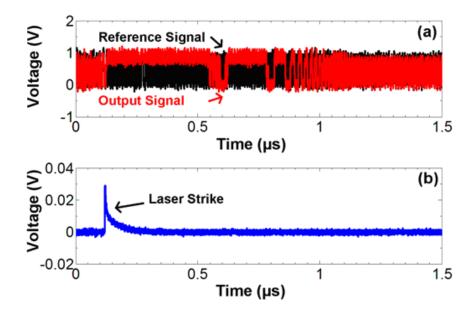

| IV-6. | <ul> <li>(a) The reference and output signals versus time following a laser strike of incident energy 30 nJ in the charge pump component of the PLL at 200 MHz.</li> <li>(b) Voltage representation (output of diode detector) of the laser strike [Lo07b]</li></ul>                                                                                      |

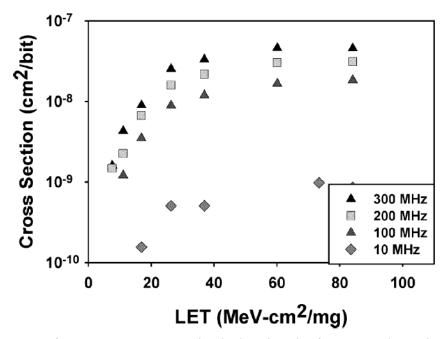

| IV-7. | Data from a 0.18 μm DICE latch showing the frequency dependence on the cross section [Ga04]73                                                                                                                                                                                                                                                             |

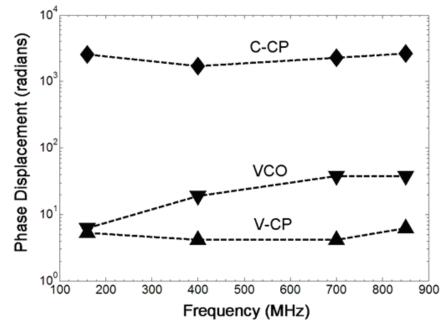

| V-1.  | Simulation results showing the maximum phase displacement vs. frequency<br>for SE strikes depositing 500 fC of charge in the C-CP, VCO, and V-CP.<br>At least 2 orders of magnitude improvement is achieved by the V-CP over<br>the C-CP [Lo06, Lo07a]                                                                                                    |

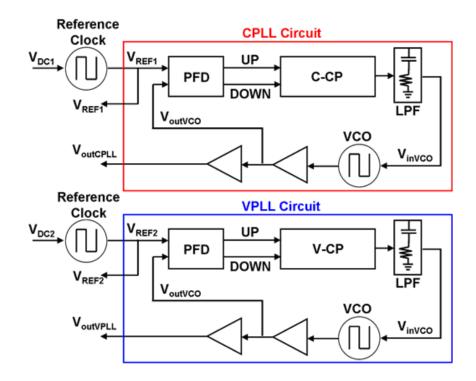

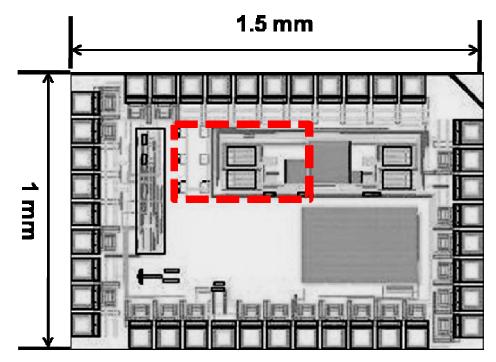

| V-2.  | General block diagram of the DUT, including the two PLL circuits (CPLL and VPLL) and two on-chip reference clock generating circuits                                                                                                                                                                                                                      |

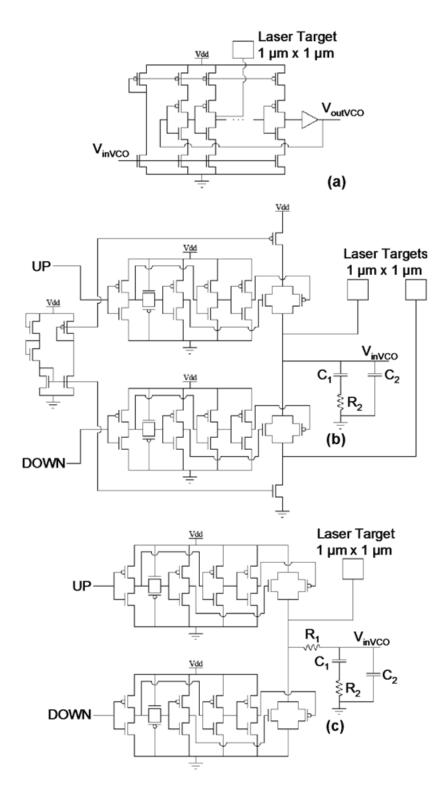

| V-3.  | Schematics of the (a) VCO, (b) C-CP, and (c) V-CP circuits indicating the locations of the 1 $\mu$ m x 1 $\mu$ m diffusion areas used for the laser targets82                                                                                                                                                                                             |

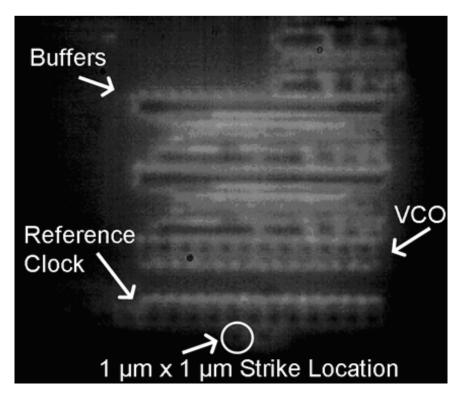

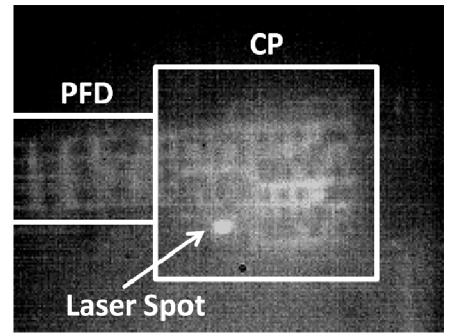

| V-4.  | Near-infrared photo of one strike location tied to a node in the VCO circuit located in the CPLL. Also indicated is the reference clock generation circuit and output buffers                                                                                                                                                                             |

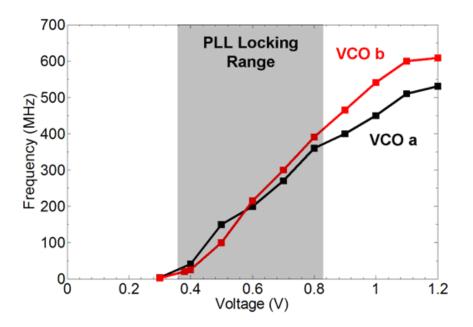

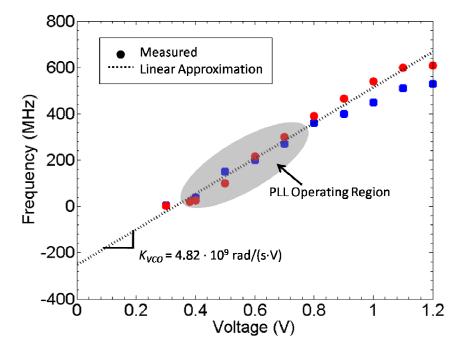

| V-5.  | Measured transfer characteristics of the VCO circuits                                                                                                                                                                                                                                                                                                     |

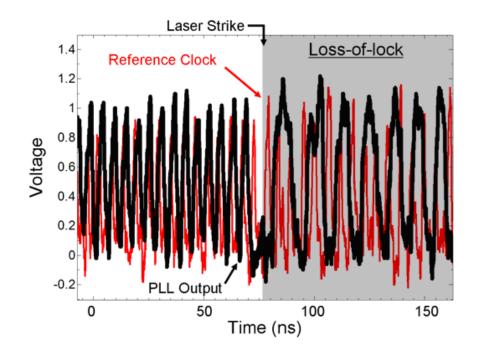

| V-6.  | Capture of an SEU (PLL loss-of-lock) following a 70 nJ laser strike in<br>the conventional current-based charge pump sub-circuit. The PLL was<br>operating at 200 MHz and lost phase lock for approximately 420 ns                                                                                                                                        |

| V-7.  | <ul><li>(a) The reference and output signals versus time following a laser strike of energy 30 nJ in the C-CP component of the CPLL at 200 MHz.</li><li>(b) Voltage representation (output of diode detector) of the laser strike</li></ul>                                                                                                               |

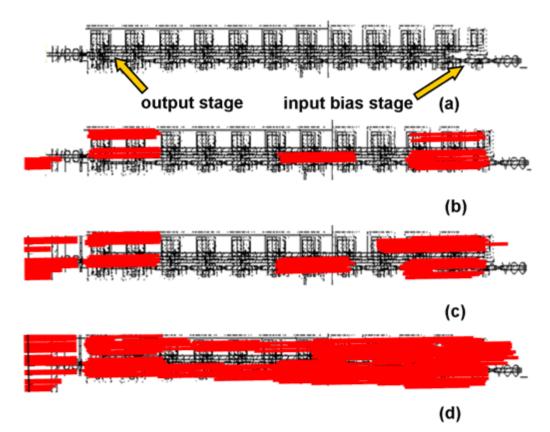

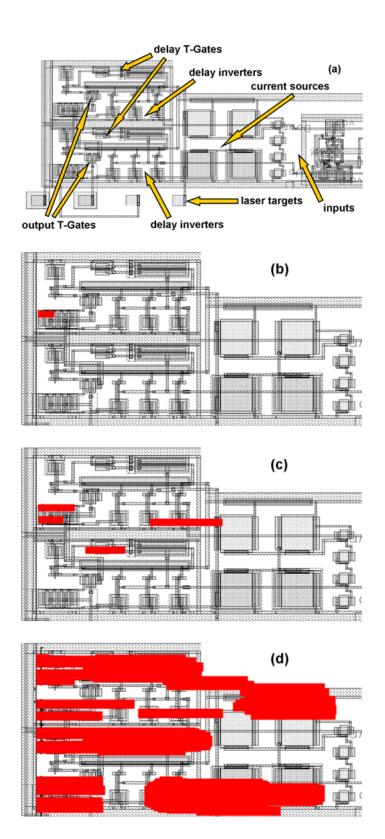

| V-8.  | (a) The layout view of the VCO circuit indicating the input and output stages. Also shown are the TPA-induced SEU maps of the VCO circuit for incident laser pulse energies of (b) 1.9 nJ, (c) 2.8 nJ, and (d) 7.0 nJ                                                                                                                                                                       | 89  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

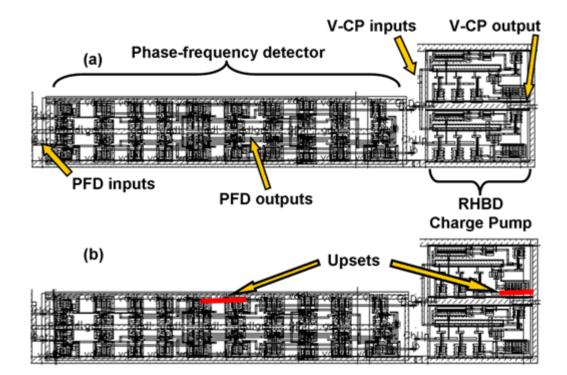

| V-9.  | (a) The layout view of the PFD and V-CP sub-circuits. Also displayed is the TPA-induced SEU map of the PFD and V-CP sub-circuits for incident laser pulse energy of (b) 7.0 nJ                                                                                                                                                                                                              | 90  |

| V-10. | (a) The layout view of the C-CP sub-circuit. Also displayed are the TPA-induced SEU maps of the C-CP sub-circuit for incident laser energies of (b) 2.5 nJ, (c) 3.7 nJ, and (d) 7.0 nJ.                                                                                                                                                                                                     | 92  |

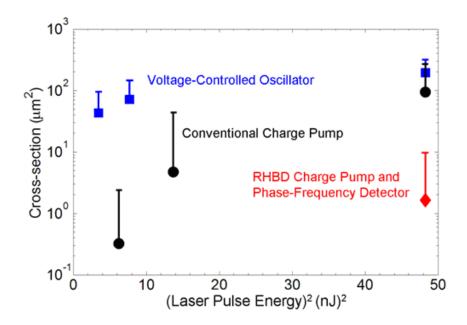

| V-11. | Laser sensitive area versus the square of the incident laser energy. Upper<br>error bars were calculated from a script that accounted for the amount of<br>additional area that the laser spot size covered over the scan resolution                                                                                                                                                        | 94  |

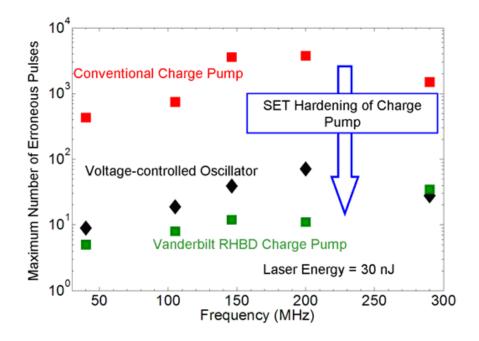

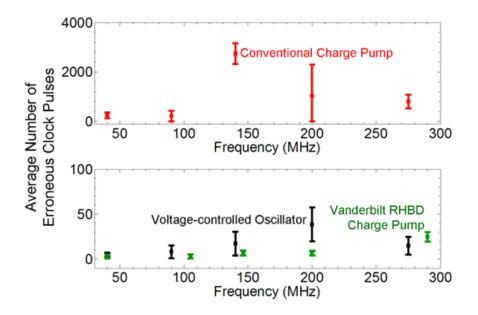

| V-12. | Maximum number of erroneous clock pulses versus frequency for laser<br>strikes in various PLL sub-circuits. A maximum of 2.3 orders of magnitude<br>improvement was achieved by the RHBD charge pump over the<br>conventional design. The incident laser energy was 30 nJ                                                                                                                   |     |

| V-13. | Average number of erroneous clock pulses versus frequency for laser<br>strikes in various PLL sub-circuits (note the difference in y-axis scale).<br>The mean number of erroneous pulses is approximately 2 orders of<br>magnitude lower for strikes occurring in the V-CP over the C-CP at<br>incident laser energy of 30 nJ. Error bars represent one standard<br>deviation from the mean | 96  |

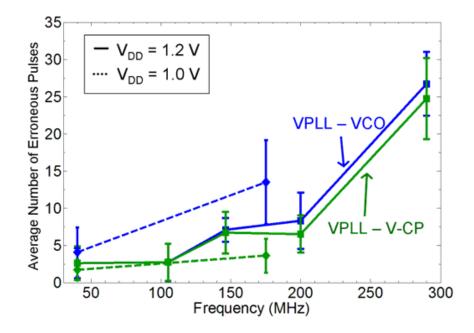

| V-14. | Average number of erroneous pulses versus frequency for various power supply voltages in the VCO and V-CP of the VPLL circuit                                                                                                                                                                                                                                                               | 97  |

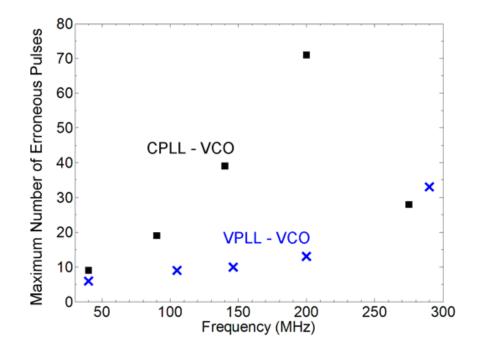

| V-15. | Maximum number of erroneous pulses versus frequency in the outputs of the CPLL and VPLL for strikes in the VCOs                                                                                                                                                                                                                                                                             | 98  |

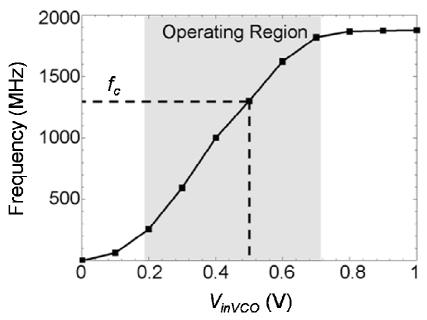

| VI-1. | Transfer characteristics, output frequency versus input voltage, of the VCO designed for a center frequency of 1.3 GHz and implemented with 7 RO stages                                                                                                                                                                                                                                     | 103 |

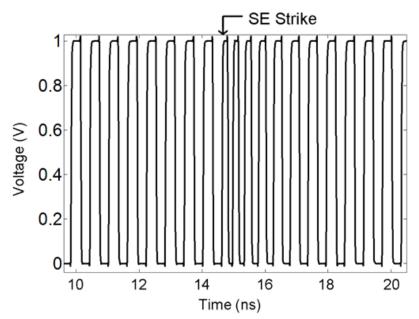

| VI-2. | The output voltage of the VCO during an SE in the input bias stage. The strike occurs at approximately 15 ns and has an LET of 80 MeV-cm <sup>2</sup> /mg. A frequency modulation occurs until the current can be restored to its initial value.                                                                                                                                            | 105 |

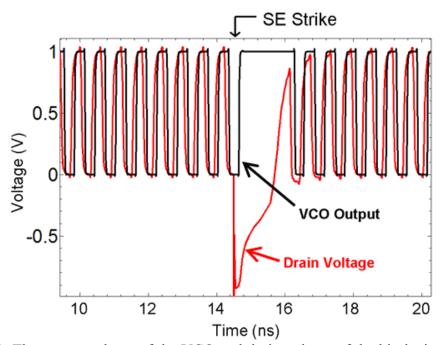

| VI-3.  | The output voltage of the VCO and drain voltage of the hit device during a single-event in a current-starved inverter stage. The strike occurs at approximately 15 ns and has an LET of 80 MeV-cm <sup>2</sup> /mg. The output of the VCO is locked to $V_{dd}$ until the drain voltage recovers                                          |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

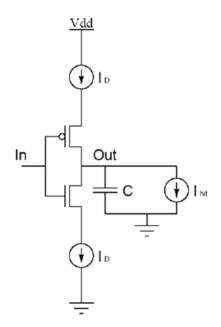

| VI-4.  | A simple model for an SE hit in a current-starved inverter can be<br>represented by two current sources $(I_D)$ representing the restoring<br>device current in an inverter, an output nodal capacitance $(C)$ , and a<br>current source representative of the current induced by the SE $(I_{hit})$ 106                                  |

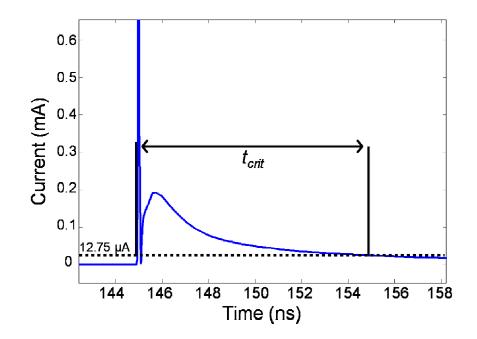

| VI-5.  | Current pulse generated by a heavy-ion with an LET of $80 \text{ MeV-cm}^2/\text{mg}$ . The critical time of the VCO with a current drive of 12.75 $\mu$ A is illustrated                                                                                                                                                                 |

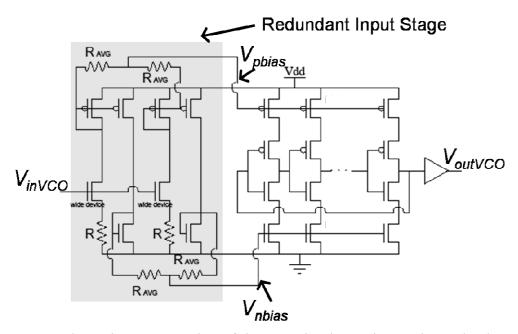

| VI-6.  | Schematic representation of the VCO implementing analog redundancy<br>in the input-bias stage in order to reduce the voltage perturbation on $V_{pbias}$<br>and $V_{nbias}$ resulting from an ion strike in the bias stage. The input stage is<br>implemented with 2 identical copies and averaged with identical resistors,<br>$R_{AVG}$ |

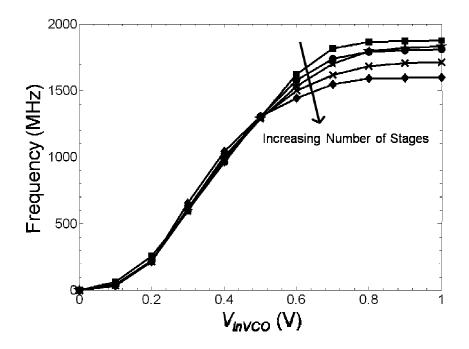

| VI-7.  | Transfer characteristics, output frequency versus input voltage, for VCOs designed with 7, 11, 15, 19, and 23 current-starved inverter stages                                                                                                                                                                                             |

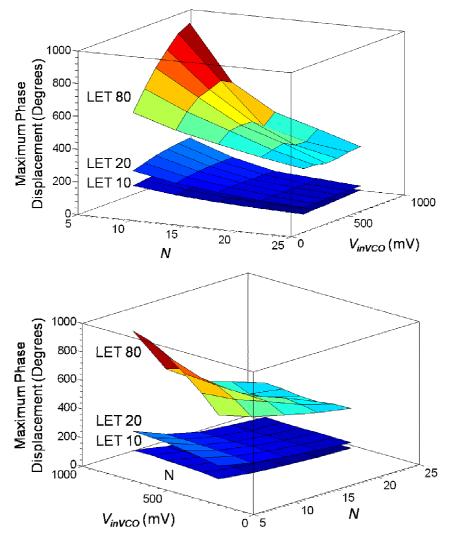

| VI-8.  | (a) Maximum phase displacement versus input voltage ( $V_{inVCO}$ ) and number of RO stages ( $N$ ) for varying LET values (MeV-cm <sup>2</sup> /mg) as generated by the analytical model. (b) Alternative view                                                                                                                           |

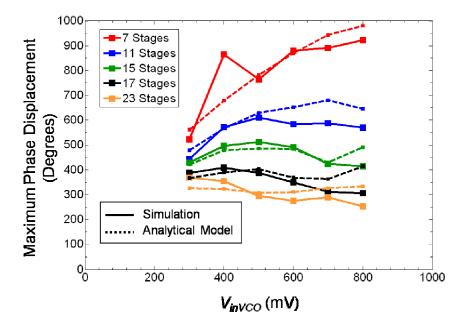

| VI-9.  | Maximum phase displacement versus input voltage for the VCO circuits at 80 MeV-cm <sup>2</sup> /mg. Results obtained from the analytical model are compared to simulations for various $N$                                                                                                                                                |

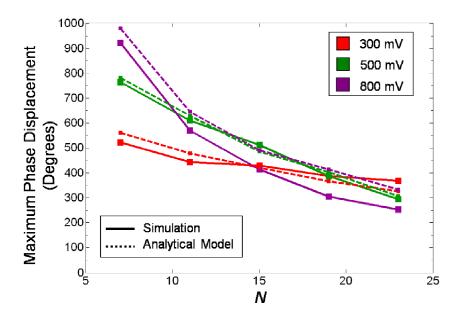

| VI-10. | Maximum phase displacement versus the number of inverter stages ( $N$ ) for 3 bias conditions (300 mV, 500 mV, and 800 mV) at 80 MeV-cm <sup>2</sup> /mg. Results obtained from the analytical model are compared to simulations114                                                                                                       |

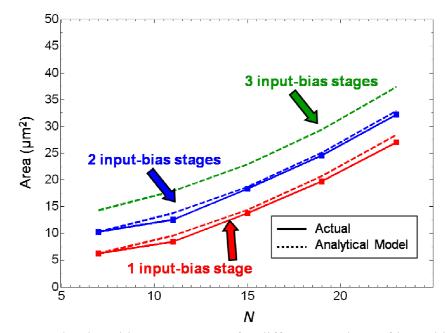

| VI-11. | Total vulnerable area versus <i>N</i> for different numbers of input bias stages.<br>The dashed lines represent the area obtained analytically and the solid<br>lines represent the actual achieved areas                                                                                                                                 |

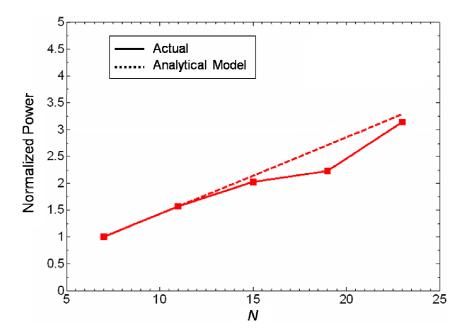

| VI-12. | Average power dissipation versus <i>N</i> normalized to the power dissipation for 7 RO stages. The dashed line represents the power obtained analytically and the solid line represents the actual power dissipation117                                                                                                                   |

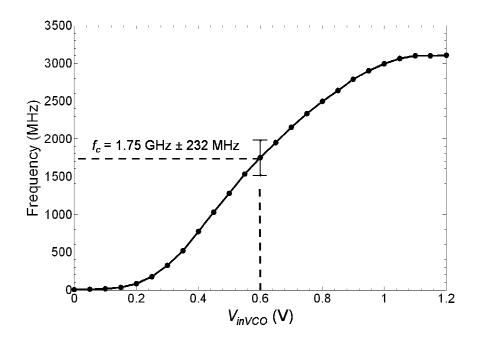

| VII-1. | Frequency transfer characteristics of the unhardened five-stage VCO120                                                                                                                                                                                                                                                                    |

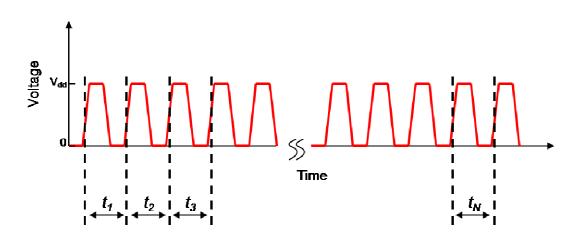

| VII-2.  | Illustration of time-domain measurements of the local operating periods $(t_i)$ used for the calculation of phase jitter, <i>rms</i> phase jitter, and the expected value of peak phase jitter, $\overline{\phi_e}$ , as described by Eqns. (VII-1 to VII-3)                                                                                               | 122 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

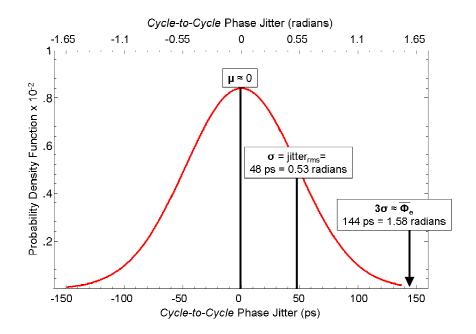

| VII-3.  | Simulated cycle-to-cycle phase jitter fit to a probability density function for a Gaussian distribution with a mean value of 0 ps and a standard deviation ( <i>rms</i> phase jitter) of 48 ps                                                                                                                                                             | 123 |

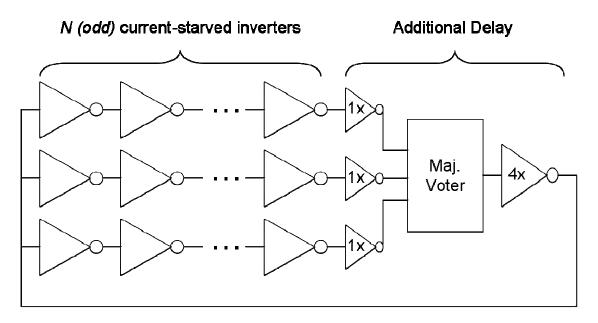

| VII-4.  | Simplified diagram of the RHBD VCO excluding the input-bias stages<br>and current-sources required to set the delay in each delay stage                                                                                                                                                                                                                    | 126 |

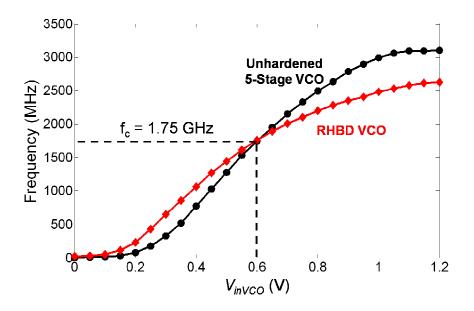

| VII-5.  | Frequency transfer characteristics of the RHBD VCO compared to the unhardened five-stage VCO                                                                                                                                                                                                                                                               | 127 |

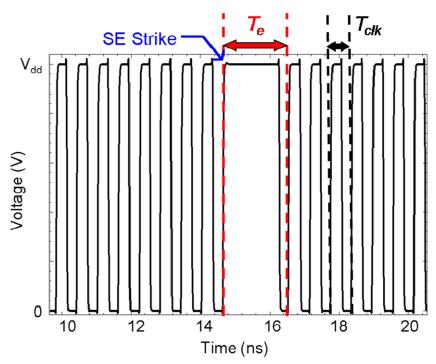

| VII-6.  | Illustration of the time perturbation, $T_e$ , used to calculate the phase displacement resulting from an SE.                                                                                                                                                                                                                                              | 130 |

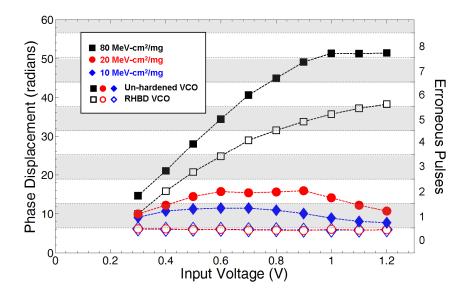

| VII-7.  | Maximum phase displacement (radians) and corresponding number of erroneous pulses versus input voltage for the unhardened VCO and RHBD VCO. Square, circle, and diamond symbols represent LET values of 80, 20, and 10 MeV-cm <sup>2</sup> /mg, respectively. Closed symbols represent the unhardened VCO whereas the open symbols represent the RHBD VCO1 | 131 |

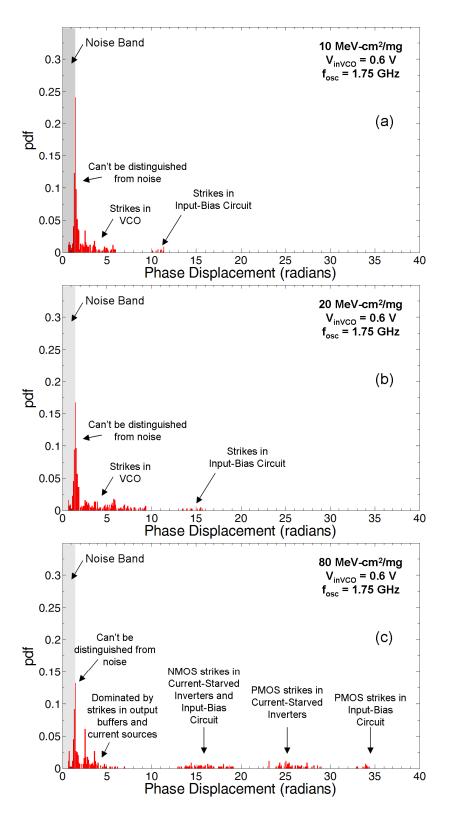

| VII-8.  | Histograms of maximum phase displacement (radians) for the unhardened VCO at various LET (MeV-cm <sup>2</sup> /mg) for an input voltage of 0.6 V, corresponding to a frequency of 1.75 GHz. All histograms are normalized so that the total area is 1, so as to represent the discrete pdf of phase displacement                                           | 134 |

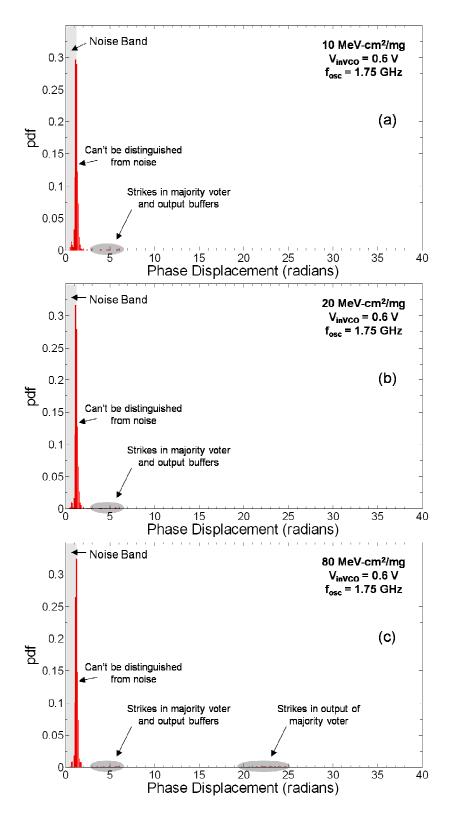

| VII-9.  | Histograms of maximum phase displacement (radians) for the RHBD VCO at various LET (MeV-cm <sup>2</sup> /mg) for an input voltage of 0.6 V, corresponding to a frequency of 1.75 GHz. All histograms are normalized so that the total area is 1, so as to represent the discrete pdf of phase displacement                                                 | 135 |

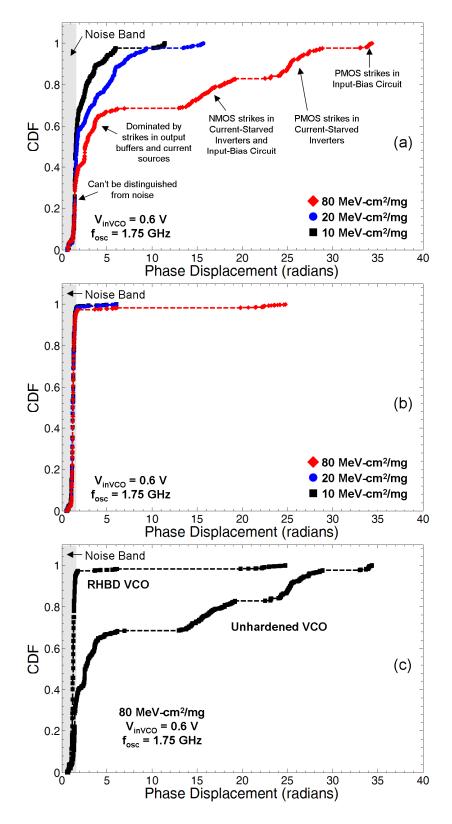

| VII-10. | Empirical Cumulative Distribution Functions (CDF) of phase displacement (radians) for the (a) unhardened VCO and (b) RHBD VCO for various LET at an input voltage of 0.6 V. (c) Also shown is a direct comparison of the two circuits at 80 MeV-cm <sup>2</sup> /mg and an input voltage of 0.6 V.                                                         | 136 |

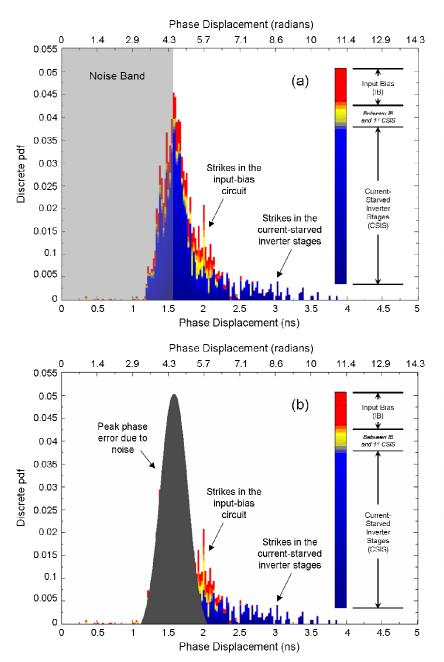

| VII-11. | (a) Histogram of phase displacement (radians) obtained from TPA<br>laser experiments at incident energy 12 nJ for the 130 nm unhardened<br>VCO. The histogram is normalized so that the total area is 1, so as to<br>represent the discrete probability density function (pdf) of phase<br>displacement. (b) Histogram identifying the contributions due to noise<br>and laser strikes in the VCO | 141  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

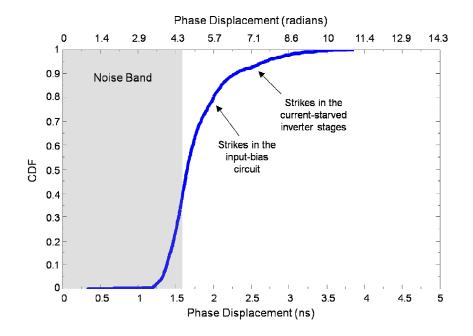

| VII-12. | Cumulative Distribution Function (CDF) of phase displacement (radians) obtained from TPA laser experiments at incident energy 12 nJ for the 130 nm unhardened VCO                                                                                                                                                                                                                                 | 142  |

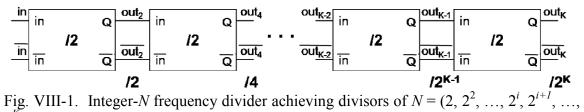

| VIII-1. | Integer- <i>N</i> frequency divider achieving divisors of $N = (2, 2^2,, 2^i, 2^{i+1},, 2^K)$                                                                                                                                                                                                                                                                                                     | 146  |

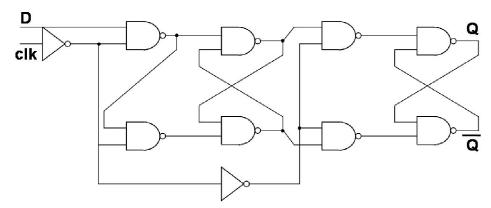

| VIII-2. | Schematic of the CMOS DFF used in the divide-by-2 topology                                                                                                                                                                                                                                                                                                                                        | 147  |

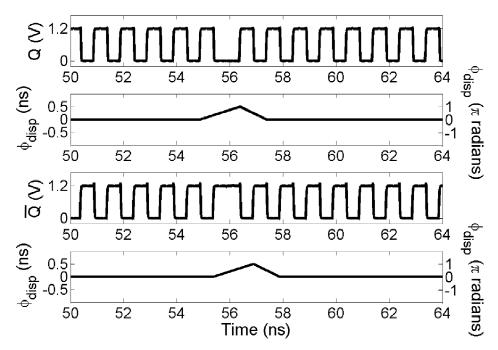

| VIII-3. | An example of two identical phase transients on the outputs of a single divide-by-2 circuit. Input frequency is 2 GHz resulting in an output frequency of 1 GHz. Peak of transient reaches a $\Phi_{disp}$ of 500 ps ( $\pi$ radians).                                                                                                                                                            | .149 |

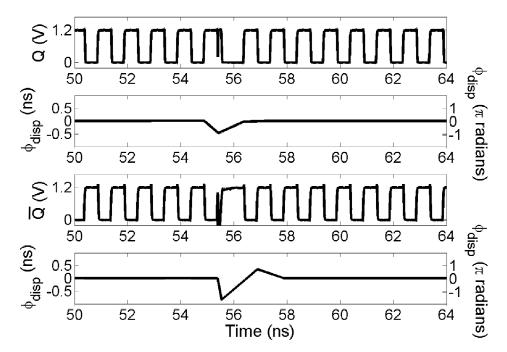

| VIII-4. | An example of two non-identical phase transients on the outputs of a single divide-by-2 circuit. Input frequency is 2 GHz resulting in an output frequency of 1 GHz. Peak of transient approaches a $\Phi_{disp}$ of -1 ns (-2 $\pi$ radians)                                                                                                                                                     | 150  |

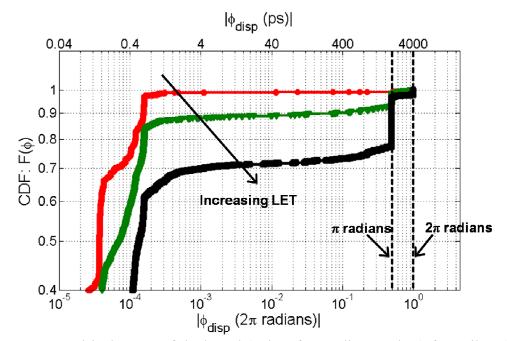

| VIII-5. | Empirical CDFs of the $ \Phi_{disp} $ (units of $2\pi$ radians and ps) for strikes (LETs of 1, 20, and 80 MeV-cm <sup>2</sup> /mg) in the divide-by-2 circuit.<br>Input and output frequencies are 500 MHz and 250 MHz, respectively                                                                                                                                                              | 151  |

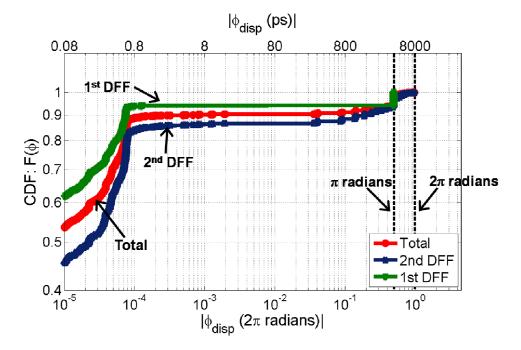

| VIII-6. | Total empirical CDF of the $ \Phi_{disp} $ (units of $2\pi$ radians and ps) for strikes (LET of 20 MeV-cm <sup>2</sup> /mg) in the divide-by-2 circuit. Empirical CDFs for strikes in the 1 <sup>st</sup> and 2 <sup>nd</sup> DFF stages are also shown. Input and output frequencies are 250 MHz and 125 MHz, respectively                                                                       | 152  |

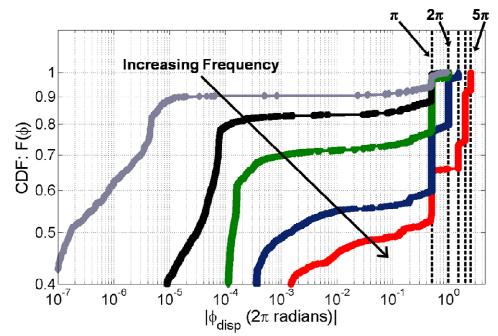

| VIII-7. | Empirical CDFs of phase displacement (units of $2\pi$ radians) for strikes (LET of 80 MeV-cm <sup>2</sup> /mg) in the divide-by-2 circuit for input frequencies of 31 MHz, 250 MHz, 500 MHz, 1 GHz, and 2 GHz                                                                                                                                                                                     | 153  |

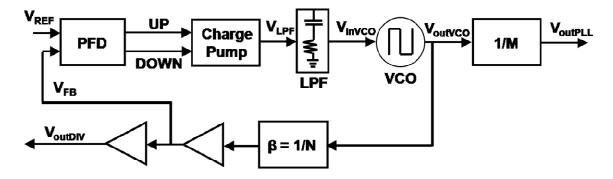

| VIII-8. | General block diagram of the PLL circuit including the phase-frequency detector (PFD), charge pump (CP), low-pass filter (LPF), voltage-<br>controlled oscillator (VCO), feedback frequency divider ( $\beta$ =1/N), output frequency divider (1/M), and buffers.                                                                                                                                 | 155  |

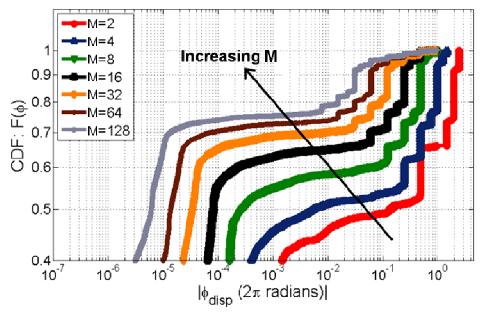

| VIII-9. | Empirical CDFs of phase displacement (units of $2\pi$ radians) for strikes (LET of 80 MeV-cm <sup>2</sup> /mg) in the divide-by- <i>M</i>                                                                                                                                                                                                                                                         | 157  |

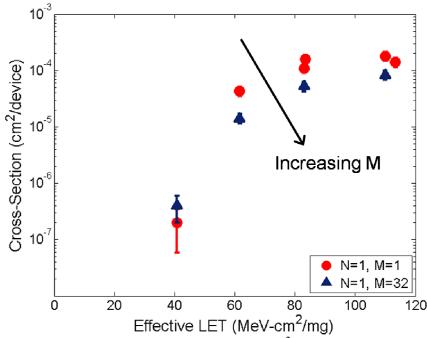

| VIII-10. | Measured event cross-section (cm <sup>2</sup> /device) versus effective LET (MeV-cm <sup>2</sup> /mg) for the programmable Aeroflex PLL discussed in the text. Two different PLL configurations (constant feedback divider) are illustrated at an operating frequency of 100 MHz. Increasing the output divisor, $M$ , decreases the measured cross-sections                                                                             |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

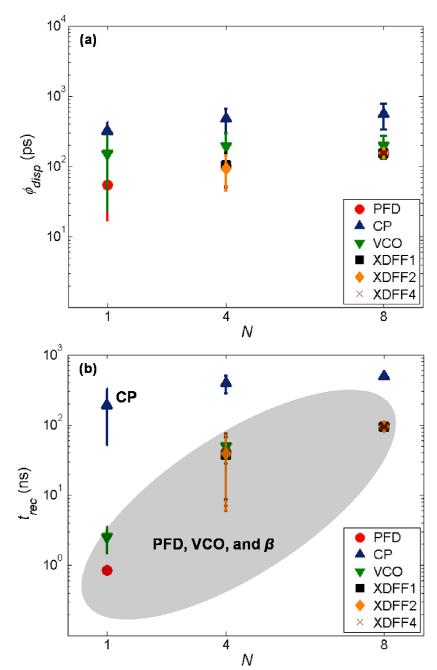

| VIII-11. | Mean (a) $\Phi_{disp}$ and (b) $t_{rec}$ vs. N for SET simulations of strikes in the PFD (nodes UP and DOWN), CP (node $V_{inVCO}$ ), VCO (node $V_{outVCO}$ ), and Frequency Divider (nodes XDFF1, XDFF2, and XDFF4) within the PLL. Simulations were for a deposited charge of 50 fC. All simulations were performed for a constant output frequency of 1.1 GHz                                                                        |

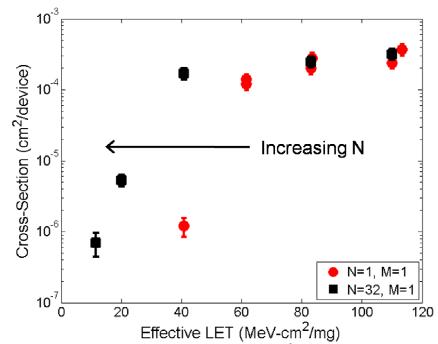

| VIII-12. | Measured event cross-section (cm <sup>2</sup> /device) versus effective LET (MeV-cm <sup>2</sup> /mg) for the programmable Aeroflex PLL discussed in the text. Two different PLL configurations (constant output divider) are illustrated at an operating frequency of 48 MHz. Increasing the feedback divisor, $N$ , decreases the LET threshold                                                                                        |

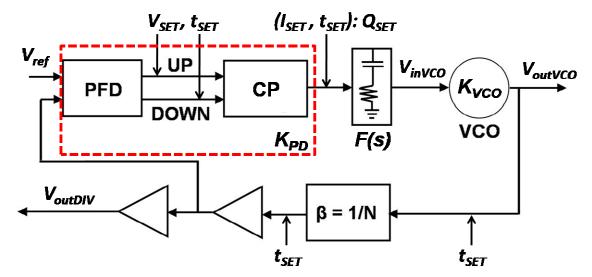

| IX-1.    | PLL model for single transient propagation170                                                                                                                                                                                                                                                                                                                                                                                            |

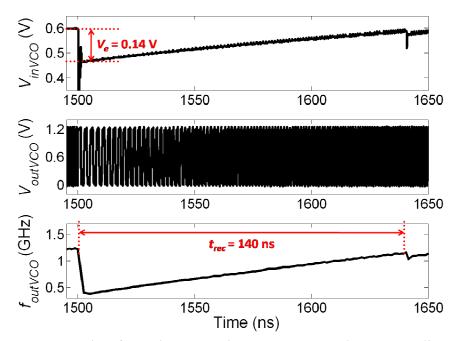

| IX-2.    | An example of a voltage transient on $V_{inVCO}$ and corresponding<br>frequency transient resulting from an initial perturbation at the<br>output of the CP sub-circuit. The simulation was performed on<br>a PLL designed using the IBM CMOS 9SF PDK. The initial<br>perturbation was induced by depositing 300 fC of extraneous charge<br>at the output node of the CP sub-circuit                                                     |

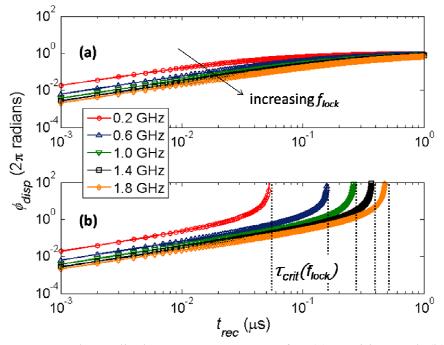

| IX-3.    | Output phase displacement versus $t_{rec}$ for (a) positive and (b) negative frequency modulations as determined by Eqn. (IX-6) and the PLL parameters provided in Table IX-I ( <i>PLL-90nm</i> ). The critical time constant, $\tau_{crit}$ , corresponds to the vertical asymptote on $t_{rec}$ and is determined by Eqn. (IX-7) for various lock frequencies                                                                          |

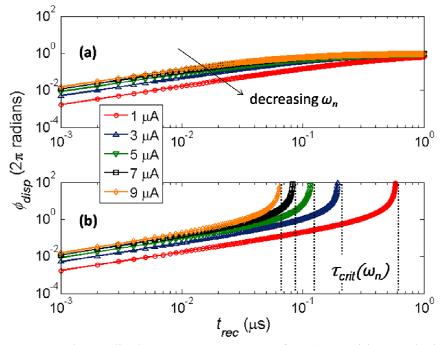

| IX-4.    | Output phase displacement versus $t_{rec}$ for (a) positive and (b) negative<br>frequency modulations as determined by Eqn. (IX-6) and the PLL<br>parameters provided in Table IX-I ( <i>PLL-90nm</i> ). The critical time<br>constant, $\tau_{crit}$ , corresponds to the vertical asymptote on $t_{rec}$ and is<br>determined by Eqn. (IX-7) for various natural frequencies achieved by<br>modifying the charge pump current $I_{CP}$ |

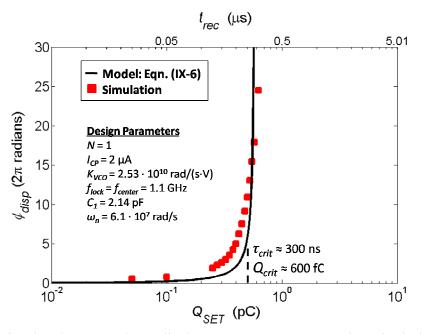

| IX-5.    | Simulated output phase displacement ( $\Phi_{disp}$ ) versus deposited charge at the output of the CP sub-circuit ( $Q_{SET}$ ) and corresponding $t_{rec}$ value following single transient perturbations. The estimated $\tau_{crit}$ and $Q_{crit}$ values resulting from the simulation results and model are approximately 300 ns and 600 fC, respectively                                                                          |

| IX-6.  | Layout view of the PLL-130nm test chip indicating the PLL sub-circuit                                                                                                                                                                                                                                                                                                                       | 188 |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| IX-7.  | Measured VCO transfer characteristics for two <i>PLL-130nm</i> test chips and linear approximation for transient model calculations                                                                                                                                                                                                                                                         | 189 |

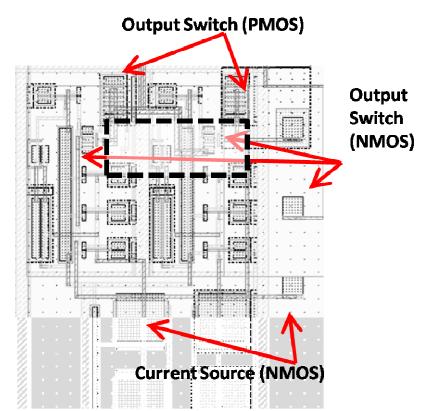

| IX-8.  | Image of the CP sub-circuit captured by an Indigo Alpha near infrared (NIR) focal plane array                                                                                                                                                                                                                                                                                               | 191 |

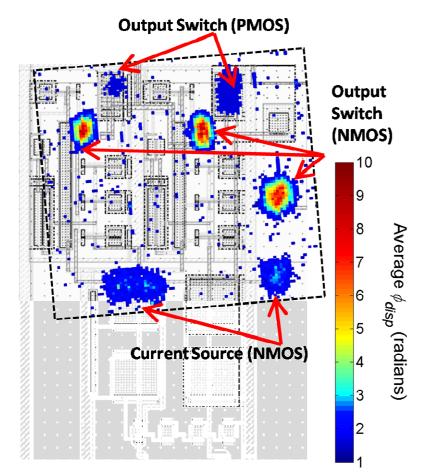

| IX-9.  | An image of the output phase displacement versus x-y location fused to<br>the layout image of the CP sub-circuit. The laser, with incident pulse<br>energy of 3.5 nJ, was scanned through the CP using a step size of 0.2 $\mu$ m.<br>The PLL operating frequency was 200 MHz. Each x-y point represents<br>the average phase displacement for 10 transient perturbations                   | 192 |

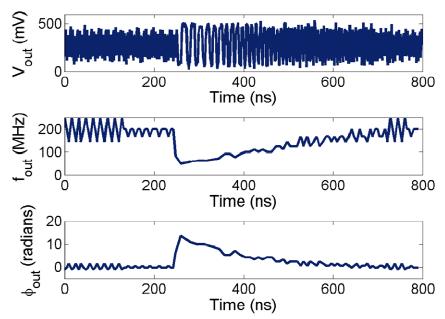

| IX-10. | Example of a measured output frequency/phase transient following a laser perturbation in the CP sub-circuit. The PLL was operating at 200 MHz. Following the laser strike with incident energy of 5.4 nJ, the output frequency was reduced to approximately 50 MHz, thus increasing the output phase displacement to approximately 15 radians. The recovery time of the PLL was over 200 ns | 193 |

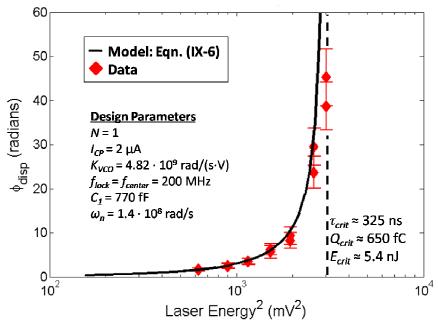

| IX-11. | Average measured phase displacement versus the squared laser energy.<br>Also displayed is the analytical solution to Eqn. IX-6 for the design<br>parameters listed in the figure                                                                                                                                                                                                            | 194 |

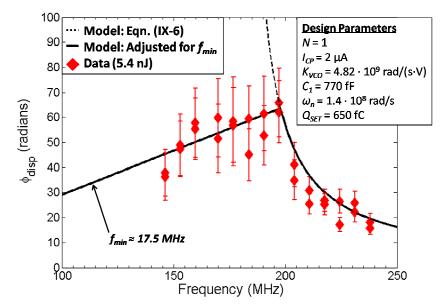

| IX-12. | Average measured phase displacement versus lock frequency within the PLL operating region for incident laser energy of 5.4 nJ. Also displayed is the analytical solution to Eqn. IX-6 for the design parameters listed in the figure assuming a $Q_{SET}$ of 650 fC.                                                                                                                        | 195 |

| C-1.   | Layout view of the conventional charge pump circuit in <i>PLL-130nm</i> indicating the approximate region of interest for the results displayed in Fig. C-2                                                                                                                                                                                                                                 | 216 |

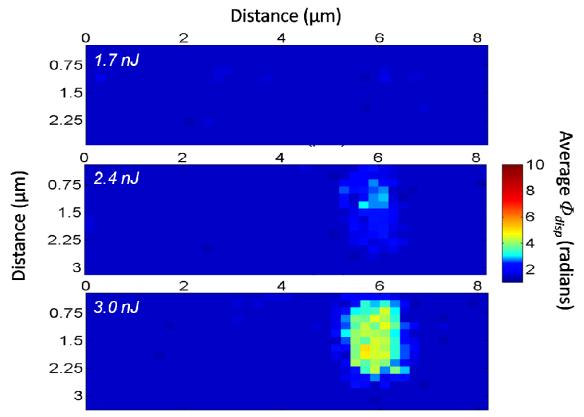

| C-2.   | 2D transient maps (0.2 $\mu$ m x-y resolution) of the output phase displacement ( $\Phi_{disp}$ ) as a function of incident laser energy (see Chapter IX) at a PLL operating frequency of 150 MHz                                                                                                                                                                                           | 217 |

# LIST OF TABLES

| Table |                                                                                                           | Page |

|-------|-----------------------------------------------------------------------------------------------------------|------|

| V-1.  | PLL General Design Specifications                                                                         | 75   |

| V-2.  | Criteria for Loss-of-Lock                                                                                 | 85   |

| IX-1. | <i>PLL-90nm</i> and <i>PLL-130nm</i> Design Parameters (Designed Using IBM CMOS9SF and CMRF8RF Processes) | 171  |

| IX-2. | Ideal Recovery Times for Transient Perturbations Generated Within Each PLL Sub-Circuit                    | 173  |

## CHAPTER I

#### INTRODUCTION

A reliability concern of growing interest in the microelectronics community is the deleterious effect of ionizing radiation. The so-called "single events" – single particles which can penetrate semiconductor material leaving ionized charge in their wake – can cause information corruption and transient system failure. Single events are ubiquitous – this radiation exists in the environment external to a circuit, and emanates from processing and packaging material integral to a circuit. Once only the concern of spacebound systems where increased susceptibilities to SEEs have been reported as device feature sizes decrease and operating frequencies increase [Bu01, Do96], integrated circuit (IC) density and power scaling have propelled this issue to the forefront of reliability concerns at current technology nodes in ground-based and space-deployed electronic systems.

The increased susceptibility to single-event effects (SEE) in advanced Complementary Metal-Oxide Semiconductors (CMOS) can be attributed primarily to factors associated with device scaling trends [Jo98]. Early scaling theories through the 1970's and 1980's followed two basic approaches: constant-voltage scaling and constantfield scaling [Ba84, De74]. In recent years, however, the higher currents necessary for greater operating frequencies, in combination with the need for higher packing densities, require the semiconductor devices to have shorter channel lengths and widths with higher oxide breakdown fields [Hu93]. These scaling pressures are principally constrained by the acceptable leakage currents when the transistors are "off," and many works have focused on more complicated scaling algorithms to counteract these scaling tradeoffs. Ultimately, the fast-paced scaling trends in CMOS technologies, consequently decreasing nodal capacitances [Ba84], results in increased single-event (SE) vulnerabilities by reducing the minimum amount of charge (i.e., critical charge) required to alter the state of a circuit node [Pe82].

Furthermore, as device feature sizes decrease, the nodal separation between devices in an IC also decreases. The decrease in nodal separation results in a phenomenon not previously encountered in pre-nanometer technologies; that is, higher package densities result in increased probabilities of multiple devices collecting charge from a single ion strike (i.e., charge sharing). This phenomenon has recently been characterized in 130 nm technologies [Am06, Am07] and will no doubt be a primary concern for future CMOS electronics as the drive for faster speeds and higher packing densities continues.

An SE occurs when a high-energy ionizing particle, such as a heavy ion, strikes the circuit. As the particle penetrates the semiconductor material it loses energy through Coulombic interactions with the lattice structure and leaves a dense track of electron-hole pairs in the material. These excess carriers can be collected as charge on circuit nodes, resulting in undesirable circuit responses which can vary depending on the circuit topology and the amount of charge collected [Do03, Ma93]. In mixed-signal (analog and digital) systems, the effect of an SE particle strike is the generation of a transient signal (single-event transient or SET) that competes with the legitimate signals propagating through a circuit or perturbs the functionality of the circuit. In digital circuits, an SET can result in a single-event upset (SEU), that is, an alteration of the state of memory

circuits (e.g., a memory cell can be changed from a logic "0" state to a logic "1" state). The SEU can lead to a circuit error if the corrupted data propagates throughout the circuit and is observable at the output. These upsets are often termed "soft errors" as they do not result in permanent failures within the circuit. However, there exists no standard metric for soft errors in analog and mixed-signal circuits, as the effect of an SE is dependent on the circuit topology, type of circuit, and the operating mode.

Since first reported through heavy-ion induced experiments [Ko93], SET effects in analog microelectronics have been examined through a variety of experimental procedures [Bu87, Ec94, Mc03, Pe02, Po99, Sa02, Sa03] and computer simulation techniques [Ad00, Bo04a, Jo00b, Pe01, St02b]. Furthermore, the combination of experimental testing and simulation efforts has enabled an understanding of analog SEE that experimental testing alone did not provide [Bo04b].

In recent years, there is a particular interest in the effect of SETs on the phase-locked loop (PLL) because of the propensity to cause a loss of frequency integrity, and the resultant wide-spread impact on high-performance systems [Bo05, Bo06, Ch06b, Ch06a, Ha05a, Ha05b, Jo96a, Lo06, Lo07a, Lo08, Lo09, Lo07b, Lo07c]. In fact, voltage-controlled oscillators (VCO) - integral components of PLL circuits - have been reported to have increased susceptibilities to SEE in advanced technology nodes [Bo05]. Additionally, as PLLs (sometimes termed bit synchronization circuits, or clock-recovery circuits) are widely used in commercial and space-deployed electronics systems to reduce the phase delay associated with the distribution of clock signals, to generate high-speed clock signals, and to synchronize data transfer [Ba08, Be98], there is a growing interest on the impacts SETs in the PLL can have on circuit designs that utilize PLLs for clock

signals [SEE04]. Furthermore, recent works have not only identified the most sensitive PLL sub-circuit to SEs [Bo06], but have designed and verified radiation-hardened-by-design (RHBD) alternatives that reduce the effects of SEs in the PLL by orders of magnitude over conventional designs [Lo06, Lo07a, Lo07b, Mc07]. These results indicate that RHBD is effective for high-speed mixed-signal circuits using unconventional analog design techniques and targeted SE circuit simulations.

This dissertation applies circuit-level simulations and experimental testing to characterize the effects of SEs on a general PLL topology. The simulations and experimental procedures target the PLL sub-circuits so that individual contributions to the overall PLL SE vulnerability are distinguished and analyzed. RHBD alternatives to each sub-circuit are offered if necessary. Additionally, novel analyses are presented that can effectively predict the relative contributions of SET generation within the PLL. Furthermore, the analyses are utilized to develop a generalized model for single transient propagation through the PLL.

Although this work primarily discusses PLLs in the context of on-chip clock generation and skew reduction in the presence of single ionizing particles, it is the goal of this work to present a generalized model for single transient propagation through PLL topologies for a variety of applications and environments. The transient model is formulated from a conventional linear PLL model commonly used in a variety of noise analyses [Ha04, He04, Kr82, Me02]. However, the model is unique in that the resulting fundamental design equations are derived in closed-form under the assumption that transients are a result of single transient impulses applied to the various sub-circuits rather than continuous nondeterministic sources. This approach vastly simplifies the

analysis and provides insight into the closed-loop parameters that directly influence the generation and propagation of transients through the PLL. As a result, a list of design guidelines is developed that can be applied to all PLL topologies. The set of principles may be applied for 'analytical transient mitigation' to reduce the sensitivity of PLLs to single transients resulting from extrinsic noise sources such as single-event radiation and crosstalk noise.

#### Organization of Dissertation

The research effort presented in this dissertation is organized as follows:

- 1) Chapter I introduces the motivation for this work.

- 2) Chapter II provides a detailed background on phase-locked loop circuits, including a control-systems analysis and derivations of important electrical parameters and characteristics. Also discussed are the detailed topologies of each PLL sub-circuit and any critical design equations.

- 3) Chapter III provides a background on SEEs, especially those of particular pertinence to this work. An introduction to the space radiation environment is included along with a discussion of the various radiation effects including totalionizing dose, displacement damage, and SEEs. However, the section primarily focuses on SEEs. Finally, charge generation and collection mechanisms for SEEs are discussed.

- Chapter IV focuses on two common methods employed in this work for modeling SETs in circuit simulators. Also, some examples of various SETs observed in analog and digital circuits are presented.

- 5) Chapter V details SETs generated within unity gain PLL circuits specifically. Simulation and laser two-photon absorption experimental results will be presented for the phase-frequency detector, voltage-controlled oscillator, and charge pump sub-circuits.

- 6) Chapters VI and VII discuss SETs in the voltage-controlled oscillator sub-circuit exclusively. Various models, simulations, and novel analysis techniques are presented for the SET characterization of mixed-signal topologies. Additionally, numerous hardening options for the VCO are presented.

- 7) Chapter VIII provides an analysis of SETs in frequency divider topologies. Further, the various impacts of the divider configuration on SETs generated internal and external to programmable PLL topologies is discussed.

- 8) Chapter IX presents a systems-oriented analysis of SET generation and propagation in PLLs. Specifically, the closed-loop parameters that have a direct impact on SET generation are identified. Additionally, a novel design/analysis parameter, the 'PLL critical time constant', is presented to facilitate the design of PLL circuits in extrinsically noisy environments. A general list of design guidelines for the analytical mitigation of single transients in PLL circuits is provided.

- 9) Chapter X will provide some concluding remarks regarding the presented research.

### CHAPTER II

#### PHASE-LOCKED LOOPS

## Introduction

For a basic understanding of phase-locked loops (PLL), this chapter provides a background on PLL topologies and develops a set of linear models for PLL feedback systems, including the fundamental design equations for PLL development. A derivation of the closed-loop transient response and fundamental tracking properties is also provided as necessary for the subsequent chapters. Although PLL systems are highly non-linear in practice it is useful to approximate PLLs as linear negative feedback networks for a fundamental understanding of their functionality. The chapter will conclude by presenting the various PLL building blocks examined throughout this work, including the phase-frequency detector, charge pump, loop filter, voltage-controlled oscillator, and frequency divider.

#### Basic PLL Topology

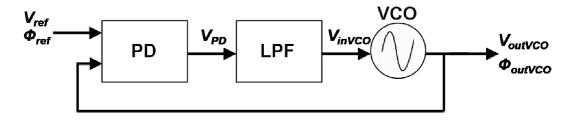

The general idea behind a PLL is to create a stable output signal that is synchronized to an input reference signal. The input reference signal, for example, may be a digital clock signal or data received from a transmission network. Therefore, in steady-state, the output phase of the PLL should be "in lock" with the phase of the input signal; that is, the difference between the input and output phases ( $\Phi_{outVCO} - \Phi_{ref}$ ) should not be changing over time. The basic architecture of a PLL is shown in Fig. II-1 and consists of a phase detector (PD), low-pass filter (LPF), and voltage-controlled oscillator (VCO).

Fig. II-1. Diagram of a basic PLL consisting of a phase detector (PD), low-pass filter (LPF), and voltage-controlled oscillator (VCO).

The PD compares the phase of the output signal ( $V_{outVCO}$ ) to the phase of the reference signal ( $V_{ref}$ ), generating an error signal ( $V_{PD}$ ) describing the phase difference ( $\Phi_{outVCO} - \Phi_{ref}$ ) between  $V_{outVCO}$  and  $V_{ref}$ . Ideally the error signal consists only of a DC component for the control of the VCO; however undesirable high-frequency noise is typically coupled onto the node and must be filtered through a LPF. The resulting control voltage ( $V_{inVCO}$ ) is then fed to the VCO to set the oscillating frequency.

As the PLL compares the phases of the input/output signals it requires no knowledge of the voltages or currents on the input/output nodes. Therefore, for sufficient phase gain  $(\Phi_{outVCO} / \Phi_{ref})$ , the phase difference between the two signals is expected to be small in steady state, denoting phase alignment (phase lock). Thus, in steady state  $\Phi_{outVCO} - \Phi_{ref}$  should be constant and close to zero. From this property, the loop is said to be in lock if  $\Phi_{outVCO} - \Phi_{ref}$  does not change with time, thus following Eqn. (II-1). As frequency is the derivative of phase with respect to time, Eqn. (II-2) also holds true for PLLs in the lock state. Thus, for the PLL shown in Fig. II-1, the output frequency is equivalent to the input frequency while in phase lock (unity gain) [Ra01].

$$\frac{\partial \phi_{outVCO}}{\partial t} - \frac{\partial \phi_{ref}}{\partial t} = 0$$

(II-1)

$$\omega_{outVCO} = \omega_{ref} \tag{II-2}$$

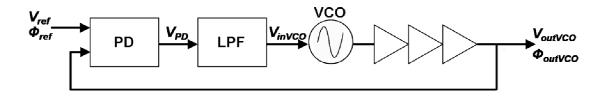

While a unity gain PLL that produces an output signal that is in phase with an input signal of equivalent frequency is not terribly practical, the basic topology may be developed for a variety of applications. For example, large ICs require a clock distribution network such that single or multiple clocks are required to drive thousands of transistors in multiple locations throughout the IC. Driving an entire IC with a single clock may result in clock skew and decrease the performance. Therefore a PLL may be designed to include high current drive buffers internal to the loop such that the high current drive output signal of the PLL is in phase lock with the reference clock, as seen in Fig. II-2. This technique may also be used to regenerate a full swing clock signal with large drive strength from an attenuated reference signal.

Fig. II-2. Diagram of a PLL for reducing the clock skew associated with clock distribution. Buffers are included internal to the closed-loop.

Fig. II-3. Diagram of a PLL for high-frequency clock generation.

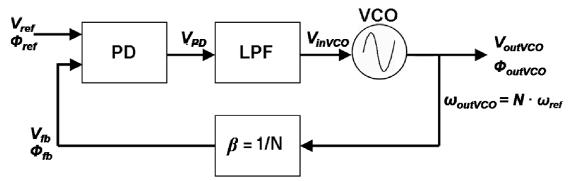

Many applications, such as frequency synthesis and high-frequency clock generation, require the signal generated by the PLL to have a different frequency than the reference signal. High-frequency clock generation, for example, may be achieved by designing a high-frequency VCO and including a frequency divider in the loop feedback network. In this case, the output phase of the frequency divider ( $\Phi_{fb}$ ) is compared to phase of a low-frequency reference signal ( $\Phi_{ref}$ ), as shown in Fig. II-3. Thus, the output frequency of the PLL is a multiple of the input frequency and is related to the input frequency by Eqn. (II-3). Rather than creating a high-frequency clock off-chip and supplying the signal to the IC, this technique allows for high frequency clock generation on-chip, thus reducing the clock skew associated with the input capacitance. Frequency divider circuits may also be placed in additional locations internal and external to the closed-loop for a variety of frequency synthesis applications in order to generate signals at multiple frequency levels [Ba08, Be98, Le04a, Ra01].

$$\omega_{out} = N\omega_{ref} = \frac{\omega_{ref}}{\beta}$$

(II-3)

Although many applications for PLL circuits exist, this section shows three basic configurations commonly referred to throughout this dissertation. The following section discusses the linearized models used for the design of the PLLs discussed throughout this work.

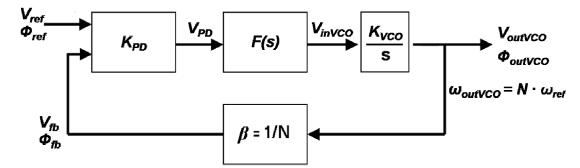

#### A Linear PLL Model

The basic linear model of the PLL is shown in Fig. II-4, where  $K_{PD}$  is the gain of the phase detector (PD), F(s) is the LPF transfer function (integrator),  $K_{VCO}$  is the gain of the VCO, and  $\beta$  is the feedback factor (adapted from [Be98]).  $K_{PD}$  has units of volts/radian or amps/radian (dependent on the type of PD) and  $K_{VCO}$  has units of radians/(second·volt). Since the PLL compares the phases of the output and reference signals rather than the frequencies, the integral of the VCO stage must be used in order to obtain the phase. As the Laplace transform of a constant *C* is *C*/*s*, the gain of the VCO stage is  $K_{VCO}/s$ , and thus adds a pole to the loop.

Fig. II-4. Linear model for a PLL (adapted from [Be98]).

# Open and Closed Loop Analyses

The linear model displayed in Fig. II-4 is the fundamental building block for a wide variety of PLL analyses; consequently, the open-loop transfer function is given by Eqn. (II-4).

$$G(s) = \frac{\phi_{out}}{\phi_{ref}}(s) \bigg|_{open} = K_{PD}F(s)\frac{K_{VCO}}{s}$$

(II-4)

The closed-loop transfer function (H(s)) may be readily obtained from Eqn. (II-4) through a standard control-systems analysis and is shown by Eqn. (II-5).

$$H(s) = \frac{G(s)}{1 + \beta G(s)} = \frac{K_{PD}F(s)\frac{K_{VCO}}{s}}{1 + \beta \cdot K_{PD}F(s)\frac{K_{VCO}}{s}} = \frac{K_{PD}F(s)K_{VCO}}{s + \beta \cdot K_{PD}F(s)K_{VCO}}$$

(II-5)

$$F(s) = \left( R_P + \frac{1}{C_1 s} \right) = \frac{1 + s R_P C_1}{s C_1}$$

(II-6)

Assuming the loop filter consists of at least one pole and is of the form shown by Eqn. (II-6), the PLL is minimally a second order closed-loop system and therefore has a natural frequency ( $\omega_n$ ) and damping ratio ( $\zeta$ ). Accordingly, the closed-loop transfer function can be expressed as Eqn. (II-7), such that the denominator is in the format  $s^2 + 2s\zeta\omega_n + \omega_n^2$ .

$$H(s) = \frac{K_{PD}K_{VCO}(1 + sR_{p}C_{1})}{s^{2} + s(K_{PD}K_{VCO}\beta) + \frac{K_{PD}K_{VCO}\beta}{C_{1}}}$$

(II-7)

The 2<sup>nd</sup> order transfer equation indicates that the PLL system can be overdamped ( $\zeta > 1$ ), underdamped ( $\zeta < 1$ ), or critically damped ( $\zeta = 1$ ), where  $\zeta$  is the damping ratio. Some works commonly refer to the Q factor rather than the damping ratio, where  $Q = 1/(2\zeta)$ . Accordingly, the natural frequency ( $\omega_n$ ) and the damping ratio ( $\zeta$ ) may be determined by Eqns. (II-8) and (II-9), respectively. The natural frequency is a measure of the response time of the loop, whereas the damping ratio measures the loop ringing and overshoot. Conventional guidelines suggest that the natural frequency should be designed to be as large as possible in order to minimize the loop response time [Ba08]. Furthermore, to obtain a maximally flat magnitude in the pass band,  $\zeta$  should be designed to equal  $1/\sqrt{2}$ . In order to avoid excessive ringing  $\zeta$  is typically designed to be approximately equal to 1.

$$\omega_n = \sqrt{\frac{K_{PD}K_{VCO}\beta}{C_1}}$$

(II-8)

$$\zeta = \frac{\omega_n}{2} R_p C_1 \tag{II-9}$$

The closed-loop PLL system as described by Eqn. (II-7) has two poles given by Eqn. (II-10). Thus, if  $\zeta > 1$ , both poles are real and the system is overdamped. On the other hand, both poles are complex and the system is underdamped for  $\zeta < 1$ . Furthermore, if  $\zeta = 1$ , both poles are equal to  $-\omega_n$  and the system is critically damped.

$$s_{1,2} = -\zeta \omega_n \pm \sqrt{\left(\zeta^2 - 1\right)\omega_n^2} = \omega_n \left(-\zeta \pm \sqrt{\zeta^2 - 1}\right)$$

(II-10)