# SINGLE EVENT LATCHUP IN A DEEP SUBMICRON CMOS TECHNOLOGY

By

John M. Hutson

Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

## DOCTOR OF PHILOSOPHY

In

**Electrical Engineering**

December, 2008

Nashville, TN

Approved:

Ron Schrimpf

Robert Weller

Robert Reed

Lloyd Massengill

Senta Greene

But there's no sense crying over every mistake. You just keep on trying till you run out of cake. And the science gets done. And you make a neat gun for the people who are still alive.

> -Still Alive, Jonathan Coulton

#### ACKNOWLEGEMENTS

To Ron Schrimpf, for being patient with me as a student and helping me along in my research. Your leading questions led to many good results and many answers that were better than the ones I had. To Bob Weller and Robert Reed, who I've always seen as an extra pair of advisors. Your encouragements and insights have made me a better engineer. To all the students of the RER group from whom I have learned innumerable things from. In particular, without the assistance of Alan Tipton, Johnny Pellish, Awole Amusan, Christina Howe, Phillipe Adell, and Claude Cirba, I would not have reached this point. To all of the professors and engineers in the RER group and ISDE who have criticized, suggested, and taught me many things in the last seven years. To the administrative assistants throughout the years that have helped me keep my head above water, particularly Connie Nichols who helped many a graduate student adjust to Vanderbilt. To Lisa, who has been the constant friend and shoulder to lean on in the last year. To Beth, who has been my on-call cheerleader. Without your encouragement and counsel I could not have made it through the last three years. To my parents, for pushing me to achieve what I was capable of and teaching me to stubbornly refuse to give up. To the huge list of people who have helped or aided me in any way in my time at Vanderbilt, thank you for your kind mercies be they large or small.

# TABLE OF CONTENTS

| CHAPTER                                                                                                                                                                                                                                                                                                                                             | PAGE                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| ACKNOWLEGEMENTS                                                                                                                                                                                                                                                                                                                                     | III                                          |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                   | IV                                           |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                     | V                                            |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                      | VIII                                         |

| I. INTRODUCTION                                                                                                                                                                                                                                                                                                                                     | 1                                            |

| II. THE SPACE RADIATION ENVIRONMENT AND SINGLE-EVENT EFFECTS                                                                                                                                                                                                                                                                                        | 5                                            |

| THE SPACE RADIATION ENVIRONMENT<br>Trapped Particles<br>Transient Particles<br>MECHANISMS FOR SINGLE-EVENT EFFECTS<br>Charge Deposition<br>Direct and Indirect Ionization<br>Charge Transport and Collection                                                                                                                                        |                                              |

| III. LATCHUP IN CMOS DEVICES                                                                                                                                                                                                                                                                                                                        |                                              |

| ELECTRICAL LATCHUP<br>SINGLE EVENT LATCHUP.<br>ENVIRONMENTAL INFLUENCES ON LATCHUP SENSITIVITY<br>SEE Test Standards<br>Effects of Temperature on Single Event Latchup<br>Effects of Particle Angle of Incidence on Single Event Latchup<br>Proton Induced Single Event Latchup<br>EFFECTS OF SCALING ON LATCHUP<br>SINGLE EVENT LATCHUP MITIGATION | 24<br>26<br>26<br>28<br>32<br>36<br>42<br>48 |

| RELATED PHENOMENA                                                                                                                                                                                                                                                                                                                                   |                                              |

| IV. CALIBRATION OF TCAD MODELS                                                                                                                                                                                                                                                                                                                      |                                              |

| V. TCAD MODELING AND ANALYSIS OF 65 NM SCR DEVICES                                                                                                                                                                                                                                                                                                  |                                              |

| DEVICE STRUCTURE<br>TCAD SIMULATION: RESULTS AND DISCUSSION<br>SEL RATE ISSUES<br>SUMMARY                                                                                                                                                                                                                                                           | 64<br>75                                     |

| VI. ANALYSIS OF SINGLE-EVENT LATCHUP IN 65 NM SRAMS                                                                                                                                                                                                                                                                                                 |                                              |

| INTRODUCTION<br>DEVICE STRUCTURES<br>EXPERIMENTAL SETUP<br>EXPERIMENTAL RESULTS<br>Cross Section Tests with <sup>84</sup> Kr<br>Temperature and LET Thresholds<br>Angular Effect on SEL Fluences<br>DISCUSSION<br>SUMMARY                                                                                                                           |                                              |

| VII. SUMMARY AND CONCLUSIONS                                                                                                                                                                                                                                                                                                                        |                                              |

| REFERENCES                                                                                                                                                                                                                                                                                                                                          |                                              |

# LIST OF FIGURES

# FIGURE .....PAGE

| Figure 1.1. Current draw on a 1.8V power supply for three subsequent latches in three different on-chip         |

|-----------------------------------------------------------------------------------------------------------------|

| locations. The latchups are induced by a pulsed laser in sensitive areas of the device. It can be seen          |

| that the power draw for the device is 6x normal operating current [8]                                           |

| Figure 2.1. Diagram of the Van Allen belts. Trapped protons are trapped closer to the earth while trapped       |

| electrons form the outer shell [17]                                                                             |

| Figure 2.2. Motion of trapped particles in the Earth's magnetosphere. Particles can be seen to spiral around    |

| the field lines as well as bouncing back and forth at the mirror points. Drift direction of particles is        |

| also shown [17, 20]7                                                                                            |

| Figure 2.3. Trapped proton energies as a function of distance from the Earth's core in Earth radii. Peak        |

| proton energy falls off with distance from the earth [20]                                                       |

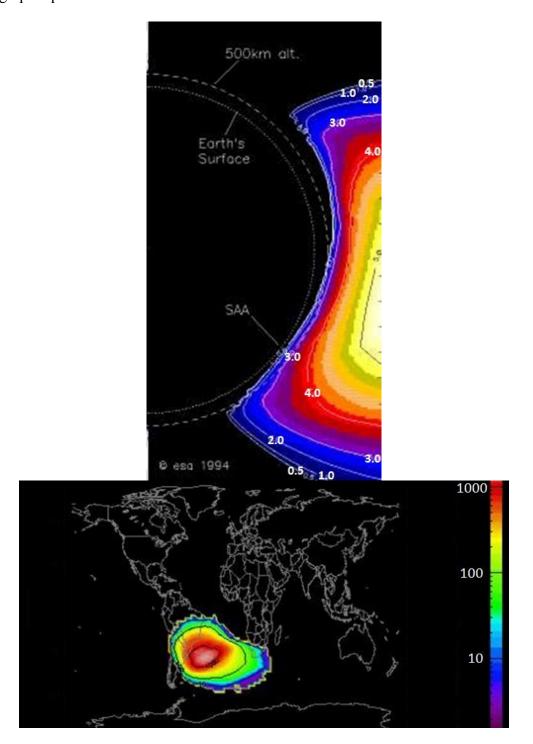

| Figure 2.4. (a) The South Atlantic Anomaly. Proton flux can be seen to increase considerably at low             |

| altitudes in the South Atlantic. Flux is shown for powers of ten in $cm^2/s$ for protons > 10MeV. After         |

| [24] (b) Contour plot of proton fluxes > 10 MeV in the SAA at a 500 km altitude during solar                    |

| maximum. Flux is shown in units of $cm^2/s$ . After [30]                                                        |

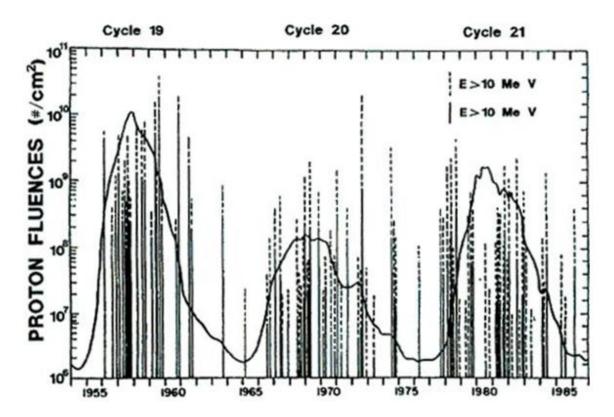

| Figure 2.5. Solar activity and solar proton events for cycles 19-21. Multiple events exceeding fluences of      |

| 109 protons over 10 MeV in energy are shown for each active sun cycle. The right Y-axis maps these              |

| events to the Zurich (or Wolf) Sunspot Number which gauges solar activity [31, 32]                              |

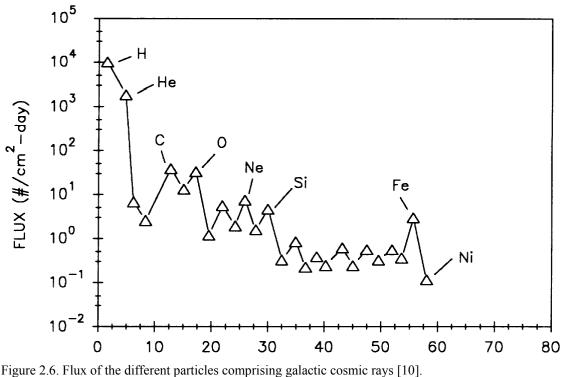

| Figure 2.6. Flux of the different particles comprising galactic cosmic rays [10]                                |

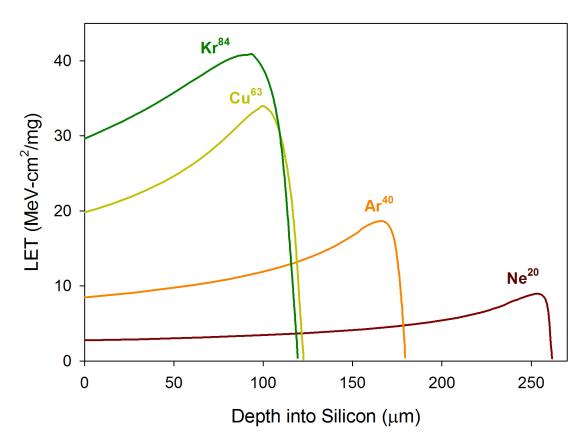

| Figure 2.7. Plots of the four ion species listed in table 7.2 in Chapter VI on a silicon target. Instantaneous  |

| dE/dx is plotted in units of MeV-cm <sup>2</sup> /mg vs. depth into the silicon target [33]                     |

| Figure 2.8. Examples of indirect ionization processes for protons in silicon [34]                               |

| Figure 3.1. (a) SEM photograph of metallization failure induced by latchup after the silicon nitride layer      |

|                                                                                                                 |

| was removed. (b) SEM photo of a region damaged from current during latchup where the                            |

| metallization line remains conductive even though metal has been ejected from over 90% of the                   |

| conducting metal line. [49]                                                                                     |

| Figure 3.2. Typical CMOS structure showing parasitic components and latch-up path. Well and substrate           |

| resistances are added for comparison to inset in figure 3.3. After [53]                                         |

| Figure 3.3. Typical I-V characteristics for forward injection of a PNPN structure [54]. Inset: circuit layout   |

| of parasitic BJTs with well and substrate resistances from figure 3.2. 21                                       |

| Figure 3.4. I-V curves for (a) an emitter-base (P-source/N-well) junction and (b) a base-emitter (N-            |

| source/P-well) junction in 65nm CMOS technology. Changing the environment temperature results in                |

| exponential changes in current, allowing the parasitic bipolar transistors to turn on at lower voltages.        |

|                                                                                                                 |

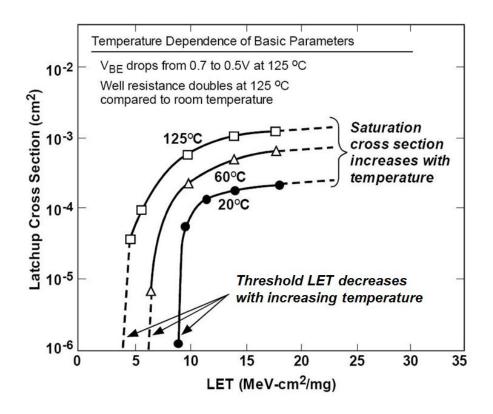

| Figure 3.5. Temperature-dependence of SEL cross sections for heavy-ion tests. Cross-section increases and       |

| threshold LET decreases with increasing temperature. The cross section increases by more than an                |

| order of magnitude and the threshold LET is halved changing from room temperature to 125 °C                     |

| [100]                                                                                                           |

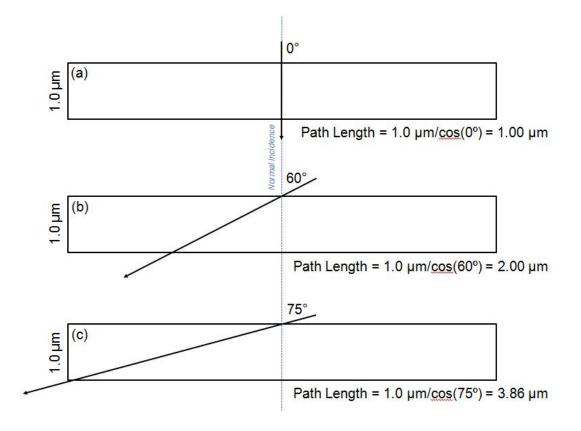

| Figure 3.6. Demonstration of ion path lengths through shallow 1.0 $\mu$ m deep thin sensitive volume structures |

| at varying angles of incidence. The increasing path length with increasing angle of incidence (and              |

| thus increasing energy deposition can be seen. The 60° incidence strike shown in (b) is twice as long           |

| as the normal incidence strike. The 75° incidence strike shown in (c) is almost four times as long as           |

| the normal incidence strike                                                                                     |

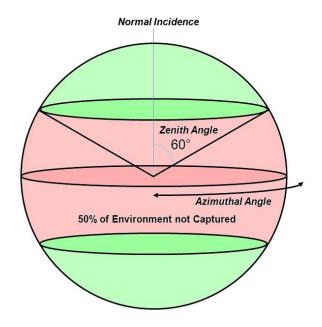

| Figure 3.7. Conceptual graphic of an isotropic environment and coverage by testing 60° from normal              |

| incidence. It can be seen that testing at only up to 60° from normal incidence only covers 50% of the           |

| solid angle from an isotropic environment. Effects from the top are similar to those entering from the          |

| bottom. After [126]. Variance along the azimuthal angle noted in the figure is also not considered by           |

| JEDEC test JESD57                                                                                               |

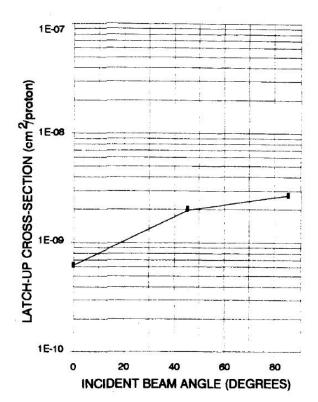

| Figure 3.8. (a) 5x increase in SEL cross-section for a 64 K memory when going from normal incidence to          |

| grazing angle for 60 MeV protons [66]                                                                           |

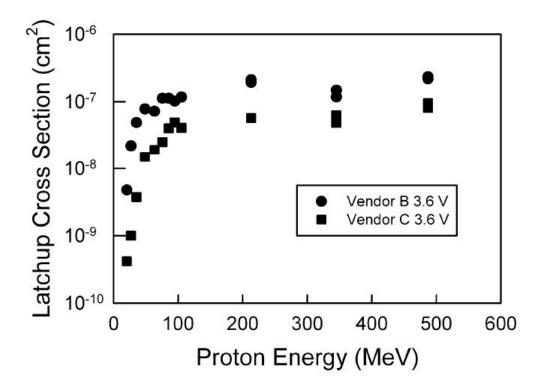

| Figure 3.9. Latchup cross section of two memories vs. proton energy at normal incidence [127]                   |

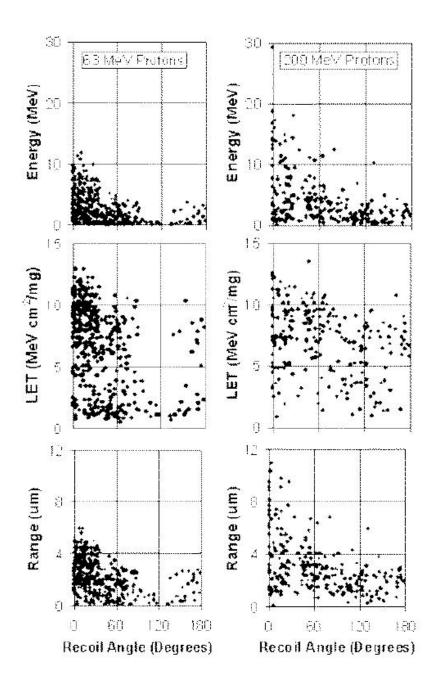

| Figure 3.10. Simulated distribution of spallation recoil energy, LET, and range in silicon for 63- and 200-<br>MeV protons [120] |

|----------------------------------------------------------------------------------------------------------------------------------|

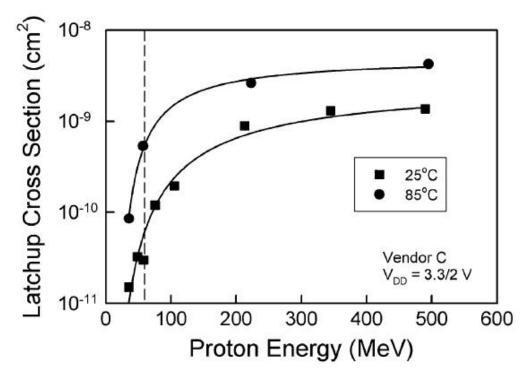

| Figure 3.11. Latchup cross section vs. proton energy for 0.16/0.14 µm SRAMs measured at room                                     |

| temperature and 85 °C [87]                                                                                                       |

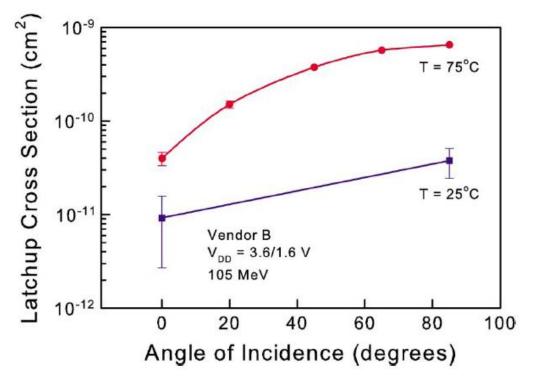

| Figure 3.12. Latchup cross section for 105 MeV protons vs. angle of incidence for 0.14 µm SRAMs                                  |

|                                                                                                                                  |

| measured at room temperature and 75 °C [86]                                                                                      |

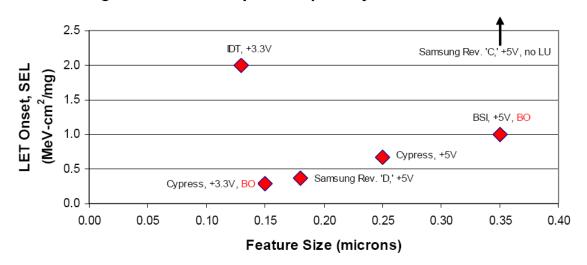

| Figure 3.13. SEL susceptibility vs. device feature size for commercial-off-the-shelf 1M and 4M SRAMS.                            |

| BO indicates a part burn-out (non-recoverable damage) due to latchup [130]                                                       |

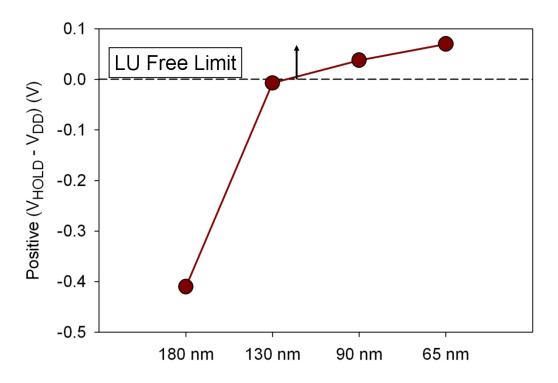

| Figure 3.14. Holding voltage minus supply voltage for four technology nodes for positive injection at room                       |

| temperature. This value increases as technology scales, making latchup harder to achieve [129] 44                                |

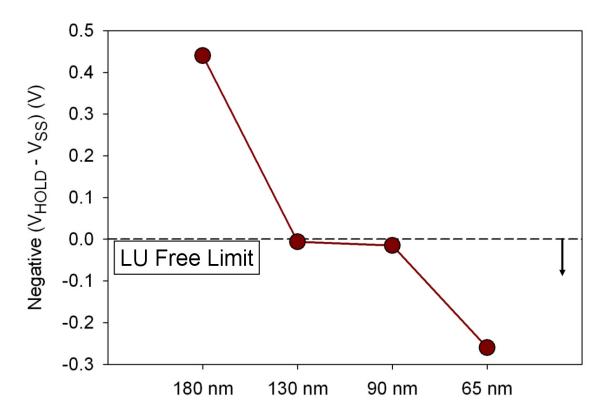

| Figure 3.15. Holding voltage minus supply voltage for four technology nodes under negative injection at                          |

| room temperature. This value decreases as technology scales, making latchup harder to achieve                                    |

| [129]                                                                                                                            |

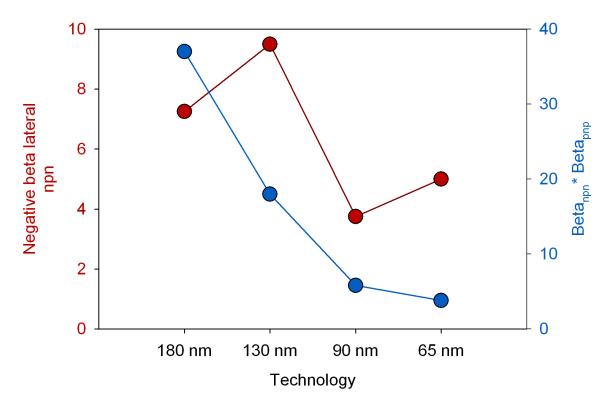

| Figure 3.16. Gain of the lateral parasitic NPN transistor (left) and the beta product (right) vs. technology                     |

| node for SCR devices at room temperature. The beta product decreases as technology scales, making                                |

| latchup harder to achieve [129]                                                                                                  |

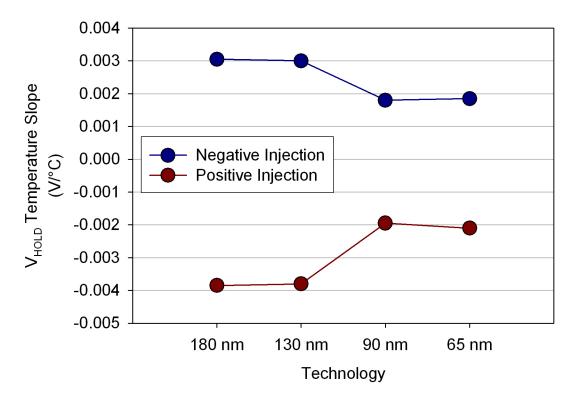

| Figure 3.17. Holding voltage (positive and negative) temperature slopes vs. technology node [129]. This                          |

| data represents the rate at which the value of the holding voltage changes with temperature for SCR                              |

| devices in four technology nodes                                                                                                 |

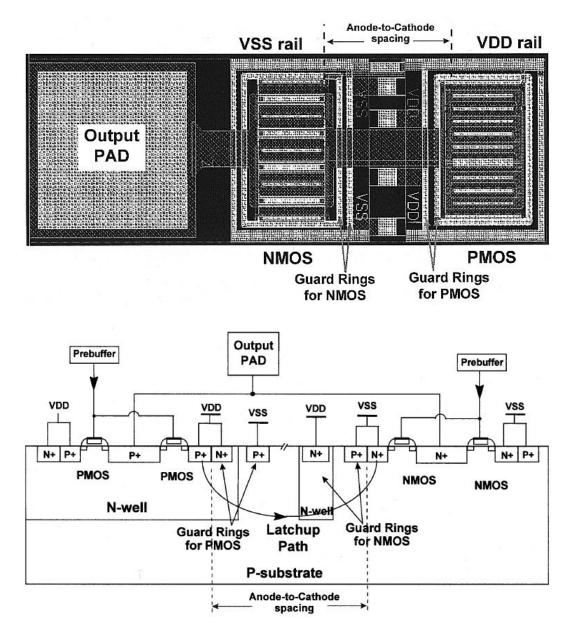

| Figure 3.18. (a) Layout example of an inverter output buffer in the I/O cell with double guard rings to                          |

| prevent latchup in a 0.5µm nonsilicided bulk CMOS process (b) Cross-section of the above device                                  |

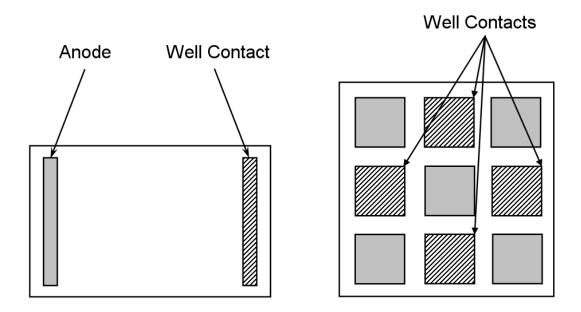

| showing the double guard rings around both PMOS and NMOS devices [131]                                                           |

| Figure 3.19. (a) Sparsely-placed well contacts and (b) Densely placed well contacts. Modeled after [76] 51                       |

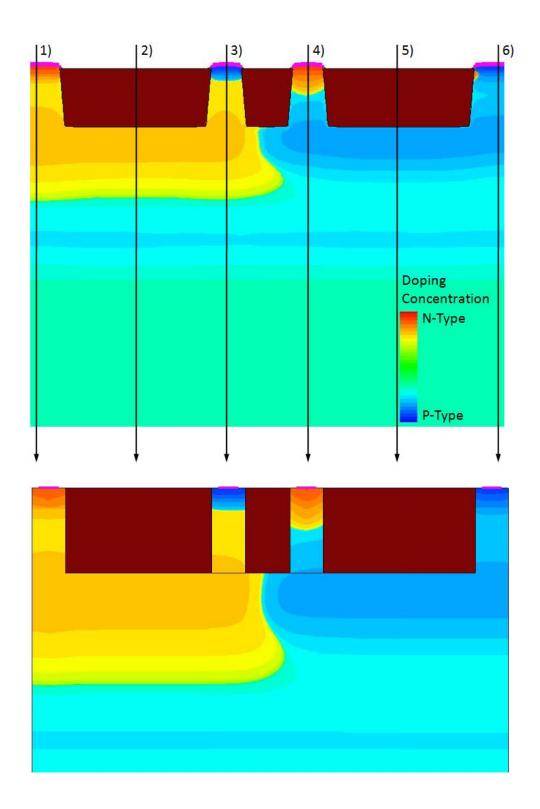

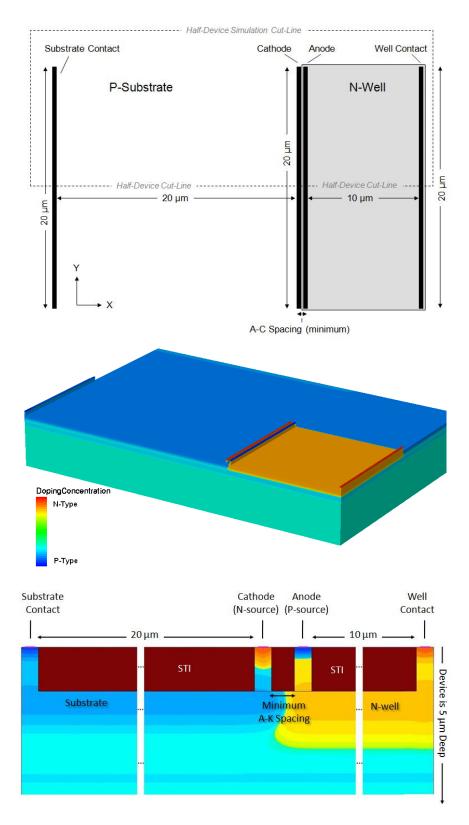

| Figure 4.1. (a) Original process output for SCR device showing doping cut lines used for profile extraction                      |

| 1) The N-Well Contact, 2) The middle of the N-Well, 3) The Anode, or P-Source, 4) The Cathode, or                                |

| N-Source, 5) The middle of the P-Well, and 6) Substrate Contact. (b) A TCAD device created using                                 |

|                                                                                                                                  |

| the doping profiles extracted from (a). The same X-Y scales and doping scales are used in both                                   |

| figures for comparison                                                                                                           |

| Figure. 4.2. (a) Layout for SCR device showing spacings and half-device cut line (b) 3D TCAD device                              |

| created from 4.1a using extracted doping profiles (c) Cross-section along half-device cut line. Lateral                          |

| breaks are included to show well and substrate contacts. 58                                                                      |

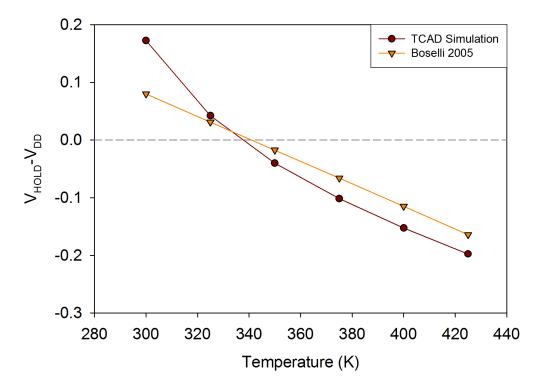

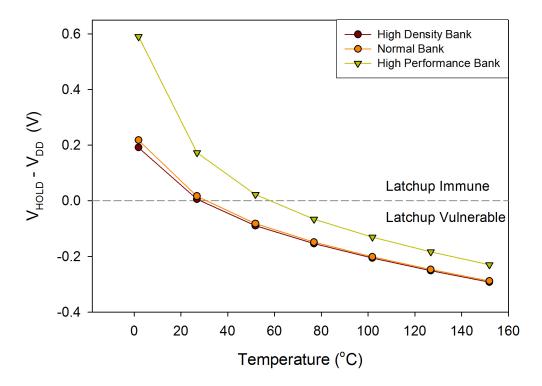

| Figure. 4.3. (a) $V_{HOLD} - V_{DD}$ comparison between TCAD 65 nm SCR model and experimental data from                          |

| [129]. $V_{HOLD} - V_{DD}$ for both TCAD and experimental work are plotted as a function of temperature. 59                      |

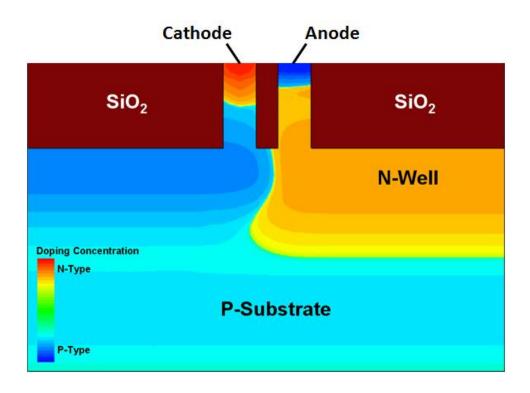

| Figure 5.1. Zoomed-in cross-section of active parts of the SCR structure from figure 5.2b. The cross-                            |

| section is taken in the Z direction on the half-device cut line to show the anode, cathode, and                                  |

| well/substrate junction                                                                                                          |

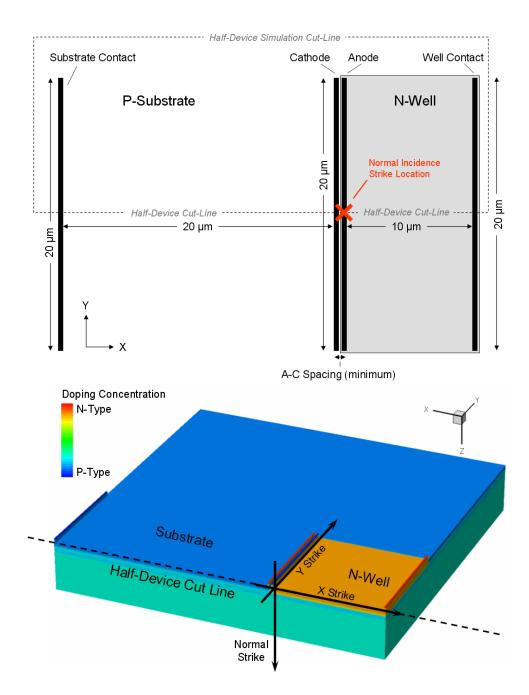

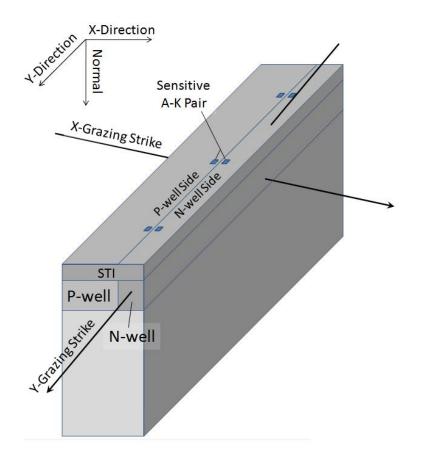

| Figure. 5.2. (a) Layout of physical 20 µm wide SCR structure in 65nm technology with a 10 µm long N-                             |

| well and 20 µm cathode-P-tap spacing. The cut-line for the TCAD device simulation in shown. (b)                                  |

| TCAD structure for simulations. Only half of the full device is simulated to save on memory and                                  |

| computation time. The cut line from figure 5.2(a) is noted in the figure. Strike orientations for SEL                            |

| TCAD simulations are indicated                                                                                                   |

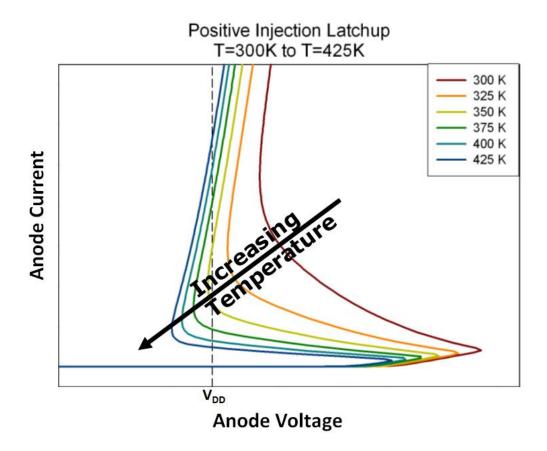

| Figure 5.3. Positive injection DC latchup curves showing a decrease in holding voltage with increasing                           |

| temperature. $V_{DD}$ is marked on the plot. Data is from simulation of the TI ESD TCAD device                                   |

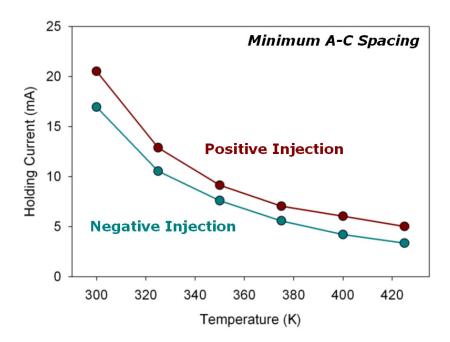

| Figure 5.4. Holding current vs. temperature for 65 nm NPNP device with minimum anode-cathode spacing:                            |

| Holding current can be seen to decrease with increasing temperature                                                              |

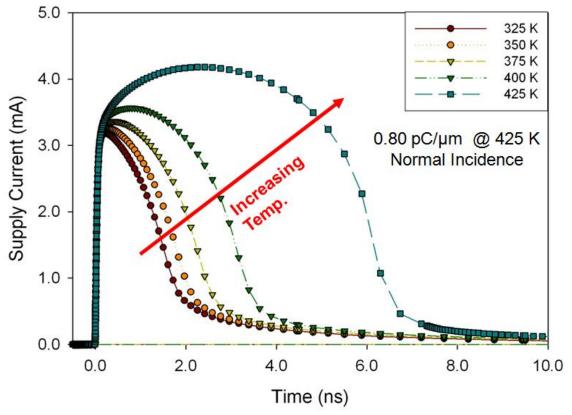

| Figure 5.5. Single event response current vs. time for varying temperatures at nominal operating voltage                         |

| (1.2  V). The current at the tied anode/N-well V <sub>DD</sub> rail is plotted                                                   |

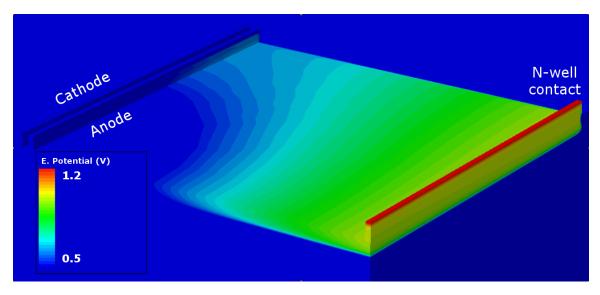

| Figure 5.6. Potential plot for 425K temperature pulse seen in figure 5.5 at t = 2.0 ns. In dark red is the                       |

| potential of the N-well contact. Dark blue is a 0.7 V potential difference (diode drop) from that                                |

| contact. About 6 $\mu$ m (out of 10 $\mu$ m) of the width of the device have the proper biasing for latchup. 68                  |

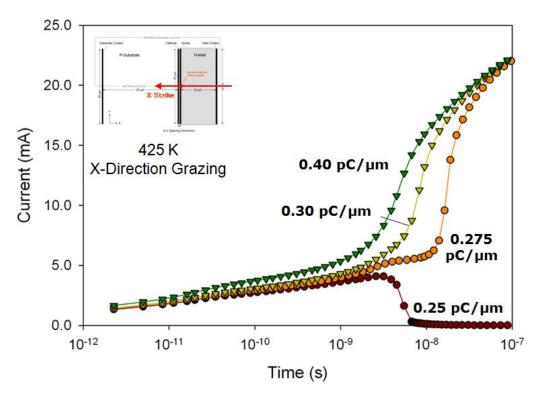

| Figure 5.7. Single event response current vs. time for varying temperatures at nominal operating voltage                         |

| (1.2  V) and 425K for varying charge density strikes at 90° grazing angle perpendicular to the anode                             |

| (X direction in figure 1b). The current at the tied anode/N-well contacts is plotted                                             |

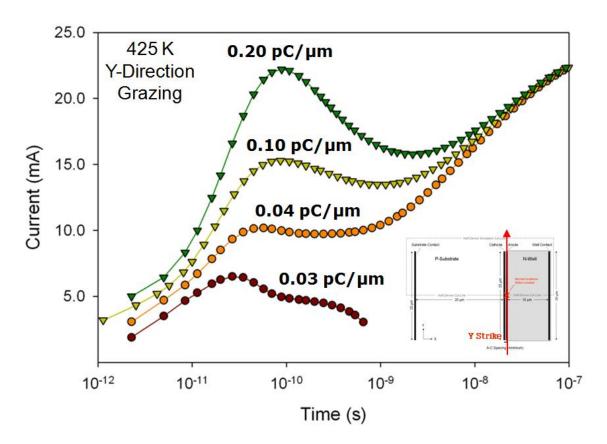

| Figure 5.8. Single event response current vs. time for varying temperatures at nominal operating voltage                         |

| (1.2  V) and 425K for varying charge density strikes at 90° grazing angle parallel to the anode (Y                               |

| direction in figure 1b). The current at the tied anode/N-well contacts is plotted                                                |

|                                                                                                                                  |

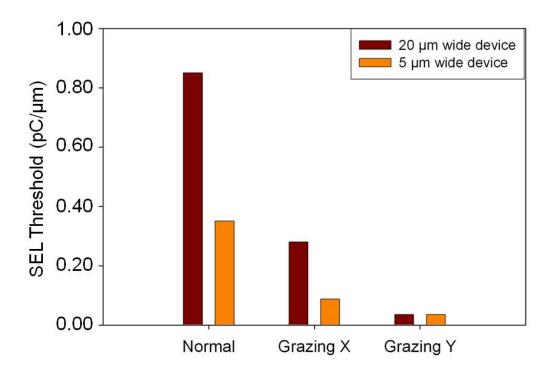

| Figure 5.9. Plot of threshold LETs for TCAD devices of different width. Both devices show a difference in |

|-----------------------------------------------------------------------------------------------------------|

| sensitivity between grazing angle strikes in different directions as well as a greater sensitivity        |

| between normal incident and grazing angle strikes. In both cases, strikes oriented along the N-well/P-    |

| substrate junction near the anode require minimum charge deposition for latchup                           |

|                                                                                                           |

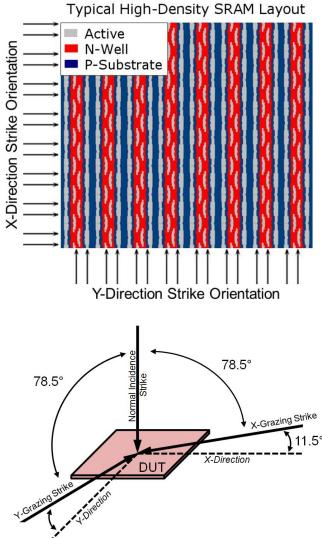

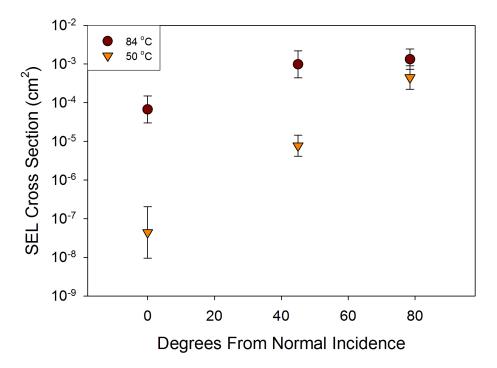

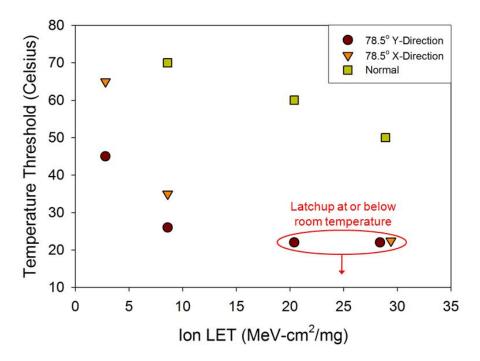

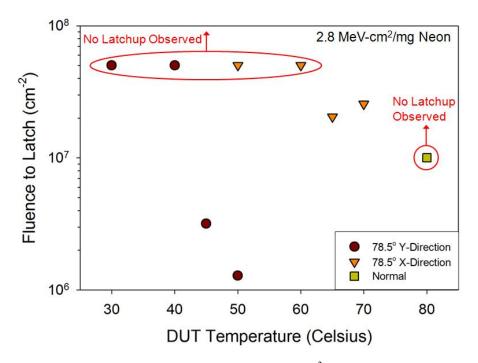

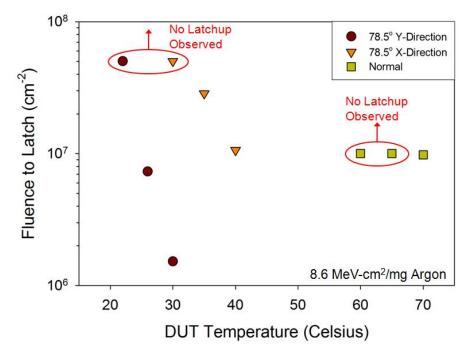

Figure 6.4. Fluence to SEL vs. die temperature for 2.8 MeV-cm<sup>2</sup>/mg Ne. Y-grazing beam orientation is shown to be significantly more susceptible to SEL.

84

Figure 6.5. Fluence to SEL vs. die temperature for 8.6 MeV-cm<sup>2</sup>/mg Ar. Y-grazing beam orientation is

# LIST OF TABLES

| TABLEPA                                                                                                            | GE |

|--------------------------------------------------------------------------------------------------------------------|----|

| Table 4.1. Comparison of Beta values at room temperature for the simulated TCAD device and results f         [129] |    |

| Table 6.1. Comparison of important properties for SEL characterization of SRAM 1-Mbit banks.                       |    |

| Parameters are normalized to the normal SRAM banks                                                                 | 78 |

| Table 6.2 List of ions and energies used for SEL testing at the Texas A&M Cyclotron Facility [150]                 |    |

Table 6.2. List of ions and energies used for SEL testing at the Texas A&M Cyclotron Facility [150].Energies and LETs are adjusted for the 52 mm air gap between the beam aperture and the DUT..... 80

#### CHAPTER I

## INTRODUCTION

One of the most important aspects in the study of radiation and its effects on microelectronic devices is the influence of device scaling on the error rates and vulnerability to phenomena such as single event latchup (SEL). In the space radiation environment, which includes the Earth's radiation belts, solar winds, and galactic cosmic rays, a satellite system needs to operate reliably with a manageable error rate that can be reduced through software or circuit-level correction techniques. Errors are caused by energetic particles passing through the semiconductor devices. Energy transferred by these particles results in generates charge in the form of electron-hole pairs. This charge creates extraneous current or voltage pulses in a circuit by changing electrostatic potentials and currents in devices. These pulses can cause errors by being falsely perceived as data by the circuit or by flipping the stored data value on a node. While it is preferable to have a process-hardened circuit for a spaceborne system that includes guard rings, extra well and substrate contacts, and buried doping layers or other layoutimplemented radiation hard by design (RHBD) techniques, commercial off the shelf (COTS) parts and commercial processes are becoming more appealing. Some of the reasons for this desirability include lower development cost, quick turnaround, and higher performance. Because of the desirability of using COTS devices in space systems, it is crucial that the effects of the radiation environment on these parts are understood and for experimental procedures to properly bound device response. As a benefit of understanding radiation effects on devices from contemporary technology nodes, insights can be gleaned with regards to dominant error mechanisms and error rates in future

technologies. Relatively few experimental or simulation results have been shown on devices from newer (65 nm and below) commercially available technology nodes [1-7].

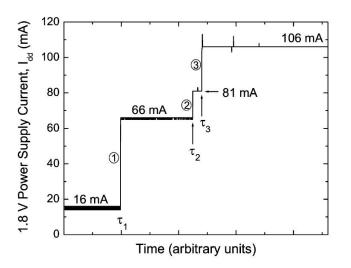

Specifically of concern in this work is the hazard of single event latchup in a radiation environment. Latchup generally occurs in a complementary metal oxide semiconductor device (CMOS) when deposited charge from a single event turns on one of the two parasitic bipolar transistors present in the CMOS structure. These two bipolar transistors are naturally in a feedback loop. If the gain of this loop is greater than unity, then a high-current latching state can occur that renders the affected devices inoperable and can cause a large increase in system power usage or permanent damage. Figure 1.1 shows an example of this effect occurring in an ASIC test chip. As different areas of the chip latch up, the current draw on the system power supply increases dramatically. In most circumstances a full system restart is used to alleviate this potentially damaging high current state.

Figure 1.1. Current draw on a 1.8V power supply for three subsequent latches in three different on-chip locations. The latchups are induced by a pulsed laser in sensitive areas of the device. It can be seen that the power draw for the device is 6x normal operating current [8].

Because of the vulnerability of microelectronics to ionizing radiation, it is imperative to test potential components for radiation environment applications. One way this is done at ground level is by operating the component in question under exposure to heavy ions or protons using an accelerator beam. For this type of single event effect (SEE) testing, the Joint Electronic Devices Engineering Council (JEDEC) test standard is typically followed [9]. This test method will be examined in Chapters VI and VII and the adequacy of the test standard for SEL will be discussed.

This work focuses on the SEL response of test devices fabricated in a commercial  $65 \text{ nm} (0.065 \ \mu\text{m})$  CMOS technology, particularly a silicon-controlled rectifier (SCR) and synchronous random access memory (SRAM) test devices. Available information for these parts includes layouts, doping profiles, and test memories as well as layout and experimental data. With experimental testing, knowledge of technology characteristics, and simulations, a thorough examination of SEL in this deep-submicron technology follows.

Latchup is simulated in both the large SCR test part and the SRAMs at the 65nm technology node. The SCRs help provide a baseline understanding for latchup in this technology through both simulations and experimental work. The 65 nm SRAMs are examined for latchup using heavy-ion testing.

Chapter II covers single event effects (SEE) and the space radiation environment. Chapter III covers the basic physics of SEL and the implications of scaling for that failure mechanism. Chapter IV covers the calibration of technology parameters for TCAD SEL simulations. Chapter V examines SEL through technology computer-aided design (TCAD) simulation of the large SCR test parts and discusses an angular orientation dependence of latchup that is unaccounted for by current test protocols. Chapter VI provides test results and analysis reinforcing the angular dependence theory from Chapter V using 65 nm SRAMS. Finally, Chapter VII summarizes the most important aspects of this work.

#### CHAPTER II

# THE SPACE RADIATION ENVIRONMENT AND SINGLE-EVENT EFFECTS

To understand the significance of this work, the reader needs a basic understanding of the space radiation environment and the effects that the highly energetic particles therein (protons, neutrons, alpha particles, heavy ions) can have on electronic circuits. There are many thorough guides on this topic and much of the information presented here is extracted from those sources [10-26]. Single-event effects (SEE) are the result of the aforementioned particles striking sensitive regions of microelectronic devices and/or sensitive nodes of a circuit. The effects of incident particles depend on strike location, angle of incidence, particle energy, particle species, and timing of the strike. Additionally, secondary particles can be created via nuclear reactions with a primary incident particle and the component materials of the microelectronic devices. These effects range from being non-observable to causing permanent physical and operational damage to the device. Of particular interest to this work is single-event latchup (SEL), but the basic physics of particle interaction with devices for all single event effects are similar. To begin, a brief introduction to the space radiation environment will be provided, followed by a detailed look at the physical mechanisms behind radiation-induced events.

#### The Space Radiation Environment

The constituents of the space radiation environment are geomagnetically trapped radiation, particles from solar events, and galactic cosmic radiation.

# Trapped Particles

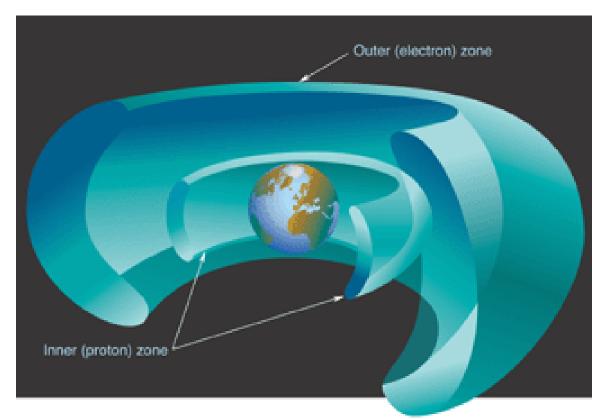

The earth's magnetic field can be approximated as a dipole field. The orientation of field lines around the earth allows particles entering the field to become trapped, creating radiation belts. The earth's radiation belts are referred to as the Van Allen radiation belts after Dr. James Van Allen, who oversaw the original Explorer missions in 1958.

Figure 2.1. Diagram of the Van Allen belts. Trapped protons are trapped closer to the earth while trapped electrons form the outer shell [17].

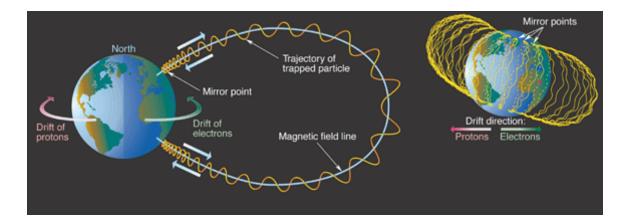

It is interesting to note that while passing through the areas of highest radiation particle density, the instruments on the early Explorer spacecrafts actually reported zero particle flux as they were overwhelmed by the radiation environment. The data taken by these spacecraft confirmed the existence of the radiation belts. Figure 2.1 is a depiction of these belts. Particles trapped in these belts include protons, alphas (hydrogen and helium nuclei), electrons, neutrons, and some heavier ions. These particles rotate around the field lines and reflect between the magnetic poles. In addition to bouncing between the poles, particles also drift around the planet with electrons moving to the east and protons (and other positively charged particles) moving to the west. This motion is depicted in figure 2.2.

Figure 2.2. Motion of trapped particles in the Earth's magnetosphere. Particles can be seen to spiral around the field lines as well as bouncing back and forth at the mirror points. Drift direction of particles is also shown [17, 20].

Because electrons do not contribute to SEE (they do contribute to total dose and charging effects), only the effects of protons and heavier ions will be considered here. For a thorough treatment of total dose effects, see [27-29].

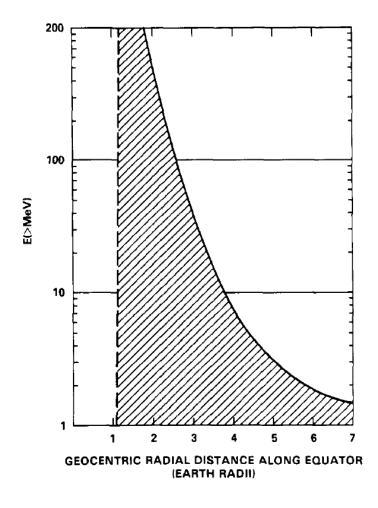

Of the particles of concern for SEEs, the most abundant are protons. This abundance also makes them the largest contributor for single-event upsets (SEUs), which are SEEs that cause a change in a data bit through charge deposition and collection processes. The region from about 1.15 Earth radii to about 2.4 Earth radii is the region

where the highest energy (and therefore of greatest concern) protons of > 30MeV energy are trapped. Protons with these energies easily penetrate spacecraft shielding and can affect the electronics within. Figure 2.3 shows the energy ranges of protons as a function of the distance from the planet's center in Earth radii.

Figure 2.3. Trapped proton energies as a function of distance from the Earth's core in Earth radii. Peak proton energy falls off with distance from the earth [20].

One of the characteristics of the geomagnetic field that is important for modeling the space radiation environment is the South Atlantic Anomaly (SAA). This is the result of the displacement of the center of Earth's magnetic field from its geographical center by about 280 miles as well as the displacement between the Earth's magnetic and geographic poles.

Figure 2.4. (a) The South Atlantic Anomaly. Proton flux can be seen to increase considerably at low altitudes in the South Atlantic. Flux is shown for powers of ten in  $cm^2/s$  for protons > 10MeV. After [24] (b) Contour plot of proton fluxes > 10 MeV in the SAA at a 500 km altitude during solar maximum. Flux is shown in units of  $cm^2/s$ . After [30].

This pole offset creates a depression in the magnetic field over the south Atlantic causing charged particles to be trapped at a lower altitude (< 1000 km) [12]. The result is a much higher flux of protons (~  $10^4 \times$  greater) for a spacecraft passing through the anomaly compared to other locations in the orbit. This has a profound effect on the operation of low Earth-orbit (LEO) satellites at inclinations affected by the anomaly. The International Space Station must also take these effects into account by using extra shielding. Figure 2.4 shows the geographic location of the SAA and the effect of the weaker electromagnetic field in the South Atlantic Ocean.

The Van Allen belts consist primarily of trapped protons and electrons. However, heavy ions can also be trapped in the geomagnetic field. These ions are believed to be the result of cosmic rays (neutral interstellar atoms) that become ionized and trapped. These ions have a similar distribution to trapped protons and like protons, have an increased presence in the SAA. Because of the fairly low energy of these ions, they are of less concern than the more plentiful and potentially more energetic trapped protons.

#### Transient Particles

Transient particles come from two sources, solar events and galactic cosmic rays. The frequency of significant solar events varies depending on the temporal location within the sun's activity cycle, which has been observed to be between 9 and 13 years. The difference in proton fluence between a "quiet" year and an "active" year can vary by as much as three orders of magnitude. Gradual solar events are events seen as a raised particle flux that slowly decreases over a period of several hours or days. These events can account for a large fluence of protons  $(10^9/cm^2)$  in a few days and have been correlated with coronal mass ejections (CMEs). Figure 2.5 plots major proton events for

three previous solar cycles. More abrupt impulsive events lasting a few hours are seen as large increases in the fluence of heavy ions.

Figure 2.5. Solar activity and solar proton events for cycles 19-21. Multiple events exceeding fluences of 109 protons over 10 MeV in energy are shown for each active sun cycle. The right Y-axis maps these events to the Zurich (or Wolf) Sunspot Number which gauges solar activity [31, 32].

Whereas solar events are responsible for the ebb and flow of particle flux seen by a spacecraft, galactic cosmic rays (GCRs) form the backdrop of the radiation environment. Because cosmic rays come from multiple sources outside of our solar system, they are more of a constant presence. The variance in the fluence of heavy ions due to galactic cosmic rays is much less dramatic than what is seen by proton fluence in a given year. The variance in GCRs that is observed is created by solar winds that serve to prevent some of the encroaching cosmic rays from entering our solar system. Thus, radiation received from GCRs is reduced during active periods in the solar cycle and increased during quiet periods. The particle composition of GCRs is shown in figure 2.6.

Figure 2.0. Flux of the different particles comprising galactic cosinic rays [10].

The vast majority of these particles are protons and alphas with about 1% of the particles being heavy ions. Although they compose such a small percentage of GCRs, these heavy ions are important because they can deposit large amounts of energy and are therefore very ionizing. Note that ions above the mass of iron have significantly reduced flux and are therefore of less concern when radiation hardening a system.

#### **Mechanisms for Single-Event Effects**

The single-event effects that are of concern for this work all are related to the same primary mechanism: collection of charge by the various transistor and circuit elements after an energetic particle passes through a device. The process of this charge deposition, collection, and transport in semiconductor devices will be covered in this section.

#### Charge Deposition

There are two basic ways that ionizing particles deposit charge in a device. The first is direct ionization from the primary incident particle and the second is ionization from secondary particles that are created via nuclear reactions of the primary particle and the atoms in the materials of the semiconductor device. When a charged particle passes through the semiconductor material, it deposits energy along its track until it loses all its energy and comes to rest inside the device or exits the device. This deposition of energy manifests itself as electron-hole pairs that are freed along the track of the charged particle by the deposited energy. The standard is to refer to this energy loss as a linear energy transfer (LET) along the route of the ionizing particle. The standard units of LET (and the ones that will be used in this work) are MeV-cm<sup>2</sup>/mg. This can be thought of as the energy deposited for unit length (MeV/cm) normalized by the density of the target material (mg/cm<sup>3</sup>). A convenient conversion for silicon technology is that an LET of 97 MeV-cm<sup>2</sup>/mg corresponds to charge deposition of 1pC/µm. This factor of ~100 makes for quick conversions between particle energy transfer and charge deposition.

### Direct and Indirect Ionization

To properly understand the interactions of a particular charged particle with electronic devices, the LET of the particle needs to be understood at various locations as the particle passes through the material of the device. Examples of these curves are shown for different ions in figure 2.7. The figure plots the instantaneous dE/dx of the four ions listed in table 7.2 in silicon in LET units of MeV-cm<sup>2</sup>/mg.

Figure 2.7. Plots of the four ion species listed in table 7.2 in Chapter VI on a silicon target. Instantaneous dE/dx is plotted in units of MeV-cm<sup>2</sup>/mg vs. depth into the silicon target [33].

These curves are obtained through computer codes created through the work of Ziegler *et al.* [33] and are referred to as the TRansport of Ions in Matter (TRIM) and Stopping and the Range of Ions in Matter (SRIM).

The direct ionization that would take place due to the energy transfer functions exhibited by the curves shown in figure 2.7 is primarily the domain for single event effects caused by the heavy ions that comprise GCRs. Heavy ions are typically defined as any ion with  $Z \ge 2$ . Particles lighter than this (such as protons) usually do not cause latchup by direct ionization as their LETs are incapable of producing sufficient charge to induce latchup in most devices. As devices continue to scale to smaller sizes and the critical charge of devices decreases, this may cease to be true. 10 MeV protons have a peak LET of ~0.5 MeV-cm<sup>2</sup>/mg at a range 30  $\mu$ m in silicon. Proton LET is around 0.05 MeV/-cm<sup>2</sup>/mg for the first 20  $\mu$ m of pathlength [33].

While lighter particles generally do not have a high enough LET to induce latchup in most devices, they still cause errors by depositing charge through indirect ionization mechanisms. For example, a high-energy proton can enter a semiconductor lattice and impact a nucleus in the semiconductor lattice. Two examples of possible resulting inelastic collisions from protons are shown in figure 2.8 [34]. Other examples of potential reactions can be found in [35, 36].

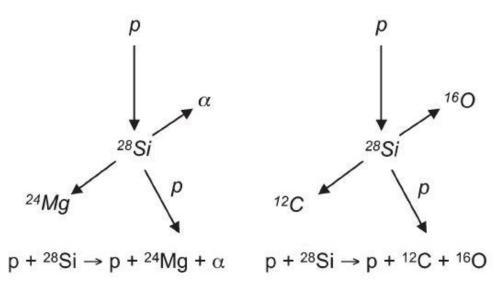

Figure 2.8. Examples of indirect ionization processes for protons in silicon [34].

The first example in figure 2.8a shows the emission of an alpha particle and a Mg nucleus recoil. Figure 2.8b shows one example of a spallation reaction where the impacted silicon nucleus is split into multiple fragments, in this case an oxygen ion recoil and a carbon ion recoil. Most of these products (the alpha and heavy ions) have much

higher LETs than the original incident proton and for purposes of charge deposition can often be thought of and modeled as the independent heavy ions would be.

#### Charge Transport and Collection

Once charge is deposited in the body of a device as electron-hole pairs, one of three things can occur. The charge can move along electric fields present in the device via drift mechanisms, it can move from areas of higher concentration to lower concentrations via diffusion mechanisms, or it can recombine with other available carriers in the device. This movement of charge in devices creates currents that are seen by the circuit. These currents can result in voltage pulses on circuit nodes (single-event transients, SETs) that are not intended by the circuit. If an erroneous voltage is present at the input to a memory element at the time data is latched, the faulty value will be propagated along the data path. For SEUs as well as SETs, the most sensitive regions are typically reverse-biased pn junctions. Due to the field placed across those junctions, these junctions are very efficient at collecting charge that is deposited in or near the depletion region. Ion strikes near depletion regions can also collect significant amounts of charge as carriers diffuse to the depletion region and are swept up and collected. For SEL, the issue is not so much the charge collected on a node as it is the current that is generated in a well or substrate. If this current is high enough to drop the potential underneath a source enough to turn a diode on, the part can latch. For SEL the most sensitive regions are typically N-well/Psubstrate junctions far away from well and substrate contacts and near source diffusions. More in-depth coverage of charge collection physics is given by Dodd [34]. This includes experimental methods like broad-beam charge collection spectroscopy [37] and measurement of charge-collection transients using ion microbeams or lasers with high

speed sampling oscilloscopes [38]. In other works, microbeams and lasers have been used to map integrated charge collection as a function of position in circuits [39, 40]. The physics of charge collection has also been studied in detail using 2-D and 3-D TCAD simulations [41, 42].

#### CHAPTER III

## LATCHUP IN CMOS DEVICES

Latchup in CMOS devices is a reliability concern for both terrestrial and space applications. Because the basic mechanisms for electrically-induced latchup (circuitlevel) and single event latchup are the same, electrical latchup will be considered first without the complication of ionizing radiation.

#### **Electrical Latchup**

In bulk CMOS, vulnerability to latchup is created by the presence of a parasitic silicon controlled rectifier (SCR) or thyristor between the power rails. This parasitic device is present whenever NMOS and PMOS transistors are placed next to each other in a circuit layout. When activated, this SCR structure creates a low impedance path across the power supply that can generate very high currents in the structure. These high currents can destroy metal interconnects due to electromigration, a phenomenon where the current passing through a metal line is so high that the metal atoms are displaced by current flow [43-47]. Even in the case of non-catastrophic failures, melting and electromigration from high current pulses have been shown to be a long-term reliability concern to circuit operation [48-52]. Figure 3.1 shows two examples of metallization lines in a circuit after the occurrence of latchup. Figure 3.1a is an example of a catastrophic failure where the circuit is destroyed by the failure of a metal interconnect due to high current from a latchup. Figure 3.1b shows a similar degradation of a metal line where the circuit remains functional after a latchup event, but may have reduced reliability and lifetime. The results from Miyahira et al. [49] shown in figure 3.1 should serve as a warning for the testing and qualification of parts for a radiation environment. Just because a device seems to survive several latchup events during testing does not mean that all latchup events will be non-destructive or that there is no permanent damage to the device.

Figure 3.1. (a) SEM photograph of metallization failure induced by latchup after the silicon nitride layer was removed. (b) SEM photo of a region damaged from current during latchup where the metallization line remains conductive even though metal has been ejected from over 90% of the conducting metal line. [49].

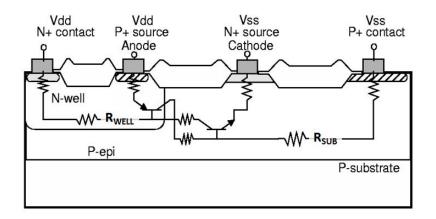

The parasitic SCR structure is formed by two bipolar junction transistors (BJTs). Both NPN and PNP bipolar devices are present as parasitic elements in a conventional CMOS structure. Because of the requirements for dense packing of paired transistors (NMOS and PMOS) in SRAM cells, latchup can figure prominently in those devices [48]. The electrically-induced turn-on of these parasitic devices can occur in vulnerable devices through device over-voltage or improper power supply sequencing. In a typical P-substrate CMOS technology, lateral NPN parasitic bipolar transistors are created by the N-source, P-substrate, and N-well configuration as well as the N-drain, P-substrate, and N-well configuration. Vertical PNP parasitic transistors are created by the P-source, Nwell, and P-substrate configuration as well as the P-drain, N-well, and P-substrate configuration. Because of the typical biasing conditions in a CMOS digital application, the parasitic transistors involving the PMOS and NMOS transistor drains are ignored. This simplification can be made for an SRAM since adjacent drains are always held at the same potential, creating a biasing situation where it is impossible for both the PNP and NPN parasitic bipolar transistors from being in forward active mode at the same time. This simplified latchup structure is shown in figure 3.2. During normal operating conditions, these parasitic transistors are both off. This PNPN (SCR) device created as a result of the configuration shown in figure 3.2 can be activated and switch from a high impedance state (low current) to a low impedance state (high current). In the SCR device, the PMOS transistor source is the anode and the NMOS source is the cathode.

Figure 3.2. Typical CMOS structure showing parasitic components and latch-up path. Well and substrate resistances are added for comparison to inset in figure 3.3. After [53].

An example of the operational curve with a simplified circuit schematic is shown in figure 3.3. This curve shape will change based on doping concentrations, applied voltages, the gains of the parasitic transistors, distances from anode/cathode to well/substrate contacts which modulate resistances, and temperature. The curve shown is for positive injection, with current being forced at the anode (PMOS transistor source) of the device. Point ( $V_{TR}$ ,  $I_{TR}$ ) is the transition between the high impedance region and the negative differential resistance region. These will be referred to as the trigger voltage and trigger current herein. In other literature, they are also referred to as the switching current and switching voltage.  $V_H$  and  $I_H$  are referred to as the holding voltage and holding current. ( $V_H$ ,  $I_H$ ) marks the point where the parasitic device transfers to the low impedance region (seen by the rapidly increasing current.)

Figure 3.3. Typical I-V characteristics for forward injection of a PNPN structure [54]. Inset: circuit layout of parasitic BJTs with well and substrate resistances from figure 3.2.

For the positive injection curve seen in figure 3.3, there are several distinct sections. At low currents and voltages, the vertical PNP transistor has not yet turned on. For the curve shown in figure 3.3, the N-well is at  $V_{DD}$  and the cathode and the substrate

(or P-well) contact are grounded. The anode voltage is increased from zero. Note that under normal device operation, the parasitic CMOS has the above operating conditions with the addition that the anode is also held at  $V_{DD}$ . This condition is noted in the inset of figure 3.3. When the voltage on the anode reaches a diode drop past the well voltage ( $V_{EB}$ of the PNP bipolar transistor approximately  $\geq 0.7$  V at room temperature) it becomes forward-biased. In the forward-biased condition, increasing anode voltage causes more current flow at the collector of the PNP bipolar transistor, which is the substrate of the device. As the substrate current increases, the voltage drop,  $V_{BE}$ , of the lateral NPN increases due to the current across  $R_{SUB}$ . When this reaches a diode-drop ( $V_{BE}$  of the NPN bipolar transistor approximately  $\geq 0.7$  V at room temperature), the lateral transistor is forward-biased and the SCR device enters a low impedance state seen by the rapid decrease in anode voltage. At this point, the device is in latchup and large increases in current can be seen with minimal increases in anode voltage. A similar curve exists for negative injection, which is the complement of the curve seen in figure 3.3. For negative injection, the lateral NPN bipolar transistor is turned on first followed by the activation of the vertical PNP bipolar transistor.

In order for sustain latchup in a circuit, several conditions must exist. First, the holding voltage for the parasitic structure must be below the supply voltage ( $V_{DD}$ ). If the operating voltage is below the holding voltage, it is not possible to sustain the low impedance latchup state even if the device is temporarily placed into that state by a fluctuation in voltage or current. There is only one solution for the current value of the SCR structure for  $V_{ANODE} < V_H$  in figure 3.3 and it lies in the high-impedance (normal operation) section of the curve noted as the forward-blocking region.

The second requirement is another circuit biasing condition. If the circuit is unable to supply a current of  $I_H$ , the parasitic device will not be able to enter the low impedance state. Thus, compliance limits for current are often set when operating devices where latchup is a concern. This often prevents the device from entering a latched state and prevents damage to interconnects from high currents.

Third, the total gain of the feedback loop created by the parasitic devices (shown as a circuit schematic inset in figure 3.3) has to be greater than one. This feedback is created by the fact that the base of each of the transistors is the collector of the other transistor.

$$\beta_{npn}\beta_{pnp} > 1 \tag{3.1}$$

If this product is below unity, any current due to a single event strike will die out instead of creating latch up. In addition to this, the currents in the N-well and substrate must be sufficient to create the voltage drops necessary to place the parasitic bipolar transistors into forward active mode. This creates the following (approximate) requirements for latchup at room temperature:

$$I_{WELL}R_{WELL} \ge 0.7 \,\mathrm{V} \tag{3.2}$$

and

$$I_{SUB}R_{SUB} \ge 0.7 \,\mathrm{V} \tag{3.3}$$

where  $R_{WELL}$  and  $R_{SUB}$  are the resistances seen between the well contact and the anode and the substrate contact and the cathode.  $I_{WELL}$  and  $I_{SUB}$  are the currents flowing through the well and substrate. Voldman [55] and others [56, 57] give a more stringent beta product requirement based upon the needed potential drops in Eq. 3.2 and 3.3. This is equation (3.4) seen below

$$\beta_{npn}\beta_{pnp} \ge \frac{I_{ANODE} + I_{SUB}\beta_{npn}}{I_{ANODE} - I_{WELL}\frac{\beta_{npn} + 1}{\beta_{npn}} - I_{SUB}}$$

(3.4)

where  $I_{ANODE}$  is the supply current. It is an important detail that many of these parameters are strongly related to device temperature. This will be discussed later in this chapter. Due to the aforementioned conditions for latchup, the layout, biasing conditions, and temperature are of the utmost importance in the determination of whether latchup can occur. These factors will be discussed in the section covering design concerns and current mitigation techniques for latchup.

#### Single Event Latchup

Ionizing particles can produce transient currents in analog and digital CMOS structures that can be amplified by parasitic devices inherent in the CMOS topology. This form of latchup is referred to as single-event latch-up (SEL) This phenomenon was observed as early as 1979 [58] and was originally considered in papers centered on examining the creation of latchup [59-61] and followed by those centered on explaining the effect through physics and modeling [48, 62, 63]. Other thorough reviews have covered SEL [48, 51, 54, 56-58, 64-88] and much of the information here is drawn from those discussions. SEL was initially observed only with heavy ions and bulk CMOS technology. Since then, it has been observed on epitaxial processes [65, 89], and has been

seen to be caused by both protons [66, 68, 70, 73, 76, 84, 90-92] and neutrons [80, 81, 86, 93] on newer technologies.

It should be noted that latchup and SEL do not occur in silicon-on-insulator (SOI) technology as the NMOS and PMOS transistors are isolated in separate volumes of silicon. SOI fabrication technology by its nature prevents the presence of the parasitic PNPN structure.

As mentioned previously, the triggering process for SEL is very similar to the process for electrical latchup. Johnston [54, 64, 76] and Troutman [48, 62] describe this as a four step progression. The process is initiated by a particle strike that deposits charge in the body or well of the SCR device. The diffusion or drift of this charge is current in the device. Current across the resistance in either the well and/or the substrate of the device creates a voltage drop between the base and emitter of one of the parasitic bipolar transistors. If this voltage drop is large enough to place one of the transistors into forward-active mode, additional current will flow into through the base of the other parasitic bipolar transistor (the collector of the forward-biased transistor). If this in turn causes a large enough voltage drop to place the other parasitic transistor into a forward-active state, the parasitic SCR device will go into latchup, granted it meets the previously stated conditions.

Specially designed structures can be used to test for latchup vulnerability, such as SCR devices that produce curves similar to figure 3.3. However, these types of tests cannot usually be performed on highly integrated parts to check for latchup. It is important to not the differences between electrically induced latchup and single event latchup. While the former is usually handled by preventing improper voltage sequencing

25

or large currents from ESD, these same techniques do not prevent extraneous charge from being placed directly into a latchup vulnerable device via ionizing radiation.

#### **Environmental Influences on Latchup Sensitivity**

When testing a CMOS device for use in a radiation environment, it is important to not overlook the unique issues that the target environment creates. In particular, the issues of concern here are the temperature extremes of the environment, the energies and types of particles the devices are exposed to in that environment, and the different directions from which the particles (or secondary particles from reactions) can intersect sensitive areas of the devices. An understanding of all of these issues is necessary to direct test procedures for qualification of parts. The general goals of single event testing are to (if possible) enable a prediction of device error/failure response in the chosen environment and to bound the response of the part in the environment with a worst case analysis. In this section, several test standards for single event effects are discussed and the factors influencing CMOS latchup sensitivity are covered.

## SEE Test Standards

There are several single-event effect test standards designed to account for the aforementioned environmental issues. These are JEDEC test standard JESD57 [9], ASTM standard F1192 [94], and ESA/SCC specification #25100 [95]. The JEDEC test standard JESD57 is only valid for heavy ions (Z > 2). The ESA/SCC 25100 is applicable for both heavy ions and protons testing. A summary of the main points of the JEDEC and ESA/SCC test standards similar to Poivey's [96] follows:

• Due to the limited penetration range of ions available at ground level, test devices must be de-lidded for heavy ion testing.

- The ESA/SCC test requires heavy ions with sufficient energy to have a particle range in silicon greater than 30 µm to insure ions can penetrate through the many overlayers in modern processes as well as to account for long collection lengths in some devices.

- Both test standards allow for testing at angle and the JEDEC standard requires an angle of at least 60° from normal incidence.

- Minimum fluence levels for heavy ions are 1x10<sup>6</sup> ions/cm<sup>2</sup> (ESA/ICC) or at least 100 events above threshold LET (JEDEC). For devices that are more radiation hard, fluence of 1x10<sup>7</sup> ions/cm<sup>2</sup> are recommended. For protons, the ESA/SCC standard recommends a fluence of up to 1x10<sup>10</sup> ions/cm<sup>2</sup> as well as commenting on the potential need for additional devices due to total dose effects.

- A minimum of 5 exposures (at different LET or proton energies) is required in order to get an accurate measurement of the cross section curve.

- The ESA/SCC standard calls for a sample size greater than 3.

- The ESA/SCC standard requires temperature to be strictly monitored while the JEDEC standard more specifically requires the device to be tested at temperatures covering the expected range of environmental temperatures.

For examining the sensitive cross section of a device with heavy ions or protons the test is typically performed similarly to the following: Initially, the ion or proton beam is oriented with the particles entering into the device perpendicular to the surface of the circuit (normal incidence) and at room temperature. As the test proceeds, the device under test (DUT) is oriented so that particles impinge on the surface at an increasingly grazing angle. The JEDEC test standard requires this angle be at least 60° from normal incidence. In addition to this, the JEDEC standard requires that this test is repeated for increasing temperatures, up to the maximum target environmental temperature. Both the angular and temperature components of the test are vital and must not be excluded when checking for SEL vulnerability. This work focuses on some of the shortcomings of these test standards and these issues are discussed in both Chapters V and VI.

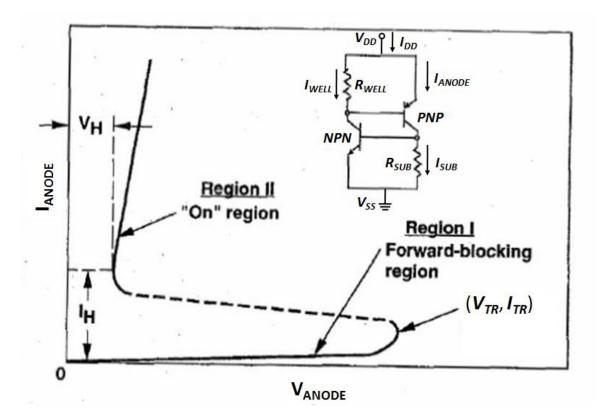

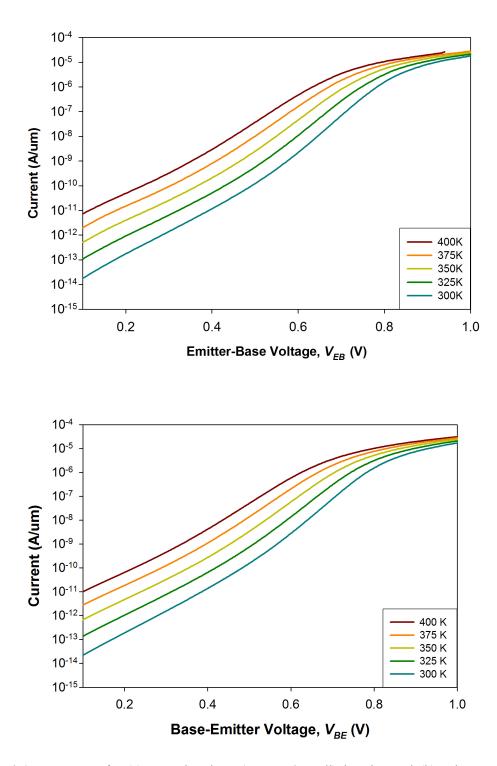

#### Effects of Temperature on Single Event Latchup

Researchers have shown that elevated temperatures and higher operating voltages cause higher sensitivity to SEL [54, 86, 87, 97-99]. The increase in well or substrate resistance reduces the current required to achieve a diode drop in the N-well or substrate and initiate the latchup process due to increased resistivity from thermal scattering (See equations 4.3 and 4.4). The resistivity in silicon scales as  $T^{3/2}$  within the operational temperature range for most silicon devices. In addition to this, increasing temperature reduces the voltage necessary to turn on the emitter-base junctions of the parasitic bipolar transistor. Figure 3.4a shows a 2D TCAD simulation of the diode formed by the Psource/N-well junction in an SCR device using the 65 nm technology examined in this work. Increasing the temperature generates more current at lower emitter-base voltage,  $V_{EB}$ . Similarly, figure 3.4b shows the diode formed by the P-substrate/N-source junction in the SCR device. Current is plotted vs. the base-emitter voltage,  $V_{BE}$ . Both plots in figure 3.4 indicate that the voltage drops required to turn on (place in forward-active mode) the parasitic bipolar transistors decrease with increasing temperature. The result of this is a decrease in the voltage between the anode and the cathode necessary (the holding voltage) to maintain latchup. The combination of: 1. increased current from an identical biasing condition (resulting in lower holding voltages) and 2. increased well and substrate resistances that lead to larger voltage drops for an identical single event combine to

significantly increase SEL vulnerability with increasing temperature. In many cases, the temperature environment will determine whether latchup is observed or not. Additionally, for a given temperature where a device is SEL vulnerable, increases in operating voltage  $(V_{DD})$  create a larger difference between the operating voltage and the holding voltage. Non-SEL-vulnerable devices at a given temperature can also become vulnerable to latchup by increasing the operating voltage above the holding voltage.

Figure 3.4. I-V curves for (a) an emitter-base (P-source/N-well) junction and (b) a base-emitter (N-source/P-well) junction in 65nm CMOS technology. Changing the environment temperature results in exponential changes in current, allowing the parasitic bipolar transistors to turn on at lower voltages.

Figure 3.5 shows these combined effects of temperature on SEL in the form of a SEL cross-section for a device. In this example, the change from room temperature to 125 °C results in an order of magnitude increase in SEL cross-section. Also, the threshold LET at which the part becomes vulnerable is halved. Reducing the threshold LET increases the range of ion LETs in the GCR spectrum that the part is vulnerable to (see figure 2.6). For a similar reason, the reduction in threshold LET can make the part more sensitive to the proton environment as it increases the range of LET from secondary particles from nuclear reactions that can latch the device (for example, the middle-left and middle-right of figure 3.10. More on this in the next section).

Figure 3.5. Temperature-dependence of SEL cross sections for heavy-ion tests. Cross-section increases and threshold LET decreases with increasing temperature. The cross section increases by more than an order of magnitude and the threshold LET is halved changing from room temperature to 125 °C [100].

## Effects of Particle Angle of Incidence on Single Event Latchup

When considering the effects of angle of incidence for testing with ionizing particles, it should be understood that in the space environment, the flux of particles will be approximately isotropic (sans shielding). The volumes of semiconductor material that are sensitive to upset via charge deposition and collection processes are determined by the circuit and individual transistor layouts of a device. In many cases, increasing the angle of incidence from normal (perpendicular to the surface of the device) of an ionizing particle increases the amount of charge that can interact or be collected by those devices. Several models for dealing with the effects of angle are described in this section.

During ion strike SEE testing, it is common practice to use angled ion strikes to mimic normally incident particles with a higher LET [101-103]. This practice is based on the concept of a thin and wide sensitive volume in a device. This model is used to create an *effective* LET during beam testing. Changing the angle at which a particle passes through the thin sensitive volume increases the path length through that volume, thus depositing more energy. This ratio is  $1/\cos(\theta)$  where  $\theta$  is the angle from normal incidence [101]. Example thin volumes and calculations of effective LET with changing path lengths due to angle are shown in figure 3.6. The path length of an ion through the thin sensitive region increases as  $L_{eff} = L/\cos\theta$  where  $L_{eff}$  is the pathlength of the ionizing particle through the sensitive volume, L is the thickness of the sensitive regions increases, so does the total energy deposited in the sensitive volume. The effective LET is similar with  $LET_{eff} = LET/\cos\theta$  where  $LET_{eff}$  is effective LET of the particle through the thin sensitive volume and, LET is the linear energy transfer of the particle in the material.

Figure 3.6. Demonstration of ion path lengths through shallow 1.0  $\mu$ m deep thin sensitive volume structures at varying angles of incidence. The increasing path length with increasing angle of incidence (and thus increasing energy deposition can be seen. The 60° incidence strike shown in (b) is twice as long as the normal incidence strike. The 75° incidence strike shown in (c) is almost four times as long as the normal incidence strike.

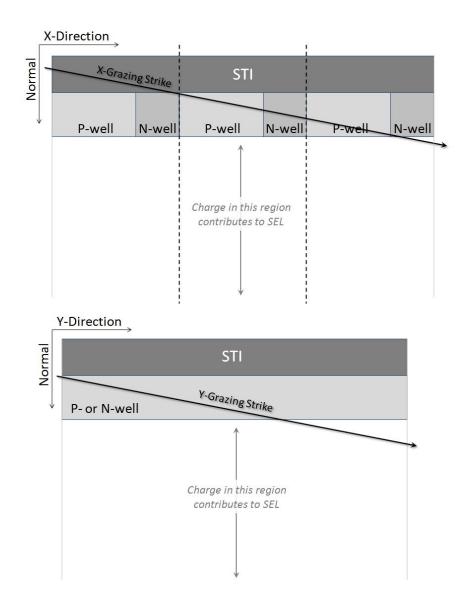

There are known shortcomings of the effective LET model [101, 104-109]. While this model accurately describes the change in charge deposition in the semiconductor material with variations in angle of incidence, many sensitive volumes are not thin or wide and flat when compared to their depth. The effective LET model cannot be used to model effects where there is 1) a difference in SEE sensitivity based on lateral orientation [110], 2) a device with a large collection depth relative to the lateral dimensions (often due to longer diffusion collection times for SEL [64]), or 3) geometry that constrains charge collection/interaction depending on lateral orientation, e.g., the sensitive volume is more box-shaped than flat [106]. All of these are true of the SRAM structures examined in this work.

A more flexible approach is to approximate sensitive volumes in devices using rectangular parallelepipeds (RPPs) of variable shape. The RPP model for a sensitive volume has been used to understand many single event phenomena in devices. These models approximate the response of a small number of sensitive devices in a circuit by using collection volumes in regions where devices are sensitive to errors from deposited charge. Models similar to this have been used extensively over the last 20 years [64, 104, 111-123] to explain the angular effects seen in sensitive device cross-sections. More advanced versions of these models often use multiple weighted volumes to model charge collection efficiency [124, 125]. The RPP model has also been used for SEL [91] and while a single sensitive volume approximation may be an oversimplified fit to existing data, the model gives a good understanding of how energy deposited in sensitive regions varies with angle of incidence.

Due to the fact that ionizing particles intersecting device structures at different angles can generate differing amounts of charge, it is important to consider the effects of beam orientation relative to a device under test (DUT). Without examining the effects of radiation from different angles, the sensitivity of the DUT can be under- or overestimated. Even the JEDEC and ESA/SCC test standards are often not thorough enough in this area of concern when determining SEL susceptibility. Whereas unexpected SEUs can often be dealt with through error detection and correction systems (EDAC), the destructive nature of SEL often means that even a single latchup cannot be tolerated by the system. Specifically, two vulnerabilities are present in these test regimens. First, assuming an isotropic environment, testing at only up to a  $60^{\circ}$  angle from normal incidence only covers 50% of the particles in the environment. This is demonstrated in figure 3.7. For a device that is located in the center of the sphere, ions incident at only up to  $60^{\circ}$  from normal incidence cover only the green portion of the sphere. Angles from  $60^{\circ}$  to  $90^{\circ}$  from normal incidence are in the red portion of the sphere and are unaccounted for when testing only the range of  $0^{\circ}$  to  $60^{\circ}$  from normal incidence.

Figure 3.7. Conceptual graphic of an isotropic environment and coverage by testing 60° from normal incidence. It can be seen that testing at only up to 60° from normal incidence only covers 50% of the solid angle from an isotropic environment. Effects from the top are similar to those entering from the bottom. After [126]. Variance along the azimuthal angle noted in the figure is also not considered by JEDEC test JESD57.

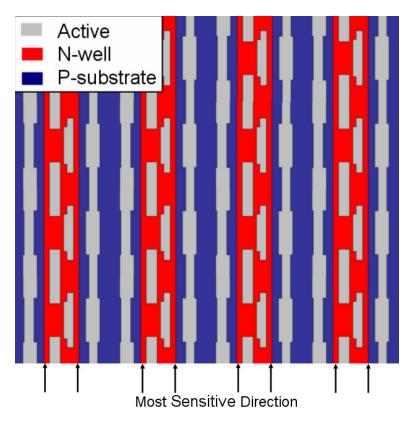

Second, the test standard assumes no variance in susceptibility with changes in the lateral orientation of the beam. More precisely, if the normal incidence is parallel to the Z direction in the device, the test standard does not account for rotation of the DUT in the XY plane. In polar coordinates, the only angle of rotation in the test standard is the polar angle and changes in the azimuth are not accounted for. This is noted in figure 3.7.

# Proton Induced Single Event Latchup

While an RPP method can be used for determining the energy deposition in sensitive volumes from heavy-ions, it alone is not sufficient for dealing with the effects of protons. Protons don't typically have a high enough LET to cause SEU or SEL by direct ionization. Instead protons cause upsets by creating secondary particles with higher LETs than that of the protons. Because of the involvement of the nuclear reaction, changing the angle at which protons intersect the device does not directly change the deposition path of the resulting secondary ions. More precisely, changing the angle of the protons does not uniquely define the direction of the secondary particles. In addition, because of the very short range of the secondary products (at least those capable of producing SELs or SEUs), the secondaries may not penetrate into the sensitive areas of the device and the angular effects for protons may be very different than those seen for heavy ions. The effects of angle for proton testing also may vary depending on the device type or technologies. Adams et al. observed a 5x increase in SEL cross section for 60 MeV (an energy where the secondaries are mostly forward directed in silicon, see figure 3.10) protons in a 64K memory when switching from a 0° to a 85° angle of incidence [66]. This result is shown in figure 3.8.

Figure 3.8. (a) 5x increase in SEL cross-section for a 64 K memory when going from normal incidence to grazing angle for 60 MeV protons [66].

Levinson et al. saw less than a 20% change between normal and grazing angles for both SEU and SEL [92] and Johnston predicted that in highly scaled devices, angular effects would be less than a factor of 2x for p-substrate devices due to the small sensitive volume sizes [76]. Recent work by Schwank et al. that covers SRAM technology nodes from 0.14  $\mu$ m to 0.35  $\mu$ m shows significant effects of both angle and temperature for protons. Other work by Schwank et al. [87, 127] demonstrated the need for testing at the maximum proton energies that would be seen in the given environment. An example of this is seen in figure 3.9. The cross section for two different SRAM parts is shown to change with increasing proton energies from normal incidence protons.

Figure 3.9. Latchup cross section of two memories vs. proton energy at normal incidence [127]

In both plots in figure 3.9, a dip can be seen in the cross section. This is likely due to the different scattering statistics with changes in proton energy. Work by Reed *et al.* [120] can be used to interpret these results. In that study, a different angular effect was seen depending on the energy of the protons. Figure 3.10 shows the result of simulations using the GEANT tool [128].

Figure 3.10. Simulated distribution of spallation recoil energy, LET, and range in silicon for 63- and 200-MeV protons [120].

The six panels in figure 3.10 are as follows: The left side if for 63-MeV protons and the right side is for 200-MeV protons. For each side, the top panel is the angular distribution of the energy of the recoiling nucleus (relative to the original proton trajectory). The middle panel shows the LET distribution of the recoil fragments (in Si) vs. recoil angle and the bottom two panels show the range or the recoil fragment in Si vs. the recoil angle. For both proton energies, the most energetic recoils (longest range, highest LET) are forward-directed and occur more frequently. Lower energy recoils tend to be more isotropic. For Reed's work, a higher upset cross section was seen at grazing angle for 63-MeV protons compared to 200-MeV protons. Schwank asserts [87, 127] that devices need to be tested at the highest proton energy seen in the application environment. While this is true, the work by Reed suggests that a range of proton energies that are seen in the environment should be examined in order to predict device response.

Two more plots are shown here that demonstrate both the impact of proton energy, temperature, and angle on latchup cross sections for SRAMs using modern technology. Figure 3.11 shows the latchup cross sections for a modern 0.16/0.14  $\mu$ m SRAM with varying proton energy and at two different temperatures. Changing from 25 °C to 85 °C results in roughly a factor of 10 increase in cross section. Many (if not most) modern ICs are within specification operating at 100 °C or above. Figure 3.12 shows the latchup cross sections for a modern 0.14  $\mu$ m SRAM with varying angle of incidence and at two different temperatures for 105 MeV protons.

Figure 3.11. Latchup cross section vs. proton energy for 0.16/0.14  $\mu$ m SRAMs measured at room temperature and 85 °C [87].

Figure 3.12. Latchup cross section for 105 MeV protons vs. angle of incidence for 0.14  $\mu$ m SRAMs measured at room temperature and 75 °C [86].

## **Effects of Scaling on Latchup**

Very little work has been reported in the literature describing the effects of scaling on single event latchup. In most cases, each study that has been undertaken only demonstrates the effects of latchup and the sensitivity (or lack thereof) on the current parts that are being studied. One work examined the sensitivity of parts with differing epitaxial thicknesses, which did cover several generations of technology [79]. These technologies are now obsolete and there is not a significant amount of insight that can be gained for current and future technologies. Because of the absence of any studies charting the effects of scaling, the general trends will be summarized here. To aid in these observations, Boselli's work on electrical latchup trends [129] and a recent study by Page and Benedetto on modern 1M and 4M SRAMS [130] will be relied upon.

Single-Event Latchup Susceptibility vs. Feature Size

Figure 3.13. SEL susceptibility vs. device feature size for commercial-off-the-shelf 1M and 4M SRAMS. BO indicates a part burn-out (non-recoverable damage) due to latchup [130].