# THE RADIATION RESPONSE AND LONG TERM RELIABILITY OF HIGH-K **GATE DIELECTRICS**

By

James Andrew Felix

Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements for

the degree of

DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

December, 2003

Nashville, Tennessee

Approved:

Professor Daniel Fleetwood

Professor Ronald Schrimpf

Professor Robert Weller

Professor Lloyd Massengill

Professor Sankaren Mahadevan

© Copyright by James Andrew Felix 2003

All Rights Reserved

### ACKNOWLEDGMENTS

There have been a lot of people who have the given the time, encouragement, knowledge, and advice that have made it possible for me to complete this work. First I would like to thank Anna who has always been supportive of me, especially for her understanding while I was gone for most of the past year completing this research. I owe a lot to my friends and colleagues Sandia National Laboratories especially Marty Shaneyfelt, Jim Schwank, Tim Meisenheimer, and Robert Fleming who gave me the opportunity to work with them and learn from them. A special thank you to Paul, Melanie, and Brian Dodd who were kind enough to open their home and allow me to be part of their family while I was in New Mexico. I would also like to thank my advisor Dan Fleetwood for it is he who encouraged me to stay at Vanderbilt and complete this doctoral research. I truly appreciate everything you have done for me, and it means a lot that you have always found the time to address my concerns and questions no matter how busy your are. I would like to thank Evgeni Gusev, Chris D'Emic and Joon Goo Hong for suppling me with devices, and Hao Xiong for experimental assistance. I am grateful to Ron Schrimpf, Bob Weller, Lloyd Massengill and Sankaren Mahadevan for their advice and input to this thesis. I have enjoyed working with and getting to know each of you. Finally, I would like to acknowledge my friends in the Radiation Effects and Reliability Group, especially Ms. Connie Nichols and Ms. Mandy Conley.

# TABLE OF CONTENTS

|      |                                                                                                                                                                              | Page                             |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| ACK  | NOWLEDGMENTS                                                                                                                                                                 | . iii                            |

| LIST | OF FIGURES                                                                                                                                                                   | . v                              |

| Chap | oter                                                                                                                                                                         |                                  |

| I.   | INTRODUCTION                                                                                                                                                                 | . 1                              |

| II.  | EFFECTS OF RADIATION                                                                                                                                                         | . 5                              |

|      | Total Dose Radiation Effects Oxide Traps Interface Traps Border Traps Single-Event Effects Radiation-induced hard breakdown Radiation-induced soft breakdown Nitrided Oxides | . 6<br>. 8<br>. 9<br>. 9<br>. 10 |

| III. | ALUMINUM OXIDE DIELECTRICS                                                                                                                                                   | . 15                             |

|      | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                         | . 17<br>. 19<br>. 23             |

| IV.  | HAFNIUM-BASED DIELECTRICS                                                                                                                                                    | . 32                             |

|      | Radiation Response                                                                                                                                                           |                                  |

| V.   | CHARGE-TRAPPING EFFICIENCY                                                                                                                                                   | . 38                             |

| VI.  | RELIABILITY                                                                                                                                                                  | . 43                             |

|      | Effects of Baking                                                                                                                                                            | . 45                             |

| VII. | SUMMARY AND CONCLUSIONS                                                                                                                                                      | . 51                             |

| REFI | ERENCES                                                                                                                                                                      | . 54                             |

# LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                                                                                           | Page  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1.     | Energy band diagram showing ionizing radiation creating electron-hole pairs in the $SiO_2$ layer of a MOS capacitor under positive gate bias. After [39]                                                                                                                                                                                  | . 6   |

| 2.     | The dependence of the threshold-voltage shift due to a) oxide-trap and b) interface-trap charge on oxide thickness. After [45]                                                                                                                                                                                                            | . 7   |

| 3.     | Schematic diagram of an $E'_{\gamma}$ center, showing the characteristic strained Si-Si bond precursor state and the charged EPR active state. After [51]                                                                                                                                                                                 | . 8   |

| 4.     | Gate voltage to breakdown versus physical film thickness for several different alternate high- $\kappa$ dielectrics and ultra-thin SiO <sub>2</sub> gates. The capacitors were exposed to 342-MeV gold ions. After [78]                                                                                                                   | . 11  |

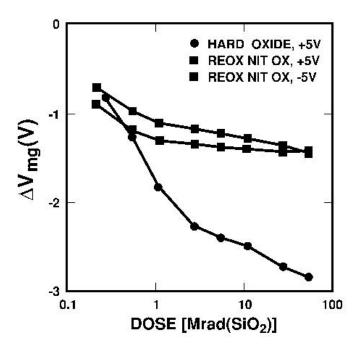

| 5.     | The change in midgap voltage measured on 37 nm RNO and thermal oxide transistors versus dose. The midgap voltage shift corresponds to the threshold-voltage shift due to oxide-trapped charge. After [103]                                                                                                                                | . 13  |

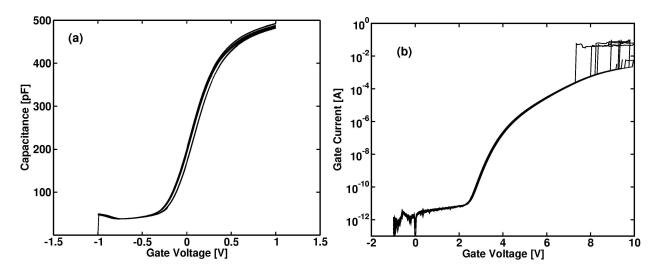

| 6.     | Pre-irradiation (a) $CV$ and (b) breakdown characteristics for 0.011 cm <sup>2</sup> devices with 10 nm $Al_2O_3$ on 2.5 nm $SiO_xN_y$ which received a FGA after $Al_2O_3$ ALD. The corresponding EOT of these samples is $\sim 7.4$ nm                                                                                                  | . 16  |

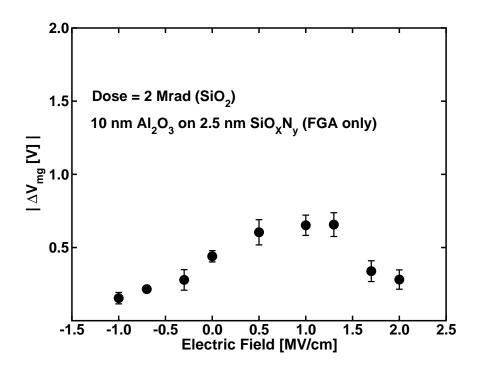

| 7.     | Absolute value of $\Delta V_{mg}$ versus electric field for $\mathrm{Al_2O_3/SiO_xN_y}$ capacitors irradiated to 2 Mrad(SiO <sub>2</sub> ). These devices were processed with a FGA only after $\mathrm{Al_2O_3}$ ALD. The data points represent the average of at least four devices and the error bars represent the standard deviation | . 18  |

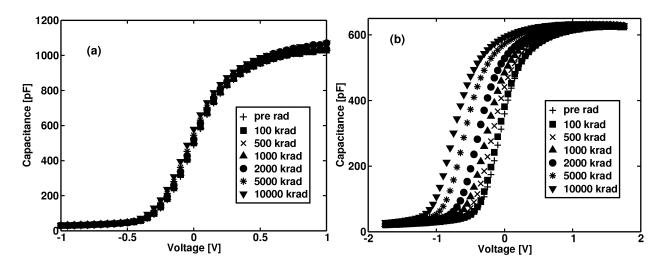

| 8.     | Pre and post irradiation 1 MHz $CV$ measurements on 0.0011 cm <sup>-2</sup> capacitors that received a FGA after $Al_2O_3$ deposition, with an EOT of (a) 3.4 nm and (b) 6.2 nm, irradiated to total doses from 100 up to 10,000 krad(SiO <sub>2</sub> ) at an electric field of +1.0 MV/cm                                               | n. 19 |

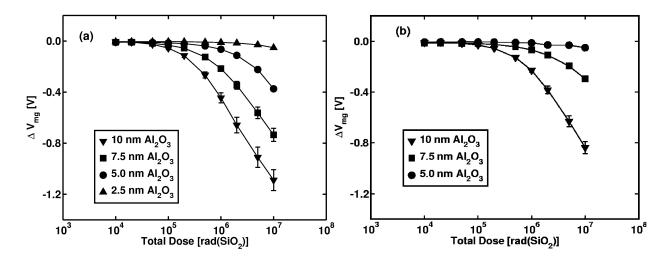

| 9.     | A complete summary of midgap voltage shifts as a function of total dose for exposures from $10  \mathrm{krad}(\mathrm{SiO}_2)$ to $10{,}000  \mathrm{krad}(\mathrm{SiO}_2)$ for devices with (a) a $2.5  \mathrm{nm}$ and (b) a $1.1  \mathrm{nm}$ interfacial oxynitride                                                                 | . 20  |

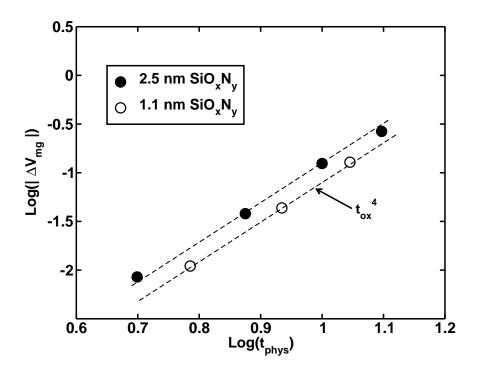

| 10.    | Logarithm of the absolute value of $\Delta V_{mg}$ data from Fig. 9a (filled symbols) and Fig. 9b (open symbols) versus the logarithm of the physical thickness of the films. These 500 krad(SiO <sub>2</sub> ) data are well correlated to a linear regression model (dashed lines) that shows a $t_{ox}^4$ thickness dependence         | . 21  |

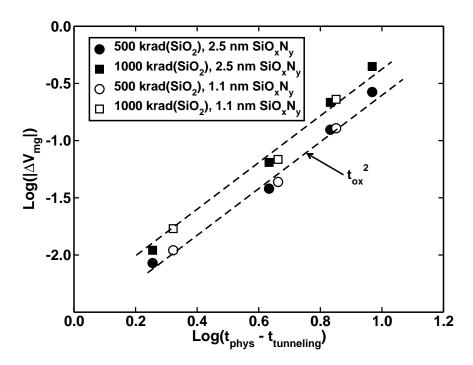

| 11.    | The data of Fig. 10, as well as 1000 krad(SiO <sub>2</sub> ) data, plotted with the effects of tunneling taken into account. The data for both the 2.5 nm (solid symbols) and 1.1 nm (open symbols) are well correlated to a linear regression model (dashed lines) showing a $t_{ox}^2$ thickness dependence                             | . 22  |

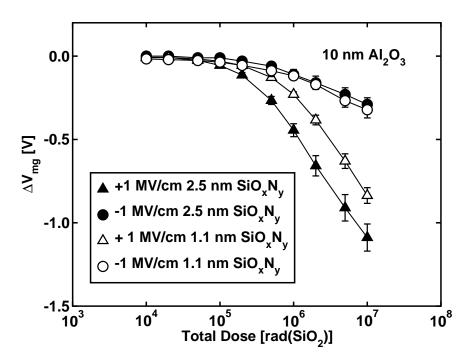

| 12.    | Midgap voltage shift versus total dose for 10 nm $\rm Al_2O_3$ devices with 2.5 and 1.1 nm interfacial oxynitrides irradiated at $+1.0~\rm MV/cm$ (triangles) and $-1.0~\rm MV/cm$ (circles)                                                                                                                                              | . 23  |

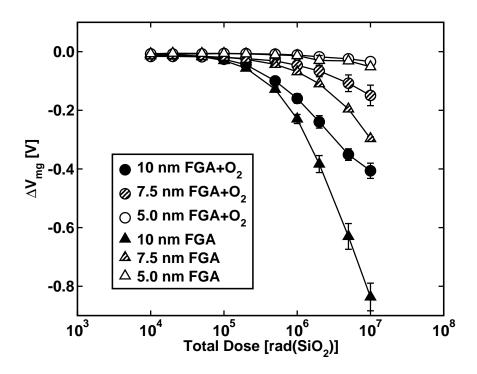

| 13. | Midgap voltage shift versus dose for 6.3 nm (solid symbols), 5.2 nm (striped symbols), and 4.0 nm (open symbols) EOT devices annealed with either a FGA or an $O_2$ anneal and a FGA after $Al_2O_3$ ALD                                                                                                                                        | 24                     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

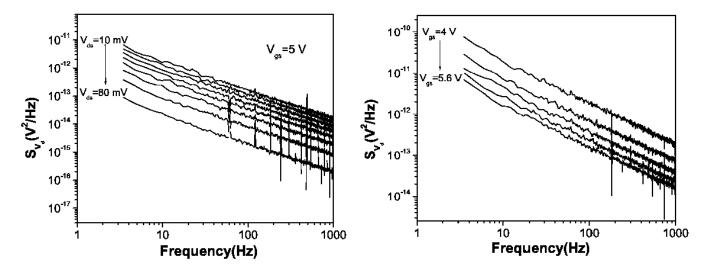

| 14. | Pre-irradiation noise power spectral density for a 2 $\mu$ m $\times$ 20 $\mu$ m transistor for (a) several values of $V_{ds}$ at a constant $V_{gs}$ of 5 V as well as for (b) several values of $V_{gs}$ for a constant $V_{ds}$ of 100 mV. The spikes are the result of 60-Hz pickup and are ignored in the fitting and analysis of the data | 26                     |

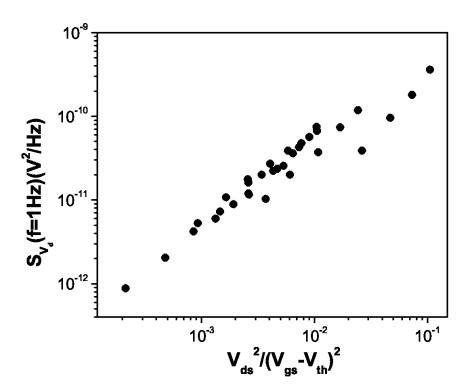

| 15. | Log-log plot of the noise power spectral density versus $V_{ds}^2/(V_{gs}-V_{th})^2$ for the data of Fig. 14                                                                                                                                                                                                                                    |                        |

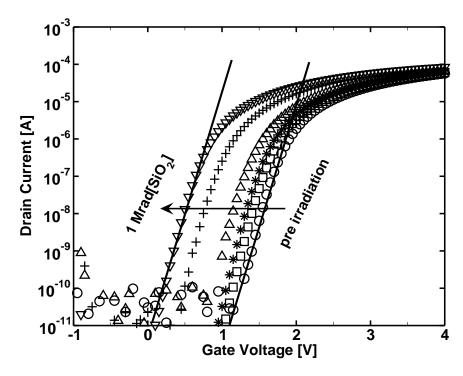

| 16. | Subthreshold $IV$ data for a 100 $\mu$ m x 100 $\mu$ m Al <sub>2</sub> O <sub>3</sub> /SiO <sub>x</sub> N <sub>y</sub> transistor irradiated at +1 MV/cm from 10 krad(SiO <sub>2</sub> ) to 1 Mrad(SiO <sub>2</sub> ). The transistors examined here received a 1000 °C dopant activation anneal and two FGAs                                   |                        |

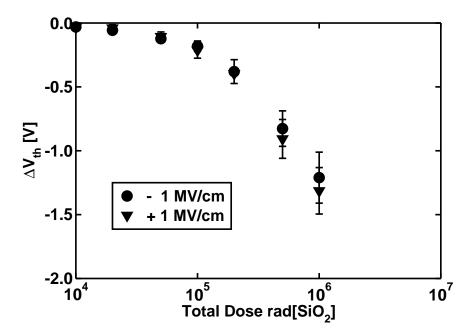

| 17. | Summary of $\Delta V_{th}$ for 100 $\mu m$ x 100 $\mu m$ nMOSFETs after irradiation with 10-keV X-rays for both positive and negative bias conditions                                                                                                                                                                                           | 28                     |

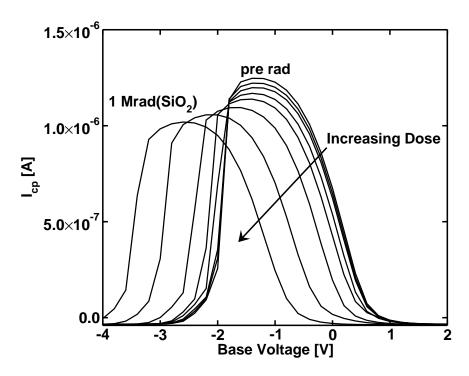

| 18. | $CP$ characteristics of a $Al_2O_3/SiO_xN_y$ transistor irradiated at $+1$ MV/cm from $10$ krad(SiO $1$ Mrad(SiO $2$ )                                                                                                                                                                                                                          | O <sub>2</sub> )<br>29 |

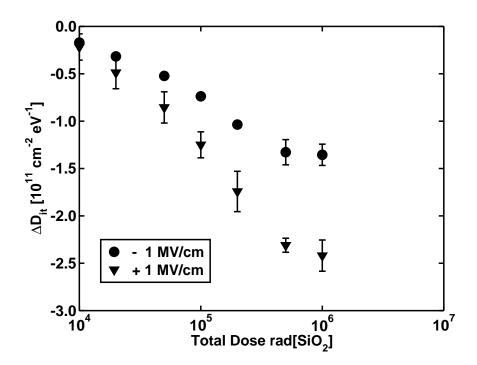

| 19. | Interface trap density as a function of dose for both positive and negative bias irradiations                                                                                                                                                                                                                                                   | 30                     |

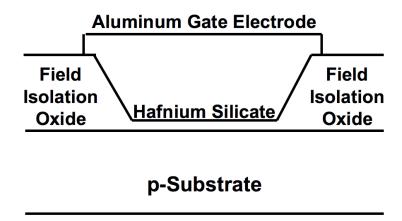

| 20. | Schematic diagram showing the cross section of the hafnium silicate devices                                                                                                                                                                                                                                                                     | 32                     |

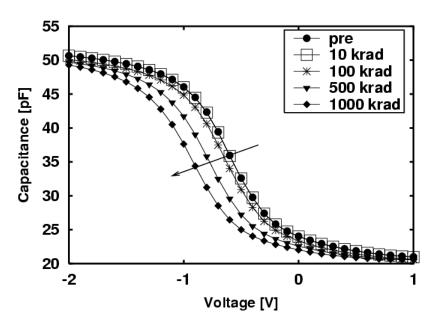

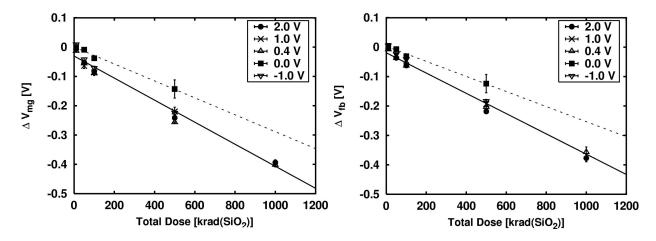

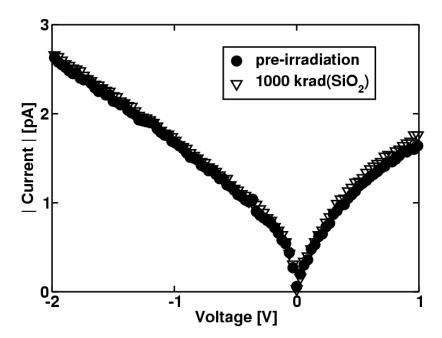

| 21. | Pre and post irradiation 1 MHz $CV$ measurements on a $1 \times 10^{-4}$ cm <sup>2</sup> hafnium silicate capacitor with an EOT of $\sim 4.5$ nm, irradiated to total doses of 10, 100, 500 and 1000 krad(SiO <sub>2</sub> ) at 2 V                                                                                                             | 33                     |

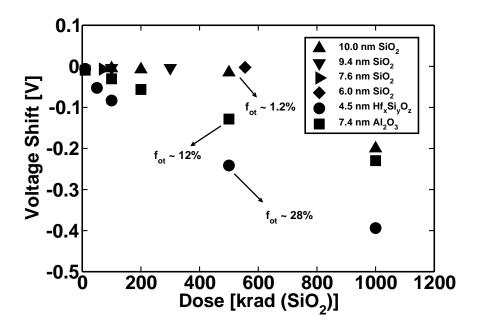

| 22. | A summary of a) midgap voltage shifts and b) flatband voltage shifts for total dose irradiations at biases of -1 V, 0 V, 0.4 V, 1 V, and 2 V for hafnium silicate capacitors with 4.5 nm EOT insulators                                                                                                                                         | 34                     |

| 23. | Absolute value of leakage current as a function of gate voltage during current-voltage measurements of the devices of Fig. 21                                                                                                                                                                                                                   | 35                     |

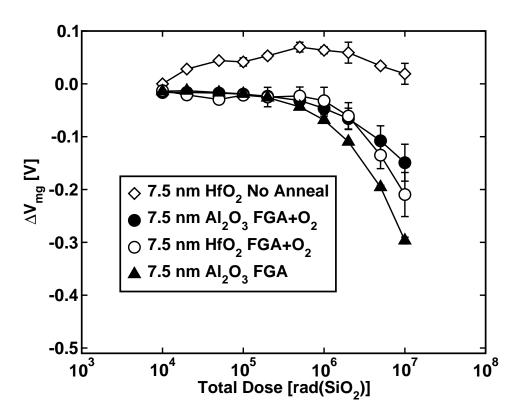

| 24. | Midgap voltage shift versus dose for $7.5$ nm $HfO_2$ and $Al_2O_3$ ALD deposited on a $1.1$ nm oxynitride for several annealing conditions                                                                                                                                                                                                     | 37                     |

| 25. | An energy band diagram for nitride-oxide MOS gate stacks during irradiation with positive bias on the gate electrode. After [145]                                                                                                                                                                                                               |                        |

| 26. | Voltage shift versus dose for several ultra thin thermal oxides and high- $\kappa$ dielectrics. For similar electrical thicknesses, the intrinsic quality of the thermal oxides is much better than the high- $\kappa$ films                                                                                                                    |                        |

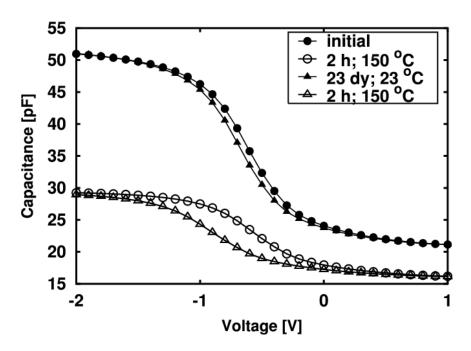

| 27. | Capacitance-voltage curves for $1x10^{-4}$ cm <sup>2</sup> capacitors with 4.5 nm EOT, which were baked in room ambient at 150 °C for 2 hours without bias, annealed in room ambient at $\sim 23$ °C for 23 days, then baked again at 150 °C for an additional 2 hours                                                                          | 43                     |

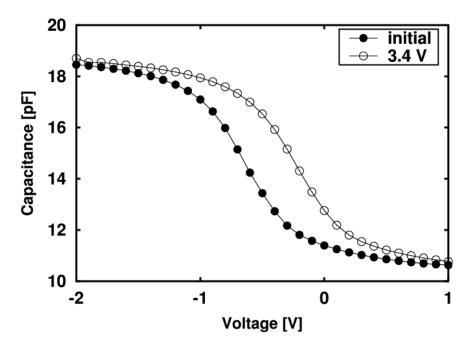

| 28. | Capacitance-voltage curves for $2.5 \times 10^{-5}$ cm <sup>2</sup> capacitors with 4.5 nm EOT showing the changes observed due to a physical electric field of $\sim 1$ MV/cm applied for $\sim 15$               |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | minutes                                                                                                                                                                                                            | 46 |

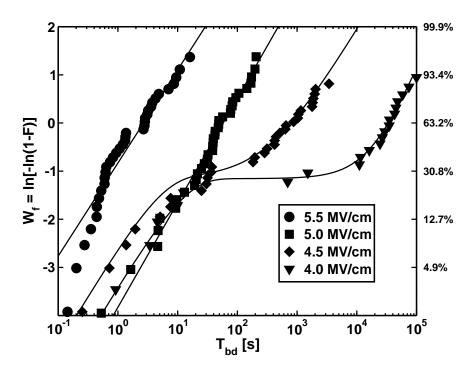

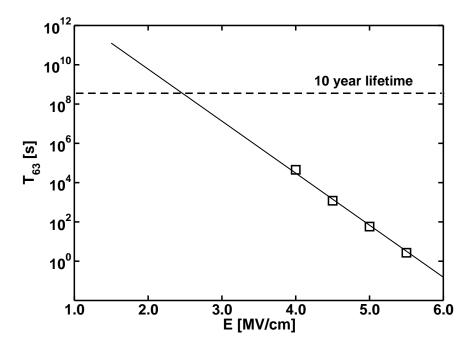

| 29. | Time dependent dielectric breakdown test results for 7.5 nm aluminum oxide gate dielectrics deposited on a 1.1 nm interfacial oxynitride. The devices were stressed at electric fields from 4 MV/cm to $5.5$ MV/cm | 48 |

| 30. | Lifetime extrapolation versus electric field based on the $T_{63}$ data from the TDDB failure distribution of Fig. 29                                                                                              | 49 |

## CHAPTER I

### INTRODUCTION

Space systems rely on advanced microelectronic devices to perform functions including communication, control, imaging, and power conversion. While in space, the electronics are exposed to various forms of radiation, including electrons, protons, neutrons, and heavy ions. The radiation may produce effects in the electronics ranging from temporary loss of data to catastrophic failure. Device failure can occur because of long-term degradation caused by continuous exposure to the space-radiation environment (total dose effects) or as a result of transient, high energy particle radiation (single event effects). The specific effects produced depend strongly on the specific technology and the radiation environment. Most space systems are designed conservatively using electronic parts that are at least several generations behind the current state of the art. However, the demand for higher performance and reduced time from design to flight has increased the pressure to use advanced technologies in space. The effects of radiation in some advanced technologies are poorly understood, or in some cases, completely unknown. At present it is not clear that it will be possible to use some advanced technologies in space, no matter how impressive the performance they promise. In addition, highly scaled devices may be sensitive to the naturally occurring radiation at the earth's surface, even though the atmosphere provides significant protection.

Scaling has enabled IC manufactures to increase production exponentially, while decreasing cost at nearly the same rate [1]. For the past  $\sim 30$  years devices have been scaled such that performance doubled as the cost was cut in half every 2-5 years, resulting in a four order of magnitude increase in processor speed and throughput since 1970 [1,2]. However, modern complementary metal oxide semiconductor (CMOS) devices are rapidly approaching the intrinsic physical scaling limit for Si/SiO<sub>2</sub>. Therefore, to keep pace with Moore's Law, which says the number of transistors on a chip should double every two year, IC manufactures are considering new materials for devices in the near future. The current practice in the semiconductor industry is to manufacture devices with SiO<sub>2</sub> or nitrided SiO<sub>2</sub> gate oxides that are only a few monolayers thick [3,4]. For example, Intel's transistors for the upcoming 90 nm technology node are projected to have 50 nm gate lengths and 1.2 nm gate oxides [5–7], corresponding to only about 4 mono-layers of SiO<sub>2</sub>. If one assumes that two of these layers are actually suboxide interfacial layers at the substrate and the gate, there are really only two atomic layers of stoichiometric "SiO<sub>2</sub>" in these transistors. According to Dennard's

constant field scaling method, the operating voltages should be scaled in conjunction with the device dimensions [8, 9]. However, in practice, device operating voltages have been scaled less aggressively than the device dimensions. Hence, devices with ultra-thin oxides operate at rather large electric fields [10,11]. This has raised concerns about the long-term reliability of devices with highly scaled gate oxides. Furthermore, devices with oxides thinner than  $\sim 4\text{-}5$  nm also exhibit large off-state leakage currents (i.e., 1 to 10 A/cm<sup>2</sup>) since carriers are able to tunnel directly between the substrate and gate electrode [12–14]. This a significant concern for space systems and mobile electronics where power conservation is essential. To reconcile the need for reduced off-state leakage currents in highly scaled devices, several high dielectric constant (high- $\kappa$ ) alternative gate dielectrics to SiO<sub>2</sub> are being investigated for incorporation into future ICs [14–23].

Finding a material to replace silicon dioxide is a formidable challenge because SiO<sub>2</sub> is a nearly perfect gate dielectric. Some of the most notable properties of silicon dioxide, which will likely be difficult to match with alternative gate dielectric materials are: (1) it is amorphous and remains thermodynamically stable on Si to temperatures exceeding 1100 °C, (2) it has a wide band gap (9 eV) with large (> 2.5 eV) conduction and valence band offsets for Si, (3) it is nearly insoluble in water, (4) it has a high breakdown strength (ultra-thin oxides can maintain electric fields of up to  $\sim 15$  MV/cm), and (5) it can be processed with low ( $\sim 10^{10}$ ) densities of bulk and interfacial defects. Indeed, the only notable drawback to SiO<sub>2</sub> is that it has a relatively low dielectric constant (3.9). Some of the high- $\kappa$  materials being considered for integration into future IC technologies are  $Al_2O_3$ ,  $HfO_2$ ,  $ZrO_2$ ,  $Y_2O_3$ ,  $TiO_2$ , and  $Ta_2O_5$  and/or the silicates and aluminates of some of these materials [13–15, 17, 22, 24, 25]. Each of these materials has advantages and disadvantages, but none of them are currently at the material quality level of SiO<sub>2</sub>. Still, all of these alternative gate dielectrics have a larger dielectric constant than SiO<sub>2</sub>. Therefore it is possible to manufacture a gate stack that is physically thicker, yet electrostatically shows a capacitance that is similar to an ultra-thin SiO<sub>2</sub> layer. The increased physical thickness significantly reduces the probability of tunneling across the insulator, and therefore reduces the amount of off-state leakage current [14, 15, 17, 19–21, 24, 26, 27]. However, an increased dielectric constant comes at the expense of a smaller band gap and smaller conduction and valence band offsets between the substrate and the gate dielectric [14, 17, 28]. With the exception of  $Al_2O_3$ , most high- $\kappa$  materials have a conduction band offset of only  $\sim 1.5-2$  eV [29, 30]. Because leakage current increases exponentially with decreasing film thickness and barrier height [31,32], this trade-off between dielectric constant and barrier height will limit the relative advantages an alternative dielectric offers in terms of reduced leakage current compared to devices with standard thermal gate oxides. Still, the initial data in the literature are promising, and most high- $\kappa$  gate dielectrics exhibit  $\sim 5$  orders of magnitude less leakage current than electrically equivalent SiO<sub>2</sub> [17, 20, 23, 26].

An alternative gate dielectric ideally needs to be integrated into standard CMOS processes without major restructuring of the process flow. Many high- $\kappa$  gate dielectrics have exhibited encouraging electrical and materials characteristics, but there are still problems that need to be solved before high- $\kappa$  gate dielectrics can be incorporated effectively into commercial ICs. Interfacial layer formation is one of the largest obstacles to high- $\kappa$  integration. For maximum capacitance, it is best to have the high- $\kappa$  material in direct contact with the Si substrate. However, it is currently difficult to create high quality direct interfaces between high- $\kappa$  materials and Si. Therefore, to improve interface quality it is common practice to use interfacial barrier layers (oxides or oxynitrides). The purpose of an interfacial layer is to take advantage of the natural Si-SiO<sub>2</sub> interface while also incorporating a high- $\kappa$  material to increase the capacitance and thickness and thereby reduce the direct tunneling probability. Nitrided interfacial layers are also used to limit dopant diffusion into the channel. In a standard polysilicon CMOS process, the gate electrodes are implanted with dopants such as phosphorous and boron [33]. The devices are then annealed at temperatures close to 1000 °C to activate the dopant and distribute it throughout the polysilicon. If the dopants are able to diffuse through the gate insulator into the channel, they can change the threshold voltage of the device, or in large quantities, can increase drain to source leakage current. The problem is that a low permittivity interfacial layer reduces the capacitance of the gate stack and ultimately limits the effectiveness of the high- $\kappa$  material. Even if it is possible to create a clean interface between silicon and a freshly deposited alternative gate dielectric, it is difficult to maintain that interface throughout a standard process flow because most high- $\kappa$  materials are not good oxygen diffusion barriers [14, 21, 34]. Oxygen uptake is slowest for Al<sub>2</sub>O<sub>3</sub>, but even modest oxygen pressures are enough to cause significant interfacial oxidation [34]. In practice, interfaces that are nearly free of oxidized silicon have been achieved in a few systems, most notably as deposited  $Al_2O_3/Si(001)$  [35]. Still, avoiding silicon oxidation has been difficult in other materials systems. For Group IV metal oxides (HfO<sub>2</sub> and ZrO<sub>2</sub>) there is typically an unintentional interfacial layer of SiO<sub>2</sub> that is  $\sim 0.5$ nm thick [35–37].

In contrast to SiO<sub>2</sub>, most high- $\kappa$  materials experience a phase change from amorphous to crystalline at relatively low temperatures ( $\sim 400$  °C to 800 °C) [15,33,37]. The crystallization temperature can be increased by adding SiO<sub>2</sub> (silicates) or Al<sub>2</sub>O<sub>3</sub> (aluminates) to the metal oxide (HfO<sub>2</sub>,

ZrO<sub>2</sub>, etc.) to form alloys [25,28]. However, for these materials to stay amorphous at temperatures near 1000 °C, the composition must be configured strongly toward pure SiO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub>, and will therefore have a significantly reduced dielectric constant. The issue is that with film crystallization comes an increase in leakage current. However, polycrystalline yttrium oxides have shown relatively low leakage levels [15], so it is unclear whether an amorphous film is absolutely necessary.

Furthermore, it is important to understand the stability and long-term reliability of these materials to ensure the problems associated with ultra-thin SiO<sub>2</sub> are not simply traded for an even larger set of problems with alternative dielectrics. Moreover, before these materials can be used for space applications, it is equally important to understand their radiation response. In this thesis the radiation response and long term reliability of several high- $\kappa$  materials is evaluated. Chapter II is an introduction, which provides a brief overview of total dose and single event radiation effects in microelectronics and a discussion of radiation effects in nitrided gate oxides. Chapter III is a discussion of the radiation response of aluminum oxide capacitors and transistors and chapter IV covers hafnium based dielectrics. Chapter V describes how to compare the relative material qualities and radiation responses of high- $\kappa$  dielectrics by calculating an effective charge trapping efficiency. The long term reliability of these materials is discussed in chapter VI, and chapter VII provides the summary and conclusions of this work.

### **CHAPTER II**

### EFFECTS OF RADIATION

### **Total Dose Radiation Effects**

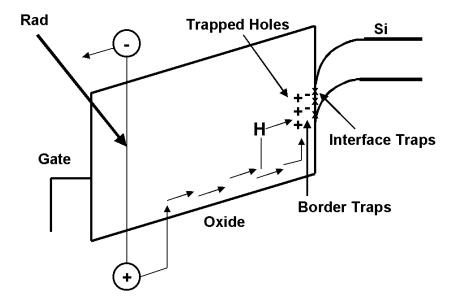

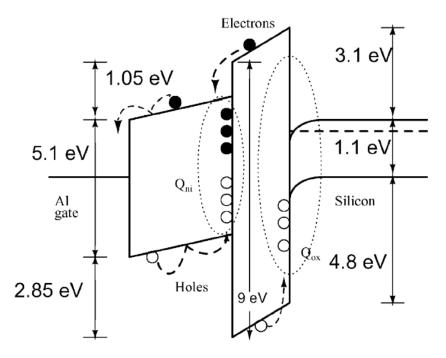

Ionizing radiation degrades a CMOS integrated circuit by producing electron hole pairs (EHPs) in the gate and isolation dielectrics. Some of the radiation-induced charge recombines and does not affect the device. The percentage of EHPs that escape initial recombination (i.e., the charge yield) depends on the oxide electric field [38, 39]. A large electric field will separate the charges more efficiently, leading to fewer recombination events [38, 40]. A significant fraction of the remaining radiation-induced charge can become trapped at micro-structural defects in the dielectric. The mechanism for radiation-induced charge generation and charge trapping in  $\mathrm{SiO}_2$  gate dielectrics is shown by the energy band diagram in Fig. 1. This figure shows a metal gate, p-substrate MOS capacitor, irradiated under positive gate bias. For this bias condition, the electrons are swept out toward the gate electrode, while the holes transport toward the Si/SiO<sub>2</sub> interface via defect sites in the oxide [39]. Some of the unrecombined holes will become trapped in the oxide, forming a positive oxide trapped charge density. As shown in Fig. 1, protons are released during hole transport to the interface and as holes are trapped near the Si/SiO<sub>2</sub> interface. These protons have been linked to radiation-induced interface trap formation in devices with SiO<sub>2</sub> gate oxides. Although Fig. 1 only shows hole trapping in the oxide, most gate dielectrics can also trap a significant density of electrons. Indeed, some HfO<sub>2</sub> films have exhibited more electron trapping than hole trapping after exposure to ionizing radiation [41]. However, the radiation-induced oxide trapped charge in SiO<sub>2</sub> and alternative dielectrics is generally net positive [42–44].

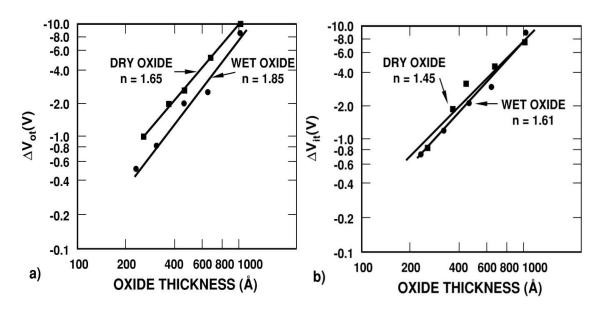

Historically, the gate oxides of CMOS devices were relatively thick and radiation-induced charge buildup in gate oxides was a major concern. Fortunately, as an IC technology is scaled and the gate oxide thickness is decreased, the radiation hardness of thermally grown gate oxides (SiO<sub>2</sub>) can improve dramatically. Figure 2 is a plot of the threshold-voltage shifts due to interface-trap and oxide-trapped charge for dry and steam grown (wet) oxides [45]. The threshold-voltage shifts due to both types of charge decrease with slightly less than a  $t_{ox}^2$  thickness dependence ( $t_{ox}^{1.5}$  to  $t_{ox}^{1.8}$ ). Thus, excellent total-dose hardness is a supplementary benefit of aggressive gate oxide scaling. For very thin oxides (<20 nm), there is evidence that the amount of radiation-induced

Figure 1: Energy band diagram showing ionizing radiation creating electron-hole pairs in the SiO<sub>2</sub> layer of a MOS capacitor under positive gate bias. After [39].

oxide-trap charge decreases with an even faster dependence on oxide thickness [46]. Because of the improvement in hardness with decreasing thickness, thermally grown gate oxides in advanced commercial technologies can be extremely radiation hard, withstanding accumulated doses in excess of 1 Mrad(SiO<sub>2</sub>) with little threshold voltage shift. With high- $\kappa$  gate materials, much thicker dielectrics can be used to obtain the equivalent capacitance of much thinner SiO<sub>2</sub> gates. This raises the concern that gate oxide radiation response could be degraded if high- $\kappa$  dielectrics are used in place of ultra-thin SiO<sub>2</sub>.

## Oxide Traps

Oxide-trapped charge is net positive charge located in the bulk and near interfacial region of the gate dielectric, which forms as holes become trapped at defect sites in the dielectric. The precursor trap densities for high- $\kappa$  devices reported in the literature are typically  $\sim 1$ -2 orders of magnitude larger than is usually achieved for high quality thermal SiO<sub>2</sub> [13, 14, 47]. The density of oxide-trapped charge is greatest immediately following radiation exposure with some annealing occurring slowly over time due to electron tunneling from the Si or thermal emission of holes from the trap sites [48–50]. Positive charge trapping in the gate oxide can invert the channel interface for nMOS devices causing leakage current to flow in the OFF state condition ( $V_{GS} = 0$  V). This will result in an increase in the static power supply current of an IC and may cause IC failure. In

Figure 2: The dependence of the threshold-voltage shift due to a) oxide-trap and b) interface-trap charge on oxide thickness. After [45].

a similar fashion, positive charge buildup in isolation oxides (field oxides and silicon-on-insulator (SOI) buried oxides) can cause large increases in IC static power supply leakage current.

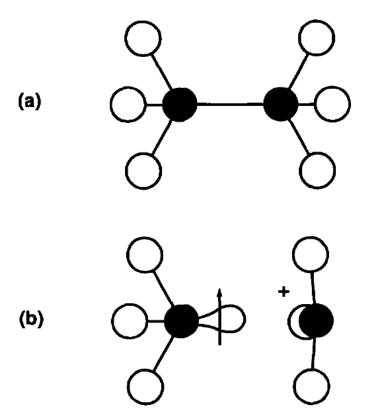

The most widely accepted precursor leading to the formation of oxide-trap charge in SiO<sub>2</sub> is the E' center or oxygen vacancy [51–54]. An oxygen vacancy can result from implantation damage or from out-diffusion of oxygen during a post-oxidation, high temperature, annealing cycle [55]. The number of oxygen vacancies in a given technology is therefore dependent on the process. As discussed in detail in chapters III and IV, high- $\kappa$  gate dielectrics show significant changes in trapping properties with processing variations. In 1992, Warren *et al.* discussed several possible structures for E' centers in amorphous SiO<sub>2</sub> [51]. Since then, it has been determined that the E'<sub>\gamma</sub> center is the most probable precursor to oxide-trapped charge formation in SiO<sub>2</sub> [52–54]. Fig. 3 shows a diagram of the E'<sub>\gamma</sub> trapping center with part (a) representing the precursor to the oxide trap (O<sub>3</sub>  $\equiv$ Si-Si $\equiv$ O<sub>3</sub>) and part (b) showing a hole trapped by the precursor site (O<sub>3</sub>  $\equiv$ Si↑  $^+$ Si $\equiv$ O<sub>3</sub>).

For alternative dielectrics, there has been little work done to understand defect microstructure. However, it is likely that a defect similar to an E' center exists in most high- $\kappa$  films in addition to other possible defect centers related to the stoichiometry of a particular high- $\kappa$  material. Charge trapping in alternative gate dielectrics is a significant concern [56–62]. Researchers at IBM have shown that the probability of bias induced charge trapping in high- $\kappa$  gate dielectrics is extremely

Figure 3: Schematic diagram of an  $E'_{\gamma}$  center, showing the characteristic strained Si-Si bond precursor state and the charged EPR active state. After [51].

high due to the large densities of intrinsic defects [56–59]. This is different than the behavior of SiO<sub>2</sub>, which generally has very few "as grown" defects, and defects are created during stressing [56].

## Interface Traps

In addition to oxide trapped charge buildup, ionizing radiation can also change the interface trapping properties of devices. Interface traps are located directly at the interface with energy levels that exist within the silicon band gap [45]. Traps in the lower half of the band gap are donor like, meaning they are neutral when filled and positively charged when empty [45]. In contrast, interface traps in the upper portion of the band gap are acceptor like, meaning they are neutral when empty and negatively charged when filled [45]. Trap sites with energies a few kT below the Fermi level (determined from Fermi statistics) are filled, and trap sites with energies a few kT above the Fermi level are empty. The number of occupied or unoccupied trap sites at the interface is therefore bias dependent because the amount of band bending determines the number of interface traps above and below the Fermi level. Thus, when a device is biased at midgap, interface traps are neutral [63,64]. Interface trapped charge causes negative threshold voltage shifts in p-channel transistors, positive

threshold voltage shifts in n-channel transistors, and channel mobility degradation [65,66]. These effects can decrease the drive of transistors and degrade the timing parameters of an IC. In contrast to oxide traps, interface trap density is at a minimum immediately following radiation exposure and slowly builds up with time [65,67]. In circuits, interface traps decrease the noise margin and increase the switching time.

The underlying mechanisms for interface trap formation in  $SiO_2$  and in alternative gate dielectrics is not completely understood. The most widely accepted model of interface trap formation in  $SiO_2$  is that hydrogen species, released during hole transport in the oxide, migrate to the  $Si/SiO_2$  interface and react with silicon dangling bonds to form interface traps [65, 67–69]. Much work is still being done to study both hydrogen motion in  $SiO_2$  and the detailed microstructure of interface traps. However, a dangling Si bond that is passivated by a hydrogen atom (H-Si $\equiv$ Si) is currently considered the most likely precursor to interface trap formation in  $SiO_2$  [52–54, 70]. Interfacial defect microstructure in alternative gate dielectrics is still largely unknown.

## Border Traps

The term border trap was first suggested by D.M. Fleetwood in 1991 [71]. Simply put, border traps are oxide traps that are able to exchange charge with the silicon on the time scale of the electrical measurements. This property of being able to exchange charge with the silicon during the measurement causes border traps to look like interface traps electrically; however, these defects are in the oxide and not at the interface. There is still some debate as to the underlying microstructure of border traps, and it is likely that there is not a single defect for all border traps in all materials and devices [71]. In this work low frequency (1/f) noise measurements are used estimate the border trap density in  $Al_2O_3$ /oxynitride transistors.

# Single-Event Effects

In addition to total dose ionization damage, energetic particles such as protons, alpha particles, and heavy ions associated with space environments can also cause single-event effects (SEE). As a single high-energy particle (e.g., energetic heavy ion, proton, alpha particle, or neutron) strikes a material, it generates a dense plasma of electron-hole pairs along the path of the particle, which can trigger a variety of SEE. Single-event effects are classified into two types: soft errors, which cause no permanent damage and may be correctable, and hard errors, which result in permanent damage to the device. A single event upset (SEU) is an example of a soft error, where only the logic state of the circuit is changed. SEUs were first observed in space in 1975 [72]. Soft errors can generally be corrected by reloading the original information into a memory element or by restarting an algorithm

in a CPU. If the error rate caused by single-event upsets is too high, performance degradation and even system failure can result. Hard errors are observed in circuits where large electric fields are present across insulating layers, such as nonvolatile memories and thin gate oxides. For example, permanent damage can be induced by energy deposition in a small region of the dielectric after the passage of a high-energy particle. This effect is known as single-event gate rupture (SEGR). Protons and heavy ions may also trigger high-current conditions that can result in permanent circuit failure. Examples of this type of hard error are single-event latchup (SEL) in CMOS and bipolar ICs, single-event snap-back (SESB) in nMOS devices, and single-event burnout (SEB) in power transistors [73].

#### Radiation-induced hard breakdown

A major consideration for designers of space systems is a catastrophic failure known as radiation-induced hard breakdown (RHB) (also called single event gate rupture (SEGR)) [74–76]. This effect can occur under conditions of high field, such as during a write or clear operation in a nonvolatile SRAM or E<sup>2</sup>PROM. It has recently become a concern for advanced technologies as oxide thicknesses scale below 10 nm and oxide fields increase above 5 MV/cm [77]. As a heavy ion passes through the dielectric, a highly conductive plasma path is formed, which allows the capacitor formed by this structure to discharge. If sufficient energy is stored on the capacitor due to high electric fields, excessive heating during discharge can create a thermal runaway condition [74]. Temperatures can be high enough to cause the dielectric to melt and the overlying conductive layers to evaporate.

The industry trend toward increasing electric fields as oxide thickness and feature size scale down in advanced technologies has raised concern that RHB may be a limiting factor for integrated circuits (ICs) in space applications. It was suggested that, as devices scaled to 0.25  $\mu$ m and below, RHB by Fe ions will occur, leading to a large increase in catastrophic failures in space hardware. Sexton, et al. [77] found that, as oxide thickness decreased below 10 nm, the increasing breakdown strength of the oxides resulted in a higher than expected gate voltage for rupture, contrary to earlier predictions. Their results suggest that advanced technologies will be more RHB resistant at a given electric field than expected. They cautioned, however, that RHB will continue to be a significant concern for devices that operate with gate oxide electric field above 5 MV/cm.

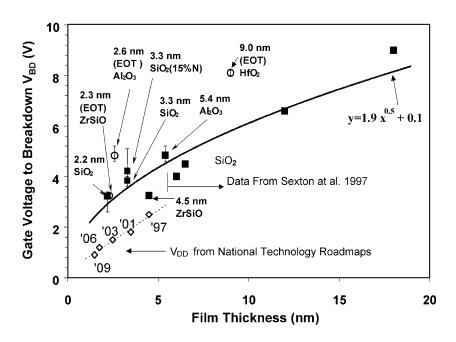

Massengill et al. found that for highly scaled (ultra-thin) gate oxides and alternate high- $\kappa$  dielectrics, RHB should not be a limiting factor in advanced technologies [78]. Figure 4 is a plot of the voltage to breakdown for capacitors versus dielectric thickness for several different nitrided and high- $\kappa$  dielectrics, as well as for SiO<sub>2</sub>. These capacitors were exposed to 342-MeV gold ions.

Figure 4: Gate voltage to breakdown versus physical film thickness for several different alternate high- $\kappa$  dielectrics and ultra-thin SiO<sub>2</sub> gates. The capacitors were exposed to 342-MeV gold ions. After [78].

The critical voltage to hard breakdown scales with the square root of the physical thickness of the insulator. The data of Fig. 4 show the breakdown data for thin oxides can be fit by a power threshold model [79] as opposed to an energy dissipation model as has been applied to high voltage devices with thick oxides [80,81]. Also shown in the figure (dashed line) is the  $V_{DD}$  scaling trend suggested by the SIA National Technology Roadmap [82]. Although there is considerable variation in the voltage to hard breakdown in the devices of Fig. 4, all of the breakdown voltages are above the power supply voltages that will be seen in future highly scaled commercial technologies. Therefore, it does not appear that RHB will be a significant problem for future highly scaled commercial technologies which incorporate alternative gate dielectrics.

### Radiation-induced soft breakdown

It is possible for energetic ions to degrade a device without causing permanent damage such as SEGR. Two examples of this are radiation-induced leakage current (RILC) [83–85] and radiation-induced soft breakdown (RSB) [78, 86–88]. Both RILC and RSB are characterized by increased oxide leakage current after ion exposure. RILC is the result of radiation-induced trap-assisted tunneling current, similar to SILC observed after constant voltage stress [83, 84]. Massengill et

al. [78] and Ceschia et al. [89] showed that RSB in high- $\kappa$  and SiO<sub>2</sub> gate oxides results as the ions create random conductive paths in the oxide proportionally with ion fluence. In contrast to RHB, there does not appear to be a critical electric field for the onset of RSB [78,89], but rather a critical threshold ion LET [77,78,89]. Choi et al. [90] showed that oxide damage leading to RSB is a function of dielectric film thickness, ion LET, and total fluence. RSB can increase the gate current by  $\sim 1~\mu\text{A}$ , which increases the power consumption in the device by  $\sim 1~\mu\text{W}$  [87]. Thus, RSB is most significant in low power applications like space electronics. However, it has also been shown recently that the combination of ion irradiation and electrical stress can affect the long term reliability of devices with ultra-thin gate oxides [87,90–92]. Suehle et al. [92] showed that capacitors irradiated with <sup>129</sup>Xe ions to a fluence of 10<sup>7</sup> ions/cm<sup>2</sup> had a time to failure in constant voltage time dependent dielectric breakdown (TDDB) tests that was reduced by approximately three orders of magnitude relative to unirradiated devices. Similar premature failures during TDDB testing have also been observed in devices irradiated with Au, Br, I, and Si ions [91]. Therefore, although ion exposure may not always cause a catastrophic failure like RHB, it can significantly reduce the operational lifetime of a device. This is a concern for space electronics, which are generally designed to have  $\sim 10$  year lifetimes. Moreover, since devices with alternative gate dielectrics often have shorter operational lifetimes (based on low Weibull slope TDDB results) than ultra-thin SiO<sub>2</sub> for a given operating voltage [22,93–95], RSB and latent ion damage could pose a serious problem for qualifying devices with alternative gate dielectrics for use in space.

# Nitrided Oxides

One alternative dielectric that has been previously explored (by others) in some detail is reoxidized nitrided oxides (RNO) [96–101]. In general, nitrided oxides have a lower pin-hole density than SiO<sub>2</sub>, can be grown at high temperatures, permitting better uniformity and less compressive stress and fixed charge, and can slow the diffusion of dopants through the insulator, which can affect the channel resistivity [97]. Furthermore, RNO oxides have been shown to be superior to thermal oxides in hot-carrier degradation [102]. Thus, nitrided and RNO dielectrics are attractive for ultra-thin gate oxides for commercial and radiation hardened devices [97]. However, because the dielectric constant of these materials is very similar to SiO<sub>2</sub>, nitrided oxides are only a viable alternative dielectric for near-term replacement (1-2 generations) of SiO<sub>2</sub>.

The primary difference between thermal SiO<sub>2</sub> and RNO dielectrics in ionizing radiation environments is the nearly total lack of interface-trap buildup for RNO dielectrics [103]. RNO dielectrics can be fabricated such that there is no measurable interface-trap buildup for transistors irradiated

Figure 5: The change in midgap voltage measured on 37 nm RNO and thermal oxide transistors versus dose. The midgap voltage shift corresponds to the threshold-voltage shift due to oxide-trapped charge. After [103].

to total doses in excess of 50 Mrad(Si) [103]. This makes RNO gates attractive for space applications. For those cases where some interface-trap buildup was observed, the number of interface traps does not increase in time after irradiation [104]. This likely occurs because hydrogen released in the bulk of the dielectric or near the interface (which is responsible for interface-trap buildup in thermal oxides), cannot penetrate the nitrogen rich oxynitride layer near the interface and create interface traps [104].

RNO dielectrics can be fabricated so that the amount of oxide trapped charge buildup is less than or comparable to that of a thermal oxide. Figure 5 is a plot of the threshold-voltage shift at midgap for p-channel transistors fabricated with a hardened oxide and with a RNO oxide versus dose [103]. The oxide and RNO dielectric thicknesses were 37 nm and the pre-irradiation fixed charge levels were  $\sim 3\times10^{10}$  and  $10^{11}$  cm<sup>2</sup>, respectively. At midgap, interface-trap charge is neutral, thus the threshold-voltage shift at midgap corresponds to the threshold-voltage shift due to oxide-trap charge. The bias during irradiation for the hardened thermal oxide was +5 V and the bias for the RNO oxides was either +5 or -5 V. After irradiation to 10 Mrad(SiO<sub>2</sub>), the amount of oxide-trap charge buildup in the hardened thermal oxides is more than twice that for the RNO oxides. Note that for the RNO oxide transistors, the shifts are nearly equal for biases of +5 and

| extremely good. |  |  |  |  |  |  |  |

|-----------------|--|--|--|--|--|--|--|

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

|                 |  |  |  |  |  |  |  |

-5 V. Based on the results of Fig. 5, the radiation hardness of ultra-thin RNO dielectrics should be

## CHAPTER III

### ALUMINUM OXIDE DIELECTRICS

Aluminum oxide is a candidate for short-term replacement (2-3 generations) of SiO<sub>2</sub> because of its larger dielectric constant and its compatibility with high temperature CMOS processing [15]. The aluminum oxide capacitors studied here were 0.0011 cm<sup>2</sup> Al gate devices fabricated at IBM's Thomas J. Watson Research Center on n-type Si(100) wafers with a doping concentration of  $\sim 10^{16}~{\rm cm^{-3}}$ . The gate dielectric stack consisted of an  ${\rm Al_2O_3}$  layer on an interfacial oxynitride. Sixteen different process splits ( $\sim 500$  devices per wafer) were fabricated within one wafer lot with 4 variations in  $Al_2O_3$  thickness, 2  $SiO_xN_y$  thicknesses, and 2 different annealing conditions. The physical thickness of the Al<sub>2</sub>O<sub>3</sub> was 10 nm, 7.5 nm, 5.0 nm, or 2.5 nm, while the physical thickness of the oxynitride was either 2.5 nm or 1.1 nm as measured ellipsometrically. The interfacial oxynitrides were thermally grown on HF-last Si(100), resulting in  $\sim 10\%$ -15% N incorporation. The Al<sub>2</sub>O<sub>3</sub> layers were deposited by atomic layer deposition (ALD) at 300 °C using standard Al(CH<sub>3</sub>) + H<sub>2</sub>O surface chemistries [15–17]. After deposition, the dielectrics were subjected to either a forming gas (5-10% H<sub>2</sub> in N<sub>2</sub>) anneal (FGA) at 550 °C or an O<sub>2</sub> anneal and a FGA at 550 °C. The accumulation capacitance of the  ${\rm O}_2$  annealed devices was consistently  $\sim 5\%$  to 10% smaller than the devices that received a FGA only, suggesting they had an oxygen rich oxynitride, or a small amount of SiO<sub>2</sub> at the interface [16,105]. After annealing, the Al gate electrodes were evaporated at room temperature. The relative dielectric constant of as-deposited  $Al_2O_3$  is  $\sim 8$  and the relative dielectric constant of silicon oxynitride is  $\sim 4$ -5 for this concentration of N. The equivalent oxide thicknesses (EOTs) of the dielectrics studied here are 7.4 nm, 6.2 nm, 5.1 nm, and 3.4 nm for the devices with the 2.5 nm oxynitride and 6.3 nm, 5.2 nm, 4.0 nm, and 2.6 nm for the devices with the 1.1 nm oxynitride.

Prior to irradiation the capacitance-voltage (CV) and breakdown characteristics of several  $(\sim 40)$  capacitors from each sample were measured using equipment at Sandia National Laboratories. These wafer level measurements were made using an Electroglass automated prober and a HP 4062 characterization system controlled by HP's ICMS wafter test control utility. Fig. 6 is a plot of representative (a) CV curves and (b) breakdown characteristics for  $\sim 20$  of these devices. Fig. 6a shows that these capacitors have well behaved CV characteristics with a flatband voltage  $(V_{fb})$  of  $\sim 0$  V and very little part-to-part variation. The devices that received only a FGA showed

Figure 6: Pre-irradiation (a) CV and (b) breakdown characteristics for 0.011 cm<sup>2</sup> devices with 10 nm  $Al_2O_3$  on 2.5 nm  $SiO_xN_y$  which received a FGA after  $Al_2O_3$  ALD. The corresponding EOT of these samples is  $\sim 7.4$  nm.

no measurable hysteresis, whereas most of the devices which received an O<sub>2</sub> anneal and FGA showed  $\sim 20$ -30 mV of hysteresis (not shown here). The bias dependence of the hysteresis suggests that it is related to electron movement into and out of border traps in the near interfacial region of the oxide [106]. However, due to the thin oxynitride layers present in these devices, the possibility of an additional contribution from traps at the  $Al_2O_3/SiO_xN_y$  interface cannot be ruled out. Fig. 6b shows that these devices have low gate leakage currents ( $\sim 1~\mathrm{pA}~\mathrm{or}~10^{-8}~\mathrm{A/cm^2}$ ) for gate voltages less than  $\sim 3$  V. Similar Al<sub>2</sub>O<sub>3</sub>/SiO<sub>x</sub>N<sub>y</sub> gate dielectrics exhibit a factor of  $\sim 100$  reduction in leakage current compared to electrically equivalent  $SiO_2$  [16]. Overall, the breakdown field  $E_{bd}$  did not depend significantly on processing conditions or Al<sub>2</sub>O<sub>3</sub> thickness. However, my results showed that the interfacial oxynitride plays an important role in the breakdown of the dielectric stacks for these devices. The samples with the 2.5 nm interfacial layer had an average breakdown of  $\sim 6$  MV/cm with a standard deviation of  $\sim 0.5$ , whereas the devices with the 1.1 nm oxynitride broke down at an electric field of  $\sim 4.7 \text{ MV/cm} \pm 0.6$ . This result is in good agreement with initial data in the literature that suggests high- $\kappa$  dielectric breakdown is determined by the interfacial layer [93, 107]. In comparing the electric fields in each of the layers at breakdown, it was found that the fields in the oxynitrides were  $\sim 8-9$  MV/cm whereas the fields in the Al<sub>2</sub>O<sub>3</sub> were  $\sim 4-5$  MV/cm. Therefore, the breakdown strength in these  $\mathrm{Al_2O_3/SiO}_x\mathrm{N}_y$  dielectric stacks is really limited by the  $\mathrm{SiO}_x\mathrm{N}_y$ . When the oxynitride breaks down, all of the gate potential is suddenly dropped across the Al<sub>2</sub>O<sub>3</sub>, and since it cannot maintain as large an electric field, it too breaks down.

Charge pumping is more precise than CV or subthreshold current-voltage (IV) stretchout

analysis for measuring interface trap densities [108]. Thus, high- $\kappa$  transistors with similar gate dielectric stacks were also examined as part of this work. These devices were 100  $\mu$ m x 100  $\mu$ m nMOSFETs with n<sup>+</sup> poly-Si gates fabricated on p-type Si(100) wafers with a doping concentration of  $\sim 3 \times 10^{17}$  cm<sup>-3</sup>. The Al<sub>2</sub>O<sub>3</sub> and SiO<sub>x</sub>N<sub>y</sub> layers were deposited in the same manner as the capacitors discussed above. The physical thickness of the Al<sub>2</sub>O<sub>3</sub> was 20 nm, and the interfacial oxynitride was  $\sim 0.7$  nm, corresponding to an EOT of  $\sim 8.0$  nm. These transistors received different post deposition thermal cycles than the capacitors, including a 1000 °C dopant activation anneal in Ar for  $\sim 5$  seconds, a standard FGA at 550 °C, and a second FGA anneal at 400 °C after deposition of the metal interconnects [16,24]. It is known that variations in post deposition anneal conditions can significantly impact the radiation response of SiO<sub>2</sub> [109]. As discussed in detail below, similar effects of processing are also observed for the radiation response of the nMOSFETs relative to the capacitors.

## Capacitor Radiation Results

The capacitors were irradiated incrementally to a total dose of 10 Mrad(SiO<sub>2</sub>) with 10-keV X-rays at a dose rate of  $1667 \text{ rad}(\text{SiO}_2)/\text{s}$ . Several types of radiation experiments were performed to determine the effects of radiation bias, dielectric film thickness, and processing conditions. The effects of the radiation were characterized using standard 1-MHz high frequency CV analysis [63], and the results of these experiments are discussed in detail below.

# Bias dependence

The effects of bias during irradiation of high- $\kappa$  devices are not well understood. However, prior work has shown that radiation-induced midgap voltage shifts ( $\Delta V_{mg}$ ) have a weak dependence on radiation bias for some alternative dielectric materials [42, 43]. Therefore, these Al<sub>2</sub>O<sub>3</sub>/SiO<sub>x</sub>N<sub>y</sub> capacitors were irradiated using several electric fields between -1.0 and 2.0 MV/cm. For fields larger than  $\sim 2.3$  MV/cm, these gate dielectrics begin to conduct enough current that any radiation results reported in this range could be skewed, resulting from trapped positive charge neutralization due to the injected charge. Fig. 7 is a plot of the absolute value of  $\Delta V_{mg}$  after a total dose of 2.0 Mrad(SiO<sub>2</sub>) as a function of oxide electric field during irradiation. The bias dependence in these devices is similar to that observed in standard thermal oxides [38], although somewhat different than the bias dependence for hafnium silicate gate dielectrics as discussed in the next chapter. In Fig. 7, the magnitude of the radiation induced voltage shift increases monotonically from  $\sim 0.1$  V

Figure 7: Absolute value of  $\Delta V_{mg}$  versus electric field for  $Al_2O_3/SiO_xN_y$  capacitors irradiated to 2 Mrad(SiO<sub>2</sub>). These devices were processed with a FGA only after  $Al_2O_3$  ALD. The data points represent the average of at least four devices and the error bars represent the standard deviation.

at -1.0 MV/cm to  $\sim 0.75$  V for fields of 1.0-1.3 MV/cm. The observed drop-off at larger fields is consistent with an approximate  $E^{-0.5}$  dependence and is likely related to a decrease in effective capture cross section with increasing field as has been observed in SiO<sub>2</sub> [38, 110, 111]. In some thermal oxides, negative bias exposures lead to larger voltage shifts than irradiations at 0 MV/cm due to an increase in charge yield. However, in making these types of comparisons, it is necessary to consider the effects of both charge yield and location of the charge centroid. For increasing negative fields, there is an increase in charge yield corresponding to a decrease in the initial recombination of radiation-induced electron-hole pairs, which will tend to increase the amount of radiation induced voltage shift [38, 112]. However, larger negative fields tend to move the charge centroid toward the gate, which reduces the measured  $\Delta V_{mg}$  [113]. Thus, charge yield and centroid motion are competing mechanisms for negative bias exposures. Since the data of Fig. 7 show the magnitude of  $\Delta V_{mg}$  decreases for decreasing field, the location of the centroid appears to be the dominant factor determining the irradiation bias dependence in these devices.

Figure 8: Pre and post irradiation 1 MHz CV measurements on 0.0011 cm<sup>-2</sup> capacitors that received a FGA after  $Al_2O_3$  deposition, with an EOT of (a) 3.4 nm and (b) 6.2 nm, irradiated to total doses from 100 up to 10,000 krad(SiO<sub>2</sub>) at an electric field of +1.0 MV/cm.

# $Al_2O_3$ and $SiO_xN_y$ thickness dependence

The amount of midgap voltage shift in these devices depends strongly on gate dielectric film thickness. Fig. 8 shows representative 1 MHz CV data for devices with (a) a 2.5 nm Al<sub>2</sub>O<sub>3</sub> and (b) a 7.5 nm Al<sub>2</sub>O<sub>3</sub> layer on a 2.5 nm interfacial oxynitride, which received only a FGA, for incremental doses up to 10 Mrad(SiO<sub>2</sub>) at an electric field of 1.0 MV/cm. After 10 Mrad(SiO<sub>2</sub>), the device in Fig. 8a has a midgap voltage shift ( $\Delta V_{mg}$ ) of -52 mV, and the device in Fig. 8b shows a  $\Delta V_{mg}$  of -735 mV. Using these values for  $\Delta V_{mg}$ , net oxide trap charge densities can be estimated by [114]

$$\Delta N_{ot} = -\frac{C_{ox}\Delta V_{mg}}{aA} \tag{1}$$

where  $\Delta N_{ot}$  is the radiation induced net oxide trap charge density projected to the interface,  $C_{ox}$  is the oxide capacitance measured in accumulation, -q is the electronic charge, and A is the area. Using equation 1 the net oxide-trapped charge densities projected to the interface  $(\Delta N_{ot})$  are estimated to be  $2.98 \times 10^{11}$  cm<sup>-2</sup> and  $2.65 \times 10^{12}$  cm<sup>-2</sup>, respectively. Similarly, the flatband voltage shifts  $(\Delta V_{fb})$  for these devices at the same total dose are -50 mV and -720 mV. The interface-trap charge densities  $(\Delta N_{it})$  can be estimated from midgap-to-flatband stretchout of 1 MHz CV curves by [63]

$$\Delta N_{it} = \frac{C_{ox}(\Delta V_{fb} - \Delta V_{mg})}{qA}.$$

(2)

Therefore, the irradiation has no measurable effect on the interface trap density (as estimated from the midgap to flatband stretch-out) to within the accuracy of the measurement. This result is consistent with radiation results for hafnium oxide and hafnium silicate dielectric materials [41,42].

Figure 9: A complete summary of midgap voltage shifts as a function of total dose for exposures from 10 krad(SiO<sub>2</sub>) to 10,000 krad(SiO<sub>2</sub>) for devices with (a) a 2.5 nm and (b) a 1.1 nm interfacial oxynitride.

A more precise analysis of the interface trapping properties of similar  $Al_2O_3/SiO_xN_y$  gate dielectric stacks using CP analysis on nMOSFETs is discussed below.

Fig. 9 is a plot of  $\Delta V_{mg}$  versus dose for 1.0 MV/cm biased exposures from 10 krad(SiO<sub>2</sub>) to 10 Mrad(SiO<sub>2</sub>) for devices with (a) a 2.5 nm oxynitride and (b) a 1.1 nm oxynitride that received only a FGA after Al<sub>2</sub>O<sub>3</sub> deposition. For total doses up to 50 krad(SiO<sub>2</sub>), none of the samples trap a significant amount of charge. After additional exposure, there is a clear difference in the amount of trapped charge for each Al<sub>2</sub>O<sub>3</sub> film thickness at a given dose. By comparison of Figs. 9a and 9b, a significant reduction in the amount of radiation damage is observed for a given Al<sub>2</sub>O<sub>3</sub> film thickness for the devices with a 1.1 nm oxynitride layer relative to devices with 2.5 nm SiO<sub>x</sub>N<sub>y</sub>. These shifts are larger than would be observed in high-quality thermal SiO<sub>2</sub> of equivalent electrical thickness [46, 115–117]. However, it is evident that total-dose degradation will not be a major concern for Al<sub>2</sub>O<sub>3</sub>/SiO<sub>x</sub>N<sub>y</sub> gate stacks of most interest to modern CMOS manufacturing processes (< 4 nm EOT), as there is only ~ 50 mV shift after a total dose of 10 Mrad(SiO<sub>2</sub>).

It is interesting to consider why there is such a large difference in the amount of radiation induced trapped charge for a given  $Al_2O_3$  thickness for the two separate interfacial layers. One would expect to see less trapping in the films with the thinner oxynitride since there is less volume in these films within which to generate electron-hole pairs (EHPs). However, for a given  $Al_2O_3$  thickness, the difference in  $\Delta V_{mg}$  between Fig. 9a and 9b is more than that expected based on a volume argument alone. Thus it is necessary to consider additional mechanisms to understand

Figure 10: Logarithm of the absolute value of  $\Delta V_{mg}$  data from Fig. 9a (filled symbols) and Fig. 9b (open symbols) versus the logarithm of the physical thickness of the films. These 500 krad(SiO<sub>2</sub>) data are well correlated to a linear regression model (dashed lines) that shows a  $t_{ox}^4$  thickness dependence.

these data completely. Since these devices were processed in the same manner, they should exhibit similar trapping properties. Fig. 10 is a plot of the logarithm of the absolute value of the  $\Delta V_{mg}$  data from Fig. 9a and Fig. 9b as a function of the logarithm of the total physical thickness (t-Al<sub>2</sub>O<sub>3</sub> + t-SiO<sub>x</sub>N<sub>y</sub>) for a total dose of 500 krad(SiO<sub>2</sub>). A linear regression model of the data (dashed lines)

indicates there is a good correlation between the measured voltage shifts and the total film thickness; the  $\Delta V_{mg}$  in these devices is proportional to  $\sim t_{ox}^4$ . For SiO<sub>2</sub> films thinner than  $\sim 20$  nm, there is a similar deviation from the  $\Delta V \propto t_{ox}^2$  relationship that is expected and typically observed for thick oxides that are otherwise processed similarly [46,115–117]. The physical reason one expects to see a  $t_{ox}^2$  dependence is to account for charge generation throughout the entire volume of the oxide, and to account for the moment arm effect resulting from the spatial distribution of the charges in the oxide projected to the interface [113]. Deviation from a  $t_{ox}^2$  thickness dependence is the result of charge removal via tunneling from a thin layer near the interface and the gate electrode [46,117,118]. This reduces the effective thickness of the dielectric by the region over which the charge is removed. For thick films (> 20 nm), this is relatively insignificant, but it becomes an important consideration for films like those being discussed here. Saks, et al. successfully used a similar model to fit data on

Figure 11: The data of Fig. 10, as well as  $1000 \text{ krad}(\text{SiO}_2)$  data, plotted with the effects of tunneling taken into account. The data for both the 2.5 nm (solid symbols) and 1.1 nm (open symbols) are well correlated to a linear regression model (dashed lines) showing a  $t_{ox}^2$  thickness dependence.

ultra-thin SiO<sub>2</sub> capacitors [46]. For these Al<sub>2</sub>O<sub>3</sub>/SiO<sub>x</sub>N<sub>y</sub> devices,  $\Delta V_{mg} \propto t_{ox}^2$  if the devices with the 2.5 nm oxynitride are thinned by  $\sim 3$  nm due to tunneling, and the devices with the 1.1 nm oxynitride are thinned by  $\sim 4$  nm due to tunneling. This result is consistent with an increased electron tunneling probability for the thinner SiO<sub>x</sub>N<sub>y</sub> films. Fig. 11 is a plot of the data in Fig. 10, as well as data for exposures to 1000 krad(SiO<sub>2</sub>), with the effects of tunneling taken into account. In Fig. 11, the data for both the 2.5 nm oxynitride and 1.1 nm oxynitride devices fall on the same curve, and show a  $\sim t_{ox}^2$  dependence. Hence, most of the measurable trapping in these devices occurs in the Al<sub>2</sub>O<sub>3</sub> since the charge trapped in the oxynitride is removed due to tunneling. As expected, more trapping is observed for thicker Al<sub>2</sub>O<sub>3</sub> films due to their larger volumes. However, for a given Al<sub>2</sub>O<sub>3</sub> thickness, the devices with a 1.1 nm oxynitride show less trapping than a 2.5 nm oxynitride due to a greater tunneling probability for the thinner interfacial layer.

Consistent with the above interpretation, consider Fig. 12 in which  $\Delta V_{mg}$  is plotted versus dose for the 10 nm Al<sub>2</sub>O<sub>3</sub> devices of Fig. 9a and Fig. 9b, as well as data for devices from these same splits irradiated at -1.0 MV/cm. Under negative bias there should not be any significant electron tunneling effects since the Si surface is in inversion. Therefore, since the Al<sub>2</sub>O<sub>3</sub> thickness is the

Figure 12: Midgap voltage shift versus total dose for 10 nm  $Al_2O_3$  devices with 2.5 and 1.1 nm interfacial oxynitrides irradiated at +1.0 MV/cm (triangles) and -1.0 MV/cm (circles).

same, the radiation responses of the 1.1 nm  $SiO_xN_y$  and the 2.5 nm  $SiO_xN_y$  samples should match more closely than for positive bias exposures. As shown in Fig. 12, for negative bias exposures there is a nearly identical radiation response for devices with the same  $Al_2O_3$  thickness, independent of the interfacial oxynitride.

# Effects of processing

Fig. 13 is a plot of  $\Delta V_{mg}$  versus total dose for devices with 10 nm, 7.5 nm, and 5.0 nm Al<sub>2</sub>O<sub>3</sub> layers deposited on a 1.1 nm interfacial oxynitride for devices that received either a FGA or an O<sub>2</sub> anneal and FGA. The data of Fig. 13 show the devices which received the additional O<sub>2</sub> anneal also have a significantly improved radiation response as seen previously for thermal oxides in [119]. For doses greater than  $\sim 1 \text{ Mrad}(\text{SiO}_2)$  the 10 nm and 7.5 nm O<sub>2</sub> annealed devices have  $\sim 50\%$  less voltage shift than the devices which received a FGA only. The 5.0 nm devices show almost no shift with dose up to 10 Mrad(SiO<sub>2</sub>), and there is no measurable difference between the FGA and O<sub>2</sub>+FGA processed devices. Therefore, the significant processing dependence shown in Fig. 13 essentially vanishes for film thicknesses of most relevance to commercial use. The large differences seen in the 10 nm and 7.5 nm devices suggests that the O<sub>2</sub> anneal either decreases the density of hole trap precursors or increases the density of electron trap precursors in the near SiO<sub>x</sub>N<sub>y</sub> interfacial

Figure 13: Midgap voltage shift versus dose for 6.3 nm (solid symbols), 5.2 nm (striped symbols), and 4.0 nm (open symbols) EOT devices annealed with either a FGA or an  $O_2$  anneal and a FGA after  $Al_2O_3$  ALD.

region of the  $Al_2O_3$  or at the  $Al_2O_3/SiO_xN_y$  interface. It has been shown that the electron trap

density in SiO<sub>2</sub> can be significant (on the same order as hole traps) and is dependent on device processing [120]. Electron traps are classified as either "deep" or "shallow" depending on their energy distribution. Deep electron traps are very stable, and will compensate some of the trapped holes, thereby reducing the net oxide-trapped charge density measured using the midgap CV shift method [120]. Shallow trapped electrons can move easily in and out of the gate dielectric, producing effects such as CV hysteresis [120]. Recall that for these capacitors, only the O<sub>2</sub> annealed devices showed a measurable hysteresis. Thus, these data may be evidence of significant electron trapping in the  $Al_2O_3/SiO_xN_y$  dielectric stacks that received the O<sub>2</sub> anneal. This result is consistent with early work on  $Al_2O_3$  gate dielectrics, which showed those aluminum oxides had a significant density of electron traps [118]. Previous work often found that  $Al_2O_3$  exhibited good total-dose radiation hardness because it trapped a significant amount of electrons, which compensated the trapped holes [118, 121, 122]. Furthermore, it was shown that  $Al_2O_3$  contains several trap levels in the band gap, making it easy for electrons to tunnel between the dielectric and the substrate [123, 124]. Therefore, although the apparent reduction in  $\Delta V_{mg}$  observed in Fig. 13 for the O<sub>2</sub> annealed devices

may be the result of less hole trapping, the possibility of compensation via trapped electrons cannot be ruled out.

## Transistor Radiation Response

Polysilicon gated transistors with similarly processed  $Al_2O_3/SiO_xN_y$  dielectrics were characterized using a combination of of low frequency 1/f noise, subthreshold IV and variable base CP measurements. All measurements were done using devices from a single wafer. Some devices were packaged to facilitate the 1/f noise measurements [125], while the radiation, IV and CP data were taken using wafer level measurements. The irradiations were performed at a dose rate of 1000 rad(SiO<sub>2</sub>)/s using a 10 keV X-ray source. These devices, with gate stacks consisting of 20 nm  $Al_2O_3$  on 0.7 nm  $SiO_xN_y$  were irradiated incrementally to a total dose of 1  $Mrad(SiO_2)$ . During irradiation, the gate was biased at +1.0 MV/cm or -1.0 MV/cm with all other terminals grounded. Prior to irradiation, and after each incremental dose, the IV and CP characteristics were measured in situ. The IV measurements were performed by sweeping the gate from -2 V to +5 V with 150 mV on the drain. During the CP measurements, the gate was pulsed using a 4.5 V square wave with a 10 ns rise and fall time at a frequency of 500 kHz, while the source and drain were reverse biased at 500 mV. The 1/f noise of the packaged devices was measured as a function of both drain voltage  $(V_{ds})$  and gate voltage  $(V_{gs})$ . It is known that 1/f noise measurements are a sensitive test for probing the effects of near interfacial oxide defects (i.e., border traps) on channel carriers. Indeed, 1/f noise in MOS devices is the result of number and/or mobility fluctuations of channel carriers resulting from interactions with border traps [68, 106, 126]. Thus, the combination of 1/f noise measurements with IV and CP analysis offer a complementary toolset for examining the interface properties of these nMOSFETs before and after exposure to ionizing radiation.

Fig. 14 is a plot of the excess-voltage noise power spectral density  $S_{Vd}$  as a function of frequency for (a) several drain voltages at a constant  $V_{gs}$  of 5 V and for (b) varying  $V_{gs}$  with a constant  $V_{ds}$  of 100 mV [125]. These data show that the 1/f noise in these devices increases with increasing drain voltage and decreases with increasing  $V_{gs}$ . In Fig. 15, the data of Fig. 14 are combined and plotted as  $S_{Vd}$  versus  $V_{ds}^2/(V_{gs}-V_{th})^2$ , which are the expected drain and gate voltage dependences for noise due primarily to number fluctuations. Arranging the data in this way makes it possible to extract the density of border traps  $D_{bt}$  by [106]

$$D_{bt} = \left(\frac{A}{qkT}\right) ln\left(\frac{\tau_1}{\tau_2}\right) \left(\frac{\epsilon_{ox}}{t_{ox}}\right)^2 K \tag{3}$$

Figure 14: Pre-irradiation noise power spectral density for a 2  $\mu$ m × 20  $\mu$ m transistor for (a) several values of V<sub>ds</sub> at a constant V<sub>gs</sub> of 5 V as well as for (b) several values of V<sub>gs</sub> for a constant V<sub>ds</sub> of 100 mV. The spikes are the result of 60-Hz pickup and are ignored in the fitting and analysis of the data.

where A is the gate area of the transistor, q is the magnitude of the electronic charge, k is the Boltzmann constant, T is the absolute temperature,  $t_{ox}$  is the (equivalent SiO<sub>2</sub>) oxide thickness,  $\epsilon_{ox}$  is the dielectric constant of SiO<sub>2</sub>,  $\tau_1$  and  $\tau_2$  are "cutoff" times associated with the tunneling and thermally activated processes that lead to the observed noise [127, 128], and K is the normalized 1/f noise magnitude as found from the slope of a fit to the data in Fig. 15. For these devices, K

$\sim 3 \times 10^{-9} \text{ V}^2$  and the pre-irradiation  $D_{bt}$  from equation 15 is found to be  $\sim 2 \times 10^{12} \text{ cm}^{-2} \text{ eV}^{-1}$ . This number is larger than is commonly seen in SiO<sub>2</sub> [106], but may not be too surprising as it likely includes contributions from defects both in the near interfacial layer of the Al<sub>2</sub>O<sub>3</sub> and at the Al<sub>2</sub>O<sub>3</sub>/SiO<sub>x</sub>N<sub>y</sub> interface, which is  $\sim 0.7$  nm away from the SiO<sub>x</sub>N<sub>y</sub>/Si interface.

Fig. 16 shows the sub-threshold IV characteristics (S ~ 150 mV/dec) of these transistors for incremental irradiations up to 1 Mrad(SiO<sub>2</sub>) at a gate bias of 1.0 MV/cm. The shifts seen in Fig. 16 are due to the net positive charge buildup in the gate insulator with dose [63]. As a guide to the eye, a set of parallel lines has been added to the pre-irradiation and 1 Mrad(SiO<sub>2</sub>) curves to show that, just like for the CV curves of the capacitors, there is no measurable stretchout due to interface traps in these devices. Fig. 17 is a summary of  $\Delta V_{th}$  for irradiations at  $\pm$  1.0 MV/cm. After a total dose of 1 Mrad(SiO<sub>2</sub>),  $\Delta V_{th} \sim$  -1.3 V corresponding to  $\Delta N_{ot} \sim$  2.1 x 10<sup>12</sup> cm<sup>-2</sup> with no significant dependence on the bias polarity during irradiation. This result differs from the bias

Figure 15: Log-log plot of the noise power spectral density versus  $V_{ds}^2/(V_{gs}-V_{th})^2$  for the data of Fig. 14

Figure 16: Subthreshold IV data for a 100  $\mu$ m x 100  $\mu$ m Al<sub>2</sub>O<sub>3</sub>/SiO<sub>x</sub>N<sub>y</sub> transistor irradiated at +1 MV/cm from 10 krad(SiO<sub>2</sub>) to 1 Mrad(SiO<sub>2</sub>). The transistors examined here received a 1000 °C dopant activation anneal and two FGAs.

Figure 17: Summary of  $\Delta V_{th}$  for 100  $\mu$ m x 100  $\mu$ m nMOSFETs after irradiation with 10-keV X-rays for both positive and negative bias conditions.