# ARENBERG DOCTORAL SCHOOL Faculty of Engineering Science

# Hardware-supported Software and Control Flow Integrity

#### Ruan de Clercq

Supervisor: Prof. dr. ir. I. Verbauwhede Dissertation presented in partial fulfillment of the requirements for the degree of Doctor of Engineering Science (PhD): Electrical Engineering

# Hardware-supported Software and Control Flow Integrity

#### Ruan DE CLERCQ

Examination committee:

Prof. dr. ir. Omer Van der Biest, chair

Prof. dr. ir. I. Verbauwhede, supervisor

Prof. dr. ir. F. Piessens

Prof. dr. ir. B. Preneel

Prof. dr. Aurélien Francillon

(EURECOM, France)

Prof. dr. ir. Bjorn De Sutter

(University of Ghent, Belgium)

Dissertation presented in partial fulfillment of the requirements for the degree of Doctor of Engineering Science (PhD): Electrical Engineering

© 2017 KU Leuven - Faculty of Engineering Science Uitgegeven in eigen beheer, Ruan de Clercq, Kasteelpark Arenberg 10, bus 2452, B-3001 Leuven (Belgium) Alle rechten voorbehouden. Niets uit deze uitgave mag worden vermenigvuldigd en/of openbaar gemaakt worden door middel van druk, fotokopie, microfilm, elektronisch of op welke andere wijze ook zonder voorafgaande schriftelijke toestemming van de uitgever. All rights reserved. No part of the publication may be reproduced in any form by print, photoprint, microfilm, electronic or any other means without written permission from the publisher.

# **Acknowledgements**

First and foremost, I would like to thank my promoter Ingrid Verbauwhede for offering me the opportunity to pursue a PhD at COSIC. I am deeply grateful for her guidance, time, tips, and trust to allow me to freely conduct my research.

I would like to thank my assessors Prof. Bart Preneel and Prof. Frank Piessens for their valuable contributions throughout the doctoral program. I would further like to thank the additional members of the jury Prof. Aurélien Francillon and Prof. Bjorn de Sutter for the time and effort that they invested in this dissertation, and Prof. Omer Van der Biest for chairing the jury.

Thanks to all my co-authors for the fruitful discussions and collaborations. I learned a lot from you, and would like to continue writing papers with you.

I would like to thank all my colleagues in COSIC for contributing to a great research environment, and also for the lunches, karting, table tennis, coffee breaks, COSIC weekends, Friday beers, and climbing sessions. I have thoroughly enjoyed my time here and I can highly recommend working at COSIC.

I am forever grateful to all my friends in Leuven for their friendship, support, and patience that made my time in Leuven an unforgettable experience. Special thanks to my climbing friends for the many amazing sessions in Freyr, Mozet, Berdorf, Fontainebleau and further afield.

I want to thank my partner and family for their ongoing support, encouragement, and for always being there when I need them. Finally, I am eternally grateful to my mom and my partner's parents for their continued support.

Ruan de Clercq Leuven, November 2017

i

### **Abstract**

Bugs are prevalent in a large amount of deployed software. These bugs often introduce vulnerabilities that can be exploited by attackers to make programs misbehave. Many devices rely on software that needs security, such as medical implants, sensor networks, RFID tags, automotive controllers. Software should do what it is asked to do, and should not misbehave; e.g., by delivering the wrong drug dosages, by stealing information, by spying on the user, by disabling the brakes on a car, or by attacking other computers.

The central topic of this thesis is the development of hardware-based mechanisms that prevent software from misbehaving. We focus on enhancing the security of microprocessors to detect runtime attacks, prevent malicious modification of software, and develop support for isolating software from malware.

The main contributions of this thesis are two-fold. First, we analyse existing hardware-based Control Flow Integrity (CFI) architectures. This includes a detailed description and comparison of each architecture's policies, security, hardware cost, performance, and suitability for widespread deployment.

Second, we design several new hardware-based security architectures. This includes developing the first known CFI architecture based on instruction-set randomisation, that also enforces software integrity through modifications to a processor. We further design the first known hardware-based software integrity architecture that is realised as a standalone Intellectual Property (IP) core that connects to the bus via standard interfaces. Finally, we develop an architectural feature which provides interrupt support for a program counter-based Protected Module Architectures (PMAs) by means of processor modifications. All the architectures developed in this thesis are evaluated on Field Programmable Gate Array (FPGA), which allows us to accurately determine the hardware cost and the performance overhead of running the software on the architecture.

# Beknopte samenvatting

Veel geïnstalleerde software bevat fouten. Dit is problematisch omdat die fouten de oorzaak zijn van zwakheden die misbruikt kunnen worden om applicaties zich te doen misdragen. Software die beveiligd moet worden wordt gebruikt op vele apparaten, zoals medische implantaten, netwerken van sensoren, RFID tags en de regelaars in voertuigen. Deze software moet doen wat het gevraagd word en mag zich niet misdragen door bijvoorbeeld de verkeerde dosis medicijnen toe te dienen, informatie te stelen, de gebruiker te bespioneren, de remmen van een auto onbruikbaar te maken of door andere computers aan te vallen.

Het centrale onderwerp van deze thesis is het ontwerp van hardware-gebaseerde mechanismen die verzekeren dat software zich niet kan misdragen. We concentreren ons op het verbeteren van de beveiliging van microprocessoren om runtime aanvallen te detecteren.

De voornaamste bijdragen van deze thesis zijn tweeledig. Ten eerste analyseren we bestaande hardware-gebaseerde architecturen die de integriteit van de programmastroom beschermen. Dit omvat een gedetailleerde beschrijving van hun richtlijnen, samen met een evaluatie van hun beveiliging, hardware kost, performantie en geschiktheid voor wijdverspreide toepassing.

Ten tweede ontwikkelen we verschillende nieuwe hardware-gebaseerde architecturen. Dit omvat de ontwikkeling van de eerste gekende architectuur die de integriteit van de programmastroom beschermt aan de hand van instructieset randomisatie. Bovendien verzekert deze architectuur de integriteit van de applicatie door middel van aanpassingen aan de processor. We hebben daarnaast ook de eerste gekende hardware-gebaseerde architectuur ontwikkeld om de integriteit van software te beschermen tijdens de uitvoering ervan aan de hand van een *IP core* die verbindt met de bus via een gestandaardiseerde interface. Tot slot ontwikkelen we een architecturale functie op basis van aanpassingen aan de processor die ondersteuning voor *interrupts* toevoegt aan architecturen die softwaremodules beschermen door geheugentoegangcontrole op basis van de

programmateller. Alle architecturen die ontwikkeld worden in deze thesis zijn geëvalueerd op FPGA, waardoor we accuraat de hardware kost en de impact op de performantie voor het uitvoeren van software op de architectuur kunnen bepalen.

# **Contents**

| ΑI  | ostrac | ct                                                    | iii  |  |  |  |

|-----|--------|-------------------------------------------------------|------|--|--|--|

| Co  | onten  | ts                                                    | vii  |  |  |  |

| Lis | st of  | Figures                                               | xiii |  |  |  |

| Li  | st of  | Tables                                                | xvii |  |  |  |

| Li  | st of  | Abbreviations                                         | xix  |  |  |  |

| 1   | Intr   | oduction                                              | 1    |  |  |  |

|     | 1.1    | Defending against runtime attacks                     | 2    |  |  |  |

|     | 1.2    | Thesis objectives                                     | 3    |  |  |  |

|     | 1.3    | Summary of Contributions                              | 4    |  |  |  |

|     | 1.4    | Thesis Structure                                      | 5    |  |  |  |

|     | 1.5    | Other Publications                                    | 6    |  |  |  |

| 2   | Tow    | Towards Secure Interrupts on Low-End Microcontrollers |      |  |  |  |

|     | 2.1    | Introduction                                          | 9    |  |  |  |

|     | 2.2    | Architecture                                          | 10   |  |  |  |

|     |        | 2.2.1 Attacker model                                  | 11   |  |  |  |

viii \_\_\_\_\_\_CONTENTS

|   |     | 2.2.2    | Domain isolation                                                 | 11 |

|---|-----|----------|------------------------------------------------------------------|----|

|   |     | 2.2.3    | Context switching between domains                                | 13 |

|   | 2.3 | Secure   | Interrupts                                                       | 13 |

|   |     | 2.3.1    | Standard interrupt mechanism                                     | 13 |

|   |     | 2.3.2    | Domain isolation support                                         | 14 |

|   |     | 2.3.3    | Interrupting non-secure task with secure ISR $\ \ldots \ \ldots$ | 15 |

|   |     | 2.3.4    | Interrupting secure task with non-secure ISR $\ \ldots \ \ldots$ | 15 |

|   |     | 2.3.5    | Scheduling                                                       | 16 |

|   | 2.4 | Imple    | mentation                                                        | 17 |

|   |     | 2.4.1    | MSP430                                                           | 17 |

|   |     | 2.4.2    | Software-based implementation                                    | 17 |

|   |     | 2.4.3    | Hardware-based implementation                                    | 19 |

|   |     | 2.4.4    | Hidden registers optimization                                    | 20 |

|   | 2.5 | Evalua   | ation                                                            | 21 |

|   |     | 2.5.1    | Results                                                          | 21 |

|   |     | 2.5.2    | Limitations                                                      | 22 |

|   | 2.6 | Conclu   | ısion                                                            | 23 |

| 3 | Con | trol Flo | w Integrity                                                      | 25 |

|   | 3.1 | Introd   | uction                                                           | 26 |

|   | 3.2 | Attack   | ss and countermeasures: an arms-race                             | 27 |

|   | 3.3 | Backgr   | round                                                            | 29 |

|   |     | 3.3.1    | Control Flow Integrity (CFI)                                     | 29 |

|   |     | 3.3.2    | The need for hardware-based CFI                                  | 30 |

|   |     | 3.3.3    | Hardware monitor                                                 | 31 |

|   | 3.4 | Attack   | ær model                                                         | 34 |

|   | 3.5 | Classic  | eal CFI                                                          | 35 |

CONTENTS \_\_\_\_\_\_ix

|     | 3.5.1  | Labels                                                       | 35 |

|-----|--------|--------------------------------------------------------------|----|

|     | 3.5.2  | Shadow Call Stack (SCS)                                      | 36 |

|     | 3.5.3  | Challenges and limitations                                   | 36 |

| 3.6 | Hardw  | rare-based CFI Policies                                      | 38 |

|     | 3.6.1  | Shadow Call Stack (SCS)                                      | 38 |

|     | 3.6.2  | HAFIX: Shadow stack alternative                              | 42 |

|     | 3.6.3  | Labels                                                       | 42 |

|     | 3.6.4  | Table                                                        | 43 |

|     | 3.6.5  | Finite State Machine (FSM)                                   | 44 |

|     | 3.6.6  | Heuristics                                                   | 44 |

|     | 3.6.7  | Monitoring graph (MG)                                        | 46 |

|     | 3.6.8  | Branch Regulation (BR)                                       | 47 |

|     | 3.6.9  | BB-CFI: Branch Regulation on Basic Blocks                    | 48 |

|     | 3.6.10 | Branch Limitation (BL) $\ \ldots \ \ldots \ \ldots \ \ldots$ | 48 |

|     | 3.6.11 | Instruction Set Randomisation (ISRAND)                       | 50 |

|     | 3.6.12 | Signature Modeling (SM)                                      | 50 |

|     | 3.6.13 | Code Pointer Integrity (CPI)                                 | 52 |

| 3.7 | CFI er | nforcement via the debug interface                           | 53 |

|     | 3.7.1  | Implementations                                              | 53 |

|     | 3.7.2  | Limitations                                                  | 54 |

| 3.8 | Compa  | arison of Architectures                                      | 55 |

|     | 3.8.1  | Protection provided                                          | 55 |

|     | 3.8.2  | Requirements                                                 | 57 |

|     | 3.8.3  | Overhead                                                     | 58 |

| 3.9 | Conclu | asion                                                        | 59 |

|     |        |                                                              |    |

4 SOFIA: Software and Control Flow Integrity Architecture 63

× \_\_\_\_\_ CONTENTS

| 4.1 | Introd            | luction                                                     | 63 |  |  |

|-----|-------------------|-------------------------------------------------------------|----|--|--|

| 4.2 | Problem Statement |                                                             |    |  |  |

|     | 4.2.1             | Threat Model                                                | 64 |  |  |

|     | 4.2.2             | System goals                                                | 65 |  |  |

| 4.3 | Archit            | secture                                                     | 65 |  |  |

|     | 4.3.1             | Control Flow Integrity (CFI)                                | 67 |  |  |

|     | 4.3.2             | Software Integrity (SI)                                     | 69 |  |  |

|     | 4.3.3             | Control Flow Integrity with Software Integrity (CFI and SI) | 73 |  |  |

|     | 4.3.4             | Blocks with Multiple Predecessors                           | 75 |  |  |

|     | 4.3.5             | Support for blocks with single and multiple predecessors    | 76 |  |  |

|     | 4.3.6             | MAC Chaining                                                | 77 |  |  |

| 4.4 | Hardw             | vare implementation                                         | 78 |  |  |

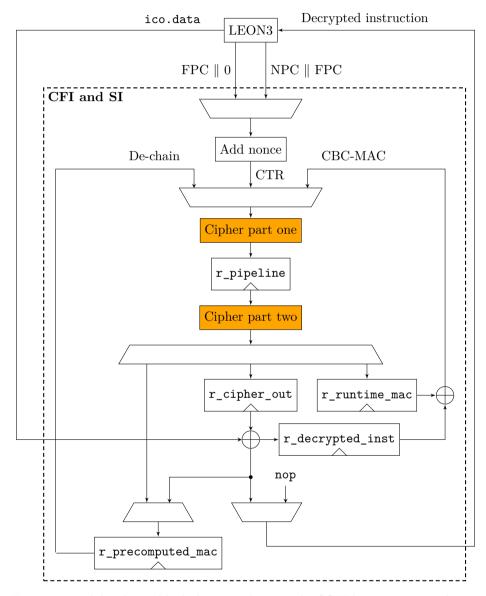

|     | 4.4.1             | Overview                                                    | 78 |  |  |

|     | 4.4.2             | Block cipher                                                | 79 |  |  |

|     | 4.4.3             | Hardware design                                             | 79 |  |  |

|     | 4.4.4             | Scheduling the Block Cipher                                 | 81 |  |  |

|     | 4.4.5             | Limitations                                                 | 83 |  |  |

| 4.5 | Softwa            | are Implementation                                          | 83 |  |  |

|     | 4.5.1             | Toolchain Design                                            | 84 |  |  |

|     | 4.5.2             | Toolchain Implementation                                    | 88 |  |  |

|     | 4.5.3             | Limitations                                                 | 92 |  |  |

| 4.6 | Evalua            | ation                                                       | 93 |  |  |

|     | 4.6.1             | Security Evaluation                                         | 93 |  |  |

|     | 4.6.2             | Hardware Evaluation                                         | 95 |  |  |

|     | 4.6.3             | Performance Evaluation                                      | 96 |  |  |

CONTENTS \_\_\_\_\_\_xi

|    |       | 4.6.4    | Practical feasibility in time constrained cyber physical systems | 98  |

|----|-------|----------|------------------------------------------------------------------|-----|

|    | 4.7   | Concl    | usion                                                            | 99  |

| 5  | SCN   | ∕I: Secu | ure Code Memory Architecture                                     | 101 |

|    | 5.1   | Introd   | luction                                                          | 102 |

|    | 5.2   | Proble   | em Statement                                                     | 103 |

|    |       | 5.2.1    | Threat Model                                                     | 103 |

|    |       | 5.2.2    | System Goal                                                      | 103 |

|    | 5.3   | SCM I    | Design                                                           | 104 |

|    |       | 5.3.1    | Conceptual Overview                                              | 104 |

|    |       | 5.3.2    | Architecture                                                     | 105 |

|    | 5.4   | Protot   | type Implementation                                              | 109 |

|    |       | 5.4.1    | Target Platform                                                  | 109 |

|    |       | 5.4.2    | Transactor                                                       | 110 |

|    |       | 5.4.3    | MAC Verification                                                 | 112 |

|    |       | 5.4.4    | Integrity Violations                                             | 113 |

|    | 5.5   | Evalua   | ation                                                            | 113 |

|    |       | 5.5.1    | Security Evaluation                                              | 113 |

|    |       | 5.5.2    | Hardware evaluation                                              | 113 |

|    |       | 5.5.3    | Performance Evaluation                                           | 113 |

|    | 5.6   | Concl    | usion                                                            | 114 |

| 6  | Con   | clusion  | s                                                                | 115 |

|    | 6.1   | Concl    | usions                                                           | 115 |

|    | 6.2   | Future   | e work                                                           | 117 |

| Bi | bliog | raphy    |                                                                  | 121 |

| xii                  | CONTENTS |

|----------------------|----------|

| Curriculum Vitae     | 133      |

| List of publications | 135      |

# **List of Figures**

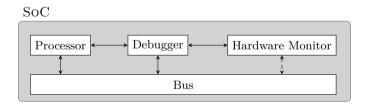

| 1.1 | A System-on-Chip (SoC) showing the security features proposed and analysed in this thesis                                                                                                                              | 4  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

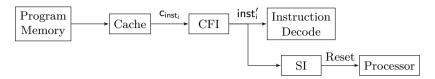

| 1.2 | A software flowchart for SOFIA and Secure Code Memory (SCM).                                                                                                                                                           | 5  |

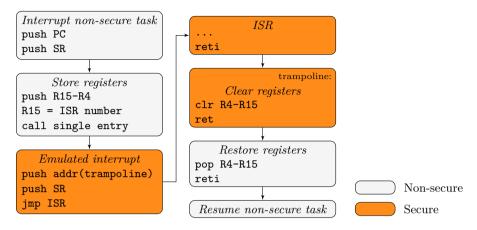

| 2.1 | The steps for invoking secure Interrupt Service Routines (ISRs) from the non-secure domain                                                                                                                             | 15 |

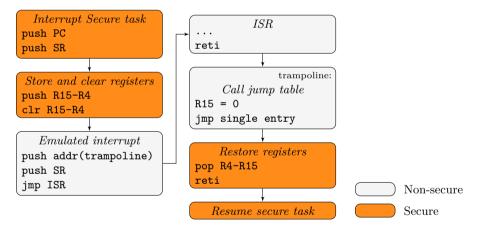

| 2.2 | The required steps for invoking non-secure Interrupt Service Routines (ISRs) from the secure domain                                                                                                                    | 16 |

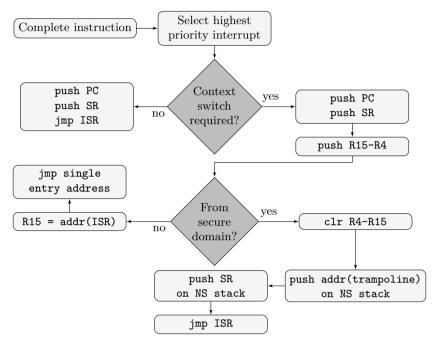

| 2.3 | Software-based flowchart for invoking a secure ISR from the non-secure domain                                                                                                                                          | 19 |

| 2.4 | Software-based flowchart for invoking a non-secure ISR from the secure domain                                                                                                                                          | 19 |

| 2.5 | The modified hardware-based interrupt logic                                                                                                                                                                            | 20 |

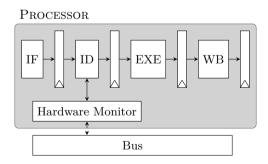

| 3.1 | The hardware monitor is integrated into the instruction pipeline of the processor. The pipeline stages are abbreviated as follows: Instruction Fetch (IF), Instruction Decode (ID), Execute (EXE), and Write Back (WB) | 32 |

| 3.2 | A CFI hardware monitor interfaces with the processor's debug port. In addition, a Memory-Mapped IO (MMIO) interface is nused by instrumented code to communicate with the hardware monitor.                            | 99 |

|     | monitor                                                                                                                                                                                                                | 33 |

xiv \_\_\_\_\_\_LIST OF FIGURES

| 4.1 | Overview of the design using Control Flow Integrity (CFI) and Software Integrity (SI)                                                                                                                                                                                                                                                                                                                                                                 | 66 |

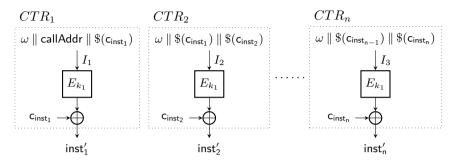

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

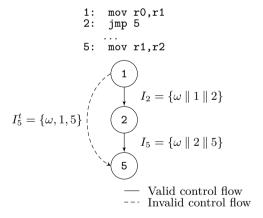

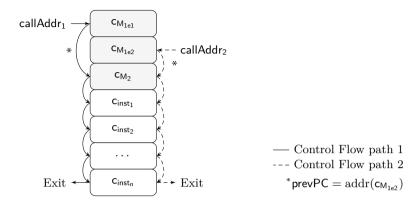

| 4.2 | Encrypted instructions $(c_{inst_n})$ are decrypted at runtime using dynamic control flow information consisting of the current and previous program counters (PC, and prevPC). Under the condition that control flow is untampered, PC = $\operatorname{addr}(c_{inst_i})$ , and $\operatorname{prevPC} = \operatorname{addr}(c_{inst_{i-1}})$ , or $\operatorname{prevPC} = \operatorname{callAddr}$ , with $\operatorname{callAddr}$ the call site | 68 |

| 4.3 | A Control Flow Graph (CFG) of a small program shows two different control flow paths from node 1 to node 5. If the valid control flow path is taken, all instructions are decrypted correctly. However, when the invalid control flow path is taken, instruction 5 is decrypted incorrectly                                                                                                                                                           | 68 |

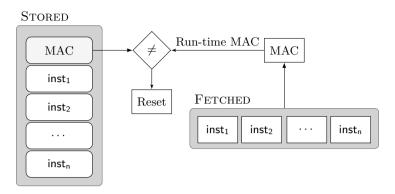

| 4.4 | The integrity of a program's instructions is verified at runtime by comparing the precomputed Message Authentication Code (MAC) with the run-time calculated MAC. If verification fails, the processor is reset to prevent tampered instructions from executing                                                                                                                                                                                       | 70 |

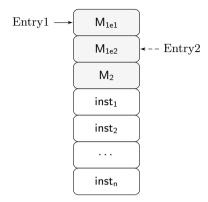

| 4.5 | The execution block consists of an $m$ -word precomputed MAC (M) and $n$ instructions. Control flow can only enter at M, and can only exit at $inst_n$ . Inside a block the control flows through each consecutive word                                                                                                                                                                                                                               | 70 |

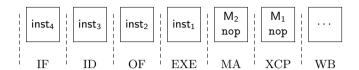

| 4.6 | The instructions in a four instruction execution block fit in the pipeline stages before the Memory Access (MA) stage. This allows the architecture to verify the integrity of the block before a memory access has been performed                                                                                                                                                                                                                    | 72 |

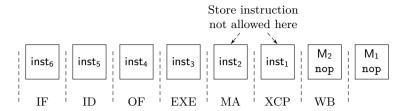

| 4.7 | The size of an execution block can be increased to six instructions if store instructions are restricted from $inst_1$ and $inst_2$                                                                                                                                                                                                                                                                                                                   | 73 |

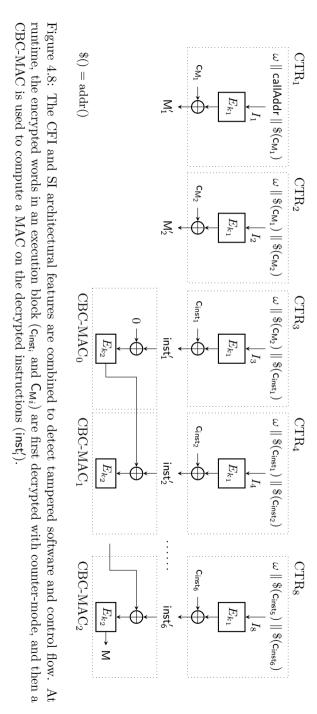

| 4.8 | The CFI and SI architectural features are combined to detect tampered software and control flow. At runtime, the encrypted words in an execution block $(c_{inst_i} \text{ and } C_{Mi})$ are first decrypted with counter-mode, and then a CBC-MAC is used to compute a MAC on the decrypted instructions $(inst'_i)$                                                                                                                                | 74 |

| 4.9 | The plaintext multiplexer block uses two copies of the first MAC word $M_1$ as its two entry points, which are respectively called $M_{1e1}$ and $M_{1e2}$                                                                                                                                                                                                                                                                                            | 75 |

LIST OF FIGURES \_\_\_\_\_\_xv

| 4.10 | The encrypted multiplexer block supports two entry points and has two unique control flow paths through the block                                                                                                                                                                                                                                                                                                            | 76   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

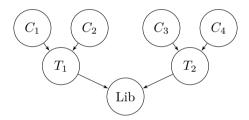

| 4.11 | A tree of multiplexer nodes is used to increase the number of call sites $(C_i)$ that can invoke a function                                                                                                                                                                                                                                                                                                                  | 76   |

| 4.12 | A hardware block diagram showing the SOFIA core integrated in the instruction pipeline stages of the LEON3                                                                                                                                                                                                                                                                                                                   | 80   |

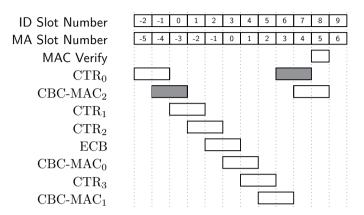

| 4.13 | A timing diagram of the block cipher operations to process a single execution block. $CTR_n$ indicates counter-mode decryption, ECB indicates MAC de-chaining, and CBC-MAC indicates part of the CBC-MAC computation. The execution block exists in slots zero to seven. Negative slot numbers indicate the previous block in the instruction pipeline. Gray blocks indicate cipher operations of the previous or next block | 82   |

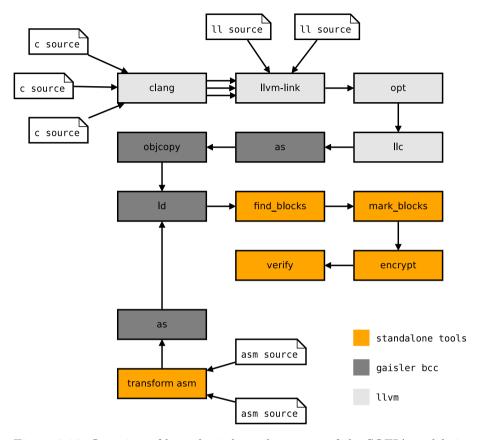

| 4.14 | Overview of how the independent parts of the SOFIA toolchain work together                                                                                                                                                                                                                                                                                                                                                   | 85   |

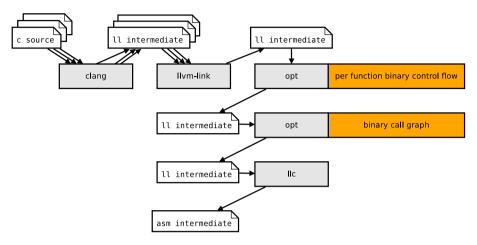

| 4.15 | Compiler Stage of the toolchain transforming C code to SPARC assembler code                                                                                                                                                                                                                                                                                                                                                  | 86   |

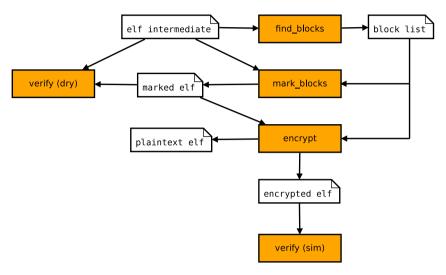

| 4.16 | The post-linkage part of the toolchain is responsible for identifying blocks, adjusting offsets, and finally encrypting each reachable block                                                                                                                                                                                                                                                                                 | 88   |

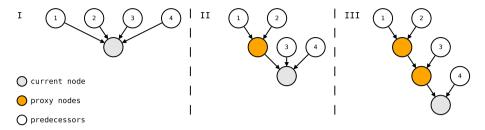

| 4.17 | Example of the iterative transformation ensuring a binary control flow graph. Proxy nodes are added until every node has at most two predecessors                                                                                                                                                                                                                                                                            | 89   |

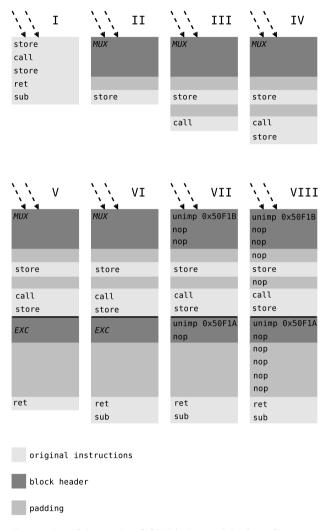

| 4.18 | Example of how the SOFIA basic block inflator transforms a sequence of assembler instructions to satisfy all low-level constraints. SPARC uses delayed branching, which means that the instruction after a branch is executed before the branch takes effect. Therefore, the ret instruction is placed on the second-to-last element in the memory block                                                                     | . 91 |

| 4.10 | A comparison of the cycle overhead of benchmarks running on a                                                                                                                                                                                                                                                                                                                                                                | . 91 |

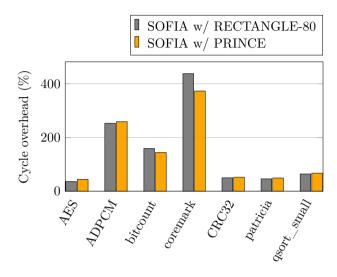

| 4.19 | SOFIA core compared to a stock LEON3 processor clocked at 92.3 MHz                                                                                                                                                                                                                                                                                                                                                           | 97   |

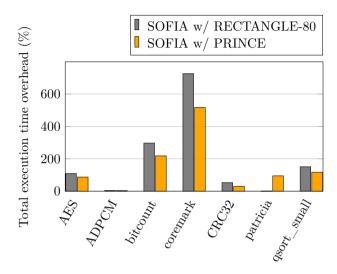

| 4.20 | A comparison of the total execution time overhead of benchmarks running on a SOFIA core compared to a stock LEON3 processor clocked at 92.3 MHz                                                                                                                                                                                                                                                                              | 98   |

xvi \_\_\_\_\_\_LIST OF FIGURES

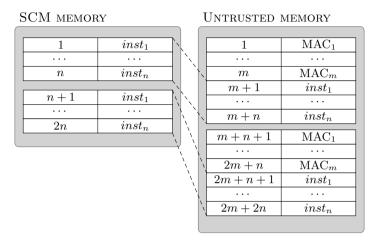

| 5.1 | Flow of code and data through system                             | 105 |

|-----|------------------------------------------------------------------|-----|

| 5.2 | Architectural overview of the system                             | 105 |

| 5.3 | Memory mapping between the SCM memory range and untrusted memory | 108 |

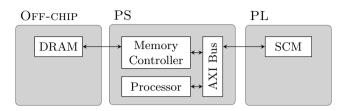

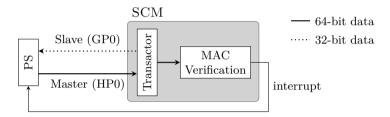

| 5.4 | System overview                                                  | 110 |

| 5.5 | The implemented architecture of SCM                              | 110 |

# **List of Tables**

| 2.1 | Access rights enforced by the memory protection unit                                                                                                                                                  | 12   |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.2 | A summary of the hardware costs for the different designs                                                                                                                                             | . 21 |

| 2.3 | Context switching cycle times for an interrupted task. The number of visible registers are indicated with $n.$                                                                                        | 22   |

| 3.1 | Overview of hardware-based CFI architectures                                                                                                                                                          | 56   |

| 3.2 | Performance and hardware overheads of the CFI architectures. All reported percentages are relative to the baseline performance of the target processor, while the non-percentages are absolute values | 60   |

| 4.1 | Architectural features vs. system model criteria                                                                                                                                                      | 66   |

| 4.2 | Hardware overhead of two block ciphers: RECTANGLE and PRINCE                                                                                                                                          | 79   |

| 4.3 | The hardware overhead of SOFIA                                                                                                                                                                        | 95   |

| 4.4 | A comparison of the code size of the benchmarks compiled for both a SOFIA core and for a stock LEON3 processor                                                                                        | 97   |

| 5.1 | Software banchmarks for SCM                                                                                                                                                                           | 111  |

## List of Abbreviations

**ASIC** Application-Specific Integrated Circuit

**BL** Branch Limitation

BR Branch Regulation

**CAM** Content-Addressable Memory

CFG Control Flow Graph

CFI Control Flow Integrity

**CPI** Code Pointer Integrity

CRA Code Reuse Attack

ELF Executable and Linkable Format

EXE Execute

**FIFO** First-In, First-Out

**FPGA** Field Programmable Gate Array

FSM Finite State Machine

**ID** Instruction Decode

IF Instruction Fetch

**IP** Intellectual Property

ISA Instruction Set Architecture

**ISRAND** Instruction Set Randomization

ISR Interrupt Service Routine

$\mathbf{IVT}$  Interrupt Vector Table

JOP Jump-Oriented Programming

LBR Last Branch Register

**LUT** Look-Up Table

MA Memory Access

MAC Message Authentication Code

MG Monitoring Graph

MMIO Memory-Mapped IO

**OF** Operand Fetch

**OS** Operating System

PC Program Counter

PL Programmable Logic

PMA Protected Module Architecture

**PS** Processing System

PT Processor Trace

**ROP** Return-Oriented Programming

**SCM** Secure Code Memory

SCS Shadow Call Stack

SI Software Integrity

SM Signature Modeling

SoC System-on-Chip

SR Status Register

TCB Trusted Computing Base

WB Write Back

XCP Exception

## Chapter 1

### Introduction

Computers play an important role in today's society and will continue to play an even greater role in the future. It is important to ensure that the software that runs on these computers perform the correct computations. Software should do what it is asked to do, and should not misbehave; e.g., by stealing information, by spying on the user, by delivering the wrong drug dosages, or by attacking other computers. Therefore, to ensure that computers behave as expected, security mechanisms are required by all classes of microprocessors: from small microcontrollers to large cloud-based servers.

Software programs are frequently deployed with bugs which makes them vulnerable to attack. A root cause of this problem can be attributed to the use of unsafe programming languages, which can introduce memory errors into programs. A *memory error* is a software bug caused by invalid pointer operations, use of uninitialised variables, and memory leaks. Memory errors occur due to the use of low-level languages, such as C and C++, which trade type safety and memory safety for performance. In contrast, *memory safe* languages aim to prevent arbitrary pointer arithmetic and provides runtime array bounds checks.

Memory errors are present in a surprisingly large amount of software, since memory unsafe languages are used by many systems, such as web browsers, embedded software, firmware, libraries, and Operating System (OS) kernels. In addition, this problem also exists in some unexpected places: (1) memory safe languages often rely on OS kernels and libraries written in memory unsafe languages, and (2) memory safe languages frequently use an interpreter which is written in a memory unsafe language.

2 \_\_\_\_\_\_ INTRODUCTION

#### 1.1 Defending against runtime attacks

In this thesis, we use the term *system* to refer to the collection of software and hardware components that are used inside a computing platform. We assume that the computing platform consists of a microprocessor, storage, and software that runs on the microprocessor.

Defending against the exploitation of existing software bugs is a difficult problem. Even though a significant effort has been made to design defences, some attack classes remain extremely difficult to defend against. Current security mechanisms are built into OSs, compilers, programming languages, and the underlying (hardware) architectures. However, the introduction of each new defence mechanism usually leads to the development of a new attack which circumvents it. This has led to an arms-race between attackers and defenders.

Page-based protection, such as  $W \oplus X$ , is a strong defence against code injection and code tampering, and is supported by most modern processors and OSs [1]. However,  $W \oplus X$  can be circumvented by  $Code\ Reuse\ Attacks\ (CRAs)$ , which do not require any code to be injected, but instead uses existing software for malicious purposes. To defend against CRAs,  $code\ randomization$  re-arranges the address space positions of key data and code areas of a process. This makes it more difficult to launch a CRA, since the location of the code is unknown to the attacker. However, this defence can be bypassed by a number of different approaches, including brute force or an information disclosure that allows for calculating the address of a randomised memory block. Therefore, CRAs still remain an important threat that is difficult to protect against.

Control flow is a term used to describe the order in which instructions are executed inside a program. The instructions in a program are executed sequentially, unless the processor runs into an instruction that changes the control flow, such as a branch instruction.

A Control Flow Graph (CFG), is a graph of the valid control flow inside a program, and is commonly used as a model of the valid control flow inside a well-behaved program. Each node in the CFG represents a basic block, which is a group of instructions where control flows sequentially from the first instruction to the last. Therefore, control can only flow into a basic block at the first instruction (e.g., through a branch targeting the first instruction in a basic block.), and control can only flow out of the basic block at the last instruction. This implies that only the last instruction in a basic block may induce a control flow change. In a CFG, forward edges are caused by jumps and calls, while backward edges are caused by returns. The CFG is typically generated by statically analysing the source code or the binary of a program.

THESIS OBJECTIVES \_\_\_\_\_\_\_ 3

Control Flow Integrity (CFI) is a security policy that prevents attackers from tampering with the control flow of a program. The observation is that a large number of attacks rely on hijacking the control flow in order to succeed. Therefore, by enforcing a strict control flow policy, CFI can prevent these control flow hijacking attacks. CFI architectures typically assume that the software being protected contains vulnerabilities which can be exploited by an attacker, and that it is the responsibility of the CFI architecture to detect abnormal control flow.

Software Integrity (SI) is a security policy that prevents the execution of tampered software on the processor. The goal is to prevent an attacker from executing malicious code (code injection / tampering). One approach is to verify the authenticity of code before execution. Another approach is to make use of access control to isolate software. This mechanism can also exist independently of an operating system.

A Protected Module Architecture (PMA) is a security mechanism that allows for the secure execution of sensitive code in an area that is isolated from other processes. It operates independently of the operating system, which allows it to provide strong isolation guarantees, even when the system is infected with malware. In addition, some PMAs provide support for remote attestation, which allows a third party to determine if a device is in a trusted state.

#### 1.2 Thesis objectives

The main objective of this thesis is to analyse and design security mechanisms that ensure that the software running on a computer processor is behaving correctly. We focus on developing new architectural security features for microprocessors. In other words, we aim to provide security from the processor itself, instead of doing so through the software. We study the modifications required to make the processor architecture support different security requirements. The focus is on small embedded processors, since they are easier to understand, use, and modify.

All the new security solutions proposed in this thesis are evaluated on an FPGA. This allows us to accurately determine the hardware cost, the performance overhead for interfacing with the hardware, the performance overhead of running the software on the modified processor, and the hardware area overhead. In contrast, many previous works rely on simulation-based evaluations, which only provides a functional evaluation, together with a rough estimate of the performance costs.

4 \_\_\_\_\_\_INTRODUCTION

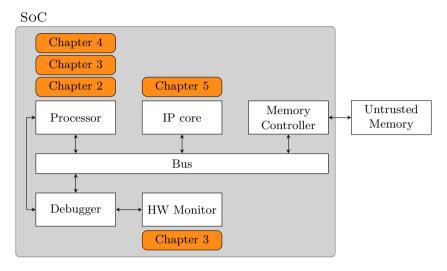

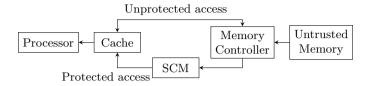

Figure 1.1: A System-on-Chip (SoC) showing the security features proposed and analysed in this thesis.

#### 1.3 Summary of Contributions

Figure 1.1 illustrates the contributions of this thesis by highlighting the location of the security mechanisms inside a typical System-on-Chip (SoC) architecture. In summary, the contributions of this thesis are as follows:

- An architecture to provide interrupt support for Protected Module Architectures (PMAs), which requires modifying the processor (Chapter 2).

- An analysis of existing hardware-based Control Flow Integrity (CFI) policies and architectures proposed by industry and academia, which require modifying either the processor or a hardware monitor connected to the processor's debug interface (Chapter 3).

- A novel hardware-based CFI architecture, called SOFIA, which uses cryptographic techniques to enforce CFI and SI. It is implemented as a processor core modification (Chapter 4).

- A novel hardware-based architecture, called Secure Code Memory (SCM), which enforces SI. SCM is a lightweight alternative to SOFIA with reduced functionality and is implemented as an IP core (Chapter 5).

THESIS STRUCTURE \_\_\_\_\_\_

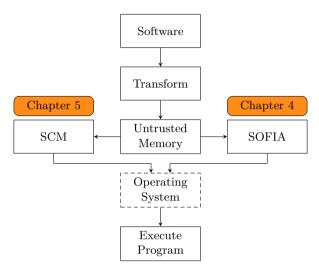

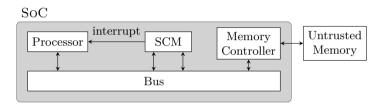

Figure 1.2: A software flowchart for SOFIA and SCM.

For SOFIA and SCM, we show a software flowchart in Figure 1.2. As a first step, a software transformation step is required, after which the transformed program is stored in untrusted memory. For SOFIA, we developed a toolchain to take care of the transformations, while for SCM we developed a scripted solution. All benchmarks were executed in baremetal, and as a future work, operating system support can be developed for these architectures.

#### 1.4 Thesis Structure

This section provides an outline of the thesis structure.

Chapter 2 - Towards Secure Interrupts on Low-End Microcontrollers In Chapter 2 we focus on the problem of providing interrupt support to a light-weight PMA. Three methods of securely handling interrupts are proposed, each exploring a different trade-off between hardware cost, software complexity, and interrupt latency.

The content of this chapter is based on [37].

Chapter 3 - Control Flow Integrity (CFI) Policies. In Chapter 3 we introduce the concept of Control Flow Integrity (CFI), which aims to detect abnormal program behaviour. We outline the recent history of attacks and countermeasures. We provide a detailed analysis and comparison of the security

6 \_\_\_\_\_\_ INTRODUCTION

policies used by 21 state-of-the-art hardware-based CFI architectures. The security policies and architectures are compared in terms of the security properties that they provide.

The content of this chapter is part of an article that is currently under review.

Chapter 4 - Instruction-Set Randomization as a CFI policy. In Chapter 4 we introduce a security architecture called SOFIA, which is the only known architecture that enforces a CFI policy based on instruction-set randomization. The architecture is capable of defending against a large number of attacks, including code injection, code reuse, and fault-based attacks on the program counter. The architecture was evaluated on an FPGA, and a custom compiler toolchain was developed to perform the extensive software transformations required by the architecture.

The content of this chapter is based on [35] which is an extended version of [33]

Chapter 5 - A light-weight Software Integrity policy. In Chapter 5 we present an architecture that addresses the issue of protecting the integrity of code and read-only data that is stored in memory. The architecture works as a standalone IP core inside a System-on-Chip (SoC), which is a novel approach to enforce a hardware-based security policy. The architecture is also flexible to select the parts of the software to be protected, which eases the integration of our solution with existing software.

The content of this chapter is based on [34].

**Chapter 6 - Conclusion.** Finally, Chapter 6 we summaries the main findings of this thesis together with opportunities for future research on related topics.

#### 1.5 Other Publications

In addition to the work published in this thesis, we worked on the following research publications which were not included in this thesis:

• In [38] we presented techniques to efficiently implement elliptic curve cryptography (ECC) on the ultra-low power ARM Cortex M0+. The paper proposed an improvement to the Lopez-Dahab field multiplication algorithm which reduces the number of memory accesses. This led to the fastest known ECC implementation on any ARM Cortex-M platform, together with the lowest energy requirement of any published microcontroller implementation with similar security parameters.

OTHER PUBLICATIONS \_\_\_\_\_\_\_ 7

[38] DE CLERCQ, R., UHSADEL, L., VAN HERREWEGE, A., AND VERBAUWHEDE, I. Ultra Low-Power Implementation of ECC on the ARM Cortex-M0+. In *Proceedings of the Design Automation Conference* (2014), DAC '14, ACM, pp. 112:1–112:6

- In [36] we presented techniques to make an efficient software implementation of a post-quantum secure public-key encryption scheme based on the ring-LWE problem on the ARM Cortex-M4F. We proposed optimization techniques for fast discrete Gaussian sampling and efficient polynomial multiplication. The implementation was faster than any other published ring-LWE implementation by a factor of 7, and faster than any known ECC implementation by at least one order of magnitude.

- [36] DE CLERCQ, R., ROY, S. S., VERCAUTEREN, F., AND VERBAUWHEDE, I. Efficient Software Implementation of ring-LWE Encryption. In *Proceedings of the Design, Automation & Test in Europe Conference & Exhibition* (2015), DATE '15, ACM, pp. 339–344

- The work in [54] proposed Soteria, which is an extension to Sancus, which provides protection of the intellectual property of code and data against powerful software attackers. The extension uses a toolchain to encrypt software IP, while at runtime a loader module decrypts the encrypted software into a software module. This ensures that code cannot leak to the outside world, while providing all the mechanisms to package and execute code.

- [54] GÖTZFRIED, J., MÜLLER, T., DE CLERCQ, R., MAENE, P., FREILING, F., AND VERBAUWHEDE, I. Soteria: Offline Software Protection Within Low-cost Embedded Devices. In *Proceedings of the Annual Computer Security Applications Conference* (2015), ACSAC 2015, ACM, pp. 241–250

- The work in [91,92] proposed new masking schemes to protect ring-LWE decryption against first-order side-channel attacks.

- [91] REPARAZ, O., DE CLERCQ, R., ROY, S. S., VERCAUTEREN, F., AND VERBAUWHEDE, I. Additively homomorphic ring-LWE masking. In *International Workshop on Post-Quantum Cryptography* (2016), Springer, pp. 233–244

- [92] REPARAZ, O., ROY, S. S., DE CLERCQ, R., VERCAUTEREN, F., AND VERBAUWHEDE, I. Masking ring-LWE. *Journal of Cryptographic Engineering* 6, 2 (2016), 139–153

3 \_\_\_\_\_\_ INTRODUCTION

• The work in [104] presents a coprocessor designed to offer hardware acceleration for a software-based VPN application. The open-source SigmaVPN application is used as the base solution, and a coprocessor is designed for the parts of Networking and Cryptography library (NaCl) which is used by SigmaVPN. The hardware-software codesign of this work is implemented on a Zynq-7000 SoC, which showed a 94% reduction in execution time for decrypting a 1024-byte Ethernet frame.

- [104] Turan, F., De Clercq, R., Maene, P., Reparaz, O., and Verbauwhede, I. Hardware Acceleration of a Software-based VPN. In *International Conference on Field Programmable Logic and Applications* (FPL) (2016), IEEE, pp. 1–9

- The work in [78] presents an analysis of the current state-of-the-art in hardware-based trusted computing architectures that provide isolation and attestation. It includes a definition of the common security properties offered by trusted computing architectures, and provides a detailed description of twelve hardware-based attestation and isolation architectures from academia and industry. In addition, the analysed architectures are compared with respect to their security properties and architectural features.

- [78] MAENE, P., GÖTZFRIED, J., DE CLERCQ, R., MULLER, T., FREILING, F., AND VERBAUWHEDE, I. Hardware-Based Trusted Computing Architectures for Isolation and Attestation. *IEEE Transactions on Computers PP(99)* (2017)

### Chapter 2

# Towards Secure Interrupts on Low-End Microcontrollers

#### CONTENT SOURCES

DE CLERCQ, R., SCHELLEKENS, D., PIESSENS, F., AND VERBAUWHEDE, I. Secure Interrupts on Low-End Microcontrollers. In *International Conference on Application-specific Systems, Architectures and Processors (ASAP)* (2014), IEEE, pp. 147–152

Contribution: Principle author together with Dries Schellekens.

Responsible for hardware and software designs.

#### 2.1 Introduction

Most modern trusted computing platforms ensure the secure execution of security-critical software by *isolating* an application from the rest of the processes running on the system. This allows for the correct execution of an application, even when the system is infected with malware. For an overview of hardware-based trusted computing platforms for isolation and attestation, which includes PMAs, the reader is referred to [78].

Currently, isolation is provided by two technologies found in high-end commercial processors, namely ARM TrustZone [10] and Intel SGX [84]. A TrustZone-capable processor contains two virtual processors, each with different privileges and a strictly controlled communication interface. Intel SGX processors provide

multiple protected domains, called enclaves, in which software can operate, free from external observation or modification of the code and data.

A number of works proposed hardware changes to enforce isolation on lowend processors. Kumar et al. designed a system that provides a number of protection domains within the address space [72]. Strackx et al. proposed a simple program counter based memory access control system to isolate software modules [98]. The SMART security architecture supports dynamic remote attestation with a software routine stored in immutable ROM [46]. The Sancus security architecture supports strong process isolation and hardware based remote attestation [87].

When we started this research, the related works applicable to low-end MCUs required their security functionality to execute uninterruptedly. For SMART this is a strict requirement, otherwise an attacker can move malware around during attestation to avoid detection [49]. Concurrent to our research, the TrustLite security architecture was developed, which provides hardware-enforced isolation of software modules with support for secure exception handling, and communication between protected modules [71]. At a later stage, Van Bulck et al. proposed extensions to a PMA to provide availability and real-time support for small microprocessors, which included an interrupt mechanism with a deterministic interrupt latency [106].

In this chapter, we provide a mechanism for handling interrupts for a program counter-based PMA which maintains the confidentiality of the protected module data. The proposed architecture allows *ISRs* to be located in either the secure or the non-secure domain of the processor. This makes it possible to use the processor for real-time processing, secure scheduling, and secure I/O, as tasks running in any security domain can be interrupted. We present a generic solution and compare the results of three implementation options.

The chapter is structured as follows. First, we present the general architecture of our security-enhanced processor, which is based on design principles of the related work [10,49,98]. Next, we describe a general scheme that can be used to allow secure interrupts. Subsequently, we discuss three implementations with different design trade-offs. Finally, we discuss our implementation results, and present the conclusion.

#### 2.2 Architecture

This section discusses the security architecture of the system. We first describe the attacker's capabilities, followed by a description of the security enhancements ARCHITECTURE \_\_\_\_\_\_\_ 11

for domain isolation and security domain switching.

#### 2.2.1 Attacker model

For the attacker model we assume that the adversary is capable of obtaining full control of the state of the software and data. This has the following implications. First, the attacker is capable of modifying any writable code, e.g., with a buffer overflow attack. Second, the attacker can read, and write to any memory region that is not explicitly protected by the processor. Third, the attacker may have compromised the underlying layer of software, e.g., the OS.

We also assume that the attacker is not capable of performing any hardwarebased attacks, including placing probes on the memory bus, performing a hard reset of the system, and inducing hardware faults.

#### 2.2.2 Domain isolation

The system is partitioned into two different domains, like in [10,46]: (1) the non-secure domain where regular activities occur, and (2) the secure domain where all processing of sensitive data occurs. If an operating system is present on the embedded device, it will typically reside in the non-secure domain; this system for instance contains a network stack or a real-time scheduler. Both the program memory and the data memory are partitioned into their respective secure and non-secure parts. For the sake of simplicity, we only consider a single secure domain, but our scheme can easily be extended to multiple secure domains [72,87,98].

The processor makes a distinction between the two domains depending on the Program Counter (PC). When the PC is in the address range of the secure program memory, the system is considered to be inside the secure domain. When the PC is in the address range of the normal program memory, then the system is considered to be in the normal domain.

We assume a low-end processor without a memory management unit (MMU) and hence no support for virtual memory. Instead a basic memory protection unit (MPU) is inserted between the processor and the memory. This unit enforces (1) program counter based access control [98] on both the data memory and the program memory, and (2) guards the entry into the secure domain by allowing only a single point of entry.

The program counter based access control feature ensures that only the normal program memory and data memory is accessible while the system is in the

|                   | Program M  | Iemory | Data Memory |                   |

|-------------------|------------|--------|-------------|-------------------|

|                   | non-secure | secure | non-secure  | $\mathbf{secure}$ |

| Secure domain     | rwx        | rwx    | rw-         | rw-               |

| Non-secure domain | rwx        | r-x*   | rw-         |                   |

Table 2.1: Access rights enforced by the memory protection unit.

normal domain. However, when the system is inside the secure domain, both the secure program memory and secure data memory also becomes accessible to the processor.

The single point of entry into the secure domain, from hereon referred to as the *single entry point*, is a mechanism that ensures that the secure domain can only be entered at a single address which is located in the secure program memory. Once the program counter has entered the secure program memory at this address, it is allowed to transition to any other address inside either the secure, or non-secure program memory. However, once the program counter points to an address that lies outside of the secure program memory, the secure domain can only be entered again via the single entry point. This feature ensures that secure code cannot be (ab)used to extract secure data from the secure domain. In Return-Oriented Programming (ROP) an attacker selectively executes chunks of program memory, which makes the program misbehave [95]. This could lead to unintended information leaks from the secure domain. The hardware enforcement of the single entry point guards against ROP attacks launched from outside a protected module.

The enforced access control is shown in Table 2.1. The secure data memory is inaccessible when the processor is in the non-secure domain. Furthermore, the non-secure domain only has read access to the secure program memory, except for its first address. This memory address has execute permission, and acts as the only entry point to the secure domain.

In order to expose multiple functions from the secure domain to the non-secure domain, a *jump table* is used, as also proposed in [72,87]. The identifier of a specific function is stored in a register before jumping to the single entry point. The code at the single entry point then jumps to the correct function based on the identifier passed inside the register.

<sup>\*</sup>Execute access only available on the single point of entry

SECURE INTERRUPTS \_\_\_\_\_\_\_13

#### 2.2.3 Context switching between domains

We define a *domain switch* as a transition from one security domain to another. Context switches within a domain (e.g., multithreading, user/kernel mode switching) are not considered in this work.

Two type of context switches can be distinguished. The first type are instructions that alter the program counter, including the call instruction, a return from a call with the ret instruction, a return from interrupt (reti), or with the jmp instruction. The second type are hardware events such as interrupts, processor exceptions or a reset.

The memory protection unit enforces the isolated memory regions of the two security domains. However, these domains still share the same set of registers. Therefore, special care is needed such that information does not leak through registers. Consequently, the general-purpose registers need to be cleared before a domain switch to the non-secure domain.

A stack frame is typically used to pass parameters, store return addresses, and for local data storage. A processor maintains a *stack pointer* that points to the top of the stack. In our solution, each domain has its own stack, which is located in its data memory address space, and a dedicated stack pointer register. The processor switches between the two registers depending on the security domain. We chose this option for the sake of simplifying domain switches, and providing better performance. An alternative method, which is used in [87], is to perform stack pointer switching in software by storing pointers to the top of each stack in fixed data memory addresses; this solution requires only a single hardware register.

### 2.3 Secure Interrupts

This section discusses the scheme for handling secure interrupts. We first describe a typical interrupt mechanism of low-end processors and then present a modified scheme for supporting interrupts with multiple security domains.

### 2.3.1 Standard interrupt mechanism

An interrupt is a signal generated by hardware or software to indicate to the processor an event that needs immediate attention (e.g., timer, peripheral device, etc.).

Each interrupt can have its own unique Interrupt Service Routine (ISR). The addresses of the ISRs are stored in the Interrupt Vector Table (IVT), which is located at a specific program memory address.

When an interrupt occurs, the following steps are generally performed: (1) the currently executing instruction is completed, (2) the PC that points to the next instruction (which we call the resume point), is stored on the stack, (3) the Status Register (SR) (which contains the status flag bits, e.g., zero, carry, and overflow) is pushed on the stack, (4) the interrupt with the highest priority is selected if multiple interrupts occurred during the last instruction, (5) the SR is cleared and further interrupts are disabled, and (6) the address stored in the IVT is loaded into the PC, causing a jump to the ISR. When the ISR is finished, it resumes the interrupted task with the reti instruction. This instruction restores the SR and PC from the stack to continue execution at the point where it was interrupted.

Some processor architectures support *nested interrupt*. In this case, interrupts can be re-enabled inside an ISR, causing any interrupt that occurs inside this ISR to interrupt the routine, regardless of its priority.

### 2.3.2 Domain isolation support

We have extended the processor with the notion of isolated protection domains. As mentioned above, it is crucial that no information leakage occurs during a domain switch from the secure to non-secure domain. With instruction based domain switching, the content of registers is cleared in software just before the transition occurs. However, this strategy cannot easily be applied with an interrupt based domain switch.

There are three main design challenges. First, a hardware interrupt can occur at any point during execution. This implies that there are four possible scenarios: (1) a non-secure task is interrupted by a non-secure ISR, (2) a secure task by a secure ISR, (3) a non-secure task by a secure ISR, and (4) a secure task by a non-secure ISR. The first two are trivial to handle, as no domain switch is required; however, the latter two require a domain switch.

Second, it should be possible for the software to choose whether to resume the interrupted task, or to execute another task. This allows for the scheduling of secure/non-secure tasks, as will be explained in Section 2.3.5.

Finally, the scheme must still comply with the hardware restricted entry into the secure domain. The ISR is unaware whether it is interrupting a secure or non-secure task. Normally it will resume execution with the reti instruction.

SECURE INTERRUPTS \_\_\_\_\_\_\_\_ 15

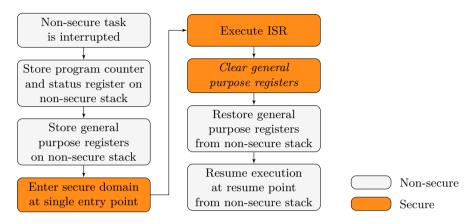

Figure 2.1: The steps for invoking secure Interrupt Service Routines (ISRs) from the non-secure domain.

However, this instruction cannot be used to directly perform a domain switch into the secure domain, as it would invalidate the single entry policy. If this restriction was not in place, then it could lead to an attacker circumventing the single entry policy by pushing a secure domain address onto the stack, followed by issuing a reti.

### 2.3.3 Interrupting non-secure task with secure ISR

In this scenario, an ISR that resides in secure program memory, is invoked from within the non-secure domain. Here we propose to handle this scenario with the scheme shown in Figure 2.1. The secure domain is entered at the single entry point. We propose to solve the problem of invoking the secure ISR from the non-secure domain by adding an entry to the single entry jump table (Section 2.2.2) for each secure ISR. Each entry is responsible for invoking a different ISR. The general-purpose registers should be cleared before a domain switch from the secure domain to the non-secure domain. However, the transition into the secure domain does not require the general-purpose registers to be cleared, because they do not contain any secrets.

### 2.3.4 Interrupting secure task with non-secure ISR

In this scenario, an ISR that resides in non-secure program memory, is invoked from the secure domain. Here we propose to handle this scenario with the

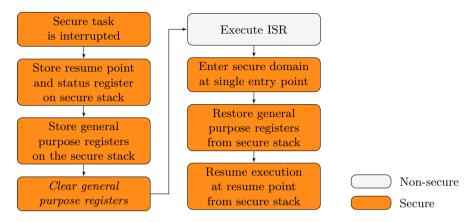

Figure 2.2: The required steps for invoking non-secure Interrupt Service Routines (ISRs) from the secure domain.

scheme shown in Figure 2.2. A domain switch from the secure domain to the non-secure domain is required. Therefore, the general-purpose registers need to be cleared before switching to the non-secure domain. We propose to solve the problem of resuming the interrupted secure task from the non-secure domain, by adding an entry into the single entry jump table (Section 2.2.2) to resume execution at the resume point.

### 2.3.5 Scheduling

Processors often have real-time operating requirements where scheduling of tasks are essential. When using a preemptive scheduler, interrupts are generated with a hardware timer, to transfer control back to the scheduler. The scheduler then selects the next task to execute, or resume, based on a ranking system. The mechanism that allows for interrupting a secure task with a non-secure ISR also enables preemptive scheduling.

A secure scheduler, as described in [83], enables the on-schedule execution of critical tasks that are running on a partially compromised system. This type of scheduler prevents components under the attacker's control from changing the execution times of other applications. The scheduler is kept isolated from the rest of the software by placing it inside the secure domain. When an application is preempted or an exception occurs, control is transferred to the scheduler which resumes execution of the pending applications. Therefore, the mechanism that allows for interrupting a non-secure task with a secure ISR also enables secure scheduling.

### 2.4 Implementation

This section presents the implementations that were made in order to demonstrate the feasibility of our proposed scheme. First, we describe the architecture of the processor that we extended with security features. Afterwards, we present three prototype implementations with different design goals, and different design trade-offs in terms of cycles, area, and code size.

#### 2.4.1 MSP430

Our implementation is based on the low-cost, low-power TI MSP430 microcontroller. It features a 16-bit von Neumann processor, and a single 16-bit address space for program and data memory. It has no external memory bus, and the amount of on-chip memory is limited to 16 kB RAM and 256 kB flash memory. It has eleven general-purpose registers (R4-R15), with R0-R3 serving as a program counter, stack pointer, status register, and constant generator.

Most interrupts on the MSP430 architecture are maskable, and can therefore only cause an interrupt when they are enabled, and if the general interrupt enable bit is set inside the status register.

A multiplexer is used to select between the normal stack pointer and the secure stack pointer, depending primarily on the value of the program counter.

One of the design problems we faced, was that ISRs have a return control flow that depends on the domain that the ISR was invoked from. We decided that each ISR should use the same return mechanism, regardless of the domain it is invoked from. We solve this by invoking all ISRs that require a domain switch in a special manner, which we call an *emulated interrupt*. Instructions are used to emulate what the hardware does when an interrupt occurs, by pushing the SR and the address of a *return trampoline* onto the stack, followed by a jump to the ISR. The invoked ISR executes, and returns with a reti. Since the address of the return trampoline is still on the stack, the reti will invoke the return trampoline.

### 2.4.2 Software-based implementation

The goal of the software-based implementation is to use the minimum amount of hardware features. We opted to make use of a different IVT for each security domain. Since the ISRs have control flows that depend on the current security domain, the idea is that each IVT will serve as the starting point for each of these control flows.

An IVT is normally populated with the addresses of ISRs, each associated with a different interrupt. As we now have an IVT for each security domain, we populate it with (1) the addresses of ISRs that exist in the same security domain as the IVT, and (2) the addresses of software routines that will initiate the control flow to invoke ISRs located in the other security domain.

The second IVT, which we refer to as the *secure IVT*, is stored at a fixed address in secure program memory. A hardware feature selects between IVTs, depending on the current security domain.

Upon entering the secure domain at the single point of entry, the value stored in R15 is used to determine which function in the jump table to execute.

#### Interrupting a non-secure task with a secure ISR

The steps for interrupting a non-secure task with a secure ISR is shown in Figure 2.3. When an interrupt occurs, the resume point is stored on the non-secure stack. Afterwards, the general-purpose registers are stored on the non-secure stack, and a call is made to the entry in the single entry jump table that corresponds to the current ISR. Next, the secure ISR is invoked with an emulated interrupt. The reti instruction inside the ISR returns from the emulated interrupt, after which the general-purpose registers are cleared, followed by returning (ret) from the call, which causes a transition back to the normal domain. Next, the registers are restored from the non-secure stack, and the resume point is used to jump to the point where execution was interrupted.

#### Interrupting a secure task with a non-secure ISR

The steps for interrupting a secure task with a non-secure ISR is shown in Figure 2.4. When an interrupt occurs, the resume point is stored on the secure stack. Afterwards, the general-purpose registers are stored on the secure stack, the registers are cleared, and the non-secure ISR is invoked by means of an emulated interrupt. The reti instruction inside the ISR returns from the emulated interrupt, after which a zero is stored in R15, and a jump is made to the single entry point. The value of zero in R15 corresponds to a jump table entry that is responsible for restoring all registers from the secure stack, and using the resume point to jump to the point where execution was interrupted.

Figure 2.3: Software-based flowchart for invoking a secure ISR from the non-secure domain.

Figure 2.4: Software-based flowchart for invoking a non-secure ISR from the secure domain.

### 2.4.3 Hardware-based implementation

The goal for the hardware-based implementation is to minimize interrupt latency by adding more functionality to hardware. As a further goal we try to minimize the amount of additional hardware. The architecture of this implementation is very similar to the software-based implementation (Section 2.4.2), with the exception of the following: (1) a single IVT is used, and (2) the clearing, storing, and restoring of general-purpose registers is now done in hardware.

Figure 2.5: The modified hardware-based interrupt logic.

A single IVT is used to store the addresses of the ISRs that can be located in either domain. The extended interrupt logic, shown in Figure 2.5, takes care of any additional processing that needs to be done if a domain switch is required to invoke an ISR.

Figure 2.1 and Figure 2.2 show that both schemes require: (1) saving the general-purpose registers to the stack, and (2) restoring the general-purpose registers from the stack after domain switching back to the interrupted task's domain. We propose to solve (1) by further extending the interrupt logic to save the general-purpose registers on the stack before performing the domain switch to the other domain. We further propose to solve (2) by introducing a new instruction that restores all registers from the current stack.

### 2.4.4 Hidden registers optimization

We also propose a performance optimization to improve interrupt latency. For this optimization, the number of visible registers inside the ISR is restricted to n. This improves interrupt latency because less registers need to be cleared, saved

EVALUATION \_\_\_\_\_\_ 21

| Design                    | LUTs | Registers |

|---------------------------|------|-----------|

| Unmodified                | 2231 | 1185      |

| Software-based            | 2241 | 1187      |

| Hardware-based            | 2417 | 1219      |

| HW-based Hidden registers | 2420 | 1220      |

Table 2.2: A summary of the hardware costs for the different designs.

and restored from the stack, but without the hardware cost of using shadow registers. To ensure that the remaining 11 - n general-purpose registers do not leak any information, all read and write operations on the remaining registers will be blocked. The compiler/programmer needs to ensure that only the visible n registers are used in the ISR, as the remaining registers are unusable.

This optimization can be done on either the hardware-based architecture (Section 2.4.3), or the software-based architecture (Section 2.4.2), and will require the following features to be activated when inside a domain switched ISR: (1) the saving and restoring of the general-purpose registers on the stack is limited to only n registers, and (2) the register file is modified to disable read and write access on the remaining registers.

### 2.5 Evaluation

This section presents our results, together with a discussion on the limitations of this work.

#### 2.5.1 Results

We extended the openMSP430 [2] softcore to create our prototype implementations. This softcore is fully compatible with the TI MSP430 microcont, roller, and executes code generated by any MSP430 toolchain in a near cycle-accurate way. The openMSP430 softcore was configured to use the following settings: a 10 MHz clock, 4 kB of data memory, 8 kB of program memory, a hardware multiplier, and a single timer. We used the Digilent Atlys, Spartan-6 LX45 based FPGA development board to test our prototype.

Table 2.2 shows the number of 6-input Look-Up Tables (LUTs), and registers for the unmodified openMSP430, and the three different designs. The synthesis optimization goal was set to "area".

| Table 2.3:   | Context    | switching   | $\operatorname{cycle}$ | ${\rm times}$ | for | an | interrupted | task. | The | number |

|--------------|------------|-------------|------------------------|---------------|-----|----|-------------|-------|-----|--------|

| of visible r | egisters a | are indicat | ed wi                  | th $n$ .      |     |    |             |       |     |        |

| Context switch    | $\mathbf{SW}$ | HW     |

|-------------------|---------------|--------|

| Interrupt S to NS | 71            | 9+n    |

| Return NS to S    | 43            | 14+n   |

| Interrupt NS to S | 54            | 13+n   |

| Return S to NS    | 52            | 10 + n |

| Interrupt *       | 6             | 6      |

| Return *          | 5             | 5      |

|                   |               |        |

<sup>\*</sup> No domain switch occurs here.