## Università di Pisa

Corso di Laurea Magistrale in Ingegneria Elettronica

Tesi di Laurea Magistrale

# Security in automotive microcontrollers of next generation

| Candidato: | Giorgio Boccini | Relatori: | Prof. Ing. Luca Fanucci  |

|------------|-----------------|-----------|--------------------------|

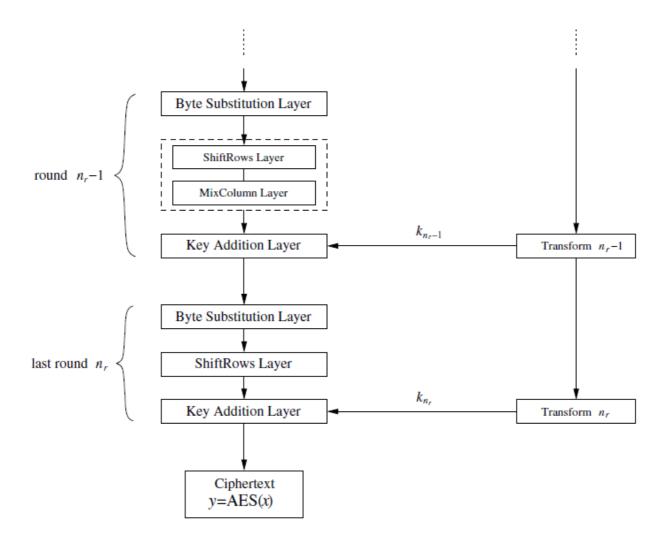

|            |                 |           |                          |

|            |                 |           | Ing. Massimiliano Donati |

|            |                 |           |                          |

Anno accademico 2013/2014

## Summary

| Chapter 1 Introduction                                       | 5            |

|--------------------------------------------------------------|--------------|

| Chapter 2 Security                                           | 7            |

| 2.1 Information security                                     | 8            |

| 2.2 IT security                                              | 9            |

| 2.3 Embedded security                                        | 11           |

| 2.3.1 Embedded Security vs. General IT Security              | 11           |

| 2.3.2 Cryptographic Algorithms in Constraint Environments.   | 12           |

| 2.3.3 Physical Security: Side Channel Attacks and Reverse En | gineering13  |

| 2.3.4 Digital Rights Management (DRM)                        | 13           |

| 2.4 Automotive Applications and IT Security                  | 14           |

| Chapter 3 Automotive Security                                | 18           |

| 3.1 Experimental Security Analysis of a Modern Automobile    | 18           |

| 3.2 Comprehensive Experimental Analyses of Automotive Attac  | k Surfaces26 |

| Chapter 4 State of art                                       | 32           |

| 4.1 Evolution of the standard solutions                      | 32           |

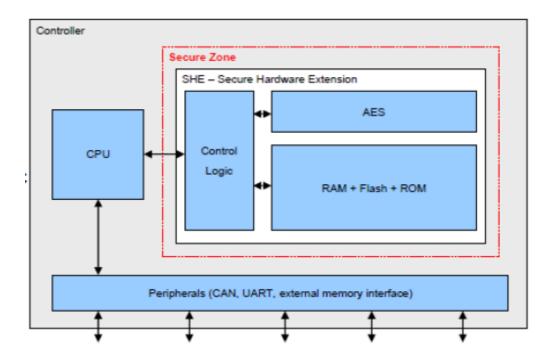

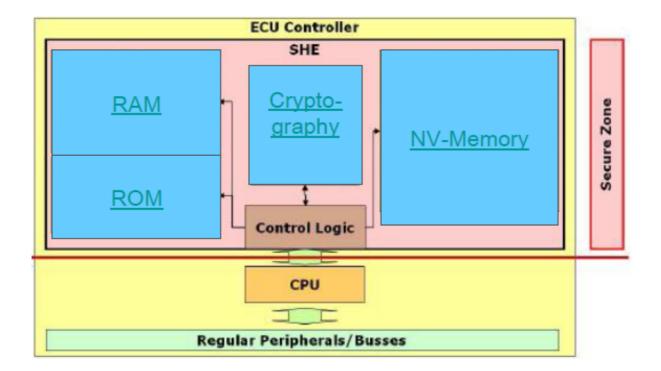

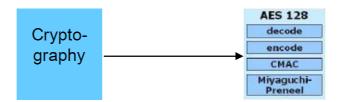

| 4.1.1 SHE                                                    | 32           |

| 4.1.2 Project EVITA                                          | 37           |

| 4.2 Comparison table                                         | 70           |

| Chapter 5 CAN protocol                                       | 73           |

| 5.1 Basic Concepts                                           | 73           |

| 5.1.1 Layered Structure of a CAN Node                        | 74           |

| 5.1.2 Frame Structure                                        | 75           |

| 5.2 CAN security features                                    | 77           |

| 5.3 Analysis of the security level requested                 | 79           |

| Chapter 6 Advance Encryption Standard                        | 82           |

| 6.1 Introduction                                             | 82           |

| 6.2 Overview of the AES Algorithm                            | 84           |

| 6.3 Some Mathematics: A Brief Introduction to Galois Fields | 87  |

|-------------------------------------------------------------|-----|

| 6.3.1 Existence of Finite Fields                            | 87  |

| 6.3.2 Prime Fields                                          | 88  |

| 6.3.3 Extension Fields GF (2 <sup>m</sup> )                 | 90  |

| 6.3.4 Addition and Subtraction in GF (2 <sup>m</sup> )      | 91  |

| 6.3.5 Multiplication in GF(2 <sup>m</sup> )                 | 92  |

| 6.3.6 Inversion in GF (2 <sup>m</sup> )                     | 94  |

| 6.4 Internal Structure of AES                               | 95  |

| 6.4.1 Byte Substitution Layer                               | 96  |

| 6.4.2 Diffusion Layer                                       | 99  |

| 6.4.3 Key Addition Layer                                    | 101 |

| 6.4.4 Key Schedule                                          | 101 |

| 6.4.5 Decryption                                            | 104 |

| Chapter 7 AES-128 HW Implementation                         | 109 |

| 7.1 System Verilog model                                    | 109 |

| 7.2 Hardware module                                         | 110 |

| 7.2.1 Overview                                              | 110 |

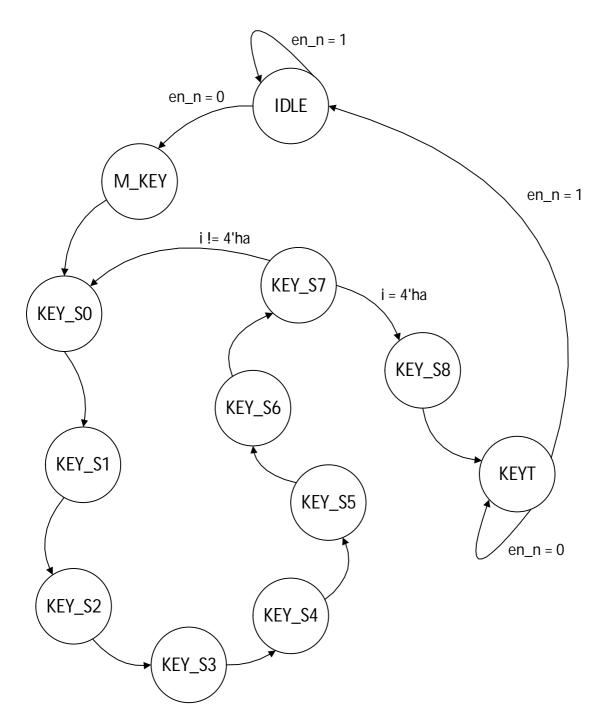

| 7.2.2 key_schedule module                                   | 111 |

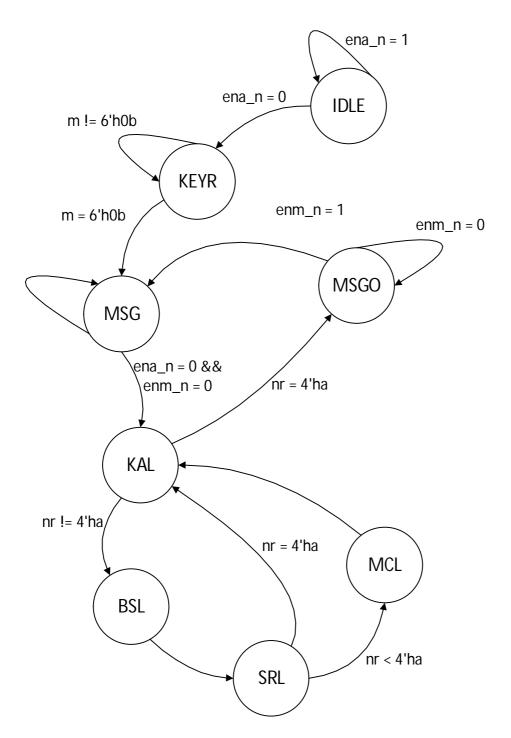

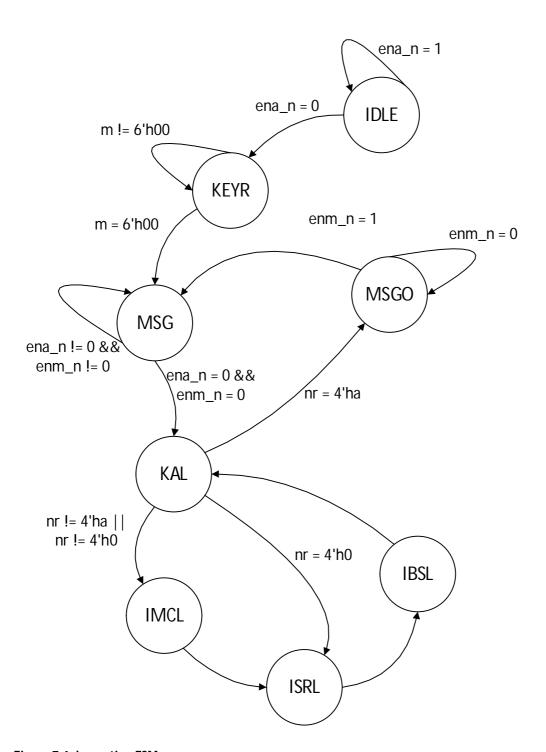

| 7.2.3 Encryption/Decryption module                          | 113 |

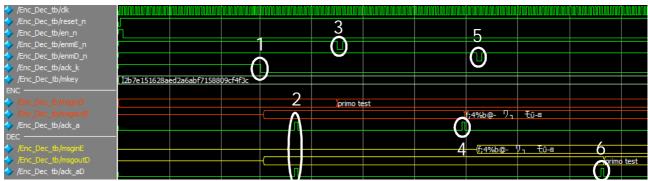

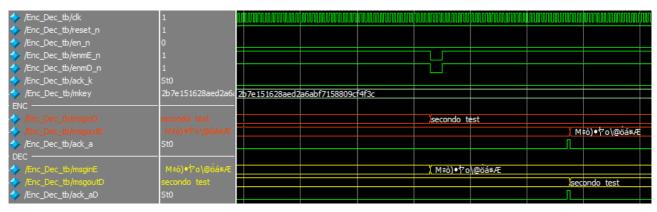

| 7.3 Functional simulations                                  | 116 |

| 7.4 Synthesis                                               | 118 |

| 7.4.1 Version 1                                             | 118 |

| 7.4.2 Version 2                                             | 120 |

| 7.5 Conclusion                                              | 122 |

| Appendix                                                    | 123 |

| System Verilog model                                        | 123 |

| System Verilog test bench                                   | 134 |

| Verilog module (version 1 encryption only)                  | 139 |

| Verilog module Top level (version 1)                        | 151 |

| ٧   | /erilog module (version 2 encryption only) | . 152 | 2 |

|-----|--------------------------------------------|-------|---|

| ٧   | /erilog simple direct test bench           | .161  | ı |

| Bib | oliography                                 | .163  | 3 |

## Chapter 1

## Introduction

This thesis deals with the implementation of a hardware security module that will be used to ensure the privacy in a bus communication in the automotive environment. This activity is born in collaboration with the RENESAS Electronics, an industry that produces automotive components and more else. The issues addressed are continually developing and they will be incorporated in the in the next generation of automotive microcontrollers. The security in the automotive environment is an emerging problem and today does not exist a standard solution to solve this problem, for this reason this thesis activity start with a search on the state of the art of the automotive microcontrollers, to understand the various solutions on the market. Afterwards, following the RENESA's directives the activity continues with a deep study of the embedded security and specifically, on the security in a CAN to CAN bus communications. The scope of this study is the realization of a hardware module, to be inserted in an existing CAN IP, which ensure the privacy aspect.

In detail, the thesis is organized as follows:

- Chapter 2, **Security**. Issues on security in computer systems have been known for a decade. After a brief summary of the concepts of security, we will see, as the embedded security is different under many aspects to the well-known security in computer systems.

- Chapter 3, **Automotive security**. The Automotive security is a particular field of application of the more general embedded security that we have just introduced in the previous chapter. This chapter answers to an important question: how did the issue of security bear in the automotive environment?

- Chapter 4, **State of art.** After the two previous chapters we have a good background in automotive security, we can understand the choices made by other companies about security in their microcontroller automotive, and then we can draw a good state of the art.

- Chapter 5, **CAN protocol**. The themes covered so far are general, and they forms a good starting point to understand the security problem in the automotive environment, if we want to narrow down the security problem to the communication bus CAN, we need a fast review of the relative standard to understand its weakness regard the security.

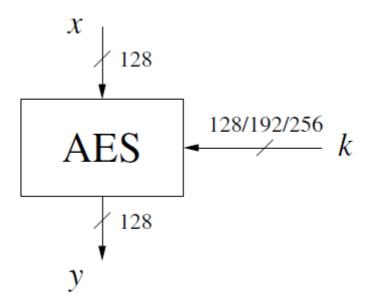

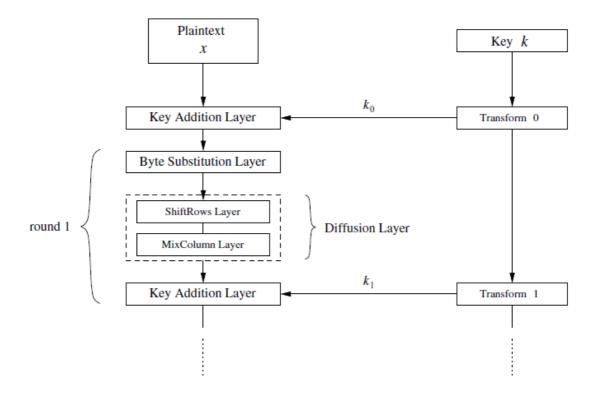

- Chapter 6, **Advance Encryption Standard**. As will be clearer in the following, to ensure the privacy in our environment we need to use the cryptography and in particular the AES (Advance

Encryption Standard), to implement as best we can this algorithm in hardware, we need a good knowledge of the relative standard.

- Chapter 7, **AES-128 HW Implementation**. Finally, we will see two hardware implementation of the AES-128 algorithm that they could be a starting point to a feasibility study for the introduction of the privacy aspect in an existing bus communication IP.

- Appendix, models (System Verilog) and code (Verilog) developed.

## **Chapter 2**

## Security

Since the early days of writing, politicians, diplomats and military commanders understood that it was necessary to provide some mechanism to protect the confidentiality of correspondence and to have some means of detecting tampering. Julius Caesar is credited with the invention of the Caesar cipher ca. 50 B.C., which was created in order to prevent his secret messages from being read should a message fall into the wrong hands, but for the most part protection was achieved through the application of procedural handling controls. Sensitive information was marked up to indicate that it should be protected and transported by trusted persons, guarded and stored in a secure environment or strong box. As postal services expanded, governments created official organisations to intercept, decipher, read and reseal letters (e.g. the UK Secret Office and Deciphering Branch in 1653).

In the mid-19th century, more complex classification systems were developed to allow governments to manage their information according to the degree of sensitivity. The British Government codified this, to some extent, with the publication of the Official Secrets Act in 1889. By the time of the First World War, multi-tier classification systems were used to communicate information to and from various fronts, which encouraged greater use of code making and breaking sections in diplomatic and military headquarters. In the United Kingdom, this led to the creation of the Government Code and Cypher School in 1919. Encoding became more sophisticated between the wars as machines were employed to scramble and unscramble information. The volume of information shared by the Allied countries during the Second World War necessitated formal alignment of classification systems and procedural controls. An arcane range of markings evolved to indicate who could handle documents (usually officers rather than men) and where they should be stored as increasingly complex safes and storage facilities were developed. Procedures evolved to ensure documents were destroyed properly and it was the failure to follow these procedures, which led to some of the greatest intelligence coups of the war (e.g. U-570).

The end of the 20th century and early years of the 21st century saw rapid advancements in telecommunications, computing hardware and software, and data encryption. The availability of smaller, more powerful and less expensive computing equipment made electronic data processing within the reach of small business and the home user. These computers quickly became interconnected through the Internet.

The rapid growth and widespread use of electronic data processing and electronic business conducted through the Internet, along with numerous occurrences of international terrorism, fuelled the need for better methods of protecting the computers and the information they store, process and transmit. The academic disciplines of computer security and information assurance emerged along with numerous professional organizations – all sharing the common goals of ensuring the security and reliability of information systems.

## 2.1 Information security

Information security, sometimes shortened to InfoSec, is the practice of defending information from unauthorized access, use, disclosure, disruption, modification, perusal, inspection, recording or destruction. It is a general term that can be used regardless of the form the data may take (electronic, physical, etc...)

Two major aspects of information security are:

- 1. IT security: Sometimes referred to as computer security, Information Technology Security is information security applied to technology (most often some form of computer system). It is worthwhile to note that a computer does not necessarily mean a home desktop. A computer is any device with a processor and some memory (even a calculator). IT security specialists are almost always found in any major enterprise/establishment due to the nature and value of the data within larger businesses. They are responsible for keeping all of the technology within the company secure from malicious cyber-attacks that often attempt to breach into critical private information or gain control of the internal systems.

- 2. Information assurance: The act of ensuring that data is not lost when critical issues arise. These issues include but are not limited to natural disasters, computer/server malfunction, physical theft, or any other instance where data has the potential of being lost. Since most information is stored on computers in their modern era, information assurance is typically dealt with by IT security specialists. One of the most common methods of providing information assurance is to have an off-site backup of the data in case one of the mentioned issues arise.

## 2.2 IT security

IT security has gained central importance for many new automotive applications and services. On the production side, we observe that the cost for electronics and IT is approaching the 50% threshold of all manufacturing costs. Perhaps more importantly, there are estimates that already today more than 90% of all vehicle innovations are centered around software and hardware (admittedly not only digital hardware, though). IT systems in cars can roughly be classified into three main areas:

- Basic car functions, e.g., engine control, steering, and braking.

- Secondary car functions, e.g., window control and immobilizers.

- Infotainment applications, e.g., navigation systems, music and video entertainment, and location-based services.

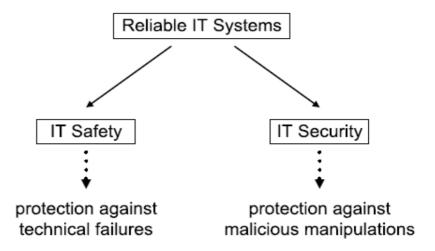

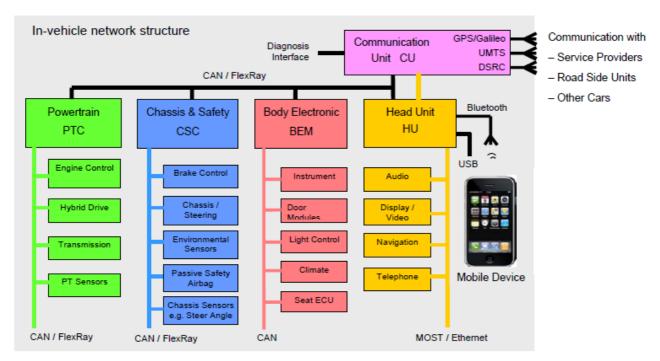

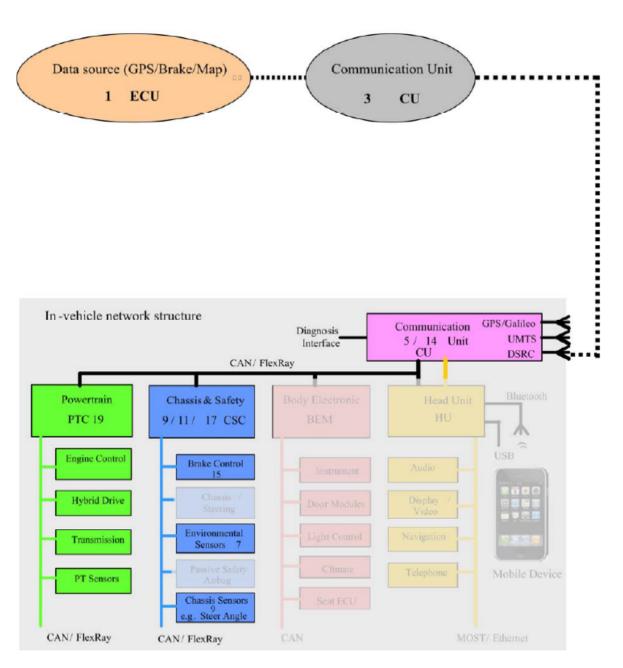

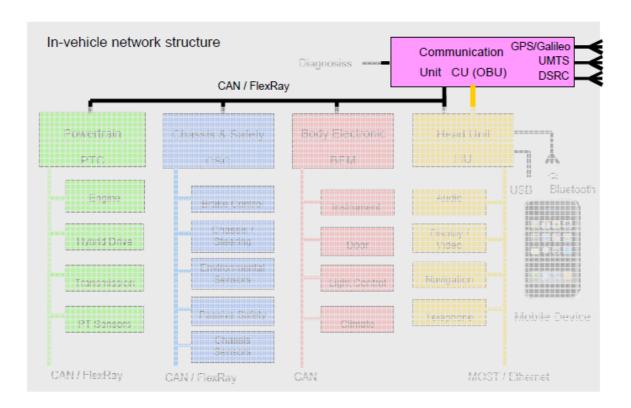

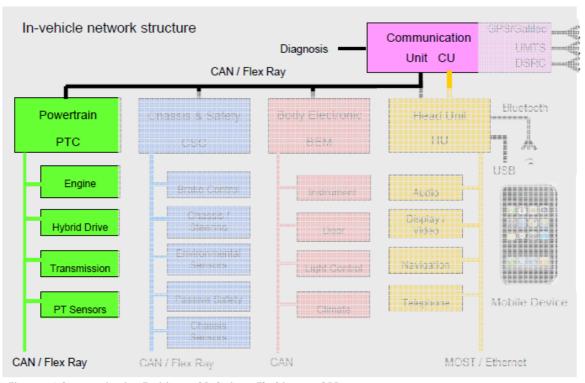

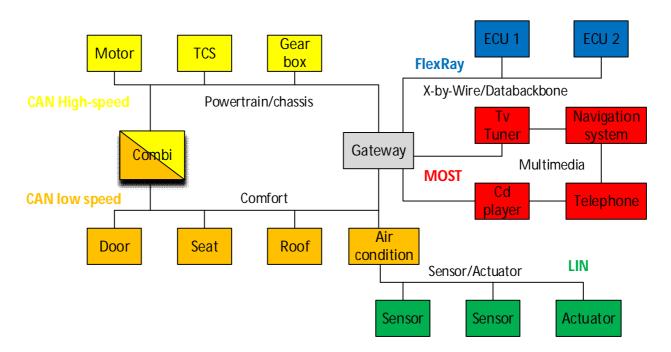

Almost all such applications are realized as embedded systems, that is, as devices, which incorporate a microprocessor. The devices range from simple control units based on an 8-bit micro controllers to infotainment systems equipped with high-end processors whose computing power approaches that of current PCs. The number of processors can be 80 or more in high-end cars. In a typical automobile, the devices are connected by several separate buses. Not surprisingly, many classical IT and software technologies are already well established within the automotive industry, for instance hardware-software co-design, software engineering, software component re-use, and software safety. However, one aspect of modern IT systems has hardly been addressed in the context of automotive applications: IT security. Security is concerned with protection against the manipulation of IT systems by humans. The difference between IT safety and security is depicted in Fig 2.1

Figure 2.1: The relationship between IT safety and security

Software and hardware safety is a relatively well-established (if not necessarily well-understood) field in the automotive industry, IT security, on the other hand, is just beginning to emerge as a proper sub-

discipline within the field of automotive IT. Of course, there have been niche applications in the automotive domain, especially concerned with electronic immobilizers that have always relied on security technologies. However, the vast majority of software and hardware systems in current cars are not equipped with security functionality. This is not entirely surprising for two reasons:

- 1. Many past car IT systems did not need security functions as there was very little incentive for malicious manipulation in traditional applications.

- 2. Security tends to be an afterthought in any IT system. Achieving the core function, i.e., getting a telematic system working or enabling remote software updates is the primary goal of every system designer and implementer.

A prime example of such an IT-system is the Internet, which is only, from few years after some decades of existence, being equipped with rudimentary security functions.

The situation has changed dramatically with respect to the first argument given above. Already today, there is a multitude of quite different car sub-systems that are in desperate need for strong security functions in order to protect the driver, the manufacturer and the component supplier. Current examples of car functions with need for security include the large field of software updates, also known as "flashing" or "chip tuning". Future cars will become even more dependent on IT security due to the following developments:

- It is predicted that an increasing number of ECUs (electronic control units) will be reprogrammable, a process that must be protected.

- Many cars will communicate with the environment in a wireless fashion, which makes strong security a necessity.

- New business models (e.g., time-limited flash images or pay-per-use infotainment content) will become possible for the car industry, but will only be successful if abuse can be prevented.

- There will be an increasing number of legislative demands, which can only be solved by means

of modern IT security functions, such as tamper resistant tachographs, secure emergency call

functions, secure road billing etc.

- Increasing networking of cars will allow the collection of data for each driver (e.g., driving behaviour, locations visited), which will put high demands on privacy technology.

- Future cars will often be personalized, which requires a secure identification of the driver.

- Electronic anti-theft measures will go beyond current immobilizers, e.g., by protecting individual components.

As we can see from the, not necessarily complete, list in the previous page, IT security will be an important topic for many future car technologies. For some future applications, such as business models based on Digital Rights Management, IT security will even play the role of an enabling technology.

We would like to stress at this point that almost all target platforms with in cars, which will incorporate security functions, are embedded systems, rather than classical PC-style computers. Hence, the technologies needed for securing car applications belong often, but not always, to the field of embedded security. The difference between embedded security vs. general IT security will be discussed in more detail afterwards.

## 2.3 Embedded security

## 2.3.1Embedded Security vs. General IT Security

Since the late 1990s embedded security, sometimes also referred to as security engineering or cryptographic engineering, has emerged as a proper sub discipline within the security and cryptography communities. Embedded security is often quite different from the security problems encountered in computer networks such as LANs or the Internet. For such classical networks, there exist established and relatively mature security solutions, e.g., firewalls, encryption software, and intrusion detection systems. The topics with which embedded security deals are, generally speaking, closer related to the underlying software and hardware of the target device, which is to be protected. Arguably, the most important event at which embedded security technologies are treated from a scientific viewpoint is the CHES (Cryptographic Hardware and Embedded Systems) Workshop, which started in 1999. Even though there are certainly many aspects of security that are shared by embedded devices and general computers, there are a number of key differences:

- First, embedded devices tend to have small processors (often 8-bit or 16-bit micro-controllers)

which are limited with respect to computational capabilities, memory, and power consumption.

Modern PCs, on the other hand, are very powerful and in most cases do not limit the use of

cryptographic functions.

- Second, potential attackers of embedded systems have often access to the target device itself, e.g., an attack of a smart card only makes sense if one actually has physical control over the smart card. On the other hand, attacks against traditional computer networks are almost always performed remotely.

- Third, embedded systems are often relatively cheap and cost sensitive because they often involve high-volume products, which are priced competitively. Thus, adding complex and costly

security solutions is not acceptable. By comparing typical prices (e.g., a laptop vs. an ECU) one easily notices a ratio of 1–2 orders of magnitude which, of course, limits the costs that can be spent on security for embedded solutions.

## 2.3.2Cryptographic Algorithms in Constraint Environments

Even though security depends on much more than just cryptographic algorithms - a robust overall security design including secure protocols and organizational measures are needed as well - crypto schemes are in most cases the atomic building blocks of a security solution. The problem in embedded applications is that they tend to be computationally and memory constrained due to cost reasons. (Often they are also power limited, but since automotive applications are often powered by their own battery, low-power crypto is not such an important topic in the car context.) It is now the task of the embedded security engineer to implement secure crypto algorithms on small devices at acceptable running times. Crypto schemes are divided into two families: symmetric and asymmetric algorithms. The first group is mainly used for data encryption and message integrity checks. Symmetric algorithms tend to run relatively fast and often need little memory resources. There exists a wealth of established algorithms, with the most prominent representatives being the block ciphers DES (Data Encryption Standard) and AES (Advanced Encryption Standard.) The family of stream ciphers can be even more efficient than block ciphers and are, thus, sometimes preferred for embedded applications. In almost all cases, it is a wise choice to use established, proven algorithms rather than unproven or self-developed ones. More on the state-of-the-art of symmetric algorithms will be said in the contribution Fundamentals of Symmetric Cryptography of this volume. The second family of schemes, asymmetric or public-key algorithms, are very different. They are based on hard number theoretical problems and involve complex mathematical computations with very long numbers, commonly in the range of 160–4048 bits, depending on the algorithm and security level. Their advantage, however, is that they offer advanced functions such as digital signatures and key distribution over unsecure channels. For common automotive applications such as secure flashing, public-key algorithms are often preferred. The problem here is the computational requirement of public key schemes. Embedded processors in the automotive domain are often only equipped with 8-bit and 16-bit processors clocked at moderate frequencies of, say, below 10 MHz Running computationally expensive public-key algorithms on such processors can result in unacceptably long execution times, for instance several seconds for the generation of a digital signature. For this reason, it is very important that a smart parameter choice together with the latest implementation techniques are being employed.

## 2.3.3Physical Security: Side Channel Attacks and Reverse Engineering

A central tool for providing security are cryptographic algorithms. Both symmetric and asymmetric algorithms are based on the fact that the protected device (e.g., tachograph, an ECU, or an infotainment device) is equipped with a secret cryptographic key. "Secret" means in this context also that it can not be read out by an attacker. If an attacker obtains knowledge of the key, the device can usually be manipulated and/or cloned. Many of the potential attackers – which includes in particular the owner and maintenance personnel – have physical access to the device. One family of attacks which attempt to recover the key from the device are side channel attacks, which were first proposed in the open literature in 1996. Side channel attacks observe the power consumption, the timing behaviour or the electromagnetic radiation of an embedded device. These signals are recorded while the cryptographic algorithm with the secret key is executed. The attacker then tries to extract the key by means of signal processing techniques. Side channel attacks are a serious threat in the real world unless special countermeasures have been implemented.

A related family of attacks are fault injection attacks, sometimes referred to as active side channel attacks. Fault injection attacks force the device to malfunction, for instance by spikes in the power supply, through overclocking, or through overheating of the embedded device. The goal is often to create an incorrect output of the cryptographic algorithm, which leaks information about the key used. Quite different from side channel and fault injection attacks are reverse engineering attacks. The goal here is to read the cryptographic keys directly from the RAM, EEPROM, FlashROM, or ROM of the embedded device.

Unlike classical reverse engineering of code it is in this context sometimes sufficient to recover a single cryptographic key for a successful attack, which is often only 16 bytes long or less. Of course, there is tamper-resistant memory available but it is for automotive systems often not available for cost or legacy reasons.

### 2.3.4Digital Rights Management (DRM)

DRM has become a very important technology for applications such as audio and film distribution over the Internet. DRM systems can enforce rules such as the time period for which access to a music file is granted or to which device a digital movie is allowed to be copied. It is perhaps a bit surprising that DRM should become important for vehicles as well. However, as soon as digital data used for car applications represent financial values, e.g., flash software, digital location-based services or entertainment content, DRM will be the technology that enforces the envisioned use of the data. DRM technologies are required

to prevent the customer from unauthorized copying or an unauthorized extension of the usage period of the content. In order to realize a proper DRM platform in a vehicle, we need trusted computing functions, which in turn are based on physical secure components such as secure memory, true random number generators and cryptographic algorithms.

## 2.4 Automotive Applications and IT Security

As sketched above, embedded IT security will be a crucial part of many future automotive features. IT security offers a wide variety of functions that can improve products. In the context of embedded automotive systems, the advantages of strong IT security can be summarized in two main categories.

- Increased reliability: Innovative IT applications must be protected against targeted manipulations. For instance, manipulation of an otherwise robust electronic engine control system may result in an unreliable engine (e.g., shortened engine life span). Another example is a highly fault tolerant telematic system. Manipulation of messages to and from the car, however, may result in a very unreliable system. IT security can prevent those and many other abuses. It is important to stress that from this viewpoint security can also be interpreted as being part of reliability.

- New business models: Cars equipped with state-of-the-art IT technology will open up opportunities for a multitude of new business models. In times where international competition is putting increasing pressure on car manufacturers, novel IT-based business models are tempting options. Examples include fee-based software updates, navigation data, location-based services and multimedia content. It is of crucial importance to stress that virtually all such business models rely heavily on strong IT security.

Admittedly, this is a rather broad classification. In the following, we will list more concrete application domains within cars that rely heavily on IT security.

Software Updates. In the last few years, the topic of software updates of ECUs (electronic control units) has gained crucial importance. The reasons why ECUs that can be updated are attractive are multitude, and a few important ones are given in the following: many software bugs are only found after shipment of the car; cars can be configured differently for different customers, reducing the variety of cars that have to be manufactured; features can be activated based on a pricing policy. Unfortunately, unauthorized software updates can pose an equal number of problems for manufactures and, to a lesser degree, for owners. For instance, it is obviously quite attractive to activate certain car features (e.g., a stronger engine or comfort functions) without paying the associated fees. This cannot only result in financial losses due to missed business transactions, but also in an increase of warranty cases. In order

to enable software update in a manner controlled by the manufacturer, one needs embedded security technologies such as digital signature, tamper-resistant hardware and encryption.

Theft Prevention. The electronic immobilizer is possibly the oldest incarnation of IT security mechanisms in the automotive. The latest generation of immobilizer has been quite a success, with the damage from car thefts reduced by 50% over the last decade or so. This proves that classical IT security (here: strong cryptographic identification) can have an immediate benefit in today's world. It is very tempting to generalize immobilizer solutions to car components. By using strong cryptography, one could identify valuable or crucial components and, thus, protect against illegal exchange of components, and enforce the usage of original manufacturer spare parts. The techniques required from embedded security are identification protocols and tamper resistance.

Business Models for Infotainment Content. It seems almost certain that the majority of future cars will be equipped with powerful infotainment devices in the dashboard. The functionality of the infotainment systems will be a fusion of

- Home entertainment (e.g., radio, music and video for the rear seats),

- Telecommunication (e.g., cell phone and email function),

- Car-specific information systems (e.g., navigation data, smart traffic routing, emergency calls).

There will be opportunities for content providers, car manufacturers and possibly for other parties to create innovative business models around the digital content mentioned above. There are already systems in use today, which provide navigation data on a time-limited basis. Another indication for the opportunities ahead is that after the 2004 more than 50% of all mini vans sold in the USA were equipped with rear seat video screens. Adding new business models, for instance fee-based video downloads at hot spots, seems not entirely unrealistic.

The topic of security plays a crucial role here. It should be noted that there is a built-in incentive for users (i.e., business partners!) to behave dishonestly, e.g., by copying content in an unauthorized manner or by using content beyond the paid-for period. This situation is similar to the hotly debated topic of content distribution via the Internet. In order to prevent abuse and, thus, to enable new business models, strong embedded security technologies are needed. First, communication security (i.e., protection of the link between car and the environment) is needed in order to transport valuable digital content to the customer. Second, digital rights management (DRM) technologies are required to prevent the customer from unauthorized copying or an unauthorized extension of the usage period of the content. Third, privacy-preventing technology will be required in order to limit the collection of customer data. Without the latter measure, user acceptance of new technologies can quickly diminish. Finally, secure hardware components are required in order to prevent manipulation of the IT security mechanisms and demolishing the business model.

Personalization of Cars. Car functions that can be updated open up a wide variety of new possibilities such as personalization of car features, from your favourite radio station and seat position to your favourite suspension setting. There is a multitude of options for realizing a recognition of the driver.

One class of approaches is token-based, e.g., through car keys, smart cards, or cell phones. Other approaches make use of biometrics, e.g., fingerprint recognition.

Another class simply requires active user input in order to communicate the person's identity to the vehicle. Again, we will need security technologies here in order to prevent abuse. Technologies needed included identification techniques, biometrics and tamper resistance hardware.

Access Control for Car Data. Already today, many cars are equipped with event data recorders. This can be as simple as tachograph data, or more advanced systems, which record a wide variety of information about the car subsystems and driving behaviour. Currently, such data can usually only be accessed via diagnosis interfaces which have to be attached physically to the car. Furthermore, today many vehicles can be equipped with wireless interfaces such as Bluetooth or GSM. It becomes crucial now to tightly control access to both technical data about the car and stored information about driving behaviour. Relevant security functions are authentication and identification protocols and communication security.

Anonymity. Cars filled with IT systems offer several possibilities for violating driver's privacy rights. The above-mentioned recording of driving behaviour is one example. Navigation data used or requests for other location based services (e.g., the purchase of certain navigation data, requests for the nearest gas station or requests for the nearest restaurant) is another example.

It is also imaginable that even traffic violations, e.g., driving beyond the allowed speed limit, are recorded. These can all be serious threats in an information society and it will be crucial to prevent abuses by incorporating technologies such as access control and anonymization.

Legal Obligations. Already today, there are several regulations that dictate the inclusion of IT security functions in cars. An example is Toll Collect, the German road toll system or the European tachograph.

In the future, there will be more applications, which require IT, security due to legal regulations. Possible examples include emergency call systems, immobilizers or other theft control measures, and event data recorders.

We do not claim that the listing above is complete. However, we can believe that embedded security is already an important technology for a host of diverse car functions, and its impact will increase in the future. In summary, it can be claimed that IT security will play the role of an enabling technology for numerous future car applications.

After this brief introduction, the motivations that stay behind the security in the automotive environment should be clearer.

Slowly, the various automotive companies, started to insert the "security" in their product, but the real push came from an article, Experimental Security Analysis of a Modern Automobile. To evaluate the importance of this article we will see briefly its contents in the next chapter.

## **Chapter 3**

## **Automotive Security**

## 3.1 Experimental Security Analysis of a Modern Automobile

Their studies focus on what an attacker could do to a car if she was able to maliciously communicate on the car's internal network thus they haven't done a full analysis of the modern automobile's attack surface.

However, we can distinguish roughly two type of vectors by which one might gain access to a car's internal networks:

Car's internal networks.

The first is physical access. Someone—such as a mechanic, a valet, a person who rents a car, an ex-friend, a disgruntled family member, or the car owner—can, with even momentary access to the vehicle, insert a malicious component into a car's internal network via the ubiquitous OBD-II port (typically under the dash). The attacker may leave the malicious component permanently attached to the car's internal network or, he may use a brief period of connectivity to embed the malware within the car's existing components and then disconnect. A similar entry point is presented by counterfeit or malicious components entering the vehicle parts supply chain—either before the vehicle is sent to the dealer, or with a car owner's purchase of an aftermarket third-party component (such as a counterfeit FM radio).

The other vector is via the numerous wireless interfaces implemented in the modern automobile. In their car, we can identify no fewer than five kinds of digital radio interfaces accepting outside input, some over only a short range and others over indefinite distance.

Their experimental analyses focus on two 2009 automobiles of the same make and model, and they selected those vehicles because they contained both a large number of electronically controlled components (necessitated by complex safety features such as anti-lock brakes and stability control) and a sophisticated telematics system. They purchased two vehicles to allow differential testing and to validate that their results were not tied to one individual vehicle. They also purchased individual replacement ECUs via third-party dealers to allow additional testing.

| Component  | Functionality                                                                                                                                                                                           | Low-Speed<br>Comm. Bus | High-Speed<br>Comm. Bus |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------|

| ECM        | Engine Control Module  Controls the engine using information from sensors to determine the amount of fuel, ignition timing, and other engine parameters.                                                |                        | ✓                       |

| EBCM       | Electronic Brake Control Module Controls the Antilock Brake System (ABS) pump motor and valves, preventing brakes from locking up and skidding by regulating hydraulic pressure.                        |                        | ✓                       |

| TCM        | Transmission Control Module  Controls electronic transmission using data from sensors and from the ECM to determine when and how to change gears.                                                       |                        | ✓                       |

| BCM        | Body Control Module  Controls various vehicle functions, provides information to occupants, and acts as a firewall between the two subnets.                                                             | ✓                      | ✓                       |

| Telematics | Telematics Module Enables remote data communication with the vehicle via cellular link.                                                                                                                 | ✓                      | ✓                       |

| RCDLR      | Remote Control Door Lock Receiver Receives the signal from the car's key fob to lock/unlock the doors and the trunk. It also receives data wirelessly from the Tire Pressure Monitoring System sensors. | ✓                      |                         |

| HVAC       | Heating, Ventilation, Air Conditioning Controls cabin environment.                                                                                                                                      | ✓                      |                         |

| SDM        | Inflatable Restraint Sensing and Diagnostic Module Controls airbags and seat belt pretensioners.                                                                                                        | ✓                      |                         |

| IPC/DIC    | Instrument Panel Cluster/Driver Information Center Displays information to the driver about speed, fuel level, and various alerts about the car's status.                                               | ✓                      |                         |

| Radio      | Radio In addition to regular radio functions, funnels and generates most of the incabin sounds (beeps, buzzes, chimes).                                                                                 | ✓                      |                         |

| TDM        | Theft Deterrent Module Prevents vehicle from starting without a legitimate key.                                                                                                                         | ✓                      |                         |

Table 3.1 lists some of the most important ECUs in their car

How we can see from the table 3.1the various ECU have a different type of bus and two separate physical layers—a high-speed bus which is differentially-signalled and primarily used by powertrain systems and a low-speed bus (SAE J2411) using a single wire and supporting less-demanding components. When necessary, a gateway bridge can route selected data between the two buses.

Before experimentally evaluating the security of individual car components, they assessed the security properties of the communication bus inside the car.

There are a variety of protocols that can be implemented on the vehicle bus, but for example, starting in 2008 all cars sold in the U.S. are required to implement the Controller Area Network (CAN) bus (ISO 11898) for diagnostics. As a result, CAN—roughly speaking, a link-layer data protocol—has become the dominant communication network for in-car networks (e.g., used by BMW, Ford, GM, Honda, and Volkswagen).

The underlying CAN protocol (and the others link-layer data protocol like Ethernet) has a number of inherent weaknesses that are common to any implementation. Key among these:

Broadcast Nature. Since CAN packets are both physically and logically broadcast to all nodes, a malicious component on the network can easily snoop on all communications or send packets to any other node on the network. To facilitate their experimental analysis, they wrote CARSHARK, a custom CAN bus analyser and packet injection tool. CARSHARK allowed them to observe and reverse-engineer packets, as well as to inject new packets to induce various actions.

Fragility to DoS. The CAN protocol is extremely vulnerable to denial-of-service attacks. In addition to simple packet flooding attacks, CAN's priority-based arbitration scheme allows a node to assert a "dominant" state on the bus indefinitely and cause all other CAN nodes to back off. While most controllers have logic to avoid accidentally breaking, the network this way, adversarially controlled hardware would not need to exercise such precautions.

No Authenticator Fields. CAN packets contain no authenticator fields—or even any source identifier fields—meaning that any component can indistinguishably send a packet to any other component. This means that any single compromised component can be used to control all of the other components on that bus, provided those components themselves do not implement defences.

Weak Access Control. The protocol standards for their car specify a challenge-response sequence to protect ECUs against certain actions without authorization. A given ECU may participate in zero, one, or two challenge-response pairs:

- Reflashing and memory protection. One challenge response pair restricts access to reflashing the ECU and reading out sensitive memory. By design, a service shop might authenticate with this challenge-response pair in order to upgrade the firmware on an ECU.

- Tester capabilities. Modern automobiles are complex and thus diagnosing their problems requires significant support. Thus, a major use of the CAN bus is in providing diagnostic access to service technicians. In particular, external test equipment (the "tester") must be able to interrogate the internal state of the car's components and, at times, manipulate this state as well.

Now we see the various type of attacks that they done at the cars under test.

Disabling Communications. For example, the standard states that, ECUs should reject the "disable CAN communications" command when it is unsafe to accept and act on it, such as when a car is moving. However, they experimentally verified that this is not actually the case in their car: they were able to disable communications to and from all the ECUs in Table 3.1 even with the car's wheels moving at speed on jack stands and while driving on the closed road course.

Reflashing ECUs While Driving. The standard also states that ECUs should reject reflashing events if they deem them unsafe. In fact, it states: "The engine control module should reject a request to initiate a programming event if the engine were running." However, they experimentally verified that they could place the Engine Control Module (ECM) and Transmission Control Module (TCM) into reflashing mode when their car was at speed on jack stands. When the ECM enters this mode, the engine stops running. They also verified that they could place the ECM into reflashing mode while driving on the closed course.

Noncompliant Access Control: Firmware and Memory. The standard states that ECUs with emissions, anti-theft, or safety functionality must be protected by a challenge response access control protocol even disregarding the weakness of this protocol, they found it was implemented less broadly than they would have expected. They verified experimentally that they can load their own code onto their car's telematics unit without authenticating, and the Device Control keys for the ECM and TCM just by authenticating with the reflashing key. They were also able to extract the telematics units' entire memory, including their keys, without authentication.

Noncompliant Access Control: Device Overrides. Recall that the Device Control service is used to override the state of components. However, ECUs are expected to reject unsafe Device Control override requests, such as releasing the brakes when the car is in motion. Some of these unsafe overrides are needed for testing during the manufacturing process, so those can be enabled by authenticating with the Device Control key. However, they found during the experiments that certain unsafe device control operations succeeded without authenticating.

Imperfect Network Segregation. The standard implicitly defines the high-speed network as more trusted than the low-speed network. This difference is likely due to the fact that the high-speed network includes the real-time safety critical components (e.g., engine, brakes), while the low speed network commonly includes components less critical to safety, like the radio and the HVAC system.

The standard states that gateways between the two networks must only be re-programmable from the high-speed network, presumably to prevent a low-speed device from compromising a gateway to attack the high-speed network. In their car, there are two ECUs, which are on both buses and can potentially bridge signals: the Body Controller Module (BCM) and the telematics unit. While the telematics unit is not technically a gateway, it connects to both networks and can only be reprogrammed (against the spirit of the standard) from the low-speed network, allowing a low speed device to attack the high-speed network through the telematics unit.

They verified that they could bridge these networks by uploading code to the telematics unit from the low-speed network that, in turn, sent packets on the high-speed network.

There are three major approaches to bring the attacks just seen:

Packet Sniffing and Targeted Probing. To begin, they used CARSHARK to observe traffic on the CAN buses in order to determine how ECUs communicate with each other. This also revealed to them which packets were sent as they activated various components (such as turning on the headlights). Through a combination of replay and informed probing, they were able to discover how to control the radio, the Instrument Panel Cluster (IPC), and a number of the Body Control Module (BCM) functions. This approach worked well for packets that come up during normal operation, but was less useful in mapping the interface to safety-critical powertrain components.

Fuzzing. Much to their surprise, significant attacks do not require a complete understanding or reverse engineering of even a single component of the car. In fact, because the range of valid CAN packets is rather small, significant damage can be done by simple fuzzing of packets (i.e., iterative testing of random or partially random packets). Indeed, for attackers seeking indiscriminate disruption, fuzzing is an effective attack by itself. (Unlike traditional uses of fuzzing, they use fuzzing to aid in the reverse engineering of functionality.)

Reverse Engineering. For a small subset of ECUs (notably the telematics unit, for which they obtained multiple instances via Internet-based used parts resellers) they dumped The ECU's code via the CAN Read Memory service and used a third-party debugger (IDA Pro) to explicitly understand how certain hardware features were controlled.

This approach is essential for attacks that require new functionality to be added (e.g., bridging low and high-speed buses) rather than simply manipulating existing software capabilities. Afterwards there are the results of their experiments with controlling critical components of the car.

All initial experiments were done with the car stationary, in many cases immobilized on jack stands for safety. Some of their results are summarized in the following tables. The tables indicate the packet that was sent to the corresponding module, the resulting action, and four additional pieces of information:

- 1. Can the result of this packet be overridden manually, such as by pulling the physical door unlock knob, pushing on the brakes, or some other action? A No in this column means that they have found no way to manually override the result.

- 2. Does this packet have the same effect when the car is at speed? For this column, "at speed" means when the car was up on jack stands but the throttle was applied to bring the wheel speed to 40 MPH.

- 3. Does the module in question need to be unlocked with its Device Control key before these packets can elicit results?

### 4. Additional column reflects their experiments during a live road test.

| Packet      | Result                                                     | Manual<br>Override | At<br>Speed | Need to<br>Unlock | Tested on<br>Runway |

|-------------|------------------------------------------------------------|--------------------|-------------|-------------------|---------------------|

| 07 AE 1F 87 | Continuously Activates Lock Relay                          | Yes                | Yes         | No                | ✓                   |

| 07 AE C1 A8 | Windshield Wipers On Continuously                          | No                 | Yes         | No                | ✓                   |

| 07 AE 77 09 | Pops Trunk                                                 | No                 | Yes         | No                | ✓                   |

| 07 AE 80 1B | Releases Shift Lock Solenoid                               | No                 | Yes         | No                |                     |

| 07 AE D8 7D | Unlocks All Doors                                          | Yes                | Yes         | No                |                     |

| 07 AE 9A F2 | Permanently Activates Horn                                 | No                 | Yes         | No                | ✓                   |

| 07 AE CE 26 | Disables Headlights in Auto Light Control                  | Yes                | Yes         | No                | ✓                   |

| 07 AE 34 5F | All Auxiliary Lights Off                                   | No                 | Yes         | No                |                     |

| 07 AE F9 46 | Disables Window and Key Lock Relays                        | No                 | Yes         | No                |                     |

| 07 AE F8 2C | Windshield Fluid Shoots Continuously                       | No                 | Yes         | No                | ✓                   |

| 07 AE 15 A2 | Controls Horn Frequency                                    | No                 | Yes         | No                |                     |

| 07 AE 15 A2 | Controls Dome Light Brightness                             | No                 | Yes         | No                |                     |

| 07 AE 22 7A | Controls Instrument Brightness                             | No                 | Yes         | No                |                     |

| 07 AE 00 00 | All Brake/Auxiliary Lights Off                             | No                 | Yes         | No                | ✓                   |

| 07 AE 1D 1D | Forces Wipers Off and Shoots Windshield Fluid Continuously | Yes <sup>†</sup>   | Yes         | No                | ✓                   |

| Packet      | Result                                       | Manual<br>Override | At<br>Speed | Need to<br>Unlock | Tested on<br>Runway |

|-------------|----------------------------------------------|--------------------|-------------|-------------------|---------------------|

| 07 AE E5 EA | Initiate Crankshaft Re-learn; Disturb Timing | Yes                | Yes         | Yes               |                     |

| 07 AE CE 32 | Temporary RPM Increase                       | No                 | Yes         | Yes               | ✓                   |

| 07 AE 5E BD | Disable Cylinders, Power Steering/Brakes     | Yes                | Yes         | Yes               |                     |

|             | Kill Engine, Cause Knocking on Restart       | Yes                | Yes         | Yes               | ✓                   |

| 07 AE 8D C8 | Grind Starter                                | No                 | Yes         | Yes               |                     |

| 07 AE 00 00 | Increase Idle RPM                            | No                 | Yes         | Yes               | ✓                   |

| Packet      | Result                                       | Manual<br>Override | At<br>Speed | Need to<br>Unlock <sup>†</sup> | Tested on<br>Runway |

|-------------|----------------------------------------------|--------------------|-------------|--------------------------------|---------------------|

| 07 AE 25 2B | Engages Front Left Brake                     | No                 | Yes         | Yes                            | ✓                   |

| 07 AE 20 88 | Engages Front Right Brake/Unlocks Front Left | No                 | Yes         | Yes                            | ✓                   |

| 07 AE 86 07 | Unevenly Engages Right Brakes                | No                 | Yes         | Yes                            | ✓                   |

| 07 AE FF FF | Releases Brakes, Prevents Braking            | No                 | Yes         | Yes                            | ✓                   |

| Destination<br>ECU | Packet      | Result                        | Manual<br>Override | At<br>Speed | Tested on<br>Runway |

|--------------------|-------------|-------------------------------|--------------------|-------------|---------------------|

| IPC                | 00 00 00 00 | Falsify Speedometer Reading   | No                 | Yes         | ✓                   |

| Radio              | 04 00 00 00 | Increase Radio Volume         | No                 | Yes         |                     |

| Radio              | 63 01 39 00 | Change Radio Display          | No                 | Yes         |                     |

| IPC                | 00 02 00 00 | Change DIC Display            | No                 | Yes         |                     |

|                    | 27 01 65 00 |                               |                    |             |                     |

| BCM                | 04 03       | Unlock Car <sup>†</sup>       | Yes                | Yes         |                     |

| BCM                | 04 01       | Lock Car <sup>†</sup>         | Yes                | Yes         |                     |

| BCM                | 04 OB       | Remote Start Car <sup>†</sup> | No                 | No          |                     |

| BCM                | 04 OE       | Car Alarm Honk <sup>†</sup>   | No                 | No          |                     |

| Radio              | 83 32 00 00 | Ticking Sound                 | No                 | Yes         |                     |

| ECM                | AE 0E 00 7E | Kill Engine                   | No                 | Yes         |                     |

In the article, they deepen these attacks, but for our scope is enough understand the problem of the security and as a starting point, we can take the conclusions of this article.

We can summarize the conclusions in the following eight points

Extent of Damage. Past works discuss potential risks to cyber-physical vehicles and thus we knew that adversaries might be able to do damage by attacking the components within cars. The authors of the

article did not, however, anticipate that we would be able to directly manipulate safety critical ECUs (indeed, all ECUs that we tested) or that we would be allowed to create unsafe conditions of such magnitude.

Ease of Attack. In starting this project, they expected to spend significant effort reverse engineering, with non-trivial effort to identify and exploit each subtle vulnerability. However, they found existing automotive systems—at least those they tested—to be tremendously fragile. Indeed, their simple fuzzing infrastructure was very effective and to their surprise, a large fraction of the random packets they sent resulted in changes to the state of their car. Based on this experience, they believe that a fuzzer itself is likely be a universal attack for disrupting arbitrary automobiles (similar to how the "crashme" program that fuzzed system calls was effective in crashing operating systems before the syscall interface was hardened).

Unenforced Access Controls. While they believe that standard access controls are weak, they were surprised at the extent to which the controls that did exist were frequently unused. For example, the firmware on an ECU controls all of its critical functionality and thus the standard for their car's CAN protocol variant describes methods for ECUs to protect against unauthorized firmware updates. They were therefore surprised that they could load firmware onto some key ECUs, like their telematics unit (a critical ECU) and their Remote Control Door Lock Receiver (RCDLR), without any such authentication. Similarly, the protocol standard also makes an earnest attempt to restrict access to Device Control diagnostic capabilities. They were therefore also surprised to find that critical ECUs in their car would respond to Device Control packets without authentication first.

Attack Amplification. They found multiple opportunities for attackers to amplify their capabilities—either in reach or in stealth. For example, while the designated gateway node between the car's low-speed and high-speed networks (the BCM) should not expose any interface that would let a low-speed node compromise the high-speed network, they found that they could maliciously bridge these networks through a compromised telematics unit. Thus, the compromise of any ECU becomes sufficient to manipulate safety-critical components such as the EBCM. As more and more components integrate into vehicles, it may become increasingly difficult to properly secure all bridging points.

Diagnostic and Reflashing Services. Many of the vulnerabilities they discovered were made possible by weak or unenforced protections of the diagnostic and reflashing services. Because these services are never intended for use during normal operation of the vehicle, it is tempting to address these issues by completely locking down such capabilities after the car leaves manufacturing.

Aftermarket Components. Even with diagnostic and reflashing services secured, packets that appear on the vehicle bus during normal operation can still be spoofed by third party ECUs connected to the bus. Today a modern automobile leaves the factory containing multiple third party ECUs, and owners often

add aftermarket components (like radios or alarms) to their car's buses. This creates a tension that, in the extreme, manifests itself as the need to either trust all third-party components, or to lock down a car's network so that no third-party components—whether adversarial or benign—can influence the state of the car.

One potential intermediate (and backwards compatible) solution they envision, is to allow owners to connect an external filtering device between an untrusted component (such as a radio) and the vehicle bus to function as a trusted mediator, ensuring that the component sends and receives only approved packets.

Detection versus Prevention. More broadly, certain considerations unique to cyber-physical vehicles raise the possibility of security via detection and correction of anomalies, rather than prevention and locking down of capabilities. For example, the operational and economic realities of automotive design and manufacturing are stringent. Manufacturers must swiftly integrate parts from different suppliers (changing as needed to second and third source suppliers) in order to quickly reach market and at low cost. Competitive pressures drive vendors to reuse designs and thus engenders significant heterogeneity. It is common that each ECU may use a different processor and/or software architecture and some cars may even use different communications architectures—one grafted onto the other to integrate a vendor assembly and bring the car to market in time. Today the challenges of integration have become enormous and manufacturers seek to reduce these overheads at all costs—a natural obstacle for instituting strict security policies. In addition, many of an automobile's functions are safety critical, and introducing additional delay into the processing of, say, brake commands, may be unsafe. These considerations raise the possibility of exploring the trade-off between preventing and correcting malicious actions: if rigorous prevention is too expensive, perhaps a quick reversal is sufficient for certain classes of vulnerabilities.

Several questions come with this approach: Can anomalous behaviour be detected early enough, before any dangerous packets are sent? Can a fail-safe mode or last safe state be identified and safely reverted to? It is also unclear what constitutes abnormal behaviour on the bus in the first place, as attacks can be staged entirely with packets that also appear during normal vehicle operation.

Toward Security. These are just a few of many potential defensive directions and associated tensions. There are deep-rooted tussles surrounding the security of cyber physical vehicles, and it is not yet clear what the "right" solution for security is or even if a single "right" solution exists. More likely, there is a spectrum of solutions that each trade off critical values (like security vs. support for independent auto shops). Thus, they argue that the future research agenda for securing cyber-physical vehicles is not merely to consider the necessary technical mechanisms, but to also inform these designs by what is feasible practically and compatible with the interests of a broader set of stakeholders. This work serves

as a critical piece in the puzzle, providing the first experimentally guided study into the real security risks with a modern automobile.

To conclude with this article we can say that its purpose is to awareness the automotive manufactures that the 'car system' presents some flaws about the security, which may bring damage to various levels, without going into detail of the attack channel type. The same editors of this article, to fill the previous gap, wrote another significant article about the attack channel types: Comprehensive Experimental Analyses of Automotive Attack Surfaces.

## 3.2 Comprehensive Experimental Analyses of Automotive Attack Surfaces

Although the purpose of this thesis is not to analyze issues relating to how the attack is carried, it is important view some principal aspects of this article, to understand the importance of the security in the automotive environment.

The previous work shown how to attack a car by the On-Board Diagnostics (OBD-II) port. This is a physical access and not ever the malicious user can have it. Thus, the threat do not seems much dangerous, because the malicious user need to dismount some part of the car and connect itself to On-Board Diagnostics port. Indeed, there are many type of channel that can be used to a malicious user to create a breach in the system and in this article, as we will see; they explored all the available channels.

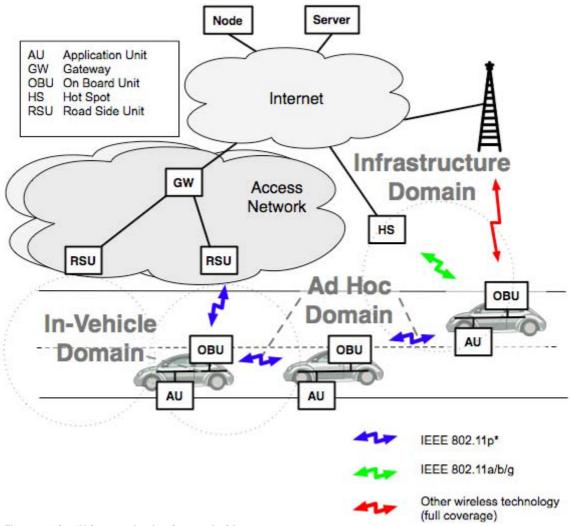

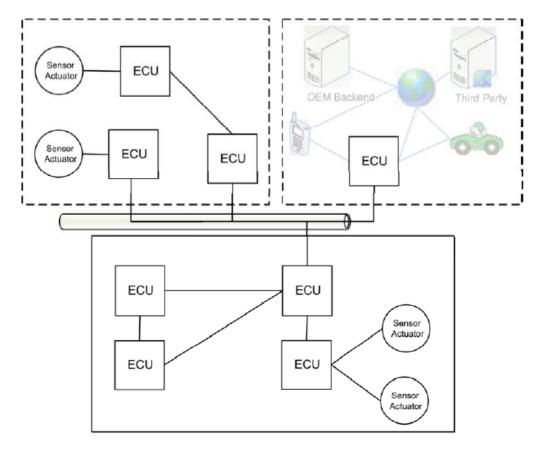

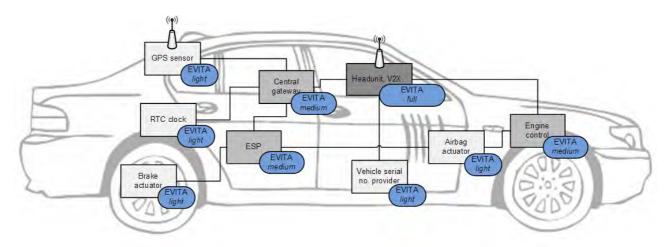

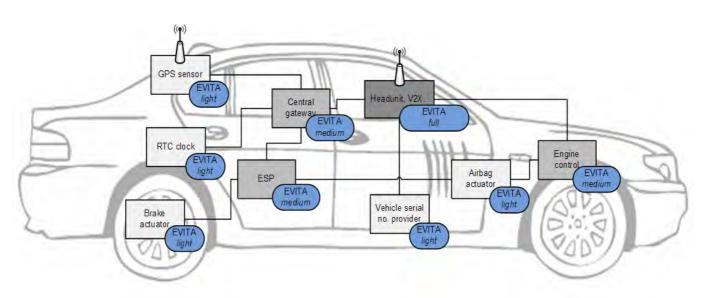

Figure 3.1: Digital I/O channels appearing on a modern car. Colours indicate rough grouping of ECUs by function.

They divide the attack channels type in three categories

1. Indirect physical access

Modern automobiles provide several physical interfaces that either directly or indirectly access the car's internal networks. They consider the full physical attack surface here, under the constraint that the adversary may not directly access these physical interfaces herself but must instead work through some

intermediary.

OBD-II. The most significant automotive interface is the OBD-II port, federally mandated in the U.S., which typically provides direct access to the automobile's key CAN buses and can provide sufficient

access to compromise the full range of automotive systems.

While their threat model forbids the adversary from direct access herself, we note that the OBD-II port is commonly accessed by service personnel during routine maintenance for both diagnostics and ECU programming. Historically this access is achieved using dedicated handheld "scan" tools such as Ford's NGS, Nissan's Consult II and Toyota's Diagnostic Tester, which are themselves, programmed via Windows-based personal computers. For modern vehicles, most manufacturers have adopted an approach that is PC-centric. Under this model, a laptop computer interfaces with a "Pass Thru" device (typically directly via USB or Wi-Fi) that in turn is plugged into the car's OBD-II port. Software on the laptop computer can then interrogate or program the car's ECUs via this device (typically using the standard SAE J2534 API). Examples of such tools include Toyota's TIS, Ford's VCM, Nissan's Consult 3

and Honda's HDS among others.

In both situations, Windows-based computers directly or indirectly control the data to be sent to the automobile. Thus, if an adversary were able to compromise such systems at the dealership she could amplify this access to attack any cars under service. Such laptop computers are typically Internetconnected (indeed, this is a requirement for some manufacturers' systems), so traditional means of personal computer compromise could be employed. Further afield, electric vehicles may also communicate with external chargers via the charging cable. An adversary able to compromise the external charging infrastructure may thus be able to leverage that access to subsequently attack any connected automobile.

Entertainment: Disc, USB and iPod.

The other important class of physical interfaces are focused on entertainment systems. Virtually all automobiles shipped today provide a CD player able to interpret a wide variety of audio formats (raw "Red Book" audio, MP3, WMA, and so on). Similarly, vehicle manufacturers also provide some kind of external digital multimedia port (typically either a USB port or an iPod/iPhone docking port) for allowing users to control their car's media system using their personal audio player or phone. Some

27

manufacturers have widened this interface further; BMW and Mini recently added to their cars, their support for "iPod Out," a scheme whereby Apple media devices will be able to control the display on the car's console.

Consequently, an adversary might deliver malicious input by encoding it onto a CD or as a song file and using social engineering to convince the user to play it. Alternatively, she might compromise the user's phone or iPod out of band and install software onto it that attacks the car's media system when connected.

Taking over a CD player alone is a limited threat; but, for a variety of reasons, automotive media systems are not standalone devices. Indeed, many such systems are now CAN bus interconnected, either to directly interface with other automotive systems (e.g., to support chimes, certain hands-free features, or to display messages on the console) or simply to support a common maintenance path for updating all ECU firmware. Thus, counterintuitively, a compromised CD player can offer an effective vector for attacking other automotive components.

### 2. Short-range wireless access

Indirect physical access has a range of drawbacks including its operational complexity, challenges in precise targeting, and the inability to control the time of compromise. Here we weaken the operational requirements on the attacker and consider the attack surface for automotive wireless interfaces that operate over short ranges. These include Bluetooth, Remote Keyless Entry, RFIDs, Tire Pressure Monitoring Systems, Wi-Fi, and Dedicated Short- Range Communications. For this portion of the attack surface, we assume that the adversary is able to place a wireless transmitter in proximity to the car's receiver (between 5 and 300 meters depending on the channel).

#### Bluetooth.

Bluetooth has become the de facto standard for supporting hands-free calling in automobiles and is standard in mainstream vehicles sold by all major automobile manufacturers. While the lowest level of the Bluetooth protocol is typically implemented in hardware, the management and services component of the Bluetooth stack is often implemented in software. In normal usage, the Class 2 devices used in automotive implementations have a range of 10 meters, but others have demonstrated that this range can be extended through amplifiers and directional antennas.

### Remote Keyless Entry.

Today, all but entry-level automobiles shipped in the U.S. use RF-based remote keyless entry (RKE) systems to remotely open doors, activate alarms, flash lights and, in some cases, start the ignition (all typically using digital signals encoded over 315 MHz in the U.S. and 433 MHz in Europe).

### Tire pressure.

In the U.S., all 2007 model year and newer cars are required to support a Tire Pressure Monitoring System (TPMS) to alert drivers about under or over inflated tires. The most common form of such systems, so called "Direct TPMS," uses rotating sensors that transmit digital telemetry (frequently in similar bands as RKEs).

RFID car keys. RFID-based vehicle immobilizers are now nearly ubiquitous in modern automobiles and are mandatory in many countries throughout the world. These systems embed an RFID tag in a key or key fob and a reader in or near the car's steering column. These systems can prevent the car from operating unless the correct key (as verified by the presence of the correct RFID tag) is present.

### Emerging short-range channels.

A number of manufacturers have started to discuss providing 802.11 Wi-Fi access in their automobiles, typically to provide "hotspot" Internet access via bridging to a cellular 3G data link. In particular, Ford offers this capability in the 2012 Ford Focus. (Several 2011 models also provided WiFi receivers, but we understand they were used primarily for assembly line programming.)

Finally, while not currently deployed, an emerging wireless channel is defined in the Dedicated Short-Range Communications (DSRC) standard, which is being incorporated into proposed standards for Cooperative Collision Warning/Avoidance and Cooperative Cruise Control. Representative programs in the U.S. include the Department of Transportation's Cooperative Intersection Collision Avoidance Systems (CICAS-V) and the Vehicle Safety Communications Consortium's VSC-A project. In such systems, forward vehicles communicate digitally to trailing cars to inform them of sudden changes in acceleration to support improved collision avoidance and harm reduction.

Summary. For all of these channels, if a vulnerability exists in the ECU software responsible for parsing channel messages, then an adversary may compromise the ECU (and by extension the entire vehicle) simply by transmitting a malicious input within the automobile's vicinity.

#### 3. Long-range wireless

Finally, automobiles increasingly include long distance (greater than 1 km) digital access channels as well. These tend to fall into two categories: broadcast channels and addressable channels.

Broadcast channels. Broadcast channels are channels that are not specifically directed towards a given automobile but can be "tuned into" by receivers on demand.

In addition to being part of the external attack surface, long-range broadcast mediums can be appealing as control channels (i.e., for triggering attacks) because they are difficult to attribute, can command multiple receivers at once, and do not require attackers to obtain precise addressing for their victims.

The modern automobile includes a plethora of broadcast receivers for long-range signals: Global Positioning System (GPS), Satellite Radio (e.g., SiriusXM receivers common to late-model vehicles from Honda/Accura, GM, Toyota, Saab, Ford, Kia, BMW and Audi), Digital Radio (including the U.S. HD Radio system, standard on 2011 Ford and Volvo models, and Europe's DAB offered in Ford, Audi, Mercedes, Volvo and Toyota among others), and the Radio Data System (RDS) and Traffic Message Channel (TMC) signals transmitted as digital subcarriers on existing FM-bands.

The range of such signals depends on transmitter power, modulation, terrain, and interference. As an example, a 5W RDS transmitter can be expected to deliver its 1.2 kbps signal reliably over distances upto 10 km. In general, these channels are implemented in an automobile's media system (radio, CD player, satellite receiver) which, as mentioned previously, frequently provides access via internal automotive networks to other key automotive ECUs.

### Addressable channels.

Perhaps the most important part of the long-range wireless attack surface is that exposed by the remote telematics systems (e.g., Ford's Sync, GM's OnStar, Toyota's SafetyConnect, Lexus' Enform, BMW's BMW Assist, and Mercedes-Benz' mbrace) that provide continuous connectivity via cellular voice and data networks. These systems provide a broad range of features supporting safety (crash reporting), diagnostics

(early alert of mechanical issues), anti-theft (remote track and disable), and convenience (hands-free data access such as driving directions or weather). These cellular channels offer many advantages for attackers. They can be accessed over arbitrary distance (due to the wide coverage of cellular data infrastructure) in a largely anonymous fashion, typically have relatively high bandwidth, are two-way channels (supporting interactive control and data exfiltration), and are individually addressable.

For each category of access vector, they will explore one or two aspects of the attack surface deeply, identify concrete vulnerabilities, and explore and demonstrate practical attacks that are able to completely compromise their target automobile's systems without requiring direct physical access.

To be clear, for every vulnerability they demonstrate, they are able to obtain complete control over the vehicle's systems

| Vulnerability<br>Class  | Channel     | Implemented<br>Capability                                                                                                  | Visible<br>to User | Scale  | Full<br>Control | Cost        |

|-------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------|--------------------|--------|-----------------|-------------|

| Direct physical         | OBD-II port | Plug attack hardware directly into car<br>OBD-II port                                                                      | Yes                | Small  | Yes             | Low         |

| Indirect physical       | CD          | CD-based firmware update                                                                                                   | Yes                | Small  | Yes             | Medium      |

|                         | CD          | Special song (WMA)                                                                                                         | Yes*               | Medium | Yes             | Medium-High |

|                         | PassThru    | WiFi or wired control connection to<br>advertised PassThru devices                                                         | No                 | Small  | Yes             | Low         |

|                         | PassThru    | WiFi or wired shell injection                                                                                              | No                 | Viral  | Yes             | Low         |

| Short-range<br>wireless | Bluetooth   | Buffer overflow with paired Android phone and Trojan app                                                                   | No                 | Large  | Yes             | Low-Medium  |

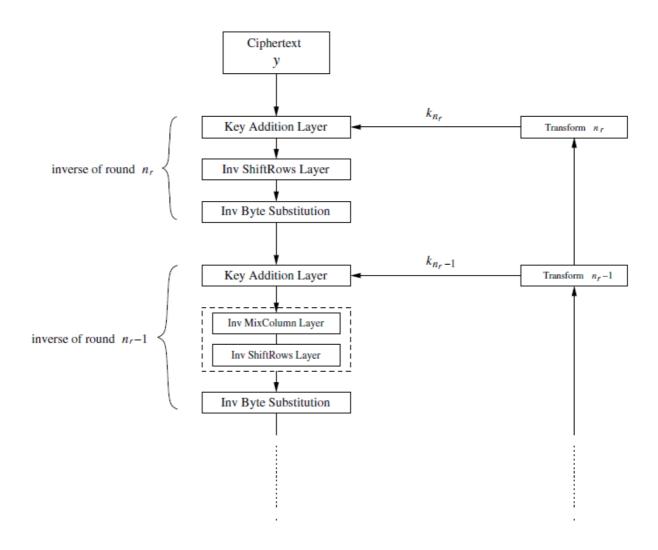

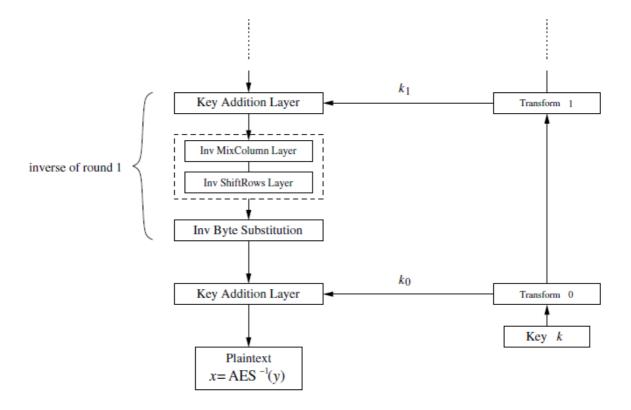

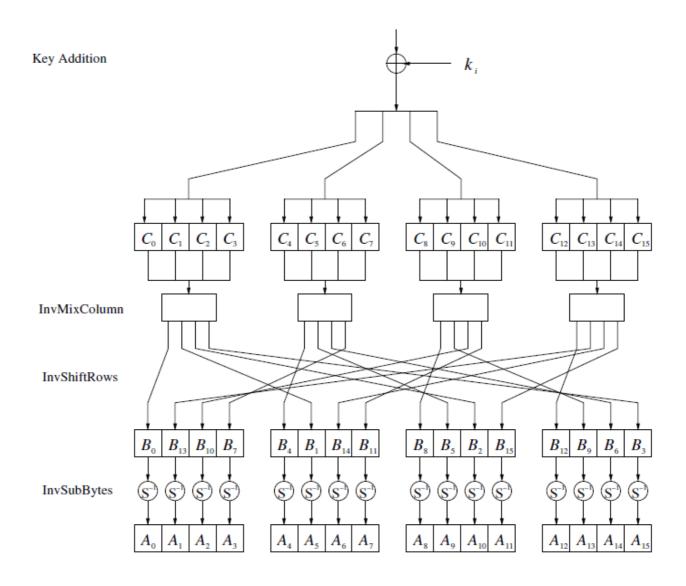

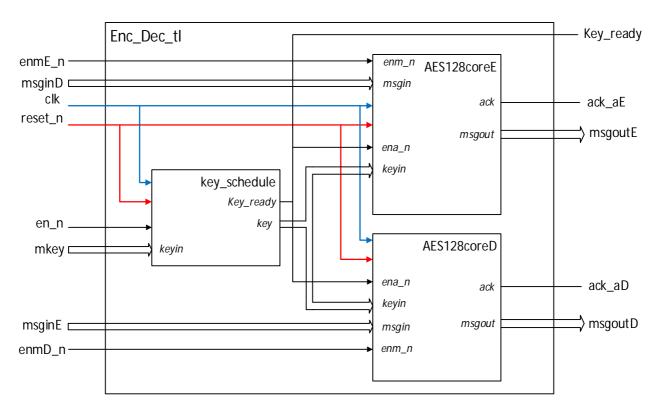

|                         | Bluetooth   | Sniff MAC address, brute force PIN,<br>buffer overflow                                                                     | No                 | Small  | Yes             | Low-Medium  |