# CMOS MESFET Cascode Amplifiers for RFIC Applications

by

# Payam Habibi-Mehr

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved March 2019 by the Graduate Supervisory Committee:

Trevor Thornton, Chair Bertan Bakkaloglu Jennifer Kitchen Gabriele Formicone

ARIZONA STATE UNIVERSITY

May 2019

#### ABSTRACT

There is an ever-increasing demand for higher bandwidth and data rate ensuing from exploding number of radio frequency integrated systems and devices. As stated in the Shannon-Hartley theorem, the maximum achievable data rate of a communication channel is linearly proportional to the system bandwidth. This is the main driving force behind pushing wireless systems towards millimeter-wave frequency range, where larger bandwidth is available at a higher carrier frequency. Observing the Moor's law, highly scaled complementary metal-oxide-semiconductor (CMOS) technologies provide fast transistors with a high unity power gain frequency which enables operating at millimeterwave frequency range. CMOS is the compelling choice for digital and signal processing modules which concurrently offers high computation speed, low power consumption, and mass integration at a high manufacturing yield. One of the main shortcomings of the submicron CMOS technologies is the low breakdown voltage of the transistors that limits the dynamic range of the radio frequency (RF) power blocks, especially with the power amplifiers. Low voltage swing restricts the achievable output power which translates into low signal to noise ratio and degraded linearity. Extensive research has been done on proposing new design and IC fabrication techniques with the goal of generating higher output power in CMOS technology. The prominent drawbacks of these solutions are an increased die area, higher cost per design, and lower overall efficiency due to lossy passive components. In this dissertation, CMOS compatible metal-semiconductor field-effect transistor (MESFETs) are utilized to put forward a new solution to enhance the power amplifier's breakdown voltage, gain and maximum output power. Requiring no change to the conventional CMOS process flow, this low cost approach allows direct incorporation of high voltage power MESFETs into silicon. High voltage MESFETs were employed in a cascode structure to push the amplifier's cutoff frequency and unity power gain frequency to the 5G and *K*-band frequency range. This dissertation begins with CMOS compatible MESFET modeling and fabrication steps, and culminates in the discussion of amplifier design and optimization methodology, parasitic de-embedding steps, simulation and measurement results, and high resistivity RF substrate characterization.

# DEDICATION

To my parents and sister

# **EPIGRAPH**

"If you're on the path

Don't despair of the distance

Arrival is the art of stepping through time

What fear of darkness?

When my soul ignites fires

And a hundred dormant suns

From my cold ashes rise"

—H. E. Sayeh

### **ACKNOWLEDGMENTS**

I would like to genuinely express my heartfelt gratitude to my doctoral adviser, Professor Trevor Thornton. I have been privileged to acquire knowledge from, learn from his wealth of experience and grow under his supervision over the past four years. His everlasting support, invaluable guidance and insightful motivation has been indispensable in helping me achieve my research goals.

I extend my deepest appreciation to Professor Bertan Bakkaloglu who relentlessly supported my efforts since the first day I met him. I learnt much from his lectures and expertise. Serving as his teaching assistant was a prodigious experience for me and I enjoyed his companionship and amicable demeanor. It was a pleasure collaborating with Dr. Jennifer Kitchen and her students, Soroush and Kevin, on the power tracking MESFET PA project. I very much appreciate her mentorship, encouragement and valuable time she dedicated to us. I am grateful to Dr. Gabrielle Formicone for his valuable feedback and suggestions as my dissertation committee member.

I would like to thank Dr. Michael Goryll for his constructive comments and discussions. I appreciate his time and assistance in responding to technical challenges and I definitely have not taken it for granted. I cannot emphasize the direct influence of Dr. William Lepkowski enough. Our early Saturday meetings educated me on addressing the tape-out difficulties; the time that he could have spent with his family instead. I gratefully acknowledge the support of Dr. Raymond Tsui, and will always remember our outreach activities at ASU. Special thanks to Mr. James Laux and Mr. Craig Birtcher for their technical support and making themselves available in times of need in a timely manner. I sincerely thank my graduate advisers, Ms. Toni Mengert and Mr. Robert Monahan, who

answered my endless questions with patience and a welcoming smile and helped me with

all the documentations.

Last but not least, I am fully indebted to my parents, Parisa and Alireza, to whom

I owe all that I am. They have unconditionally loved and supported me through thick and

thin, and their selfless sacrifices have been the wind beneath my wings. I am blessed to

have a little angel by my side; my sister Pegah who has always been there for me. I express

my gratitude to my grandmother, Parvin, and my aunt, Pooneh, who always inspired me.

Ever since I left the motherland, my family has been present in my heart perpetually.

Finally, I am grateful to my nurturing cousin, Ramin, whose support was not withdrawn

momentarily.

Payam Mehr

Scottsdale, AZ

February 2019

vi

## TABLE OF CONTENTS

| Page                                                         |

|--------------------------------------------------------------|

| LIST OF FIGURES X                                            |

| LIST OF TABLESXVI                                            |

| CHAPTER                                                      |

| 1. INTRODUCTION1                                             |

| 2. CMOS SOI MESFETS                                          |

| 2.1. CMOS MESFET Fabrication                                 |

| 2.2. MESFET Operating Regions 8                              |

| 2.3. MESFET DC and RF Characterization                       |

| 2.3.1. MESFET DC and RF Performance Dependence on $L_{aD$    |

| 2.3.2. MESFET DC and RF Performance Dependence on $L_{G}$ 19 |

| 2.3.3. MESFET RF Performance Dependence on the gate Finger   |

| Width $(W_f)$                                                |

| 2.4. 4-Terminal MESFET DC Measurements                       |

| 2.5. MESFET Models                                           |

| 2.5.1. Curtice Quadratic Model29                             |

| 2.5.2. Statz Model30                                         |

| 2.5.3. Triquint Own Model (TOM3)30                           |

| 2.5.4. Angelov (Chalmers) Model31                            |

| 2.6. 4-Terminal Angelov Modeling                             |

| 2.7. Summary and Discussion41                                |

| СН | IAPTER | Pag                                              | ξE |

|----|--------|--------------------------------------------------|----|

| 3. | TRAP-  | RICH SUBSTRATES FOR RF PERFORMANCE IMPROVEMENT 4 | .2 |

|    | 3.1.   | High-Resistivity Silicon Substrates              | .2 |

|    | 3.2.   | MESFETs on Trap-Rich Substrates                  | .4 |

|    | 3.3.   | DC Transfer Characteristics 4                    | -5 |

|    | 3.4.   | RF Gain Characteristics4                         | 8  |

|    | 3.5.   | Lumped Element Circuit5                          | 51 |

|    | 3.6.   | Summary and Discussion5                          | ;6 |

| 4. | MOSF   | ET-MESFET CMOS CASCODE AMPLIFIERS5               | 57 |

|    | 4.1.   | Overview5                                        | 57 |

|    | 4.2.   | MOSFET-MESFET Cascode Architecture               | 2  |

|    | 4.3.   | MOSFET-MESFET Cascode Design                     | 4  |

|    | 4.4.   | Cascode DC Characterization                      | 7  |

|    | 4.5.   | Cascode RF Characterization                      | '4 |

|    | 4.6.   | Parasitics De-embedding Procedure                | 7  |

|    | 4      | .6.1. Cold-FET Measurement                       | '9 |

|    | 4.7.   | Cascode RF De-embedded Results                   | )1 |

|    | 4.8.   | Summary and Discussion9                          | 19 |

| 5. | SCALE  | D UP MOSFET-MESFET POWER AMPLIFIERS 10           | C  |

|    | 5.1.   | Cascode Power Amplifier Initial Design           | 0  |

|    | 5.2.   | Optimized Cascode Power Amplifier Design10       | )5 |

| CHAPTER                            | Page                         |

|------------------------------------|------------------------------|

| 5.2.1. MESFET PCell in 45RF SO     | I Technology 106             |

| 5.2.2. NFET Layout Optimization    |                              |

| 5.2.3. Transistors Width Ratio     | 108                          |

| 5.3. Optimized Cascode Power Ampl  | lifier Characterization110   |

| 5.3.1. DC Measurements             | 110                          |

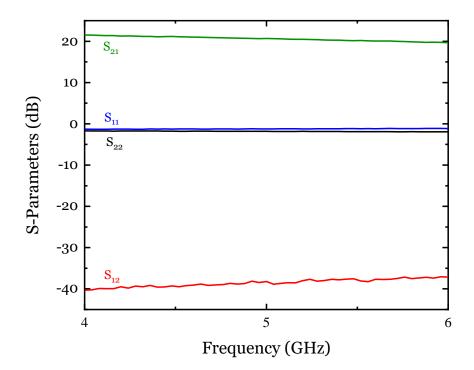

| 5.3.2. Cascode Power Amplifire S   | -parameters Measurements 112 |

| 5.3.3. Cascode Power Amplifier L   | arge Signal Measurements118  |

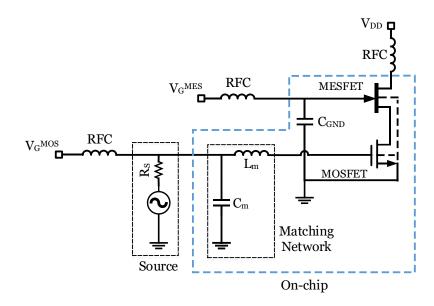

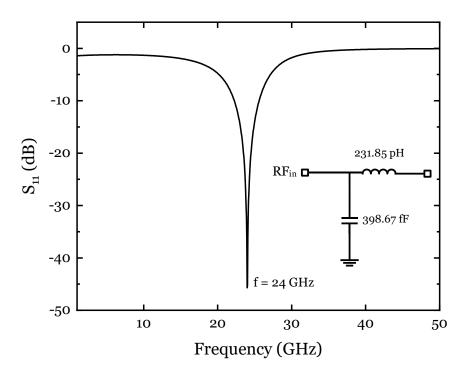

| 5.4. On-chip Input Matching and Fu | ture Work123                 |

| 5.4.1. On-chip Input Matching No   | etwork Design124             |

| 5.5. Summary and Discussion        | 128                          |

| REFERENCES                         | 130                          |

# LIST OF FIGURES

| 1 | igure Page                                                                                                                                                                                                        |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 2.1. Cross Section View of an N-type SOI MESFET Transistor on a P-type Substrate 5                                                                                                                                |

|   | 2.2. Measured Distributions in a) Threshold Voltage, b) Current Drive, and control Transconductance from Three Different Multi-project Wafer Runs                                                                 |

|   | 2.3. Family Of Curves (FOC) of a 45 nm SOI MESFET (W=300 $\mu$ m, $L_G = L_{aD} = L_{aS} = 200 \mu$ m), $V_{BS} = 0$ V                                                                                            |

|   | 2.4. Gummel Plots of a 45 nm SOI MESFET (W = 300 $\mu$ m, $L_G = L_{aD} = L_{aS} = 200 ~\mu$ m) $V_{BS} = 0 \text{ V}$ , -1.5 V < $V_{GS}$ < 0.5 V, $V_D = 0.025$ , 0.25, 0.5, 1, 2 and 4 V                       |

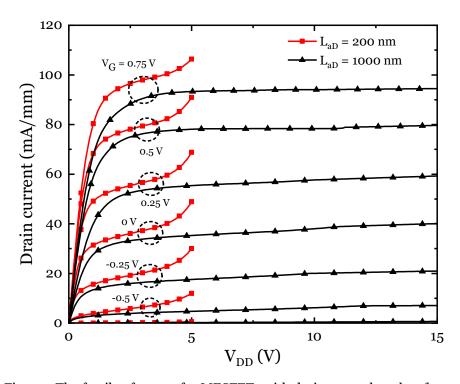

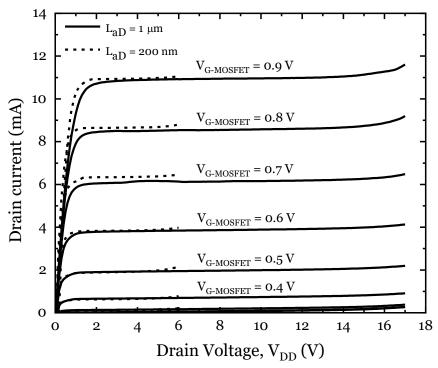

|   | 2.5. The Family of Curves for MESFETs with Drain Access Lengths of 200 nm (Squares and 1000 nm (Triangles)                                                                                                        |

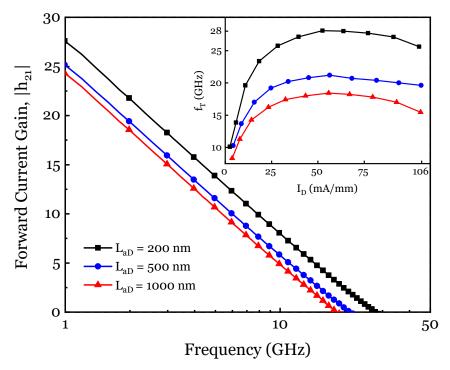

|   | 2.6. The De-embedded $h_{21}$ as a Function of Frequency for Devices with Different Drain Access Lengths of 200 nm, 500 nm and 1000 nm.                                                                           |

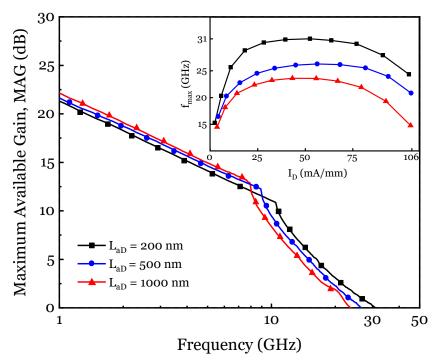

|   | 2.7. The De-embedded MAG as a Function of Frequency for Devices with Different Drain Access Lengths of 200 nm, 500 nm and 1000 nm. The Devices Were Biased with $V_{GS}=0.1\mathrm{V}$ and $V_{DS}=3\mathrm{V}$ . |

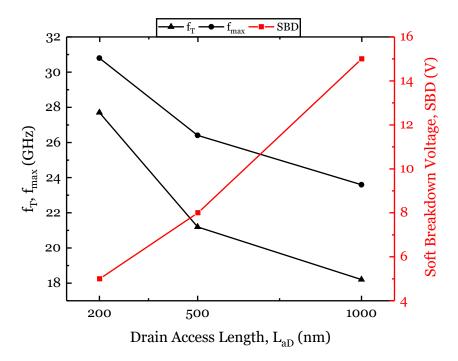

|   | 2.8. MESFET $f_T$ , $f_{max}$ and Breakdown Voltage Variations with Respect to $L_{aD}$ 18                                                                                                                        |

|   | 2.9. MESFET $g_m$ and $I_D$ Variation with Respect to $V_{GS}$                                                                                                                                                    |

|   | 2.10. FOC Comparison Between $L_G = L_{aD} = L_{aS} =$ 200 nm, and $L_G =$ 150 nm, $L_{aD} = L_{aS} =$ 300 nm MESFETs                                                                                             |

|   | 2.11. MESFET Cut-off Frequency ( $f_T$ ) Dependence on the Gate Length ( $L_G$ )                                                                                                                                  |

|   | 2.12. Maximum Oscillation Frequency ( $f_{max}$ ) Dependence on the Gate Length ( $L_G$ ) 22                                                                                                                      |

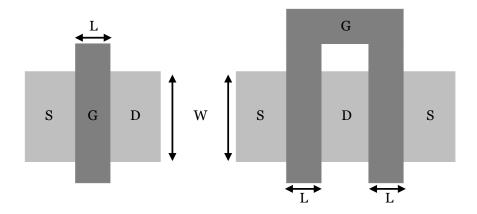

|   | 2.13. Left: Single Finger Transistor, Right: Transistor With Two Fingers 25                                                                                                                                       |

|   | 2.14. $f_T$ and $f_{max}$ Variations with Respect to the Gate Finger Width ( $W_f$ )                                                                                                                              |

| 2.15. Drain Current Versus Drain Voltage of a SOI MESFET ( $W$ =300 $\mu$ m, $L_G$ = 200 $\mu$ m)                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| for Different Substrate Voltages                                                                                                                                   |

| 2.16. Drain and Gate Currents of a SOI MESFET ( $W=300~\mu\text{m}, L_G=200~\mu\text{m}$ ) as a Function of Gate Voltage                                           |

| 2.17. Angelov Circuit Diagram [23] Including a Current Source, Parasitic Capacitances and Resistances31                                                            |

| 2.18. Angelov Slope Parameters Extraction from a 300 $\mu$ m Wide MESFET FOC with $L_G$ = $L_{aD}$ = $L_{aS}$ = 200 nm                                             |

| 2.19. Parameter Extraction for the First Order Angelov Model Using Measurement Results of a MESFET With $L_G$ = 500 $\mu$ m, $W$ = 300 $\mu$ m                     |

| 2.20. Current Paths Between the Schottky Gate and Source/Drain Junctions in a CMOS MESFET Transistor                                                               |

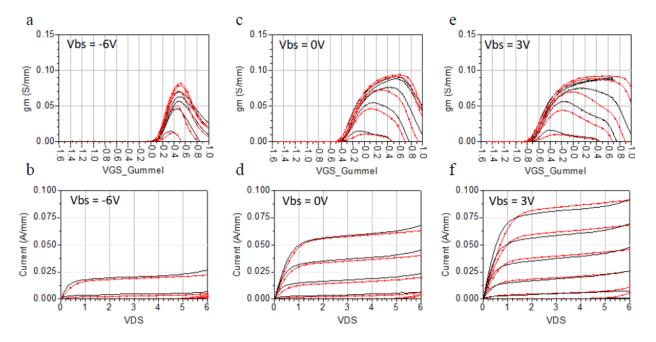

| 2.21. DC Model Fit for $g_m$ and FOC for Different Substrate Bias Voltages. $V_{GS}$ in FOC Plots Was Swept from -0.75 V to 0.5 V in 0.25 V Steps40                |

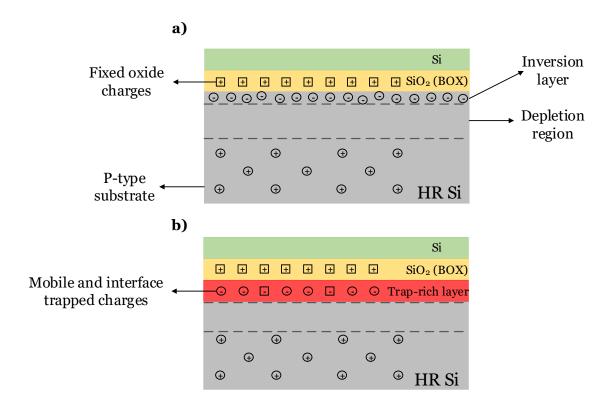

| 3.1. a) Conventional High Resistivity SOI Substrate b) Trap-rich SOI Substrate 43                                                                                  |

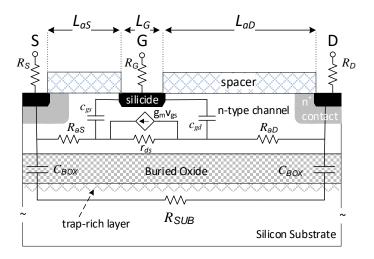

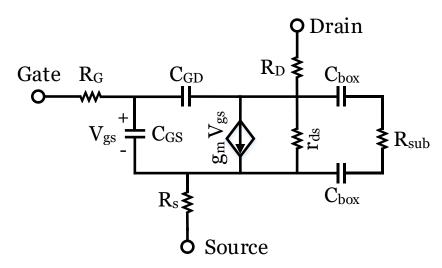

| 3.2. Schematic Cross-section of an SOI MESFET [24] with the Lumped Element Components Used in the Small-signal Model                                               |

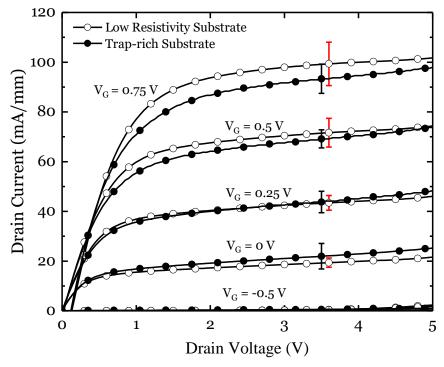

| 3.3. The Averaged Family of Curves (FOC) for MESFETs on Trap-rich Substrates (Solid Symbols) and Low Resistivity Substrates (Open Symbols)                         |

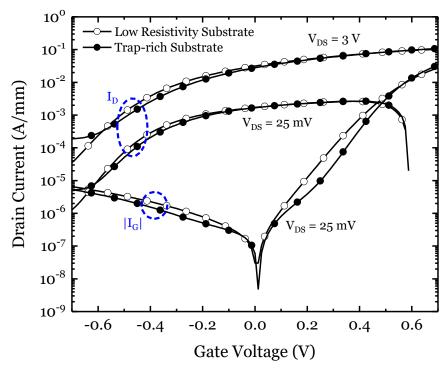

| 3.4. The Drain Current and Gate Current Magnitude as a Function of Gate Voltage Showing the Turn-on Characteristics of the MESFETs on the Two Different Substrates |

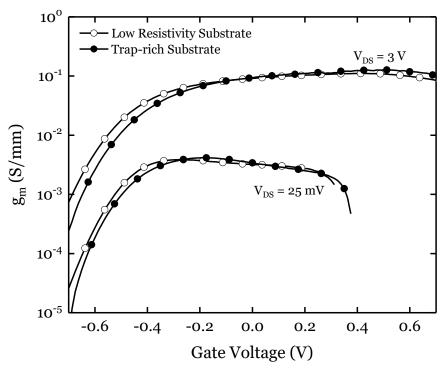

| 3.5. The Transconductance Derived from the Data in Figure 3.448                                                                                                    |

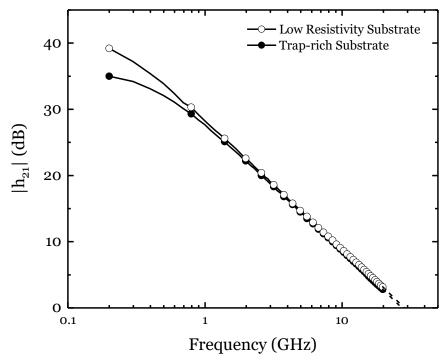

| 3.6. $h_{21}$ for $V_{DS}$ = 5 V and $V_{GS}$ = 0.1 V as a Function of Frequency                                                                                   |

Figure

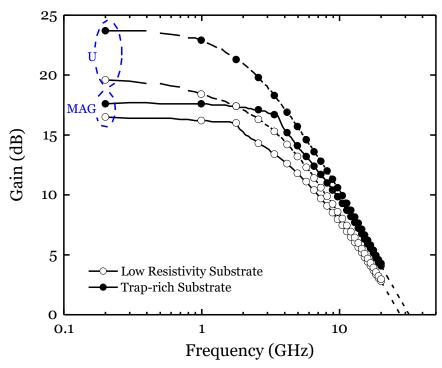

| 3.7. The MAG and U Plotted Against Frequency for $V_{DS} = 5$ V and $V_{GS} = 0.1$ V 50                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

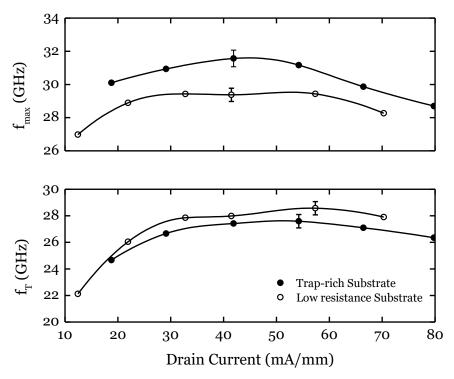

| 3.8. The Average Values of $f_T$ and $f_{max}$ as a Function of Drain Current for $V_D = 5 \text{ V} \dots 5 \text{ J}$                                                                                                                              |

| 3.9. The Small-signal Equivalent Circuit of the SOI MESFETs as Interpreted from the Cross-section of Figure 3.2.                                                                                                                                     |

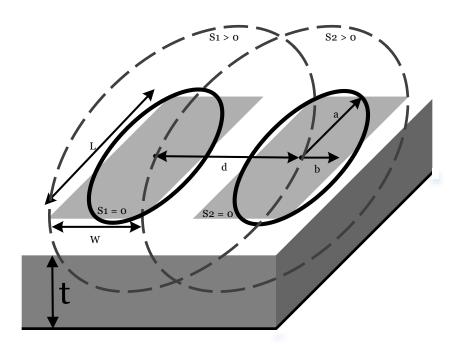

| 3.10. Two Rectangular Contacts Approximated as Elliptic Contacts to Approximate the Spreading Resistance Between the Contacts and an Infinite Backplane                                                                                              |

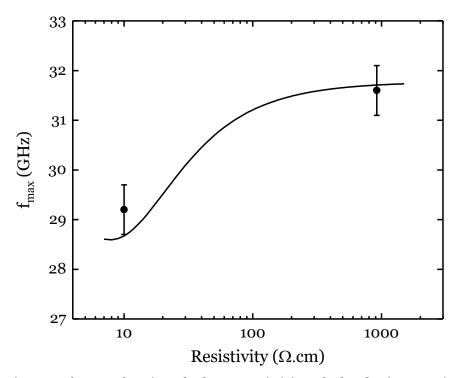

| 3.11. $f_{max}$ as a Function of Substrate Resistivity 55                                                                                                                                                                                            |

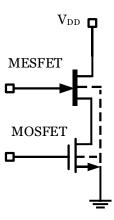

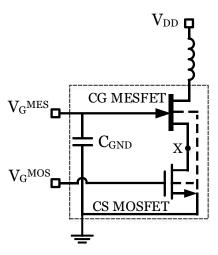

| 4.1. Cascode MOSFET-MESFET RF Power Amplifier                                                                                                                                                                                                        |

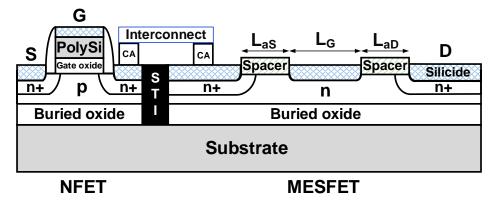

| 4.2. Cascode Amplifier Cross-section, Integrated on a SOI RF Substrate 64                                                                                                                                                                            |

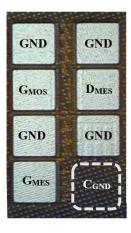

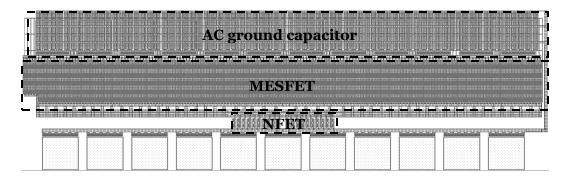

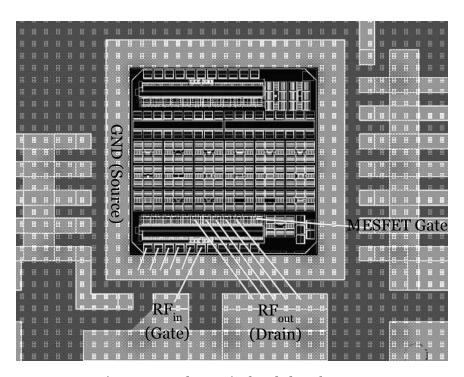

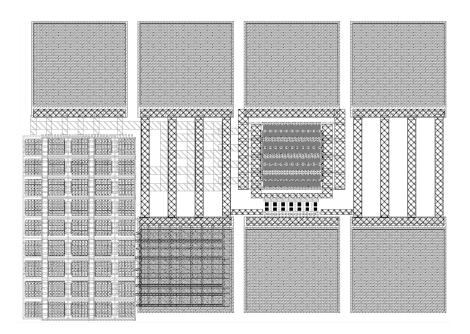

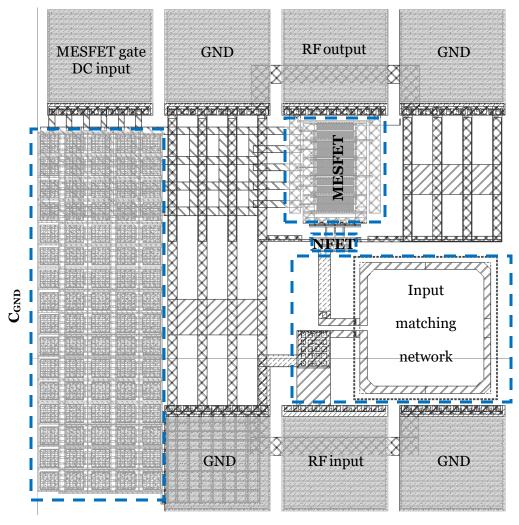

| 4.3. Left: Screen Shot of the CG MESFET and CS MOSFET Cascode Layout Using Silicon Area of 84.7 $\mu$ m $\times$ 13.4 $\mu$ m. Right: Photograph of the Die Including GSG Pads and Integrated Capacitor. Silicon Area is 414 $\mu$ m x 216.6 $\mu$ m |

| 4.4. MOSFET-MESFET Cascode Cell Schematic with a $C_{GND}$ = 52 pF                                                                                                                                                                                   |

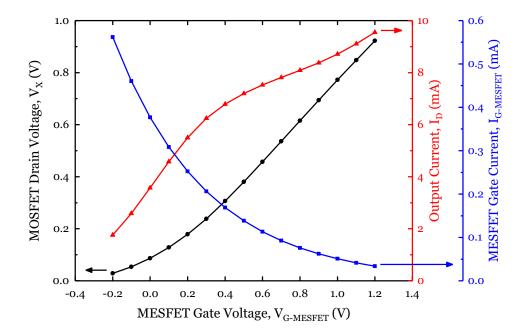

| 4.5. Simulated MOSFET Drain Voltage ( $V_X$ ), the Amplifier Output Current ( $I_D$ ), and The MESFET Gate Current ( $I_{G-MESFET}$ ) Variations with $V_{G-MESFET}$                                                                                 |

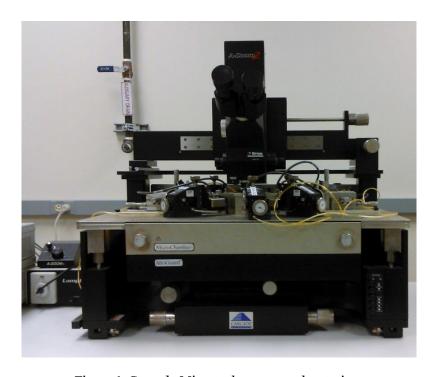

| 4.6. Cascade Microtech 11000 Probe Station                                                                                                                                                                                                           |

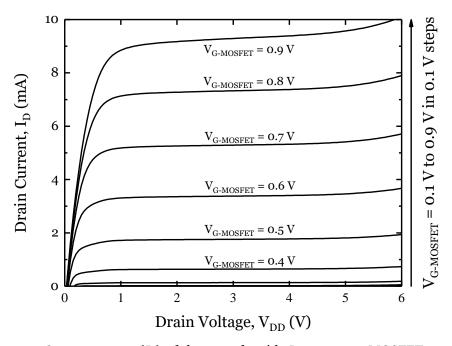

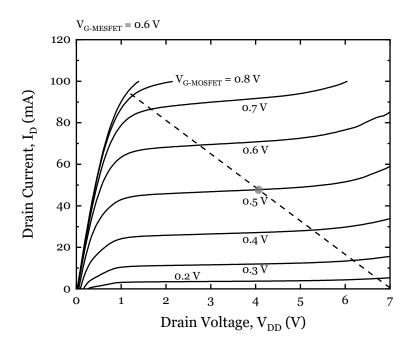

| 4.7. Output Current ( $I_D$ ) of the Cascode with $L_G$ = 112 nm MOSFET Versus Output Voltage ( $V_{DD}$ ) Measurement Results                                                                                                                       |

| 4.8. The Turn-on Characteristics of the Cascode with a $L_G$ = 112 nm MOSFET and a 300 $\mu$ m Wide MESFET, for $V_{G\text{-}MES}$ = 0.5 V, $V_{DD}$ = 2 V                                                                                           |

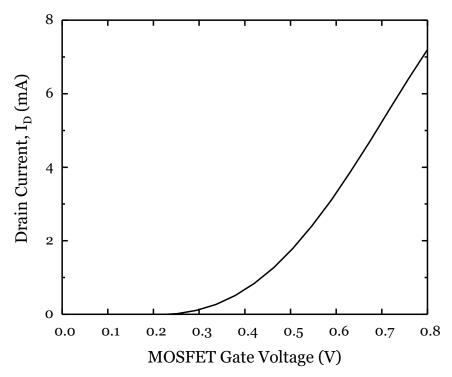

| 4.9. The Measured Drain Current of the Cascode Amplifier as a Function of Supply                                                                                                                                                                     |

| Voltage ( $V_{DD}$ ) for MESFETs with $L_{aD}$ of 200 nm and 1000 nm72                                                                                                                                                                               |

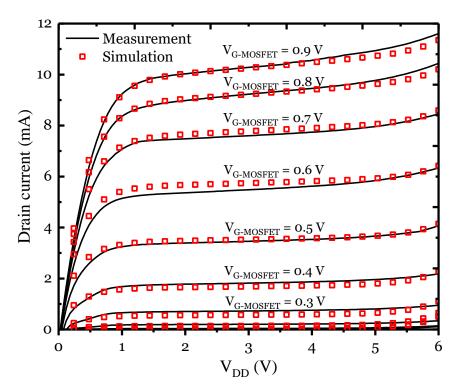

| 4.10. Cascode with $L_G$ = 40 nm MOSFET and $L_{aD}$ = $L_{aS}$ = $L_G$ = 200 nm MESFET Outpu |

|-----------------------------------------------------------------------------------------------|

| Current $(I_D)$ Versus Output Voltage $(V_{DD})$ Measurement (Line) and Simulation            |

| (Symbol) Results                                                                              |

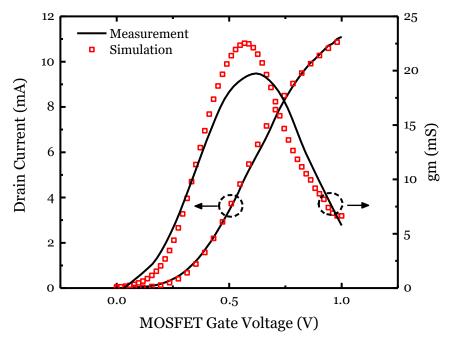

| 4.11. The Measured Drain Current and Transconductance as a Function of the MOSFET             |

| Gate Voltage. The CS MOSFET Has $L_G$ = 40 nm and $W_G$ = 20 $\mu$ m                          |

| 4.12. Cascade Microtech Impedance Standard Substrate (ISS)                                    |

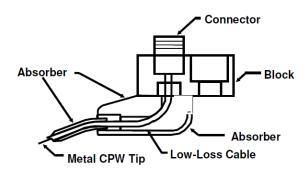

| 4.13. Air Co-Planar Transition (ACP) Probe Structure [78]                                     |

| 4.14. General PPR Steps in WinCal                                                             |

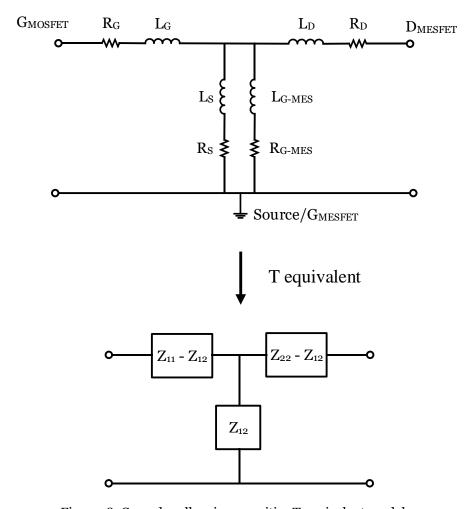

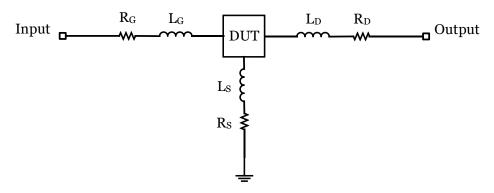

| 4.15. Cold-FET Two Port Equivalent Circuit                                                    |

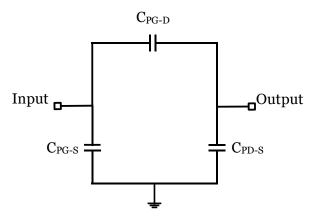

| 4.16. Pad and Coupling Parasitic Capacitances in the Cascode Cell80                           |

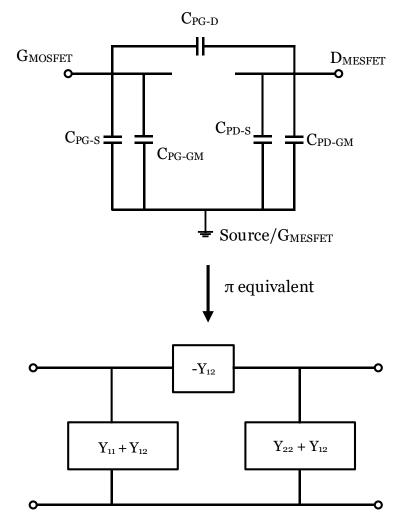

| 4.17. Cascode Cell Parasitic Capacitances $\pi$ Equivalent Model8:                            |

| 4.18. Cascode Cell Series Parasitics T Equivalent Model                                       |

| 4.19. Reverse Biased Equivalent Circuit with the Series Parasitics Removed                    |

| 4.20. Open Pads Layout Evaluated in Calibre PEX                                               |

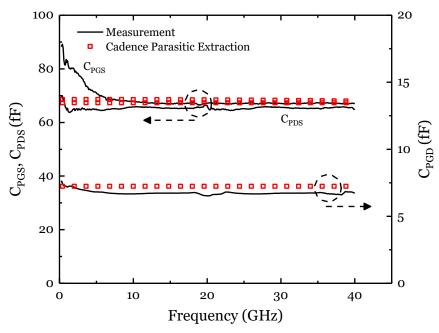

| 4.21. Solid Lines: Calculated Pad Parasitic Capacitances Through Reverse Biased Cold          |

| FET Measurement. Symbols: Calculated Pad Parasitic Capacitances Through                       |

| Calibre PEX in Cadence                                                                        |

| 4.22. Simplified Cold-FET Two Port Equivalent Circuit in Figure 4.15 After Pad Parasition     |

| Capacitances Removal88                                                                        |

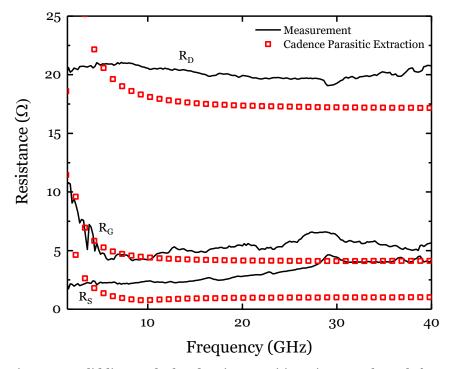

| 4.23. Solid Lines: Calculated Series Parasitic Resistances Through Forward Biased Cold        |

| FET Measurement. Symbols: Calculated Series Parasitic Resistances Through                     |

| Calibre PEX in Cadence90                                                                      |

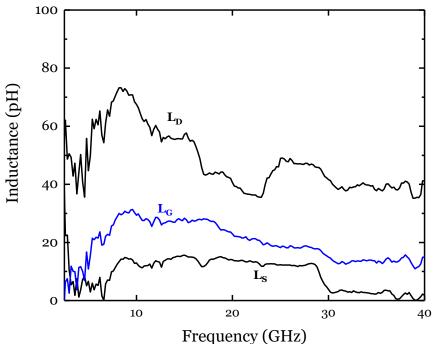

| 4.24. Calculated Series Parasitic Inductances Through Forward Biased Cold-FET                                                   |

|---------------------------------------------------------------------------------------------------------------------------------|

| Measurement91                                                                                                                   |

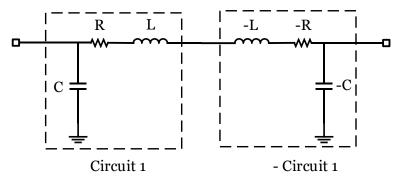

| 4.25. Keysight ADS De-embed Component Usage                                                                                     |

| 4.26. Cascode Cell Parasitics De-embedding Schematic in ADS                                                                     |

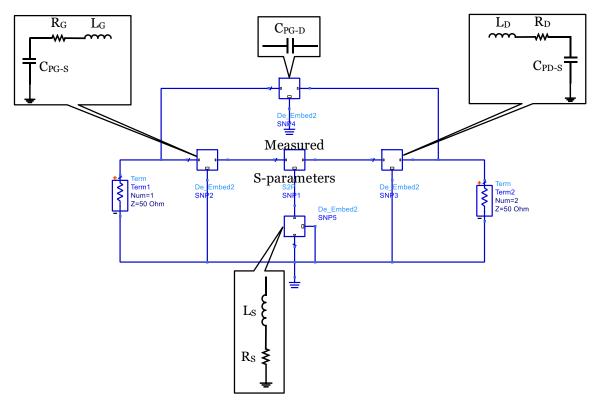

| 4.27. Comparison Between the Intrinsic and Extrinsic h21 for a Cascode Cell with $L_{G\text{-}MOSFET}$ = 112 nm                 |

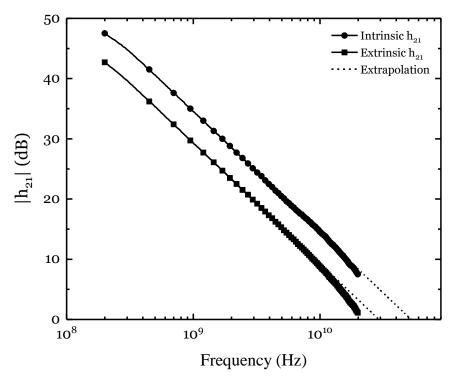

| 4.28. The Measured (Solid Lines) and Simulated (Symbols) Forward Current Gain ( <i>h21</i> ) of the CS MESFET and Cascode Cells |

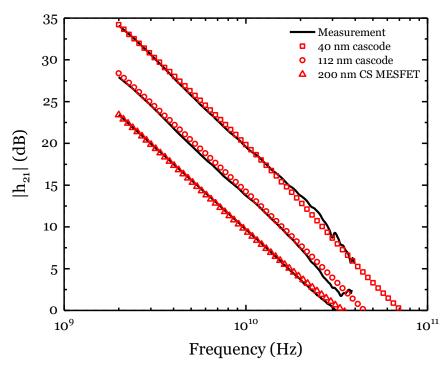

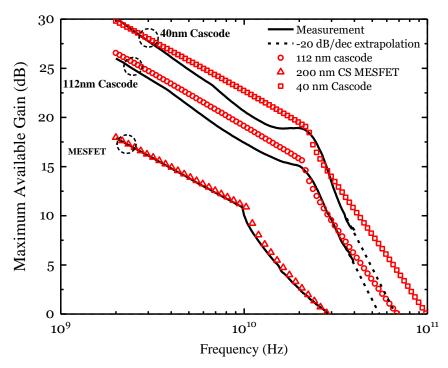

| 4.29. The Measured (Solid Lines) and Simulated (Symbols) Maximum Available Gain of the CS MESFET and Cascode Cells              |

| 5.1. Initial PA Design Comprising a 1.8 mm MOSFET and 41 mm MESFET 102                                                          |

| 5.2. Cascode PA Wire Bonded on the PCB103                                                                                       |

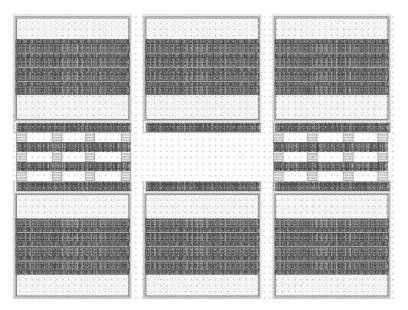

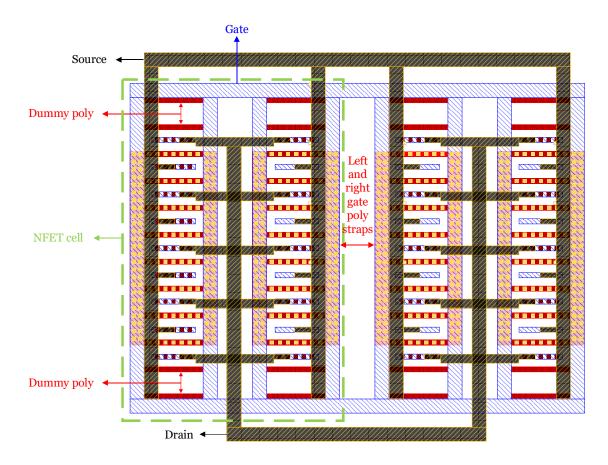

| 5.3. Optimized NFET Layout                                                                                                      |

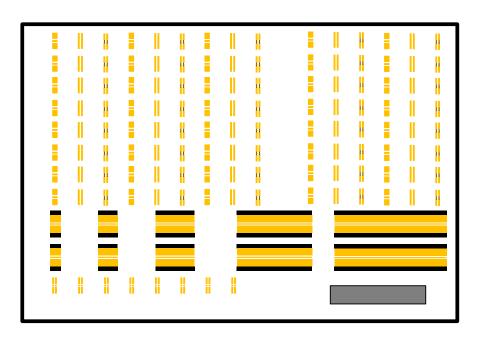

| 5.4. Layout of the Optimized MOSFET-MESFET Cascode PA109                                                                        |

| 5.5. The 0.28 mm-1.1 mm MOSFET-MESFET Power Amplifier FOC with a 0.1 W Power Limitation                                         |

| 5.6. Measured S-parameters of the Cascode PA112                                                                                 |

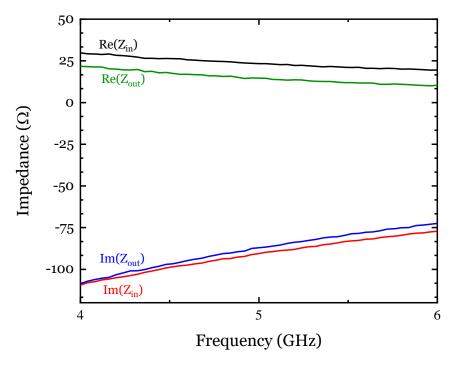

| 5.7. Measured Input and Output Impedances of the PA in the 4-6 GHz Frequency Range                                              |

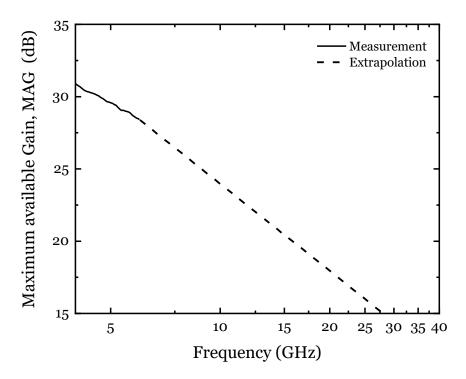

| 5.8. MAG of the PA Calculated Based on the Measured S-parameters                                                                |

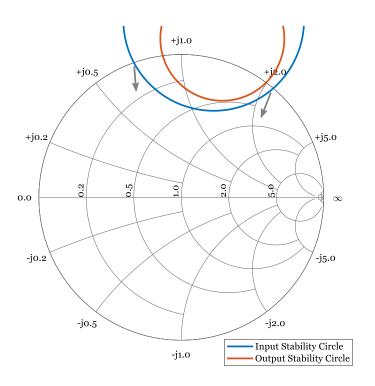

| 5.9. Input and Output Stability Circles of the PA at 5 GHz117                                                                   |

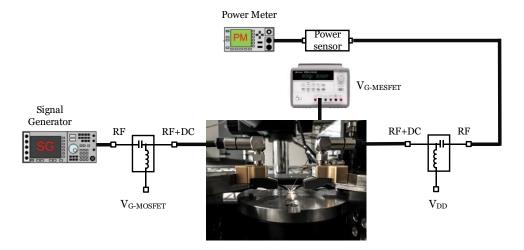

| 5.10. Large Signal Measurements Setup                                                                                           |

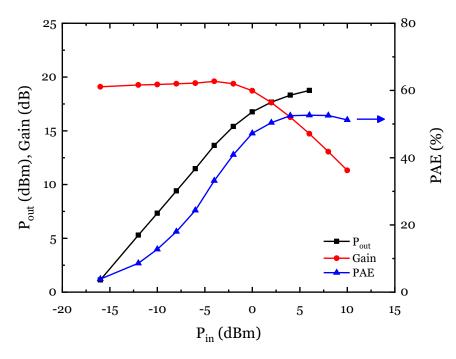

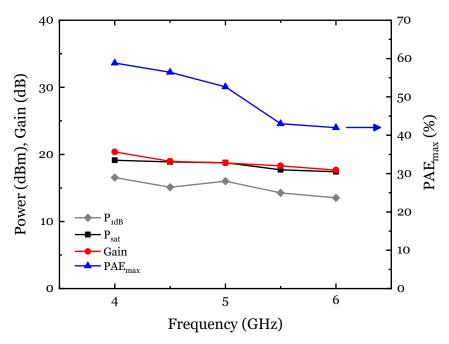

| 5.11. Gain, PAE and Output Power of the Cascode PA Plotted Versus Input Power at 5 GHz for $V_{G\text{-}MOSFET} = 0.25 \text{ V}$ , $V_{G\text{-}MESFET} = 1 \text{ V}$ and $V_{DD} = 3 \text{ V}$ |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.12. Measured Large Signal Performance Versus Frequency Under the Same Biasing Conditions as in Figure 5.9                                                                                        |

| 5.13. The Schematic of the Optimized <i>K</i> -band RF PA124                                                                                                                                       |

| 5.14. The On-chip Input Matching Network                                                                                                                                                           |

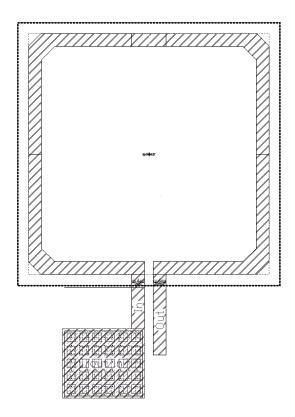

| 5.15. On-chip Input Matching Network Layout126                                                                                                                                                     |

5.16. Layout of the Optimized PA in 45RF SOI Technology......127

Page

Figure

# LIST OF TABLES

| Page                                                                                                    | Гable |

|---------------------------------------------------------------------------------------------------------|-------|

| Extracted DC Parameters from a CMOS MESFET for the First Order Angelov Model 3                          | 2.1.  |

| Small-signal Component Values Extracted for the SOI MESFETs on Trap-rich and Low Resistivity Substrates | 3.1.  |

| Cascode Amplifier Parallel Parasitic Capacitance Values                                                 | 4.1.  |

| Cascode Amplifier Series Parasitic Resistance and Inductance Values90                                   | 4.2.  |

| Characteristics of the Compared MESFET and Cascode Amplifiers                                           | 4.3.  |

| Summary of the Cascode Amplifiers RF Performance                                                        | 4.4.  |

| Performance Comparison of K-band Stacked Amplifiers                                                     | 4.5.  |

| Performance Comparison to state-of-the-art PAs at ~ 5 GHz                                               | 5.1.  |

#### CHAPTER 1

#### INTRODUCTION

The semiconductor industry is trending towards circuit manufacturing technologies which are lower in cost, higher in efficiency and integration of features, and more reliable. Complementary metal-oxide semiconductor (CMOS) is widely adopted since it offers mass integration of MOSFET transistors with lower cost. Silicon on insulator (SOI) substrates are also used in CMOS processes since they reduce parasitic capacitances, leakage current, have better sub-threshold swing and higher drive current [1]. CMOS technology is continuously scaled down to decrease the feature size and increase the integration of transistors, as well as lowering the supply voltage and power of the system which are all advantages for digital designers. However, the maximum allowable voltage on the scaled technology nodes is limited and is getting lower still as the technology is further scaled down. Lower voltages means lower output power and is not desirable for RF designers. RF blocks such as power amplifiers (PA) are high power devices (preferably more than a Watt) and the lower supply voltage of scaled technology nodes impose an undesirable restriction for the RF designers to achieve high powers. This problem will limit the usefulness of SOI CMOS technology for RF applications despite of all its advantages.

To overcome the low-output-power problem in scaled technology nodes, PAs are mostly fabricated in GaAs technologies which are more expensive, but offer higher cutoff frequency ( $f_t$ ), operating voltage, and better linearity. On the other hand, the mobile communications industry is pushing towards fully integrated CMOS processes due to the aforementioned reasons [2]. Furthermore, high transistor cutoff frequencies are now attainable in deep sub-micron technologies and integration of RF and digital CMOS circuits is now feasible. Hence, it is worth investigating solutions to increase the operating

voltage of deep sub-micron technologies. As the transistor size becomes smaller, the breakdown voltage of the transistor also decreases and this is the main reason why we cannot apply higher operating voltages. Lateral-diffused MOSFETs (LD-MOSFET) were developed to increase the breakdown voltage to possibly over 100V by creating a lateraldrift region between the end of the channel and the drain region [3]. To fabricate LD-MOSFETs, some process modifications need to be made to the CMOS process which make them more expensive and not suitable for all applications. This type of transistor also uses a thicker gate oxide which degrades the frequency performance of the device. Another technique is higher impedance transformation which reduces voltage swings on the transistor which leads to higher supply voltage value. But this technique causes more losses in the matching network and the overall efficiency is not high [4]. Another common solution is to use several die which have been fabricated in different technologies and embed them into one module. These modules usually contain a GaAs power amplifier, a pseudomorphic high-electron-mobility-transistor RF switch, and a high voltage CMOS power management die which are all bounded to a laminate [5]. Obviously, we need different technologies and processes to make such a module and the final price of the product will be high.

One of the best solutions to increase the operating voltage of deep sub-micron technologies which has been studied by our group is using SOI metal-semiconductor-field-effect-transistors (MESFET). Silicon on insulator MESFETs are CMOS compatible devices and can be fabricated with no change to the process [6]. More well-known GaAs MESFETs are not CMOS compatible. The breakdown voltage of the MESFET depends on the transistor size and geometry and also the process technology, and is at least 2-15 times greater than MOSFET transistors. Other advantages of MESFETs are depletion mode operation [7] and radiation tolerance [8].

#### CHAPTER 2

#### **CMOS SOI MESFETS**

The demand for low-cost CMOS RFICs is being driven by a number of rapidly growing markets including consumer wireless devices, automotive electronics as well as the anticipated Internet of Things. High-volume CMOS foundries are well positioned to support this anticipated demand using commercially successful digital platforms. However, the low operating voltage of the digital CMOS is challenging for RFIC design, especially for any power blocks including the RF power amplifier (PA). In this chapter the enhanced voltage handling capability of a CMOS-compatible MESFET is investigated as an approach which can be adopted to generate higher output power level PAs than conventional methods and transistors in CMOS technology. The device structure and manufacturing considerations, design tradeoffs, DC and RF characterization, the effect of substrate bias on DC performance, and modeling of the CMOS compatible MESFETs are discussed in this chapter.

### 2.1. CMOS MESFET Fabrication

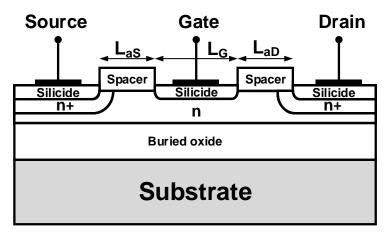

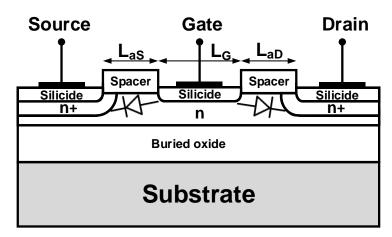

MESFETs can be fabricated with no changes to the standard CMOS process flow [9]. The key process requirement is the availability of a silicide block step, which is commonly available to form passive resistor components in the active silicon layer. For MESFET fabrication the silicide block is used to create spacer regions between the gate and the source (source access length,  $L_{aS}$ ), and between the gate and the drain (drain access length,  $L_{aD}$ ). The gate length ( $L_G$ ) is also controlled by the distance between the source and drain spacers. The MESFET cross section is shown in Figure 2.1.

The transistor gate oxide breakdown is an important limitation in increasing the operating voltage in CMOS technology. As the technology scales down, the transistor gate oxide thickness decreases. Large voltages applied to the transistor gate increases the electrical stress on the device:

$$E = \frac{V_{ox}}{t_{ox}}$$

(2.1)

Narrower gate oxide increases the electric field intensity at the gate terminal of the transistor and to avoid the oxide breakdown, lower voltages should be applied. The gate of the MESFET transistor as shown in Figure 2.1, does not have an oxide layer and consists of a silicide layer which is formed above the lightly doped n-channel. Therefore, the gate is a metal-semiconductor junction and behaves like a Schottky diode and the barrier height controls the voltage swing on the gate [6]. Hence, the MESFET gate can tolerate higher voltages which comes at a price however. The current leakage flowing through the Schottky junction is large and varies exponentially with the voltage on the transistor gate. This can generate large gate leakage currents flowing out of the gate at higher supply voltages and increases the power dissipation.

Another cause of the transistor breakdown in deep sub-micron technologies is the drain-source breakdown which happens due to the strong electric field between the two terminals as the supply voltage increases. The MESFET contacts are not self-aligned and this characteristic can be used to increase the voltage handling capability of the device. If the drain and source access lengths are increased, the electric field between the gate and source/drain junctions also plummets. The source of the transistor is often grounded. The quiescent gate voltage is also set to be close to 0 V in the scope of this thesis as a  $V_{GS} \sim 0$  V maximizes the MESFET transconductance which will be discussed later. As a result, a huge voltage drop across the gate-source junction is not expected and  $L_{aS}$  does not need to be

extended extravagantly. However, the main purpose of deploying MESFETs is increasing the supply voltage (as high as 15 V) to increase the output power. Considering the range of voltages on the gate terminal, the electric field on the gate-drain junction will be much more intense, and  $L_{aD}$  should be elongated more than  $L_{aS}$  to mitigate the electric field at the gate-drain junction if higher breakdown voltage is needed.

Fig. 2.1. Cross section view of an N-type SOI MESFET transistor on a P-type substrate.

The silicide over the highly doped n regions in Figure 2.1 forms the low resistance source and drain ohmic contacts, as the highly doped n regions have much higher conductivity. These ohmic contacts won't impede with the electric current flow in the transistor from the source to the drain. The drain and source access lengths play an important role in the DC and RF performance of the MESFET, and can be varied to reach a trade-off to fit the desired application. The longer the access lengths, the larger the breakdown voltage ( $V_{BD}$ ) and the parasitic resistance stemming from the long spacer regions. As a result, the transistor current drive and cutoff frequency ( $f_T$ ) degrades. A higher voltage can also be applied to the gate terminal of the device since there is no gate oxide. MESFETs were initially fabricated with GaAs technology [10], but it would not be possible to integrate such transistors with other blocks which mostly are built in CMOS.

Consequently, SOI MESFET transistors are a suitable choice to design high output stages which can be integrated on wafer with CMOS technology.

MESFET breakdown mostly happens due to impact ionization and avalanche breakdown, which is categorized into soft breakdown and hard breakdown. Soft breakdown, unlike hard breakdown, doesn't cause a permanent damage to the transistor and can be reversed by reducing the local electric field, or annealing the device at higher temperatures which repairs the traps close to the metal-semiconductor interface. The transistor performance can be almost fully recovered after a soft breakdown. The reason behind the breakdown mechanism is large local electric fields applied to the transistor. When the supply voltage increases, it creates stronger electric fields and provides more energy to the electrons in the conduction or valence bands. The semiconductor Fermi level, unlike the constant metal Fermi level, changes under the external electric field and reduces the barrier height at the gate. The electron tunneling probability becomes higher as a consequence, and more electrons can tunnel from the gate metal into the transistor channel. This is how more current is generated through impact ionization. If the supply voltage further increases, it will eventually cause an avalanche breakdown which causes much larger current flow during stress.

The zero bias depletion region under the silicide Schottky gate is less than the thickness of the SOI channel. As a result, the MESFETs operate as depletion mode devices with a negative threshold voltage ( $V_{th}$ ).

SOI transistors suffer from body effects such as the kink effect. To solve this issue, a body contact is needed in SOI CMOS technology to eliminate the body effects. Since MESFETs are majority carrier devices, body effects do not appear and no body contact is needed, thereby simplifying the design of the SOI MESFET. MESFETs can be fabricated using partially depleted (PD) and also fully depleted (FD) CMOS technology. We concentrate on partially depleted MESFETs in this research project. The depletion layer width is less than the silicon layer under the gate in PD MESFETs, and the gate voltage adjusts the width of the depletion region and the current flow in the channel.

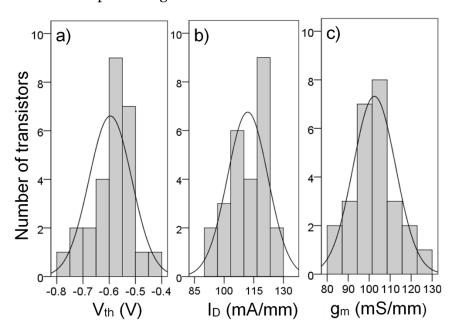

Fig. 2.2. Measured distributions in a) threshold voltage, b) current drive, and c) transconductance from three different multi-project wafer runs. The fitted bell curves are used to extract the mean and standard deviations [11].

The run-to-run variations in the MESFET characteristics depend largely on the thickness of the self-aligned silicide (salicide) layer, and the variations in  $L_{aS}$  and  $L_{aD}$ . These parameters are well-controlled during the 45 nm CMOS fabrication, allowing for good MESFET manufacturability. Process monitor devices with minimum size dimensions of  $L_G = L_{aS} = L_{aD} = 200$  nm were fabricated during three separate multi-project wafer runs, each separated by 3-4 months. Figure 2.2 [11] shows preliminary

measurements of the distributions in the threshold voltage, current drive and transconductance for 26 devices.

### 2.2. MESFET Operating Regions

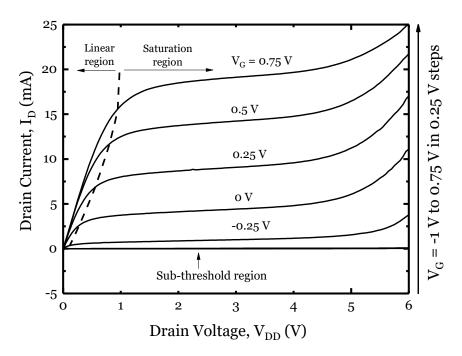

MESFETs are depletion mode devices and they can be turned on and enter the saturation region when  $V_{GS}$  has a negative value. Same as with MOSFETs, three regions of operation are defined for MESFET transistors as shown in Figure 2.3.

Fig. 2.3. Family of curves (FOC) of a 45 nm SOI MESFET (W=300  $\mu$ m,  $L_G = L_{aD} = L_{aS} = 200 \ \mu$ m),  $V_{BS} = 0$ V.

## Sub-threshold region

When the gate voltage is lower than the threshold voltage, there is an exponential relation between the gate voltage and drain current:

$$I_{\text{sub}} = I_{\text{o}} \cdot e^{\frac{V_{\text{GS}} - V_{\text{t}}}{N_{\text{G}} \cdot V_{\text{t}}}} \left( 1 - e^{\frac{-V_{\text{DS}}}{V_{\text{t}}}} \right)$$

(2.2)

where

$N_G$  = ideality factor of the Schottky gate junction

$I_S$  = saturation current

Based on the above formula, the drain voltage in the sub-threshold region has a low impact on the drain current, especially when  $V_{DS}$  is at least three times greater than  $V_{th}$ . In this region,  $I_D$  is the result of carrier diffusion. Since there is a lightly doped channel in the diode, the mobility of the carriers are higher than MOSFET transistors and the cutoff frequency of MESFETs in sub-threshold region is almost five times higher than MOSFETs with the same sizing [12]. MESFETs in the sub-threshold region can be used in micro power applications and the reverse gate leakage current can be used to control the drain current [13]. If a negative gate voltage is applied to the device, the gate leakage current will increase until it dominates the drain diffusion current.

### Linear region

A depletion region is formed under the Schottky barrier when  $V_{GS} > V_{th}$  which is wider at the drain end since the drain voltage creates a reverse bias across the channel-gate junction. In this region, when  $V_{DS}$  is small, the drain current will increase linearly as the drain voltage is increased and that is the reason why it is called the linear region [14]. The drain current,  $I_D$ , of the linear region can be calculated using the following formula:

$$I_{D} = \frac{q \mu_{n} N_{d} d_{eff} W}{L_{G}} \left( V_{D} - \frac{2}{3\sqrt{V_{p}}} \left( \sqrt{(\phi_{i} - V_{GS} + V_{DS})^{3}} - \sqrt{(\phi_{i} - V_{GS})^{3}} \right) \right)$$

(2.3)

Where

$\mu_n$  = channel mobility (cm<sup>2</sup>/ Vs)

d<sub>eff</sub> = undepleted channel width (cm)

W = channel width (m)

$L_G$  = channel length (m)

$N_d$  = channel doping density (cm<sup>-3</sup>)

$\phi_i$  = gate built-in potential (eV)

Linear increase in the drain current with increasing drain voltage continues until the width of the depletion region is equal to the channel thickness [15]. This point is called the pinch-off point and the corresponding drain voltage is called "saturated drain voltage ( $V_{Dsat}$ ). Any increase in the drain voltage beyond this point will not change the width of the depletion region and  $I_D$  becomes saturated; Equation 2.3 will no longer be valid.

### Saturation region

Ideally, if  $V_D > V_{Dsat}$ , the drain current is independent of drain voltage. But since the increase in the drain voltage reduces the effective channel length,  $I_D$  slightly increases with  $V_D$  after the pinch-off point. Hence, a channel length modulation factor should be added to Equation 2.3:

$$I_{D} = \frac{q \mu_{n} N_{d} d_{eff} W}{L_{g}} \left( V_{D} - \frac{2}{3\sqrt{V_{p}}} \left( \sqrt{(\phi_{i} - V_{GS} + V_{DS})^{3}} - \sqrt{(\phi_{i} - V_{GS})^{3}} \right) \right) (1 + \lambda V_{DS})$$

(2.4)

## • High voltage region

If we keep increasing the drain voltage, breakdown happens due to the gate-drain junction tunneling and avalanche mechanisms [6]. The MESFET breakdown voltage is

higher than that of a MOSFETs with the same size since they don't have a thin oxide layer at the gate. In addition, the access region between the gate and source and also drain in MESFETs, increases the breakdown voltage.

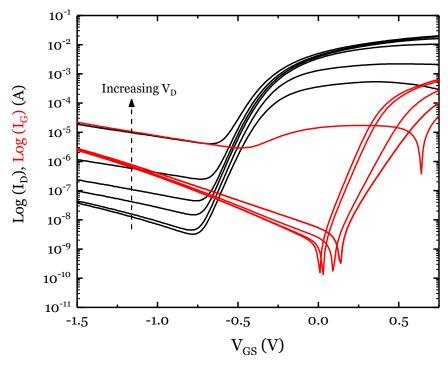

Figure 2.4 shows the Gummel plots of the same MESFET transistor used in Figure 2.3. The gate voltage is swept from -1.5 V to 0.75 V for different values of drain voltage (0.025, 0.25, 0.5, 1, 2 and 4 V). As can be seen, the transistor turns on and enters the saturation region for negative gate voltages ( $V_{th}$  is negative) since it is a depletion mode device.  $V_{th}$  is also slightly changing with drain voltage. The transistor is off when  $V_{GS} < V_{th}$  and if the gate voltage is decreased below  $V_{th}$ , the reverse bias voltage on the Schottky gate will increase which leads to an increasing gate leakage current. As explained, there is a direction change in the gate current and  $I_G$  values vary from negative (leakage) to positive (forward bias) and has a zero crossing. Since a logarithmic scale is used on the vertical axis and log (o) is not defined, a low value discontinuity is created.

Fig. 2.4. Gummel plots of a 45 nm SOI MESFET (W = 300  $\mu$ m,  $L_G = L_{aD} = L_{aS} = 200 \,\mu$ m),  $V_{BS} = 0 \,\text{V}$ , -1.5 V <  $V_{GS} < 0.5 \,\text{V}$ ,  $V_D = 0.025$ , 0.25, 0.5, 1, 2 and 4 V.

### 2.3. MESFET DC and RF Characterization

Figures 2.3 and 2.4 illustrated typical family of curves (FOC) and Gummel plots for a 300  $\mu$ m wide MESFET transistor with  $L_G = L_{aD} = L_{aS} = 200 \ \mu$ m. As explained in 2.1, extending the drain side silicide spacer in order to increase  $L_{aD}$  will increase the drain-source junction break-down voltage, as it diminishes the electric field intensity at this critical junction. However, the further parasitic resistance introduced by the larger spacer block reduces the current flowing into the drain terminal, also degrades the RF performance of the device. Figure 2.5 shows the family of curves for two MESFETs with different drain access lengths. The MESFET body terminal is connected to the die substrate, which is referred to as the global ground in Cadence layout. The probe station chuck was grounded for the measurements. Hence, when the die is placed on top of the chuck, its substrate is grounded as well and results in  $V_{body} = 0$  V.

Fig. 2.5. The family of curves for MESFETs with drain access lengths of 200 nm (squares) and 1000 nm (triangles). For both devices  $L_G = L_{aS} = 200$  nm.

As expected, the device with  $L_{aD}$  = 200 nm has a higher current drive and lower on-resistance, while the device with  $L_{aD}$  = 1000 nm has a significantly higher breakdown voltage, along with an increased saturated output resistance. The device with a shorter  $L_{aD}$  has a soft breakdown voltage of ~ 4 V, above which the drain current slowly rolls off with increasing  $V_{DD}$  due to leakage from the drain-gate junction of the MESFET [6]. Measurements of the turn-on characteristics of each device indicate similar threshold voltages of approximately -0.65 V for both devices.

The high breakdown voltage of the MESFET with  $L_{aD}$  = 1000 nm sacrifices the RF performance of the device. To study the RF performance degradation, two of the RF figures of merit are compared for the two MESFET sizes mentioned above:

• Cut-off frequency ( $f_T$ ): the transition frequency at which the transistor's small signal current gain equals to unity:

$$A_{i}(j\omega) = \frac{I_{out}(j\omega)}{I_{in}(j\omega)} = 1$$

(2.5)

$$f_{T} = \frac{g_{m}}{2\pi \left(C_{gs} + C_{gd}\right)}$$

(2.6)

$f_T$  is an intrinsic characteristic of the transistor, meaning that the effect of the parasitics stemming from the pads and layout interconnects needs to be removed from the measurements. For  $f > f_T$ , the transistor will not be able to provide any current gain. Throughout this thesis,  $f_T$  was derived from the DUT S-parameter measurements, and calculation of the forward current gain  $(h_{21})$  zero crossing. The relation between  $h_{21}$  and S-parameters is as below:

$$h_{21} = \frac{-2 S_{21}}{S_{21}S_{12} + (1 - S_{11})(1 + S_{22})}$$

(2.7)

As expected, the forward current gain (h21) is also dependent on the transistor biasing and intrinsic capacitances:

$$h_{21} = \frac{g_m - j\omega C_{gd}}{j\omega \left(C_{gs} + C_{gd}\right)}$$

(2.8)

• Maximum oscillation frequency ( $f_{max}$ ): the frequency at which the transistor's maximum power gain reaches o dB.

$$f_{\text{max}} = \frac{f_{\text{T}}}{2\sqrt{2\pi f_{\text{T}} R_{\text{G}} C_{\text{gd}} + \frac{R_{\text{G}} + R_{\text{S}}}{r_{\text{o}}}}} \approx \frac{f_{\text{T}}}{\sqrt{8\pi R_{\text{G}} C_{\text{gd}}}}$$

(2.9)

For frequencies greater than  $f_{max}$ , the transistor won't provide any power gain and there is no point in utilizing that. To find  $f_{max}$ , the maximum available gain (MAG, also called  $G_{max}$ ) can be plotted versus frequency and the zero crossing will give the  $f_{max}$  value. The MAG equation assumes the transistor is conjugate matched to the input and output ports for the maximum power transfer at each frequency. MAG is not defined for unstable two port networks.  $K-\Delta$  test is a prevalent way to verify the stability of the DUT. For a two port to be stable,  $\Delta$  (determinant of the S-parameters matrix) should be less than one, and the Rollett's stability factor (K) should be greater than 1:

$$\begin{cases} \Delta = S_{11}S_{22} - S_{21}S_{12} < 1 \\ \\ K - \Delta \text{ test for two port stability} \end{cases}$$

(2.10)

$$\begin{cases} K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{12}| |S_{21}|} \geq 1 \end{cases}$$

(2.11)

Keysight ADS software was used to analyze the measured S-parameter data. If the measured S-parameters matrix give K < 1, the software automatically sets K = 1 to ensure the two port stability requirement is met. This means the MAG and  $f_{max}$  values that the software reports are under the assumption that the two port is stabilized, and conjugate matched to the input and output ports which can be considered as the potential capability of the DUT. Last but not least, MAG is calculated through Equation 2.12:

MAG =

$$\frac{|S_{21}|}{|S_{12}|} \left( K - \sqrt{K^2 - 1} \right)$$

(2.12)

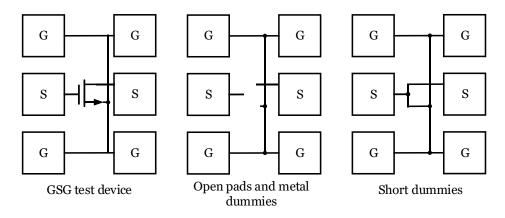

### 2.3.1. MESFET DC and RF Performance Dependence on LaD

To study the effect of longer drain access lengths on the MESFET RF performance, the h21 and MAG plots are compared for 3 different  $L_{aD}$  values (200 nm, 500 nm and 1000 nm) in Figures 2.6 and 2.7 respectively. All the MESFETs have an equal width of 300 µm. The MESFETs were designed with a ground-signal-ground (GSG) pad configuration to allow DC and RF probing of individual die to measure the S-parameters using an 8510C vector network analyzer under different bias conditions. The plots show the maximum measured  $h_{21}$  and MAG, which means  $V_{GS}$  was set to 0.1 V which maximizes the MESFET gm. The S-parameter measurements and pad parasitic de-embedding were done in Cascade Microtech Wincal software. Open GSG pads were used to de-embed the measured S-parameters to obtain the intrinsic forward current gain,  $h_{21}$ , and the maximum available gain (MAG). As expected, the higher voltage devices with  $L_{aD}$  of 1000 nm have lower peak cutoff frequency,  $f_T$  and lower maximum oscillation frequency,  $f_{max}$  than the  $L_{aD} = 200$  nm and 500 nm devices. Figure 2.8 summarizes the measurement results and illustrates the possible design choices that are available when considering trade-offs between high voltage and high frequency operation. The MESFET with  $L_{aD}$  = 200 nm exhibits the maximum measured  $f_T$  of 27.7 GHz. As  $L_{aD}$  is extended to 500 nm and 1000 nm,  $f_T$  experiences a drop to 21.2 GHz and 17.2 GHz respectively. Likewise, the measured  $f_{max}$  for  $L_{aD}$  = 200 nm, 500 nm and 1000 nm was 30.8 GHz, 26.4 GHz and 23.6 GHz respectively.

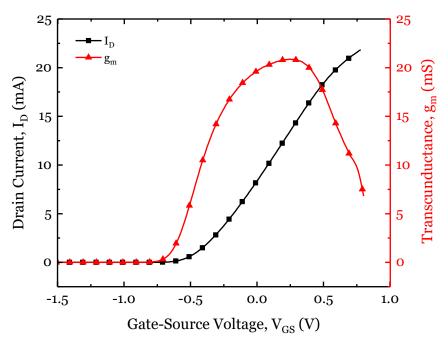

The insets in Figures 2.6 and 2.7 emphasize the importance of DC biasing on the RF figures of merit. As the drain current increases with biasing,  $f_T$  and  $f_{max}$  values also increase, until the drain current starts to saturate and reduces the transistor  $g_m$ . This phenomenon can also be seen in the FOC in Figure 2.5. For a fixed  $V_{DD}$  value, the distance between the current curves  $(g_m)$  gets reduced as  $V_{GS}$  is increased. So there exists a biasing sweet spot which maximizes the  $g_m$  and RF figures of merit. To clearly illustrate the MESFET  $g_m$  variations with respect to  $I_D$ , Figure 2.9 is presented which shows the measured results for a MESFET with all the access lengths equal to 200 nm while biased with  $V_{DD} = 2$  V.

Fig. 2.6. The de-embedded  $h_{21}$  as a function of frequency for devices with different drain access lengths of 200 nm, 500 nm and 1000 nm. The devices were biased with  $V_{GS} = 0.1$  V and  $V_{DS} = 3$  V.

Fig. 2.7. The de-embedded MAG as a function of frequency for devices with different drain access lengths of 200 nm, 500 nm and 1000 nm. The devices were biased with  $V_{GS} = 0.1 \text{ V}$  and  $V_{DS} = 3 \text{ V}$ .

Fig. 2.8. MESFET  $f_T$ ,  $f_{max}$  and breakdown voltage variations with respect to  $L_{aD}$  ( $L_G$  = 200 nm)

Fig. 2.9. MESFET  $g_m$  and  $I_D$  variation with respect to  $V_{GS}$  ( $V_{DD} = 2$  V,  $L_{aD} = L_{aS} = L_G = 200$  nm).

### 2.3.2. MESFET DC and RF Performance Dependence on $L_G$

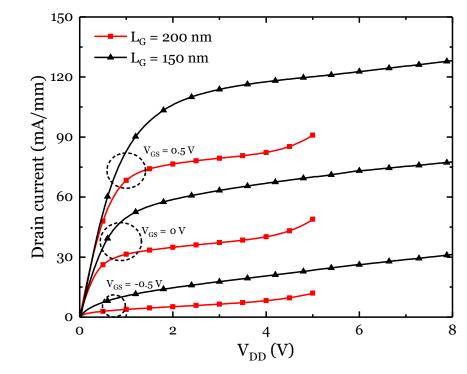

Another takeaway from Equation 2.6 is the inverse relation between  $f_T$  and the transistor gate length. So far, the impact of the MESFET drain access length on the RF performance has been studied in this chapter. To increase the operating frequency of the MESFET, it is worth investigating the gate length ( $L_G$ ) reduction as well. To address this question, a MESFET with a 25% shorter gate length, i.e.  $L_G$  = 150 nm compared to the 200 nm gate length MESFET was studied. Both transistors were 300  $\mu$ m wide. Furthermore, to enhance the voltage capability of the 150 nm gate length MESFET alongside its RF performance, the drain and source access lengths were also increased by 50%, i.e.  $L_{aD}$  =  $L_{aS}$  = 300 nm. The expectation should be increased  $V_{BD}$  due to longer silicide spacers, and higher  $f_T$  in comparison to the  $L_{aD}$  =  $L_{aS}$  = 200 nm MESFET.

As the measured FOC in Figure 2.10 shows, both the current drive ability and transconductance of the MESFET with  $L_G$  = 150 nm,  $L_{aD}$  =  $L_{aS}$  = 300 nm are substantially greater than the  $L_G$  =  $L_{aD}$  =  $L_{aS}$  = 200 nm counterpart due to shorter gate length. Although the source and drain access lengths of the  $L_G$  = 150 nm MESFET are longer and introduce higher parasitic resistance values, the effect of the reduced gate length is dominant and the overall DC performance of the MESFET is superior to the  $L_G$  = 200 nm MESFET. While the drain current in the  $L_G$  = 200 nm MESFET starts to roll off close to  $V_{DD}$  = 5 V, the  $L_G$  = 150 nm MESFET exhibits a steady performance up until  $V_{DD}$  = 8 V thanks to its longer  $L_{aD}$  (300 nm, vs. 200 nm for the  $L_G$  = 200 nm MESFET). It should be emphasized that both of these devices are fabricated on a 1 V technology node.

Fig. 2.10. FOC comparison between  $L_G = L_{aD} = L_{aS} = 200$  nm, and  $L_G = 150$  nm,  $L_{aD} = L_{aS} = 300$  nm MESFETs.

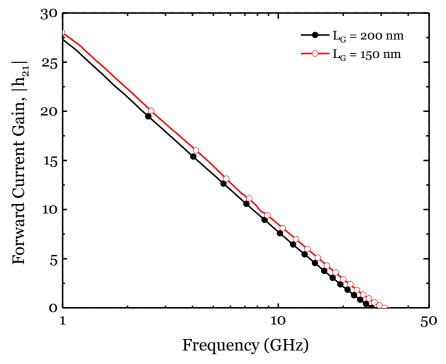

Apart from the DC performance, reducing the MESFET gate length by 50% results in a  $\sim$  12.5% increase in the device  $f_T$ . The forward current gain of the  $L_G$  = 200 nm

MESFET in Figure 2.6 is compared to the  $L_G$  = 150 nm MESFET, and the results are presented in Figure 2.11.  $V_{GS}$  was set to 0.1 V for both devices, but  $V_{DS}$  of the  $L_G$  = 150 nm MESFET was increased to 5 V due to its higher voltage handling capability, while  $V_{DS}$  was kept at 3 V as before for the  $L_G$  = 200 nm device. The measured  $f_T$  of the  $L_G$  = 150 nm MESFET is increased to 31.5 GHz with respect to  $f_T$  = 28 GHz for the  $L_G$  = 200 nm MESFET, which concludes that the RF performance is also superior.

Fig. 2.11. MESFET Cut-off frequency ( $f_T$ ) dependence on the gate length ( $L_G$ ).

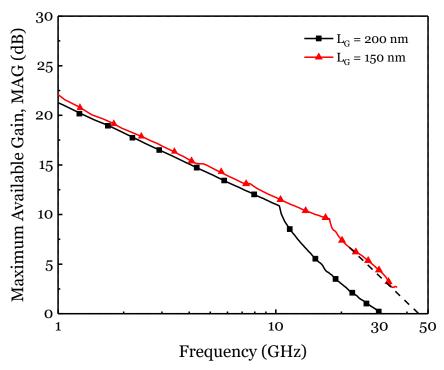

Since  $f_{max}$  is proportional to  $f_T$ , a higher  $f_{max}$  is expected for the  $L_G$  = 150 nm MESFET as well. Under the same biasing conditions as in Figure 2.11, the -20 dB/dec extrapolation line (dashed) in Figure 2.12 suggests a  $f_{max} \sim 44$  GHz for the  $L_G$  = 150 nm MESFET, increased from  $f_{max} \sim 31$  GHz for the  $L_G$  = 200 nm MESFET. Overall, considering the trade-off between the DC and RF performance of the MESFET, the transistor layout can be engineered to deliver the optimum performance which fits the application requirements the best.

Fig. 2.12. Maximum oscillation frequency ( $f_{max}$ ) dependence on the gate length ( $L_G$ ).

### 2.3.3. MESFET RF Performance Dependence on the Gate Finger Width $(W_t)$

Another parameter which can be taken into consideration while optimizing the MESFET layout design is the number of gate fingers (N) and the width of individual gate fingers ( $W_f$ ). To make the layout of a large transistor more compact, get a more reasonable aspect ratio, and reduce the total gate resistance the transistor can be divided into multiple fingers. The total transistor width ( $W_T$ ) will be:

$$W_{T} = N \times W_{f} \tag{2.13}$$

Figure 2.13 illustrates the idea behind the multi-finger transistors. The drain/source area is in common between two adjacent transistors and reduced the total occupied space. The effective width ( $W_{eff}$ ) of the transistor with two fingers is twice as much as the single finger transistor, while the gate length of the two is the same.

Fig. 2.13. left: single finger transistor, right: transistor with two fingers ( $W_{eff} = 2W$ ,  $L_{eff} = L$ ).

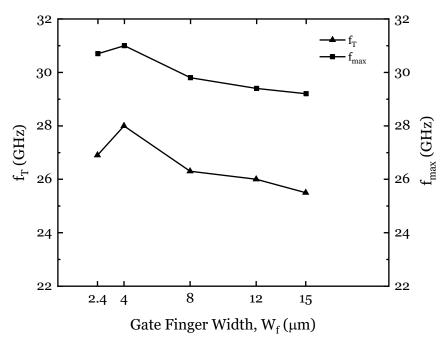

The gate finger width  $(W_f)$  and the total number of gate fingers affect the RF performance of the MESFET. Albeit, no noticeable dependency was detected in the DC measurement results of the MESFETs with different  $W_f$ . To clearly show the RF performance dependency on  $W_f$ , the intrinsic  $f_T$  and  $f_{max}$  of separate MESFETs with equal total width  $(W_T)$  of 300  $\mu$ m and different gate finger widths  $(W_f)$  of 2.4  $\mu$ m, 4  $\mu$ m, 8  $\mu$ m, 12  $\mu$ m and 15  $\mu$ m were measured and compared. All the MESFETs had gate and access lengths of  $L_G = L_{aD} = L_{aS} = 200$  nm. The total number of fingers can be calculated from Equation 2.13. The comparison results are presented in Figure 2.14, which are in accordance with the reported trends in literature [16].

Fig. 2.14.  $f_T$  and  $f_{max}$  variations with respect to the gate finger width ( $W_f$ ).

Parasitic capacitances increase as the finger width gets larger and as Equation 2.6 suggests,  $f_T$  drops with increasing parasitic capacitances. Another parameter which attributes to the  $f_T$  dependency on  $W_f$  is the transistor distributed gate resistance  $(R_G)$ . The cutoff frequency equation does not contain  $R_G$ , as  $f_T$  excludes the transistor junction parasitics such as  $R_G$ , sidewall junction capacitances, etc. by definition [17]. Consequently, to calculate the cutoff frequency, the transistor is considered as an ideal current source. The distributed gate resistance however, forms an RC filter with the transistor capacitances which can eventually restrict the switching speed.  $R_G$  can be calculated through Equation 2.14:

$$R_{\rm G} = \frac{R_{\rm sh} W_{\rm f}}{3 \, n^2 \, L_{\rm G}} \tag{2.14}$$

where

$R_{sh}$  = sheet resistance of silicide

$W_f$  = gate finger width

# n = number of gate contacts

As the above equation suggests, larger  $W_f$  leads to higher gate resistance which reduces  $f_T$ . An inconsistency is witnessed between 2.4  $\mu m$  and 4  $\mu m$  finger widths, which is believed to ensue from the total number of gate fingers. To construct a 300  $\mu m$  wide MESFET, 67% more gate fingers are required when using 2.4  $\mu m$  wide fingers instead of 4  $\mu m$  (125 versus 75). The extravagantly increased number of fingers contribute to the total parasitic capacitances and become the dominant parameter which degrades  $f_T$ . The conclusion which can be drawn is there should be a lower limit in reducing  $W_f$ .

$f_{\text{max}}$  is proportional to  $f_T$  based on Equation 2.9, so the same trend is expected for  $f_{\text{max}}$  variations with respect to  $W_f$

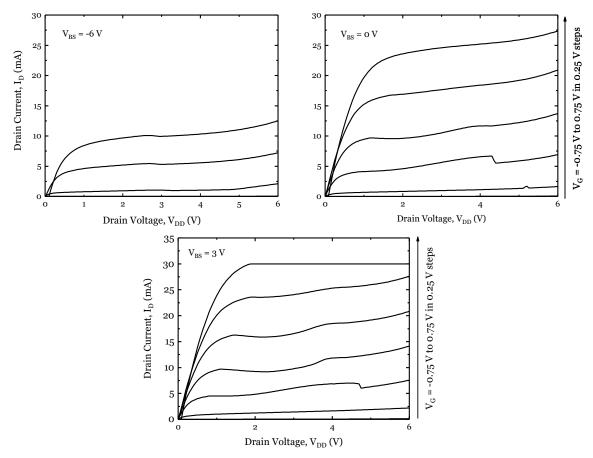

### 2.4. 4-Terminal MESFET DC Measurements

In many applications such as cascode amplifiers, there is a voltage difference between the source and body (bulk) terminals. Non-zero  $V_{SB}$  changes the depletion layer width and affects the threshold voltage. The body terminal can be considered as a back gate and its effect should be taken into account for device modeling and circuit design.

Fig. 2.15. Drain current versus drain voltage of a SOI MESFET (W=300  $\mu$ m,  $L_G$  = 200  $\mu$ m) for different substrate voltages.  $I_D$  increases as  $V_{BS}$  is raised.

Figure 2.16 shows the effect of the substrate bias on the drain current and threshold voltage. If a negative voltage is applied to the bulk terminal ( $V_{BS}$  < 0), it creates an opposing electric field which hardens the transistor turn-on, or tapers the depletion layer width and reduces the current flowing through drain. If the bulk-source terminal is forward biased

$(V_{BS} > 0)$ , it makes channel formation easier or it widens the depletion region and we expect an increase in  $I_D$  and lower threshold voltage.

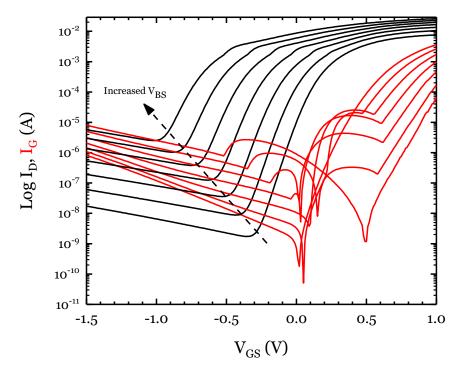

Fig. 2.16. Drain and gate currents of a SOI MESFET ( $W = 300 \mu m$ ,  $L_G = 200 \mu m$ ) as a function of gate voltage, while  $V_{DD}$  is kept constant at 2 V.  $V_{BS}$  is swept from -6 V to 3 V in 1.5 V steps in the direction of the arrow.

### 2.5. MESFET Models

Simulations are an essential part of the design process, tape-out and fabrication will be based on the simulation results. In order to get accurate simulation results, a precise device model is needed to predict the behavior of the device under different operating conditions. Device models need to be run on different popular CAD platforms such as Cadence or Agilent ADS to be convenient and useful. Device models can be categorized into 2 different categories:

#### Physical Models

These models are derived based on the physical parameters such as material properties, device physics, geometry, etc. and different variables are used to model each parameter [15]. Many of these parameters are nonlinear and they change with frequency. In addition, many approximations and hypotheses are being made to analyze the behavior of the device. For this reason, physical models are not the best choices for circuits design and simulation. But physical models provide detailed information about the device operation, and the device can be optimized itself using the physical parameters. Process variations can also be predicted by changing the physical parameters of the device. The latter can cause difficulties for the circuit designers as well since one may not be familiar with physical parameters and how to adjust them for the optimized device behavior.

#### Table based models

These types of models are developed based on hands-on measurements of different parameters such as terminal currents, charges or other characteristics. Typically one thousand measurement points are needed for an accurate model which can be time consuming. The measured data are stored in lookup tables and the device behavior is predicted by interpolating the lookup table data during simulations. The simulation results, however, cannot be trusted out of the measurements range or conditions.

#### Empirical Models

Empirical models fit mathematical functions to DC and AC measurement results. In order to extend the model out of the measurement range, an equivalent circuit can be introduced and its parameters can be replaced in the fitting functions to extrapolate the results. Such extrapolation is an ultimate goal for most of the models which may not be fully realized. Measurement errors can disrupt the final precision of the model and multiple measurements need to be done as sanity checks to assure the model's fidelity. If

the device characteristics (e.g. materials, geometry, etc.) change, new sets of measurements and new device characterization should be done.

Empirical models are usually favored over the other two as they offer higher computational efficiency and don't require complicated physical parameters. There are different models available for MESFET transistors including Triquint models (e.g. TOM3), Curtice, Statz and Angelov (Chalmers). A short description of these models are provided here:

### 2.5.1. Curtice Quadratic Model

The Curtice model is one of the first MESFET models which is not complicated and includes important transistor parameters such as pinch-off voltage and transconductance. It suggests a Taylor series expansion around the threshold voltage to calculate the drain current [18]:

$$I_{DS} = \beta (V_{GS} - V_{TO})^2 \tanh(\alpha V_{DS}) (1 + \lambda V_{DS})$$

(2.15)

Where

$\beta$  = Transconductance parameter (mA/V<sup>2</sup>)

$V_{To}$  = Pinch-off voltage (V)

$\alpha$  = Slope of  $I_{DS}$  VS.  $V_{DS}$  in the linear region (V<sup>-1</sup>)

$\lambda$  = Slope of  $I_{DS}$  VS.  $V_{DS}$  in the saturation region (V<sup>-1</sup>)

The tanh function is used to describe the current in the linear region. The Curtice model is valid above the threshold voltage and not accurate when the transistor is reversed biased or when  $V_{DS} = o$ .

#### 2.5.2. Statz Model

In the Statz model —which is a modification of the Curtice model— the *tanh* function is replaced with a third order polynomial [10], and the square law is only valid for small gate over drive voltages ( $V_{GS} - V_{To}$ ). I<sub>DS</sub> becomes linear for higher gate over drive voltages.

$$I_{DS} = \frac{\beta (V_{GS} - V_{TO})^2 (1 + \lambda V_{DS}) \left(1 - \left(1 - \frac{\alpha V_{DS}}{3}\right)^3\right)}{1 + b(V_{GS} - V_{TO})}$$

(2.16)

Where  $\left(1-\left(1-\frac{\alpha V_{DS}}{3}\right)^3\right)$  is the truncated series representation of the  $tanh(\alpha V_{DS})$  function. The Statz approach fails to model the drain conductance for higher values of  $V_D$ .

### 2.5.3. Triquint Own Model (TOM3)

There is not a square law relation between the gate over drive voltage and  $I_{DS}$  for all devices. The TOM3 model changes the constant exponent in this expression from 2 to a variable number and represents a continuous expression for  $I_{DS}$  in all operation regions [19]. Previously, our group developed a 3-terminal TOM3 MESFET model in simulations. As explained before, in some circuit architectures such as cascode amplifiers, there is a voltage difference between the body and source terminals and the body effect needs to be taken into account since it modifies the drain current. That is why a 4-terminal Angelov model was developed to generate more accurate simulation results.

# 2.5.4. Angelov (Chalmers) Model

Currently, the Angelov model is the most popular MESFET model in the industry, especially for GaN technology. This is the reason why we chose the Angelov model to model the CMOS compatible MESFETs. Some parameters of the fitting mathematical equations need to be changed as the size and geometry of the device change. Therefore, the model is developed in Verilog-A which enables us to easily make the needed changes to tune the model. The Angelov model directly uses hands-on measurement results to estimate different parameters [20], [21]. All model parameters have continuous derivatives without poles. The Angelov's equivalent circuit diagram is shown in Figure 2.17.

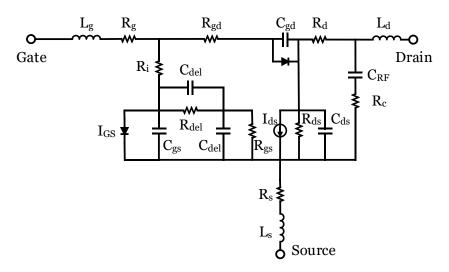

Fig. 2.17. Angelov circuit diagram [23] including a current source, parasitic capacitances and resistances. Since the gate forms a Schottky contact, two diodes between the gate and source/drain terminals are used to model the leakage current.

There are several DC and AC fitting parameters used in the Angelov model, which call for extensive measurements of both types. The DC measurements are usually done first and  $I_{DS}$  of the MESFET is recorded versus  $V_{DS}$  (family of curves) and  $V_{GS}$  (Gummel plots) in order to extract the related DC parameters. Followed by the DC measurements are S-parameter measurements at different bias points to find the nonlinear and parasitic

elements of the model. To evaluate the DC and small signal performance of the Angelov model, I-V curves and S-parameters can be compared to their respective measured values. The large signal performance of the model is usually compared to the load-pull results at a specific frequency.

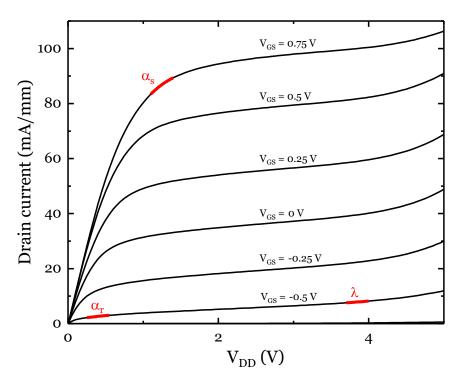

The basic Angelov model proposes an equation for  $I_{DS}$  which has a bell-shaped derivative, same as the measured transconductance. The first order Angelov model consists of five parameters including  $I_{pks}$ ,  $V_{pks}$ ,  $P_{Im}$ ,  $\alpha_s$  and  $\lambda$  which can be extracted using direct measurements. The essential measurement biasing points to extract the model parameters are low and high current quiescent points with low and high  $V_{ds}$ . Thus, FOC measurements can be a good start for the model extraction as  $V_{DS}$  and  $V_{GS}$  both get swept and various current levels are generated. Channel length modulation ( $\lambda$ ) and two saturation parameters ( $\alpha_r$ ,  $\alpha_s$ ) can be found from the FOC plot as shown in Figure 2.18. The parameter  $\alpha_s$  defines the slope of  $I_{DS}$  versus  $V_{DS}$  at high saturated currents with small drain voltages where  $V_{DS} < V_{knee}$ .  $\lambda$  defines the slope of a low drain current curve for higher drain voltages, where  $V_{DS} > V_{knee}$ .

Fig. 2.18. Angelov slope parameters extraction from a 300  $\mu$ m wide MESFET FOC with  $L_G = L_{aD} = L_{aS} =$  200 nm.

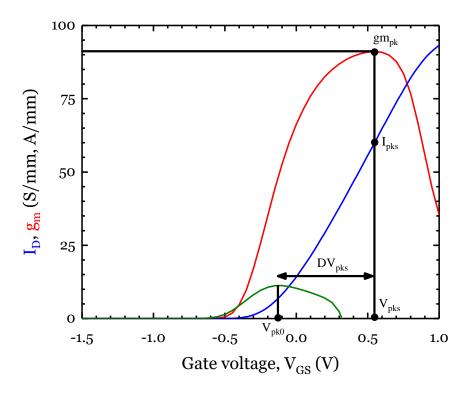

The remaining parameters can be calculated by plotting the transistor transconductance at one low and one high  $V_{DS}$  value as shown in Figure 2.19. In this figure, the measured  $I_{DS}$  and  $g_m$  results versus  $V_{GS}$  for a 300  $\mu$ m wide MESFET fabricated on 180 nm Jazz Semiconductor technology. The current and transconductance should be measured for high and low  $V_{DS}$  values, which were selected as  $V_{DS} = 2$  V, 0.1 V in Figure 2.19.  $\Psi_p$  is a power series function centered at  $V_{pk}$  and varies with  $V_{gs}$ . For the first order model,  $\Psi_p$  is a simple first order polynomial.

Fig. 2.19. Parameter extraction for the first order Angelov model using measurement results of a MESFET with  $L_G$  = 500  $\mu$ m, W = 300  $\mu$ m which was fabricated on the 180 nm Jazz Semiconductor technology.

$$I_{DS} = I_{pks} \left( 1 + \tanh(\Psi_p) \right) \tanh(\alpha_s V_{DS}) (1 + \lambda V_{DS})$$

(2.17)

$$\Psi_{p}=P_{1m}\left(V_{GS}-V_{pks}\right) \tag{2.18}$$

$$P_{1m} = \frac{g_{m-pk}}{I_{pks}} \tag{2.19}$$

Where

$I_{\mathrm{pks}}$  = drain current at which the transconductance is maximized

$P_{im}$  = polynomial coefficient for channel current

$\alpha_s$  = saturation voltage parameter

$\lambda$  = channel length modulation

$\ensuremath{V_{pks}}\xspace$  = gate voltage at which the transconductance is maximized

$g_{m-pk}$  = maximum transconductance

$D_{\text{vpks}}$  = change in  $V_{pk}$  versus  $V_{ds}$

The first-order Angelov model typically generates results with less than 10% global error [18] which can predict the I-V curves and transconductance trends. The first order model can be can be extended to get more accurate results. In the next step, 6 more model parameters can be added to the first order model to construct an 11 parameter model. The equations will be updated as follows [18]:

$$D_{vpks} = V_{pks} - V_{pks0}$$

(2.20)

$$\Psi_{p} = P_{1m} \left( \left( V_{GS} - V_{pk0} \right) + P_{2} \left( V_{GS} - V_{pks} \right)^{2} + P_{3} \left( V_{GS} - V_{pkm} \right)^{3} \right)$$

(2.21)

$$V_{pk} (V_{DS}) = V_{pks} - DV_{pks} + DV_{pks} \tanh(\alpha_s V_{DS})$$

(2.22)

$$P_{1m} = \frac{g_{m-pk}}{I_{pks}} [(1 + \Delta P_1) (1 + \tanh(\Psi_p))]$$

(2.23)

$$\alpha = \alpha_r + \alpha_s (1 + \tanh(\Psi_p))$$

(2.24)

$\Psi_p$  power series which was chosen to be a first order polynomial in the first order model, can be extended to higher order polynomials for more accuracy.  $\Delta P_1$  accounts for the  $P_{1m}$  reduction at high  $V_{DS}$  values by modifying the gain of the transistor. As a result of the higher gain, the voltage swing on the gate will be less, which degrades linearity and intermodulation characteristics.  $P_2$  and  $P_3$  introduce higher order polynomial coefficients for channel current to adjust different  $g_m$  shapes.  $B_1$  and  $B_2$  are the unsaturated coefficients for  $P_1$  and  $P_2$  and track  $\Delta P_1$  changes with respect to  $V_{ds}$ .  $D_{vpks}$  models the effect of the drain voltage changes on  $V_{pks}$ , which is partially due to the voltage drop on the source resistance.

The parameter  $\alpha_r$  controls the slope of low  $I_{DS}$ , for lower values of  $V_{DS}$  and  $V_{GS}$ .  $\alpha_s$  sets the slope of saturated  $I_{DS}$  for low values of  $V_{DS}$  and higher  $V_{GS}$  values. 7 important parameters including  $I_{pks}$ ,  $V_{pks}$ ,  $P_{1m}$ ,  $\alpha_s$ ,  $\alpha_r$ ,  $\lambda$  and  $D_{vpks}$  can be directly found from the measurements, and a CAD tool such as Cadence can be used for fine tuning and optimization.

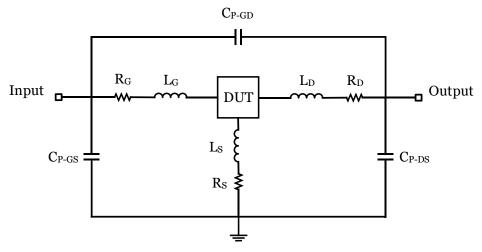

The next step is fitting the simulated S-parameters to their respective measured values at RF frequencies. Since S-parameters can be converted to  $h_{2i}$ , forward current gain and its corresponding cutoff frequency can also be considered as the comparison basis. To complete the small signal model and get accurate simulation results at higher frequencies, layout parasitic components such as  $R_g$ ,  $R_d$ ,  $R_s$ ,  $R_i$ ,  $C_{ds}$ ,  $L_g$ ,  $L_d$  and  $L_s$  should be extracted from S-parameter measurements at different biasing points. Initial estimate for these parameters can be found through ColdFET measurements which are described in details in Chapters 3 and 4. Examples of extracted model parameters and intrinsic/parasitic components through DC and ColdFET measurements for individual CMOS compatible MESFETs can be found in [22], [23].

Finally, the following are some other fitting parameters which are very useful in controlling the high frequency performance of the Angelov model. Frequency dependent anomalies caused by deep level traps at surface or channel-substrate interface prompt frequency dispersion of  $g_m$ , I-V characteristics and output conductance [21], [24]. The Sparameters and RF figures of merit are also affected consequently. To model dispersion,  $R_C$  in series with  $C_{rf}$  is added to the small signal equivalent circuit (Figure 2.17) between drain and source terminals, which controls the frequency dependent output transconductance. At frequencies higher than the MESFET cutoff frequency,  $R_C$  shunts the output and decreases the transconductance.  $C_{RF}$  determines the time constant of this RC network. In the Angelov Verilog-A model, a similar RC network is added to the transistor input port, between gate and source terminals, due to the symmetry of the

transistor. To account for the input dispersion,  $R_{cin}$  and  $C_{rfin}$  in the Angelov Verilog-A model control the frequency dependent input conductance. If the desired RF simulation accuracy is not attained via the aforementioned 4 dispersion variables, 3 more parameters including  $R_{del}$ ,  $C_{del}$  and  $K_{bgate}$  are available in the Angelov model which provide more control knobs.  $R_{del}$  and  $C_{del}$  shunt the gate control node to change the frequency dependent gate control and delay. As the frequency is increased, the gate control is delayed further which is why RF devices don't respond instantly to excitation. The delay RC network ( $R_{del}$ ,  $C_{del}$ ) generates high frequency delay by changing the input conductance.  $K_{bgate}$  enables the back gate parasitic feedback to the gate control voltage in the Angelov Verilog-A model which changes the effective  $V_{GS}$ .

To acquire an accurate RF fit to the S-parameters, the frequency dispersion parameters along with the parasitic and intrinsic component values can be modified around the initial estimations in the Angelov Verilog-A model. A close simulation result can be achieved by iteration.

#### 2.6. 4-Terminal Angelov Modeling

The 4-terminal Angelov model was presented by our group for the first time [23] to incorporate the substrate bias effects into the initial Angelov model. To start, an initial drain current model was presented at  $V_{bs} = 0$  V for a 45 nm SOI MESFET with  $L_G = L_{aS} = L_{aD} = 200$  nm and W = 300  $\mu$ m. A device with average behavior was chosen to develop the model. Different DC measurements were done to produce enough data points and extract five basic Angelov model parameters as explained in Section 2.5.4 (Equations 2.17 through 2.19). Parameter extraction results at  $V_{BS} = 0$  were as follows:

Table 2.1. Extracted DC Parameters from a CMOS MESFET for the First Order Angelov Model

| g <sub>mpks</sub> (mS/mm) | I <sub>pks</sub> (mA/mm) | V <sub>pks</sub> (V) | α <sub>s</sub><br>(V-1) | α <sub>r</sub><br>(V-1) | λ     |

|---------------------------|--------------------------|----------------------|-------------------------|-------------------------|-------|

| 91.7                      | 66.3                     | 0.59                 | 0.005                   | 1.8                     | 0.045 |

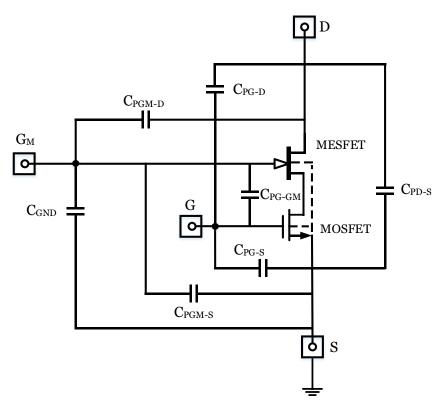

The major change in the 4-terminal Angelov model is added gate current equations to account for the forward and reverse gate leakage diodes. The Schottky gate contact in the MESFET forms two current paths to the source and drain regions as shown in Figure 2.20[23].

Fig. 2.20. Current paths between the Schottky gate and source/drain junctions in a CMOS MESFET transistor.

The gate to source leakage current equation in the initial Angelov model [18] is:

$$I_{gs}=I_{j}\left(\exp\left(P_{g} \cdot \tanh\left(V_{gsi}-V_{jg}\right)\right)-\exp\left(-P_{g} \cdot V_{jg}\right)\right) \tag{2.25}$$

Where

$I_i$  = gate forward saturation current

$$P_g = \frac{kT}{N_e \cdot q}$$

(gate current parameter)

$V_{\mathrm{gsi}}$  = internal gate node voltage

$V_{\rm jg}$  = fitting offset in the gate current parameter  $\,$

$P_g$  needs to be divided into two parts, forward ( $P_{gF}$ ) and reverse ( $P_{gR}$ ) to incorporate the forward and reverse gate leakage currents. Adding  $P_{gF}$  and  $P_{gR}$  to Equation 2.25 will change it to:

$$I_{gs} = I_j \left( \exp \left( P_{gF} \cdot \tanh \left( V_{gsi} - V_{jg} \right) \right) - \exp \left( -P_{gR} \cdot V_{jg} \right) \right)$$

(2.26)