# Theoretical Design Methodology for Practical Interconnection Networks

Ryota Yasudo

A dissertation submitted in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

School of Science for Open and Environmental Systems Graduate School of Science and Technology Keio University

January 2019

# Abstract

End-to-end network latency is a concern for parallel applications in high-performance computing platforms and high-end data centers. On one hand, computer architects have tried to design interconnection networks experimentally and empirically. On the other hand, theorists have tried to model computer networks and then studied their properties theoretically. However, the model does not sufficiently capture real computer systems. This dissertation aims at establishing a novel method for designing high-performance network topologies to bridge a gap between the theoretical and practical studies. In particular, we make use of the knowledge of graph theory, network science, and design theory, as well as the research on interconnection networks.

We firstly present a novel graph called a host-switch graph, which consists of host vertices and switch vertices with maximum degree 1 and r, respectively. This graph represents a network topology of a practical parallel/distributed computer system with host computers connected by r-port switches. We then discuss important metrics for designing high-performance interconnection networks: the host-to-host average shortest path length (h-ASPL) and the bisection width (BiW). In particular, we explore a method for constructing host-switch graphs with low h-ASPL and high BiW that connect the fixed number of hosts via any number of r-port switches. We demonstrate that the number of switches that provides the minimum h-ASPL can mathematically be approximated, and the minimum number of switches that provides a certain BiW can experimentally be approximated. On the basis of the approximations, we propose a randomized algorithm for searching host-switch graphs. We then apply the graphs to interconnection networks and compare them with typical network topologies. As compared with the torus, Dragonfly, and Fat-tree, our networks attain higher performance and smaller power and costs.

Furthermore, we propose adding ports to a host as a method for reducing the network latency as well as increasing the number of ports of a switch. To this end, we extend a host-switch graph so that it represents multi-port hosts. Multi-port hosts are conventionally used for link aggregation (LA) and network duplication (ND), but they do not reduce the hop count. We hence propose the permutation of host-switch mapping for reducing the hop count. It can be applied to LA and ND, and we label the obtained networks p-LA and p-ND, respectively. In addition, we propose the application of a finite projective plane (an instance of block designs) and label it PP. Our methods can be applied to arbitrary topologies, and thus we can directly use any existing topologies. We evaluate five designs above (LA, ND, p-LA, p-ND, and PP) for randomly-optimized, torus, Dragonfly, and Fat-tree topologies in terms

of the design complexity, the hop count, the bisection width, costs, the size of routing tables, and simulated message passing interface (MPI) performance. Our results demonstrate that our methods (p-LA, p-ND, and PP) reduce the hop count while increasing the bisection width and costs for every topology. In particular, we demonstrate that PP is a cost-effective method for reducing the hop count, especially for randomly optimized and Fat-tree topologies.

# Acknowledgments

First and foremost, I would like to thank my academic adviser, Professor Hideharu Amano, for his tremendous commitment to teaching and mentoring throughout my career as a graduate student.

I would like to thank Associate Professor Michihiro Koibuchi for his teaching and mentoring since I became a research assistant at National Institute of Informatics.

I would also like to thank Professor Tadao Nakamura, Professor Koji Nakano, and Associate Professor Hiroki Matsutani. I was fortunate to have them as teachers and collaborators, and my scientific perspective broadened.

I would also like to thank Professor Wayne Luk and Dr. Jose Gabriel de Figueiredo Coutinho for their tremendous supports when I was visiting Imperial College London, as well as collaborative research on reconfigurable computing.

I am grateful to my doctoral committee members, Professor Koji Nakano, Professor Katsuhiro Ota, and Associate Professor Hiroki Matsutani for their careful reviews and valuable comments to my thesis.

Last but not least, I would like to thank my family and friends for their supports and encouragement during my time at Keio University.

Ryota Yasudo Yokohama, Japan December 2018

# Contents

| Ab | Abstract i         |          |                                                   |    |  |  |

|----|--------------------|----------|---------------------------------------------------|----|--|--|

| Ac | Acknowledgments ii |          |                                                   |    |  |  |

| 1  | Intro              | oduction |                                                   |    |  |  |

|    | 1.1                | Motiva   | tion                                              | 1  |  |  |

|    | 1.2                | Objecti  | ves                                               | 1  |  |  |

|    | 1.3                | Contrib  | putions                                           | 2  |  |  |

|    | 1.4                | Dissert  | ation Outline                                     | 3  |  |  |

| 2  | Tech               | nical an | nd Theoretical Backgrounds                        | 5  |  |  |

|    | 2.1                | Interco  | nnection Networks                                 | 5  |  |  |

|    |                    | 2.1.1    | Topology                                          | 5  |  |  |

|    |                    | 2.1.2    | Routing                                           | 9  |  |  |

|    |                    | 2.1.3    | Layout                                            | 11 |  |  |

|    | 2.2                | An Uno   | directed Graph                                    | 13 |  |  |

|    |                    | 2.2.1    | Definition and Notation                           | 13 |  |  |

|    |                    | 2.2.2    | Degree/Diameter Problem for General Graphs        | 13 |  |  |

|    |                    | 2.2.3    | Degree/Diameter Problem for Bipartite Graphs      | 14 |  |  |

|    |                    | 2.2.4    | Order/Degree Problem                              | 15 |  |  |

|    | 2.3                | Networ   | k Science and its Applications                    | 16 |  |  |

|    |                    | 2.3.1    | Random Graph Models                               | 16 |  |  |

|    |                    | 2.3.2    | Watts-Strogatz Model                              | 17 |  |  |

|    |                    | 2.3.3    | Models of Scale-free Networks                     | 18 |  |  |

|    | 2.4                | Design   | Theory                                            | 19 |  |  |

| 3  | Low                | -Latenc  | y Interconnection Networks with Single-Port Hosts | 21 |  |  |

|    | 3.1                | Overvie  | ew                                                | 21 |  |  |

|    | 3.2                | Introdu  | ction of a Host-Switch Graph                      | 21 |  |  |

|    |                    | 3.2.1    | Definition and Notation                           | 21 |  |  |

|    |                    | 3.2.2    | Upper and Lower Bounds                            | 23 |  |  |

| vi |     |            |                                                   |

|----|-----|------------|---------------------------------------------------|

|    | 3.3 | Deterr     | ninistic Construction of Host-Switch Graphs       |

|    |     | 3.3.1      | Radix/Diameter Problem                            |

|    |     | 3.3.2      | Host-Switch Graphs of Diameter 2                  |

|    |     | 3.3.3      | Host-Switch Graphs of Diameter 3                  |

|    |     | 3.3.4      | Host-Switch Graphs of Diameter 4                  |

|    |     | 3.3.5      | Relationship between RDP and h-ASPL               |

|    | 3.4 | Heuris     | stic Construction of Host-Switch Graphs           |

|    |     | 3.4.1      | Order/Radix Problem                               |

|    |     | 3.4.2      | Minimizing h-ASPL                                 |

|    |     | 3.4.3      | Maximizing BiW                                    |

|    |     | 3.4.4      | Three Proposed Topologies                         |

|    | 3.5 | Evalua     | ntion                                             |

|    |     | 3.5.1      | Previously proposed topologies                    |

|    |     | 3.5.2      | Existing topologies                               |

|    |     | 3.5.3      | Fundamental Properties                            |

|    |     | 3.5.4      | Experimental Method                               |

|    |     | 3.5.5      | Results and Discussion                            |

|    |     | 3.5.6      | Practical Feasibility and Limitations             |

|    | 3.6 | Relate     | d Work                                            |

|    | 3.7 | Summ       | ary                                               |

|    | -   | <b>-</b> . |                                                   |

| 4  |     |            | cy Interconnection Networks with Multi-Port Hosts |

|    | 4.1 |            | iew                                               |

|    | 4.2 | Prelim     | -                                                 |

|    |     | 4.2.1      | Extension of a Host-Switch Graph                  |

|    |     | 4.2.2      | Assumptions                                       |

|    | 4.3 |            | ntional Methods Revisited                         |

|    |     | 4.3.1      | Link Aggregation (LA)                             |

25

25

25

25 25

29

29

29

30

35

37

38

38

39

42

42

45

49

50

50

53 53

53

53

54

55 55

56

56

57

58

61

61

62

63

68

69

. . .

. . .

. . . . . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . .

. . . . . .

. . .

|     | 4.3.1  |                                    |

|-----|--------|------------------------------------|

|     | 4.3.2  | Network Duplication (ND)           |

| 4.4 | Propos | ed Methods                         |

|     | 4.4.1  | Permutation of Host-Switch Mapping |

|     | 4.4.2  | Using Small Switch Networks        |

| 4.5 | Evalua | tion                               |

|     | 4.5.1  | Experimental Setup                 |

|     | 4.5.2  | Design Complexity                  |

|     | 4.5.3  | Topological Properties             |

|     | 4.5.4  | Costs                              |

|     | 4.5.5  | Size of Routing Tables             |

|    |              | 4.5.6    | Discrete-Event Simulation                     | 71 |

|----|--------------|----------|-----------------------------------------------|----|

|    | 4.6          | Relate   | d Work                                        | 72 |

|    |              | 4.6.1    | Direct Networks                               | 72 |

|    |              | 4.6.2    | Packet Forwarding in Hosts                    | 72 |

|    |              | 4.6.3    | On-Chip Networks with Multi-Port Hosts        | 73 |

|    |              | 4.6.4    | Low-Latency Networks with Single-Port Hosts   | 73 |

|    | 4.7          | Summ     | ary                                           | 74 |

| 5  | Con          | clusions | 8                                             | 75 |

|    | 5.1          | Summ     | ary                                           | 75 |

|    | 5.2          | Future   | Directions                                    | 75 |

|    |              | 5.2.1    | Theoretical and Practical Extensions          | 75 |

|    |              | 5.2.2    | Routing methods including Virtual 1-D Mapping | 76 |

|    |              | 5.2.3    | Topology-Routing Co-Optimization              | 76 |

|    | 5.3          | Conclu   | Iding Remarks                                 | 76 |

| A  | The          | orems    |                                               | 77 |

|    | A.1          | Optim    | ality of a Clique Host-Switch Graph           | 77 |

| Bi | Bibliography |          |                                               |    |

| Pu | Publications |          |                                               |    |

# **List of Tables**

| 3.1 | Summary of fundamental properties of host-switch graphs                                    | 41 |

|-----|--------------------------------------------------------------------------------------------|----|

| 3.2 | Summary of nine topologies to connect more than 1024 hosts for simulation                  | 44 |

| 4.1 | Time complexity for Step 1 (calculating ASPL between switches in a switch network)         |    |

|     | and Step 2 (calculating h-ASPL between hosts on the basis of the results of Step 1). $\ .$ | 63 |

| 4.2 | Total size of routing tables.                                                              | 70 |

| 4.3 | Improvement rate of simulated MPI performance relative to the case when $p = 1$ (%).       | 71 |

|     |                                                                                            |    |

# **List of Figures**

| 2.1  | Concept of theoretical studies of network topology.                                           | 6  |

|------|-----------------------------------------------------------------------------------------------|----|

| 2.2  | A conceptual figure of Dragonfly.                                                             | 8  |

| 2.3  | A conceptual figure of a multi-stage interconnection network                                  | 8  |

| 2.4  | An example of Fat-tree                                                                        | 9  |

| 2.5  | Concept of the use of network science for designing computer architecture. Network            |    |

|      | scientists mathematically model real-world networks, and then computer architects             |    |

|      | can apply the models for designing computer networks                                          | 16 |

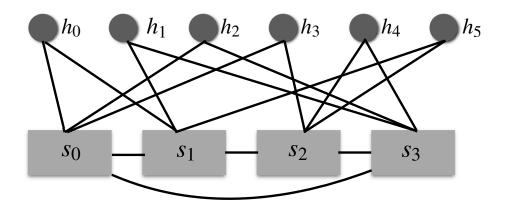

| 3.1  | An example of a host-switch graph $(n = 15, m = 4, r = 6)$                                    | 22 |

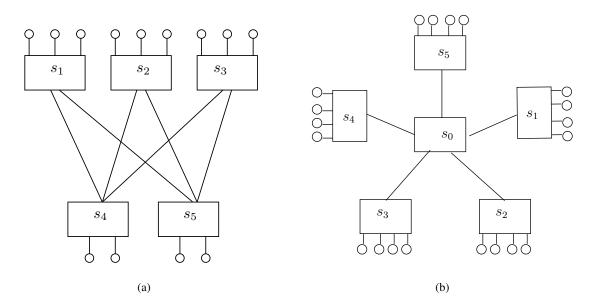

| 3.2  | Examples of a biclique host-switch graph with $r = 5$ ; (a) $\{m_1, m_2\} = \{3, 2\}, n = 13$ |    |

|      | and (b) star host-switch graph with $n = 20$ .                                                | 26 |

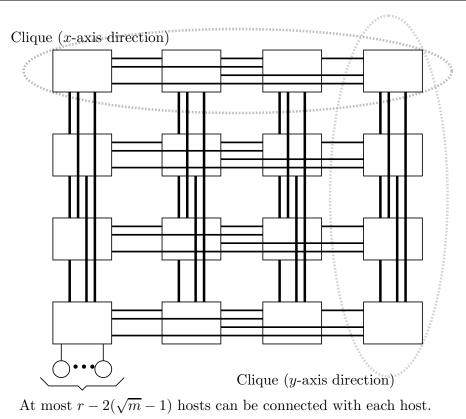

| 3.3  | An example of an XY-clique host-switch graph.                                                 | 27 |

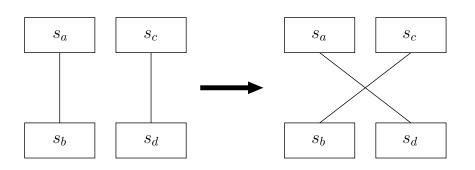

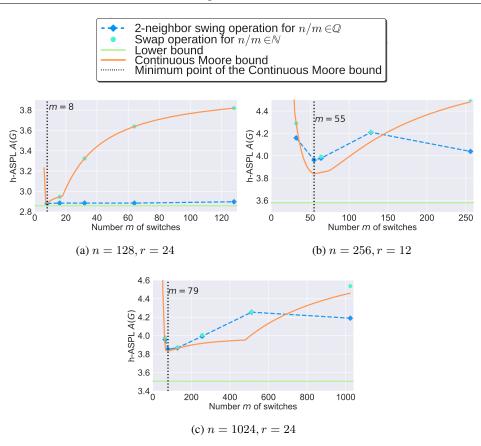

| 3.4  | Swap operation which changes endpoints of two switch-switch edges. $\ldots$                   | 31 |

| 3.5  | Swing operation which changes endpoints of a switch-switch edge and a host-switch             |    |

|      | one                                                                                           | 31 |

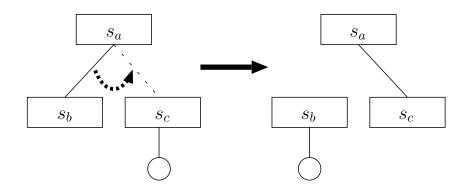

| 3.6  | 2-neighbor swing operation (hosts are omitted for simplicity)                                 | 32 |

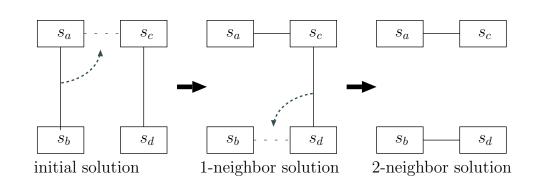

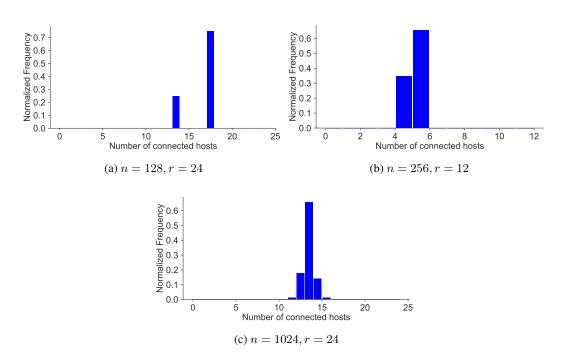

| 3.7  | Relationship between h-ASPL and the number of switches                                        | 33 |

| 3.8  | Host distribution when $m = m_{opt}$ .                                                        | 34 |

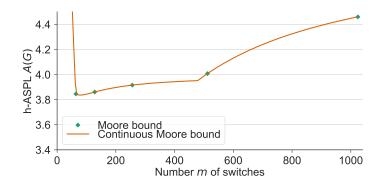

| 3.9  | Comparison between the Moore bound and the continuous Moore bound. $\ldots$ .                 | 34 |

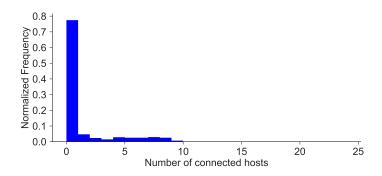

| 3.10 | Host distribution of a host-switch graph with unused switches when $(n,m,r) =$                |    |

|      | (1024, 1024, 24)                                                                              | 35 |

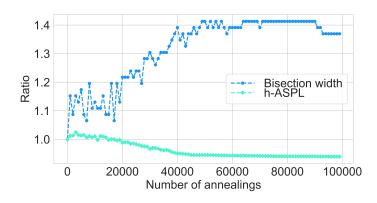

| 3.11 | Changes of h-ASPL and BiW during optimization.                                                | 36 |

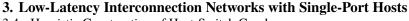

| 3.12 | Relationship between the BiW and the number of switches                                       | 37 |

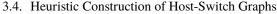

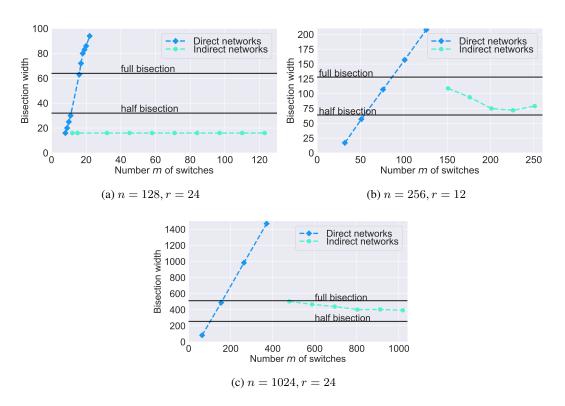

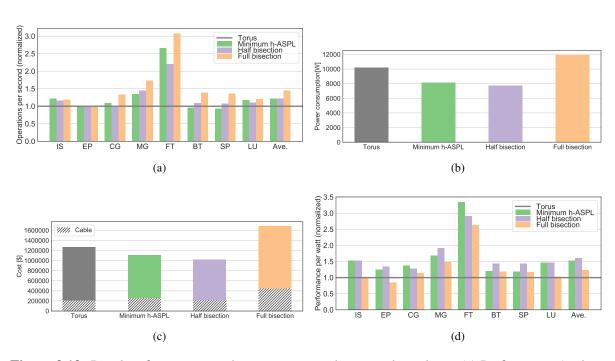

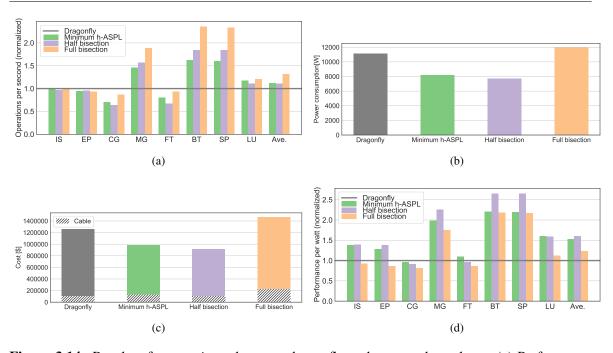

| 3.13 | Results of comparisons between torus and proposed topology: (a) Performance (eight            |    |

|      | benchmarks and the geometric mean); (b) Power consumption; (c) Cost breakdown                 |    |

|      | (Cable and Switch); (d) Performance per watt                                                  | 46 |

| 3.14 | Results of comparisons between dragonfly and proposed topology: (a) Performance               |    |

|      | (eight benchmarks and the geometric mean); (b) Power consumption; (c) Cost break-             |    |

|      | down (Cable and Switch); (d) Performance per watt.                                            | 47 |

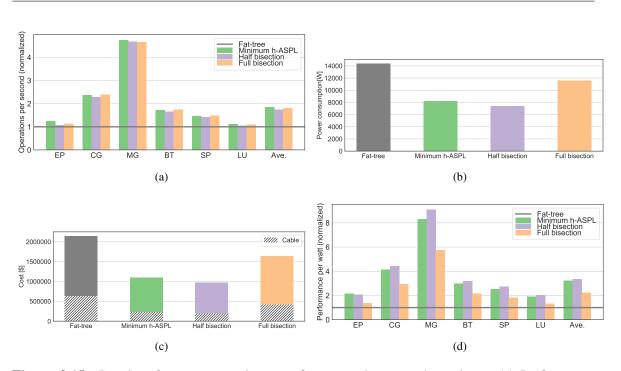

| 3.15 | Results of comparisons between fat-tree and proposed topology: (a) Performance (six                                         |    |

|------|-----------------------------------------------------------------------------------------------------------------------------|----|

|      | benchmarks and the geometric mean); (b) Power consumption; (c) Cost breakdown (Cable and Switch); (d) Performance per watt. | 48 |

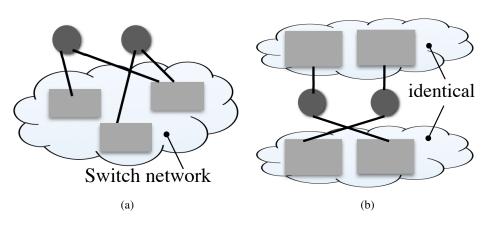

| 4.1  | An example of a host-switch graph with 6 2-port hosts and 4 5-port hosts                                                    | 54 |

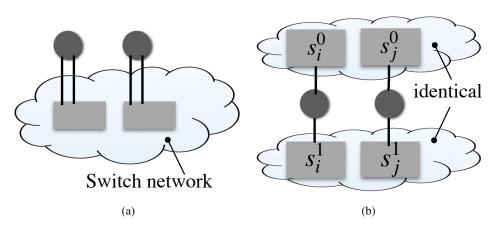

| 4.2  | Conventional interconnection networks with multi-port hosts when $p = 2$ . (a) Link                                         |    |

|      | Aggregation (LA). (b) Network Duplication (ND)                                                                              | 55 |

| 4.3  | Proposed methods when $p = 2$ . (a) Permutation for Link Aggregation (p-LA). (b)                                            |    |

|      | Permutation for Network Duplication (p-ND).                                                                                 | 57 |

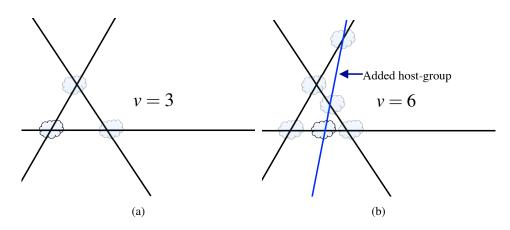

| 4.4  | Obvious design represented by Euclidean plane. (a) $p = 2$ . (b) $p = 3$                                                    | 59 |

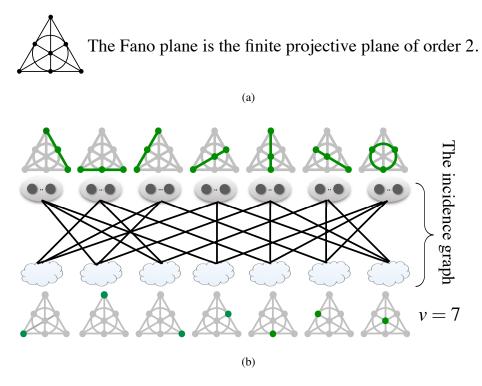

| 4.5  | Proposed design applying a finite projective plane and its incidence graph $(p = 3)$ .                                      |    |

|      | (a) The Fano plane. (b) The incidence graph of the Fano plane, where a line and a                                           |    |

|      | point of the Fano plane correspond to a host-group and a switch network, respectively.                                      | 60 |

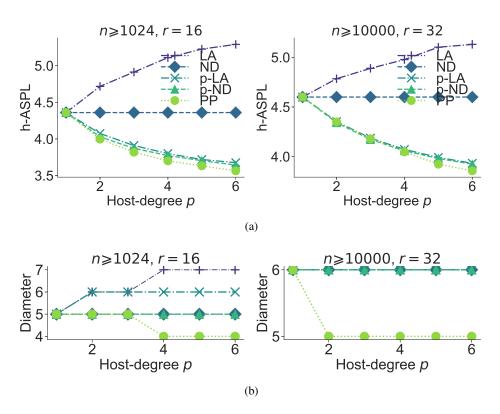

| 4.6  | Hop count of randomly optimized topologies with <i>p</i> -port hosts ( $0 \le p \le 6$ ) when                               |    |

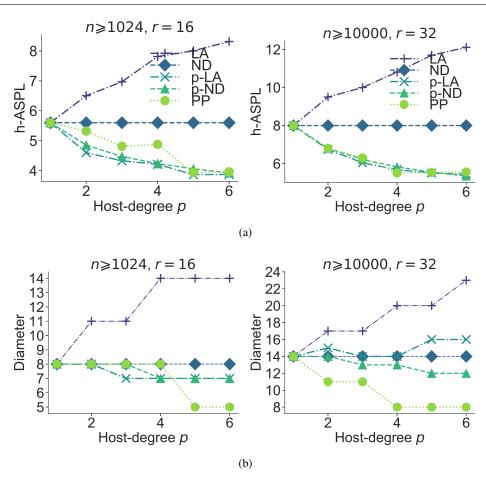

|      | (n,r) = (1024,16) and $(n,r) = (10000,32)$ : (a) h-ASPL and (b) diameter.                                                   | 64 |

| 4.7  | Hop count of torus topologies with p-port hosts ( $0 \le p \le 6$ ) when $n \ge 1024$ and                                   |    |

|      | $n \ge 10000$ : (a) h-ASPL and (b) diameter.                                                                                | 65 |

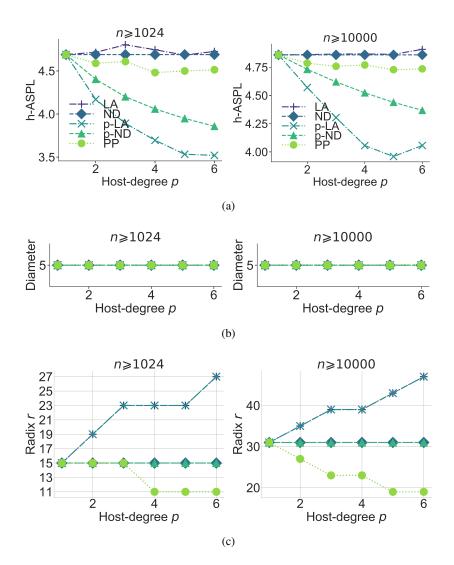

| 4.8  | Hop count of Dragonfly topologies with $p\text{-port}$ hosts (0 $\leqslant p \leqslant 6$ ) when $n \geqslant 1024$         |    |

|      | and $n \ge 10000$ : (a) h-ASPL; (b) diameter; and (c) radix. Note that the Dragonfly                                        |    |

|      | changes radix according to the required number of connected hosts                                                           | 66 |

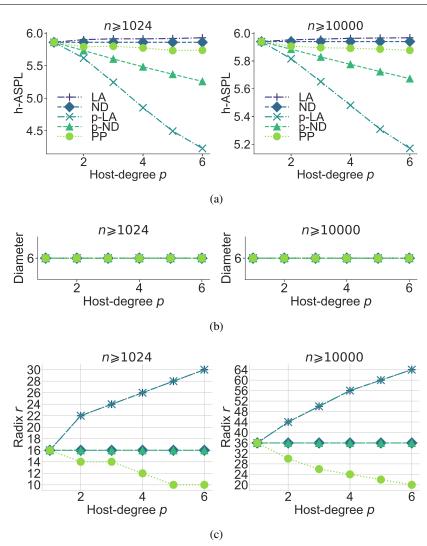

| 4.9  | Hop count of Fat-tree topologies with $p\text{-port}$ hosts ( $0\leqslant p\leqslant 6$ ) when $n\geqslant 1024$ and        |    |

|      | $n \ge 10000$ : (a) h-ASPL; (b) diameter; and (c) radix. Note that the fat-tree changes                                     |    |

|      | radix according to the required number of connected hosts                                                                   | 67 |

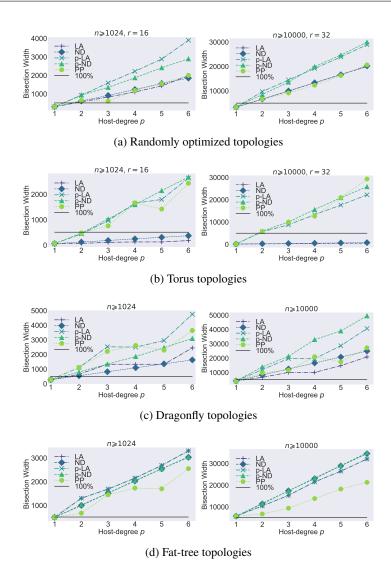

| 4.10 | Bisection widths. The line denoted by "100%" shows full bisection width, i.e., $n/2_{\cdot}$ .                              | 68 |

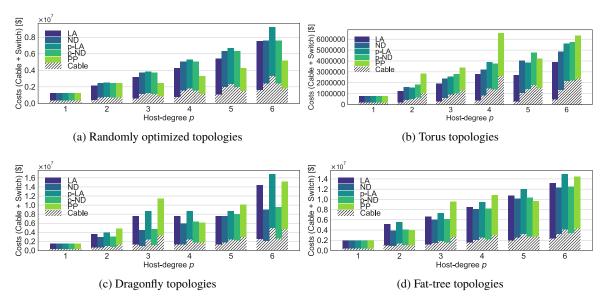

| 4.11 | Costs of cable and switches when $n \ge 1024$ : (a) Randomly optimized topologies;                                          |    |

|      | (b) Torus topologies; (c) Dragonfly topologies; and (d) Fat-tree topologies. Note that                                      |    |

|      | the number of hosts is not fixed; costs per host is shown in Fig. 4.12                                                      | 69 |

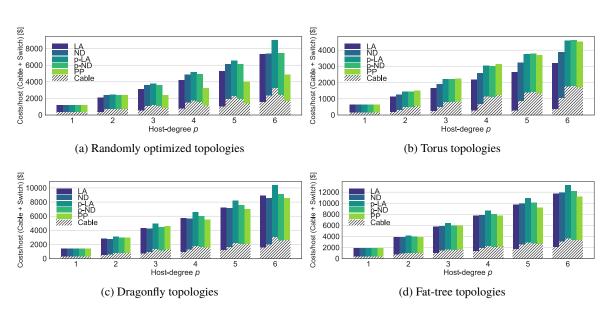

| 4.12 | Costs per host of cable and switches when $n \ge 1024$ : (a) Randomly optimized                                             |    |

|      | topologies; (b) Torus topologies; (c) Dragonfly topologies; and (d) Fat-tree topologies.                                    | 70 |

|      |                                                                                                                             |    |

# **List of Theorems**

| 2.1 | Problem (Degree/Diameter Problem)                                                      | 13 |

|-----|----------------------------------------------------------------------------------------|----|

| 2.2 | Problem (Order/Degree Problem)                                                         | 15 |

| 3.1 | Lemma (Trivial upper bound on the order)                                               | 22 |

| 3.1 | Theorem (Upper bound on the order)                                                     | 23 |

| 3.1 | Corollary (Lower bound on the diameter)                                                | 23 |

| 3.2 | Theorem (Lower bound on the h-ASPL)                                                    | 24 |

| 3.1 | Problem (Radix/Diameter Problem)                                                       | 25 |

| 3.3 | Theorem (Upper bound on the order of a host switch graph of diameter 2) $\ldots$ .     | 25 |

| 3.2 | Lemma (Condition for constructing a host-switch graph of diameter 3)                   | 25 |

| 3.4 | Theorem (Upper bound on the order of a host-switch graph of diameter 3) $\ldots$ .     | 25 |

| 3.3 | Lemma (Upper bound on the switch order of a biclique host-switch graph) $\ldots$ .     | 26 |

| 3.5 | Theorem (Upper bound on the order of a biclique host-switch graph)                     | 27 |

| 3.4 | Lemma (Conditions for constructing an XY-clique host-switch graph)                     | 27 |

| 3.6 | Theorem (Upper bound on the order of an XY-clique host-switch graph)                   | 28 |

| 3.7 | Theorem (The order of an XY-clique and star host-switch graphs)                        | 28 |

| 3.5 | Lemma (Upper bound on the order of a polarity host-switch graph)                       | 28 |

| 3.2 | Problem (Order/Radix Problem)                                                          | 30 |

| 3.1 | Observation (Relationship between the h-ASPL and the continuous Moore bound)           | 34 |

| 3.2 | Observation (Relationship between the h-ASPL and the BiW)                              | 36 |

| 3.3 | Observation (Linear relation between the number of switches and the BiW) $\ldots$ .    | 37 |

| 4.1 | Definition (LA)                                                                        | 56 |

| 4.2 | Definition (ND)                                                                        | 56 |

| 4.1 | Lemma (Upper bound on the diameter of a network with multi-port hosts) $\ldots \ldots$ | 60 |

| A.1 | Lemma                                                                                  | 77 |

| A.1 | Corollary                                                                              | 77 |

| A.1 | Theorem                                                                                | 77 |

## Chapter 1

# Introduction

## 1.1 Motivation

The international roadmap for devices and systems (IRDS 2017 edition [7]) predicts that a cloud system is one of the important market drivers. Cloud systems support many important applications such as web service, multimedia, shopping, big data analytics, and high-performance scientific computation. In particular, big data analytics is increasingly important with the growth of big data for social networking, artificial intelligence (AI), smart cities, and so forth. Big data requires abundant computing power and continuing performance scaling.

A typical application of big data analytics is used as the Graph 500 benchmark [4]. In the Graph 500 benchmark, graph construction and breadth-first search (BFS) are processed. BFS requires many communications as compared with computation. Furthermore, the communications have few locality. To accelerate the Graph 500 benchmark, reducing costs of data movement is therefore essential.

As with big data applications including the Graph 500 benchmark, data-intensive applications such as physical system simulation are also emerging. In general, Peter Kogge suggests that we are now facing the *locality wall* on the heels of the memory wall and the power wall; growing non-predictable regularity and non-locality limits the performance [2]. To accelerate such applications, we need to improve the latency and the bandwidth for both memory and interconnection networks. Especially, interconnection networks should provide faster all-to-all communication and support irregular communication patterns. Thus, irregular network topology that handles non-local traffic would work effectively.

## **1.2** Objectives

A long-standing design goal for high-performance computing (HPC) is to provide low end-to-end network latencies between compute nodes. This requirement for low latency is also relevant for high-end data center networks (DCN). For example, DCNs that target high-frequency trading (HFT)

applications can benefit from end-to-end latencies down to microseconds levels, thus motivating the use of interconnects traditionally used in HPC platforms.

Supporting large-scale applications requires large-scale platforms, e.g., exascale platforms that aggregate millions of cores in hundreds of thousands of compute nodes. Large-scale HPC platforms are currently deployed as compute nodes that are interconnected using large numbers of switches, and DCNs are built following a hierarchical structure with so-called top of rack (ToR) switches, cluster routers, and border routers [9]. In both cases, end-to-end network paths between two compute nodes traverse multiple switches located in different cabinets. End-to-end latencies must decrease to design scalable platforms for workloads that lead to many small message exchanges between compute nodes. Especially, switch delays are high as compared with wire and flit injection delays; for instance, port-to-port switch latency reaches 90 nanoseconds in InfiniBand EDR 100 Gb/s switch [6]. Thus, the number of switches traversed by a network path, called the *hop count*, should be reduced.

Recent research shows that complex networks such as small-world and random networks have low hop counts. Moreover, such complex networks should provide fast all-to-all communications and support irregular traffic patterns, and thus they satisfy the requirement of data-intensive applications, described in Section 1.1. Therefore, this dissertations study a design method and practical feasibility of complex network topologies with low hop count.

### **1.3** Contributions

To achieve the objectives above, this dissertation mainly makes the following contributions.

- 1. We survey both theoretical and practical studies for graphs, complex networks, and interconnection networks, including graph theory, network science, design theory, and computer engineering.

- 2. We propose a novel graph called a *host-switch graph*. It will firstly be defined as a model of an interconnection network with single-port hosts, and then extended to a model of an interconnection network with multi-port hosts.

- 3. We establish two novel graph problems: the *radix/diameter problem* (*RDP*) and the *order/radix problem* (*ORP*). Subsequently, we provide some theory and solutions for both problems.

- 4. We propose and run a heuristic algorithm for solving ORP. It is based on the simulated annealing, but it includes a new concept called a *2-swing* operation and a *continuous Moore bound*.

- 5. For interconnection networks with multi-port hosts, we propose two novel methods for reducing the network latency: *permutation of host-switch mapping* and application of finite projective planes.

6. We compare our proposed network topologies with existing network topologies including theoretically proposed topologies and practical topologies used in supercomputers ranked in TOP500.

## **1.4 Dissertation Outline**

The rest of this dissertation is organized as follows.

Chapter 2 describes technical and theoretical backgrounds. Technical backgrounds include architectural concepts of interconnection networks for large-scale parallel computer systems from three perspectives: the topology, the routing, and the layout. Theoretical backgrounds include graph theory, design theory, and network science; the study set forth in this dissertation effectively applies them to practical interconnection networks.

Chapter 3 studies low-latency interconnection networks with single-port hosts. The two novel concepts are proposed: a host-switch graph and the order/degree problem. A host-switch graph is a model of an interconnection networks with hosts and switches, and the order/degree problem is a graph problem for minimizing the ideal (zero-load) end-to-end latency of an interconnection network. Several interesting findings are described.

Chapter 4 studies low-latency interconnection networks with multi-port hosts. To represent a network with multi-port hosts, a host-switch graph is extended. As in Chapter 3, the ideal end-to-end latency is minimized. To this end, the solution obtained in Chapter 3 can be utilized. It is shown that design theory provides excellent design of the networks with multi-port hosts.

Chapter 5 summarizes this dissertation and suggests future directions.

## Chapter 2

# **Technical and Theoretical Backgrounds**

### 2.1 Interconnection Networks

An *interconnection network* is a programmable system that transports data between terminals [39]. It occurs at many scales, including on-chip networks (a.k.a. networks-on-chip) and off-chip networks. Physical characteristics depend on the scale, but fundamental principles are the same. In this section, we describe interconnection networks with a focus on off-chip ones.

Three issues mainly dominate the design of an interconnection network: topology, switching technique, and routing algorithm. In addition to the three issues above, this section studies the physical layout, which is becoming more and more important due to the increasing gap between switching delays and cable delays.

#### 2.1.1 Topology

#### 2.1.1.1 Theoretical Studies on Network Topology

Theoretically, a topology of a computer network is represented as an undirected graph, in which vertices and edges correspond to computers and communication links, respectively. The performance potentiality of the network can be measured by analyzing topological properties of the graph. In the design of networks for computer systems such as multiprocessors and supercomputers, there are certain requirements and limitations. In particular, requirements include the number of nodes, and limitations include the degree and the diameter. Hence the three parameters above have been studied in graph theory. The degree/diameter problem (DDP) is a classical problem for such studies. The DDP is the problem of finding the largest number of vertices in a graph of given maximum degree  $\Delta$  and diameter D. The known upper bound—called the Moore bound [86]—on the number of vertices of an undirected graph is  $1 + \Delta \sum_{i=0}^{D-1} (\Delta - 1)^i$ . Near-optimal/optimal solutions of the DDP are considered for topologies of interconnection networks [21,77,87]. Figure 2.1 illustrates a concept of theoretical studies of network topology.

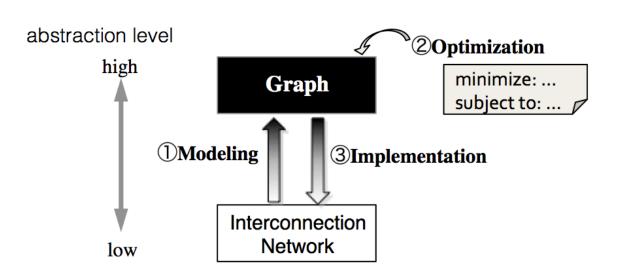

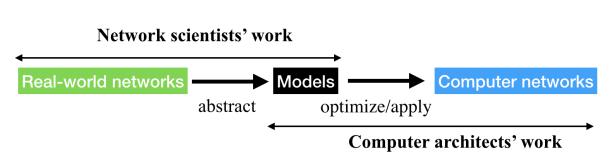

Figure 2.1: Concept of theoretical studies of network topology.

However, the DDP solutions may not be usable for building network topologies in practical interconnection networks. This is because the DDP requires the specific number of vertices, and hence we cannot meet technical requirements such as the number of nodes. To cover this shortcoming, we should fix the number of vertices (*order*) of a graph. We can consider the order/degree problem (ODP), the problem of finding the smallest diameter in a graph of given order and degree. Although less attention is given to the ODP as compared with the DDP, the ODP is recently studied by designers of interconnection networks [5].

In the field of network science, researchers find that complex networks such as social networks provide low diameter and ASPL. Thus some models are proposed, e.g, a cycle plus a random matching [28], the Erdős-Rényi model (random graph) [49], and the Watts-Strogatz model (small-world networks) [121]. Some solutions for the ODP are such complex graphs and applied to computer systems, including high-performance computing systems [76], data centers [110], and on-chip networks [95]. To apply such complex topologies to practical networks, physical layouts [74] and routing algorithms [55] are also studied.

Even if we tackle the ODP, however, a shortcoming remains; in conventional graph theory, one kind of vertex is considered on a graph, though two types of nodes—hosts and switches—exist in typical interconnection networks. Hence, the mapping between vertices and physical devices is not obvious. If we regard vertices as switches, we have no information for hosts. This is a serious issue because the mapping strongly affects the network performance (we show this in Section 3.4). Therefore, we should radically change both a model of interconnection networks and a graph problem.

#### 2.1.1.2 Practical Studies on Network Topology

Practical studies on topologies of interconnection networks for parallel/distributed computer systems have a long history. In the 1970s, hypercubes were used in many systems such as Cosmic Cube [106];

2.1. Interconnection Networks

in the 1980s, 2-D/3-D tori and meshes became the mainstream due to their short cables that provide high bandwidth and cost-efficiency; from the 1990s to 2000s, as the number of nodes becomes over 10 thousand, high-radix networks such as the dragonfly [71] are researched for reducing communication overhead; and now, in the 2010s, the high-radix networks are used in commercial high-performance computers [13, 15].

All the networks above are *direct networks*, which denote the networks such that a certain number of hosts are connected to each switch. In addition to direct networks, *indirect networks* are also used, which denote the networks such that some switches are connected with a certain number of hosts while the other switches are connected with no hosts. Above all, the fat-tree [78] is widely used in parallel/distributed computer systems from generation to generation, though technology for each generation is different (e.g., both CM-5 [63] in the 1980s and Tianhe-2 [81] in the 2010s use the fat-tree). In this respect, indirect networks contrast with direct networks. For this reason, the question of our interest is how we should uniformly discuss direct and indirect networks (note that prior theoretical study based on the DDP and the ODP deals with only direct networks). This should be studied systematically, but there has been no prior research to answer this question yet. Also, the rationality of existing topologies should be backed by graph theory.

#### 2.1.1.3 Commonly Used Existing Topologies

**Torus** The torus topology is a mesh graph (a.k.a. a lattice graph or a grid graph) with wraparound channels, and consequently each dimension constitutes a ring structure. Formally, a K-ary N-torus is a topology with parameters K and N. Each node is identified by a N-bit base-K address  $a_{N-1}a_{N-2}\cdots a_0$ , and connected to nodes with addresses  $a'_{N-1}a'_{N-2}\cdots a'_0$  where  $a'_i \pm 1$ (mod K) =  $a_i$  for any  $i \ (0 \le i \le N-1)$  and  $a'_j = a_j$  for all  $j \ (0 \le j \le N-1)$  and  $j \ne i$ ).

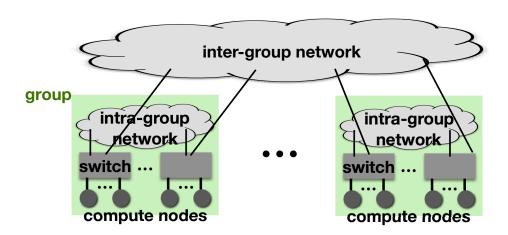

**Dragonfly** Dragonfly is, so to speak, a meta-topology proposed for designing technology-driven, highly-scalable interconnection networks with high-radix routers [71]. It consists of multiple *groups*, in which an intra-group network connect the routers, and an inter-group network as shown in Figure 2.2. In [71], Kim *et al.* suggest that every intra-group network should be a clique or Flattened butterfly and the inter-group network should be a clique. However, rather interestingly, the topologies of inter- and intra-group networks are not deterministic since Dragonfly is not topology itself but a meta-topology. Also, we can change parameters such as the number of links within a group and between groups.

Dragonfly provides a high-performance networks, so it is adopted by many supercomputers ranked in Top 500.

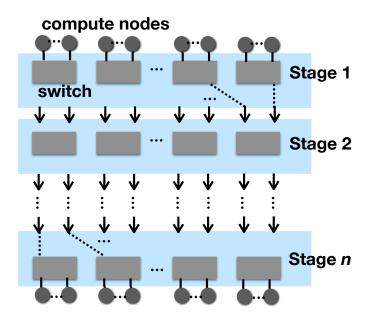

**Fat-tree** Fat-tree is a class of *bidirectional multi-stage interconnection networks (BMIN)*. MIN is a directed network consisting of multiple stages as shown in Figure 2.3; then, by folding it, we get an

Figure 2.2: A conceptual figure of Dragonfly.

Figure 2.3: A conceptual figure of a multi-stage interconnection network.

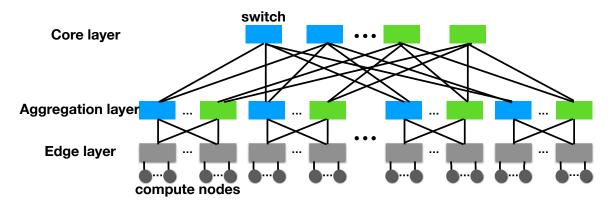

undirected network, i.e., BMIN. An example of Fat-tree is shown in Figure 2.4. In this figure, Fat-tree has three layers—called core, aggregation, and edge layers—and it provides full bisection bandwidth.

#### 2.1.1.4 Bridging a Gap between Theoretical and Practical Studies

The study set forth in this dissertation aims at establishing a novel method for designing highperformance network topologies to bridge a gap between theoretical studies based on graph theory and practical studies based on computer engineering. There exist many gaps between graphs and real systems; a real system may consist of various types of nodes, including CPUs, accelerators, memories, and switches, and we should consider the execution time for real applications, the fault tolerance, the layout, and the energy consumption. 2.1. Interconnection Networks

Figure 2.4: An example of Fat-tree.

This study focuses on distinguishing hosts and switches and considering the end-to-end latency between two hosts. We will present a novel graph called a *host-switch graph*, which consists of *host* vertices and *switch* vertices. A host can be connected to exactly one switch using an edge. A switch can be connected to at most r vertices, each of which is a host or a switch. Clearly, a host-switch graph represents a topology of a computer network with 1-port host computers and r-port network switches. Thus, studying the topological characteristics of host-switch graphs leads to find good topologies for practical computer systems.

#### 2.1.2 Routing

#### 2.1.2.1 Switch

Large-scale HPC platforms are currently deployed as compute nodes that are interconnected using large numbers of switches, and DCNs are built following a hierarchical structure with so-called top of rack (ToR) switches, cluster routers, and border routers [9]. In both cases, end-to-end network paths between two compute nodes traverse multiple switches located in different cabinets. End-to-end latencies must decrease to design scalable platforms for workloads that lead to many small message exchanges between compute nodes. Especially, switch delays are high as compared with wire and flit injection delays; for instance, port-to-port switch latency reaches 100 nanoseconds in InfiniBand QDR [6]. Thus, the number of switches traversed by a network path, called the hop count, should be reduced.

To reduce the hop count, switches with dozens of ports, called high-radix switches, have been used in the HPC domain for many years [72, 104]. High-radix switches expand the design space for topologies because a variety of high-degree topologies become feasible. It is thus possible to use network topologies with the low diameter and the low average shortest path length (ASPL) [21, 56, 67, 71, 77, 87], both measured in the hop count. Recently, random [76, 110] (or randomly optimized [90, 124]) topologies are demonstrated to provide the ASPL and the diameter that are close to the lower bounds [90, 124]. However, switch complexity increases quadratically impacting

on the area, costs, and the latency in a switch. Thus, the number of ports of a switch is limited, and low-radix switches are preferred if the hop count is the same [123].

#### 2.1.2.2 Routing Algorithm

A switch determines a route (a proper output port) for each incoming packet so that it finally reaches the destination node. In general, this *routing* must guarantee *deadlock-freedom* and *livelock-freedom*. A *deadlock* refers to a situation such that group of agents (packets) are unable to act because of waiting each other to release some resource (buffers or channels). A *livelock* refers to a situation such that packets are unable to reach their destinations although they can continue to move. Obviously, a livelock occurs only if non-minimal routing is used. A livelock can easily be avoided by specifying one or more paths for every pair of nodes and bounding the number of misroutings. However, how to design deadlock-free routing is not clear.

For regular topologies, specific deadlock-free routing algorithms can be designed and used; for example, dimension-order routing for two-dimensional mesh topologies. However, for irregular topologies, there exist no specific routing algorithm, and hence we need a general method to design deadlock-free routing algorithm for arbitrary topologies. We now describe previous work that proposes such methods and theoretical foundations on deadlock-free routing.

**Dally's theory** Dally *et al.* introduces a *channel dependency graph* (*CDG*) for guaranteeing deadlock-freedom of arbitrary interconnection networks [38]. A *CDG*, for a given interconnection network and a given set of possible routing paths, is a directed graph where

- the vertices denote the channels of the interconnection network;

- the edges denote the possible routing paths.

Dally *et al.* then proved that an interconnection network is deadlock-free if and only if the CDG is acyclic (we call it *Dally's theory*). Note that Dally's theory per se is not routing algorithm. Also, Dally's theory allows us only to check whether given pair of a network and routing is deadlock-free or not.

**Turn model and its extensions** The *turn model* [59] is a well-known application of Dally's theory for two-dimensional mesh/torus topologies. In the turn model, the packet forwardings are divided into four directions: north, south, east, and west. The change of directions, called a *turn*, are then classified into eight patterns; note that all the turns make right angles. As a result, we can see there exist only two types of cyclic dependencies (clockwise and counterclockwise). Thus, a deadlock-free routing can be designed by prohibiting one turn for each type of cyclic dependency.

The turn model, however, restricts the topology to mesh and tori. Thus, the turn model has been extended to n-dimensional topologies without diagonal links [45] and arbitrary topologies [69].

**Using additional buffers** Virtual channels are also useful for avoiding deadlock on the basis of Dally's theory. The *layered shortest path* (*LASH*) [113] uses virtual channels to achieve deadlock-free minimal routing. LASH can be combined with the *transition oriented routing* (*TOR*) [102] to enable flexibility of the different algorithms among the virtual channel layers; it is called *LASH-TOR* [112]. *In-transit buffers* (*ITB*) also enable a deadlock-free minimal routing. Packets are ejected from the network temporarily and stored in an ITB when deadlock occurs. These methods can be applied to arbitrary network topology and use the shortest path routing. Thus, we can assume the shortest path routing for any topology.

**Up\*/Down\* routing** Up\*/Down\* routing, introduced in [103], is a deadlock-free routing method that avoids cyclic dependencies by using spanning trees obtained by using a breadth-first search. Given network topology, a spanning tree is constructed and the packet forwardings are classified into the *up* direction or the *down* direction; then, a routing is deadlock-free if there exist no move to the up direction after moves to the down direction. A drawback of the Up\*/Down\* routing is the poor performance due to the biased link utilization.

Several methods for improving Up\*/Down\* routing have been proposed. Sancho *et al.* demonstrated that using a depth-first search (DFS) instead of BFS when constructing a spanning tree improves traffic balance [100]. *Left-up-first turn routing* (*L-turn routing*) [75] improves Up\*/Down\* routing by using *L-R directed-graph*, which is a transformation of the spanning tree and has left and right directions in addition to up and down directions. Using this graph, it distributes prohibited turns (in particular, avoids the heavy traffic around the root node of the spanning tree), and consequently the throughput is improved.

### 2.1.3 Layout

The nodes of an interconnection network are typically arranged in two-dimensional space. The layout determines the lengths of cables, and consequently it is essential for reducing signal propagation delay and cabling costs. Large-scale computer systems such as supercomputers have historically used Manhattan cabling in floorplan, because Euclid cabling makes both cabling and its maintenance become complex due to the diagonal cables on a floor. In the case of simple networks such as 2-D mesh networks, the layout is easily determined. However, in the case of irregular networks studied in this dissertation, the layout is not clear. Thus, we focus on the layout of irregular network topologies.

#### 2.1.3.1 Quadratic Assignment Problem

The layout of an interconnection network is determined by mapping each cluster to a cabinet on a floorplan so that the total cable length becomes minimum. This problem corresponds to the facility location problem, which has been studied in operation research [52]. This problem is NP-hard, and thus there is no known algorithm for solving this problem in polynomial time. Hence, metaheuristics-

based techniques have been developed to solve it. Solutions to this problem have been used in the computer industry for computer chip design and physical network layouts for HPC systems.

When we determine physical network layouts, we should reduce the cable lengths (the maximum length or the average length or both); this should be formulated as a quadratic assignment problem (QAP). It is reported that several algorithms can successfully applied to QAP (e.g., the simulated annealing [35], the robust tabu search [117], the reactive tabu search [20], the greedy randomized adaptive search procedure [96], the fast ant colony algorithm (FANT) [116], and the memetic algorithm [84].

#### 2.1.3.2 Randomly Optimized Grid Graph

Nakano *et al.* propose a method for designing interconnection networks with link-length constraints [90] by introducing a new graph called a *grid graph*. Using this, they propose a randomized algorithm for optimizing network topologies and layouts at the same time. A *grid graph* is a graph G = (V, E) such that  $V = \{(x, y) \mid 0 \leq x, y \leq \sqrt{N} - 1\}$  is a set of N nodes and E is a set of edges connecting a pair of two distinct nodes in V. We can think that nodes in V are arranged in a 2-dimensional space so that each node (x, y) is located at position (x, y). Let l(u, v) denote the Manhattan distance of two nodes u and v in V, that is,  $l(u, v) = |u_x - v_x| + |u_y - v_y|$ , where  $u = (u_x, u_y)$  and  $v = (v_x, v_y)$ . In a network with topology represented by a grid graph, the two nodes (u, v) are connected by a communication link of length l(u, v) wired along the grid.

A grid graph G = (V, E) is *L*-restricted if  $l(u, v) \leq L$  for all edges  $(u, v) \in E$ . Clearly, in a network with topology represented by an *L*-restricted grid graph, the length of every communication link is restricted to no more than *L*. A grid graph is *K*-regular if every node is connected with *K* edges. In [90], the authors show lower bounds on the diameter and the average shortest path length (ASPL) of *K*-regular *L*-restricted grid graph and provide a *K*-regular *L*-restricted grid graph whose diameter and ASPL are close to the lower bounds by using a randomized algorithm.

Moreover, [90] discusses quite interesting relationship between N, K, and L; the authors derive the following asymptotic formula, which provides a *well-balanced*<sup>1</sup> grid graph:

$$\Theta(\log N / \log K) \approx \Theta(\sqrt{N/L}).$$

(2.1)

Let us here describe an interesting finding. From (2.1), we have a decreasing function  $\log K = \Theta(L \log N/\sqrt{N})$  of N. Thus, if L is fixed and N is increased, K must be decreased to keep wellbalanced. Quite surprisingly, this relationship suggests that we should reduce the number of ports in each node of a computer system when we increase the number of nodes, provided that we use communication cables with the same technology.

$<sup>^{1}</sup>$ A K-regular L-restricted grid graph is *well-balanced* if the absolute difference between the lower bound on the ASPL of K-regular grid graph and that of L-restricted grid graph is a local minimum.

Nakahara *et al.* extended a grid graph so that it represents a 3D-NoC and call it a *stacked grid graph* [89]. They proposed a method for optimizing the average shortest path length and energy consumption of a 3D-NoC by using a multi-objective simulated annealing (MOSA) [92].

### 2.2 An Undirected Graph

#### 2.2.1 Definition and Notation

An *undirected graph* is an ordered pair G = (V, E) where

- V is a set of elements called *vertices*, and

- E is a set of elements called edges, each of which is a 2-element subset of V.

In the field of computer architecture, an undirected graph is used to represent a network of a computer system. An undirected graph is preferred to a directed graph because an interconnection networks use bi-directional links rather than uni-directinal ones.

There are three parameters important for interconnection networks: the number n of vertices (called the *order*), the maximum number of edges connected to a vertex  $\Delta$  (called the *degree*), and the maximum value of the shortest path length D (called the *diameter*). The shortest path length  $\ell(u, v)$  is the smallest possible path length between two vertices, u and v. The order should increase so that many processing units operate in parallel to improve the performance. The degree should be limited because designing a switch with many ports require high costs and the switching latency. The diameter should be reduced as much as possible because the ideal<sup>2</sup> communication latency depends on the path length between a source and a destination; the diameter is especially important for reducing the worst case communication latency.

In this context, the *degree/diameter problem* (*DDP*) has traditionally been attracting attention. This problem is defined as follows.

**Problem 2.1** (Degree/Diameter Problem). *Given natural numbers*  $\Delta$  *and* D, *find the largest possible order* n *in an undirected graph with maximum degree*  $\Delta$  *and diameter* D.

The DDP is considered for several classes of graphs, including undirected graphs, directed graphs, mixed graphs, bipartite graphs, planar graphs, and so forth. Among them, this dissertation focuses on the cases of undirected graphs, which are used for representing interconnection networks, and bipartite undirected graphs, which we will use in Chapter 4.

#### 2.2.2 Degree/Diameter Problem for General Graphs

Let us consider the tight upper bound on the order  $n^+$  of an undirected graph G = (V, E) with degree  $\Delta$  and diameter D. Trivially, if  $\Delta = 1$ , then D = 1 and  $n^+ = 2$ . Hence, we assume that  $\Delta \ge 2$ .

<sup>&</sup>lt;sup>2</sup>The ideal communication latency means the communication latency if there is no packet congestion.

For any fixed vertex  $u \in V$ , we can partition all the vertices in V into subsets  $V_0, V_1, \ldots$  such that  $V_i = \{v \in V \mid \ell(u, v) = i\}$ . Clearly,  $V_0 = \{u\}$  and  $|V_0| = 1$  hold. Since u is connected with at most  $\Delta$  edges,  $|V_1| \leq \Delta$  holds. Since each vertex in  $V_1$  is connected with at most  $\Delta - 1$  vertices in  $V_2, |V_2| \leq \Delta(\Delta - 1)$  holds. In general, we have

$$|V_i| \leqslant \begin{cases} 1 & \text{if } i = 0\\ \Delta(\Delta - 1)^{i-1} & \text{if } i \geqslant 1 \end{cases}$$

$$(2.2)$$

Thus, the upper bound on the order of an undirected graph with degree  $\Delta$  and diameter D becomes as follows:

$$n^{+} = 1 + \sum_{i=1}^{D} \Delta (\Delta - 1)^{i-1}$$

(2.3)

$$= \begin{cases} 1 + \Delta \frac{(\Delta - 1)^{D} - 1}{\Delta - 2} & \text{if } \Delta > 2\\ 2D + 1 & \text{if } \Delta = 2 \end{cases}.$$

(2.4)

This upper bound is called the *Moore bound*, and a graph of order  $n^+$  is called a *Moore graph* [64].

Solutions of DDP are applied to topologies of interconnection networks. For example, MMS graphs [83] are applied to Slim Fly [21].

#### 2.2.3 Degree/Diameter Problem for Bipartite Graphs

A bipartite graph (a.k.a. bigraph) is a graph  $G = (V_1, V_2, E)$  where

- $V_1$  and  $V_2$  are two disjoint and independent sets of vertices, and

- E is a set of edges that connect a vertex in  $V_1$  to one in  $V_2$ .

A bipartite graph is said to be *biregular* if two vertices in the same bipartition class have the same degree. We can consider DDP limited to the bipartite graphs.

The tight upper bound on the order  $n_{bi}^+$  of a bipartite graph with maximum degree  $\Delta$  and diameter D was given by Biggs [24]:

$$n_{\rm bi}^+ = \begin{cases} \frac{2(\Delta-1)^D - 1}{\Delta - 2} & \text{if } \Delta > 2\\ 2D & \text{if } \Delta = 2 \end{cases}.$$

(2.5)

This upper bound is called the *bipartite Moore bound*, and a bipartite graph of order  $n_{bi}^+$  is called a *bipartite Moore graph*.

A generalized polygon is a biregular bipartite graph such that the girth is equal to 2D. Feit and Higman proved that a  $\Delta$ -regular finite generalized polygon (i.e., a bipartite Moore graph) with  $\Delta > 2$ is either a complete bipartite graph (D = 2), a finite projective plane (D = 3), a finite generalized quadrangle (D = 4), or a finite generalized hexagon (D = 6) [53]. Chapter 4 will apply this theorem for designing interconnection networks.

#### 2.2.4 Order/Degree Problem

Even though DDP solutions have been applied to topologies of interconnection networks, they may not directly be usable for network topologies in supercomputer and data center systems. This is because they are for particular number of vertices (corresponding to compute nodes in a system), whereas the number of nodes in a real system is determined based on practical considerations such as power consumption and costs.

In this context, researchers on computer engineering proposed another graph problem called the *order/degree problem (ORP)* [5].

**Problem 2.2** (Order/Degree Problem). *Given natural number* n *and*  $\Delta$ , *find the minimum possible diameter* D *in an undirected graph with order* n *and maximum degree*  $\Delta$ . *If two or more graphs take the minimum diameter, find the minimum possible average shortest path length (ASPL) in an undirected graph with the minimum diameter.*

Note that, by definition, ORP contains two objective functions: the diameter and the ASPL.

Let us consider the tight lower bounds on the diameter  $D^-$  and the ASPL  $A^-$  of an undirected graph G = (V, E) with order n and maximum degree  $\Delta$ . For any fixed vertex  $u \in V$ , we can partition all the vertices in V into  $V_0, V_1, \ldots$  such that  $V_i = \{v \in V \mid \ell(u, v) = i\}$ . Clearly,  $V_0 = \{u\}$  and  $|V_0| = 1$  hold. Since u is connected with at most  $\Delta$  edges,  $|V_1| \leq \Delta$  holds. Since each vertex in  $|V_1|$ is connected with at most  $\Delta - 1$  vertices in  $V_2, |V_2| \leq \Delta(\Delta - 1)$  holds. In general, we have

$$|V_i| \leqslant \begin{cases} 1 & \text{if } i = 0\\ \Delta(\Delta - 1)^{i-1} & \text{if } i \geqslant 1 \end{cases}$$

(2.6)

From Eq. 2.4, we have

$$D = \begin{cases} \log_{\Delta - 1} \left( \frac{(n^{+} - 1)(\Delta - 2)}{\Delta} + 1 \right) & \text{if } \Delta > 2\\ \frac{n^{+} - 1}{2} & \text{if } \Delta = 2 \end{cases}.$$

(2.7)

Thus, we have

$$D^{-} = \begin{cases} \left\lceil \log_{\Delta-1} \left( \frac{(n-1)(\Delta-2)}{\Delta} + 1 \right) \right\rceil & \text{if } \Delta > 2\\ \left\lceil \frac{n-1}{2} \right\rceil & \text{if } \Delta = 2 \end{cases}.$$

(2.8)

Let m(i) be the *Moore function* such that

$$m(i) = \begin{cases} 1 & \text{if } i = 0\\ \min\left(1 + \sum_{j=1}^{i} \Delta(\Delta - 1)^{j-1}, n\right) & \text{if } i \ge 1 \end{cases}.$$

(2.9)

Clearly, the number of vertices reachable in i hops from u does not exceed m(i). Thus, we have

$$A^{-} = \sum_{i \ge 1} \frac{(m(i) - m(i-1)) \cdot i}{n-1}.$$

(2.10)

**Figure 2.5**: Concept of the use of network science for designing computer architecture. Network scientists mathematically model real-world networks, and then computer architects can apply the models for designing computer networks.

### 2.3 Network Science and its Applications

Thus far, we have described (classical) graph theory and examples of mathematical problems and results. What we have shown in this dissertation is just a tip of an iceberg, and there exists much beautiful and elegant work in the field of graph theory. However, several researchers in various fields such as complex systems, sociology, biology, and computer engineering should understand properties of real-world networks, which are possibly complex, dynamic, and/or stochastic. Thus, the new science of networks called *network science* has been studied empirically as well as theoretically. Mainly, researchers have proposed three basic models of real-world networks, which we describe below. Computer architects utilize network science for designing computer architecture on the basis of the concept shown in Fig. 2.5.

#### 2.3.1 Random Graph Models

A *random graph*—introduced by Solomonoff and Rapoport [114] and studied extensively by Erdős and Rényi [49, 50]—is a graph obtained by randomly sampling from a collection of possible graphs with fixed number of vertices. Among several proposed models, the *Erdős-Rényi model*, described below, is mostly be studied.

The Erdős-Rényi (ER) model generates a random graph  $G_{n,p}$  as follows:

- 1. Fix the number n of vertices and probability p (0 ).

- 2. Connect each pair of vertices with independent probability p.

As a result, the ER model generates either of possible  $2^{n(n-1)/2}$  graphs, including a complete graph and a graph with no edge. However, it is known that p determines the properties of ER model. For example, the ER model almost surely provides a connected graph when  $p \ge \log n/n$  while it does not when  $p < \log n/n$ . Such a qualitative change according to the value of p is called a *phase transition*.

According to [27], the average distance L satisfies

$$L \approx \frac{\log n}{\log \langle k \rangle},\tag{2.11}$$

where  $\langle k \rangle$  denotes the average degree. Thus, when we use a random graph for the network topology, the ASPL becomes  $\mathcal{O}(\log n)$ , which grows slowly as the order increases. That is why using randomness when constructing network topologies is helpful for designing low-latency interconnection networks.

The random graph  $G_{n,p}$  has a specific degree distribution. Since each vertex is connected to the other n-1 vertices with probability p, the degree distribution becomes

$$p(k) = \frac{(n-1)!}{k!(n-1-k)!} p^k (1-p)^{n-1-k},$$

(2.12)

where p(k) denotes the probability that the degree of a vertex is k. It is clearly a binomial distribution and becomes the Poisson distribution in the limit where  $n \to \infty$ ,  $p \to 0$ , and  $(n-1)p \to \lambda$  ( $\lambda$  is a positive constant).

Computer architects may think that the degree distribution should not be the Poisson distribution. Instead, a network should be regular, i.e., the degree is fixed. To construct a random network with arbitrary degree distribution, we can use an extended model of random graphs. The *configuration model* [93] generates a random graph with arbitrary degree distribution as follows:

- 1. Fix the number n of vertices.

- 2. Fix the degree distribution  $p(0), p(1), \ldots, p(k_{\max})$  where  $k_{\max}$  denotes the maximum degree  $(k_{\max} \leq n-1)$ .

- 3. Generate the *degree sequence*  $k_1, k_2, \ldots, k_n$  so that it satisfies the fixed degree distribution.

- 4. Generate a random graph G = (V, E) where  $V = \{v_1, v_2, \dots, v_n\}$  and the degree of  $v_i$  is  $k_i$ .

According to [93], the average distance L of a configuration model satisfies the following if  $\langle k^2 \rangle$  exists in the limit where  $n \to \infty$ :

$$L = 1 + \frac{\log \frac{n}{\langle k \rangle}}{\log \frac{\langle k^2 \rangle - \langle k \rangle}{\langle k \rangle}}.$$

(2.13)

One of the important examples of the configuration model is a *regular random graph*. It is a random graph where the degree of all the vertices is the same, i.e.,  $\langle k \rangle$ . Thus, it is straightforward to use a regular random graph for a topology of an interconnection network since the network typically consists of the switches with fixed ports. Several researchers propose the use of a regular random graph for designing network topologies [51, 74, 90, 109, 110, 123, 124].

#### 2.3.2 Watts-Strogatz Model

In 1967, Milgram demonstrated the *small-world phenomenon*, that is to say, human society consists of a network with short path-lengths; more specifically, people in the United States seemed to be connected by approximately three friendship links on average, without speculating on global linkages [85]. This phenomenon is sometimes associated with the phrase "six degrees of separation" and regarded as a characteristics of real-world complex networks.

Afterward, in 1998, Wattz and Strogatz published an epoch-making paper proposing the *Wattz-Strogatz (WS) model* (a.k.a. the small-world model), which excellently characterizes the networks with the small-world phenomenon [121]. The WS model provides a network with the short average distance and the large *clustering coefficient*, which denotes the probability that two adjacent nodes of a node is connected.

The WS model provides a network as follows:

- 1. Fix the number n of vertices and the average degree  $\langle k \rangle$  ( $\langle k \rangle$  is an even number).

- 2. Construct a cycle graph with n vertices.

- 3. Connect a vertex u and the vertices that can be reached within  $\langle k \rangle / 2$  hops from u.

- 4. Change an endpoint of an edge with independent probability  $p \ (0 \le p \le 1)$ .

Obviously, the obtained network depends on the value of p. When p = 0, a network becomes an extended cycle graph. When p = 1, a network almost corresponds to a random graph obtained by the ER model. The small-world phenomenon is obtained when  $p \in [0.01, 0.1]$ . The degree of the WS model is fixed when p = 0, and its distribution approaches the Poisson distribution as p increases.

According to [19], the clustering coefficient C(p) of the WS model with probability p satisfies

$$C(p) = \frac{3\langle k \rangle - 6}{4\langle k \rangle - 4} (1 - p)^3.$$

(2.14)

According to [94], the average distance L(p) of the WS model with probability p satisfies

$$L(p) = \frac{2n}{\langle k \rangle} f\left(\frac{n\langle k \rangle p}{2}\right), \qquad (2.15)$$

$$f(x) = \frac{1}{2\sqrt{x^2 + 2x}} \tanh^{-1}\left(\frac{x}{\sqrt{x^2 + 2x}}\right).$$

(2.16)

Note that L(p) is minimized when p = 1. Hence we should use the ER model rather than the WS model if we consider only the ASPL of a network topology. However, the clustering coefficient decreases as p increases.

Several researchers propose the use of a small-world network for designing network topologies [41, 95, 108]

#### 2.3.3 Models of Scale-free Networks

One might wonder if the models described above capture real-world networks precisely. In fact, they do not. In 1999, Albert et al. showed that the power law described the topology of the World-Wide Web [14]. Formally, the degree distribution p(k) satisfies

$$p(k) \propto k^{-\gamma}.$$

(2.17)

A random graph with the power law degree distribution is called a *scale-free* network. There are many models describing the scale-free networks. For example, the configuration model, described earlier, is one of such models.

Cohen and Havlin [34] shew that the average distance L (or the diameter) of the scale-free networks satisfies

$$L \propto \begin{cases} \log \log n & \text{if } 2 < \gamma < 3\\ \log n / \log \log n & \text{if } \gamma = 3. \end{cases}$$

(2.18)

Note that the average distance grows more slowly as *n* increases than it does in the case of small-world networks. Thus, Cohen and Havlin say that scale-free networks are *ultra-small*.

Several researchers propose the use of a scale-free network for designing network topologies [54, 62]. However, a scale-free network would not be useful for designing interconnection networks because it requires switches with many ports, which should induce high switching latency and costs. Also, the number of ports of a switch do not vary.

## 2.4 Design Theory

In combinatorial mathematics, design theory [43] refers to the study of *designs*—systems of finite sets whose arrangements satisfy generalized concepts of balance or symmetry or both. In particular, it studies necessary and sufficient conditions for the existence of a *block design*.

A *block design* with parameters  $(v, b, r, k, \lambda)$  is a pair  $(\mathbf{X}, \mathcal{A})$  where

- X is a set of v elements (called *points*),

- $\mathcal{A}$  is a family of b subsets of **X**, each of cardinality k (called *blocks*),

- Every point occurs in exactly r blocks, and

- Every pair of distinct points occurs in exactly  $\lambda$  blocks.

If  $\mathcal{A} = \{\mathbf{X}\}$ , then  $(\mathbf{X}, \mathcal{A})$  is obviously a block design, and it is said to be an *obvious* design. Also, if  $\mathcal{A}$  is a set of the *k*-subsets of  $\mathbf{X}$ , then  $(\mathbf{X}, \mathcal{A})$  is obviously a block design, and it is said to be a *complete* design. If a block design is neither obvious nor complete, it is called a *balanced incomplete block design* (*BIBD*) and denoted as  $(v, b, r, k, \lambda)$ -BIBD. The five parameters are not all independent; the basic two equations are

$$bk = vr, (2.19)$$

$$\lambda(v-1) = r(k-1).$$

(2.20)

Thus, it is not uncommon to write a BIBD as a  $(v, k, \lambda)$ -BIBD.

The most basic necessary condition for the existence of a BIBD known as *Fischer's inequality*, named after the statistician Ronald Fisher, states that a  $(v, b, r, k, \lambda)$ -BIBD exists only if  $b \ge v$  (or

equivalently, if  $r \ge k$ ). A BIBD with b = v (or equivalently, r = k) is called a *symmetric* BIBD. The parameters of a symmetric design satisfy

$$\lambda(v-1) = k(k-1).$$

(2.21)

Finite projective planes are symmetric BIBD with  $\lambda = 1$ . From Eq. 2.21, finite projective planes satisfy

$$v - 1 = k(k - 1).$$

(2.22)

Since r = k holds by the definition of a symmetric BIBD, the order n of a finite projective plane is equal to k - 1. From Eq. 2.22, we obtain  $v = (n + 1)n + 1 = n^2 + n + 1$  points in a finite projective plane of order n. Thus, a finite projective plane of order n is a  $(n^2 + n + 1, n + 1, 1)$ -BIBD.

From a  $(v, b, r, k, \lambda)$ -BIBD, we can construct a graph called an *incidence graph* (a.k.a. *Levi graph*), which is a bipartite graph  $G = (V_1, V_2, E)$  where

- $V_1$  is a set of points,

- $V_2$  is a set of blocks, and

- E is a set of edges that connect a point  $p_i$  and a block  $B_j$  if and only if  $p_i$  occurs in  $B_j$ .

The incidence graph of a BIBD will be applied to a network topology in Chapter 4.

# Chapter 3

# Low-Latency Interconnection Networks with Single-Port Hosts

## 3.1 Overview

In this chapter, we deal with two topological properties that are important for designing interconnection networks, the host-to-host average shortest path length (h-ASPL) and the bisection width (BiW). We propose a method for designing a topology with low h-ASPL and high BiW. By analyzing host-switch graphs, we provide answers to the following questions: (1) given the number of hosts and the number of ports per switch, how many switches should be used?; and (2) which is better, direct or indirect networks, in terms of the h-ASPL and the BiW?

First, Section 3.2 provides theoretical foundation of host-switch graphs; we formally define a host-switch graph and provide upper and lower bounds on the maximum number of hosts, the diameter, and the h-ASPL. Second, Sections 3.3-3.4 present host-switch graphs with low h-ASPL; we take deterministic and heuristic approaches in each section. Here we demonstrate that the heuristic approach is more practical than the deterministic one for certain reasons. We empirically show that the optimal number of switches is a key parameter for host-switch graphs in terms of the h-ASPL and also the BiW. Third, in Section 3.5, we practically compare proposed network topologies with existing ones in terms of performance, topological properties, power consumption, and cost breakdowns. Section 3.6 reviews related work, and finally, we conclude the chapter in Section 3.7.

# **3.2** Introduction of a Host-Switch Graph

## 3.2.1 Definition and Notation

A host-switch graph is a 3-tuple G = (H, S, E) with integer parameters  $n \ge 3$ ,  $m \ge 1$ , and  $r \ge 3$ where

•  $H = \{h_0, h_1, \dots, h_{n-1}\}$  is a set of *n* elements called *host vertices* (or simply *hosts*),

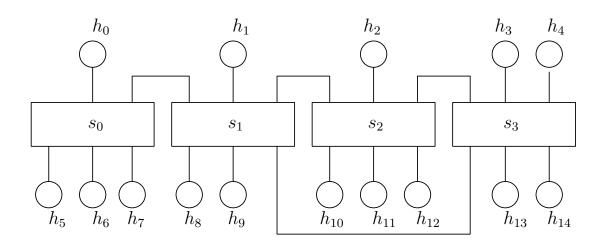

Figure 3.1: An example of a host-switch graph (n = 15, m = 4, r = 6).

- $S = \{s_0, s_1, \dots, s_{m-1}\}$  is a set of m elements called *switch vertices* (or simply *switches*), and

- E ⊂ {{s<sub>i</sub>, s<sub>j</sub>} | s<sub>i</sub>, s<sub>j</sub> ∈ S} ∪ {{h<sub>i</sub>, s<sub>j</sub>} | (h<sub>i</sub> ∈ H) ∧ (s<sub>j</sub> ∈ S)} is a set of unordered pairs of connected vertices called *edges*.

The number n of hosts is called the *order* of G. Each host must be connected with exactly one edge while each switch is connected with at most r edges. Thus each switch must have at least r ports. The number r of required ports per switch is called the *radix* of G. In Fig. 3.1 we illustrate an example of a host-switch graph with 15 hosts and 4 switches with radix r = 6. Throughout this paper, a circle and a rectangle represent a host and a switch, respectively.

Clearly, at least m - 1 edges are necessary to connect m switches such that they are reachable each other. Since m switches can connect at most mr edges, we can state:

**Lemma 3.1** (Trivial upper bound on the order). For any connected host-switch graph with m r-port switches, the order n is not greater than mr - 2(m - 1).

For any two hosts  $h_i$  and  $h_j$ , let  $\ell(h_i, h_j)$  denote the number of edges along the shortest path between  $h_i$  and  $h_j$ . For example,  $\ell(h_0, h_{14})$  of a host-switch graph shown in Fig. 3.1 is 4, because the shortest path between them is  $(h_0, s_0, s_1, s_3, h_{14})$ . Using  $\ell(h_i, h_j)$ , we can define two topological properties. The *diameter* D(G) of a host-switch graph is defined as

$$D(G) \coloneqq \max\{\ell(h_i, h_j) \mid 0 \leq i < j < n\}.$$

The host-to-host average shortest path length (h-ASPL) A(G) is defined as

$$A(G) \coloneqq \sum_{0 \le i < j < n} \ell(h_i, h_j) / \binom{n}{2}.$$

23

These metrics are essentially different from the diameter and the average shortest path length (ASPL) of an ordinary undirected graph in that the considered path is between hosts rather than switches. In this paper we mainly discuss the h-ASPL, because it measures the ideal all-to-all communication latency of interconnection networks.

#### 3.2.2 Upper and Lower Bounds

Let us consider tight upper bound on the order of a host-switch graph with r and D(G). For any source host  $h_s \in H$ , we can partition all the hosts in H into subsets  $H_0, H_1, \ldots$  such that  $H_i = \{h_d \in H \mid \ell(h_s, h_d) = i\}$ . Similarly, we can partition all the switches in S into subsets  $S_1, S_2, \ldots$  such that  $S_i = \{s_d \in S \mid \ell(h_s, s_d) = i\}$ . Let  $A_{h_s}(G)$  and  $D_{h_s}(G)$  respectively denote a single-source h-ASPL from  $h_s$  and a single-source diameter from  $h_s$ , as follows:

$$\begin{aligned} A_{h_s}(G) &\coloneqq \sum_{0 \leqslant i < n, i \neq s} \ell(h_s, h_i) / (n-1), \\ D_{h_s}(G) &\coloneqq \max\{\ell(h_s, h_i) \mid 0 \leqslant i < n \text{ and } i \neq s\}. \end{aligned}$$

Using these notations, we obtain the upper bound on the order, as follows:

**Theorem 3.1** (Upper bound on the order). For any host-switch graph with radix r and diameter D(G), the order n of a host-switch graph is not greater than  $(r-1)^{D(G)-1} + 1$ .

*Proof.* For any fixed host  $h_s$  of a host-switch graph, let  $N_i$  be the upper bound on  $|H_i| + |S_i|$ . Clearly,  $N_i$  is equal to

$$\begin{cases} |H_0| = 1, & \text{if } i = 0\\ |S_1| = 1, & \text{if } i = 1\\ |S_{i-1}| (r-1). & \text{if } i > 1 \end{cases}$$

(3.1)

Hence, to maximize the order, we must satisfy  $N_i = |S_i|$  for  $1 \le i < D(G)$  and  $N_i = |H_i|$  for i = D(G). In this situation, the order is

$$\sum_{i=0}^{D(G)} |H_i| = (r-1)^{D(G)-1} + 1.$$

The lower bound on the diameter follows from Theorem 3.1:

**Corollary 3.1** (Lower bound on the diameter). For any host-switch graph with order n and radix r, the diameter is not less than  $\lceil \log_{r-1}(n-1) \rceil + 1$ .

Let us call a host-switch graph with a root host  $h_s$  and  $(r-1)^{D_{h_s}(G)-1}$  leaf hosts a *full host-switch tree*. Clearly, the lower bound on  $A_{h_s}(G)$  is the lower bound on A(G).

We define a *complete host-switch tree* as follows:

- 1. A full host-switch tree is a complete host-switch tree.

- 2. A host-switch tree obtained by performing the following operations to any complete host-switch tree T is also a complete host-switch tree: (A) if T has a switch connected to less than r vertices, then connect a new host to it; and (B) if T has no such switch, then we pick one of the hosts closest to  $h_s$  and replace it by a new switch with two hosts.

Both operations (A) and (B) increase the order n by one, and hence a complete graph host-switch tree is a full host-switch tree if and only if n is equal to  $(r-1)^{d-1} + 1$  for some d.

In a complete host-switch tree T with a root host  $h_s$ ,  $H_{D_{h_s}(T)} \cup H_{D_{h_s}(T)-1}$  includes all the leaf hosts. Clearly, a complete host-switch tree has at least one host in  $H_{D_{h_s}(T)-1}$  if it is not a full host-switch tree. Also, at most one switch in  $S_{D_{h_s}(T)-1}$  in a complete host-switch tree can take degree less than r.

Now we can state the following theorem:

**Theorem 3.2** (Lower bound on the h-ASPL). A single-source h-ASPL from the root of a complete host-switch tree provides the lower bound on the h-ASPL.

*Proof.* Consider any host-switch tree T with a root host  $h_s$ . If there exists a host  $h_a \in H_i$   $(1 \leq i \leq D_{h_s}(T) - 2)$ , then we can decrease  $A_{h_s}(T)$  by performing the following operations: (1) replace  $h_a$  with a new switch  $s_m$  connected with a host; (2A) if r > 3, then reconnect more than two hosts in  $H_{D_{h_s}(T)}$  to  $s_m$ ; and (2B) if r = 3, then reconnect two hosts in  $H_{D_{h_s}(T)}$  and replace a switch in  $S_{D_{h_s}(T)-1}$  with another host in  $H_{D_{h_s}(T)}$ . Hence, a host-switch tree can provide the lower bound on  $A_{h_s}(T)$  only if  $H_i$  is empty for all i  $(1 \leq i \leq D_{h_s}(T) - 2)$ ; in this case,  $A_{h_s}(T)$  takes the minimum value if and only if a host-switch tree is a complete host-switch tree. Therefore a complete host-switch tree provides the lower bound on the single-source h-ASPL, which is also the lower bound on the h-ASPL.

By Theorem 3.2, we can compute the lower bound on the h-ASPL as follows:

$$\begin{cases} D^{-}, & \text{if } n = (r-1)^{D^{-}-1} + 1\\ D^{-} - \alpha/(n-1), & \text{otherwise} \end{cases}$$

where  $D^- = \lceil \log_{r-1}(n-1) \rceil + 1$  is the lower bound on the diameter of G, and  $\alpha$  denotes the number of hosts in  $H_{D_{h_s}(T)-1}$  in a complete host-switch graph T. In  $H_{D_{h_s}(T)-1}$ , at most  $(r-1)^{D^--2}$  hosts can be connected. However, it is less than n by  $(n-1-(r-1)^{D^--2})$  if T is not a full host-switch tree, and hence we must run operations (B) and then (A). After we run operation (B), we can increase the number of hosts by r-2 (remove one host from  $H_{D_{h_s}(T)-1}$  and add r-1 hosts to  $H_{D_{h_s}(T)}$ ). Thus, we have