# **THÈSE**

En vue de l'obtention du

### **DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE**

**Délivré par** *INP Toulouse* **Discipline ou spécialité :** *INFORMATIQUE*

#### Présentée et soutenue par Tzvetomila Slavova Le 28 Avril 2009

**Titre :** Résolution triangulaire de systèmes linéaires creux de grande taille dans un contexte parallèle multifrontal et hors-mémoire.

Parallel triangular solution in the out-of-core multifrontal approach for solving large sparse linear systems.

#### **JURY**

Amestoy P.R Duff,I. Guermouche, A. L'Excellent,J-Y. Ng, E. G. Trystram, D Ucar, B. Professeur, INPT, Toulouse Directeur de recherche, CERFACS, Toulouse LaBRI, Univ. Bordeaux 1 / INRIA Futurs Chargé de recherche, INRIA-LIP, Lyon Directeur de recherche, Lawrence Berkeley Lab. Professeur, INPG, Grenoble Chargé de recherche CNRS, LIP, Lyon Directeur de thèse Co-encadrant Co-encadrant Membre Rapporteur Rapporteur Membre

**Ecole doctorale :** *Mathématiques, Informatique et Télécommunications de Toulouse*

**Unité de recherche :** *CERFACS* **Directeur de Thèse :** *Amestoy, P. R.*

### **THÈSE**

présentée pour obtenir

### LE TITRE DE DOCTEUR DE L'INSTITUT NATIONAL POLYTECHNIQUE DE TOULOUSE

Spécialité: INFORMATIQUE

par

# **Tzvetomila Slavova**CERFACS

# Résolution triangulaire de systèmes linéaires creux de grande taille dans un contexte parallèle multifrontal et hors-mémoire.

Parallel triangular solution in the out-of-core multifrontal approach for solving large sparse linear systems

Thèse présentée le 28 Avril 2009 devant le jury composé de:

Amestoy, P. R. Professeur, INPT, Toulouse Directeur de thèse Duff, I. Directeur de recherche, CERFACS, Toulouse Co-encadrant Guermouche, A. LaBRI, Univ. Bordeaux 1 / INRIA Futurs Co-encadrant L'Excellent, J-Y. Chargé de recherche, INRIA-LIP, Lyon Membre Directeur de recherche, Lawrence Berkeley Lab. Ng, E. G. Rapporteur Trystram, D. Professeur, INPG, Grenoble Rapporteur Ucar, B. Chargé de recherche CNRS, LIP, Lyon Membre

Thèse préparée au CERFACS, CERFACS Report Ref: TH-PA-09-59

#### **Abstract**

We consider the solution of very large systems of linear equations with direct multifrontal methods. In this context the size of the factors is an important limitation for the use of sparse direct solvers. We will thus assume that the factors have been written on the local disks of our target multiprocessor machine during parallel factorization. Our main focus is the study and the design of efficient approaches for the forward and backward substitution phases after a sparse multifrontal factorization. These phases involve sparse triangular solution and have often been neglected in previous works on sparse direct factorization. In many applications, however, the time for the solution can be the main bottleneck for the performance.

This thesis consists of two parts. The focus of the first part is on optimizing the out-of-core performance of the solution phase. The focus of the second part is to further improve the performance by exploiting the sparsity of the right-hand side vectors.

In the first part, we describe and compare two approaches to access data from the hard disk. We then show that in a parallel environment the task scheduling can strongly influence the performance. We prove that a constraint ordering of the tasks is possible; it does not introduce any deadlock and it improves the performance. Experiments on large real test problems (more than 8 million unknowns) using an out-of-core version of a sparse multifrontal code called MUMPS (MUltifrontal Massively Parallel Solver) are used to analyse the behaviour of our algorithms.

In the second part, we are interested in applications with sparse multiple right-hand sides, particularly those with single nonzero entries. The motivating applications arise in electromagnetism and data assimilation. In such applications, we need either to compute the null space of a highly rank deficient matrix or to compute entries in the inverse of a matrix associated with the normal equations of linear least-squares problems. We cast both of these problems as linear systems with multiple right-hand side vectors, each containing a single nonzero entry. We describe, implement and comment on efficient algorithms to reduce the input-output cost during an out-of-core execution. We show how the sparsity of the right-hand side can be exploited to limit both the number of operations and the amount of data accessed.

The work presented in this thesis has been partially supported by SOLSTICE ANR project (ANR-06-CIS6-010).

**Keyword:** Gaussian elimination, multifrontal method, Distributed computing, parallel computing, sparse matrices, tasks scheduling, multiple right-hand side vectors.

#### Résumé

Nous nous intéressons à la résolution de systèmes linéaires creux de très grande taille par des méthodes directes de factorisation. Dans ce contexte, la taille de la matrice des facteurs constitue un des facteurs limitants principaux pour l'utilisation de méthodes directes de résolution. Nous supposons donc que la matrice des facteurs est de trop grande taille pour être rangée dans la mémoire principale du multiprocesseur et qu'elle a donc été écrite sur les disques locaux (hors-mémoire : OOC) d'une machine multiprocesseurs durant l'étape de factorisation. Nous nous intéressons à l'étude et au développement de techniques efficaces pour la phase de résolution après une factorization multifrontale creuse. La phase de résolution, souvent négligée dans les travaux sur les méthodes directes de résolution directe creuse, constitue alors un point critique de la performance de nombreuses applications scientifiques, souvent même plus critique que l'étape de factorisation.

Cette thèse se compose de deux parties. Dans la première partie nous nous proposons des algorithmes pour améliorer la performance de la résolution hors-mémoire. Dans la deuxième partie nous pousuivons ce travail en montrant comment exploiter la nature creuse des seconds membres pour réduire le volume de données accédées en mémoire.

Dans la première partie de cette thèse nous introduisons deux approches de lecture des données sur le disque dur. Nous montrons ensuite que dans un environnement parallèle le séquencement des tâches peut fortement influencer la performance. Nous prouvons qu'un ordonnancement contraint des tâches peut être introduit; qu'il n'introduit pas d'interblocage entre processus et qu'il permet d'améliorer les performances. Nous conduisons nos expériences sur des problèmes industriels de grande taille (plus de 8 Millions d'inconnues) et utilisons une version hors-mémoire d'un code multifrontal creux appelé MUMPS (solveur multifrontal parallèle).

Dans la deuxième partie de ce travail nous nous intéressons au cas de seconds membres creux multiples. Ce problème apparaît dans des applications en electromagnétisme et en assimilation de données et résulte du besoin de calculer l'espace propre d'une matrice fortement déficiente, du calcul d'éléments de l'inverse de la matrice associée aux équations normales pour les moindres carrés linéaires ou encore du traitement de matrices fortement réductibles en programmation linéaire. Nous décrivons un algorithme efficace de réduction du volume d'Entrées/Sorties sur le disque lors d'une résolution horsmémoire. Plus généralement nous montrons comment le caractère creux des seconds -membres peut être exploité pour réduire le nombre d'opérations et le nombre d'accès à la mémoire lors de l'étape de résolution.

Le travail présenté dans cette thèse a été partiellement financé par le projet SOLSTICE de l'ANR (ANR-06-CIS6-010).

**Mots-clés:** calcul distribué, calcul parallèle, élimination de Gauss, matrices creuses, méthode multifrontale, séquencement des tâches, seconds membres multiples

## **Contents**

|   | Abs  | ract                                                           | i         |

|---|------|----------------------------------------------------------------|-----------|

|   | Résu | ımé                                                            | iii       |

| 1 | Gen  | eral introduction                                              | 1         |

|   | 1.1  | Context of our study                                           | 8         |

|   | 1.2  | General background                                             | 10        |

|   |      | Graphs                                                         | 10        |

|   |      | Direct methods                                                 | 13        |

|   |      | Least-square solution                                          | 15        |

|   | 1.3  | Test environment                                               | 17        |

| I | Ana  | ysis of the Solution Phase of a Parallel Multifrontal Approach | 21        |

| 2 | Intr | oduction                                                       | 27        |

| 3 | Mai  | n in-core parallel features of the solver                      | <b>29</b> |

|   | 3.1  | Introduction                                                   | 29        |

|   | 3.2  | In-core parallel factorization phase                           | 29        |

|   |      | 3.2.1 Parallelism during the factorization phase               | 31        |

|   | 3.3  | r r r                                                          | 33        |

|   |      |                                                                | 33        |

|   |      |                                                                | 33        |

|   |      | 3.3.3 Algorithm for forward substitution                       | 35        |

|   |      | 3.3.4 Detailed illustration of the forward substitution        | 38        |

|   |      | 8                                                              | 40        |

|   |      | 3.3.6 Detailed illustration of the backward substitution       | 41        |

| 4 | Out  | of-Core (OOC) main features                                    | <b>45</b> |

|   | 4.1  | Introduction                                                   | 45        |

|   | 4.2  | OOC factorization phase                                        | 45        |

|   | 4.3  | OOC solve phase                                                | 46        |

|   | 11   | System based demand driven approach                            | 47        |

VI

| 5  | DIRECT_IO based method 49 |              |                                                                   |           |  |  |  |  |  |  |

|----|---------------------------|--------------|-------------------------------------------------------------------|-----------|--|--|--|--|--|--|

|    | 5.1                       | Introduction |                                                                   |           |  |  |  |  |  |  |

|    | 5.2                       | User d       | lefined buffer                                                    | 49        |  |  |  |  |  |  |

|    | 5.3                       | States       | of a node                                                         | 50        |  |  |  |  |  |  |

|    | 5.4                       | Comp         | arison of System_Based and Direct_IO methods                      | 51        |  |  |  |  |  |  |

|    |                           | 5.4.1        | Sequential case                                                   | 51        |  |  |  |  |  |  |

|    |                           | 5.4.2        | Influence of parallelism on the performance                       | 52        |  |  |  |  |  |  |

|    | 5.5                       | Influer      | nce of scheduling                                                 | 53        |  |  |  |  |  |  |

|    |                           | 5.5.1        | Sequential performance                                            | 53        |  |  |  |  |  |  |

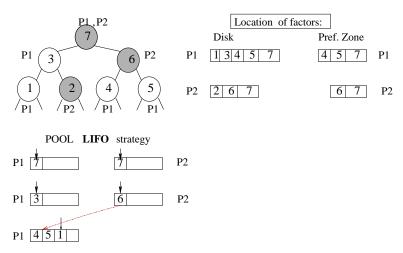

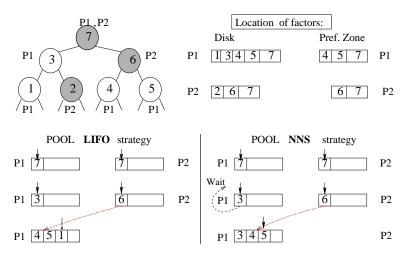

|    |                           | 5.5.2        | Parallel performance with LIFO scheduler                          | 55        |  |  |  |  |  |  |

|    |                           | 5.5.3        | Illustration of the high number of emergency calls with LIFO      | 56        |  |  |  |  |  |  |

| 6  | Scho                      | eduling      | to improve performance                                            | <b>59</b> |  |  |  |  |  |  |

|    | 6.1                       | NNS s        | scheduler                                                         | 59        |  |  |  |  |  |  |

|    |                           | 6.1.1        | Description of the algorithm                                      | 59        |  |  |  |  |  |  |

|    |                           | 6.1.2        | Experiments with LIFO and NNS strategies                          | 63        |  |  |  |  |  |  |

|    | 6.2                       | BPN s        | cheduler                                                          | 66        |  |  |  |  |  |  |

|    |                           | 6.2.1        | Description of the algorithm                                      | 66        |  |  |  |  |  |  |

|    |                           | 6.2.2        | Experiments with BPN strategy                                     | 70        |  |  |  |  |  |  |

| II | Exp                       | oloit Spa    | arsity of Sparse Right-Hand Sides in OOC Environment              | 73        |  |  |  |  |  |  |

| 7  | Inti                      | roductio     | on .                                                              | <b>79</b> |  |  |  |  |  |  |

| 8  | Exp                       | loiting s    | sparsity of the right-hand sides: Context and applications        | 81        |  |  |  |  |  |  |

|    | 8.1                       | Conte        | xt of our study                                                   | 81        |  |  |  |  |  |  |

|    |                           | 8.1.1        | Relationship between matrix graph and structure of the solution . | 81        |  |  |  |  |  |  |

|    |                           | 8.1.2        | Background on computing entries in the inverse of a matrix        | 84        |  |  |  |  |  |  |

|    | 8.2                       | Spars        | ity of the right hand-sides and applications                      | 91        |  |  |  |  |  |  |

|    |                           | 8.2.1        | Sparse right-hand sides / reducible matrices                      | 91        |  |  |  |  |  |  |

|    |                           | 8.2.2        | Null-space computations                                           | 92        |  |  |  |  |  |  |

|    |                           | 8.2.3        | Computing entries in $A^{-1}$                                     | 96        |  |  |  |  |  |  |

|    |                           | 8.2.4        | Pruning and concluding remarks                                    | 98        |  |  |  |  |  |  |

| 9  | Algo                      | orithms      | to exploit sparsity                                               | 101       |  |  |  |  |  |  |

|    | 9.1                       | Introd       | uction                                                            | 101       |  |  |  |  |  |  |

|    | 9.2                       | Prunin       | ng algorithms                                                     | 101       |  |  |  |  |  |  |

|    |                           | 9.2.1        | 'Branch detection'                                                | 101       |  |  |  |  |  |  |

|    |                           | 9.2.2        | Subtree detection                                                 | 103       |  |  |  |  |  |  |

|    | 9.3                       | Topolo       | ogically-based permutations                                       | 104       |  |  |  |  |  |  |

|          | •    |

|----------|------|

| CONTENTS | VI   |

| CONTENTS | V 11 |

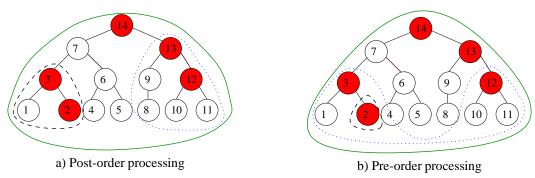

|     |        | 9.3.1 Post-order permutation of the right-hand sides             | 106          |

|-----|--------|------------------------------------------------------------------|--------------|

|     |        | 9.3.2 Pre-order permutation of the right-hand sides              | 106          |

|     | 9.4    | Permuting columns of the right-hand sides to address parallelism | 107          |

| 10  | Нур    | ergraph models to exploit the sparsity                           | 109          |

|     | 10.1   | Introduction                                                     | 110          |

|     | 10.2   | Model for entries in $A^{-1}$                                    | 110          |

|     | 10.3   | Model for null-space computations                                | 114          |

|     | 10.4   | Conclusions                                                      | 115          |

| 11  | Resu   | dts and performance analysis                                     | 117          |

|     | 11.1   | Introduction                                                     | 117          |

|     | 11.2   | Null-space computations                                          | 117          |

|     |        | 11.2.1 Sequential execution                                      | 117          |

|     |        | 11.2.2 Parallel execution                                        | 120          |

|     | 11.3   | Computing elements in $A^{-1}$                                   | 122          |

|     |        | 11.3.1 Sequential execution                                      | 122          |

|     |        | 11.3.2 Parallel execution and permutations                       | 124          |

| 12  | Gene   | eral conclusion and future work                                  | 1 <b>2</b> 9 |

| Bił | oliogr | aphy 1                                                           | 133          |

viii CONTENTS

## **Chapter 1**

## **General introduction**

#### Introduction générale

#### Contexte de l'étude

Nous nous intéressons à la résolution de grands systèmes linéaires

$$Ax = b ag{1}$$

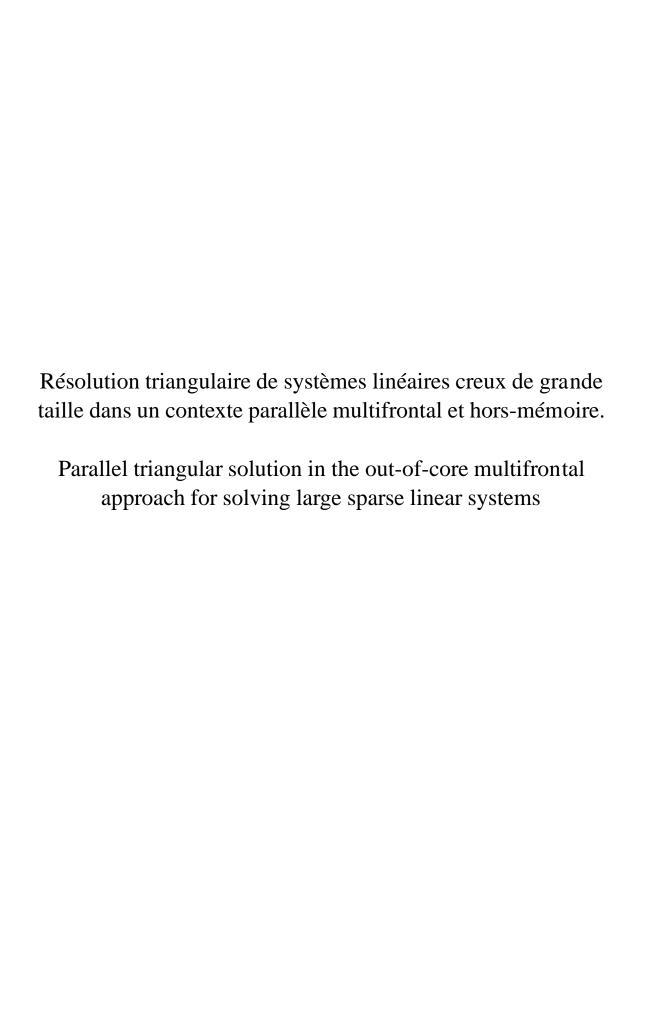

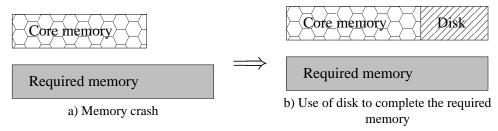

avec une méthode directe multifrontale, dans un environnement parallèle hors-mémoire (dans un environnement hors-mémoire le disque dur est utilisé comme extension de la mémoire centrale, voir Figure 1).

Figure 1: Limitation mémoire résolue par l'utilisation de la mémoire du disque dur.

A est une matrice carrée creuse de très grande taille, et x et b sont des vecteurs colonnes. La matrice originale A est factorisée en un produit de matrices dites matrices de facteurs. Selon que la structure de la matrice est symétrique ou non on effectuera respectivement une factorisation  $A = LDL^T$  ou A = LU. Les matrices L et U sont respectivement des matrices triangulaires inférieures et supérieures, et D est une matrice diagonale ou bloc-diagonale avec des blocs  $1 \times 1$  et  $2 \times 2$ . Les matrices de facteurs sont ensuite utilisées pour résoudre le système initial via une séquence de résolution élémentaires,

$$LDL^{T}x = b \quad ou \quad LUx = b \tag{2}$$

selon que la matrice est symétrique ou non.

Le nombre d'entrées dans les facteurs (pour des problèmes tridimensionnels de grande taille) peut être beaucoup plus important ( 10 à 100 fois plus grand) que la taille de la matrice originale. Ainsi la mémoire utilisée pour stocker ces facteurs peut constituer un obstacle dans l'utilisation d'approches directes de résolution. Pour autant les méthodes directes, de par leur robustesse numérique sont souvent préférées aux méthodes itératives [35, 66] pour beaucoup d'applications.

Implémenter efficacement les méthodes directes reste un travail délicat dans le cas séquentiel comme dans le cas parallèle. Prévoir le remplissage dans les matrices de facteurs, répartir dynamiquement les tâches pour équilibrer la mémoire en fonction des processeurs utilisés, et beaucoup d'autres subtilités algorithmiques tout aussi critiques pour la performance demandent une expérience forte et un investissement important en temps de développement.

La phase de résolution a été souvent négligée dans les travaux précédents sur la factorisation directe creuse [44, 65, 73, 74, 102, 104, 105]. Pourtant, dans beaucoup d'applications, le temps de résolution peut constituer le problème principal. Dans un contexte hors-mémoire où les facteurs sont stockés sur disque dur, c'est encore plus

critique car le temps de la phase de résolution peut être dominé par l'accès au disque local (et non pas par le temps de calcul comme c'est normalement le cas). Il faut noter qu'il y a alors peu d'espoir pour recouvrir, même partiellement, les calculs avec des entrées/sorties (E/S). Ceci explique la forte influence de l'environnement hors-mémoire sur le temps total de résolution.

Notre principal objectif dans cette thèse a été l'étude et le développement d'approches efficaces pour la phase de résolution dans un environnement parallèle à mémoire distribuée [9, 10, 11] et dans un contexte hors-mémoire. Nous proposons dans cette thèse des algorithmes pour améliorer la performance de la résolution directe multifrontale hors mémoire. Notre travail diffère et étend le travail d'autres applications en environnement hors-mémoire (voir [1, 103, 104, 105] et [114]) selon trois axes : d'abord, comme décrit dans [1] nous considérons un contexte parallèle. Deuxièmement, nous nous concentrons sur la performance de la phase de résolution. Troisièmement, nous mettons en oeuvre des algorithmes pour exploiter le caractère creux (" sparsité") des seconds membres (quand *b* dans l'Équation (2) devient une matrice creuse).

Avant l'introduction des notions de base, nous décrivons dans le paragraphe suivant la structure de la thèse. Dans la première partie de ce travail, nous étudions et comparons deux mécanismes d'entrées-sorties pour accéder aux données du disque dur. Une couche logicielle a été écrite en C pour cacher tous les mécanismes d'E/S de bas niveau (gestion du buffeur, pré-chargement des données, synchronisation). Nous avons remarqué que la performance de la phase de résolution est fortement liée à la façon dont on accède aux données sur le disque dur et au nombre et à la régularité de ces accès. Nous avons aussi démontré qu'en parallèle l'ordre avec lequel les tâches sont exécutées influence d'une manière importante la performance de la phase de résolution. Notre travail sur l'ordonnancement des tâches nous a permis de développer une nouvelle approche efficace aussi bien en séquentiel qu'en parallèle. Les expériences sur de nombreuses matrices, dont certaines de plus de 8 millions d'inconnues, montrent le bon comportement des approches proposées en utilisant la version parallèle out-of-core du solveur direct multifrontal MUMPS.

Dans la deuxième partie de la thèse nous nous intéressons à la sparsité (nature creuse) du second membre. Nous étudions différentes techniques qui préservent la sparsité des calculs grâce à l'exploitation de la nature creuse des seconds membres. Des applications à plusieurs seconds membres issues des domaines applicatifs tels que l'électromagnétisme et l'assimilation de données sont utilisées pour illustrer les performances des approches proposées. Par ailleurs, lorsque le nombre de seconds membres est important (dans certains cas plusieurs dizaines de milliers de seconds membres) nous avons étudié, implémenté et décrit des techniques efficaces pour réduire le volume d'Entrées/Sorties. Nous démontrons que l'ordre de traitement des seconds membres peut être utilisé pour réduire aussi bien le nombre d'opérations que la taille totale des données à précharger du disque dur. Nous proposons des permutations de seconds membres permettant d'améliorer l'utilisation de la mémoire et d'optimiser les préchargements du disque dur.

4

#### Notions de base et définitions

#### Graphes

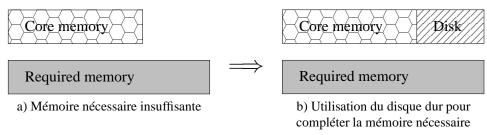

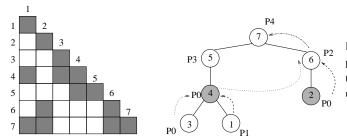

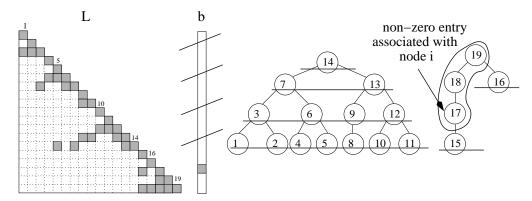

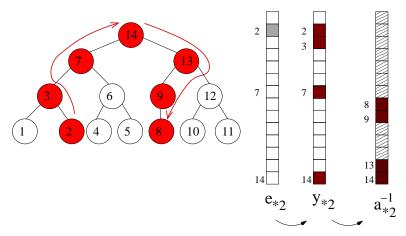

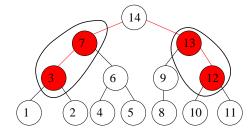

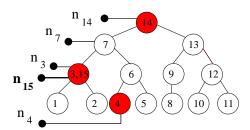

Un graphe est un ensemble fini de noeuds et d'arêtes. Une arête est définie par une paire non-ordonnée de sommets. Un graphe est connexe s'il est possible, à partir de n'importe quel sommet, de rejoindre tout autre sommet en parcourant les arêtes du graphe. En donnant un sens aux arêtes d'un graphe, on obtient un graphe orienté. Un graphe orienté sans cycle est dit acyclique (**dag**). On utilise les dags pour représenter la structure de la matrice (voir Figure 2).

Figure 2: L'entrée non-nulle  $a_{i,j}$  correspond à l'arête orientée  $\langle i,j \rangle$  dans la representation-graphe.

**Propriété 1.** Toute matrice triangulaire (supérieure ou inférieure) peut être représentée par un graphe orienté sans cycle (dag).

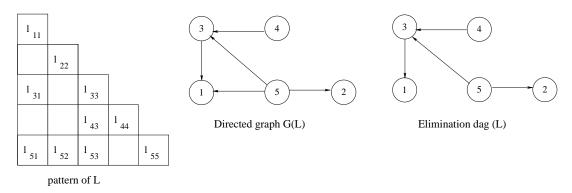

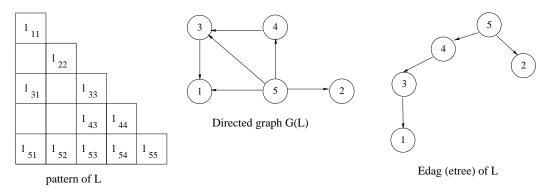

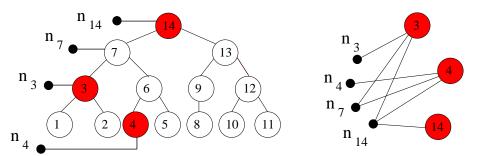

La connectivité entre noeuds d'un graphe orienté peut être représentée de façon efficace grâce au graphe obtenu par réduction transitive. Si la matrice est symétrique, la réduction transitive du graphe associé à la matrice des facteurs (L telle que  $A = LDL^T$ ) est un arbre appelé **l'arbre d'élimination** (voir par exemple Gilbert et Liu [63]). Si la matrice est non-symétrique alors la réduction transitive du graphe associé à chacune des matrices de facteurs (L et U telles que A = LU) est un graphe orienté acyclique particulier appelé **e-dag** par Gilbert et Liu en [63].

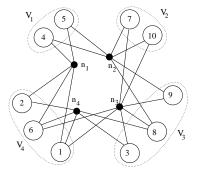

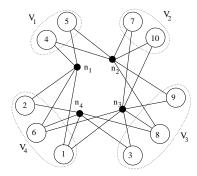

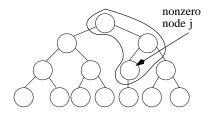

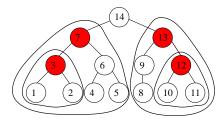

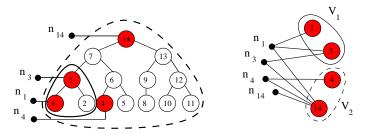

Les hypergraphes généralisent la notion de graphe dans la mesure où les arêtes ne relient plus un ou deux sommets, mais un nombre quelconque de sommets. Un hypergraphe (défini comme un ensemble de noeuds et un ensemble de "nets") a la particularité que chaque net est aussi un ensemble de noeuds. Les noeuds qui ont certaines propriétés communes sont mis ensemble sous forme de nets. Un noeud peut faire partie de plusieurs nets (voir Figure 3, le noeud 4 fait partie des nets 1 et 2).

Figure 3: Exemple d'un hypergraphe contenant 10 noeuds (représentés par des cercles) et 4 nets (représenté par des points). L'hypergraphe est partitioné en 4 parties, representées par des ellipses.

Les hypergraphes sont manipulés dans tous les domaines où l'on utilise la théorie des graphes : résolution de problèmes de satisfaction de contraintes, traitement d'images, optimisation d'architectures réseaux, modélisation, etc.

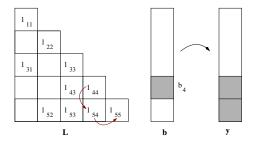

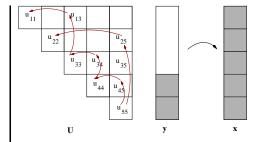

#### • Méthodes directes

Les méthodes directes de résolution de systèmes linéaires creux se déroulent en trois phases : une phase d'analyse, une phase de factorisation, et une phase de résolution. Une fois la factorisation réalisée (A=LU ou  $A=LDL^T$  dans le cas d'un matrice symétrique), le système Ax=b se résout en deux étapes : résolution du système Ly=b (phase dite de 'descente'), puis du système Ux=y (phase de 'remontée').

La dépendance des calculs est représentée par le graphe d'élimination (e-dag) qui est un arbre (l'arbre d'élimination) dans le cas symétrique. Dans notre approche directe multifrontale, nous utilisons la matrice symétrisée  $A+A^T$ , ce qui conduit à la substitution de l'e-dag par un arbre d'élimination. Une particularité sur laquelle repose l'efficacité des méthodes directes est que les colonnes de la matrice qui ont une structure similaire sont groupées dans des supervariables appelées supernodes [51, 94, 98], qui sont ensuite éliminées simultanément. Les méthodes multifrontales diffèrent d'autres méthodes directes (voir [78]), telles que les approches dites left-looking et right-looking, qui sont caractérisées par la façon dont les mises à jour sont faites. Dans une approche rightlooking, les modifications résultant du calcul courant sont immédiatement répercutées sur le reste des données concernées. Dans une approche left-looking, ce n'est qu'au moment où l'on travaille sur une donnée que l'on va prendre en compte toutes les modifications résultant des étapes précédentes. Il faut noter que les mises à jour correspondent à des messages dans le cas d'exécution parallèle sur architectures à mémoire distribuée. Dans ce contexte, la structure des communications dépend fortement de la méthode choisie. Le volume et le nombre de messages dépendent aussi de la répartition ("mapping") des noeuds sur des processeurs.

#### • Environnement et matrices de test

Nos tests ont été effectués sur le calculateur parallèle à mémoire partagée Cray XD1 situé au CERFACS (58 noeuds, 2 processeurs par noeud, 4 Go par noeud, 2 Go par processus MPI, système de fichier reiserfs, et bande passante pour la lecture des données de 16 Mo/s au maximum), en utilisant un seul processus MPI par noeud.

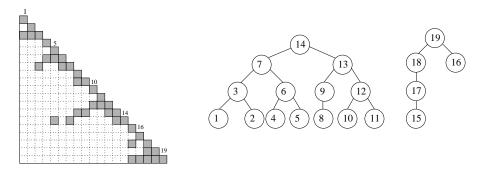

Le tableau 1 décrit nos matrices de tests, ordonnées par rapport à la taille de leurs facteurs. Nous avons aussi fait des expériences sur des matrices de plus petite taille dont la structure particulière est orientée vers des applications de seconds membres creux multiples. Le tableau 2 représente les matrices utilisées pour le calcul du noyau des matrices déficientes. Dans le tableau 3 nous décrivons les matrices correspondant à l'étude de problèmes de moindres carrés. Plus précisément, l'étude de la variance et de la covariance conduit à calculer certains éléments de l'inverse de la matrice des équations normales  $A^TA$ . Certaines de ces matrices sont issues d'une collaboration avec le Centre d'Etude Spatiale du Rayonnement (CESR) de Toulouse et correspondent à des problèmes d'astrophysique. Cette application requiert un fort volume de calcul (14528 secondes) et nous montrerons que l'exploitation de la structure creuse des seconds membres permet de réduire ce temps de calcul de façon tout a fait significative.

| Nom de la matrice | Ordre     | Entrées    | Facteurs | Nb Noeuds    | Description (origine)                      |

|-------------------|-----------|------------|----------|--------------|--------------------------------------------|

|                   |           | (Millions) | (MB)     | dans l'arbre |                                            |

| QIMONDA07*        | 8 613 291 | 66.9       | 2 534    | 3 083 998    | Simulation de circuit (Qimonda AG)         |

| CAS4R-L15         | 2 423 135 | 19.5       | 4 832    | 864 447      | Electromagnétisme 3D (EADS)                |

| CONESHL *         | 1 262 212 | 43.0       | 5 908    | 113 513      | Eléments finis 3D (SAMTECH)                |

| NICE20MC *        | 715 923   | 28.1       | 9 263    | 68 134       | Traitement sismque (BRGM)                  |

| AUDI *            | 943 695   | 39.3       | 12 202   | 113 119      | Modélisation d'un vilebrequin              |

| GRID3.5M          | 3 500 000 | 37.8       | 15 720   | 1 535 044    | Discrétisation 11 points d'un Laplacien 3D |

| GRID5M            | 5 000 000 | 53.8       | 17 798   | 2 203 434    | Discrétisation 11 points d'un Laplacien 3D |

| COR5HZ *          | 2 233 031 | 90.2       | 21 622   | 268 798      | Traitement sismique (BRGM)                 |

| AMANDE            | 6 994 683 | 58.5       | 55 295   | 871 621      | Electromagnétisme 3D (CEA-CESTA)           |

| NICE9HZ *         | 5 140 838 | 215.5      | 64 848   | 603 495      | Traitement sismique (BRGM)                 |

Table 1: Matrices de tests: taille et origine. Les matrices marquée d'une \* sont publiques.

| Nom de la matrice | Ordre  | Nb entrées | Nb Noeuds    | Globale | Racine | Pivots |

|-------------------|--------|------------|--------------|---------|--------|--------|

|                   |        |            | dans l'arbre | Def.    | Def.   | nuls   |

| boxcav_8_5_3      | 619    | 3 471      | 319          | 56      | 7      | 49     |

| boxcav_16x10x3    | 2 675  | 15 953     | 1 311        | 270     | 10     | 260    |

| boxcav_20x13x3    | 4 419  | 26 129     | 2 121        | 456     | 10     | 446    |

| boxcav_30x20x4    | 14 454 | 89 185     | 5 758        | 1 653   | 103    | 1 550  |

| boxcav_40x27x5    | 33 627 | 212 883    | 12 948       | 4 056   | 185    | 3 871  |

Table 2: Matrices de tests pour le calcul de la base du noyau de matrices déficientes: taille et déficience.

| Nom de la matrice | Ordre   | Nb entrées | Nb Noeuds |

|-------------------|---------|------------|-----------|

| a-1_08M           | 8 999   | 497 628    | 1 186     |

| a-1_21M           | 21 532  | 855 866    | 5 207     |

| d-11_25M          | 25 000  | 249 720    | 12 091    |

| a-1_46M           | 46 799  | 1 791 242  | 12 419    |

| a-1_72M           | 72 358  | 3 549 284  | 7 941     |

| a-1_148M          | 148 286 | 7 388 031  | 12 734    |

Table 3: Matrices de tests pour calculer des entrées dans  $(A^TA)^{-1}$  .

#### 1.1 Context of our study

We are interested in solving large sparse linear systems of the form

$$Ax = b ag{3}$$

with direct methods [45, 47, 59] in a parallel limited-memory environment. Here A is a large, square, sparse matrix and b and x are column vectors. We are first interested in case where A is nonsingular matrix. The case of a singular matrix A is discussed in Chapter 8.2.1 where the specific structure of the matrix is exploited for the sparsity of the computations during the solution phase. In the direct solution of this linear system, the matrix A is first factorized into the factors  $LDL^T$  (when A is symmetric) or LU (when A is unsymmetric), where L and U are triangular matrices and D is a diagonal or block diagonal matrix with  $1 \times 1$  and  $2 \times 2$  blocks. These factors are then used to solve the system through the forward and backward substitution steps

$$\begin{bmatrix} LDy = b \text{ and } L^Tx = y \end{bmatrix}$$

or  $\begin{bmatrix} Ly = b \text{ and } Ux = y \end{bmatrix}$ , (4)

depending on whether the matrix is symmetric or not.

In this context, the number of entries in the factors can be an important limitation for using sparse direct solvers. Indeed, the number of entries in the factors (on large 3-dimensional problems) can be much larger (10 to 100 times larger) than the size of the original matrix. This is one reason for users to choose iterative methods (see for example [35, 66]). Time for solution can be another reason. The direct solution of sparse linear systems using Gaussian elimination [59]has a clear advantage over iterative methods in terms of numerical robustness, and it remains the method-of-choice for many applications. However, it is very challenging to implement such methods efficiently on a single processor. This is even more complicated on multiprocessor machines. One of the main reasons is because of fill-in created during the matrix factorization. Moreover, if numerical pivoting is necessary this involves dynamically tracking the fill-ins that are generated in a somewhat unpredictable way. Handling highly irregular data access and computation is further compounded by sophisticated computer architectures with several layers of memory hierarchy. Therefore, unlike many iterative algorithms that users can often implement reasonably well and quickly by themselves, direct solvers require much more expertise and a longer time to develop.

Working out-of-core (using the storage disks to extend the main memory), we can overcome the memory limitation of direct methods [44, 65, 73, 74, 102, 104, 105] and handle large matrices whose factors do not fit within the main memory of the computer. If the memory required for solving a matrix is larger than the available core memory (as shown in Figure 4-a), a natural possibility to overcome this problem is to use the hard disk memory (as shown in Figure 4-b).

In general, direct methods proceed in the following three phases.

- Analysis phase: The matrix is preprocessed to limit the fill-in and to improve its numerical behaviour. The symbolic factorization is performed and the computational dependency graph is computed.

- Factorisation phase: The factors are computed (A = LU or, in the symmetric case  $A = LDL^T$ ).

Figure 4: Memory constraint is solved by extending the main memory with the memory on disk.

• Solution phase: Forward and backward substitutions (respectively Ly = b and Ux = y, in general, or  $DL^Tx = y$  in the symmetric case).

For an unsymmetric matrix, we compute its LU factorization; if the matrix is symmetric, its  $LDL^T$  factorization is computed. Because of numerical stability, pivoting is required in these cases in contrast to symmetric positive definite sparse systems where pivoting can be avoided.

The solution phase involves sparse triangular solutions and has often been neglected in previous work on sparse direct factorization. In many applications, the time for solution is even the main bottleneck for the performance. In an out-of-core context (factors stored on local disk), this is even more critical since the time for the solution phase can be dominated by the time for memory access and not by the time to perform the arithmetic operations. It is interesting to notice that running out-of-core does not significantly affect the time performance of the factorization (see for example [1, 3, 102, 105]). This can be explained by the fact that the time spent doing computation during the factorization phase is generally much larger than the time to perform input/output (I/O) on disks. I/O access can then be 'hidden' by overlapping I/O with computation. On the other hand, the number of operations during the solution phase is of the order of the size of the factors (in the case of a single right-hand-side), which is equal to the volume of I/O. Thus, there is very little scope for overlapping computation with I/O, which explains the strong influence of the out-of-core environment on the time for solution.

Our main focus in this thesis has been the study and design of efficient approaches for the forward and backward substitution phases of a distributed parallel sparse multifrontal solver [9, 10, 11] in an out-of-core context. Our work differs and extends the work of other out-of-core applications (see [1, 103, 104, 105] and [114]) in three aspects. First, as done in [1] we consider a parallel out-of-core context. Second, we focus on the performance of the solution phase. Third, we design algorithms to exploit the sparsity of multiple right-hand side vectors (when b in Equation (4) is a sparse matrix).

Before providing in the general background section some basic ideas and theory, we describe in the following the outline of the thesis.

In the first part of this work, we describe and compare two I/O approaches to access data from the hard disk. An input/output (I/O) software layer written in C has been designed to hide all the low level I/O mechanisms (small buffer management, prefetch and post-store mechanism, synchronisation). Using this software layer we have been able to work at an algorithmic level on the algorithms to design an efficient solution phase in an out-of-core (OOC) context. We have observed that the performance of the solution phase is strongly related to the way data on disk is accessed and to the number and the regularity

of the accesses. We have then shown that in a parallel environment task scheduling can also strongly influence the performance. We have proved that a constrained ordering of the tasks is possible – it does not introduce any deadlock and it improves the performance. Experiments on large real test problems (more than 8 million unknowns) using an out-of-core version of a sparse multifrontal code called MUMPS (MUltifrontal Massively Parallel Solver) have shown the good behaviour of our algorithms.

In the second part of the thesis, we are interested in applications with sparse multiple right-hand sides. Applications in electromagnetism and data assimilation have been used to illustrate our discussion. In such applications we need either to compute the null-space of a highly deficient matrix or to compute entries in the inverse of a matrix associated with the normal equations of linear least-squares problems. We have described, implemented and discussed efficient algorithms to reduce I/O data when solving with OOC execution. We have shown how the sparsity of the right-hand sides can be exploited to limit both the number of operations and the amount of data accessed.

#### 1.2 General background

#### **Graphs**

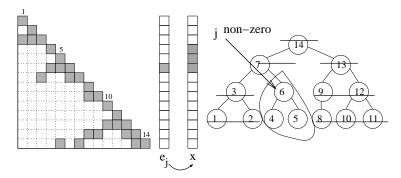

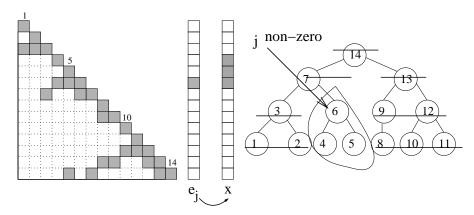

A given square matrix A can be structurally represented by its associated graph G(A). A **graph** G=(V,E) is a set of **nodes** or vertices V connected by a set of **edges** E. Nodes correspond to rows (columns) of the matrix and edges correspond to nonzero entries. Any nonzero position in A ( $a_{ij} \neq 0$ ) corresponds to an edge from node i to node j in the graph G(A) which we write as i (see Figure 5).

Figure 5: The non-zero entry  $a_{i,j}$  corresponds to a directed edge < i, j > in the graph representation.

A one-way edge is called a **directed edge** and has the property:

$$a_{i,j} \neq 0 \iff \exists directed \ edge \ \langle i,j \rangle$$

Note that as we differentiate entries  $a_{i,j}$  and  $a_{j,i}$ , we also distinguish their corresponding directed edges < j, i > and < i, j >. We say that, there is a **path** from node i to node k in the graph, if we can follow directed edges from node i to node k in the graph. In such a case we say that node k is **reachable** from node i.

A graph is said to be **connected**, in the sense of a topological space, if there is a path from any vertex to any other vertex in the graph. Any irreducible matrix A can be represented by a connected graph G(A).

A graph with directed edges and no cycle is called a directed acyclic graph (or dag).

**Property 1.** Any lower triangular matrix or upper triangular matrix can be represented by a directed acyclic graph (dag).

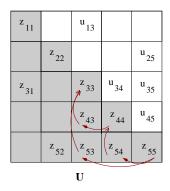

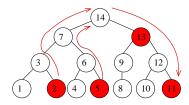

An economical way to represent path information for a directed graph is by its transitive reduction ([4]). An arbitrary graph may have many transitive reductions, but Aho, Garey and Ullman [4] show that a dag has only one. For a given unsymmetric matrix A which can be factored as A = LU, Gilbert and Liu in [63] define an **edag** of L (respectively U) as the unique transitive reduction of G(L) (respectively G(U)).

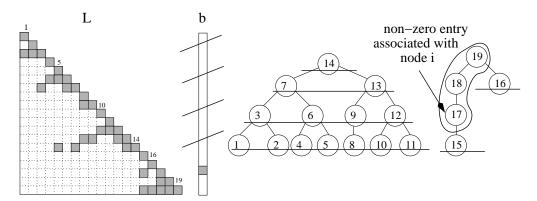

#### **Example 1.** Elimination dag

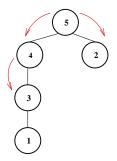

We consider the L pattern of a given matrix, as shown in Figure 6. Its associated directed graph G(L) is acyclic, as stated in property 1. The edges corresponding to redundant paths are removed (edge from node 5 to node 1) and the reduced elimination dag or edag is build.

Figure 6: Example of L pattern with the associated dag and the reduced elimination dag (edag) of L.

**Theorem 1** (Gilbert and Liu [63]). For a symmetric matrix, the edag(L) is a tree, the so called **elimination tree**.

Note that for our example in Figure 6 the edag of L is not a tree, since node 3 has two father nodes -4 and 5. From Theorem 1, the original matrix A was thus not symmetric. Indeed entry  $u_{34}$  of the U factors of the factorization of A must be zero to have  $l_{54}=0$ . On our test example, symmetrizing the matrix such that the U entry  $u_{34}$  becomes non-zero is enough to make our edag a tree ( $u_{34}\neq 0$  implies  $l_{54}\neq 0$ ) as shown in Figure 7.

Figure 7: Modification of the patten of L from Figure 6 such that the associated edag is a tree.

#### **Hypergraphs**

We give a brief definition of hypergraphs, which will be used in Section 10 for the hypergraph based permutation of the right-hand sides. Hypergraph use and construction will be described in Chapter 1.2.

A hypergraph H=(V,N) is defined as a set of vertices V and a set of nets N. Every net is a subset of vertices. The size of a net  $n_i$  is equal to the number of its vertices, i.e.,  $|n_i|$ . The set of nets that contain vertex  $v_j$  is denoted by  $Nets(v_j)$ .

**Example 2. Hypergraph model:** Figure 8 shows a hypergraph with 10 vertices, represented by circles, and 4 nets, represented by points. The net  $n_1$  contains 5 vertices:  $v_4, v_5, v_1, v_2$  and  $v_6$ , thus its size is 5 ( $|n_1| = 5$ ).

Weights and costs can be associated with vertices and nets, respectively. We use w(j) to denote the weight of the vertex  $v_i$ , and c(i) to denote the cost of the net  $n_i$ .

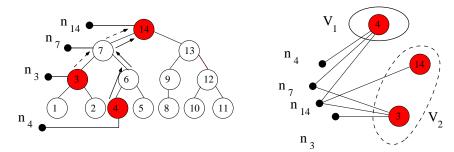

$\Pi = \{V_1, \dots, V_s\}$  is a s-way vertex partition of H = (V, N) if each part is nonempty, the parts are pairwise disjoint, and the union of parts equals V. In  $\Pi$ , a net is said to connect a part if it has at least one vertex in that part. The connectivity set  $\Lambda(i)$  of a net  $n_i$  is the set of parts connected by  $n_i$ . The connectivity  $\lambda(i) = |\Lambda(i)|$  of a net  $n_i$  is the number of parts connected by  $n_i$ . In  $\Pi$ , the weight of a part is the sum of the weights of vertices in that part.

In the hypergraph partitioning problem, the objective is to minimize

$$cutsize(\Pi) = \sum_{n_i \in N} c(i).(\lambda(i) - 1) . \tag{5}$$

**Example 3. Net's cost and partitioning:** In Figure 8, there are four disjoint parts  $\{V_1, \ldots, V_4\}$  and their union by definition gives V. The connectivity of net  $n_1$  is 2 ( $\lambda(1) = 2$ ), because  $n_1$  is connected to parts  $V_1$  and  $V_4$ .

Let suppose that the cost of each net in Figure 8 is 1 (c(i) = 1). Thus:

$$cutsize(\Pi) = \sum_{i=1}^{4} c(i).(\lambda(i) - 1) =$$

$$= 1.(2 - 1) + 1.(3 - 1) + 1.(3 - 1) + 1.(2 - 1) = 6$$

Figure 8: Example of hypergraph containing 10 vertices (represented by circles) and 4 nets (represented by points). The hypergraph is partitioned into 4 parts, represented by ellipses.

Minimizing the cutsize function is widely used in the VLSI (Very-Large-Scale Integration) community [89] and in the scientific computing community [17, 27, 115, 116], and it is referred to as the connectivity -1 cutsize metric. The partitioning objective is to satisfy a balancing constraint on part weights:

$$\frac{W_{max} - W_{avg}}{W_{avg}} \le \varepsilon . agen{6}$$

Here  $W_{max}$  is the largest part weight,  $W_{avg}$  is the average part weight, and  $\varepsilon$  is an allowable imbalance ratio. The problem is NP-hard [89].

#### **Direct methods**

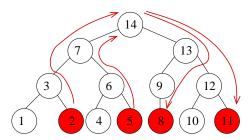

As we focus on the multifrontal method, we will comment on some of its main properties with respect to other methods. For an overview of the multifrontal method (although we describe in the next chapter), we refer the reader to [47, 51, 78, 93]; for the discussion of other direct approaches, we refer the reader to [39, 77, 81]. The multifrontal method was initially developed for indefinite sparse symmetric linear systems [51] and was then extended to unsymmetric matrices [52]. It belongs to the class of approaches which separates the factorization into two phases. The symbolic factorization phase is not concerned with numerical values. It looks for a permutation of the matrix that will reduce the number of operations and memory requirements in the subsequent phase, and then computes a dependency graph associated with the factorization. Finally, in an implementation for parallel computers, this phase partially maps the graph onto the target multiprocessor computer. The numerical factorization phase computes the matrix factors that will then be used during the solution phase to compute a solution. The experimental part and the development performed in this thesis are based on the MUMPS, a MUltifrontal Massively Parallel Solver [8, 10].

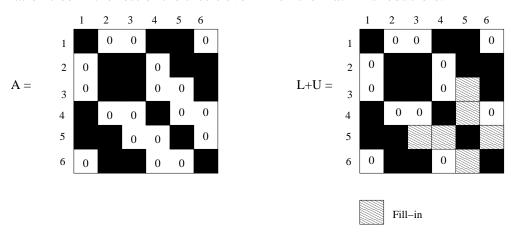

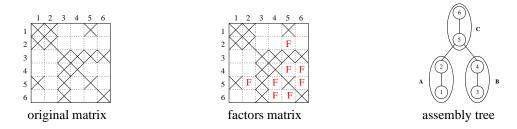

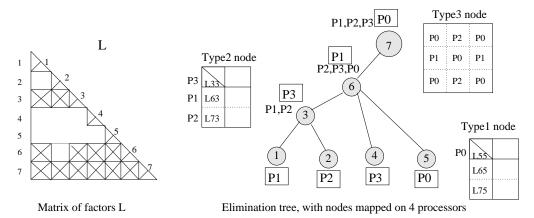

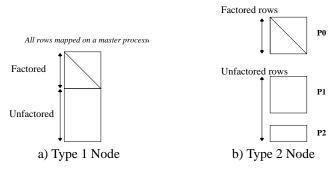

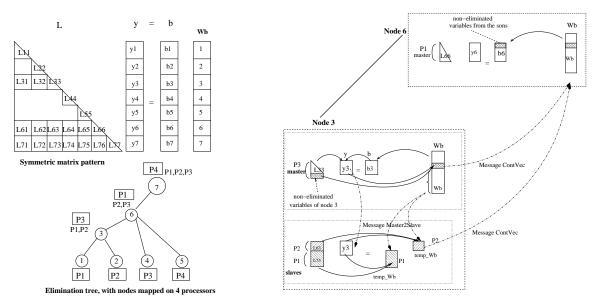

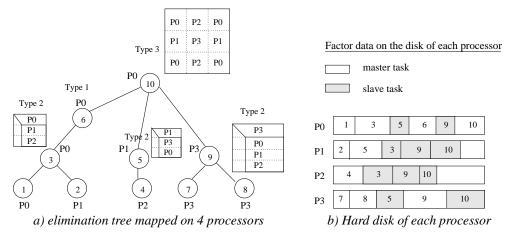

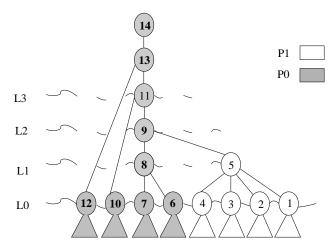

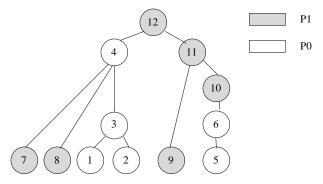

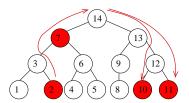

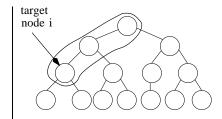

Note that on unsymmetric matrices, the computational dependency graph is the so-called elimination dag (or edag). This edag is used in the unsymmetric multifrontal approaches UMFPACK [34] and WSMP [75, 76]. In our multifrontal approach, the pattern of the symmetrized matrix  $A + A^T$  will be used so that the edag is in fact an elimination tree. The elimination tree represents the task dependency of the computations, it gives a partial order in which the columns can be eliminated. For example the elimination tree on Figure 9, associated with factors on Figure 10 expresses dependency: column 5 must

wait for the elimination of columns 3 and 4. Node 5 of the elimination tree is said to be the father of nodes 3 and 4. The elimination tree also provides parallelism; column 3 and 4 can be processed in parallel. Note that in a general case the elimination tree is a forest (if the matrix is reducible). For the sake of clarity we will continue to use the term elimination tree in the rest of the thesis even when the matrix is reducible.

Figure 9: Pattern of a structurally symmetric matrix and fill-in in its factors.

An important issue for efficiency is that columns with similar sparsity pattern are grouped into large supernodes [51, 94, 98]. The resulting tree will be referred to as **the assembly tree**. In Figure 9, columns 2 and 3 of the L factors have the same structure and are processed as a unique node in the assembly tree compatible with the elimination tree, shown in Figure 10.

Figure 10: Elimination tree and assembly tree associated with the matrix of Figure 9.

In practice, supernodes are naturally used in direct solvers whatever the method is (left-looking, right-looking or multifrontal), as for example in SuperLU [38, 40], Pastix [80], UMFPACK [34], Taucs [113], Oblio [42, 43], Pardiso [106, 107], Pspases [77], Hsl library [82], Spooles [15], WSMP [75, 76], MUMPS [9, 10, 11], and others. Some of these solvers have been designed for distributed memory computers (see for example Pastix, SuperLU\_Dist, Pspases and MUMPs. Because of the difficulty of handling dynamic data structures efficiently, most distributed memory approaches do not perform numerical pivoting during the factorization phase. Instead, they are based on a static mapping of the tasks and data and do not allow task migration during numerical factorization. In this context one unique and original feature of MUMPS solver is that it enables standard numerical pivoting. Dynamic task creation, scheduling and data mapping are used to handle numerical issues and to provide a very adaptive approach. Numerical pivoting can clearly be avoided for symmetric positive definite matrices. For unsymmetric matrices, Duff and Koster [48, 49] have designed algorithms to permute large entries onto the diagonal and have shown that this can significantly

reduce numerical pivoting. Demmel and Li [90] have shown that, if one preprocesses the matrix using the code of Duff and Koster, static pivoting (with possibly modified diagonal values) followed by iterative refinement can normally provide reasonably accurate solutions. They have observed that this preprocessing, in combination with an appropriate scaling of the input matrix, is a key issue for the numerical stability of their approach.

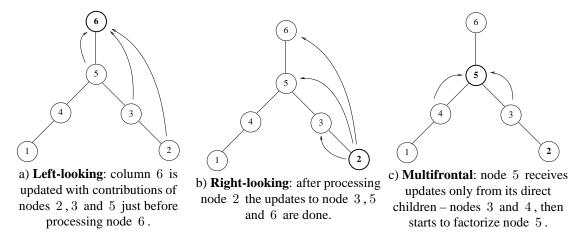

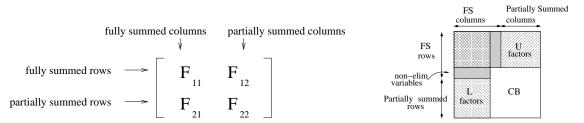

One main difference between multifrontal and other direct approaches (see [78]) such as left-looking and right-looking, is in the way of doing the updates for each node in the elimination tree. In the left-looking approach the updates to a node are done just before the node is factorized. This is also known as a fan-in method [14, 79]. In the right-looking approach, the updates to each node are sent just after the factorization. This approach is also known as a fan-out method. From this point of view, the multifrontal method [13, 52, 93] can be seen as a combination of left-looking and right looking approaches, where all updates are sent after the factorization of the current node but only to its father. To do the update the father must be capable of storing all contributions from all its descendants. One can show that a full square matrix (so called frontal matrix) of order the number of nonzero entries in the column of L is enough to store all contributions. More that one branch of the tree and multiple associated frontal matrices can be processed simultaneously so that the method has been named the multifrontal approach.

Figure 11: Updates in left-looking, right-looking and multifrontal approaches. The bold nodes represent the current node and the arrows refer to updates.

Note that each update corresponds to a communication message in a parallel distributed memory environment so that each approach will have a different communication pattern. The volume and number of messages will then strongly depend on the mapping of the nodes of the elimination tree onto the processors (see [78]).

#### **Least-square solution**

Linear least-squares problems arise in many important fields of science and engineering, such as econometry, geodesy, statistics, structural analysis, fluid dynamics, etc. The linear least-squares problem [21, 61, 95, 96, 97, 99] is a computational problem that originally arose from the needs to fit a linear mathematical model to given observations. To reduce the influence of errors in the observations a great number of measurements are taken. Thus the resulting problem to solve is an overdetermined linear

system of equations. In matrix terms, given a vector  $\mathbf{b} \in \mathcal{R}^m$  and a matrix  $\mathbf{A} \in \mathcal{R}^{m \times n}$ , m > n, we want to find a vector  $\mathbf{x} \in \mathcal{R}^n$ , such that Ax is the 'best' approximation to b. There are many possibilities of defining this 'best' approximation. Often for statistical reasons, but also to provide a simple computational problem x is chosen to minimize the Euclidean vector norm:

$$min_x||Ax - b||_2$$

, where  $A \in \mathcal{R}^{m \times n}$ ,  $b \in \mathcal{R}^m$  (7)

This is known as the linear least-squares problem. Vector x is the linear least-squares solution of the system Ax = b. Let  $\mathbf{r}$  be the residual vector, r = b - Ax. Thus to solve the linear least-squares problem we must minimize  $||r||_2^2$  which is the sum of the squared residuals:  $||r||_2^2 = \sum_{i=1}^m r_i^2$ . If the rank of matrix A is smaller than n (rank(A) < n), the solution x of equation (7) is not unique. However, among all least-squares solutions there is an unique solution which minimizes  $||x||_2$  (see Chapters 1 and 2 of Björck, Numerical Methods for Least-Square Problems [21]).

In linear statistical models the vector b of observations is related to the unknown vector x by the linear relation:

$$Ax = b + \epsilon \tag{8}$$

where  $\epsilon$  is a vector of random errors. Let rank(A)=n and  $\epsilon$  has zero mean,  $\mathcal{E}(\epsilon)=0$ . Let also the variance-covariance matrix be  $\nu(\epsilon)=\sigma^2 I$ . Then by the Gauss-Markov theorem, the least-squares estimate  $\hat{\mathbf{x}}$  is the linear unbiased estimator of x (an estimator for which there is no difference between an estimator's expected value and the true value of the parameter,  $\hat{x}=x$ ) with minimum variance equal to

$$V_x = \sigma^2 C_x$$

,  $C_x = (A^T A)^{-1} = R^{-1} R^{-T}$  (9)

where R is the Cholesky factor of the so called **normal equations**  $A^TA$ . An unbiased estimate of  $\sigma^2$  is given by :

$$s^2 = ||\hat{r}||_2^2 / (m - n)$$

,  $\hat{r} = b - A\hat{x}$ .

In order to assess the accuracy of the computed estimate of x it is often required to compute the minimum variance matrix  $V_x$  or part of it. In particular, the variance of the component  $\hat{x}_i$  is given by the diagonal entries  $v_{ii}$  in  $V_x$  [101].

1.3 Test environment

#### 1.3 Test environment

Except where stated otherwise, all our runs have been performed on the multiprocessor Cray XD1 located at CERFACS (58 nodes with 2 processors per node; and 4 GB per node, 2 GB per MPI process). Each node is equipped with an IDE disk managed by the reiserfs file system of maximum bandwidth for a read operation close to 16 MB/sec with one MPI process per node.

#### Performance of the solution phase

Our set of test matrices used for the experiments in the first part of the thesis – solution phase performance is described in Table 4, sorted by factor size. The size of the factors is obtained using a Metis reordering [83] of the original matrix. All test matrices are real symmetric except CAS4R-L15 and AMANDE which are complex symmetric.

| Matrix name | Order     | Entries    | Factors | Nb Nodes    | Description (origin)                         |

|-------------|-----------|------------|---------|-------------|----------------------------------------------|

|             |           | (Millions) | (MB)    | in the tree |                                              |

| QIMONDA07*  | 8 613 291 | 66.9       | 2 534   | 3 083 998   | Circuit simulation (Qimonda AG company)      |

| CAS4R-L15   | 2 423 135 | 19.5       | 4 832   | 864 447     | 3D Electromagnetism (EADS)                   |

| CONESHL *   | 1 262 212 | 43.0       | 5 908   | 113 513     | 3D finite element from SAMTECH               |

| NICE20MC *  | 715 923   | 28.1       | 9 263   | 68 134      | Seismic processing (BRGM Lab.)               |

| AUDI *      | 943 695   | 39.3       | 12 202  | 113 119     | Automotive crankshaft model                  |

| GRID3.5M    | 3 500 000 | 37.8       | 15 720  | 1 535 044   | 3D 11pt-discretization of Laplacian operator |

| GRID5M      | 5 000 000 | 53.8       | 17 798  | 2 203 434   | 3D 11pt-discretization of Laplacian operator |

| COR5HZ*     | 2 233 031 | 90.2       | 21 622  | 268 798     | Seismic processing (BRGM Lab.)               |

| AMANDE      | 6 994 683 | 58.5       | 55 295  | 871 621     | 3D Electromagnetism (CEA-CESTA)              |

| NICE9HZ*    | 5 140 838 | 215.5      | 64 848  | 603 495     | Seismic processing (BRGM Lab.)               |

Table 4: Test matrices: size and origin. Matrices marked by \* are publicly available.

Matrix AUDI from the PARASOL Collection <sup>1</sup> or the matrices from our applications partners that are publicly available can be found on the gridtlse.org web site. COR5HZ matrix corresponds to a dynamic analysis of the Cornioglio (Italy) earthquake (1994) with maximum signal frequency of 5 Hz. NICE20MC and NICE9HZ correspond to dynamic analysis of the Nice earthquake (2001) with maximum signal frequency of 1.5 Hz and 9 Hz respectively. AMANDE and CAS4R-L15 are problems from electromagnetism. CONESHL corresponds to 3D computations from structural engineering and QIMONDA07 to circuit simulation.

We show in Table 4 the order and the number of entries for each matrix which give us an estimation about the size and the sparsity of the matrix. The factor size denotes the amount of LU factors stored on disk during the factorization phase and read during the solution phase. The time performance of the solution phase in an out-of-core environment is strongly related to this amount of data. We show also the number of nodes in the elimination tree which is very useful to estimate the impact of the scheduling strategy. The more nodes that are in the tree, the more important will be the influence of the scheduling.

We note the difficulty in getting very large problems from industry. It is also necessary that the integer description (symbolic representation of the matrix) will fit on a single processor in order for us to complete the analysis and construct the data structures for subsequent numerical factorization and solution.

<sup>&</sup>lt;sup>1</sup>www.parallab.uib.no/projects/parasol/data

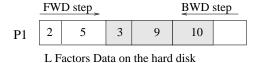

During factorization **all** factors are written to files (local to each MPI process) on disks. In our experimental context (one MPI process per node) all I/O files of each MPI process are thus associated with local disks. Our approach will however naturally work when disks are shared by more than one MPI process but with a reduction in the average I/O bandwidth. Furthermore, factors are not kept in memory at the beginning of the solution phase *and* between the forward and backward steps. So we have no intended reuse of data, which will help to better understand the behaviour of each step.

With these assumptions, we will thus have to load all of the factors during the solve phase. Note that QIMONDA07 is a large and very sparse matrix with more than 3 million nodes in the assembly tree. Indeed, it is the matrix with the largest number of nodes in our set. I/O access might occur for each node of the elimination tree and thus it is an interesting matrix to illustrate the behaviour of our algorithms. We thus use this example extensively in our detailed analysis but show relevant results on all our test problems later in the thesis.

#### Exploit the sparsity of the right-hand side vectors

In the second part of the thesis we are interested in applications with sparse multiple right-hand sides. An application in electromagnetism leads to computing the null-space basis of a matrix with a large deficiency. Another application in astrophysics requires the computation of the diagonal entries of the inverse of a matrix.

For null-space basis computations our test matrices (given in Table 5) come from 3D applications in electromagnetism when computing resonance modes in box cavities discretization.

| Matrix name    | Order  | Nb entries | Nb Nodes    | Global | Root | Null   |

|----------------|--------|------------|-------------|--------|------|--------|

|                |        |            | in the tree | Def.   | Def. | Pivots |

| boxcav_8_5_3   | 619    | 3 471      | 319         | 56     | 7    | 49     |

| boxcav_16x10x3 | 2 675  | 15 953     | 1 311       | 270    | 10   | 260    |

| boxcav_20x13x3 | 4 419  | 26 129     | 2 121       | 456    | 10   | 446    |

| boxcav_30x20x4 | 14 454 | 89 185     | 5 758       | 1 653  | 103  | 1 550  |

| boxcav_40x27x5 | 33 627 | 212 883    | 12 948      | 4 056  | 185  | 3 871  |

Table 5: Test matrices for null-space basis computations: size and deficiency.

The matrices are not as large as the matrices for analysing the performance of the parallel out-of-core solution. However the main issue with these matrices is the relatively large deficiency (rank of the null-space basis of the matrix) with respect to the order of the matrix (compare column 5 (Global Def) with column 2 (Order)). As shown in Section 8.2.2 of Part2, computing the null-space basis will require a large number of backward solutions with highly sparse right-hand-side since as many solution steps as the size of the deficiency must be performed. In columns 6 and 7 we indicate how the deficiency was detected during the factorization. As explained in Section 8.2.2 one part of the deficiency can be detected on the fly of a "quasi-normal" factorization phase (column Null Pivots) with modified pivoting strategies; another part can be detected while processing the root of the elimination tree with a rank revealing algorithm (column Root Def.). We will show in Section 8.2.2 that the locality of the deficient rows in the elimination tree influences the performance of our algorithms.

To illustrate the behaviour of our algorithms for computing entries in  $A^{-1}$ , our set of matrices is based on applications in astrophysics and results from a collaboration

1.3 Test environment

with SPI/INTEGRAL team at CESR (Centre d'Etude Spatiale des Rayonnements in Toulouse). In the context of the INTEGRAL (INTErnational Gamma-Ray Astrophysics Laboratory [119]) mission of ESA (European Space Agency) a spatial observatory with high resolution (both in terms of angle and energy) hardware technology has been launched on October 2002. SPI [118] is one of the main instrument onboard INTEGRAL, a spectrometer with high energy resolution and indirect imaging capabilities. To obtain a complete sky survey with SPI/INTEGRAL, the processing of a very large amount of data acquired by the INTEGRAL observatory is needed [23]. For example, to estimate the total point-source emission contributions, a linear least-squares problem of about 1 million equations and 100000 unknowns must be solved. As already explained in this chapter (see previous Section 1.2 for least-square solution), one might want in this case to compute part of the inverse of the variance (see Equation 9). To do so one must then compute part of the inverse of the normal equation matrix  $A^TA$  where A is the matrix associated with the original linear least-squares problem. A few test matrices associated with the normal equations built from our application are shown in Table 6.

| Matrix name | Order   | Nb entries | Nb Nodes |

|-------------|---------|------------|----------|

| a-1_08M     | 8 999   | 497 628    | 1 186    |

| a-1_21M     | 21 532  | 855 866    | 5 207    |

| d-11_25M    | 25 000  | 249 720    | 12 091   |

| a-1_46M     | 46 799  | 1 791 242  | 12 419   |

| a-1_72M     | 72 358  | 3 549 284  | 7 941    |

| a-1_148M    | 148 286 | 7 388 031  | 12 734   |

Table 6: Test matrices to compute entries in  $(A^TA)^{-1}$ .

This application is computationally intensive because, in the context of the sky survey, all diagonal entries of the inverse of the normal equation matrix are required. For example, on the largest matrix in the test set, solving the complete problem requires about 7 seconds for the analysis phase, 1.4 seconds to factor the matrix and 14 528 seconds to compute all diagonal entries of the inverse of the matrix (results obtained at CESR with an incore factorization based on MUMPS solver on an Opteron 2.8 GHz with 16 Gbytes of main memory). We will show in Part 2 of the thesis how we can exploit the sparsity better in order to reduce the solution time and limit the memory used.

## Part I

# **Analysis of the Solution Phase of a Parallel Multifrontal Approach**

## Résumé de la Partie I : Analyse de la phase de résolution parallèle dans une approche multifrontale

Le système linéaire de grande taille Ax=b est résolu en utilisant une méthode directe de factorisation basée sur une approche multifrontale dans un environnement parallèle out-of-core (hors-mémoire). Les méthodes directes sont souvent composées de trois phases : une phase de prétraitement et d'analyse, une phase de factorisation (A=LU ou A=LDL si A est symmétrique) et une phase de résolution. La phase de résolution se décompose en une étape de descente Ly=b suivie d'une étape de remontée Ux=y dans le cas non-symétrique. Dans ce travail nous nous intéressons à la phase de résolution et aux possibilités de l'optimiser, surtout dans un contexte hors-mémoire où le temps de résolution est dominé par le temps d'accès et de lecture du disque dur.

Avant d'étudier et présenter des performances dans un contexte hors-mémoire, nous allons présenter certaines propriétés générales de la phase de résolution.

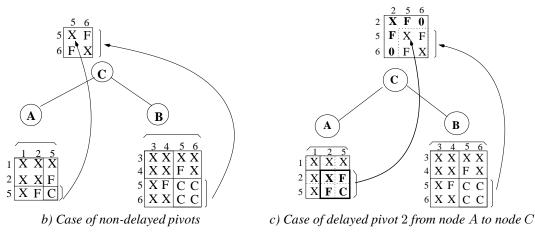

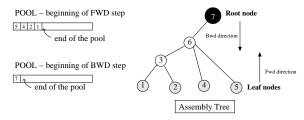

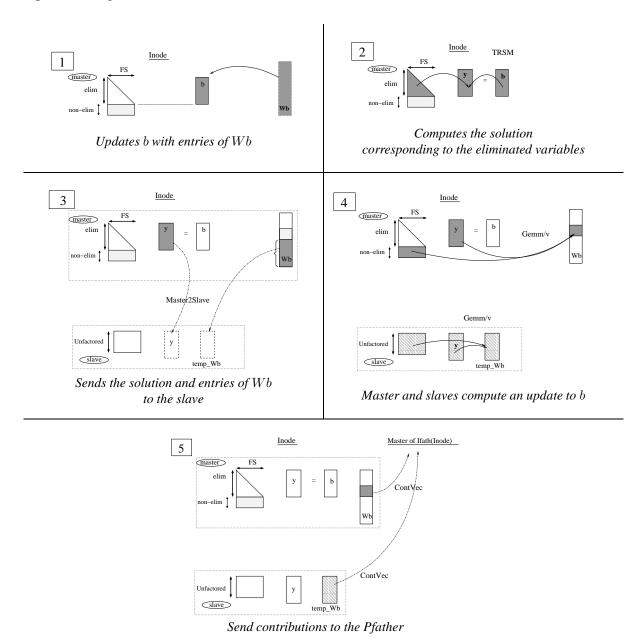

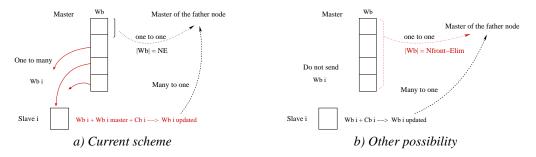

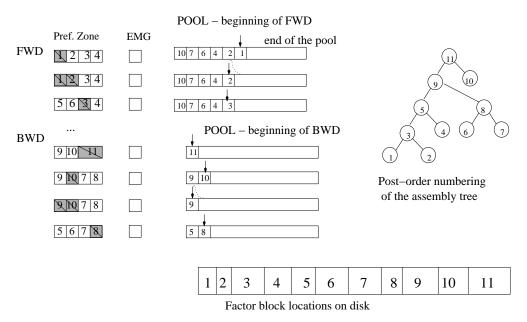

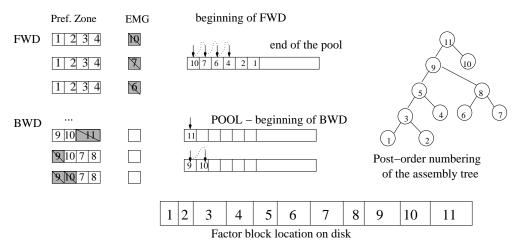

### Dans un environnement en mémoire (in-core)

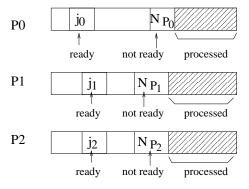

Les méthodes directes utilisent l'arbre d'élimination pour représenter la dépendance des calculs. Pour gérer l'ordre dans lequel les tâches de calcul sont effectuées nous utilisons une structure de données appelé POOL. Elle représente toutes les tâches prêtes à être exécutées à tout moment de la résolution. Au début de l'étape de descente (forward substitution, résolution de Ly=b) toutes les tâches associées aux feuilles de l'arbre de l'élimination sont stockées dans le POOL en respectant un post-ordre de parcours de l'arbre. Au début de l'étape de remontée (backward substitution, résolution de Ux=b dans le cas d'une matrice symétrique), la seule tâche prête à être exécutée correspond au noeud associé à la racine de l'arbre. Dans les deux étapes (la descente et la remontée) les tâches mises dans le POOL sont extraites en utilisant l'ordonnancement LIFO, ce qui dans le cas séquentiel correspond à une traversée optimale de l'arbre - post-ordre des tâches. Dans le cas parallèle, l'extraction des noeuds du POOL est influencée par le mapping des noeuds sur les processeurs. Dans ce cas, le post-ordre ne peut plus être respecté et on parle d'ordonnancement topologique des tâches (chaque noeud père ne peut être activé qu'après avoir traité tous ses enfants).

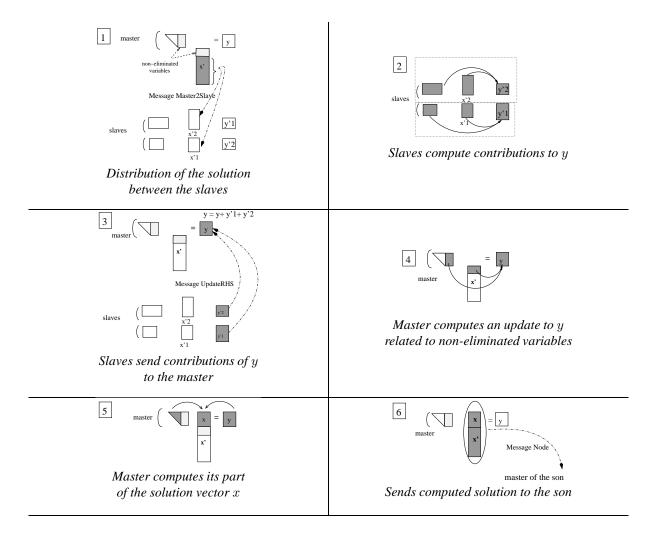

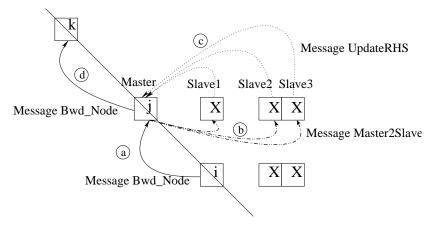

Implémenter efficacement les méthodes directes multifrontales dans un environnement parallèle reste un travail difficile au niveau des communications entre les processeurs et la synchronisation des tâches à exécuter. Pour la première fois, une description détaillée des algorithmes parallèles utilisés dans la phase de résolution de la méthode multifrontale sera faite dans cette thèse. Des particularités importantes en parallèle seront illustrées (Propriétés 3.1, 3.2, 3.3 et 3.4) tout en prouvant leur efficacité pour la parallélisation massive de la méthode.

### Dans un environnement hors-mémoire (OOC)

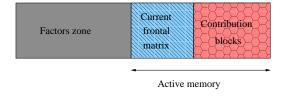

Il faut insister sur le fait que le temps de toute la phase de résolution est dominé par le temps d'accès et de préchargement du disque dur. Il devient alors primondial d'optimiser le processus de préchargement des données. Dans ce contexte, l'objectif de notre travail a été de diminuer le nombre d'accès au disque dur tout en rendant la lecture des données

la plus 'régulière' si possible. Une implémentation simple et efficace, dans le cas où la mémoire n'est pas critique, est d'utiliser le cache du système pour le préchargement des données. Dans le cas où la mémoire pour résoudre le système devient critique, les mécanismes du cache ne sont plus efficaces, comme indiqué dans le Tableau 1.7 - en diminuant le nombre de processeurs utilisés on observe un réduction du débit d'accès aux facteurs sur le disque (du 92.6 MB/s avec 8 processeurs à 9.2 MB/s en utilisant un seul processeur.)

|         | Taille des facteurs | Solution Parallèle |       |                            |  |  |

|---------|---------------------|--------------------|-------|----------------------------|--|--|

| Nprocs  | (per proc)          | Fwd                | Bwd   | Débit d'accès aux facteurs |  |  |

|         | MB                  | (sec)              | (sec) | (MB/s)                     |  |  |

| In core |                     |                    |       |                            |  |  |

| 8       | 317.5               | 0.9                | 0.9   | _                          |  |  |

| OOC (O  | ut-Of-Core)         |                    |       |                            |  |  |

| 8       | 317.5               | 3.6                | 4.5   | 92.6                       |  |  |

| 4       | 635.0               | 45.9               | 15.1  | 83.3                       |  |  |

| 2       | 1 270.1             | 129.4              | 93.1  | 22.8                       |  |  |

| 1       | 2 534.3             | 269.4              | 282.9 | 9.2                        |  |  |

Table 1.7: Influence de la mémoire utilisée par noeud sur le Cray XD1 pour la performance en parallèle de la phase de résolution sur la matrice QIMONDA07. Cette approche OOC est basée sur la simple utilisation de mécanisme cache (SYSTEM\_BASED approche).

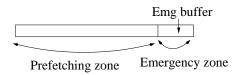

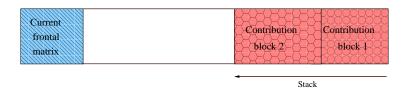

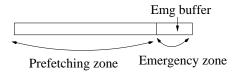

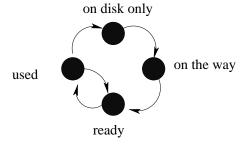

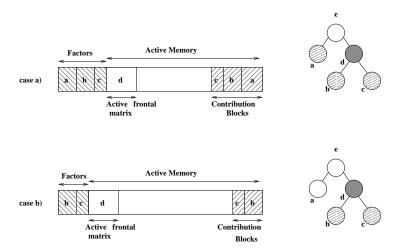

On propose donc une autre méthode pour lire les données sur le disque (méthode appelée Direct I/O), plus contraignante pour le développeur, mais beaucoup plus efficace du point de vue du temps d'accès et de la gestion de la mémoire. Des buffeurs internes au programme sont destinés à précharger les données du disque. Le grand avantage de cette approche est que leur taille est indépendante de la taille du problème et qu'elle peut être fixée par l'utilisateur. Le buffeur est divisé en deux parties - une partie pour un préchargement d'un grand nombre de données en utilisant des méthodes sophistiquées d'optimisation; et une partie de lecture sur un seul bloc de données en urgence (lecture en mode bloquant) (voir Figure 1.12).

Figure 1.12: Buffeur dont la taille est prédéfinie par l'utilisateur.

Une comparaison entre les deux méthodes en terme de temps de calculs et de nombre d'accès au disque dur est donnée dans le Tableau 1.8.

| Méthode                  | Fwd   | vd Bwd Nb_Req Fwd Nb_Req |          | Nb_Req Fwd |          | eq Bwd   |  |

|--------------------------|-------|--------------------------|----------|------------|----------|----------|--|

|                          | (sec) | (sec)                    | Prefetch | Emg zone   | Prefetch | Emg zone |  |

| DIRECT_IO (Emg+Prefetch) | 171.5 | 176.8                    | 541      | 0          | 496      | 0        |  |

| SYSTEM_BASED             | 269.4 | 282.9                    | _        | _          | _        | _        |  |

Table 1.8: Influence du nombre des buffeurs sur la réolution sequentiel de QIMONDA07. Fwd=forward phase. Bwd=backward phase. Emg zone: 1 MB; Prefetch buffer: 10 MB.

Après une comparaison exhaustive, nous avons démontré l'efficacité de la méthode DIRECT\_IO sur l'ensemble de nos matrices.

### **Ordonnancement (Scheduling)**

Comme nous l'avons déjà dit précédemment, l'accès régulier au disque est extrêmement important pour le temps de calcul de la phase de résolution. Par accès régulier, on sous-entend le préchargement des données de grande taille d'une manière contiguë sur le disque dur. Dans ce contexte, l'ordonnancement efficace des différentes tâches prêtes à être exécutées devient très important. Dans le cas séquentiel, l'ordre optimal pour parcourir l'arbre d'élimination et traiter les tâches correspond à un post-ordre. Dans le cas parallèle, les choses se compliquent en introduisant le mapping des tâches sur les différents processeurs, et donc le post-ordre ne peut plus être respecté. Les stratégies connues jusqu'à présent, LIFO et FIFO, ne sont pas adaptées non plus à la résolution parallèle du système à cause du grand nombre d'appels irréguliers au préchargement des données du disque. (Plus de 400 000 appels dans l'étape de backward substitution avec 3 et 4 processeurs).

|           | Nb    | Fwd   | Bwd   | Nb Max requêtes par step |          |          |                   |  |

|-----------|-------|-------|-------|--------------------------|----------|----------|-------------------|--|

| Stratégie | of    |       |       | Fw                       | Fwd (*)  |          | /d <sup>(*)</sup> |  |

|           | Procs | (sec) | (sec) | Prefetch                 | Emg zone | Prefetch | Emg zone          |  |

| LIFO      | 1     | 171.5 | 176.8 | 541                      | 0        | 496      | 0                 |  |

| LIFO      | 3     | 64.9  | 262.1 | 190                      | 3        | 169      | 422 497           |  |

| LIFO      | 6     | 38.0  | 186.7 | 102                      | 6        | 86       | 422 498           |  |

| LIFO      | 8     | 24.9  | 137.6 | 70                       | 0        | 64       | 321 871           |  |

| LIFO      | 16    | 13.2  | 94.4  | 39                       | 2        | 32       | 214 245           |  |

| LIFO      | 24    | 10.9  | 48.5  | 42                       | 5        | 38       | 119 792           |  |

| LIFO      | 32    | 9.1   | 53.1  | 25                       | 1        | 30       | 116 209           |  |

Table 1.9: Influence de l'ordonnancement LIFO sur la matrice QIMONDA07. Emg=emergency buffer:1 MB; Prefetch buffer:10MB par processeur; (\*): Max par processeur.

Nous proposons une nouvelle stratégie d'ordonnancement des tâches, NNS, basée sur le stockage des tâches sur le disque dur. Elle prend en compte la répartition des tâches sur les disques locaux de chaque processeur. En ordonnançant les tâches maîtres afin de respecter la séquence de chaque processeur, on arrive à reproduire la séquence d'écriture des facteurs lors de la phase de factorisation. Ainsi on obtient un accès beaucoup plus régulièr en lecture aux données du disque dur et un temps de la résolution fortement réduit.

| Stratégie | Nb de | T_min | Bwd   | Nb_Req <sup>(*)</sup> |     |

|-----------|-------|-------|-------|-----------------------|-----|

|           | Procs |       |       | Bwo                   | i   |

|           |       | (sec) | (sec) | Prefetch              | Emg |

| NNS       | 1     | 158.4 | 177.2 | 496                   | 0   |

| NNS       | 3     | 57.9  | 65.5  | 174                   | 1   |

| NNS       | 6     | 31.5  | 37.9  | 93                    | 0   |

| NNS       | 8     | 21.8  | 45.2  | 57                    | 0   |

| NNS       | 16    | 11.9  | 13.8  | 36                    | 0   |

| NNS       | 24    | 9.0   | 13.2  | 38                    | 0   |

| NNS       | 32    | 8.2   | 10.7  | 34                    | 0   |

Table 1.10: Influence de l'ordonnancement NNS sur la matrice QIMONDA07. Emg=buffer d'urgence:1 Mo; Prefetch buffer:10Mo par processeur; (\*): Max per processor.

Les tableaux 1.9 et 1.10 montrent les performances des deux ordonnancements LIFO et NNS. Dans les deux cas, on compare le temps obtenu (Fwd et Bwd) avec le temps minimum pour charger les facteurs du disque dur ( $T_min$ ). On montre aussi le nombre des préchargements du disque. Comme le montre le Tableau 1.10 sur la matrice

QIMONDA07 mais aussi sur l'ensemble de nos matrices, l'ordonnancement NNS s'est montré plus efficace à réduire le nombre de préchargements du disque et le temps global de la phase de résolution.

### Chapter 2

### Introduction

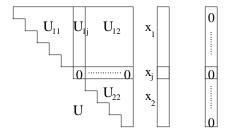

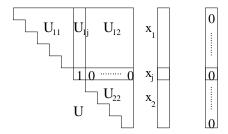

We are interested in solving large sparse linear systems Ax = b with direct methods [45, 47, 78], in a parallel limited-memory environment. We suppose that the original matrix A is first factorized into the factors  $LDL^T$  (when A is symmetric) or LU (when A is unsymmetric), where L and U are triangular matrices and D is diagonal (or block diagonal with blocks of order 1 or 2 in the case of numerical pivoting for indefinite systems). Note that in our factorization expressions, we have omitted, for the sake of clarity, the permutations performed to preserve sparsity and to implement numerical pivoting. These factors are then used to solve the system through the forward and backward substitution steps

$$\begin{bmatrix} LDy = b \text{ and } L^Tx = y \end{bmatrix}$$

or  $\begin{bmatrix} Ly = b \text{ and } Ux = y \end{bmatrix}$ , (2.1)

depending on whether the matrix is symmetric or not. In this work, we are concerned with the case when the matrix A is large and sparse [47, 59]. The main limitation in the use of sparse direct methods comes from the need to store the factors that often have many (10 to 100 times) more entries than the original matrix.