Design of Asset tracking device with GPRS Interface

by

**Robin Maharaj**

# Thesis submitted in fulfilment of the requirements for the degree

Master of Engineering: Electrical Engineering

in the Faculty of Engineering

at the Cape Peninsula University of Technology

Supervisor: Dr A.K. Raji Co-Supervisor: Mr Q.J.Bart

Bellville October 2018

# **CPUT** copyright information

The dissertation/thesis may not be published either in part (in scholarly, scientific or technical journals), or as a whole (as a monograph), unless permission has been obtained from the University

## DECLARATION

I, Robin Maharaj, declare that the contents of this thesis represent my own unaided work, and that the thesis has not previously been submitted for academic examination towards any qualification. Furthermore, it represents my own opinions and not necessarily those of the Cape Peninsula University of Technology.

Signed

Date

# ABSTRACT

IOT devices have the potential to improve asset lifecycle optimization because of their ability to provide relevant real time data to high level applications. This data with minimal latency can assist asset managers to control the behaviour of assets and asset users to optimize asset lifecycle cost. There are many environments that require asset tracking devices but this design focussed on motor vehicles with auxiliary functions and apparatus.

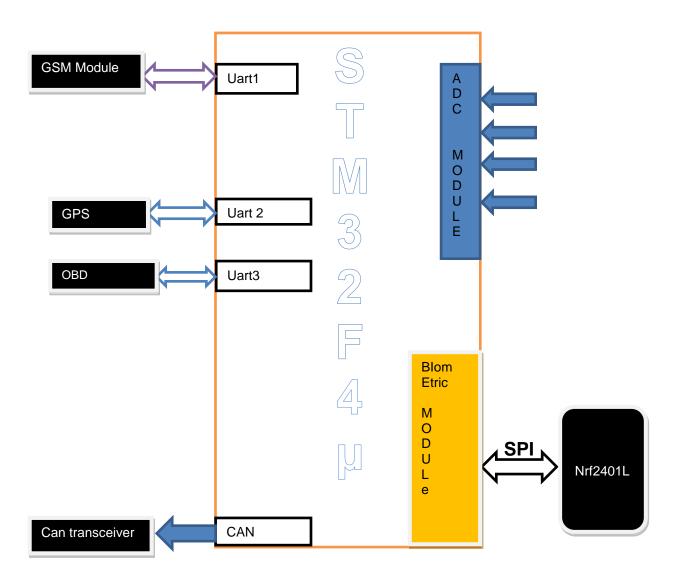

This research work documented the design of an asset tracking device built and tested on a 32.bit microcontroller platform with built-in CAN peripheral. This design resolved handling multiple serial interfaces collating data simultaneously concatenating this data and transmitting the data via GPRS interface as a single UDP sentence. Apart from interfacing various serial interfaces to the Stm24f4 this design also implemented a Wireless module as well as a multichannel ADC Module.

This design was accomplished by researching and implementing software techniques as well as researching the hardware/firmware in terms of DMA and Nested Vector Interrupt Controller of the STM32 devices.

The solution that this design will accomplish is to provide the industry an asset-tracking device with data capturing functionality capable of delivering the above needs at reasonable data cost. The device designed in this thesis is the client device of asset tracking network. This design was accomplished on a proof of concept basis delivering built hardware in the form of various application modules interfaced to a 32 –bit microcontroller via uart, SPI and CAN.

## ACKNOWLEDGEMENTS

First, all praise be to GOD for giving me the opportunity to complete my research/design work successfully and for acquiring new knowledge in the process that I know He has plans for.

My sincere gratitude and appreciation to my supervisor, DR A.K Raji, for his invaluable guidance, enthusiastic help and consistent encouragement throughout the entire research project.

Also would like to extend my thanks to my co-supervisor Mr Quinton Bart.

I would like to dedicate this thesis to my late parents, my wife Gail, my three kids Aston, Aidon and Sashni for all the unconditional love and support and patience, for all the encouragement. For all the Sacrifices made in terms of time I would like to extend a special thanks to my kids I know they felt it most thanks, love you guys.

# Robin Maharaj

# TABLE OF CONTENTS

| Declaration      | ii  |

|------------------|-----|

| Abstract         | iii |

| Acknowledgements | iv  |

| Glossary         | Х   |

# **CHAPTER 1: Introduction**

| 1.1 | Background                        | 1 |

|-----|-----------------------------------|---|

| 1.2 | Statement of the Research Problem | 3 |

| 1.3 | Objectives of the Research        | 3 |

| 1.4 | Significance of the Research      | 4 |

| 1.5 | Delineation of the thesis         | 5 |

| 1.6 | Organisation of the Research      | 5 |

# **CHAPTER 2: Literature Review**

| 2.1    | Introduction                                               | 6  |

|--------|------------------------------------------------------------|----|

| 2.2    | Perspective of the Project                                 | 6  |

| 2.3    | Research Methodology                                       | 7  |

| 2.3.1  | Literature review and protocols Investigation              | 7  |

| 2.3.2  | Understanding the Hardware.                                | 8  |

| 2.3.3  | Investigate Serial Communication interface and AT Commands | 8  |

| 2.4    | Other Designs that influenced this Design                  | 9  |

| 2.5    | Direct Memory Access (DMA)                                 | 11 |

| 2.5.1  | How does DMA operate                                       | 13 |

| 2.5.2  | DMA or Burst                                               | 14 |

| 2.5.3  | Setting up DMA in stm32f4                                  | 16 |

| 2.6    | Interrupts                                                 | 17 |

| 2.6.1  | Exceptions                                                 | 17 |

| 2.6.2  | Using Interrupts                                           | 18 |

| 2.6.3  | Nested Vector Interrupt Controller                         | 20 |

| 2.7    | Serial Peripheral Interface (SPI)                          | 22 |

| 2.8    | Analogue to Digital Convertor (ADC)                        | 23 |

| 2.8.1  | The Implementation of the Multi-channel ADC Module         | 24 |

| 2.9    | OBD Module                                                 | 25 |

| 2.9.1  | Overview                                                   | 26 |

| 2.9.2  | Research the OBD protocol                                  | 28 |

| 2.10   | Controller area Network (CAN) Module                       | 30 |

| 2.10.1 | Characteristics of CAN protocol                            | 31 |

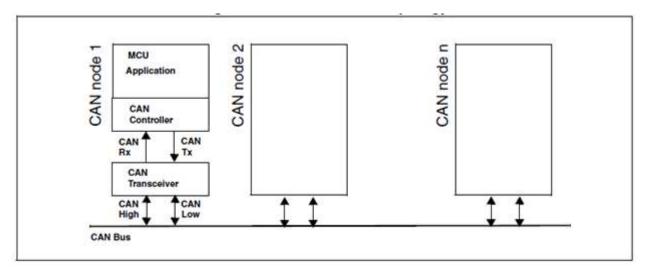

| 2.10.2 | Structure of a node in CAN network                         | 33 |

| 2.10.3 | Bus Arbitration                                            | 34 |

| 2.10.4 | Message Broadcasting                                       | 35 |

| 2.10.5 | Addressing Modes in CAN                                    | 35 |

| 2.11   | GPS Module                                                 | 37 |

| 2.12   | Biometric Module                                           | 39 |

| 2.12.1 | Functional description of Biometric module                 | 40 |

| 2.12.2 | Principle of operation of the Biometric module.            | 41 |

| 2.13.  | GSM and GPRS module                                        | 43 |

| 2.13.1 | Using GPRS                                                 | 43 |

| 2.13.2 | Overview of Billing of GPRS Data                           | 45 |

| 2.13.3 | TCP and UDP Headers                                        | 46 |

| 2.14 | Transmission control Protocol | 48 |

|------|-------------------------------|----|

| 2.15 | User Datagram Protocol        | 50 |

| 2.16 | Buffering techniques          | 50 |

| 2.17 | Level Shifting                | 52 |

# **CHAPTER 3: Hardware Design and Implementation**

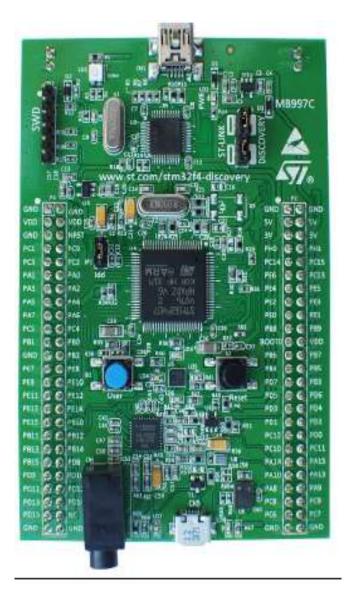

| 3.1    | STM32f4 Discovery Board ATD                                    | 56 |

|--------|----------------------------------------------------------------|----|

| 3.2    | Asset Tracking Device different Scenarios                      | 56 |

| 3.2.1  | Asset tracking device scenario No 1                            | 57 |

| 3.2.2  | Asset tracking device scenario No 2                            | 57 |

| 3.2.3  | Asset tracking device scenario No 3                            | 58 |

| 3.3    | Asset Tracking Device Concept Design                           | 59 |

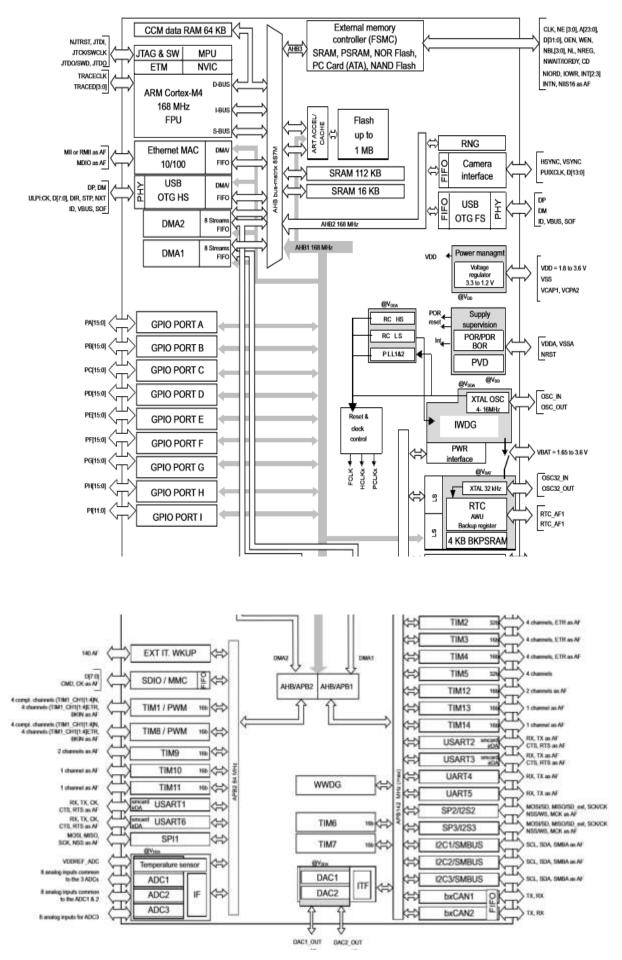

| 3.4    | Hardware architecture of Discovery Board                       | 61 |

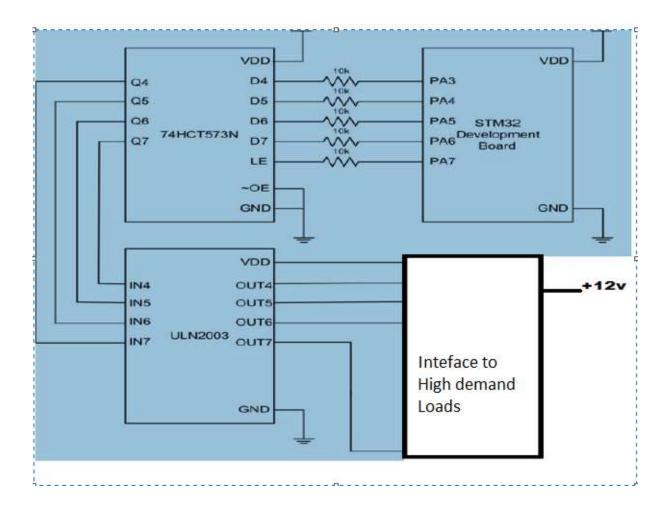

| 3.5    | Power Electronics Interface                                    | 63 |

| 3.6    | The Software Modules                                           | 65 |

| 3.6.1  | The CAN Module                                                 | 66 |

| 3.6.2  | IMPLEMENTATION OF CAN ON ASSET TRACKING DEVICE(ATD)            | 66 |

| 3.6.3  | Baud Rate of CAN protocol                                      | 67 |

| 3.6.4  | Interrupts of CAN protocol on STM32f                           | 67 |

| 3.6.5  | CAN Control Network for the ATD                                | 68 |

| 3.7    | GPRS /GSM Module                                               | 69 |

| 3.7.1  | Implementing the GPRS Module                                   | 70 |

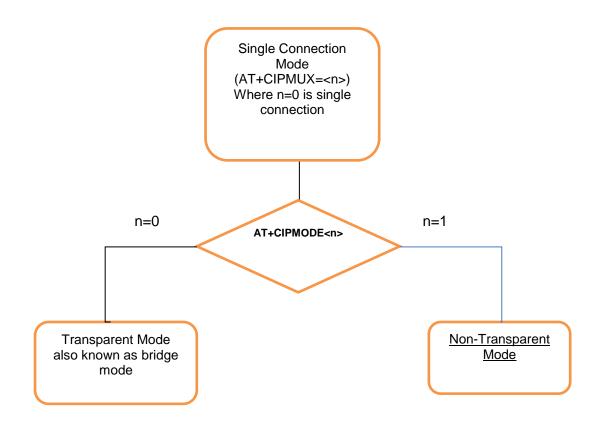

| 3.7.2  | Modes of Operation                                             | 71 |

| 3.7.3  | Sending UDP over GSM                                           | 73 |

| 3.7.4  | Configuring the ATD for GPRS Specific to sim900                | 73 |

| 3.7.5  | To send data via GSM                                           | 74 |

| 3.8    | Multiple channel ADC Module using DMA                          | 75 |

| 3.9    | Biometric module with SPI interface.                           | 76 |

| 3.9.1  | Interfacing the nrf2401I Module via SPI to the Microcontroller | 77 |

| 3.9.2  | Operating modes                                                | 78 |

| 3.9.3  | SPI Instruction set for the nRF2401                            | 78 |

| 3.9.4  | nRF2401L Data Pipes                                            | 79 |

| 3.9.5  | Arduino nrf2401I Transmitter Module                            | 81 |

| 3.10   | GPS Module                                                     | 82 |

| 3.11   | The OBD Module                                                 | 83 |

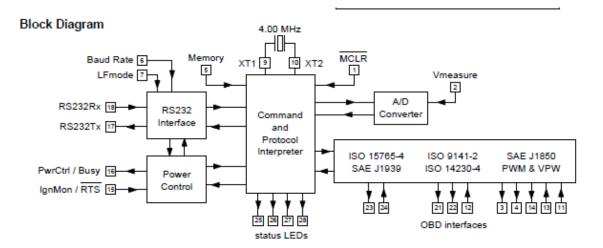

| 3.11.1 | Communicating with OBD Interpreter via AT Commands             | 83 |

| 3.11.2 | Function description of the OBD Module                         | 84 |

| 3.12   | Putting all Together                                           | 85 |

| CHAPTE | ER 4: Testing Results and Discussion                           |    |

| 4.1    | Testing and analysis of GPRS                                   | 89 |

| 4.2    | Analysis and Interpretations of the research Conducted         | 90 |

| CHAPTE | ER 5: Conclusion and Recommendation                            |    |

|        |                                                                |    |

| 4.1 | Conclusion     | 92 |

|-----|----------------|----|

| 4.2 | Recommendation | 93 |

# REFERENCES

# List of Tables

| Table 2.1 | DMA1 Request Mapping                      | 15 |

|-----------|-------------------------------------------|----|

| Table 2.2 | DMA2 Request Mapping                      | 15 |

| Table 2.3 | Detail Comparison of the OBD Interpreters | 28 |

| Table 2.4 | List of NMEA Sentences types              | 38 |

| Table 3.1 | SPI Instruction Set of nRF2401L           | 79 |

| Table 3.2 | Configuration Register of nRF2401L        | 80 |

# List of Figures

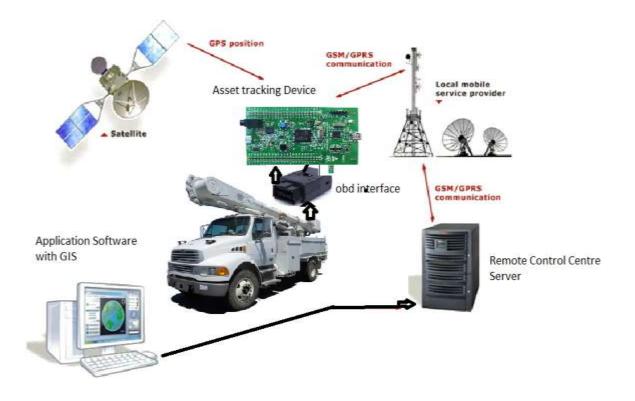

| Figure 2.1  | Vehicle tracking and Performance Monitoring                          | 9  |

|-------------|----------------------------------------------------------------------|----|

| Figure 2.2  | Showing DMA Transfer without engaging Central Processor              | 12 |

| Figure 2.3  | Architecture of NVIC                                                 | 18 |

| Figure 2.4  | Priority levels of STM32                                             | 19 |

| Figure 2.5  | Example of Vector Table                                              | 20 |

| Figure 2.6  | Tail-chaining                                                        | 22 |

| Figure 2.7  | Stack-Pop Pre-Emption                                                | 23 |

| Figure 2.8  | Serial Peripheral Interface                                          | 24 |

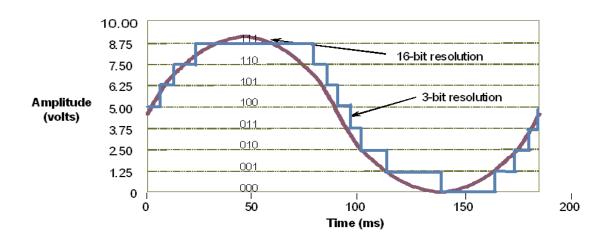

| Figure 2.9  | ADC showing 3-Bit resolution and 16-bit resolution Signal            | 24 |

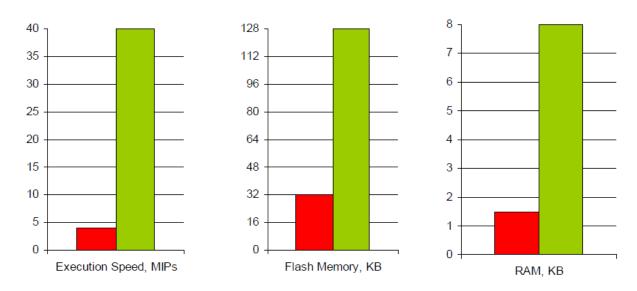

| Figure 2.10 | Graphical Comparison of Performance factors of diff OBD Interpreters | 29 |

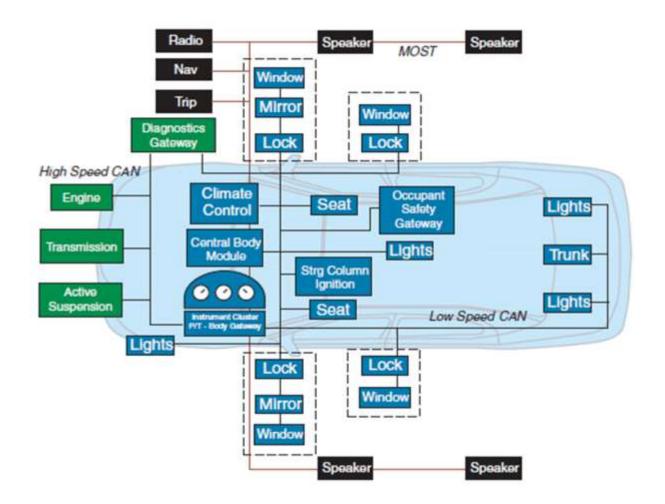

| Figure 2.11 | Typical CAN Network                                                  | 30 |

| Figure 2.12 | Frame structure of CAN ID field with data                            | 33 |

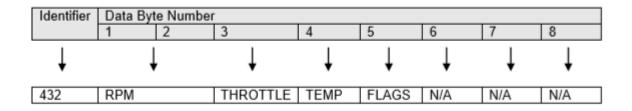

| Figure 2.13 | Example of data structure in CAN data fame                           | 33 |

| Figure 2.14 | Architecture of Data and Remote frame                                | 34 |

| Figure 2.15 | Explanation of NMEA Sentence of Type \$GPGGA                         | 39 |

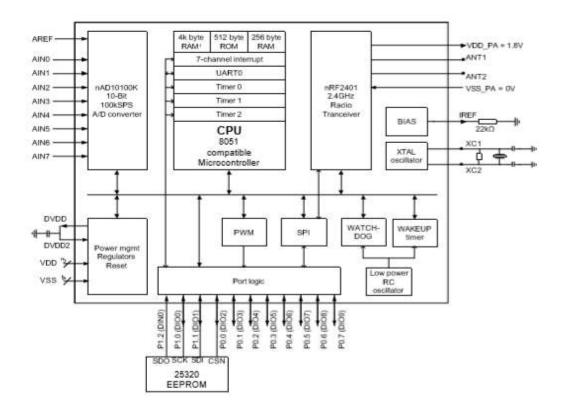

| Figure 2.16 | Block diagram of nRF24E1 with built-in microcontroller.              | 41 |

| Figure 2.17 | Diagram illustrating Biometric Module                                | 42 |

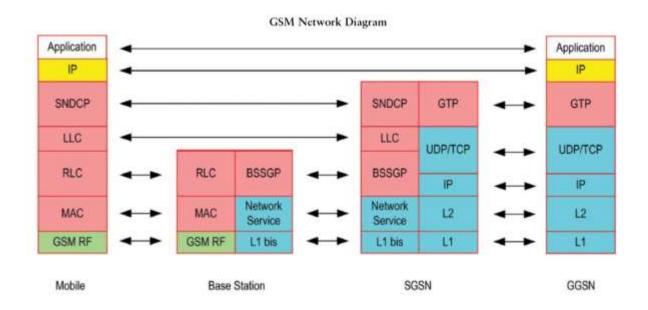

| Figure 2.18 | GSM Network Diagram                                                  | 46 |

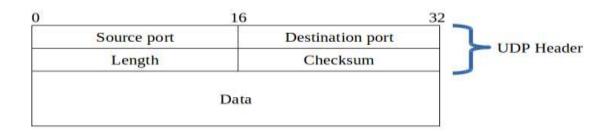

| Figure 2.19 | UDP structure                                                        | 49 |

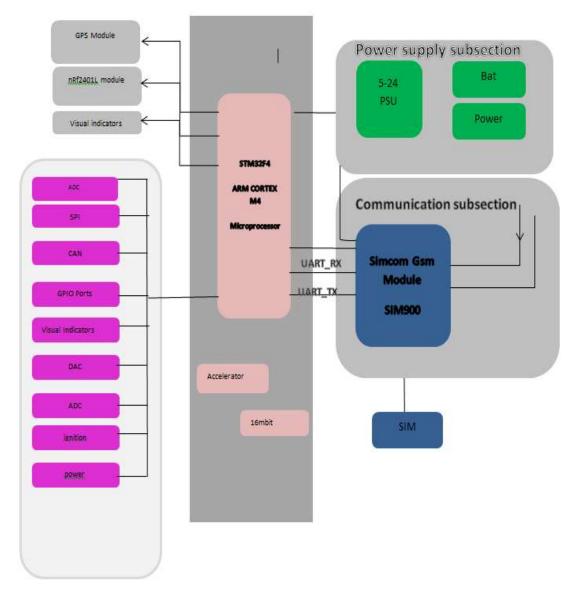

| Figure 3.1  | Functional diagram of asset Tracking Device                          | 56 |

| Figure 3.2  | Asset Tracking Device Concept                                        | 59 |

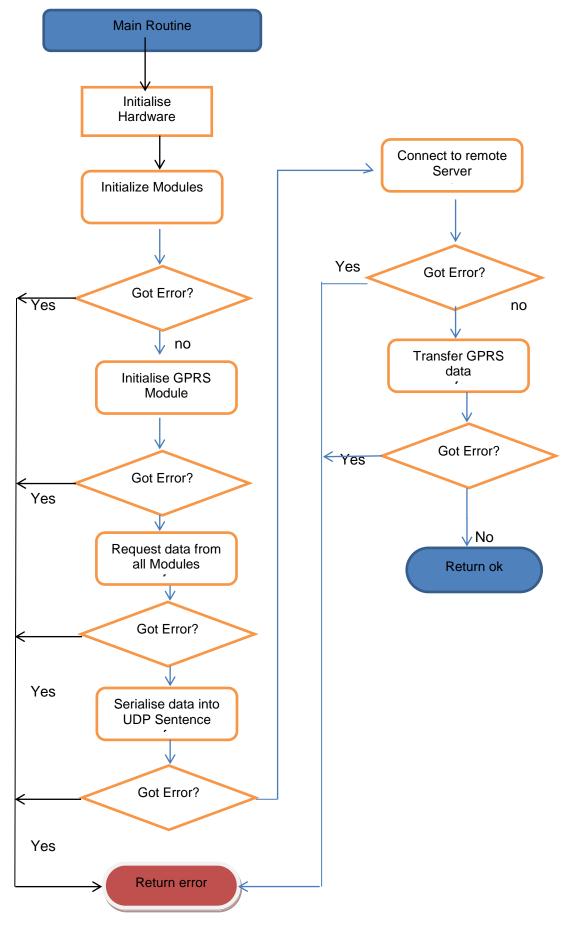

| Figure 3.3  | Flow-Chart of Asset Tracking Device                                  | 60 |

| Figure 3.4  | The Hardware architecture of Discovery Board                         | 61 |

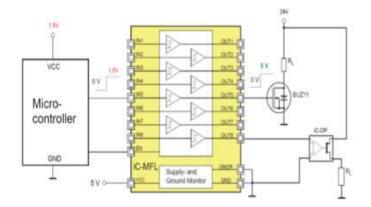

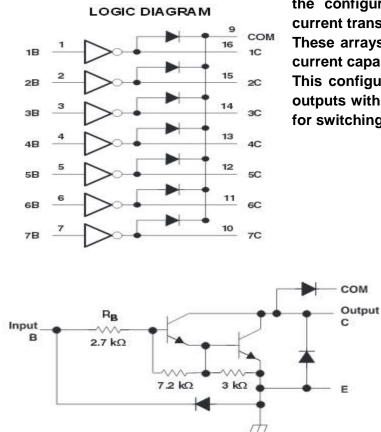

| Figure 3.5  | Power Electronics Interface                                          | 63 |

| Figure 3.6  | Block Diagram of STM32f4 Discovery Board                             | 64 |

| Figure 3.7  | Hardware structure of the Asset Tracking Device with GPRS Interface. | 65 |

| Figure 3.9  | CAN Network with Transceivers                                        | 69 |

| Figure 3.10 | Illustrates Single mode Connection                                   | 71 |

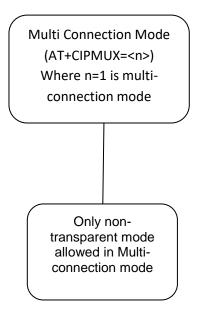

| Figure 3.11 | Illustrates Multi-mode connection                                    | 72 |

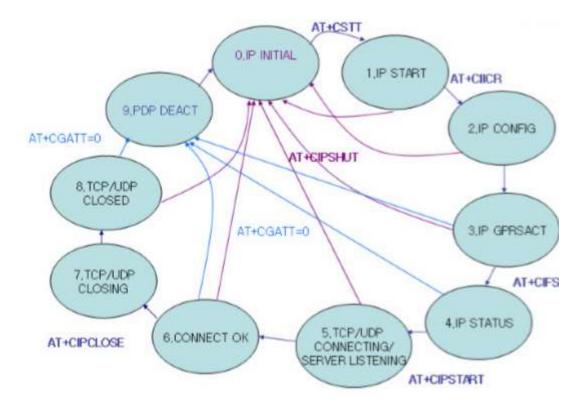

| Figure 3.12 | FSM :GPRS States Diagram for single connection                       | 75 |

| Figure 3.13 | OBD connector and Pinout                                             | 81 |

| Figure 3.14 | Function description of the OBD Module                               | 84 |

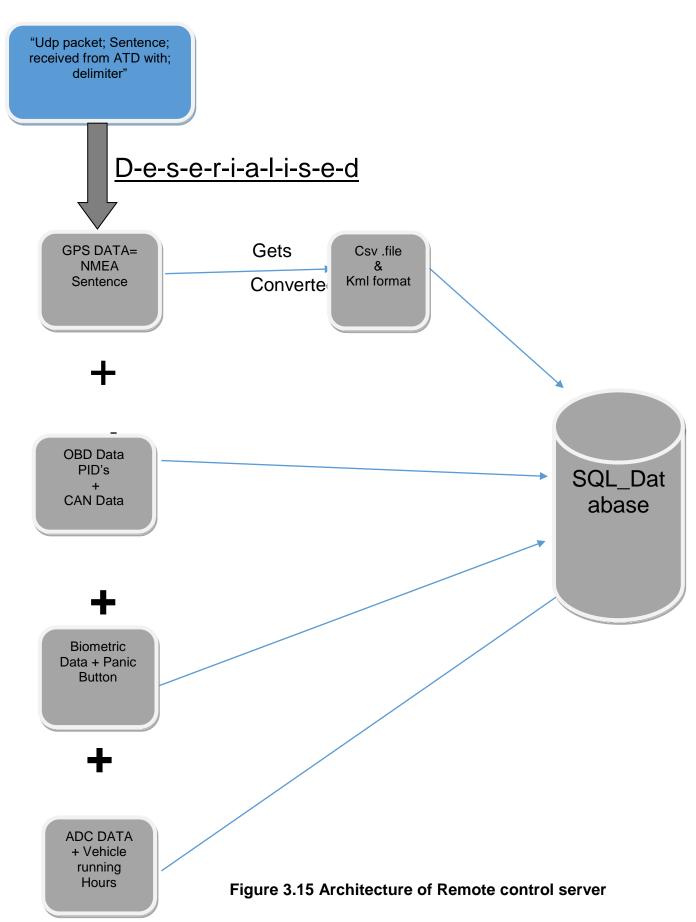

| Figure 3.15 | Architecture of Remote control server                                | 87 |

|             |                                                                      |    |

# Appendices

| Appendix A | Software code for ADC Module                                          | 97  |

|------------|-----------------------------------------------------------------------|-----|

| Appendix B | Software code for GPS                                                 | 101 |

| Appendix C | Pseudo code and state machine to implement the different GSM<br>Modes | 114 |

| Appendix D | Code for Biometric Module using nRF2401                               | 116 |

# GLOSSARY

| Terms/Acronyms/Abbreviations | Definition/Explanation             |

|------------------------------|------------------------------------|

| ADC                          | Analogue to Digital Convertor      |

| APN                          | Access Point Name                  |

| ATD                          | Asset Tracking Device              |

| CAN                          | Controller Area Network            |

| CPU                          | Central Processing Unit            |

| DAC                          | Digital to Analog Convertor        |

| DMA                          | Direct Memory Access               |

| DNS                          | Direct Memory Access               |

| ECU                          | Engine/Electronic Control Unit     |

| EMI                          | Electromagnetic Induction          |

| FDM                          | Frequency Division Multiplexing    |

| FIFO                         | First In First Out                 |

| FSM                          | Finite State Machine               |

| FTP                          | File transfer Protocol             |

| GNSS                         | Global Navigation Satellite system |

| GPIO                         | General Purpose Input Output       |

| GPRS                         | General Packet Radio Service       |

| GPS                          | Global Positioning System          |

| GTP                          | GPRS Tunnelling Protocol           |

| HTTP                         | Hyper Text Transfer Protocol       |

| I/O                          | Input/output                       |

| IOT                          | Internet of Things                 |

| IP                           | Internet Protocol                  |

| ISR                          | Interrupt Service Routine          |

| LAN                          | Local Area Network                 |

| MISO                         | Master In Slave Out                |

| MOSI                         | Master Out Slave In                |

| NMEA | National Marine Electronics Association |

|------|-----------------------------------------|

| NTC  | Negative Temperature Coefficient        |

| OBD  | On Board Diagnostics                    |

| PWM  | Pulse width modulation                  |

| RF   | Radio Frequency                         |

| SAE  | Society of Automotive Engineers         |

| SCI  | Serial communications interface         |

| SPI  | Serial Peripheral Interface             |

| TCP  | Transmission Control Protocol           |

| TDMA | Time Division Multiple Access           |

| UDP  | User Datagram Protocol                  |

| UDS  | Unified Diagnostic Services             |

| WAN  | Wide area Network                       |

# Chapter 1 Introduction

### 1.1 Background

With the present trends in the modern digital era in terms of the Internet of things, there is an ever-growing need for devices to be connected to internet or to a remote control centre. The industry has undergone huge technologically advancements in the last twenty years both from a mechanical perspective as well as from an electronic and power electronic perspective. Low cost microcontrollers have advanced quiet tremendously giving us 32-bit microprocessor capability as well as numerous peripherals with numerous communications interfaces. In addition, the cost of this technology has decreased exponentially making asset tracking a viable option for technology solutions.

The public sector more so the government departments have thousands of specialised vehicles that are currently being abused. In the South African environment there is presently no device that is capable of bringing the different management systems together into one system for proper automated audit and asset management process. In this dissertation, we will embark on capturing data from numerous modules through different communication interfaces or techniques and relay this data to a remote control centre.

This project will focus on research methods in terms of acquiring data, processing this data converting to a data algorithm for transmission. The project will also look at efficient buffering and storage techniques as not all the collated data will be transmitted. This research project endeavours to solve these issues using a 32-bit micro-controller as an asset tracking and data acquisition device. It also looked at cost of transmitting data using to different protocols namely UDP and TCP in the form of HTTP. All of these translate into a perimeter-based asset-tracking device

This project will also employ GPS, GSM modules and Digital signal processing techniques using the 32-bit arm microprocessor. The design will tap into an OBD control unit using an OBD interpreter interfaced to an arm microprocessor via a UART peripheral.

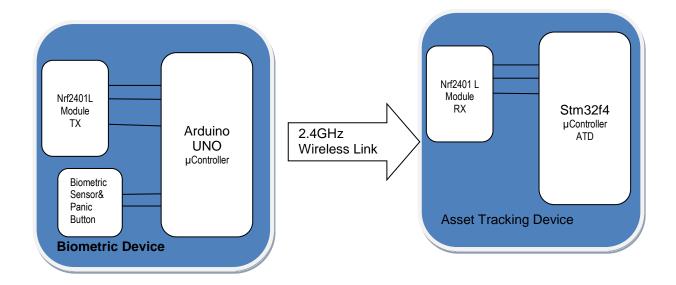

The design has in addition interfaced a RF biometric interface with panic button via the microcontroller for the purpose monitoring security personnel of the public sector like Metro police or extended use by the public. The purpose of this interface is to stream data such as pulse rate, blood pressure as well distress signal to a control centre via the microcontroller. In the RF biometric module, the research has explored different radio frequency communication interfaces between the biometric device and the microcontroller like RF or wireless technologies and implemented the most efficient and robust interface.

The purpose of this project is to design an asset tracking control unit with a GPRS comms interface that would be able to connect remote control centre. The asset-tracking device will monitor input signals connected locally to the I/O module; it will communicate to the OBD unit of the vehicle through an OBD interpreter, the CAN interface will also transmit live vehicle data but this interface will also allow the control centre limited control functions; the microcontroller will relay buffered GPS data and it will also stream biometric data and a distress signal to a Remote Control Centre .It will process and transmit auxiliary data acquired by the asset-tracking Device.

The purpose of this specific asset-tracking modules is to capture engine running hours of the vehicles as the auxiliary equipment like the Hydraulic pumps for the PTO (Hydraulic cherry picker) is running while the vehicle engine is running but vehicle is stationery. This means vehicle mileage is not a good indication of vehicle use as well as not an accurate measure of fuels consumed by vehicle per mileage. With asset tracking device installed Vehicle maintenance can be carried out on running hours as opposed to mileage of the vehicle. This will ensure that an accurate cost of fuel consumed by the vehicle to operate auxiliary can be isolated from the cost to move the vehicle around. In the public sector the vehicles are not treated as mere vehicles but operational assets and thus the maintenance strategy surrounding these heavy duty vehicles.

Also the control centre will have vehicle OBD status at any given time as well as fault status of the engine and if required other control units at all times. If operator of vehicle operates vehicle or any equipment during the fault conditions the control centre will be informed in real time. The call centre can dispatch staff automatically during these exception conditions or the software can be programmed to automatically inform technical staff.

#### **1.2 Statement of the research Problem**

IOT devices have the potential to improve asset lifecycle optimization because of their ability to provide relevant real time data to high level applications. This data with minimal latency can assist asset managers to make and control the behaviour of assets and asset users to optimize asset lifecycle cost.

But the present perception of devices or applications in the IOT Space is that they are resource intensive as well as that they have short comings in terms of data efficiency. This

leads to asset managers neglecting to implement these solutions as part of asset optimization applications.

This research design embarked to investigate these shortcomings and implement solutions to reduce data cost using a 32 microcontroller. This design will look at these solutions using both hardware and software routines to improve on data cost and data latency issues using a microcontrollers

# 1.3 Objectives of the Research

The aim of this research is to achieve a barebones approach to the design of asset tracking device using different communication devices to interface into microcontroller to capture data, buffer data and transmit it with minimal data cost.

a. this thesis will focus on design to capturing data via different interfaces, which will handle data coming in at different rates from different communications interface

b. this thesis will also look at arbitration as well as priorities of the different interfaces as well as the microcontrollers handling direct io.

c. in term of data transmission, this research will experiment with different ways of sending data and examining the cost variables and reliability of sending data via gsm/gprs methods.

d. This research project will focus on research methods in terms of acquiring data, processing this data converting to a data algorithm for transmission. This thesis will also look at efficient buffering and storage techniques as not all the collated data will be transmitted. It will attempt to solve these issues using a 32-bit micro-controller as an asset tracking and data acquisition device.

e. This research will look at cost of transmitting data using different protocols namely UDP and HTTP.

f. To develop an RF biometric interface with panic button to the microcontroller for the purpose monitoring security personnel of the public sector like Metro police. The purpose of this interface is to stream data such as pulse rate, blood pressure as well distress signal to a control centre via the microcontroller. This will add value to the device from an operational perspective.

# 1.4 Significance of the Research

This research intends to significantly change the mind-set in terms of present development platforms in the South African context. It also intends to demystify the role of IOT devices with regard to asset life cycle management as to implement an asset tracking device with the purpose of collating data for the purpose of intelligently using it for remote call centre as well as for data analysis for asset life cycle management.

Very few research projects have been undertaken to implement an asset tracking device that will serve as an asset tracking device that will also serve as an automated data interface to assist with life cycle asset management optimisation in South Africa.

The purpose of this project is to build the foundation to generate and automate data from devices that have an impact on asset life cycle that can be optimised if not managed. In term of the Internet of things, there are a lot of assets that that have high maintenance cost and acquiring data from these devices as well as offering some controllability in many instances will improve maintenance cost and in turn optimise asset life cycle.

In this particular project, there are also numerous safety spinoffs like the RF biometric interface it assists the personnel using the vehicle in case they incapacitated they can press the panic button and if that is not possible and if their vitals are that of distress condition the device will relay a distress signal to the control centre and the Control centre can dispatch emergency personnel to that location.

# 1.5 Delineation of the thesis

The interfacing of the various modules poses numerous design challenges which includes hardware, software and electromagnetic interference.

This thesis will not cover the design or implementation of the control centre but will briefly discuss it with some pseudo code. The testing of the design will be done via a udp sockets application called sockets tester.

This thesis will be limited to the design and implementation of only the ATD, a client module that will communicate to a control centre and Central Remote Database

The design will be implemented on a proof of concept basis and as a development prototype.

This design includes various modules and architectures to bring about a device that serves multiple functions as well has several benefits from asset life cycle optimisation to applications that can be extended to safety and security of personnel or to the user of the asset being tracked.

# 1.6 Organisation of the Thesis

This thesis is organised into different chapters for ease of reading as well as separating the different technologies and modules. The breakdown of the chapters is as per table of contents. Chapter 2 covers the theoretical research that was acquired during this project, Chapter 3 is Hardware implementation of the design. Chapter 4 highlights the analysis of design and some findings related to the design. And the final chapter concludes this research and gives some insight to future work in the line of this research.

# Chapter 2

#### Literature review

#### 2.1 Introduction

The concept of asset tracking has been around for many years now and has been employed to different assets for different purposes. This research investigated asset tracking and monitoring. This research has reviewed these types and combined different aspects of asset tracking and monitoring techniques for the purpose of asset optimisation. In South Africa however there are very few developers or students that have embarked on this field and if they did they have adopted the rapid development platform to implement these solutions. In the South African context students and developers need to adopt a "bare metals" approach to implementing solutions so that they can develop their own software libraries and techniques and have a better understanding of the technologies present. It has been a trend in "third world economies "to implement a lot of solutions using rapid development platforms, this has resulted in not understanding the technologies and creating a lag in terms of development of new products because they do not have their own libraries and the foundation and acquired knowledge to develop new products. There might be an argument that there is various open source libraries available to implement these solutions to this I again say that these solutions without a deep understanding of what is being done also does not put us third world countries on the platform to be ground breakers in the embedded systems environment.

## 2.2 Perspective of this project

It is important to put the design approach employed in this design project into perspective. The growing trends at present in terms of development of new products is to employ the rapid development platforms like Arduino, mbed and the likes. These platforms certainly have their place industry but the underlying issues in developing countries like South Africa it takes away the opportunity to understand the building blocks of microcontrollers and embedded system engineering; in these countries we find developers merely adapting first world country's design to suite their own environments, they simply use libraries written by their 1st world counterparts in their applications without in-depth understanding the architecture of the hardware is being used. In order for these counties to acquire this deep understanding of the architecture they need to code from the data sheet and write their own libraries using low level coding languages so that they can become pioneers/experts in the development of embedded products. This will also give them the in-depth understanding to solve problems that is presently persistent in these countries in terms of embedded systems

without the need to pull in foreign help to solve some of their design issues. During this design it was one of the key objectives was to write "our own" libraries to implement this design, which was accomplished quite successfully.

# 2.3 Research Methodology

The research methodology used in the project is Applied Research Methodology. This research looked at problems industry and parastatals face with regard to asset lifecycle optimisation, and also looked at how technology from an embedded systems perspective or Internet of things perspective can bridge the gap for asset life cycle optimisation. A great deal of the research methodology comes from the tacit experience an electronic engineer acquired through a long career in the asset maintenance environment and the wants or the gaps that were presented over the years. It is the asking the questions of how the new digital era and IOT can solve old asset lifecycle issues. A key factor in terms of this design was also to understand the architecture of the control centre as to understand how the data needs to be presented to the control centre/asset lifecycle management software.

Having researched the above the next phase of this research was to research all the technologies that was planned to be implemented in this design so as to implement a streamlined design process negating errors and shortcomings other developers may have experienced in this field.

This research can be broken down into three areas viz: Research software techniques. Researching the hardware as well as communication interface. In addition, the third phase, once a working prototype is produce to monitor data transmission cost using different data transmission techniques and protocols.

#### 2.3.1 Phase 1: Literature review and protocols Investigation

Literature review was conducted to understand the technologies and techniques available with this research, apply, and improve on techniques and technologies researched.

In order to be implement the design of an asset tracking control unit the incumbent will be required to do the following:

Use and interpret NMEA commands and data to implement the GPS module

This is a fundamental software requirement in order to carry out this project. The project requires an expert knowledge of embedded design and to be able to program a microprocessor in the C-language. C is a very power language that allows a programmer access the inner workings of microcontrollers. The project employs expert knowledge of implementation of buffers as well numerous modules all competing for CPU time. The design will also employ advanced c programming techniques as well as use Finite state machines to implement the code.

#### 2.3.2 Phase 2: Understanding the Hardware.

There was also a direct requirement to read and understand the datasheets for all the hardware that was implemented. The stm32f4 data sheet is on its own has more than 1800 pages as well as numerous application notes that complement the datasheet. This data sheet together with some research and forums really puts into context the capabilities as well as issues other developers and designers have had with the stm32f4 development board.

All the other modules implemented in this design required a detailed familiarisation with their data sheets to understand the interfacing of these modules to the mother module especially with regard to the voltages and electromagnetic interference, especially important because of the some modules implemented have radio frequency implication. Electromagnetic Interference especially of the close proximity of these modules to each other. This design has not covered any documentation in terms of the electromagnetic interference but expect that cognisance should be taken of this influential factor with regard to the design and layout of components and modules specifically knowing that many modules of this design operates in the RF domain.

In this research we implemented various technologies all of which required some form of investigation and research all of which has been documented in depth in some cases and succinct in other cases.

#### 2.3.3 Phase 3: Investigate Serial Communication interface and AT Commands

Development of communication interfaces to the various devices connected to the microprocessor also required some investigation. Investigating SPI, Uart as well as CAN as a communications interface required in-depth understanding of the protocol implementation as well as a low level understating especially CAN. To this end the investigation assisted in developing efficient software routines necessary to implement the design.

Because this design is using different communication interfaces operating simultaneously it was imperative to investigate underlying techniques in terms of buffering this data efficiently

8

without loss or latency. This design investigated different buffer techniques. This thesis also researched principles of Finite state machines, Interrupt handling techniques as well other software techniques in order to accomplish this design. It was also the purpose of this design to reduce data costs which was essential if we ever wanted to take this design to market. This design also looked at finite state machines in terms of monitoring the asset-tracking device in order to control the mode that the device will be in, in order to optimise data costs. Research AT Commands:

In order implement these interfaces in this design it was required to research and implement the AT commands to access the various workings and data of these modules. The AT commands are specific to the individual modules and would have to be implemented differently and separately.

This module is an integral part of this project in order to implement perimeter based asset tracking.

Research and implement AT commands set for both OBD, GPRS and GPS interfaces

# 2.4 Other Designs that influenced this Design

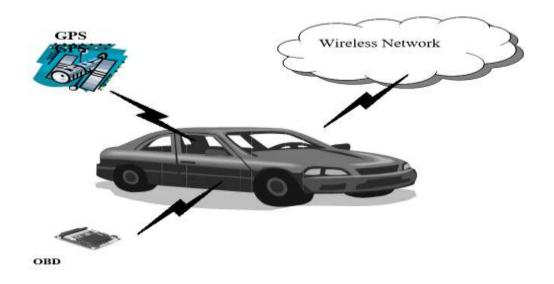

The first type of asset tracking that was researched was the popular vehicle tracking and performance monitoring systems. (Jenkins, 2006) in his research demonstrated the core underlying technologies, illustrated in, position tracking, i.e., GPS, performance monitoring, i.e., OBD-II, and wireless communications, i.e., GPRS

Figure 2.1 Vehicle tracking and Performance Monitoring

Jenkins in his design used GPS 35-PC receiver collected the recommended minimum data sentence (GPRMC) from the NMEA standard protocol. OBD-II data was gathered by a BR-3 interface. This interface incorporates a Microchip BR16F84-1.07 microcontroller, which operates on three SAE J1850 protocols i.e., VPW, PWM, and ISO-9141. (Jenkins, 2006) Microsoft C# using Visual studio was used as the platform to write the data collection software. A tomcat web server, in conjunction with a MySQL database server, functioned as the gateway for users to view the location and performance data of each vehicle. The user interface was developed with JAVA SDK 1.4.2\_05.

The data collection software combined GPS coordinates and OBD-II data into a single data stream that was sent to the server via the GSM/GPRS network. The data retrieved from the OBD-II system by continuous polling. Transmission of data to the server triggered by a received event from the GPS device connected to a serial port. This allows for a one-second minimum resolution. As it can be seen from the above approach of implementing the design or solution are all done on rapid development platforms or interfaces that are already implemented by some third party. This is all good and well if all that is to be achieved was a short-term solution to a business need but as for development and acquiring knowledge to implement new breakthrough designs this approach leaves one wanting.

Most of the implementation of the above design was implemented on High level application using high level programming languages; this research however have taken a step back and have explored development using the microcontrollers datasheet and writing routines from the datasheet using a low level programming language C. In addition, the other difference in this design is the microcontroller used. It is always the case that the microcontroller family that a designer was exposed to in their early years of development is the family of microcontrollers that they will go on to develop later in their careers purely based on familiarity with the said controller. Migration to other microcontrollers is only done if the features that developer is looking to implement is not present in their preferred choice but in the other.

The microcontrollers over the last decade has evolved quiet substantially and have capabilities of much more communication interfaces with advanced DMA capabilities this allows for interrupt or dma based communication interfaces. The other short coming of the design above is the method of polling used for the communication interface, very primitive as well as it ties up the processor putting restriction in the no of routines it can process.

(Bangali S.A & Shah S.K. Dr 2015) Implemented a vehicle tracking system for a school bus incorporating Biometrics, GPS, and GPRS also implemented on a Stm32f discovery board. The approach is fundamentally different as well as the objectives but a lot the work covered are very similar to what we want to implement. The biometric module implemented in this project is used for student identification via fingerprint identification and is verified by eeprom-

stored data. The GPS and GPRS Modules are used for vehicle location and internet connectivity.

The transmission protocol used for the transmission of data is HTTP. Their device is developed on a higher application layer than the device proposed in this design. There is also foreseeable high transmission cost with http as whether a device send 3bytes of data with http or whether it sends 80 bytes of data you are billed for the same with each http session. This design implements encapsulating data as well as using plain UDP for transmission thus reducing cost. The research also provides discussion of this in this dissertation.

The microcontrollers over the last decade has evolved quiet substantially and have capabilities of much more communication interfaces with advanced DMA capabilities this allows for interrupt or dma based communication interfaces. This thesis will explore and analyze the implementation of Serial communications interface using DMA and interrupt driven controller.

The design of Controller for multi-Layer parking controller based on the STM32 was researched based on the successful implementation of the CAN module as well as the use of the Stm32 arm microcontroller used. This design was based on the predecessor microchip the STM32f103 as opposed to the microcontroller used in this design but the baseline architecture is very similar and thus very useful information was derived from researching this design (Zhang et al. 2014).

The review of their design lead to understand the Power of using the DMA when implementing the ADC Module for this design as well as the architecture of the STM32 microcontroller in terms of using the can mailbox and the DMA without engaging the microprocessor thus being able to write macros to realize some of the control functionalities for the CAN Module.

Apart from researching other or similar thesis to this design it was important to research other theoretical and coding concepts in order to implement this design. Essentially that was the idea required to accomplish this design but after researching other thesis there was still unanswered questions and knowledge in terms of completing and implementing this design. Further researching of different technologies individually as well as software coding techniques had to be instituted to achieve a level of knowledge to implement the desired outcomes. Thus the research literature review was extended to the ensuing theories and technologies.

11

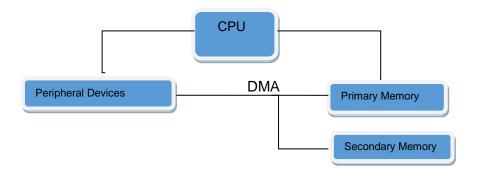

## 2.5 Direct Memory Access (DMA)

The design of the Asset tracking unit with GPRS relies on the proper use of the microcontrollers peripheral interfaces to get data from different modules and be able to store it in buffers for transmission to a control center and for selected local storage. To be able to achieve this it was necessary to understand and implement the proper use of DMA as well as Interrupts. It is with this in mind that the theory and implementation of DMA As well as Interrupts in this thesis was researched.

Direct memory Access negates the need to engage the processor for peripheral to memory, memory to memory and memory to peripheral transfer. DMA is a peripheral controller that controls the processor's bus directly. The DMA is an advanced high performance bus module. DMA only engages the processor for permission to use the Bus.

The STM32f4 DMA controller has numerous independently configurable channels that can perform autonomous transfers from peripheral to peripheral, peripheral to memory and memory to memory.

## Figure 2.2 Showing DMA Transfer without engaging Central Processor

DMA enables the use of interrupts more efficiently as well increases data throughput and reduces the need for costly peripheral – specific FIFO Buffers it also reduces data latency.

## 2.5.1 Principle of Operation of DMA

In a routine DMA operation, some configurable event or flag or interrupt notifies the built-in DMA controller that data needs to be transferred from a peripheral to memory or vice versa.

The DMA controller then sends a DMA request signal/event to the CPU, requesting authority to use the bus. The CPU completes its current bus activity, stops driving the bus, replies with a DMA acknowledge signal to the DMA controller. The acknowledge signal is the signal that gives the DMA permission to use the bus.

The DMA controller then transfers one or more bytes, driving the preassigned address, data, and control signals without engaging the processor. When the process is completed, the DMA controller stops driving the bus dis-asserts the DMA request signal. The processor then resets its DMA acknowledge signal and then the bus control is handed back to the processor. In Embedded applications where the design requires minimal processor engagement DMA is the preferred method of transferring data from peripheral to memory and vice versa.

DMA controllers are typically initialized /configured by the software. Typical setup parameters include the length of the block, the base address of the destination area, the base address of the source area, which channel and stream to be used and whether the DMA controller should generate a processor interrupt once the block transfer is complete. See biometric module for detailed implantation of the DMA.

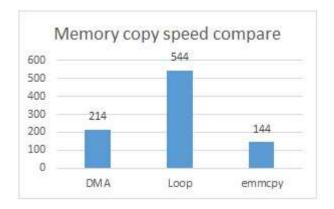

#### 2.5.2 DMA: Burst or Single-cycle Mode

DMA operations can be performed in either burst or single-cycle mode. Some DMA controllers support both. In burst mode, the DMA controller keeps control of the bus until all the data buffered by the requesting device has been transferred to memory (or when the output device buffer is full, if writing to a peripheral). This is obviously not viable in Small active microcontroller designs that have many peripherals in use as this would tie up the bus. So in principle before one goes ahead and implement one or the other modes its best try to understand how the available bus will be affected. It is also advisable to kind a share bus usage when it come to the peripherals. In essence, what is being said that if when assigning a specific peripheral to a bus try and assign them according to bus usage if there is more than one busses like in the STM32f4 microcontroller.

In single-cycle mode, the DMA controller gives up the bus after each transfer. This minimizes the amount of time that the DMA controller keeps the processor off the memory bus, but it requires that the bus request/acknowledge sequence be performed for every transfer. This overhead can result in a drop in overall system throughput if a lot of data needs to be transferred. DMA isn't great for very fast memory copies, the most defining benefit of DMA does occupy the main processor. DMA is certainly much faster than the conventional loop

method of transferring data but much slower memcpy function as can be seen in the graphic below:

In most designs, one would use single cycle mode if the system cannot tolerate more than a few cycles of added interrupt latency. Likewise, if the peripheral devices can buffer very large amounts of data, causing the DMA controller to tie up the bus for an excessive amount of time, single-cycle mode is preferable.

# 2.5.3 Setting up DMA Transfers on STM32f4

- need a "source", a memory address when copying data from, a "destination", i.e. where copying to.

- The size of the data chunks to be transferred. This needs to be done for both source and destination

- And some sort of signal telling the DMA controller when the next byte is ready to be transferred.

STM32f4 has 2 DMA controllers. Both Controllers are almost identical main difference being that DMA2 controller can only perform memory-to-memory data transfers. The other difference is that DMA2 is connected to APB2 while DMA1 is connected to APB1.Each DMA controller has separate streams. Each stream itself needs to be associated with one of eight channels.

These channels carry the signals to notify the DMA controller that data is ready to be transferred. Also known as DMA requests.

Which stream or channel to be used is determined by the following two tables?

## Table 2.1 DMA1 Request Mapping

| Peripheral<br>requests | Stream 0            | Stream 1              | Stream 2            | Stream 3              | Stream 4              | Stream 5        | Stream 6             | Stream 7            |

|------------------------|---------------------|-----------------------|---------------------|-----------------------|-----------------------|-----------------|----------------------|---------------------|

| Channel 0              | SPI3_RX             |                       | SPI3_RX             | SPI2_RX               | SPI2_TX               | SPI3_TX         |                      | SPI3_TX             |

| Channel 1              | I2C1_RX             |                       | TIM7_UP             |                       | TIM7_UP               | I2C1_RX         | I2C1_TX              | I2C1_TX             |

| Channel 2              | TIM4_CH1            |                       | I2S2_EXT_<br>RX     | TIM4_CH2              | I2S2_EXT_<br>TX       | I2S3_EXT_<br>TX | TIM4_UP              | TIM4_CH3            |

| Channel 3              | I2S3_EXT_<br>RX     | TIM2_UP<br>TIM2_CH3   | I2C3_RX             | I2S2_EXT_<br>RX       | I2C3_TX               | TIM2_CH1        | TIM2_CH2<br>TIM2_CH4 | TIM2_UP<br>TIM2_CH4 |

| Channel 4              | UART5_RX            | USART3_RX             | UART4_RX            | USART3_TX             | UART4_TX              | USART2_RX       | USART2_TX            | UART5_TX            |

| Channel 5              |                     |                       | TIM3_CH4<br>TIM3_UP |                       | TIM3_CH1<br>TIM3_TRIG | TIM3_CH2        |                      | TIM3_CH3            |

| Channel 6              | TIM5_CH3<br>TIM5_UP | TIM5_CH4<br>TIM5_TRIG | TIM5_CH1            | TIM5_CH4<br>TIM5_TRIG | TIM5_CH2              |                 | TIM5_UP              |                     |

| Channel 7              |                     | TIM6_UP               | I2C2_RX             | I2C2_RX               | USART3_TX             | DAC1            | DAC2                 | I2C2_TX             |

# Table 2.2 DMA2 Request Mapping

| Peripheral requests | Stream 0  | Stream 1  | Stream 2                         | Stream 3 | Stream 4                          | Stream 5  | Stream 6                         | Stream 7                          |

|---------------------|-----------|-----------|----------------------------------|----------|-----------------------------------|-----------|----------------------------------|-----------------------------------|

| Channel 0           | ADC1      |           | TIM8_CH1<br>TIM8_CH2<br>TIM8_CH3 |          | ADC1                              |           | TIM1_CH1<br>TIM1_CH2<br>TIM1_CH3 |                                   |

| Channel 1           |           | DCMI      | ADC2                             | ADC2     |                                   |           |                                  | DCMI                              |

| Channel 2           | ADC3      | ADC3      |                                  |          |                                   | CRYP_OUT  | CRYP_IN                          | HASH_IN                           |

| Channel 3           | SPI1_RX   |           | SPI1_RX                          | SPI1_TX  |                                   | SPI1_TX   |                                  |                                   |

| Channel 4           |           |           | USART1_RX                        | SDIO     |                                   | USART1_RX | SDIO                             | USART1_TX                         |

| Channel 5           |           | USART6_RX | USART6_RX                        |          |                                   |           | USART6_TX                        | USART6_TX                         |

| Channel 6           | TIM1_TRIG | TIM1_CH1  | TIM1_CH2                         | TIM1_CH1 | TIM1_CH4<br>TIM1_TRIG<br>TIM1_COM | TIM1_UP   | ТІМ1_СНЗ                         |                                   |

| Channel 7           |           | TIM8_UP   | TIM8_CH1                         | TIM8_CH2 | TIM8_CH3                          |           |                                  | TIM8_CH4<br>TIM8_TRIG<br>TIM8_COM |

The above tables illustrate how the DMA streams are associated with which peripherals via which channel for example Using Tables above: To setup DMA for SPI\_2Rx

Using DMA Controller 1; Stream 3 and DMA request signal Channel 0

For ADC1 we would be using DMA2, Stream 0 and Channel 0;

To complete the DMA setup one will need to configure the Microcontroller further. There are Hal Drivers that are available to set up the stm32f4 but in this design chose to use the standard peripheral libraries keeping in line with the bare bones approach. SPI portion of the Biometric module Interface will be used to explain with a bit of code how to set the data transfer using dma;

For this one will need to Include two file i.e. the DMA.h and DMA.c files.

For the Biometric module, the STM32F4 controller is set up to receive data via the SPI2.

- The DMA request for the received buffer is associated with channel0 of stream3 of DMA 1

- The peripheral base address is a pointer to data register of the SPI2 module the biometric module is interface to the asset-tracking device via SPI2.

- The memory base address is the pointer to an array Bio\_Buffer. This where the data for the biometric module that was acquired is stored.

- For DMA mode there are two options: normal and circular. In normal mode, the DMA stops transferring bytes after the specified number of data units, whereas in circular mode it simply returns to the initial pointer and keeps going.

- the peripheral address doesn't change, the pointer location into memory does get incremented thereby stepping through my "Bio\_Buffer" array.

- the size of this array is exactly 6\*84 bytes

- it is also imperative to specify a priority level for this DMA stream as in this design numerous peripherals are being used and relying on DMA to handle transfers on other peripherals as well.

Each DMA stream has its own small FIFO (first-in-first-out) buffer, which can temporarily store data from the source before transferring it to the destination. In addition, the transfer can happen in burst instead of single transfers.

So for a quick recap of DMA with the STM32F4. It can be an incredibly powerful feature that allows one to make the most of available computing power of the microcontroller. So as long as there is data that is being passed around the microcontroller from peripheral to memory or vice versa or from memory to memory, DMA is very useful but it if none of those requirements needs to be implemented then DMA will seem like a waste of time and resource. How useful it is will depend on the precise nature of the task to be accomplished. Key driving factor is that if we have Data that need to be passed or moved around use DMA it's the quickest most efficient way to do that without processor intervention. The DMA controller has definitely allowed embedded designers a channel to improve data latency issues as well as reduce processor overhead quiet incredibly making the 32-microcontroller very viable options in the IOT space.

#### 2.6 INTERRUPTS

In this research project, it was necessary to understand and conceptualise the inner workings of interrupts. This understanding enabled the design to implement most of the modules in this thesis as well as put them together to function as one unit.

Interrupt is a powerful concept in embedded systems for control of how we want to execute the time-critical events and handle them in controlled and prioritized manner. In a typical embedded system, the processor (microcontroller) can only perform one task at a time but is responsible for doing more than one tasks often in time-constrained manner.

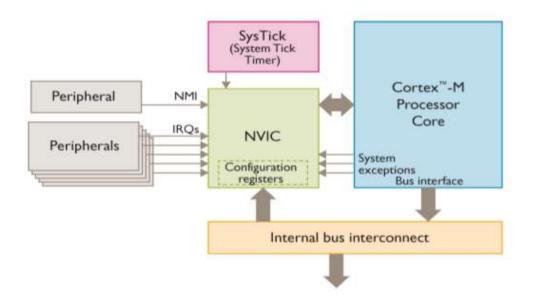

The arm microprocessor has Nested Vector Interrupt Controller(NVIC) that makes the task of handling/processing prioritising the different interrupts quiet an easy task that would have been quiet complicated if it was not for this feature of the microcontroller.

Interrupts are essentially kind of a hardware/software trigger that gets remembered as a flag that can be called to get the micro to perform a routine and return to its main function or its last operation before it was called.

Interrupts are an essential feature of a microcontroller that enables the software to respond in a controlled manner to internal/external hardware and software events. Interrupts were used extensively in this thesis for example in the GPS module for the transmission and reception of serial data via the uart.

Using interrupts requires that one understands how the central processor processes an interrupt so that we write code to handle them effectively.

#### 2.6.1 Exceptions

Exceptions are events that occur that intentionally or intentionally cause changes to the program routine. When an exception occurs the central processor suspends executing the current task and executes part of the program called the exception handler. When exception handler completed, the processor returns to the normal operation. An interrupt is a type of exception.

#### 2.6.2 Using Interrupts in Arm Microprocessor

In order to enable a specific interrupt separate bit or flag needs to be, e.g. RIE (The UART Receive Interrupt Enable bit). The hardware sets the flag bit when it wants to receive an interrupt. The software must clear the flag bit when it has handled the interrupt and allow the device to trigger an interrupt.

There are number of special registers in the microcontroller processor that contain the processor status and defines the operation states and interrupt/exception masking. These special registers are not memory mapped. There are specially defined registers that enables or disable all armed interrupts according to the PRIMASK bit (visualgdb.com n.d). Interrupt Polling

Some interrupts share the same interrupt vector like the receive and transmit routines of the UART. In this case, the software routine i.e. The ISR is responsible for polling the status flags to see which event has triggered the interrupt. Handling interrupt routines can very intricate, very close attention should be payed to the data sheet and app notes that are available.

## 2.6.3 Nested Vector Interrupt Controller

All Arm Cortex processor provide a Nested Vectored Interrupt Controller (NVIC) for handling interrupts. The NVIC receives interrupts and exception requests from various sources. In order to set up interrupts effectively proper understanding of the datasheet and application notes is necessary. But having said that it quiet self- explanatory and easy to implement because the nested vector controller takes care of most arbitration and conflicts of the different interrupts. What needs to be properly implemented is the priorities of the IRQs.

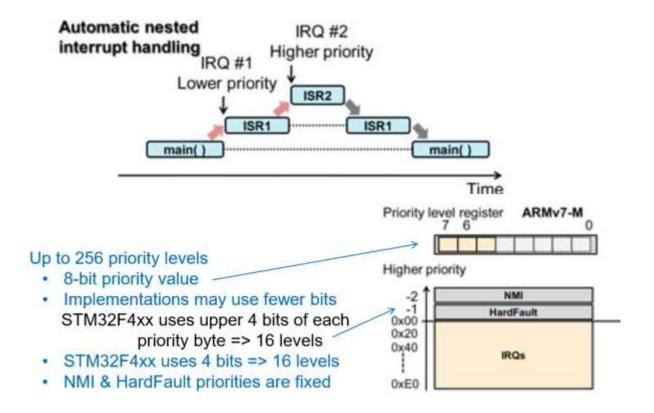

The NVIC forms integral part of all Cortex-M processors and provides the processors' outstanding interrupt handling abilities. NVIC is integral in this this design because of the number of peripherals are interfaced to the microcontroller. NVIC supports numerous interrupts up to 32 IRQ in some ARM devices (www.st.com n.d). Depicted below is a Visual Architecture of the NVIC in relation to other core parts of the Stm32f microcontroller.

Figure 2.3 Architecture of NVIC

Most of the NVIC settings are programmable. The configuration registers are part of the memory map and can be accessed as C pointers. There are also numerous libraries including the standard peripheral libraries from ST Microelectronics that are available to be used when setting up the NVIC. Using the standard peripheral libraries of the Stm 32f4 device makes configuring the Asset tracking device quiet simple using *Structs* types in the c language. So all we do is use an instance of the structure that is defined in the standard peripheral library obviously after including the necessary file in the start-up code. Inside the NVIC, each interrupt source is assigned an interrupt priority. A few of the system exceptions like such as NMI haves a fixed priority level, and others have programmable priority levels. By assigning different priorities to each interrupt, the NVIC can support Nested Interrupts automatically without any software intervention.

Figure 2.4 Graphical explanation of handling of Priority Levels in STM32 Controller

The architecture provides 8-bits of priority level settings for each programmable interrupt or exception.

The Stm32f4 uses a stack based exception model which essentially means that when an event and or exception occurs that a number of registers are pushed onto the Stack. These

Register are restored to their original values after the exception handler finishes. This feature allows exception to be written as normal c functions, and reduce processor overhead in terms of interrupt processing.

In addition, the Cortex-M processors use a vector table that contains the address of the function to be executed for each particular interrupt handler. On accepting an interrupt, the processor fetches the address from the vector table. Again, this avoids software overhead and reduces interrupt latency.

| Memory<br>Address | Vectors             | Exception<br>Number |

|-------------------|---------------------|---------------------|

| 0x0000_03FC       | IRQ #239            | 255                 |

|                   | :                   |                     |

| 0x0000_0048       | IRQ #2              | 18                  |

| 0x0000_0044       | IRQ #1              | 17                  |

| 0x0000_0040       | IRQ #0              | 16                  |

| 0x0000_003C       | SysTick             | 15                  |

| 0x0000_0038       | PendSV              | 14                  |

| 0x0000_0034       | Reserved            | 13                  |

| 0x0000_0030       | Debug Monitor       | 12                  |

| 0x0000_002C       | SVC                 | 11                  |

| 0x0000_0028       | Reserved            | 10                  |

| 0x0000_0024       | Reserved            | 9                   |

| 0x0000_0020       | Reserved            | 8                   |

| 0x0000_001C       | Reserved            | 7                   |

| 0x0000_0018       | Usage Fault         | 6                   |

| 0x0000_0014       | Bus Fault           | 5                   |

| 0x0000_0010       | MemManage Fault     | 4                   |

| 0x0000_000C       | HardFault           | 3                   |

| 0x0000_0008       | NMI                 | 2                   |

| 0x0000_0004       | Reset               | 1                   |

| 0x000_0000        | Initial value of SP | 0                   |

# Figure 2.5 Example of Vector Table

Various optimization techniques are also used in the Cortex-M processor implementations to make interrupt processing more efficient and make the system more responsive:

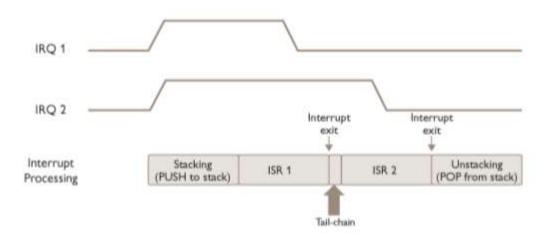

**Tail chaining** – can be explained simply if there is another exception pending when an ISR exits, the processor does not restore all saved registers from the stack and instead moves on to the next ISR. This reduces the latency when switching from one exception handler to another. In a high speed data acquisition environment this can be a very useful feature of the NVIC it allows processes to seem real time.

• NVIC can halt stacking (and remember its place) if a new IRQ is received.

#### Figure 2.6 Timing Diagram Illustrating of the principle of Tail-chaining

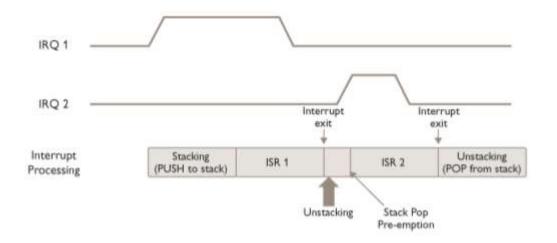

**Stack pop pre-emption** –Another optimisation technique used in interrupt handing of the NVIC is Stack pop pre-emption. If during the andling of an event another exception occurs during the unstacking process of an exception, the processor abandons the stack Pop and services the new interrupt immediately. By pre-empting and switching to the second interrupt without completing the state restore and save, the NVIC achieves lower latency in a deterministic manner which simply means the NVIC takes controll of the time taken to handle and optimise both interrupts. (Github.com, n.d)

#### Figure 2.7 Timing Diagram Illustrating of the principle of Stack-Pop Pre-Emption

In the Arm cortex microprocessors there are 2 different kinds of priorities: this feature handles arbitration of interrupts and can be very useful when tasks have to be executed with very low latency; the two of priorities is preemption priorities and sub priorities

Events that have the same preemption priority will look to the sub priorities for arbitration decision which means then that one with the high sub priority will be executed first. If they then have the same sub priority then the first come first served rule will be used as the arbitration decision. The default rule is that the event with highest preemption priority will always be executed first. This arbitration capability of the arm processor is fundamental in this design because of the number of different peripherals and events there is for processing data. It is important that there is no ambiguity in terms of priority because that could lead to increased latency or complete failure with regard to handling the interrupt.

Previous generation 8- bit microcontrollers did not have Nested Vector Interrupt controller which are now introduced in the Arm micro-processer. This innovated feature has gained the respect and admiration of main embedded designers and makes handling multiple peripherals a breeze. In the past years it was always a challenge handling a large number of peripherals and processes asynchronously, there were arbitration techniques that had to be built into the code to handle conflict of two or more events. NVIC allows the code to much more efficient as there is a dedicated controller handling the interrupts. The processor can now be programmed to handle numerous and cumbersome tasks as the NVIC if programmed properly. It is however a steep learning curve that is well worth the effort of learning because of the numerous benefits it bring to an embedded designer.

## 2.7 Serial Peripheral Interface Protocol (SPI)

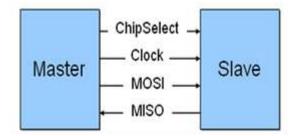

The Serial peripheral interface is an internal interface to the microcontroller that allows it to communicate with external devices.

A detailed a thorough understanding of the SPI protocol was necessary for this thesis; it was essential for the implementation of the biometric module. The grasp of the SPI concept is essential for any embedded systems designer. The SPI communication stands for serial peripheral interface communication protocol, which was developed by the Motorola in 1972. SPI is a hierarchical synchronous communication full duplex protocol amongst electronic devices which means that carries data signals in both directions. It also means that it uses separate lines for clock and separate lines for data so as keep both sides in synchrony.

There are four key pins that make up the SPI interface namely

– Clock, Miso, Mosi and chip selector – it manages to transfer data between two or more devices. As part of an SPI setup there is a master (usually a micro controller) and one or more slaves.

The Clock pin serves as a coordination mechanism; it tells the devices when to read/write data.

Chip Selector is used to inform the slave device that we want to exchange data, this is done by merely pulling the CS pin down. In a multi slave set up the devices share the same clock, MISO and MOSI lines but have their own independent chip selector. Mosi- As the Name suggest is Master in Slave Out (output pin) Miso- Is Master In Slave out (Input pin)

SPI protocol uses four wires named as MISO, MOSI, CLK, SS used for master/slave communication. The master is predominantly a microcontroller, and normally the slaves are other peripherals like sensors, GSM modem and GPS modem or like in this design a module like the nRf2401I module, etc. Multiple slaves are interfaced to the master through a SPI serial bus. The SPI protocol does not support the multi-master communication, and it is used for a short distance within a circuit board (Marwedel, 2010). There are four i/o signals associated with the SPI peripheral

## Figure 2.8 Serial Peripheral Interface

MISO (Master in Slave out): The MISO line is configured as the input in a master device and as an output in a slave device. Used to receive data from a slave device.

MOSI (Master out Slave in): The MOSI is a line configured as the output in a master device and as an input in a slave device wherein it is used to synchronize the data movement. This terminal is associated with receiving data from the master device.

SCK (Serial Clock): This signal is always driven by the master for synchronous data transfer between the master and the slave. It is used to synchronize the data movement both in and out through the MOSI and MISO lines.

SS (Slave Select) and CS (Chip Select): This signal is driven by the master to select individual slaves/Peripheral devices. It is an input line used to select the slave devices. Master Slave Communication with SPI Serial Bus. When this line is active then the SPI communication interface between the two devices is enabled and data exchange can begin.

The SPI protocol is implemented quiet extensively in the thesis and deserved a mention as it is the backbone of successful implementation of the Biometric Module. The STM32f4 serial peripheral interface offers various operating modes which makes it a high configurable interface which in turns requires a detail knowledge of the data sheet to implement correctly. It is a very useful interface and is used in many hardware interfaces like display panels, data acquisition chips to name a few.

## 2.8 Analogue to Digital Convertor (ADC)

An ADC is a peripheral that allows measuring the voltage (between 0 and  $V_{ref}$ ) on a certain configured input of the microcontroller. The basic principle of operation is that peripheral sample the digital input or value of the signal received at specific peripheral stores an array in the order it was received order for further processing with regard to voltage reference signal. The resolution of the analogue signals is the number of samples taken per cycle. ADC resolution is one of the key factors to determine how precise the conversion can achieve. If a chip has a resolution of 8-bit (0-255), meaning that it can detect 256 different levels of input analog signal. The stm32f4 microcontroller is being used has a 12-bit ADC, which increases the resolution of analog conversion to 4096 steps (from 0 to 4095). This resolution is configurable to 12-bit, 10-bit, 8-bit or 6-bit where faster conversion times can be obtained by lowering the resolution.

#### Figure 2.9 ADC showing 3-Bit resolution and 16-bit resolution Signal [30]

The STM32F4 has a built-in Analogue to Digital converter.

## 2.8.1 The Implementation of the Multi-channel ADC Module

The basic principle of operation of the multichannel ADC Module is;

Firstly: required 5 unused GPIO ports to be configured as analogue inputs. These

ports will be reading the sensors that attached to these ports referenced to 3.3 Volts.

Most sensors on motor vehicles are normally 5v sensors which means the device will

need to do some level shifting.

- The ADC module on the microcontroller has to be configured for multichannel processing. See appendix A.

- Seeing that device will be using DMA to transfer the data from the ADC peripheral to the ADC Buffer. This will also be set up.. In this design the peripheral\_base\_address of the ADC is the Data register of the ADC the device is using. The memory address will be the array that is created to store the respective converted ADC values ConvertedAdcValue[].This array will be volatile as the values can change any given time and outside the code.

- So each index of the array will store one sensor value, the value of the sensor that the GPIO is reading. Each index of the ConvertedAdcValue will be copied to a static array and each index of that array will be stored as global variables for use in the code.

- E.g. int Vspd=ConvertedAdcValue[0];The static buffer created will be used in the serialization routine for transmission to the remote control centre. The variables created from this array will be used by the GSM state machine to control the various modes of transmission.

- The ADC Module will also responsible for determining the engine running hours that is necessary for asset management. The Ignition of the vehicle and Engine speed are the two parameters used to start the Running\_Hours function which is a counter: if(IGN>0&&Rpm>0)

```

{

Running_Hours();

}

```

# 2.9 OBD Module

# 2.9.1 Overview

The fundamental purpose of this design is to acquire data from a specific asset and present it in a desired format to remote collection service for storage as well as analytics. The asset in question is a modern motor vehicle.

Motor vehicles are no longer just a mechanical apparatus they have numerous electronic control units networked together.

Since 1996, most vehicles have been required by law to monitor their own emissions performance and to report on it through an On-Board Diagnostics port. This has lent us the

opportunity to able to retrieve this data and possibly analyse it but also to make decisions based on this data in terms of asset lifecycle management as well as asset optimisation. Before 2008, several different protocols were used as base protocol for transferring OBD data. All vehicles after 2008 have to be CAN compliant. Today's vehicles have many built- in computer systems that control parts of the car such as fuel injections, airbags or brakes. All of these systems are controlled by one of several Electronic Control Units (ECU), which communicate with each other over the internal high speed Controller Area Network (CAN) of the car.

In this chapter, we focus on the implementation of the OBD module on its own and it the next Chapter the CAN module on its own. The reason being their functional implementation in this thesis is different for the purpose of asset tracking and also they are fundamentally different technologies. As many of the vehicles that we are interested in monitoring will be vehicles prior to 2008 the OBD module is and essential module for the asset tracking device. 5.2 The OBD II Standard

The On-Board Diagnostics (OBD) can discover and diagnose problems with the data reported by the ECUs. If a problem occurs, the OBD system generates a trouble code that which makes it possible for a service engineer to identify and fix the problem. Trouble codes and other diagnostic information can be accessed by plugging an OBD scan tool into the OBD interface in the car. The main advantage with having an OBD system is that it makes it easier to diagnose faults that occur in the vehicle. An advantage from a sustainability point of view is that vehicle emissions can be reduced by discovering and fixing problems, that makes the vehicles emission levels rise, that otherwise might not have shown any noticeable symptoms to the user or service personnel. This design however will not be using the full functionality of the OBD system just the monitoring capability as the main purpose is to retrieve data that can impact asset lifecycle management. There is clearly numerous application for using the fault codes and engine management diagnostics capability of the OBD module but will not implemented in this design as this design is focussed on the tracking of specific asset data.

There are numerous end-user products for extracting OBD trouble codes from cars but these products are stand-alone with little to no user-based content around the faults and or monitoring. For the asset-tracking device, this will be monitoring pre-2008 vehicles and in some case specialised vehicles pre 1996.

On Board Diagnostics OBD is the computer system built into cars that monitors the performance of the engine components as well as other control units. It consists of several ECUs that uses various sensors to collect data and evaluate the performance of the car. The OBD module in this design will monitor various predefined data or PID's of the vehicle and

26

relay it to the control centre. There is how ever very few or no aftermarket implementation of remote monitoring real time obd data to a control centre

There is no available implementation of an OBD software library that can freely be used on an embedded system to communicate with the OBD system in a car and extract information.

The objective of this module is to develop a system that can monitor data present by the OBD system and make the information accessible to the asset manager.

OBD2 permits five different communication protocols, as listed in table 3-1, which can be used to communicate with the OBD2 interface. Most vehicle manufacturers only implement one of these protocols so it is often possible to identify the used communication protocol by looking at which pins are present on the connector.

- Standard Description

- SAE J1850 Pulse-Width Modulation (PWM)

SAE J1850 Variable Pulse Width (VPW)

- ISO 9141-2 Similar to RS232

- ISO 14230 Keyword Protocol 2000 (KWP2000)

- ISO 15765 CAN (250kbps or 500kbps)

#### 2.9.2 Research the OBD protocol

The main purpose of this design and thesis is to design an Asset Tracking device that will relay data to a control center. The asset in question is a modern motor vehicle. The modern motor vehicle is equipped with an obd network.