## OS-LEVEL ATTACKS AND DEFENSES: FROM SOFTWARE TO HARDWARE-BASED EXPLOITS

Dissertation zur Erlangung des akademischen Grades Doktor der Ingenieurswissenschaften (Dr.-Ing.) genehmigt durch den Fachbereich Informatik (FB 20) der Technischen Universität Darmstadt

# von DAVID GENS aus Wiesbaden, Deutschland

#### **Gutachter:**

Prof. Dr.-Ing. Ahmad-Reza Sadeghi (Erstreferent) Prof. Dr. Thorsten Holz (Zweitreferent)

Tag der Einreichung: 14. Dezember 2018 Tag der Disputation: 13. Februar 2019

CYSEC/System Security Lab

Intel Collaborative Research Institute (ICRI-CARS)

Fachbereich für Informatik

Technische Universität Darmstadt

Hochschulkennziffer: D17

OS-level Attacks and Defenses: from Software to Hardware-based Exploits © December 2018 by David Gens

#### PHD REFEREES:

Prof. Dr.-Ing. Ahmad-Reza Sadeghi ( $1^{st}$  PhD Referee) Prof. Dr. Thorsten Holz ( $2^{nd}$  PhD Referee)

#### FURTHER PHD COMMISSION MEMBERS:

Prof. Dr. Sebastian Faust Prof. Dr. Guido Salvaneschi Prof. Dr.-Ing. Thomas Schneider

Darmstadt, Germany December 2018

Veröffentlichung unter CC-BY-SA 4.0 International https://creativecommons.org/licenses/

Run-time attacks have plagued computer systems for more than three decades, with control-flow hijacking attacks such as return-oriented programming representing the long-standing state-of-the-art in memory-corruption based exploits. These attacks exploit memory-corruption vulnerabilities in widely deployed software, e.g., through malicious inputs, to gain full control over the platform remotely at run time, and many defenses have been proposed and thoroughly studied in the past. Among those defenses, control-flow integrity emerged as a powerful and effective protection against code-reuse attacks in practice. As a result, we now start to see attackers shifting their focus towards novel techniques through a number of increasingly sophisticated attacks that combine software and hardware vulnerabilities to construct successful exploits. These emerging attacks have a high impact on computer security, since they completely bypass existing defenses that assume either hardware or software adversaries. For instance, they leverage physical effects to provoke hardware faults or force the system into transient micro-architectural states. This enables adversaries to exploit hardware vulnerabilities from software without requiring physical presence or software bugs.

In this dissertation, we explore the real-world threat of hardware and softwarebased run-time attacks against operating systems. While memory-corruption-based exploits have been studied for more than three decades, we show that data-only attacks can completely bypass state-of-the-art defenses such as Control-Flow Integrity which are also deployed in practice. Additionally, hardware vulnerabilities such as Rowhammer, CLKScrew, and Meltdown enable sophisticated adversaries to exploit the system remotely at run time without requiring any memorycorruption vulnerabilities in the system's software. We develop novel design strategies to defend the OS against hardware-based attacks such as Rowhammer and Meltdown to tackle the limitations of existing defenses. First, we present two novel data-only attacks that completely break current code-reuse defenses deployed in real-world software and propose a randomization-based defense against such dataonly attacks in the kernel. Second, we introduce a compiler-based framework to automatically uncover memory-corruption vulnerabilities in real-world kernel code. Third, we demonstrate the threat of Rowhammer-based attacks in securitysensitive applications and how to enable a partitioning policy in the system's physical memory allocator to effectively and efficiently defend against such attacks. We demonstrate feasibility and real-world performance through our prototype for the popular and widely used Linux kernel. Finally, we develop a side-channel defense to eliminate Meltdown-style cache attacks by strictly isolating the address space of kernel and user memory.

Softwarebasierte Laufzeitangriffe stellen Rechnerplattformen seit mehr als drei Jahrzehnten vor große Sicherheitsprobleme. In Form weit verbreiteter Offensivtechniken wie Return-Oriented Programming, die Programmierfehler durch bösartige Eingaben gezielt ausnutzen, können Angreifer im Extremfall so die vollständige Kontrolle über die Plattform erlangen. Daher wurden über die Jahre eine Vielzahl von Defensivmaßnahmen wie Control-Flow Integrity und Fine-Grained Randomization vorgeschlagen und die Effektivität dieser Schutzmechanismen war lange Zeit Gegenstand intensiver Forschungsarbeit. In jüngster Zeit wurden jedoch eine Reihe zunehmend ausgefeilterer Angriffe auf Hardwareschwachstellen aus Software heraus vorgestellt, die bei Beibehaltung des Angreifersmodells zur kompletten Kompromittierung dieser Systeme führen können. Diese neuartige Entwicklung stellt bestehende Verteidigungen, die traditionelle Softwareangriffe annehmen, somit in der Praxis vor große Herausforderungen.

Diese Dissertation erforscht eine Reihe solcher neuartigen Angriffsszenarien, um die reale Bedrohung auf das Betriebssystem trotz bestehender Verteidigungsmechanismen abschätzen zu können. Insbesondere geht die Arbeit im ersten Teil auf die Problematik sogenannter Data-Only Angriffe im Kontext von Defensivmaßnahmen wie Control-Flow Integrity ein und demonstriert, wie diese unter Ausnutzung von Softwarefehlern vollständig ausgehebelt werden können. Der zweite Teil erforscht die Bedrohung von Laufzeitangriffen durch Hardwarefehler, auch in Abwesenheit von Softwarefehlern auf welche sich bisherige Verteidigungen beschränken. Um die bisherigen Problem in den vorhandenen Schutzmechanismen anzugehen wurden neue Designstrategien entwickelt, mit Hilfe derer sich das Betriebssystem vor solch weiterführenden Angriffen durch geeignete Maßnahmen in Software schützen kann. Zunächst demonstrieren wir eine randomisierungsbasierte Verteidigung gegen Data-Only Angriffe auf Seitentabellen. Des weiteren wird ein Framework zur automatisierten Identifikation von Softwarefehlern im Betriebssystem anhand des Quelltexts auf Basis des LLVM Compilers vorgestellt. Außerdem erforscht die Arbeit eine Absicherung des Betriebbsystems vor Seitenkanalangriffen durch geeignete Isolation des Addressraumes. Ferner entwickeln wir eine Schutzmaßnahme vor Rowhammer-basierten Angriffen auf das OS, indem der physische Speicherallokator des Systems um eine Partitionierungsstrategie erweitert wird.

First and foremost I would like to thank my thesis advisor Professor Ahmad-Reza Sadeghi for his excellent supervision and continuous support. I am grateful to have Professor Thorsten Holz as thesis co-advisor. I thank Professor Sebastian Faust, Professor Guido Salvaneschi, and Professor Thomas Schneider for being members of my thesis committee.

Additional thanks go to Professor Lucas Davi with whom I had the privilege to collaborate and work with while he was still based in Darmstadt and who offered me an initial position in his Junior Research Group funded by DFG's Emmy Noether program.

My research work and travels were funded in part by the Federal Ministry of Education and Research (BMBF) through SAL and by the DFG through CROSS-ING, both of which provided a great working environment and allowed me to collaborate with renowned and leading researchers from academia and industry worldwide.

Further, I thank all my co-authors besides Ahmad and Lucas: Orlando Arias, Ferdinand Brasser, Poulami Das, Ghada Dessouky, Lisa Eckey, Rolf Egert, Sebastian Faust, Marc Fischlin, Tommaso Frassetto, Jason M. Fung, Patrick Haney, Kristina Hostakova, Sven Jacob, Patrick Jauernig, Yier Jin, Arun Karthik Kanuparthi, Hareesh Khattri, Christopher Liebchen, Garrett Persyn, Jeyavijayan Rajendran, Simon Schmitt, Matthias Senker, Emmanuel Stapf, Dean Sullivan, Jörg Tillmans, and Shaza Zeitouni.

Thanks to all my colleagues of the System Security Lab at Technische Universität Darmstadt for fruitful and interesting technical discussion, as well as their help in organizing courses, and a great time.

Finally, I would like to thank my family and in particular my parents Monika and Andreas for their continuing encouragement. Special thanks to Miriam for her enduring sympathy, support, and friendship.

#### CONTENTS

| I  | INT   | RODUCTION                                                                          |

|----|-------|------------------------------------------------------------------------------------|

| 1  | OVE   | RVIEW 3                                                                            |

|    | 1.1   | Goals and Scope 5                                                                  |

|    | 1.2   | Summary of Contributions 5                                                         |

|    | 1.3   | Organization 7                                                                     |

|    |       | Publications 8                                                                     |

| 2  | •     | KGROUND 9                                                                          |

|    | 2.1   | Basic OS-level Defenses 9                                                          |

|    |       | 2.1.1 Privilege-Level Separation 9                                                 |

|    |       | 2.1.2 Virtual-Memory Protection 10                                                 |

|    | 2.2   | The Traditional Threat Models 11                                                   |

|    | 2.3   |                                                                                    |

|    | ,     | 2.3.1 Causes of Memory Corruption 12                                               |

|    |       | 2.3.2 A Model for Exploitation 13                                                  |

|    |       | 2.3.3 Typical Attack Workflow 14                                                   |

|    | 2.4   |                                                                                    |

|    |       | 2.4.1 Return-to-libc and Return-Oriented Programming 15                            |

|    |       | 2.4.2 Code-Reuse Defenses and Advanced Attacks 16                                  |

|    |       | 2.4.3 Data-only attacks 17                                                         |

|    | 2.5   | Modern Hardware Platforms 18                                                       |

|    |       | 2.5.1 Overall System Architecture 18                                               |

|    |       | 2.5.2 Processor Design Principles 19                                               |

|    |       | 2.5.3 Remote Hardware Exploits 21                                                  |

| тт | ) (T) | CORV. CORRESPONDE THE THREE OF PART ONLY ART OVER                                  |

| II |       | MORY CORRUPTION: THE THREAT OF DATA-ONLY ATTACKS                                   |

| 3  |       | ASSING CFI IN MODERN BROWSERS. 25                                                  |

|    | 3.1   | Data-Only Attacks on Dynamic Code Generation 25                                    |

|    | 3.2   | Assumptions and Threat Model 26                                                    |

|    | 3.3   |                                                                                    |

|    |       | ,                                                                                  |

|    |       | 3.3.2 Corrupting the Intermediate Representation 28                                |

|    | 2.4   | 3.3.3 Attack Framework 29 On the Prevalence of Data Only Attacks 20                |

|    | 3.4   | On the Prevalence of Data-Only Attacks 29 Possible Mitigations 30                  |

|    | 3.5   |                                                                                    |

| 4  |       | AKING AND FIXING CFI IN OS KERNELS. 31  OS Kornols as Targets of Data Only Attacks |

|    | 4.1   | OS Kernels as Targets of Data-Only Attacks Assumptions and Threat Model 31         |

|    | 4.2   | 1                                                                                  |

|    | 4.3   | Our Page Table Exploit 32 4.3.1 Attack Overview 32                                 |

|    |       |                                                                                    |

|    | 1 1   | DED 1 MGC C D CO1 AU 1 C CO1 D TE11                                                |

|    | 4.4   | - · · · · · · · · · · · · · · · · · · ·                                            |

|    |       | 4.4.1 Design and Overview 34                                                       |

|     |        | 4.4.2 Challenges 36                                            |  |  |  |  |  |

|-----|--------|----------------------------------------------------------------|--|--|--|--|--|

|     | 4.5    | Implementation 37                                              |  |  |  |  |  |

|     |        | 4.5.1 Page Table Allocations 37                                |  |  |  |  |  |

|     |        | 4.5.2 Generating a Randomized Area 39                          |  |  |  |  |  |

|     |        | 4.5.3 Page Table References 39                                 |  |  |  |  |  |

|     |        | 4.5.4 Handling of the one-to-one mapping 40                    |  |  |  |  |  |

|     |        | 4.5.5 Translation of Physical Addresses 40                     |  |  |  |  |  |

|     | 4.6    |                                                                |  |  |  |  |  |

|     | 4.0    | 4.6.1 Methodology 41                                           |  |  |  |  |  |

|     |        | 4.6.2 Leakage Resilience and Randomization Entropy 41          |  |  |  |  |  |

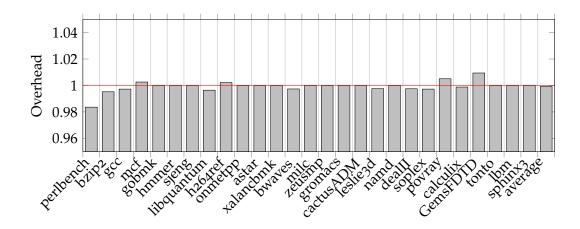

|     |        | 4.6.3 Performance 42                                           |  |  |  |  |  |

|     |        |                                                                |  |  |  |  |  |

| _   | A T.T. |                                                                |  |  |  |  |  |

| 5   |        | OMATICALLY UNCOVERING MEMORY CORRUPTION IN KERNEL CODE. 47     |  |  |  |  |  |

|     | 5.1    | Run-time defenses vs. compile-time verification 47             |  |  |  |  |  |

|     | -      | Data-Flow Analysis 48                                          |  |  |  |  |  |

|     |        | Problem Description 50                                         |  |  |  |  |  |

|     | 5.4    | Design of K-Miner 50                                           |  |  |  |  |  |

|     |        | 5.4.1 Goals and assumptions 51                                 |  |  |  |  |  |

|     |        | 5.4.2 Overview 51                                              |  |  |  |  |  |

|     |        | 5.4.3 Uncovering Memory Corruption 52                          |  |  |  |  |  |

|     |        | 5.4.4 Challenges 53                                            |  |  |  |  |  |

|     | 5.5    | Implementation 54                                              |  |  |  |  |  |

|     |        | 5.5.1 Global Analysis Context 55                               |  |  |  |  |  |

|     |        | 5.5.2 Analyzing Kernel Code Per System Call 56                 |  |  |  |  |  |

|     |        | 5.5.3 Minimizing False Positives 57                            |  |  |  |  |  |

|     |        | 5.5.4 Efficiently Combining Multiple Analyses 58               |  |  |  |  |  |

|     | 5.6    | Evaluation 59                                                  |  |  |  |  |  |

|     |        | 5.6.1 Security 59                                              |  |  |  |  |  |

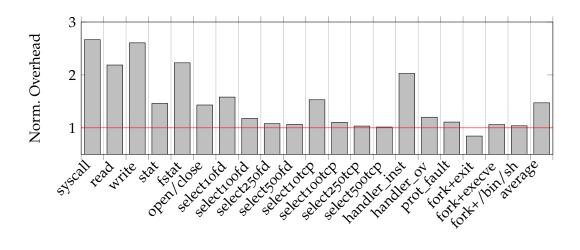

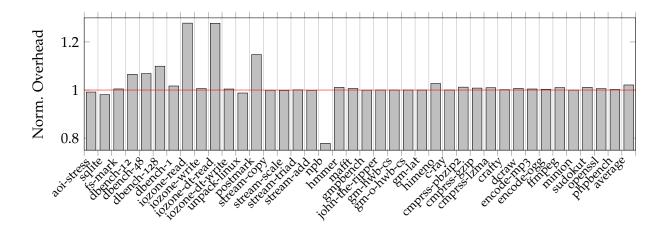

|     |        | 5.6.2 Performance 61                                           |  |  |  |  |  |

|     |        | 5.6.3 Usability 62                                             |  |  |  |  |  |

|     | 5.7    | Possible Extensions 64                                         |  |  |  |  |  |

| 6   | REL    | ATED WORK 67                                                   |  |  |  |  |  |

|     | 6.1    | Data-only Attacks and Defenses for Static Code 67              |  |  |  |  |  |

|     | 6.2    | Data-only attacks and defenses for JIT code 68                 |  |  |  |  |  |

|     | 6.3    | Kernel and Page Table Protection 69                            |  |  |  |  |  |

|     | 6.4    | Static Analysis Frameworks 71                                  |  |  |  |  |  |

|     |        | 6.4.1 Kernel Static Analysis Frameworks 71                     |  |  |  |  |  |

|     |        | 6.4.2 User Space Static Analysis 72                            |  |  |  |  |  |

|     |        |                                                                |  |  |  |  |  |

| III | REM    | IOTE HARDWARE EXPLOITS: AN EMERGING ATTACK PARADIGM            |  |  |  |  |  |

| 7   | HAN    | MMER TIME: REMOTE ATTACKS ON DRAM AND INITIAL DEFENSES. 77     |  |  |  |  |  |

|     | 7.1    | DRAM and the Rowhammer Bug 77                                  |  |  |  |  |  |

|     | 7.2    | Rowhammer in the Context of Security-sensitive Applications 78 |  |  |  |  |  |

|     | 7.3    | Rowhammer as an Exploit Primitive 80                           |  |  |  |  |  |

|     | 7.4    | On the Distribution of Bit Flips 82                            |  |  |  |  |  |

|     | 7·5    | Initial Rowhammer Defense 83                                   |  |  |  |  |  |

| 8   |        | IGATING ROWHAMMER ATTACKS AGAINST OS KERNELS. 85               |  |  |  |  |  |

xi

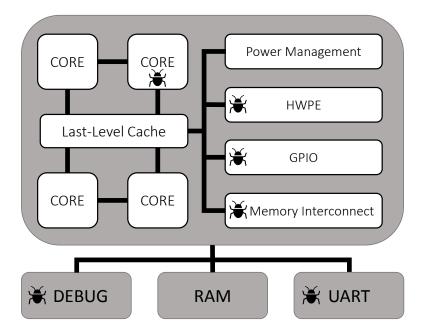

10.1 Hardware Vulnerabilities from a Software Perspective

10.1.2 Quality Assurance Techniques for Hardware

118

10.1.1 The Origin of the Hardware Bug

10.3 Exploiting Hardware Bugs From Software 10.3.1 Threat Model and Assumptions

10.2 Assessing the state-of-the-art

```

10.3.2 Attack Details

121

11 RELATED WORK

125

11.1 Rowhammer

125

11.1.1 Attacks 125

11.1.2 Defenses

126

11.2 Side-channel attacks against the OS

11.2.1 Paging-based Side-channel Attacks on KASLR 127

11.2.2 Software Mitigations

128

11.2.3 Hardware Mitigations

11.3 Recent Hardware Exploits

IV discussion and conclusion

12 DISSERTATION SUMMARY

13 FUTURE WORK

V APPENDIX

A ABOUT THE AUTHOR

141

B LIST OF FIGURES

145

C LIST OF TABLES

149

BIBLIOGRAPHY

151

```

## Part I INTRODUCTION

OVERVIEW

Computer systems are an integral part of our society. We leverage these systems in controlling large parts of our infrastructure, such as the transportation networks and energy grids. We use computers on a daily basis to communicate with friends and family, and consume, create, and publish media. Today, we even entrust those systems with handling the financial markets and aiding in our democratic processes. Consequently, computing platforms represent an extremely valuable target for adversaries. At the same time computer systems are also highly diverse, ranging from embedded devices and sensors in planes and cars, to smart phones, laptops, desktop computers, and powerful servers running the cloud. To manage this broad array of hardware and abstract the underlying complexity, the Operating System (OS) provides application developers with a software interface for user-space programs. The OS is typically considered part of the system's trusted computing base (TCB) [8], and usually runs with elevated privileges to protect the platform from malicious software. To achieve this, the OS enforces strict isolation policies for user programs utilizing dedicated security mechanisms that are provided by the hardware.

However, modern platforms execute a large number of applications and many of these programs are written in low-level languages, which do not provide any memory safety guarantees in the case of an error. This means that bugs in such pieces of software leave computer systems vulnerable to run-time attacks based on memory corruption, e.g., through maliciously crafted inputs. In practice, this allows attackers to overwrite code pointers that are stored in unprotected memory, such as the stack or the heap of the program. One of the earliest examples for such a vulnerability is the *buffer overflow* [9]: many programs use buffers to temporarily store user-provided input such as a string of text characters in memory. If the software developer forgot to properly check the length of the input, a user can overflow this buffer by providing an input that exceeds the originally defined size of the storage. This allows an adversary to corrupt parts of the program memory that are located beyond the storage of the buffer. For instance, by writing beyond the boundaries of a stack buffer an adversary can overwrite code pointers such as return addresses, which are typically stored on the stack as well. This enables the attacker to hijack the control flow of the program and execute code that was not originally intended by the developer in a code-reuse attack. In this way, an adversary can in principle achieve arbitrary behavior at run time [10].

Stack-based buffer overflows are one example of a bug class that allows memory corruption. They are part of a much larger family of vulnerabilities that further include heap-based errors, format string vulnerabilities, type confusion, uninitialized data usage, use-after-free and double-free errors, dangling pointers, synchronization errors, and integer overflows [11, 12]. These *memory-corruption vulnerabilities* are introduced due to human error in low-level software code, such as mis-

takes in memory management or missing corner cases in manually crafted checks. Memory-corruption vulnerabilities allow adversaries to subvert and take control of the affected program through malicious inputs, and hence, continue to pose severe threats for the security of real-world software [13–19].

For this reason, operating systems treat applications as *untrusted* and the kernel is designed to act as a *reference monitor* [20, 21] for user processes. The OS mediates all accesses of application software and enforces a strict separation of privileges to protect the platform. To implement this isolation efficiently and achieve a strong policy enforcement, the OS usually leverages dedicated hardware mechanisms such as virtual memory and privilege separation. However, for legacy and performance reasons all major operating systems are written in low-level programming languages that leave the system vulnerable to memory corruption in case of an error. This means, that a user-space adversary who gained access to the platform through a vulnerable application can target bugs in OS kernel code in a second step, e.g., by launching attacks against memory-corruption vulnerabilities in system calls or drivers in low-level OS code [22–26].

Such multi-staged attacks are increasingly common in practice, as many examples demonstrate the severe impact of memory-corruption vulnerabilities in large and complex code bases of major OS kernels: in 2016 Dirty CoW [27] was discovered to be a widely exploited bug in the Linux kernel that also affected all Android-based phones [28]. In 2017 Project Zero demonstrated a kernel exploit for iOS based on a double-free bug in Apple's Mach kernel [29]. Every year we are seeing memory-corruption-based exploits across all vendors and platforms that affect billions of devices [30-39]. This is why a great amount of time and effort has been invested over the recent years to systematically develop efficient mitigations and analyze their effectiveness, with Control-Flow Integrity [40-45], Code-Pointer Integrity [46], and various randomization-based schemes [46–56] representing the current state-of-the-art in defenses. In particular, CFI enforces the control flow of a program by matching the execution against an explicitly defined set of allowed code locations at run time to mitigate code-reuse attacks. Since CFI offers formal security guarantees while incurring only modest performance overheads, it is now in the process of being widely adopted in practice, e.g., through compiler extensions [57, 58], kernel patches [43–45], and hardware support [42, 59–61].

However, all of these defenses assume conventional software attacks in their threat models and software-based defenses implicitly assume the underlying hardware, particularly the processor and the main memory, to be trustworthy. This assumption is now being challenged, as researchers are discovering serious and foundational security vulnerabilities at the hardware level, such as vulnerabilities in memory or processor chips. Indeed, we are witnessing an unexpected shift in the traditional attack paradigms through hardware-based exploits. In this emerging threat the attacker exploits a vulnerability at the hardware level by triggering it from software at run time. Various hardware bugs have been shown to affect a wide range of platforms, manufacturers, and vendors, and a number of real-world exploits have been demonstrated recently [62–67]. So far, state-of-the-art defenses are entirely oblivious to hardware vulnerabilities, and hence, completely bypassed by these upcoming techniques. As a result, there currently exists a protection gap in practice, leaving operating systems vulnerable to remote attacks on hardware.

#### 1.1 GOALS AND SCOPE

The main goals of this dissertation are (1) revisiting state-of-the-art defenses with respect to their assumption that mitigating control-flow hijacking solves the problem of memory-corruption-based exploits, and (2) exploring cross-layer attacks in the form of remote hardware exploits, introducing novel design strategies to defend against these profound attacks in practice.

Due to the advances in effectiveness and deployment of defenses such as CFI, an increasing number of exploits aim at attacking the data of applications or the OS rather than their control flows. While control-flow hijacking was shown to give rise to a general and powerful attack framework granting the attacker Turing-complete computational capabilities [10], no analogous construction has been found for data-only attacks, since data accesses heavily depend on the structure of the target program [68]. As we will discuss in the first part of this dissertation the extensive focus of the related work in this area towards the computational capabilities of attack techniques might be to no avail. In practice, adversaries do not require arbitrary computation as part of individual attacks but rather achieve their goals through a multi-step approach, i.e., by initially compromising an application, and then escalating privileges, or leaking sensitive information such as the administrator password the attacker can successfully gain full control over the platform. None of these steps require Turing-complete computation.

Further, we can already see that adversaries are moving from attacking software vulnerabilities towards exploiting hardware vulnerabilities remotely from software—marking a shift in the traditional attack paradigms and threat models that raises a number of significant challenges for existing defenses. Thus, in the second part of this dissertation we explore emerging attacks and introduce novel design strategies to defend the OS in light of these evolving threats.

#### 1.2 SUMMARY OF CONTRIBUTIONS

The main contributions of this dissertation are as follows:

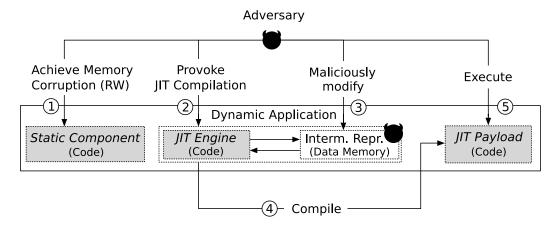

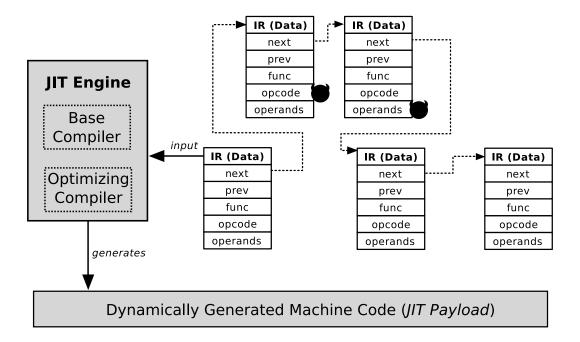

Bypassing CFI in Microsoft's Edge Browser. We demonstrate the power of data-only attacks, by constructing a Data-Only JIT Attack (DOJITA) [1] for Microsoft's Edge browser despite its deployed code-reuse defenses. In particular, we show that just-in-time (JIT) compilers can be tricked into generating arbitrary malicious payloads dynamically in a pure data-only attack by corrupting the intermediate representation in memory. Our attack works despite existing code-injection and code-reuse defenses being deployed and active in the JIT engine and browser.

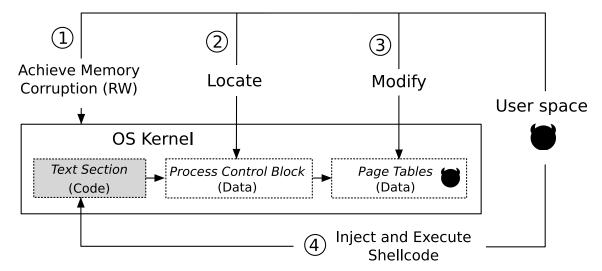

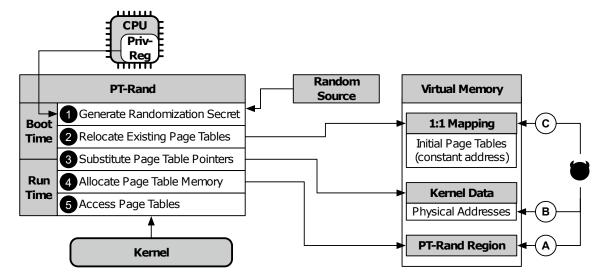

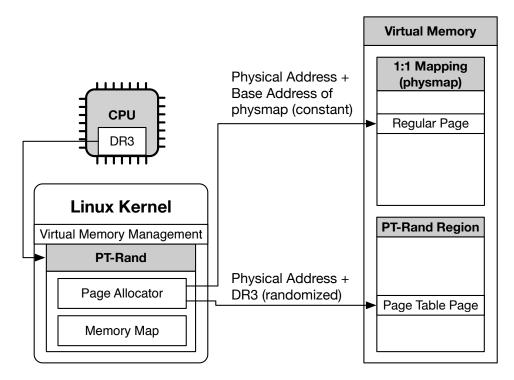

Breaking and Fixing CFI in the Kernel. By exploiting a vulnerability in kernel code, the attacker can escalate privileges in a second step, again only resorting to data-only attacks. In our work PT-Rand [2], we craft a page-table based attack that completely bypasses all existing defenses in the kernel. It exploits the fact that the kernel manages memory permissions dynamically at run time using data objects, which are called page tables. The attacker leverages the memory-corruption vulnerability to walk the page tables and maliciously modify memory access permissions, e.g., to make code pages writable in the kernel. Our exploit works despite code-injection and code-reuse defenses being deployed and active.

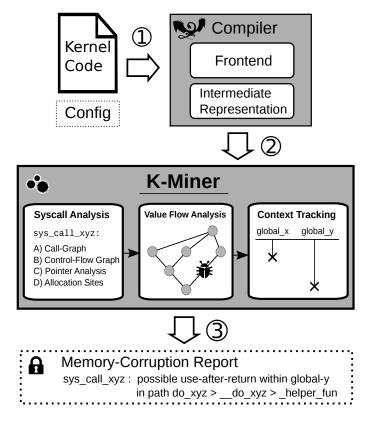

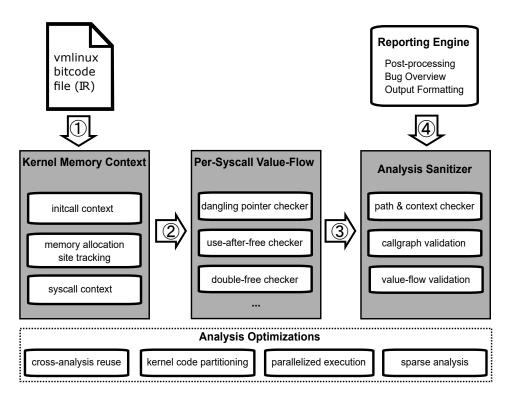

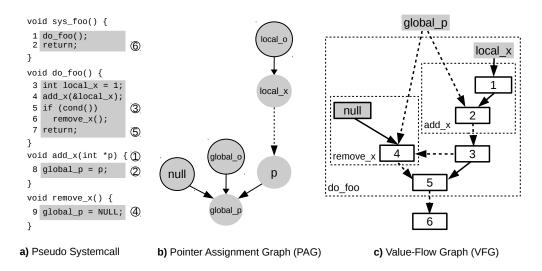

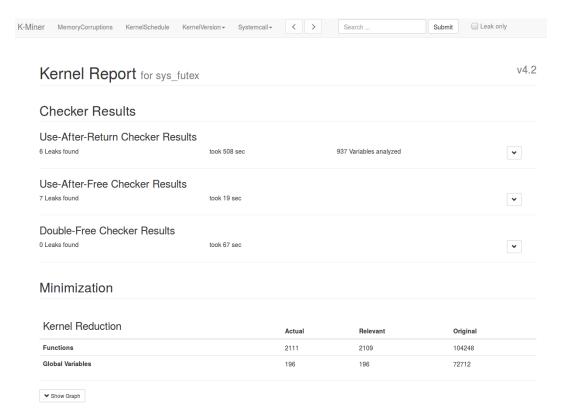

Automatically Uncovering Memory Corruption in Linux. In our work K-Miner [3], we conclude that software-based memory corruption still poses a significant threat and propose the first data-flow analysis framework for the kernel to identify any causes of memory corruption statically in the code and enable fixing vulnerabilities before they are deployed. K-Miner is able to analyze recent Linux kernels completely automatically and was used to uncover real-world vulnerabilities. Our prototype framework implementation builds on top of the popular open-source LLVM compiler and is available online [69]. K-Miner already sparked significant interest from the community and is actively used in follow-up publications [70].

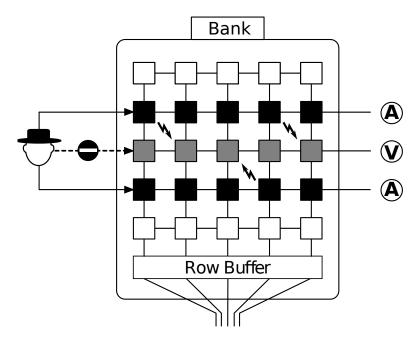

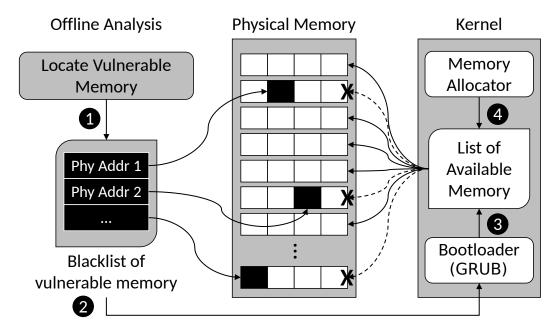

Attacking DRAM hardware from Software. Today, Dynamic Random Access Memory (DRAM) represents the standard choice for practically all computer systems due to cheap prices and widespread availability. However, several independent studies found that frequently accessing physically co-located memory cells in DRAM chips leads to bit flips in adjacent cells [63, 71], an effect called *Rowhammer*. In our work Hammer Time [4] we demonstrate that these software-based fault-injection attacks pose significant security challenges for security-sensitive applications, and we present an initial blacklisting-based defense [5], which leverages the fact that reproducible bit flips tend to cluster around characteristic areas for a given memory module. We demonstrate that this simple strategy can be implemented in a straightforward and OS-independent way in the boot loader.

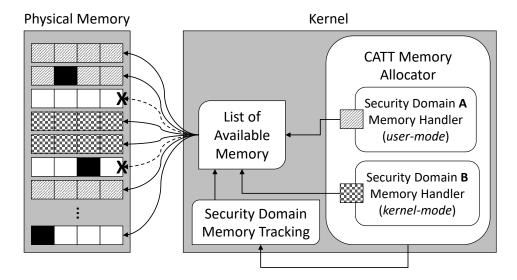

Practical Software-only Defenses against Rowhammer. Since DRAM chips represent the basic hardware building blocks for main memory on most platforms, Rowhammer represents a general threat to many computer systems. This was also demonstrated through a number of attacks [72-74] even in the remote setting [75-77] to completely break the security guarantees provided by existing software defenses. In particular, these attacks demonstrate that an adversary can allocate memory locations that are physically adjacent to kernel memory on the DRAM chips and subsequently influence the contents of privileged memory cells by exploiting the Rowhammer effect. Since the security of our initial bootloader-based defense approach relies on the quality of the blacklist, we designed a generic softwareonly defense, called CATT [5], which does not require any information about the distribution of bit flips and can be implemented through a patch to the physical memory allocator in the OS kernel. The basic idea underlying our defense is to partition physical memory into a privileged and an unprivileged zone. In this way we prevent allocation of adjacent rows that belong to different security domains such as the kernel and userland. We evaluated our prototype on a number of test systems and were able to show that it successfully prevents real-world Rowhammer attacks efficiently.

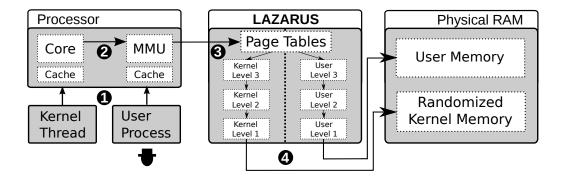

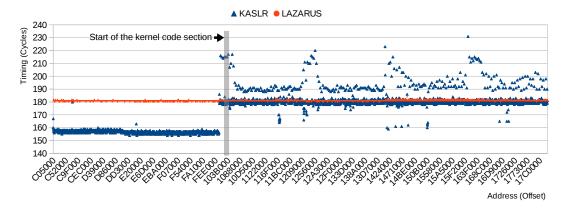

**Sidechannel-resilient Kernel-Space Randomization.** Even if software-based memory corruption is excluded from the threat model (e.g., because the OS is formally verified [78, 79]), software-exploitable hardware bugs are becoming an increasingly relevant problem. One example are vulnerabilities in the hardware design, for instance, shared caches in the processor can leak information between privileged and unprivileged software and were previously demonstrated to be able to break randomization-based defenses such as KASLR [80–83]. In our work LAZARUS [6] we design and implement a patch for the low-level address space switching mechanism in the OS to protect randomization-based defenses in the kernel against such

micro-architectural sidechannels. Interestingly, a processor vulnerability dubbed Meltdown [66] was discovered concurrently to our work, which exploits speculative execution to load arbitrary memory from an unprivileged process. Since the responsible disclosure process was ongoing at the time, we did not have prior knowledge of this vulnerability, yet, our design of LAZARUS mitigates the exploit by eliminating the side channel created by the shared address space between userland and OS. A similar strategy has since been adopted by all major operating systems to protect against this widespread hardware vulnerability [84].

Looking ahead on Software-exploitable Hardware Vulnerabilities. Since software-exploitable hardware vulnerabilities represent an emerging threat, we take a deep dive into micro-architectural security from a software perspective [7]. In joint work with experts from the semiconductor industry and academia we systematically review existing security-auditing tools for hardware and found fundamental limitations. In particular, existing methodologies fail to adequately model specific classes of vulnerabilities in hardware-description code and suffer from scalability problems in practice. Since all major processor designs are also highly proprietary this can result in bug classes slipping through even combinations of existing techniques. We demonstrate the feasibility of such vulnerabilities being exploitable from software using the popular open-source RISC-V architecture.

#### 1.3 ORGANIZATION

This dissertation is structured as follows. In Chapter 2 we provide comprehensive background on run-time attacks and defenses with a focus towards memorycorruption vulnerabilities and software-exploitable hardware vulnerabilities, which are an upcoming attack vector. Next, in Part II we present two data-only attacks on CFI. First, we demonstrate a novel attack that completely bypasses CFI in Microsoft's Edge browser in Chapter 3. Second, we show that CFI for the Linux kernel can be broken without modifying code pointers in an attack against the page tables. We also introduce our design and implementation of an efficient mitigation in Chapter 4. Third, we present a novel framework to statically analyze real-world kernel code at scale to automatically uncover memory-corruption vulnerabilities in Chapter 5. In Part III we then turn towards software-exploitable hardware vulnerabilities, which represent an emerging attack paradigm. First, we introduce a novel attack based on the infamous Rowhammer vulnerability in DRAM chips in Chapter 7. Second, we present the design and implementation of CATT, the first software-only defense that successfully stops Rowhammer-based attacks against kernel memory in Chapter 8. Next, we look at side-channel attacks on the kernel and present LAZARUS, our practical side-channel defense for the OS in Chapter 9. Lastly, we show that software-exploitable hardware vulnerabilities represent a growing problem by systematically reviewing state-of-the-art auditing approaches used by semiconductor companies to verify real-world SoCs in Chapter 10. We conclude this dissertation in Part IV.

#### 1.4 PUBLICATIONS

This dissertation is based on the following previous publications:

#### PART II: MEMORY CORRUPTION AND THE THREAT OF DATA-ONLY ATTACKS

#### [1] JITGuard: Hardening Just-in-time Compilers with SGX.

Tommaso Frassetto, David Gens, Christopher Liebchen, Ahmad-Reza Sadeghi. In 24th ACM Conference on Computer and Communications Security (CCS), November 2017 [Inproceedings].

#### [2] PT-Rand: Practical Mitigation of Data-only Attacks against Page Tables.

David Gens, Christopher Liebchen, Lucas Davi, Ahmad-Reza Sadeghi. In 24th Annual Network and Distributed System Security Symposium (NDSS), February 2017 [Inproceedings].

#### [3] K-Miner: Uncovering Memory Corruption in Linux.

David Gens, Simon Schmitt, Lucas Davi, Ahmad-Reza Sadeghi. In 25th Annual Network and Distributed System Security Symposium (NDSS), February 2018 [Inproceedings].

#### PART III: REMOTE HARDWARE EXPLOITS AS AN EMERGING ATTACK PARADIGM

[4] **It's Hammer Time: How to Attack (Rowhammer-based) DRAM-PUFs** Shaza Zeitouni, David Gens, and Ahmad-Reza Sadeghi. In 55th Design Automation Conference (DAC'18), June 2018 [Inproceedings].

## [5] CAn't Touch This: Software-only Mitigation against Rowhammer Attacks targeting Kernel Memory.

Ferdinand Brasser, David Gens, Christopher Liebchen, Lucas Davi, Ahmad-Reza Sadeghi. In 26th USENIX Security Symposium, August 2017 [Inproceedings].

#### [6] LAZARUS: Practical Side-channel Resilient Kernel-Space Randomization.

David Gens, Orlando Arias, Dean Sullivan, Christopher Liebchen, Yier Jin, Ahmad-Reza Sadeghi. In 20th International Symposium on Research in Attacks, Intrusions and Defenses (RAID), September 2017 [Inproceedings].

### [7] When a Patch is Not Enough — HardFails: Software-Exploitable Hardware Bugs.

Ghada Dessouky, David Gens, Patrick Haney, Garrett Persyn, Arun Karthik Kanuparthi, Hareesh Khattri, Jason M. Fung, Jeyavijayan Rajendran, Ahmad-Reza Sadeghi. [Technical Report].

In this chapter we first give a short overview of the traditionally deployed defense mechanisms and operating system security concepts vital to the understanding of this dissertation. We then introduce the notion of memory-corruption vulnerabilities, which underlie most software-based attacks against those traditional defenses and discuss advanced attacks and mitigations. Finally, we cover the high-level architecture of modern hardware platforms, including the most relevant components in the context of upcoming and emerging attack scenarios that exploit hardware vulnerabilities remotely from software.

#### 2.1 BASIC OS-LEVEL DEFENSES

As mentioned in Chapter 1 operating systems support a large number of applications running concurrently or time-shared on a single hardware platform. Since applications may be vulnerable to attacks, or even malicious in some cases, modern operating systems are designed as reference monitors and strictly separate access control and resource management from user processes [8, 20, 21]. Implementing this separation requires hardware support and modern processors provide two different isolation mechanisms in the form of *privilege separation* and *virtual memory*. We give a brief introduction into both mechanisms and explain how the OS leverages them to achieve strict isolation at run time.

#### 2.1.1 Privilege-Level Separation

OS kernel software normally runs with higher privileges than application software. Many processors support different privilege levels and allow software to switch between them at run time, e.g., via dedicated control-transfer instructions. Typically, there is an unprivileged level for executing applications and a privileged level that is reserved for the operating system. When the processor executes with the highest privilege level, the running software has complete access to any instructions, can directly access platform hardware, interact with debug and control registers of the platform, and consequently has full control over the system. Executing code within the unprivileged level only leaves a limited number of benign instructions available to software, for instance, it is usually only possible to load and store unprivileged memory or registers, calculate arithmetic operations, evaluate conditionals, and branch execution. At run time, the hardware maintains separate execution contexts for the different privilege levels and switching between privilege levels transparently invokes the respective context. For instance, when a user program crashes due to a benign operation, such as when dividing by zero, the processor automatically invokes the code in the highest privilege level (i.e., the operating system). The OS can then handle the error condition caused by the user program and terminate the application. User-level software can also purposefully

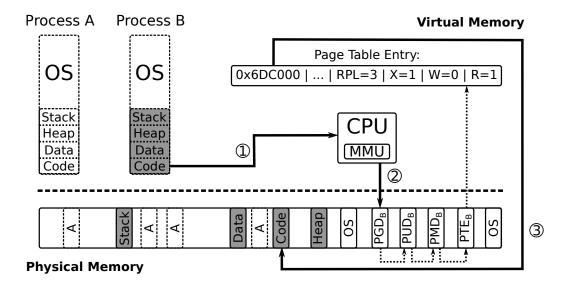

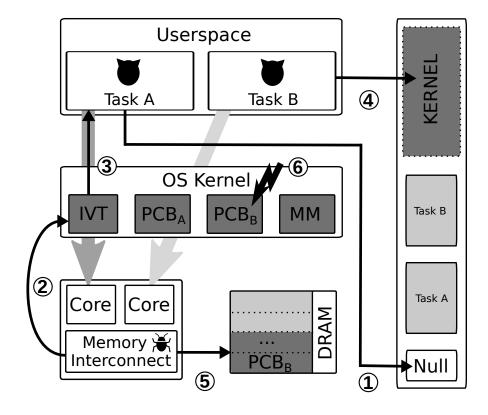

Figure 2.1: Virtual memory represents a page-based memory-protection scheme that can be enforced in hardware on many platforms.

invoke the OS. For example, if an application requires privileged access, such as opening a file stored on the platform's hard disk, it has to issue a request to the OS for accessing the disk and retrieving the file on its behalf. In this way the OS can mediate any accesses and enforce security policies. OS services are standardized in the form of *system calls* [85] and this interface represents one major part of the kernel's attack surface towards user-space software [86].<sup>1</sup>

#### 2.1.2 Virtual-Memory Protection

In addition to privilege separation, the OS usually also maintains a strict isolation of memory for application software. On many Central-Processing Units (CPUs), memory isolation is enforced by a dedicated piece of hardware called the memorymanagement unit (MMU), which is part of the processor (as depicted in Figure 2.1). If the MMU is disabled, all memory accesses from software operate directly on physical memory, which means that no memory isolation is enforced.<sup>2</sup> If the MMU is enabled by the OS, all memory accesses from software are interpreted as virtual addresses instead and every process is associated with its own virtual-address space. This indirection forces all accesses from software to be checked against a set of controls before any actual access to physical memory is allowed. These access control flags are stored in a hierarchical data structure, called the *page table*. In the example from Figure 2.1 Process B accesses a virtual address in Step (1) which is translated and checked by the MMU. Obtaining the access controls for the given virtual address requires a look-up in the page table in Step 2), which might involve several layers of indirection in physical memory. Therefore, this page walk is considered a costly operation and often optimized by the OS and the hardware in various

<sup>1</sup> Alongside the file system, drivers, and the network stack in monolithic kernels.

<sup>2</sup> This used to be a common mode of operation on old operating systems, such as Microsoft's Disk Operating System (MS-DOS).

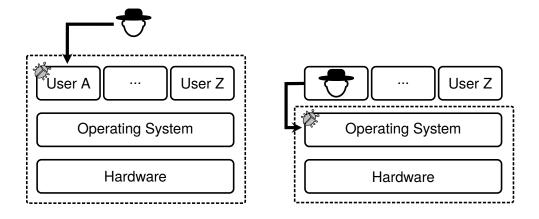

Figure 2.2: Today, many attacks involve multi-step exploits, in which the attacker successively migrates from a *remote* to a *local* adversary model to gain full control over the platform. Since the OS implements most of the security-relevant hardening techniques, attacks against kernel software in this second step are increasingly common in practice.

ways.<sup>3</sup> Once the page table entry for the given address is retrieved, the virtual address can be translated in Step ③ to the respective physical address, which can be interpreted directly by the memory bus of the platform. Alongside the physical address, the page-table entry stores access-control flags associated with the entry, such as Requested-Privilege Level (RPL), readable, writable, or executable. Depending on the nature of the access and the Current-Privilege Level (CPL) of the code that issued the access, the MMU will grant or deny that access. In case of a denied access the OS will be notified. When execution switches to Process A, another set of page tables will be loaded in the MMU. In general, this can result in entirely different access control policies as page tables of different processes can be kept completely independent. In this way, different parts of the main memory can be assigned to different processes exclusively. However, it is also possible to share memory between applications by mapping the same physical page within different address spaces or map it multiple times under different aliases within the same address space.

#### 2.2 THE TRADITIONAL THREAT MODELS

In combination, both mechanisms enable the OS to enforce strict isolation for application software at run time. The adversary models commonly considered in this setting can loosely be categorized into two variants, which are depicted in Figure 2.2.4 On the left-hand side we can see the *remote adversary* attacking the platform from the outside, e.g., through a network connection. In this case, the Trusted-Computing Base (TCB) of the system includes all user-space programs for which the attacker is able to provide some form of input. Many real-world scenarios can

<sup>3</sup> Since this aspect has important security implications we will in fact discuss it in greater detail in Section 2.5.2 and Chapter 9.

<sup>4</sup> Both cases usually exclude physical attacks (i.e., any techniques requiring physical presence), since this imposes additional, strong requirements on an adversary.

be modeled in this way. For instance, the attacker could have access to a shared file storage on the local network, or there might be a webserver running on the target system that the attacker can connect to via the internet. If the respective server program contains a vulnerability, an adversary can leverage this to exploit the server and achieve some initial control over the victim machine in the remote setting. In some cases, the attacker might want to extract information, or the goal could be modifying the webserver's configuration. In other cases, an adversary might utilize the compromised process to attack other parts of the system or even compromise other machines. The right-hand side shows the model for a local adversary, which assumes that the attacker already controls a user process on the victim machine. This means that the attacker can in principle execute arbitrary unprivileged code. However, most computer systems nowadays run hundreds of processes in parallel, and hence, operating systems are designed to consider user processes as untrusted and potentially malicious a priori. To this end, most major operating systems employ various hardening techniques, such as mandatory-access control [87], sandboxing [88, 89], and address-space layout randomization [90] by default. In practice, we can see that attacks against the kernel as a subsequent step are gaining more and more relevance for several reasons: first, the kernel executes with higher privileges, often allowing the attacker to gain full control over the machine based on a single kernel exploit. Second, the OS implements a major part of the security hardening techniques mentioned above, and hence, obtaining a root process or escaping from sandboxes often requires a kernel compromise. Consequently, many real-world attacks involve a multi-step approach in which the attacker starts out in the remote setting and successively migrates to the local setting by first acquiring code execution in user space and subsequently attacking the OS. Indeed, the OS has become a high-value target in the recent past as kernel exploits are leveraged in all of the latest Android root exploits [37-39, 91] and iOS jailbreaks [92], application sandbox escapes [23], and even large-scale attacks against industrial control systems [24].

#### 2.3 MEMORY-CORRUPTION ATTACKS

In this section, we explain why run-time attacks based on *memory corruption* pose a number of difficult challenges for these basic defenses under the traditional threat models. First, we give a quick introduction into the underlying root causes of software-based memory corruption. Second, we provide an abstract model and definition of what constitutes a memory-corruption exploit. Third, we give a simple real-world example of a typical exploitation workflow.

#### 2.3.1 Causes of Memory Corruption

The problem of memory corruption has proven uniquely challenging from a security perspective. In part, this is due to the fact that memory corruption is closely tied to the way in which we specify program behavior using low-level languages like C. Normally, the developer specifies the intended behavior of the program in the code and a compiler then translates this high-level human-readable description into machine code which can be executed directly by the processor. However,

these languages explicitly allow for undefined behavior, i.e., programs which do not adhere to a strict set of technical specifications defined in the language standard are allowed to exhibit any behavior at run time. A popularly exercised example states that a program exhibiting undefined behavior could format the user's hard drive in full accordance with the standard. While in reality, accidentally formatted hard drives do not rank among the most frequently reported programming bugs<sup>5</sup>, undefined behavior can have severe consequences for the system that executes the program. In theory, any program that is written in an unsafe language could contain a memory-corruption vulnerability. Unfortunately, empirical evidence from almost 40 years shows that a large part of real-world software is prone to such bugs over time: memory-corruption vulnerabilities are a wide-spread problem and occur frequently in deployed code [13-19]. Even worse, patches that fix a number of older bugs may also introduce new bugs [11, 12]. Indeed, memory-corruption vulnerabilities represent a vast number of security-relevant bugs for modern software written in low-level languages [98, 99], which can be exploited by adversaries, e.g., to obtain remote code execution or elevated privileges at run time. Memorycorruption vulnerabilities are often classified according to their root defect and integer overflows, use-after-free, dangling pointers, double free, buffer overflows, missing pointer checks, uninitialized data usage, type errors, or synchronization errors are commonly listed classes of memory corruption [11-13].

While untrained or inexperienced software developers certainly account for a number of these vulnerabilities, there are also more fundamental, systemic root causes for memory corruption. The ANSI C standard [100] explicitly lists 96 instances which will cause undefined behavior<sup>6</sup> and further remarks that a language implementation "may generate warnings in many situations, none of which is specified as part of the Standard" [100]. This means that in practice software developers can easily miss one of the listed conditions in their code, accidentally writing a program that will exhibit undefined behavior at run time. One of the consequences can be memory corruption, i.e., a situation in which part of program memory, and hence, the overall program state is no longer well-defined. A simple real-world example of such a case is the buffer overflow. In this situation, the size of some user-controlled input should be written to a memory location but exceeds the capacity of the buffer reserved at that location. This can be exploited by adversaries to maliciously modify the data or even hijack the control flow of the program at run time.

#### 2.3.2 A Model for Exploitation

Abstractly, program execution can be viewed as a sequence of transitions within a particular finite-state machine (FSMs) as depicted in Figure 2.3. The left-hand side shows the benign states of the intended state machine as originally specified by the programmer. In this case, there is a dedicated initial state ① of the program from which execution begins. State transitions are specified by the software developer

<sup>5</sup> Although, it does happen occasionally [93-97].

<sup>6</sup> By comparison, the modernized standard ISO/IEC 9899:1999 [101] (commonly called C99) lists 191 cases and the most recent standard ISO/IEC 9899:2011 [102] (commonly called C11) lists 203 instances of undefined behavior.

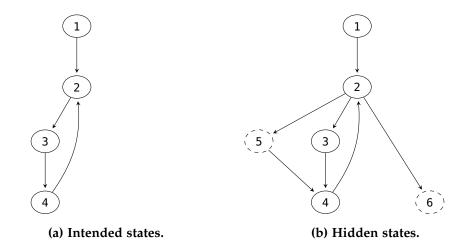

Figure 2.3: Programs can be represented as finite-state machines (a), with vulnerable programs containing hidden states (b), which only become reachable through undefined behavior to form *weird machines* [103, 104].

in the code, e.g., in this case the developer intended the program to cycle endlessly between the three states (2), (3), and (4) after leaving its initial state. The right-hand side shows that in the case of undefined behavior the same program might in fact exhibit unintended, hidden states or weird states [103], which are not reachable during benign execution. If it is possible to trigger the vulnerability explicitly, an adversary might be able to force the program into hidden states that are beneficial from an attacking perspective. Strictly speaking, the code that the developer specified for such a program becomes completely meaningless and the intended finite state machine is replaced by a weird machine [103]. This is also evident from the program on the right-hand side, which now contains a hidden terminal state (6), contrary to the originally specified intended state machine, which cycles endlessly between the three benign states. In this abstract view of exploitation, the actual exploit represents an input or trigger which programs the weird machine to exhibit unspecified or unintended behavior at run time. It is important to note, that this abstract model is completely supported by the language specification. It was recently formalized and also shown to allow reasoning about non-exploitability of a program [104].

#### 2.3.3 Typical Attack Workflow

A classic example for the workflow of such a memory-corruption exploit is given in Figure 2.4: here, the program in (a) utilizes the legacy function gets to read user input and store it in a pre-defined buffer storage without checking the length of the input. So, while the programmer only reserved memory for 17 characters in the program code a user can provide inputs of arbitrary size at run time. In most benign cases, this will simply cause the vulnerable program to crash. However, an adversary can provide a specifically crafted input similar to (b) which will force the program into a weird state (c) that spawns a terminal program and provides the attacker with an interactive programming environment. This is achieved by

```

1 #include <stdio.h>

4141 4141 4141 4141

__GI_exit

2 #include <strings.h> 4141 4141 4141 4141

spawns

4141 4141 4141 4141

3

__libc_system

shell

4 int main(void) {

4141 4141 4141 4141

address of "/bin/sh"

char buffer[17];

4141 4141 4141 4141

gets(buffer);

0306 4000 0000 0000

6

pop rdi

libc_csu_init+99

printf(buffer);

579d b9f7 ff7f 0000

7

ret

9023 a5f7 ff7f 0000

8

return 0;

4141..4141

9 }

3070 a4f7 ff7f 0000

(a) Program.

(b) Exploit.

(c) Corrupted stack.

```

Figure 2.4: The vulnerable program (a) exhibits undefined behavior for inputs exceeding the length of the buffer. An adversary can exploit this by providing malicious input (b) to bring the program into a weird state (c) that will spawn a terminal—a behavior that was never specified anywhere in the program code.

overwriting the return address of the main function which is stored on the stack. Any instance of memory corruption leaves the program vulnerable to run-time attacks, and typical exploitation techniques range from injecting malicious code, to reusing existing code with a malicious input, to corrupting integral data structures of the running program without hijacking its control flow. An adversary with knowledge of any such vulnerability can potentially exploit this at run time by deliberately triggering the error to achieve unintended, malicious behavior and take control over the system.

#### 2.4 STATE-OF-THE-ART ATTACKS AND DEFENSES

Here, we give a quick overview of the relevant literature and state-of-the-art research in run-time attacks and defenses based on memory corruption, such as Return-Oriented Programming (ROP) [10] and Control-Flow Integrity (CFI) [40]. First, we introduce code-reuse attacks and initial, randomization-based defenses. Second, we explain the basic concept behind enforcement-based code-reuse defenses like CFI and variants thereof. Since a rich body of literature exists on the topic of code-reuse attacks and defenses already, we refer the interested reader to the related work for an in-depth and fully comprehensive discussion [105–111]. Third, we briefly introduce the notion of data-only attacks in that context.

#### 2.4.1 Return-to-libc and Return-Oriented Programming

Run-time attacks based on memory-corruption vulnerabilities have been a persistent threat to application and kernel-level software for more than three decades [13–19, 22–26]. Initially, *code-injection attacks* received much attention, since a simple buffer overflow vulnerability enabled adversaries to inject arbitrary code into a running program, e.g., by providing malicious inputs that would spawn a shell (hence the term *shellcode*). Nonetheless, these attacks were quickly prevented by deploying hardware-based defenses such as Data Execution Prevention (DEP) [112, 113],

which disable execution of data memory on the platform as a general policy. Hence, attackers are no longer able to execute code that they injected into the memory of the program. However, the underlying attack paradigm was quickly adapted to bypass DEP as a defense by generalizing code-injection attacks to code-reuse attacks [10, 114]. In a code-reuse attack an adversary exploits a memory-corruption vulnerability to hijack the control flow of a running program by maliciously modifying a code pointer instead of injecting any code, e.g., the return address which is usually stored on the stack of the program can be modified to point to some arbitrary code location that is already present in the memory. In the simplest case, this enables the attacker to redirect execution to another function, such as a library function that forks another program, and supply a malicious input (e.g., "/bin/sh" to launch a shell). However, the most prominent example is return-oriented programming (ROP) [10, 115], in which execution is redirected to small snippets of individual instructions (called gadgets) that end in a return instruction. Since the attacker is able to chain arbitrary sequences of gadgets together, ROP attacks have been shown to be Turing-complete. This means, that the attacker can achieve arbitrary computation in theory, and hence, ROP attacks represent a powerful exploitation tool in practice. It is important to note that code-reuse attacks are possible on a wide range of system, some of which do not even offer a dedicated return instruction. In particular, the possibility of dynamic (or indirect) branching suffices to construct code-reuse attacks [116–118].

#### 2.4.2 Code-Reuse Defenses and Advanced Attacks

Consequently, a number of advanced defenses have been proposed in the related work to protect existing systems against such attacks. Most approaches fall into either of two categories: (1) randomization-based, or (2) policy-based defenses.

Randomization-based approaches aim to lower the portability of a vulnerability among identical systems by randomizing parts of the virtual-address space between applications. Thus, these approaches are sometimes referred to as software diversification as well [110]. The idea of address space layout randomization (ASLR) dates back to 1997 [119] and was first implemented in 2000 [90] to randomize the virtual memory layout for user processes. In particular, ASLR randomizes the stack, heap and shared libraries prior to program loading. Randomization-based defenses usually come with a security-performance trade-off, where increased randomization granularity amounts to higher entropy while typically also introducing more overhead [50]. Besides brute-force guessing attacks, which are rendered infeasible in practice by requiring more than 20 to 30 bits of entropy, randomizationbased defenses are subject to information-disclosure attacks. An information leak discloses information about the memory layout or individual addresses of a process giving an adversary the opportunity to adjust the exploit. There are multiple examples of memory-disclosure vulnerabilities exploited in the real world, such as in Adobe's Flash [120], Adobe's PDF Reader [121], and Microsoft's Internet Explorer [122]. For this reason, more fine-grained randomization techniques were proposed, e.g., by randomizing at the function-level [50], or even at the instructionlevel [47, 123]. However, the run-time penalties associated with those schemes is generally considered too high in practice. Moreover, even a single leaked code

pointer enables an adversary to completely de-randomize an application at run time by disassembling randomized code pages while following newly discovered code pointers. In this way, the attacker can dynamically assemble a gadget payload via indirect disclosure of code pages, a technique dubbed just-in-time code reuse, or JIT-ROP [17]. While information leaks pose significant challenges to fine-grained randomization schemes, a proposed defense technique is to make code pages nonreadable [54, 55]. This was demonstrated to defeat indirect information-disclosure attacks. However, standard hardware does not support non-readable code pages, and hence, implementing this defense requires a hypervisor and extended page table support. Code-Pointer Integrity [46] proposes to partition a program's data memory into a region for code pointers and a region for the remaining data. By randomizing the location of the code-pointer region, all accesses to code pointers can then be assumed to be safe. While this compiler-based approach was shown to introduce a lower overhead than fine-grained randomization defenses against code-reuse attacks, the location of the safe region was subsequently shown to be prone to timing sidechannels [124].

In contrast to these probabilistic randomization-based defenses, Control-Flow Integrity (CFI) [40] emerged as a promising defense mechanism that offers formal security guarantees, while incurring modest overheads. The high-level idea behind CFI is to analyze the program code at compile time to compute *labels* at all possible branch locations and insert checks that restrict the control flow to the correct label set. Since this approach requires additional checks to be executed at run time for indirect jumps, initial implementations induced overheads from 5 to 20 percent, which is still considered impractical for many applications [41]. Moreover, the accuracy of the pre-computed and enforced label sets is essential to achieve a high level of security. Deploying CFI in the context of object-oriented code has proven challenging, as implementations that neglect the detailed semantics of languages like C++ were shown to be subject to attacks [18]. For binary code, imprecise label sets can lead to attacks despite coarse-grained CFI policies being enforced [125]. Hence, secure CFI implementation typically require an in-depth static analysis and instrumentation phase at compile time, costly run-time checks, and a shadow stack implementation [126]. To reduce the performance hit, hardware-assisted CFI implementation have been investigated [42, 60] and hardware extensions have been announced to offer dedicated CFI support for upcoming CPU architectures [61].

#### 2.4.3 Data-only attacks

In contrast to code-injection and code-reuse attacks, data-only attacks [13] do not hijack the control flow of an application. Instead, the attacker tampers with the input data of functions or directly corrupts data structures in memory. Although data flows are in general heavily application-dependent, data-only attacks were previously shown to severely affect the security of vulnerable software [68]. Additionally, while data-only attacks may not always offer the same flexibility and expressiveness as code-reuse attacks, they can pose a significant threat in practice. For example, the attacker can change the current user id to elevate privileges, or change file names to disclose secrets such as configuration files or cryptographic keys. So far, no efficient and general data-only defense exists as all intended data flows

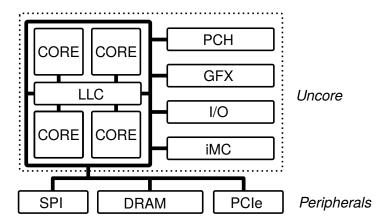

Figure 2.5: Modern computer platforms feature complex SoC architectures that combine multi-core designs with performance-critical elements *uncore* inside the CPU package. Components inside the CPU package share a large last-level cache and are tightly coupled through high-speed interconnect fabric on the die. Peripherals are connected to the processor package via the system bus.

must be protected to construct an effective mitigation, resulting in prohibitively expensive overheads for existing schemes [49, 127, 128]. We demonstrate the real-world threat of data-only attacks in the context of multi-step attack approaches against OS kernels and also present possible mitigations in depth in Part II.

#### 2.5 MODERN HARDWARE PLATFORMS

Since many defenses against memory-corruption-based attacks have been presented and also deployed over the years, adversaries are looking for new ways to attack systems at run time. Naturally, software runs on physical hardware, which has grown quite complex over time. As it turns out, this also opens up novel opportunities for attacks. Computer platforms have evolved significantly during the last 30 years, trading their relatively simple, discrete layouts in the beginning for more complex, but faster system-on-chip (SoC) designs. In this section, we first look into the overall system architecture of modern platforms. We then discuss the processor design principles underlying recent computing platforms in more detail and further outline in which ways this can prove problematic from a security perspective.

#### 2.5.1 Overall System Architecture

In particular, earlier architectures connected a large number of these discrete and specialized components through hard-wired or printed circuit lanes on the main-board. In contrast to that, modern processors integrate many of these traditionally separate chip elements on a single die, minimizing the number of required communication pathways off-chip to enable faster and wider data connections. The basic platform architecture of such an integrated, SoC-based design is depicted in Figure 2.5. At the highest level, multi-core architectures typically have an intricate interconnect fabric between individual cores, the last-level cache (LLC), the uncore elements, and the system bus which connects to the off-chip peripher-

Figure 2.6: Semiconductor manufacturers aim to enhance single-core performance by maximizing *instruction-level parallelism*. For this, chip designers leverage techniques such as super-scalar processing, simultaneous multi-threading, and out-of-order execution, which heavily increase implementation complexity of modern processors.

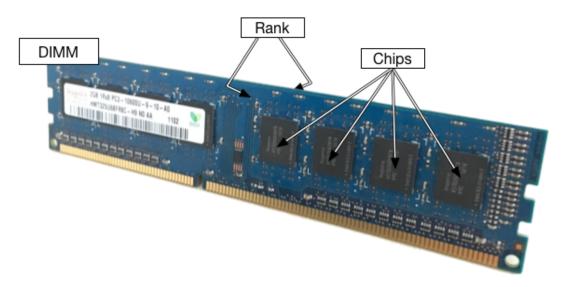

als. While the main components have remained largely the same, many elements were moved from off-chip to uncore in recent years. Traditionally, the mainboard chipset employed a north- and southbridge architecture, which used to connect peripherals with faster and slower data connections respectively. However, since many peripherals rapidly increased their communication speed and maximal capacity, the Platform Controller Hub (PCH) has replaced this older layout. On recent CPUs, it was moved into the processor package to allow for more direct links, enabling faster communication and more fine-granular control. It now also combines power management and security services, e.g., in the form of the Converged Security and Management Engine (CSME) [129]. Moreover, modern CPUs typically also directly contain dedicated graphics processing capabilities (GFX), as well as complex configurable hardware controllers (I/O). Lastly, they incorporate an integrated memory controller (iMC), which usually resided on the mainboard as well on older platforms. The main peripheral connections that remain on the mainboard on modern platforms represent the flash ROM chip<sup>7</sup> attached via Serial-Peripheral Interface (SPI), main memory in the form of Dynamic Random-Access Memory (DRAM), and high-speed peripherals such as SSDs and GPUs which are connected over Peripheral Component Interconnect Express (PCIe).

#### 2.5.2 Processor Design Principles

The bi-annual doubling of transistor density no longer drives performance improvements in integrated circuit designs, as Moore's Law is hitting the physical limits of silicon-based semiconductor technology [130]. Thus, processors are increasingly designed to optimize execution, e.g., by heavily improving the number of instructions executed per unit time (dubbed *instruction-level parallelism*). For instance, practically all modern processors are super-scalar architectures, which

<sup>7</sup> Which contains the firmware (i.e., boot ROM, CSME code and data partitions, BIOS, and  $\mu$ -code).

means they are able to utilize functional units in parallel to execute more than one instruction per cycle. This requires careful management of the instruction pipeline to identify data dependencies between consecutive instructions and puts additional constraints on the design of the decode and fetch stages. Further, Simultaneous Multithreading (SMT) [131] subdivides a single physical core into a number of *logical cores*, introducing the ability to simultaneously process different instruction streams within a single core.

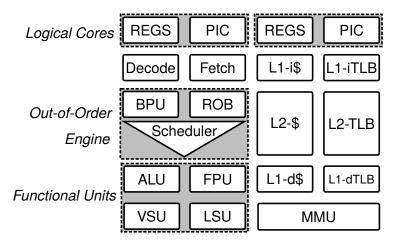

The high-level design of such a processor is depicted in Figure 2.6 and usually simply replicated for each physical core on a multi-core chip. Individual instructions are loaded into the pipeline by the fetch stage of the processor, and decoded into a number of microcode instructions ( $\mu$ -ops), which are executed by the functional units. High-end processors often feature complex Out-of-Order Engines that may schedule and process  $\mu$ -ops of the same instruction stream ahead of time, leveraging Re-Order Buffers (ROB) to emit the results of re-ordered instructions in the correct sequence before finalizing execution. Some processors additionally employ Branch-Prediction Units (BPUs) to speculate on the target address of branch instructions, e.g., to make loop iterations cheaper. The functional units, such as Arithmetic Logic Units (ALU), Floating-Point Units (FPU), Vector-Scalar Units (VSU), and the Load-Store Units (LSU) represent the fundamental building blocks that are contained in some form on every processor. Usually, the LSUs are the only functional units that operate on external memory. DRAM access latencies are many orders of magnitude slower than processor cycles, and hence, CPUs leverage complex, multi-level caching hierarchies to close this gap and enhance performance in practice [132]. The fastest level, L1, is divided into an instruction cache (L1-i\$), which contains the machine code of the currently executed thread, and a data cache (L1-d\$). Typically, its size is in the order of a few memory pages and access latencies are in the range of a single CPU cycle. The second level, L2, usually unifies code and data, and while its access latency is about an order of magnitude slower than the L1, its size can be a magnitude larger. SMT processors contain multiple Register Sets (REGS) and Programmable-Interrupt Controllers (PICs) to maintain separate threads independently at run time, and hence, threads running on two logical cores share all of the core's physical resources. Since individual instructions can exhibit large differences in execution time, one thread may often stall the core while waiting for a scheduled instruction to finalize operation. The instruction stream from other threads running on the same physical core can then be used to maximize resource utilization by executing its instructions in parallel to the instruction stream from the stalled thread. As mentioned in Section 2.1.2, many processors support virtual-memory protection through a Memory-Management Unit (MMU). While MMUs allow for a fine-granular, pagebased policy management and enforcement, this also requires an indirection for every memory access, which strongly affects run-time performance. For this reason, processors which include an MMU typically also feature a series of faster caches for these policy look-ups, called the Translation-Lookaside Buffers (TLBs), which usually mirror the cache hierarchy for code and data memory. Again, these hardware resources are shared among all logical cores of a physical package.

#### 2.5.3 Remote Hardware Exploits

Resource sharing maximizes utilization, and hence, optimizes run-time performance. However, the added complexity and extreme transistor densities of today's chips also lead to side effects that can be leveraged by malicious software.

One example of this are *side-channel attacks*. The goal behind a side-channel attack is usually to leak information, such as passwords or cryptographic keys and many practical attacks have been presented in the past. Side-channel attacks are especially problematic when processor resources are shared across different privilege levels, as this may allow an unprivileged adversary to disclose privileged information. For instance, by leaking internal data from the OS through a side channel an adversary can break fine-grained randomization and subsequently launch a codereuse attack [22, 80]. Additionally, many architectures offer dedicated prefetching and flushing instructions to load or empty out caches to allow manual optimization from software. These operations directly influence and disclose information about the state of the caches and allow co-located attackers to probe and measure the effects of accesses by victim software [82, 83, 133].

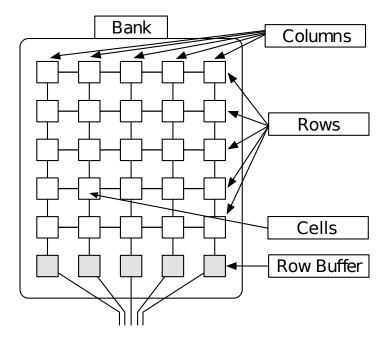

While side-channel attacks are limited to information disclosure, *remote-fault injection attacks* enable adversaries to corrupt hardware entirely from software, potentially compromising the security of the entire platform. One recent example is Rowhammer [63], which leverages a hardware vulnerability in DRAM chips to generate bit flips in memory from software at run time and many attacks have been presented that completely bypass existing defense mechanisms [64, 74–77, 134, 135]. Another example is CLKScrew [65], which exploits power management functionality to produce processor glitches at run time from software. This enables attackers to compromise even dedicated hardware security extensions, such as ARM TrustZone, which were envisioned as a general defense against software-based attacks [136].

While both attack classes mentioned above exploit specific vulnerabilities or features of bare-metal hardware, it is important to note that *firmware attacks* may also enable remote attacks against hardware. Firmware represents software that is embedded into the chip by the manufacturer and (contrary to the OS) cannot easily be modified by the owner of the platform. To this end, it serves as a bridging technology by managing low-level control tasks, such as platform bring-up, power-saving stages, and chip-level peripheral control. Although these tasks could in principle be implemented through additional hardware, firmware allows for greater flexibility across different product lines and, in contrast to hard-wired circuitry, can also be updated after deployment. Naturally, as firmware grows more complex it is prone to similar attacks as traditional system software: for instance, firmware attacks have been demonstrated against Intel ME [137] and NVIDIA's Tegra Cores [138] recently, affecting millions of platforms such as many recent Intel's x86 processors [139] and Nintendo's Switch gaming consoles [140].

Overall, we can see all three techniques are increasingly gaining attention, as remote hardware exploits represent an upcoming threat. Recently, successful hardware-based exploits have been demonstrated from malicious software against applications [141], the OS [66], and even against advanced hardware-security architectures like Intel SGX [67] and ARM TrustZone [65]. Since firmware could in principle be

protected by adapting software-based defenses, we focus on the first two techniques in this dissertation. We discuss remote hardware-based attacks as well as possible mitigations in depth in Part III.

#### Part II

## MEMORY CORRUPTION: THE THREAT OF DATA-ONLY ATTACKS

based on JIT-Guard [1], PT-Rand [2], and K-Miner [3].

In this chapter, we demonstrate that state-of-the-art code-reuse defenses like CFI are not sufficient to stop the threat of memory-corruption attacks. In particular, we present a data-only attack, termed DOJITA [1], which completely defeats CFI in the browser context.

#### 3.1 DATA-ONLY ATTACKS ON DYNAMIC CODE GENERATION

Big applications, such as web browsers and document editors support a large number of features, for instance, to support a variety of file formats, and increasingly offer highly customizable functionality to end users. To achieve a high level of flexibility, many of these applications leverage *dynamic code*. These scripting languages, like JavaScript, are interpreted at run time and can easily be updated or modified without changing the static code of the surrounding application. In contrast to static programming languages, like C and C++, this requires a dedicated run-time environment, that additionally takes care of memory management and provides an interface to a rich set of functions. For instance, dynamic scripting languages are typically included in most web browsers, as today many websites require a form of dynamic interaction with the user. As such, high-performance execution of dynamically generated code can be essential. To this end, static code that includes dynamic scripting components usually employs just-in-time (JIT) compilers to translate the interpreted, high-level scripting code into machine code at run time, since interpretation is orders of magnitude slower than native execution.

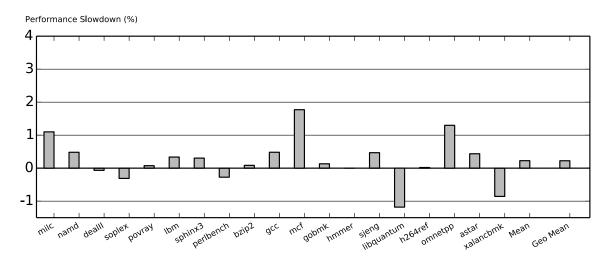

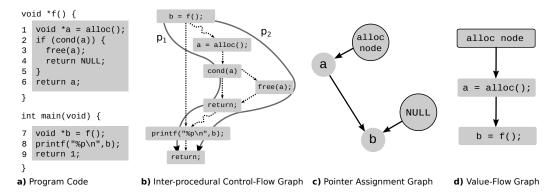

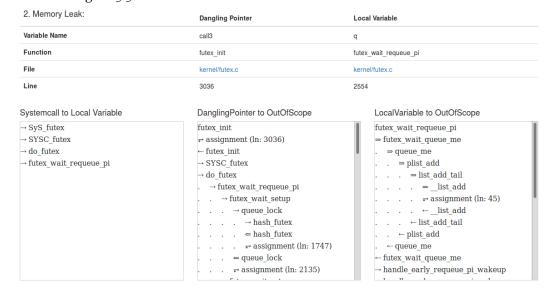

It is noteworthy to mention that dynamic code is not limited to the application level, but represents a common technique to increase flexibility of large software in general: even some operating systems include a dedicated JIT engine in the form of the Berkley Packet Filter (BPF) [142], which was originally designed as a user-programmable network filter in the kernel, however, it has been significantly extended over time to support a variety of use cases (e.g., sandboxing).