# Microsemi RTG4 Rev C Field Programmable Gate Array Single Event Effects (SEE) Heavy-ion Test Report

Melanie Berg – Principal Investigator: AS&D in support of NASA/GSFC HAK Kim, Anthony Phan, Christina Seidleck: AS&D in support of NASA/GSFC Ken Label: NASA/GSFC Jonny Pellish: NASA/GSFC Michael Campola: NASA/GSFC

Test Dates: TAMU2015Dec; LBNL2016Mar; LBNL 2016Oct; TAMU 2016Oct-Nov;TAMU 2017March

| Revision Number       | Submission Date | Comment                        |  |

|-----------------------|-----------------|--------------------------------|--|

| RTG4_test_report_rev0 |                 | Original submission Rev B data |  |

|                       |                 | only                           |  |

| RTG4_test_report_rev1 |                 | Addition of Rev C data         |  |

| RTG4_test_report_rev2 | 06/2017         | Additional test data           |  |

| RTG4_test_report_rev2 | 09/2017         | Inclusion of lot date codes    |  |

RTG4

# **Table of Contents**

| 1. | Introduction                                                                                      | 8    |

|----|---------------------------------------------------------------------------------------------------|------|

| 2. | Devices Tested                                                                                    | 8    |

|    | 2.1 Device Specifics                                                                              | 8    |

| 3. | Background                                                                                        | . 11 |

|    | 3.1 Cross Sections                                                                                | . 11 |

|    | 3.2 Divide and Conquer Test Approach                                                              | . 11 |

|    | 3.3 Configuration Test and Analysis                                                               | . 12 |

|    | 3.3.1 Dynamic Test and Configuration Analysis                                                     | . 12 |

|    | 3.4 Data Path and Global Upset Investigation:                                                     | . 12 |

|    | 3.4.1 RTG4 Expected Single Event Upsets and Error Rate Calculation                                | . 12 |

|    | 3.4.2 Test Circuits used for Establishing SEU Cross Sections and Error Rates                      | . 13 |

|    | 3.5 NASA DUT Preparation Plan                                                                     | . 14 |

| 4. | Test Procedures and Best Practices                                                                | . 16 |

|    | 4.1 Functional Control                                                                            | . 16 |

|    | 4.2 Monitoring Functionality                                                                      | . 16 |

|    | 4.3 Automated Data Capture and Messaging                                                          | . 17 |

|    | 4.4 Monitoring DUT Power and SEL Investigation                                                    | . 18 |

|    | 4.5 Investigating SEFIs                                                                           | . 18 |

| 5. | Test Hardware (test system)                                                                       | . 18 |

|    | 5.1 Pictures of the Test System                                                                   | . 18 |

|    | 5.2 LCDT Architectural Overview                                                                   | . 19 |

|    | 5.2.1 RS232 communication from the LCDT to the Host PC                                            | . 20 |

|    | 5.3 RS232 communication From the Host PC to the LCDT                                              | . 21 |

|    | 5.3.1 User GUI                                                                                    | . 21 |

|    | 5.3.2 User Interface and Command Control                                                          | . 21 |

| 6. | DUT Test Structures and Dynamic Accelerated testing                                               | . 22 |

|    | 6.1 Challenges for Testing                                                                        | . 22 |

|    | 6.2 Overview of DUT Test Structures                                                               | . 23 |

|    | 6.3 Windowed Shift Registers (WSRs)                                                               | . 23 |

|    | 6.3.1 General Operation                                                                           |      |

|    | 6.3.2 WSRs and LCDT Requirements                                                                  |      |

|    | 6.3.3 WSR SEU Data Monitoring and Capture                                                         | . 25 |

|    |                                                                                                   | . 26 |

|    | 6.3.5 Post Processing of LCDT WSR Data Analysis for First Round of Testing                        | . 27 |

|    | 6.4 Global Routes and Microsemi RTG4 Clock Conditioning Circuit (CCC)                             | . 28 |

|    | 6.4.1 Resets                                                                                      | . 29 |

|    | 6.5 DUAs Based on WSR and Global Route Variations – 1 <sup>st</sup> Round of RTG4 Rev C Heavy Ion |      |

|    | Testing                                                                                           | . 29 |

|    | 6.5.1 Design A: 4 Clock 4 Reset DUA                                                               |      |

|    | 6.5.2 Design B: 4 Clock 4 Reset with DFF SET Filters DUA                                          | . 30 |

|    | 6.5.3 Design C: 4 clk 4 rst Direct CLKBUF DUA                                                     |      |

|    | 6.5.4 Design D: Long Shift Register DUA                                                           |      |

|    | 6.5.5 Design E: Long Shift Register with DFF SET Filters DUA                                      |      |

|    | 6.5.6 Design F: Large shift register CCC with DFF SET Filters DUA                                 |      |

|    |                                                                                                   |      |

| 6.5.7    | Summary of WSR – Global Route DUA Variations 1 <sup>st</sup> Round of Rev C Heavy Io 32 | n Testing |

|----------|-----------------------------------------------------------------------------------------|-----------|

| 6.5.8    | WSR and Global Route Variations Data Capture, Error Records, and Data Proces            | ssing 32  |

|          | L DUAs Based on WSR and Global Route Variations – 2 <sup>nd</sup> Round of RTG4 Rev C   |           |

|          | ing                                                                                     | •         |

| 6.6.1    | 6                                                                                       |           |

|          | unter Array DUA                                                                         |           |

| 6.7.1    | Counter Array Implementation                                                            |           |

| 6.7.2    | Counter I/O Interface and Expected Outputs                                              |           |

| 6.7.3    | Counter Array and LCDT Specifics                                                        |           |

| 6.7.4    | Processing the DUT Outputs during Testing                                               |           |

| 6.7.5    | Counter Array Error Record                                                              | 45        |

| 6.7.6    | Counter Array Post Processing                                                           |           |

|          | ernal SRAM Memory DUAs                                                                  |           |

| 6.8.1    | uSRAM DUA Schematic and Configuration Details                                           |           |

| 6.8.2    | LSRAM DUA Schematic and Configuration Details                                           |           |

| 6.8.3    | Summary of RTG4 internal SRAM DUAs                                                      |           |

| 6.8.4    | SRAM DUA Operation                                                                      |           |

| 6.8.5    | SRAM DUT to LCDT Requirements                                                           |           |

| 6.8.6    | LSRAM and uSRAM Data Processing                                                         |           |

| 6.8.7    | Additional Data Processing for uSRAM EDAC DUAs                                          |           |

| 6.8.8    | LSRAM and uSRAM Error Record                                                            |           |

| 6.8.9    | LSRAM and uSRAM Data Post Processing                                                    |           |

|          | SP (HMACC) DUAs                                                                         |           |

| 6.9.1    | DUA FIR to LCDT Requirements                                                            |           |

| 6.9.2    | DUA FIR Data Processing                                                                 |           |

| 6.9.3    | DUA FIR Error Record                                                                    |           |

| 6.9.4    | DUA FIR Data Post Processing                                                            |           |

|          | Accelerated Heavy ion Test Procedures                                                   |           |

|          | mmary of DUT-Tester operation.                                                          |           |

|          | nning a Full Test                                                                       |           |

|          | Files required for running a test $-1^{st}$ round of Rev C Testing                      |           |

|          | Files required for running a test $-2^{st}$ round of Rev C Testing                      |           |

| 7.2.2    | Procedures for running a test                                                           |           |

|          | Ion Test Facility and Test Conditions                                                   |           |

| 8.1.1    | Overview of Heavy-ion Accelerated Tests Performed at LBNL March 2016 and 7              |           |

| - · ·    | 2016                                                                                    |           |

|          | Overview of Heavy-ion Accelerated Tests Performed at LBNL October 2016                  |           |

| 8.1.2    | Overview of Heavy-ion Accelerated Tests Performed at LBNL October-Novem                 |           |

| 0.1.5    | 68                                                                                      | Jei 2010  |

| 9. Heavy | -Ion Accelerated Testing Data Analysis                                                  | 69        |

| 9.1 RT   | G4 Flash Configuration Cells                                                            |           |

| 9.1.1    | Configuration Cell failures                                                             |           |

| 9.1.2    | Programmability failures                                                                |           |

| 9.2 De   | scription of WSR Halt Tests (1st Round (no PLL) and 2nd round (with PLLs) of tes        | ting) 70  |

| 9.2.1 WSR Halt Test Results                                                   | 71 |

|-------------------------------------------------------------------------------|----|

| 9.3 WSR 1 <sup>st</sup> round heavy ion tests                                 |    |

| 9.3.1 WSR 1 <sup>st</sup> Results                                             |    |

| 9.4 Global Routes and PLL WSR Heavy Ion Tests (2 <sup>nd</sup> Round) Results | 76 |

| 9.4.1 DFF SEUs with respect to a variety of clock sources                     |    |

| 9.4.2 Global route overview                                                   |    |

| 9.5 Counter Heavy Ion Tests                                                   |    |

| 9.5.1 Description of Heavy Ion RTG4 Counter Tests                             |    |

| 9.6 Results                                                                   |    |

| 9.7 RTG4 Internal SRAM Heavy Ion Tests                                        |    |

| 9.7.1 Description of Internal SRAM Heavy Ion Tests                            |    |

| 9.7.2 LSRAM Results                                                           | 79 |

| 9.7.3 uSRAM Results                                                           |    |

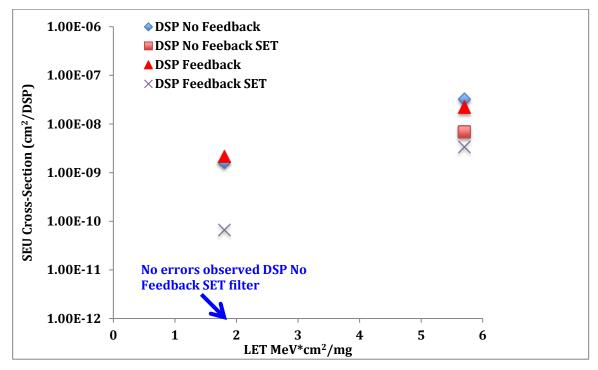

| 9.8 DSP Heavy Ion Testing                                                     |    |

| 10. Comparison of NEPP RTG4 to NEPP ProASIC3 Heavy-ion Data                   |    |

| 11. Conclusion                                                                |    |

| 12. Appendix 1:                                                               |    |

|                                                                               |    |

# Table of Figures

| <ul> <li>Figure 2: Directly coupled interconnection scheme for Microsemi RTG4 flash configuration cells 10</li> <li>Figure 3: Localized TMR DFF scheme. Microsemi refers to it as self-correcting TMR (STMRFF) 10</li> <li>Figure 4: Ultra Tec ASAP-1 device preparation system</li></ul>                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4: Ultra Tec ASAP-1 device preparation system       14         Figure 5: Top side of DUT daughter board with de-lidded and thinned DUT.       15         Figure 6: Bottom side of DUT daughter board with de-lidded and thinned DUT.       16         Figure 7: Sample Message from the LCDT to the Host PC.       Message describe the SEU and Includes a         Timestamp       17         Figure 8: Test Setup - Connected LCDT3 and Daughter Card (1).       19         Figure 9: Test Setup - Connected LCDT3 and Daughter Card (2).       19         Figure 10: System Level Tester Architecture for the DUT configured as a counter.       20 |

| <ul> <li>Figure 5: Top side of DUT daughter board with de-lidded and thinned DUT.</li> <li>15</li> <li>Figure 6: Bottom side of DUT daughter board with de-lidded and thinned DUT.</li> <li>16</li> <li>Figure 7: Sample Message from the LCDT to the Host PC. Message describe the SEU and Includes a Timestamp</li> <li>17</li> <li>Figure 8: Test Setup - Connected LCDT3 and Daughter Card (1).</li> <li>19</li> <li>Figure 9: Test Setup - Connected LCDT3 and Daughter Card (2).</li> <li>19</li> <li>Figure 10: System Level Tester Architecture for the DUT configured as a counter.</li> </ul>                                                      |

| <ul> <li>Figure 6: Bottom side of DUT daughter board with de-lidded and thinned DUT</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <ul> <li>Figure 7: Sample Message from the LCDT to the Host PC. Message describe the SEU and Includes a Timestamp</li> <li>17</li> <li>Figure 8: Test Setup - Connected LCDT3 and Daughter Card (1)</li> <li>19</li> <li>Figure 9: Test Setup - Connected LCDT3 and Daughter Card (2)</li> <li>19</li> <li>Figure 10: System Level Tester Architecture for the DUT configured as a counter</li> <li>20</li> </ul>                                                                                                                                                                                                                                            |

| Timestamp17Figure 8: Test Setup - Connected LCDT3 and Daughter Card (1)19Figure 9: Test Setup - Connected LCDT3 and Daughter Card (2)19Figure 10: System Level Tester Architecture for the DUT configured as a counter20                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 8: Test Setup - Connected LCDT3 and Daughter Card (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 9: Test Setup - Connected LCDT3 and Daughter Card (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 10: System Level Tester Architecture for the DUT configured as a counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 11: WSR Chains. WSR variations are based off of the number of combinatorial logic blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| between each DFF stage; the number of DFF stages per chains; and how the WSR DFFs are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| connected to global routes. In this figure, WSR <sub>0</sub> indicates a WSR with no combinatorial logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| gates. WSR <sub>8</sub> indicates a WSR with 8 levels of combinatorial logic gates between each DFF stage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 12: WSR Functional Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 13: WSR output under normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 14: WSR Operation with SEU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 15: Microsemi clock conditioning circuit. FDDR: Memory Double Data Rate Interface Control;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 16: Asynchronous assert synchronous de-assert reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 17: General schematic showing the potential variations in clock connections. The DFF can be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| configured to have SET filters at their data input pin or not to have SET filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# RTG4

| Figure 18: Design A: 4 Clock 4 Reset WSR to Clock connection                                                             |

|--------------------------------------------------------------------------------------------------------------------------|

| Figure 19: Design C: All WSRs are controlled by DGBIO/CLKBUF. All WSR chains contain DFF                                 |

| SET filters                                                                                                              |

| Figure 20. Design D. Long WSK to DFF SET Inters                                                                          |

| the RTG4 CCC block. No resets are connected to the DFFs in the WSR chain                                                 |

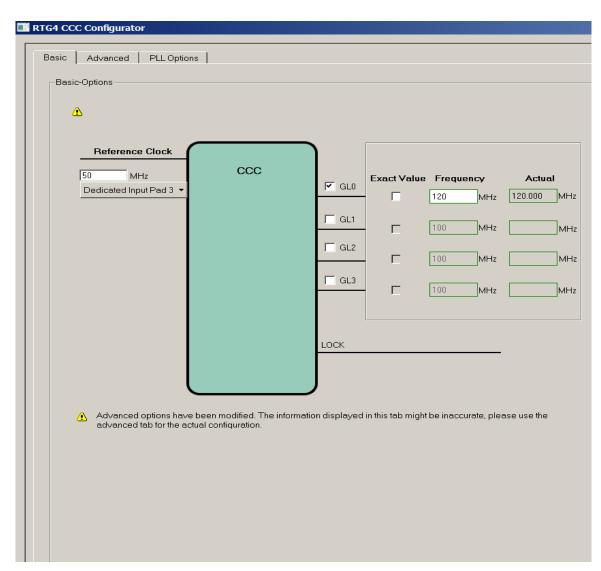

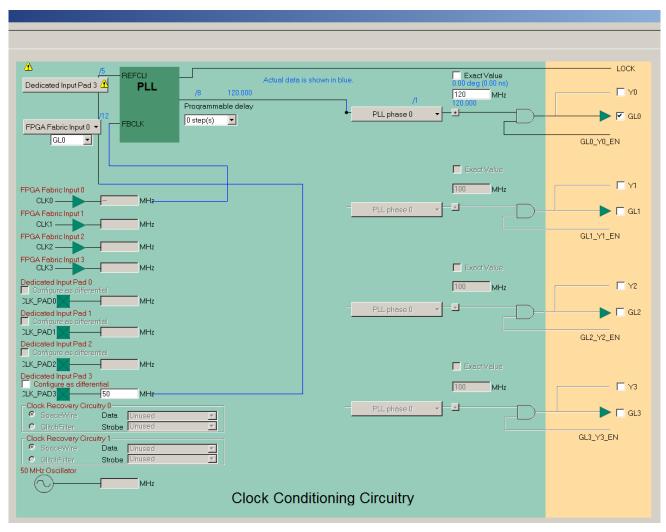

| Figure 22: Front panel of CCC configuration in Microsemi Libero CAD tool. 50MHz input from a                             |

| DGBIO with 120MHz output to a CLKINT buffer                                                                              |

| Figure 23: 2 <sup>nd</sup> tab for CCC configuration with internal feedback in Microsemi Libero CAD tool.                |

| Chain0 in $2^{nd}$ round heavy ion testing                                                                               |

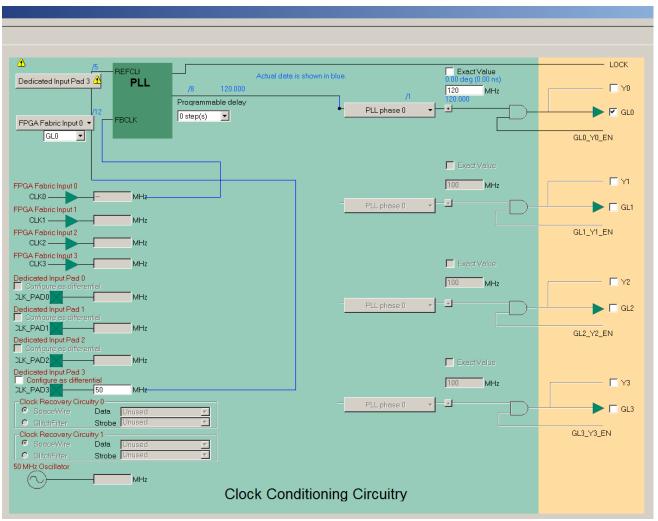

| Figure 24: 2 <sup>nd</sup> tab for CCC configuration with external feedback in Microsemi Libero CAD tool.                |

| Chain2 in 2 <sup>nd</sup> round heavy ion testing                                                                        |

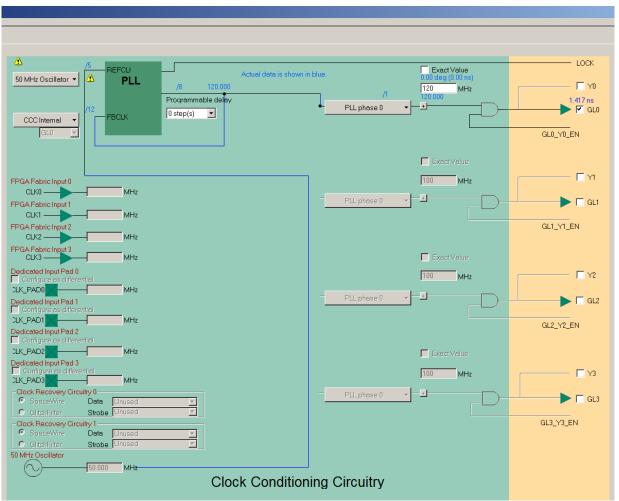

| Figure 25: 2 <sup>nd</sup> tab for CCC configuration with OSC as input and internal feedback in Microsemi Libero         |

| CAD tool. Chain3 in 2 <sup>nd</sup> round heavy ion testing                                                              |

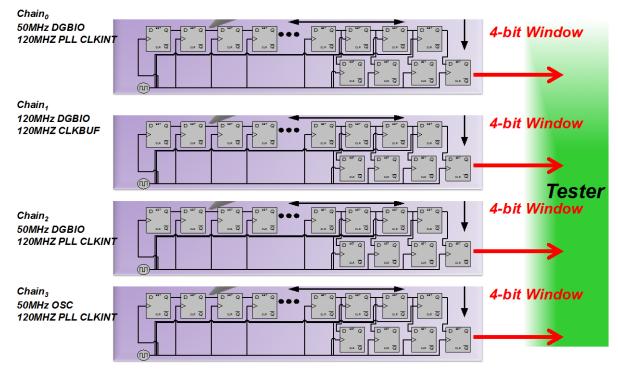

| Figure 26: PLL WSR Chains. Four Chains (Chain0, Chain1, Chain2, and Chain3). All WSR chains                              |

| are WSR <sub>0</sub> with PLL configuration variations as clock sources                                                  |

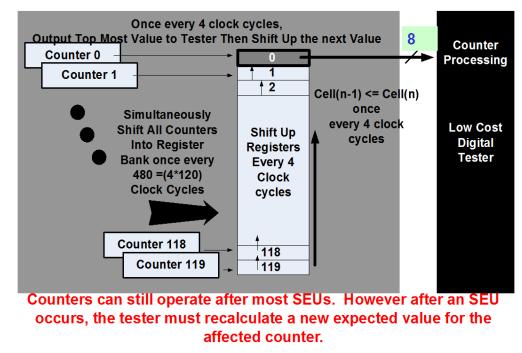

| Figure 27: Schematic of the 8-bit Counters and their Output Selection Logic. In this case, the output                    |

| selection logic is a Snapshot shift register (Shifts up counter values to the output registers every 4                   |

| cycles). The DUT uses a 8-bit counter scheme with 200 counters labeled "counter 0" through                               |

| "counter 199"                                                                                                            |

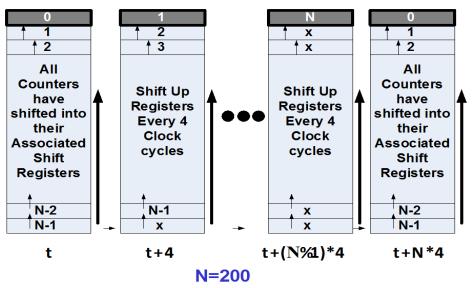

| Figure 28: Counter Shift Register Cycles inside a snapshot bank; Values in Snapshot shift registers                      |

| represent counter labels at a given moment in time. Regarding this figure, if there is an x with the                     |

| Snapshot register, then it is considered a "don't-care" state. N=200 for the RTG4 Radiation Test.                        |

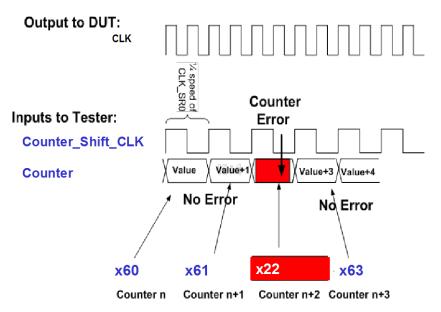

| Figure 29: Typical SEE Counter Outputs. Each output represents a value from a different counter in                       |

| the array. Counter selection is sequential, hence, the counter number and the counter values all                         |

| increment by 1 each Counter_Shift_Clk cycle                                                                              |

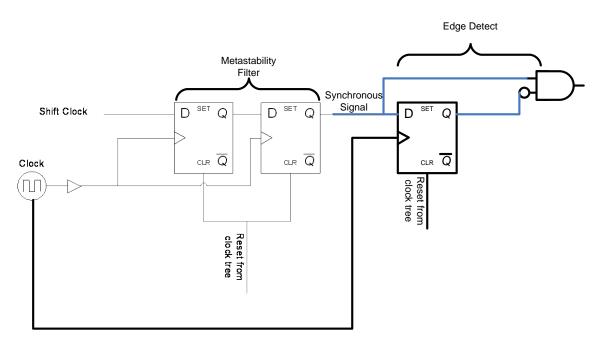

| Figure 30: Shift_ClK Capture consists of a Metastability Filter and a Edge Detect                                        |

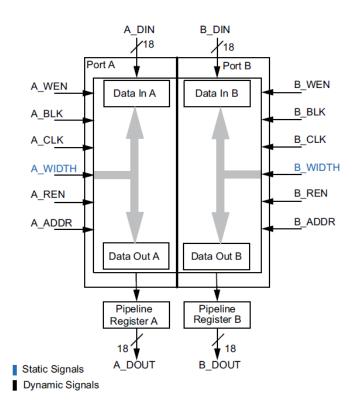

| Figure 31: High-level schematic of RTG4 internal SRAM                                                                    |

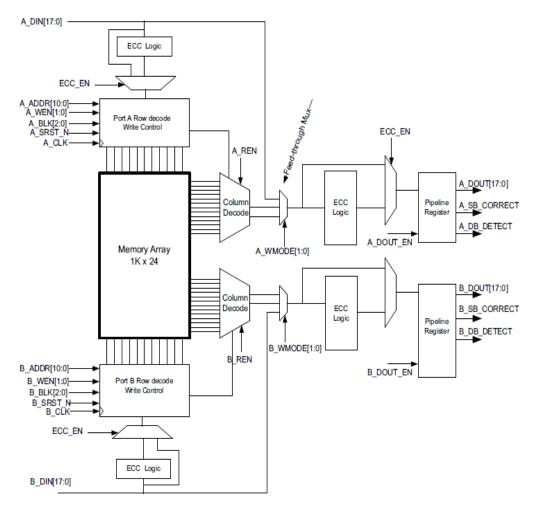

| Figure 32: High-level schematic of RTG4 internal SRAM including EDAC circuitry                                           |

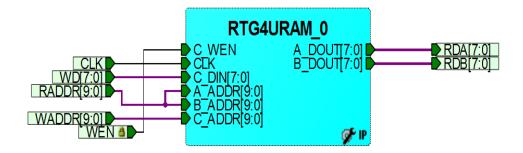

| Figure 33: Top level representation of the uSRAM without EDAC circuitry. Inputs are on the left of                       |

| the picture and outputs are on the right                                                                                 |

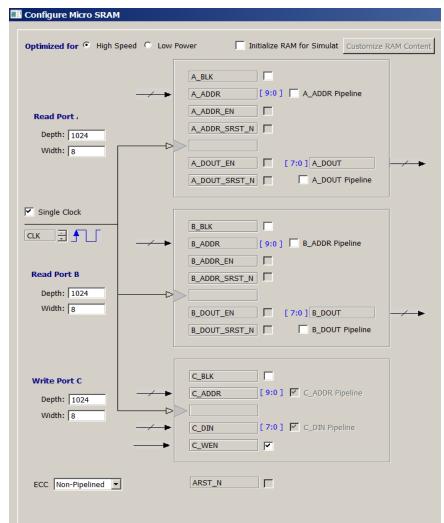

| Figure 34: Microsemi Libero CAD uSRAM configuration panel. This is the configuration of the                              |

| uSRAM without EDAC circuitry                                                                                             |

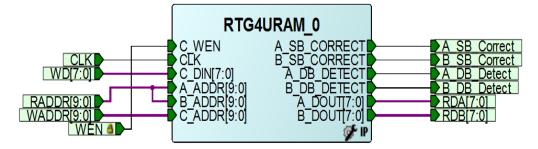

| Figure 35: Top level representation of the uSRAM with EDAC circuitry. Inputs are on the left of the                      |

| picture and outputs are on the right                                                                                     |

| Figure 36: Microsemi Libero CAD uSRAM configuration panel. This is the configuration of the                              |

| uSRAM with EDAC circuitry                                                                                                |

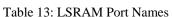

| Figure 37: Top level representation of the LSRAM without EDAC circuitry. Inputs are on the left of                       |

| the picture and outputs are on the right                                                                                 |

| Figure 38: Microsemi Libero CAD LSRAM configuration panel. This is the configuration of the LSRAM without EDAC circuitry |

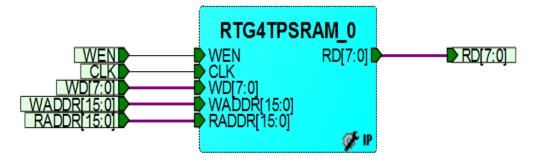

| Figure 39: Microsemi top-level diagram of a hard multiplier accumulate (HMACC) block                                     |

| Figure 40: Logic schematic of a Microsemi RTG4 hard multiplier accumulate (HMACC) block 59                               |

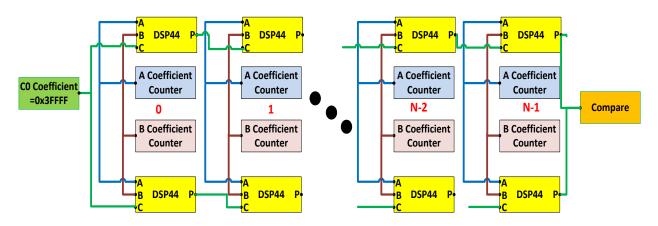

| Figure 41: DUA finite response filter (FIR). The compare sends out two signals: BADCOMPARE and                           |

| ALLZERO                                                                                                                        | . 59 |

|--------------------------------------------------------------------------------------------------------------------------------|------|

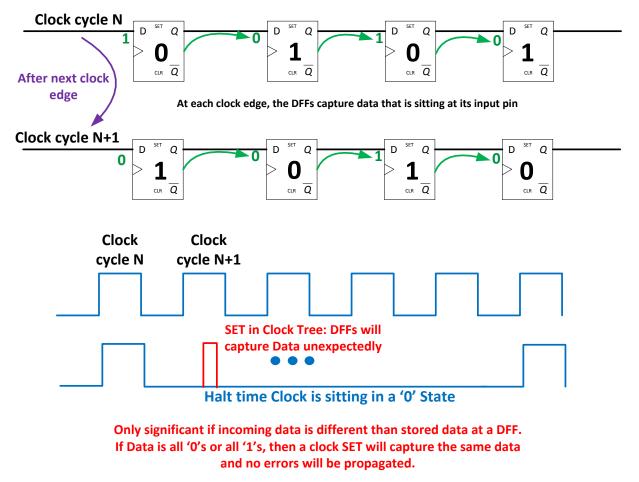

| Figure 42: Halt Test timing diagram and DFF capture for a WSR checkerboard pattern. If an SET                                  |      |

| occurs during the halt state (while the clock is low), any DFFs that are affected by the clock SE                              | Т    |

| can capture data incorrectly via the clock SET edge                                                                            |      |

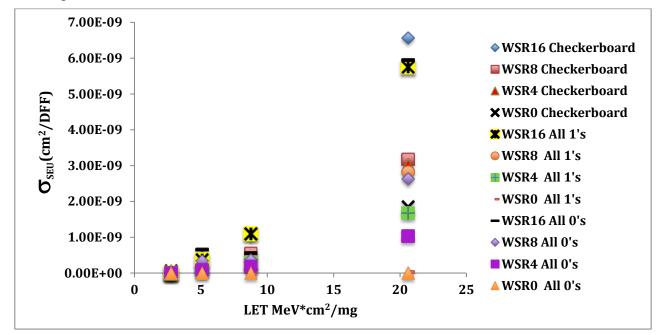

| Figure 43: 4 CLK 4 RST FILTER versus LET at 100MHz                                                                             |      |

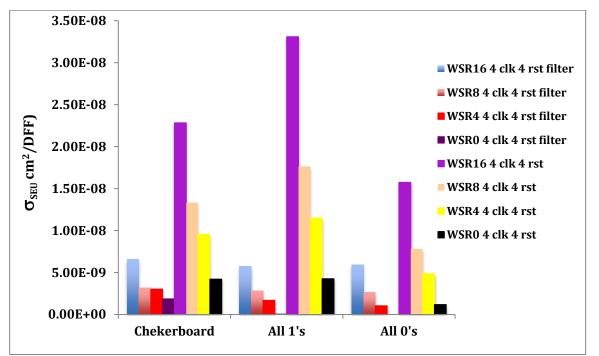

| Figure 44: Comparing WSR Chains: 4 clk 4 rst with Filter and 4 clk 4 rst100MHz with LET =                                      |      |

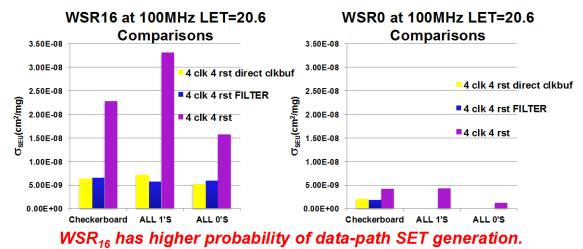

| 20.6MeVcm <sup>2</sup> /mg                                                                                                     | .73  |

| Figure 45: Comparing 4 clk 4 rst DUT Variations: How much Better Is A Direct Connection to                                     |      |

| CLKBUF and/or A SET Filter?                                                                                                    | .74  |

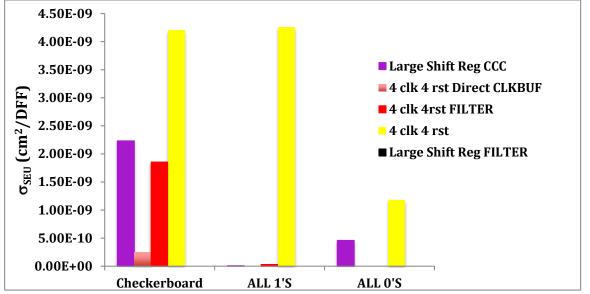

| Figure 46: Large WSRs : Comparison of WSR <sub>0</sub> SEU Cross Sections at 100MHZ at LET =                                   |      |

| 20MeV*cm <sup>2</sup> /mg                                                                                                      | .74  |

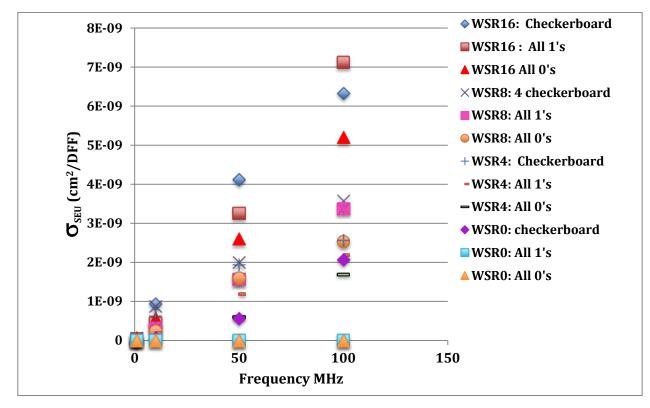

| Figure 47: 4 Clk 4 rst Direct CLKBUF SEU Cross Sections versus Frequency at LET = 20.6                                         |      |

| MeVcm <sup>2</sup> /mg                                                                                                         | .74  |

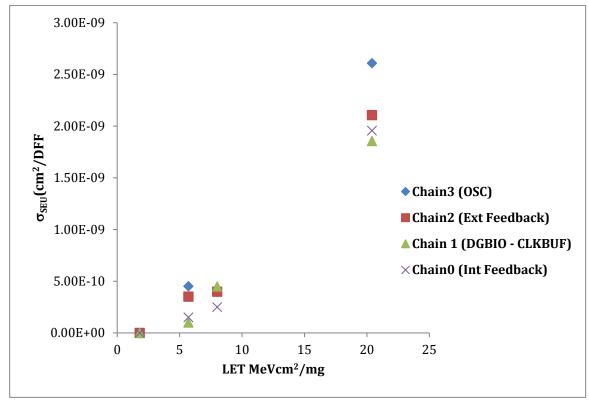

| Figure 48: WSR_PLL_1000_SET SEU DFF cross sections across LET. All chains are WSR0                                             | .76  |

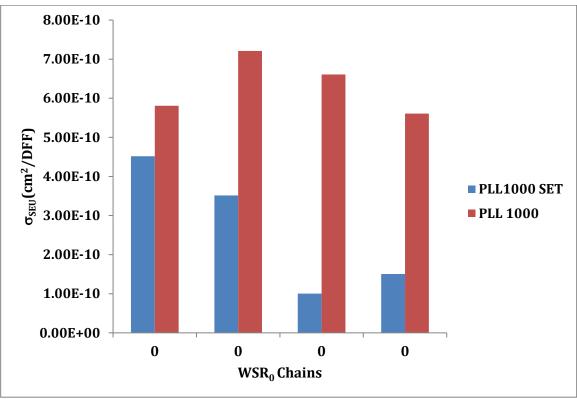

| Figure 49: Comparison of WSR_PLL_1000_SET and WSR_PLL_1000 at an LET = 5.7MeVcm <sup>2</sup> /mg                               | g    |

|                                                                                                                                | .77  |

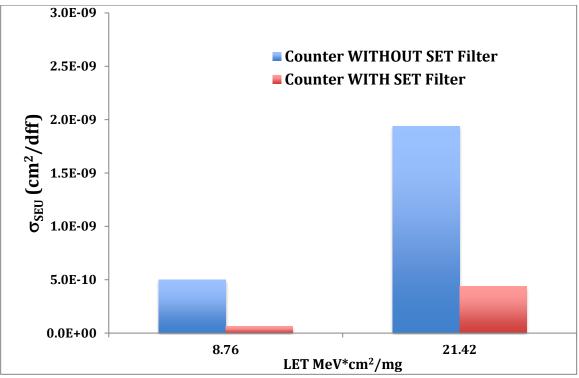

| Figure 50: Rev C Counter Arrays Single Bit sseus: without SET Filter versus with SET Filter at                                 |      |

| 50MHz                                                                                                                          | .78  |

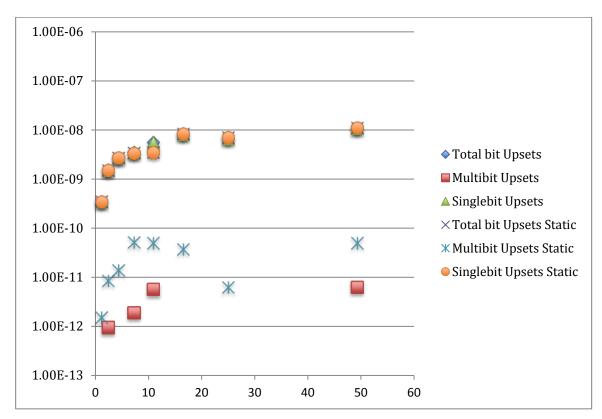

| Figure 51: Large SRAM SEU Cross Sections across LET. All memory patterns are 8-bit counters.                                   |      |

| The stored 8-bit counter is equivalent to its address' lower 8-bits.                                                           | .79  |

| Figure 52: Large SRAM SEU Cross Sections across LET. A comparison of LSRAM with DFF SET                                        |      |

| filters turned on versus DFF SET filters turned off. All memory patterns are 8-bit counters. The                               | е    |

| stored 8-bit counter is equivalent to its address' lower 8-bits.                                                               | . 80 |

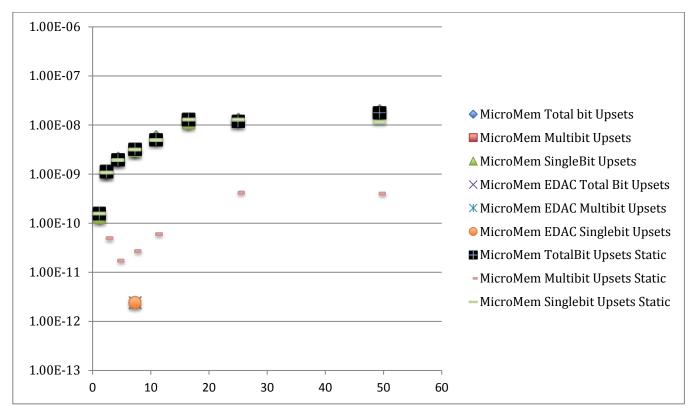

| Figure 53: uSRAM SEU cross sections across LET.                                                                                | 81   |

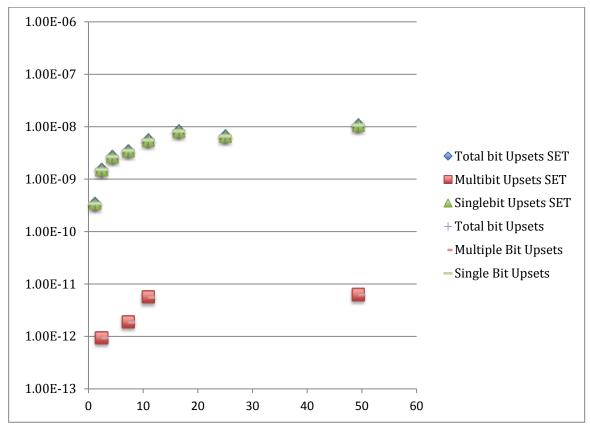

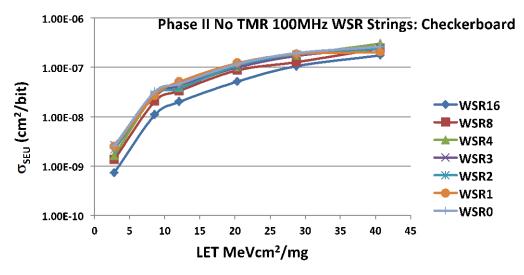

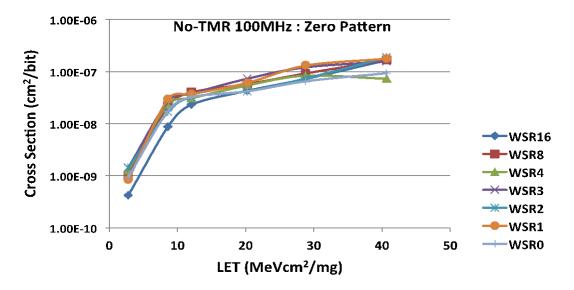

| Figure 54: ProASIC3 Heavy-ion data. Data pattern is checkerboard taken at 100MHz                                               | . 82 |

| Figure 55: ProASIC3 Heavy-ion data. Data pattern is All 0's taken at 100MHz                                                    | .83  |

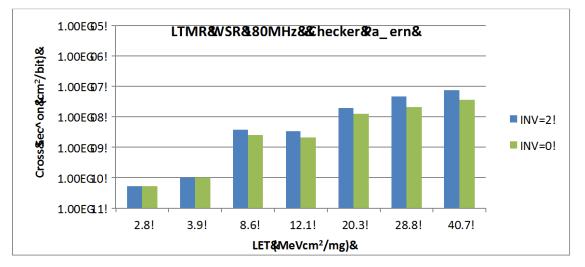

| Figure 56: ProASIC3 WSR <sub>0</sub> and WSR <sub>2</sub> circuits. Data pattern is checkerboard taken at 180MHz.              |      |

| LTMR was manually inserted per DFF.                                                                                            | .83  |

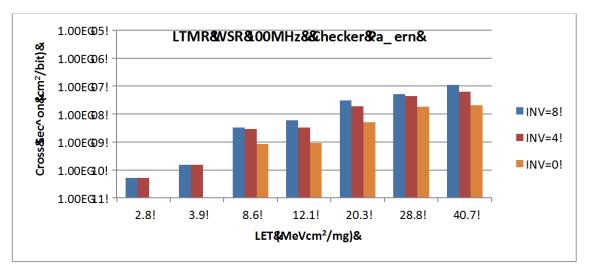

| Figure 57: ProASIC3 WSR <sub>0</sub> , WSR <sub>4</sub> , and WSR <sub>8</sub> circuits. Data pattern is checkerboard taken at |      |

| 100MHz. LTMR was manually inserted per DFF                                                                                     | . 84 |

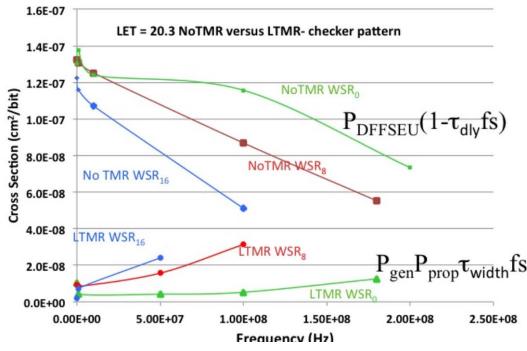

| Figure 58: Comparison of ProASIC3 heavy-ion $\sigma_{SEU}$ data: LTMR versus No-TMR                                            | . 84 |

#### 1. INTRODUCTION

The goal of this study was to perform an independent investigation of single event destructive and transient susceptibility of the Microsemi RTG4 device. The devices under test were the Microsemi RTG4 field programmable gate array (FPGA) Rev C. The devices under test will be referenced as the DUT or RTG4 Rev C throughout this document. The DUT was configured to have various test structures that are geared to measure specific potential susceptibilities of the device. Design/Device susceptibility was determined by monitoring the DUT for Single Event Transient (SET) and Single Event Upset (SEU) induced faults by exposing the DUT to a heavy ion beam. Potential Single Event Latch-up (SEL) was checked throughout heavy-ion testing by monitoring device current.

The objectives of this study are the following:

- Analyze DFF behavior in simple designs such as shift registers. Compare SEU behavior to more complex designs such as counters and finite impulse response (FIR) filters. Evaluating data trends helps in extrapolating test data to actual designs.

- Analyze global route behavior clocks, resets.

- Analyze configuration susceptibility.

# 2. DEVICES TESTED

#### 2.1 Device Specifics

The DUT part number is: RT4G150-CG1657M. We tested two revision bins: Rev B and Rev C. However, this document will only reference Rev C data. Rev B data has been published in an alternate document.

The following is a list of tested device by lot date code and test date:

- RT4G150-CB1657MSX449, lot date code: 1534 (TAMU2015Dec; LBNL2016Mar)

- RT4G150-CB1657PROTOX463, lot date code: 1548 (TAMU2016Oct; LBNL2016Oct)

- RT4G150-CB1657PROTO, lot date code: 1629 (TAMU 2016Oct-Nov; LBNL 2016Oct)

- RT4G150-CB1657PROTO, LDC 1638 (TAMU 2017March)

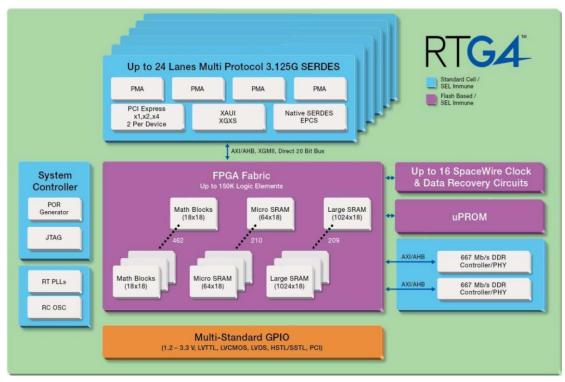

The DUT contains 158214 look up tables (4-input LUTs); 158214 flip-flops (DFFs); 720 user I/O; 210K Micro-SRAM (uSRAM) bits; 209 18Kblocks of Large-SRAM (LSRAM); 462 Math logic blocks (DSP or HMACC Blocks); 8 PLLs; 48 H-chip global routes (radiation-hardened global routes); 2 FDDRs; and 6 SERDES channels. Figure 1 is a block diagram illustrating the RTG4's internal components.

Figure 1: Block diagram of RTG4 internal components.

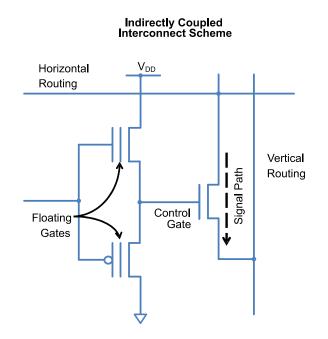

RTG4 FPGA devices are fabricated using a 65nm Flash technology, which provides industryleading low power consumption and also provides complete (to be tested) immunity to radiationinduced configuration upsets. Consequently, if the configuration is deemed to be 100% immune, the RTG4 devices never lose their functionality in the harsh space radiation environment. An additional advantage of Flash technology is that the configuration of the FPGA is retained through power cycles, unlike SRAM-based FPGAs, meaning that no companion devices are required for code storage, relieving board space, and eliminating additional component cost. Figure 2 is an illustration of one flash based configuration cell.

Figure 2: Directly coupled interconnection scheme for Microsemi RTG4 flash configuration cells.

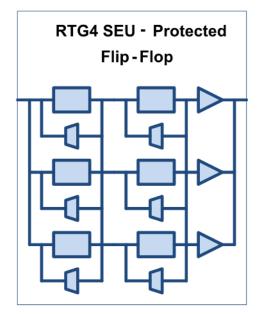

In addition, the manufacturer has implemented Single Event Effect (SEE) Radiation Hardened by Design (RHBD) circuitry that is available to the user such as: localized triple mode redundancy (LTMR) at each flip-flop; and hardened global routing networks (such as clocks). Figure 3 is an illustration of LTMR.

Figure 3: Localized TMR DFF scheme. Microsemi refers to it as self-correcting TMR (STMRFF).

# 3. BACKGROUND

Testing a Flash-based FPGA requires the user to test SEU behavior in the following device components: Configuration hardness, data path susceptibility, global structures and hidden logic (Single Event Functional Interrupt (SEFI) susceptibility).

#### 3.1 Cross Sections

SEU cross sections ( $\sigma_{seu}$ ) characterize how many upsets will occur during a radiation test. Generally a  $\sigma_{seu}$  is calculated by counting the number of observed upsets during irradiation and normalizing it (dividing by) the particle fluence:

General Terminology for heavy-ion testing:

- Flux: Particles/(sec-cm<sup>2</sup>)

- Fluence: Particles/cm<sup>2</sup>

$\sigma_{SEU} = \frac{\text{Number of Upsets}}{\text{Fluence}} (1)$

SEU cross sections are calculated at several linear energy transfer (LET) values (particle spectrum) as in equation (1). Particle flux-settings are determined per LET. It is desired to test with the highest flux in order to achieve acceptable SEU statistics. However, if the flux seems to overwhelm the device during a test, the flux is lowered. Proper flux is determined such that flux rate does not influence the number of errors observed during a test at a given LET.

# 3.2 Divide and Conquer Test Approach

An FPGA is a complex device with a variety of components containing varying susceptibilities to SEUs. Accordingly, tests are conducted such that components are isolated in order to develop an understanding of each of the component's SEU characteristics [1][2]. REAG categorizes FPGA components and their susceptibilities as follows:

$P(fs)_{error}$ : system or design  $\sigma_{seu}$

P<sub>configuration</sub>: Configuration  $\sigma_{seu}$

$P(fs)_{functionalLogic}$ : data path  $\sigma_{seu}$

$P_{\text{SEFI}}$ : hidden logic and global route  $\sigma_{\text{seus}}$

All  $\sigma_{SEUS}$  are calculated independently. It is important to note that configuration upsets (if the configuration bit is used by the design and enabled) will cause an upset in the functional operation. However, we denote this type of upset as a configuration upset not a functional logic upset. Functional logic upsets are categorized as malfunction that occurs due to SEUs affecting DFFs or combinatorial logic elements in the programmable user space.

$$P(fs)_{error} \propto P_{Configuration} + P(fs)_{functionalLogic} + P_{SEFI}$$

(2)

#### 3.3 Configuration Test and Analysis

Configuration SEUs are checked by performing a verify function via Microsemi Libero software. The software does not return an error count. It returns a pass-fail indication. This is deemed an acceptable evaluation because flash-based configuration is considered to have negligible susceptibility to SEUs. This has been shown with ProASIC3 SEU testing.

Configuration upsets may or may not cause a design (system level) error. If a configuration bit, that has changed state because of an SEU, is being used by the design and is in an enabled path of logic, then there is a chance that the changed state will cause system malfunction. Dynamic testing is required to investigate configuration upsets and their impact on system level functionality; i.e., this is not considered a configuration test – it is considered a dynamic functional test. In general, Configuration SEUs that directly affect active circuitry have error signatures that resemble stuck faults. This is because the flash configuration cannot be scrubbed; nor will a power cycle correct non-volatile configuration errors. The device will have to be reconfigured in order to correct configuration SEUs.

#### 3.3.1 Dynamic Test and Configuration Analysis

Dynamic testing concentrates on evaluating the SEU susceptibility of the design under analysis (DUA) during accelerated radiation testing. Such testing requires the DUT to be operating and its outputs to be monitored during irradiation. Deviations from expected values are reported and noted as error responses.

This is a challenging study because, as previously mentioned, the complexity of the FPGA devices has various components with different error signatures and susceptibilities. The component contribution to overall design  $\sigma_{seus}$  was given in equation (2). If tests are not constructed to isolate these components during the test and analysis phase, radiation data can be convoluted and difficult to process.

#### 3.4 Data Path and Global Upset Investigation:

#### 3.4.1 RTG4 Expected Single Event Upsets and Error Rate Calculation

Following convention, the bit-error rates ( $dE_{bit}/dt$ ) published in the Microsemi datasheets are calculated from shift register SEU characterization. It is important to note that DFF upsets are both corrected and masked by the LTMR circuitry. Therefore, the most significant upsets in the RTG4 device are due to transients; i.e., combinatorial logic data path SETs captured by DFFs. It has been shown that SET capture by a DFF tends to be directly proportional frequency [2][3]. As a result, radiation tests are performed at various frequencies to determine trends. Each radiation test counts the number of upsets observed during irradiation. The SEU cross section per test is defined to be the number of observed upsets normalized by the particle fluence per test. The goal is to use the SEU cross sections to calculate bit error rates per frequency. Error rates ( $dE_{bit}(fs)/dt$ ) calculated per test design and frequency are extrapolated to predict error rates (dE(fs)/dt) of space-flight FPGA circuitry as noted in equation 3.

$$\frac{dE(fs)}{dt} < \frac{dE_{bit}(fs)}{dt} * (\#UsedDFFs)$$

(3)

#### 3.4.2 Test Circuits used for Establishing SEU Cross Sections and Error Rates

Shift registers are the most common test circuit used in SEU radiation testing. Shift registers are considered to have a linear data path because each node only has one input and one output (i.e. fanout = fanin = 1). Due to the decrease in transistor geometries and capacitive node loading it has come to question if the calculated shift register  $dE_{bit}/dt$  can be applied to complex circuits. In other words, will the predicted system error rate be accurate using shift register data as parameters? As an example, counter architectures are not linear. They contain nets with fan-out and fan-in >1. The fan-out will change both the capacitive loading of cells and the utilization of routing resources within FPGA fabrics. Depending on the rise/fall time and width of a Single Event Transient (SET) the capacitive loading of a cell can filter away the SET. On the other hand, a SET that is not filtered can fan-out to multiple nodes and can have the effect of a multiple bit upset. As noted, variations of SET signatures exist and will depend on design topology and operational parameters.

Understanding the various upset event probabilities and their effects are essential when designing critical applications and predicting error rates. As a response, a more in-depth approach to SEE characterization of complex circuits has been developed and has been performed by NASA Goddard Radiation Effects and Analysis Group (REAG) on RTAXs and ProASIC3 FPGA devices. The testing technique incorporates testing shift registers and counters. The information extracted from the previous RTAXs-family and ProASIC3 evaluations has been used to develop the RTG4 study as follows:

- 1. In the RTAXs FPGAs, upsets were observed to be generated via the combinatorial logic data path not from the LTMR'd DFFs. Consequently, SET propagation and transient capture is the most significant source of DUT SEEs.

- 2. Global route SETs were observed in the ProASIC3 devices at low LET values.

- 3. Global route SETs were not observed in the RTAXs devices until high LET values but were still rare events.

- 4. With the RTAXs FPGAs, the potential for SET propagation through chains of combinatorial logic was attenuated at low Heavy Ion (HI) LET values. It was observed that after approximately 8 levels of logic, the SEE cross section (due to SET attenuation) decreased at low LET values. Emphasis is placed on the fact that this error signature only occurred at low LETs. This is because at Low LET values, generated SETs have less energy. Consequently, these low energy SETs do not have enough power to propagate through multiple levels of combinatorial logic gates.

- 5. SET propagation was not attenuated at higher HI LET values. As N increased, the SEE cross section increased (as expected) at higher LETs.

- 6. Circuits with higher fan-in to DFFs can produce lower threshold LETs cross sections. Hence, the error rate will be higher.

- 7. In the RTAXs FPGAs, as frequency increased, the SEE error cross section increased. This is because most of the upsets occurred from captured SETs in the design data paths and not the LTMR'd DFFs.

- 8. ProASIC3 configuration is flash memory. Flash configuration SEUs were extremely rare events.

#### 3.5 NASA DUT Preparation Plan

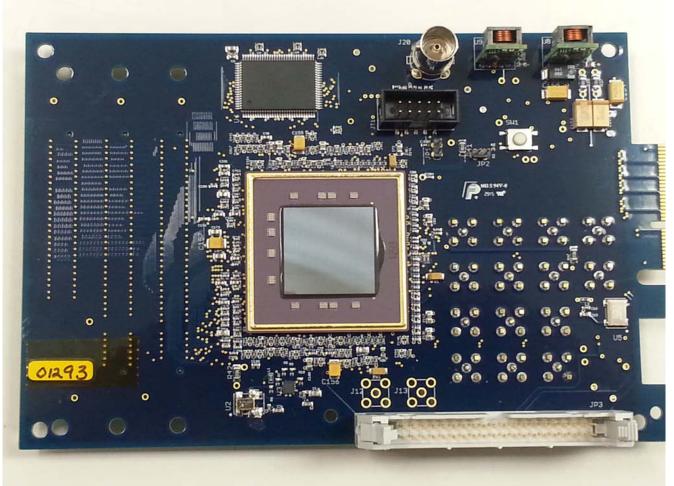

NASA has four populated boards with RT4G150-CG1657M devices. There are two boards that contain RTG4 Rev B FPGAs; and two boards that contain RTG4 Rev C FPGAs. The parts (DUTs) were thinned using mechanical etching via an Ultra Tec ASAP-1 device preparation system (illustrated in Figure 4). The Ultra Tec ASAP-1 system is a proven process previously used successfully on both Virtex-5QV and Virtex-5 parts. The parts have been successfully thinned to 70um – 90um. As previously mentioned, only Rev C FPGA SEE data is provided in this document.

Figure 4: Ultra Tec ASAP-1 device preparation system

Figure 5: Top side of DUT daughter board with de-lidded and thinned DUT.

Figure 6: Bottom side of DUT daughter board with de-lidded and thinned DUT.

# 4. TEST PROCEDURES AND BEST PRACTICES

#### 4.1 Functional Control

Types of DUT functional input control: clocks, resets, and data inputs.

Concerns and Challenges:

- Synchronizing inputs and managing skew between inputs. Challenging with high frequencies.

- Operating the device in a realistic manner:

- Do not over-load the device with unrealistic stimulus during radiation testing. If the device is operating in states that would never occur, then radiation data will not be characteristic.

- Do not under-load the device during radiation testing. If the device is underperforming, this means that a large amount of circuitry is not operating. This produces operational states with a large amount of logic masking; consequently, radiation data will not be characteristic.

#### 4.2 Monitoring Functionality

The following are general practices for monitoring FPGA functionality during heavy-ion testing.

• Compare DUT outputs to expected values

- Visually (only recommended as a supplement); i.e., watching the error indication on the error detection equipment (e.g., logic analyzer);

- Custom comparison circuitry (Low Cost Digital Tester: LCDT).

- Differentiate upset types: e.g., clock tree SET, flip-flop (DFF) SEU, combinatorial logic (CL) captured SET, or configuration faults.

- Count SEUs (upset statistics): After the upsets have been detected and differentiated, they need to be counted. The higher the number of upsets, the better the statistics.

# 4.3 Automated Data Capture and Messaging

The following are general practices for data capture during heavy-ion testing.

- Reliable data capture:

- Follow synchronous design rules which include how to capture asynchronous signals.

- Determine minimal sampling frequency (when applicable).

- Understand the limitations of the automated test equipment with respect to the DUT (e.g., memory-storage space, I/O voltage, I/O interface, and speed).

- Once erroneous data are captured, they should be packaged and stored (e.g., sent to a host PC). Example of package fields:

- Timestamp,

- Expected value, and

- Received value.

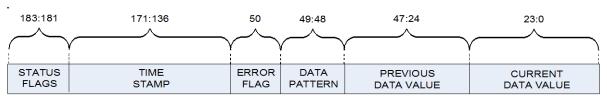

| Field          | # of Bits | Description                                                                                                                                                                                                                                                                                          |

|----------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Current Value  | 24        | Current captured data (cycle N)                                                                                                                                                                                                                                                                      |

| Previous Value | 24        | Previous captured data (cycle N-1)                                                                                                                                                                                                                                                                   |

| Data Pattern   | 2         | Unused: data pattern is always checkerboard                                                                                                                                                                                                                                                          |

| Error Flag     | 1         | Unused                                                                                                                                                                                                                                                                                               |

| Time Stamp     | 32        | Cycle counter. Must multiply by the DUT frequency to convert to time. Used to determine error burst sequences                                                                                                                                                                                        |

| Status         | 3         | Indicates type of error record:<br>"001" is a timeout – one of the shift clocks not detected<br>"011"Out of timeout – all shift clocks are recovered<br>"000" Error or non-error – current value does not equal<br>previous value<br>"010" Debug check – command was sent to check value<br>settings |

Figure 7: Sample Message from the LCDT to the Host PC. Message describes the SEU and Includes a Timestamp

# 4.4 Monitoring DUT Power and SEL Investigation

The following are general practices for monitoring DUT power.

- Use of power supply monitors.

- Use of an automated monitor/capture system is beneficial. Provides the ability to store and perform post processing on power data. Great for identifying particular error signatures.

- Power glitching or Single Event Latch-up (SEL) can cause the system to cease operation or be damaged. Hence it is best practice to separate test vehicle power from DUT power.

- It is also ideal to have current limiting circuitry for the test vehicle and the DUT.

# 4.5 Investigating SEFIs

We look for particular error signatures to determine SEFI occurrence:

- Read-back of configuration returns a fail.

- Unable to connect to the device to read-back assume problem in the configuration interface.

- Global SEFIs in functional logic not performed during static read-back.

- Reset correction: clock tree or reset tree (global routing).

PSEFI is calculated using equation (4). Test until upset occurs and record the fluence.

$$\sigma_{\rm SEFI} = \frac{1}{(fluence)}$$

(4)

The following sections describe the construction of the LCDT including communication interfaces with the DUT and user PCs.

# 5. TEST HARDWARE (TEST SYSTEM)

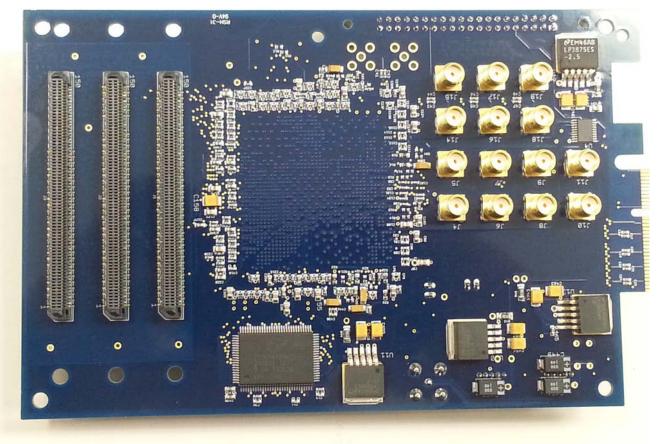

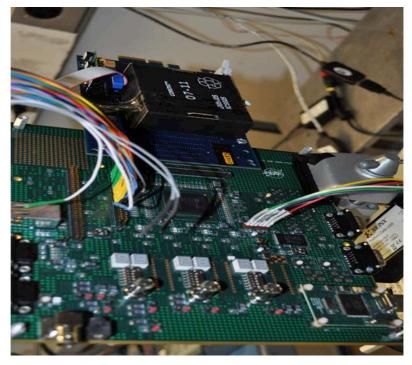

In this study, a test system refers to the NEPP (NASA Goddard developed) LCDT3 and a custom daughter card containing the DUT.

#### 5.1 Pictures of the Test System

Figure 8 and Figure 9 are pictures of the RTG4 populated DUT board connected to the LCDT tester.

Figure 8: Test Setup - Connected LCDT3 and Daughter Card (1)

Figure 9: Test Setup - Connected LCDT3 and Daughter Card (2)

#### 5.2 LCDT Architectural Overview

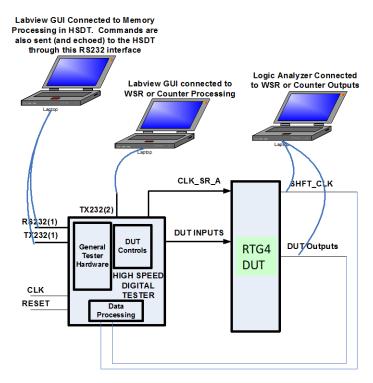

As previously mentioned, the test system consists of a Mother Board (FPGA Based Controller/Processor) and a daughter board (containing DUT and its associated necessary circuitry). The DUT controller/processor is instantiated as a sub component within the LCDT. A block diagram is illustrated in Figure 10.

The objective of this DUT controller/processor is to supply inputs to the DUT device and perform data processing on the outputs of the DUT. The LCDT communicates with a user controlled PC. The

user PC interface is LabVIEW. LabVIEW code was designed to send user specified commands to the motherboard and receive information from the motherboard. Please see Documents: "LCDT" and "General Tester" for further information concerning the LCDT functionality. The LCDT is connected to the DUT as shown in the following block diagram.

Figure 10: System Level Tester Architecture for the DUT configured as a counter.

# 5.2.1 RS232 communication from the LCDT to the Host PC

All RS232 communication from the LCDT to the host PC is prefaced with a header. Information from the LCDT to the Host PC is one of the following listed in Table 1: an alive-timer, a command echo, or an Error Record.

Table 1: A list of the LCDT to Host PC RS232 Header bytes. Only the LCDT uses header information. The host PC sends pure commands to the LCDT without headers.

| Header      | Description                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------|

| 00 FA F3 20 | Alive Header No data bytes follow (i.e. only<br>the header is sent from the LCDT to the PC)                               |

| 00 FA F3 22 | Command Echo. 4 data bytes follow that<br>represent the command that was previously sent<br>from the Host PC to the LCDT. |

| 00 FA F3 21 | Data Error Record: 23 bytes follow.                                                                                       |

#### 5.3 RS232 communication From the Host PC to the LCDT

Communication from the host PC to the LCDT does not contain a header. Information sent from the host PC to the LCDT are commands and are all 4 bytes in length The interface is controlled by a user GUI designed with LabVIEW software.

#### 5.3.1 User GUI

Commands are sent by typing specific values into LabVIEW fields or controlling LabVIEW on/off buttons listed on the screen.

#### 5.3.2 User Interface and Command Control

The user controls the tests via a LabVIEW interface running on a PC. The PC communicates with the LCDT with a RS232 serial link. The format of communication is a command/Data 4 byte word.

| Table 2 : Summary of Commands Used in DOT Tests |                   |    |    |    |                                                                                                                                                                                                    |

|-------------------------------------------------|-------------------|----|----|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command #                                       | Command           | D0 | D1 | D2 | Description                                                                                                                                                                                        |

| 01                                              | Reset LCDT        | n  | n  | n  | Resets Tester and DUT (stops DUT clocks and makes DUT reset active)                                                                                                                                |

| 03                                              | Reset Counter     | N  | N  | n  | RESETS Counters without resetting tester<br>circuitry (only used in counter tests)                                                                                                                 |

| 02                                              | Start Testing     | N  | N  | N  | Starts the DUT clocks                                                                                                                                                                              |

| A0                                              | Clock divider     | у  | у  | n  | D0 (LSB) and D1 (MSB) are the Clock<br>frequency divider of 100mhz. The synthesized<br>LCDT3 clock output is sent to the DUT. This<br>signal is the DUT's system clock.<br>Default=0 (no division) |

| 91                                              | Pattern Selection | у  | n  | n  | Only used in WSR tests:<br>D0 = 0=> all 0's<br>D0 =1 => all 1's<br>D0 >1 => checkerboard                                                                                                           |

| 06                                              | WSR Halt command  | n  | n  | n  | Stops the DUT clocks. Does not perform a reset.                                                                                                                                                    |

# 6. DUT TEST STRUCTURES AND DYNAMIC ACCELERATED TESTING

In this study, we started with simple test structures; increased complexity per test structure; study trends; and then tried to make sense out of the convoluted data obtained from complex test structures.

Test Structure Considerations Taken from the NASA Electronics Parts and Packaging (NEPP) FPGA SEU Test Guidelines:

https://nepp.nasa.gov/files/23779/fpga\_radiation\_test\_guidelines\_2012.pdf .

Referencing the FPGA SEU Test Guidelines manual, for simple test structures, they should have the ability to flush SEU's (post-detection)... i.e., test circuits should have the ability to keep working after an SEU occurs to increase statistics of each beam run. This helps to increase statistics during testing. In addition, the tester (for these simple test structures) should be robust enough to resynchronize to new DUT expected values caused by SEUs; i.e., expected values should be dynamic based off of impact of SEUs. These statements are not necessarily implementable in a complex system. However, in shift registers and counters; i.e., flushable test systems, it is feasible.

#### 6.1 Challenges for Testing

Microsemi computer aided design (CAD) software is new:

- Place and route is not optimal yet. Hence, it is difficult to get high speed without manual placement.

- Early versions of the CAD tools did not handle some components properly: e.g., asynchronous resets were not tied correctly to components, DSP blocks (HMACCs) had bugs, Memory blocks did not have adequate power ties (such that current would rise during testing), etc. With CAD tool bugs, some test results are deemed useless or expected to change with upgraded CAD tools. This wastes test time.

- Microsemi reports that devices show TID tolerance up to 160 krad(Si). Although, when testing with heavy-ions, dose tolerance will be much higher. TID limits the amount of testing per device. The number of devices is expensive and is limited for radiation testing. A large variety of tests are required.

Current consortium participants:

- NEPP

- Aerospace

- JPL

- Potential: ESA

#### 6.2 Overview of DUT Test Structures

Table 3 is an overview of the DUT test structures that were analyzed in heavy ion testing. Some of the test structure designs were created with variations for trend analysis.

| Table 3: Overview of Test Structures                                                          |                   |                                 |  |  |  |

|-----------------------------------------------------------------------------------------------|-------------------|---------------------------------|--|--|--|

| Test Structure                                                                                | Frequency Range   | SEU Flow-Through<br>(Flushable) |  |  |  |

| Global routes                                                                                 | 2 KHz – 150 MHz   | N/A                             |  |  |  |

| Shift registers (WSR)                                                                         | 100 KHz – 160 MHz | Yes                             |  |  |  |

| Counters (Count Array):<br>Parallel independent counters                                      | 5 MHz – 100 MHz   | Yes                             |  |  |  |

| Finite impulse response (FIR)<br>(chain of DSP 18x18 multiplier<br>accumulate blocks (HMACC)) | 1 MHz - 100 MHz   | Yes                             |  |  |  |

#### 6.3 Windowed Shift Registers (WSRs)

#### 6.3.1 General Operation

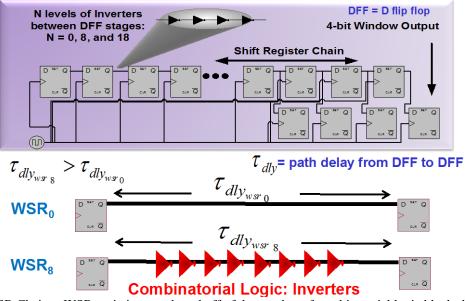

A windowed shift register (WSR) is based off of the traditional shift register used for SEU testing. The difference between a WSR and a traditional shift register is that the last 4 stages of the shift register are captured into a 4-bit window. This helps with signal integrity and reliability of data capture between the DUT and the tester. Figure 11 illustrates a WSR with and without inverter logic between DFF stages.

A variety of WSR chains were tested and analyzed for SEE susceptibility to heavy ions. WSR variations are based off of the number of combinatorial logic blocks between each DFF stage; the number of DFF stages per chains; DFF SET filter usage; and how the WSR DFFs are connected to global routes. In Figure 11, WSR<sub>0</sub> indicates a WSR with no combinatorial logic gates. WSR<sub>8</sub> indicates a WSR with 8 levels of combinatorial logic gates between each DFF stage. In essence, the number associated with a WSR indicates the number of inverters inserted between each DFF stage. All stages within one WSR chain have equivalent circuits.

Figure 11: WSR Chains. WSR variations are based off of the number of combinatorial logic blocks between each DFF stage; the number of DFF stages per chains; and how the WSR DFFs are connected to global routes. In this figure, WSR<sub>0</sub> indicates a WSR with no combinatorial logic gates. WSR<sub>8</sub> indicates a WSR with 8 levels of combinatorial logic gates between each DFF stage.

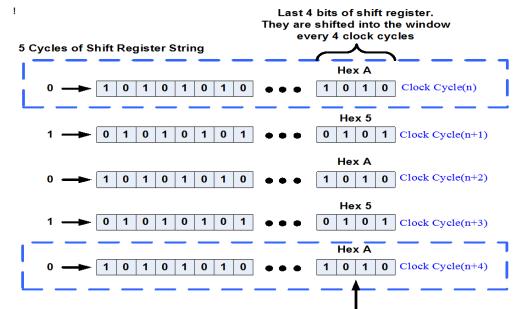

Figure 12 is a timing diagram that illustrates WSR operation under normal conditions.

Every 4 cycles, the last 4-bits are equivalent. Therefore, the window is static under normal operating conditions Figure 12: WSR Functional Behavior

# RTG4

#### 6.3.2 WSRs and LCDT Requirements

The following are requirements for LCDT control of the WSR chains:

- LCDT must supply DUT clocks. Clock frequency is command driven by the user and physically controlled by the LCDT.

- Active high Resets (one per WSR chain) RST<sub>0</sub>, RST<sub>4</sub>, RST<sub>8</sub>, RST<sub>16</sub>.

- 2-bit MUX control (see Table 4) to select WSR data input pattern:

| MUX: Bit1 Bit0 | Data Pattern |  |  |

|----------------|--------------|--|--|

| 00             | All0's       |  |  |

| 01             | All 1's      |  |  |

| 10             | Checkerboard |  |  |

| 11             | Checkerboard |  |  |

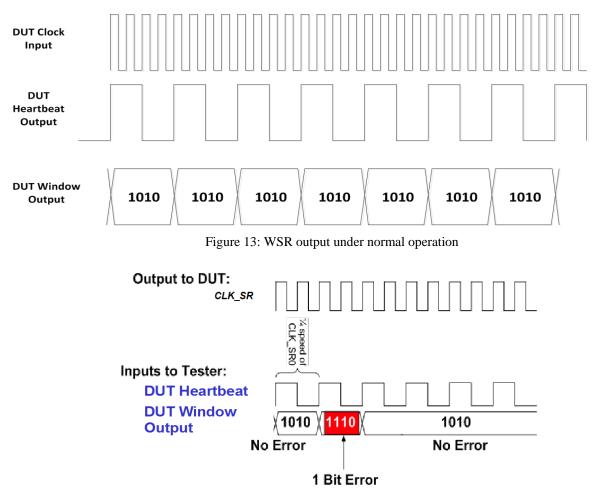

#### 6.3.3 WSR SEU Data Monitoring and Capture

- Heartbeat monitoring:

- DUT heartbeat output will be <sup>1</sup>/<sub>4</sub> the speed of the DUT clock input.

- DUT heartbeat is oversampled by >4x of the heartbeat speed by the LCDT and is passed through a metastability (synchronizer) circuit. Output of the heart detect metastability circuit is edge detected (rising). The edge is under watchdog to make sure that the system hasn't died.

- Expected data monitoring:

- Because the window should be static, any change in the window is detected and reported to the host PC. LCDT oversamples the DUT output window in order to potentially detect change.

- Each WSR window is monitored for data change. Data change signifies SEU.

- SEUs are differentiated: single bit, versus stuck, versus burst upsets (global).

#### WSR window stays constant unless there is a SEU. WSR provides optimal signal integrity for SEE testing An error record is created and is sent to the Host PC Figure 14: WSR Operation with SEU

#### 6.3.4 WSR Error Reporting Record

#### Table 5: Error record for First Round of WSR Testing

| Record Bit<br>Position | Data Field                                                        |

|------------------------|-------------------------------------------------------------------|

| 15:0                   | Bad data of current clock cycle                                   |

| 31:16                  | Data last clock cycle                                             |

| 57:56                  | Pattern Selection:<br>00 All 0's<br>01 All 1's<br>10 Checkerboard |

# RTG4

|         | 11 Checkerboard                                                                                                                                                                               |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60      | Chain0 PLL lock (1 – indicates locked; 0 indicates unlocked). Only used for PLL WSR tests.                                                                                                    |

| 65      | Unused (no PLL for Chain1)                                                                                                                                                                    |

| 66      | Chain2 PLL lock (1 – indicates locked; 0 indicates unlocked). Only used for PLL WSR tests.                                                                                                    |

| 67      | Chain3PLL lock (1 – indicates locked; 0 indicates unlocked). Only used for PLL WSR tests.                                                                                                     |

| 64      | Chain0 Heartbeat (indicates if a chain's heart beat is alive): 0 indicates alive, 1 indicates dead)                                                                                           |

| 65      | Chain1 Heartbeat (indicates if a chain's heart beat is alive): 0 indicates alive, 1 indicates dead)                                                                                           |

| 66      | Chain2 Heartbeat (indicates if a chain's heart beat is alive): 0 indicates alive, 1 indicates dead)                                                                                           |

| 67      | Chain3 Heartbeat (indicates if a chain's heart beat is alive): 0 indicates alive, 1 indicates dead)                                                                                           |

| 95:80   | Frequency selection for WSR <sub>0</sub>                                                                                                                                                      |

| 177:146 | Timer – clock cycles (granularity of 1 timer clock cycle is equal to DUT operational speed)                                                                                                   |

| 183:181 | Record indicator:<br>000: debug<br>010: SEU error record<br>100: In timeout (one of the heart beats has died)<br>101: Out of timeout (one of the heart beats was dead and now has come alive) |

# 6.3.5 Post Processing of LCDT WSR Data Analysis for First Round of Testing

Post processing is performed on all error records (see previous section).

As previously mentioned, error signatures are differentiated between:

- 1-bit errors within a window.

- Multiple-bit errors within a window.

- Burst Errors:

- Clock upsets: error signatures with WSRs generally last nanoseconds to microseconds.

- Configuration-bit upset: error signatures will appear as a stuck fault.

Timestamps and window data values are used to differentiate error signatures during the postprocessing phase.

SEU cross sections are calculated for each error signature. They are calculated by counting the number of bits upsets within a window as in (5). Consecutive window upsets are considered part of a burst and are not part of a single bit upset.

$$\sigma_{_{WSRseu}} = \frac{\#WSRerrors}{(fluence)^* \#WSR\_DFFs}$$

(5)

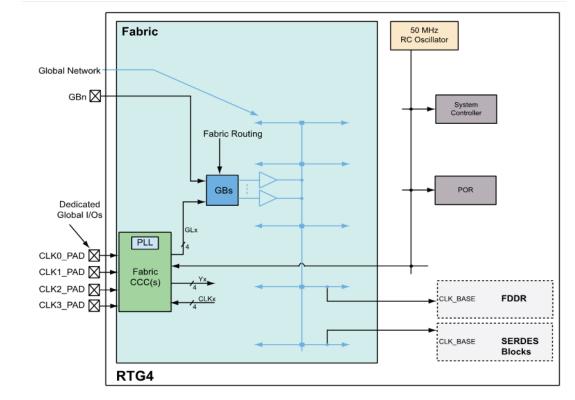

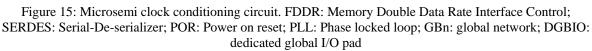

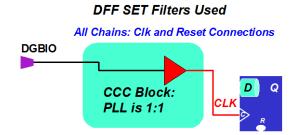

6.4 Global Routes and Microsemi RTG4 Clock Conditioning Circuit (CCC)

A CLKBUF is a RTG4 internal buffer that connects to a hardened global route. Input to the CLKBUF can only be a dedicated global I/O pad (DGBIO). A CLKINT is a RTG4 internal buffer that connects to a hardened global route. Input to a CLKINT can come from fabric or any input.

CLKINTs are generally used in conjunction with Microsemi clock conditioning circuits (CCC). A CCC block is illustrated in Figure 15.

A variety of designs were created to analyze different global circuit usage.

#### 6.4.1 Resets

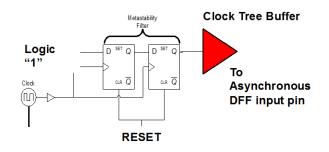

Figure 16: Asynchronous assert synchronous de-assert reset

Asynchronous assert synchronous de-assert (AASD) is the traditional method of reset implementation in NASA driven systems. The AASD reset is illustrated in Figure 16. This is a requirement for the protection of a mission in case of loss-of-clock. Synchronization is performed prior to clock tree connection. The AASD global reset is connected to the asynchronous pin of each DFF; however, it is synchronized to the clock and is hence synchronous. Rev B tests implemented pure AASD via asynchronous reset tree connections to DFFs. AASD was not used in Rev C designs. Rev C designs use a pure synchronous reset.

# 6.5 DUAs Based on WSR and Global Route Variations – 1<sup>st</sup> Round of RTG4 Rev C Heavy Ion Testing

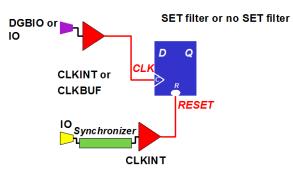

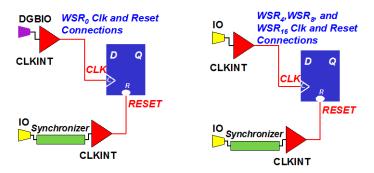

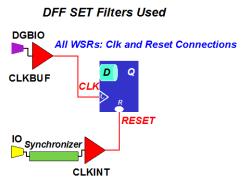

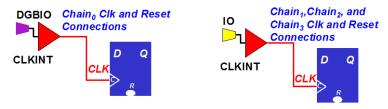

Figure 17: General schematic showing the potential variations in clock connections. The DFF can be configured to have SET filters at their data input pin or not to have SET filters.

In the first round of testing, Rev C WSR designs were varied by combinatorial logic block insertions and clock connections. Clocks are supplied to the DUT from the LCDT tester output to a DUT input pin. The DUT input pin (used for the clock) was either a dedicated clock I/O (DGBIO) or a normal I/O. All clocks are placed on a clock tree. Clocks are place on a clock tree via a RTG4 CLKBUF or CLKINT buffer component. A CLKINT buffer is a hardened clock tree connection via a

buffer for normal I/O pins. A CLKBUF is a hardened clock tree connection via a buffer for DGBIO. All WSR DFF data input pins either have the DFF SET filter turned on or turned off. Figure 17 is a schematic that illustrates potential variations for clock to WSR connections. The following provides more detail per DUT WSR designs used in the 1<sup>st</sup> round of Rev C heavy ion testing.

#### 6.5.1 Design A: 4 Clock 4 Reset DUA