#### Printed Circuit Board Inspection and Quality Control – PCB Failure Causes and Cures (Workshop G)

(workshop G)

Bhanu Sood Reliability and Risk Assessment Branch Safety and Mission Assurance Directorate NASA Goddard Space Flight Center

Phone: +1 (301) 286-5584 bhanu.sood@nasa.gov August 8<sup>th</sup> and 9<sup>th</sup>, 2018

1

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

2

Disclaimer

The material herein is presented "for guidance only". We do not warrant the accuracy of the information set out on this

presentation. It may contain technical inaccuracies or errors and/or non-updated data.

Information may be changed or updated without notice.

August 8th and 9th, 2018

#### **Course Outline**

3

- Section 1: Introduction

- Section 2: PCB Technology

- Section 3: Moisture

- Section 4: Tests and Inspection

- Section 5: Closure

#### What is Reliability?

Reliability is the ability of a product to properly function, within specified performance limits, for a specified period of time, under the life cycle application conditions

- <u>Within specified performance limits</u>: A product must function within certain tolerances in order to be reliable.

- For a specified period of time: A product has a useful life during which it is expected to function within specifications.

- <u>Under the life cycle application conditions</u>: Reliability is dependent on the product's life cycle operational and environmental conditions.

4

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

| When a Product Fails, There Are Costs                                                                                       |                     |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------|

| • To the Manufacturer                                                                                                       |                     |

| <ul> <li>Time-to-market can increase</li> </ul>                                                                             |                     |

| <ul> <li>Warranty costs can increase</li> </ul>                                                                             |                     |

| <ul> <li>Market share can decrease. Failures can stain the<br/>reputation of a company, and deter new customers.</li> </ul> |                     |

| • Claims for damages caused by product failure can increase                                                                 |                     |

| • To the Customer                                                                                                           |                     |

| o Personal injury                                                                                                           |                     |

| <ul> <li>Loss of mission, service or capacity</li> </ul>                                                                    |                     |

| <ul> <li>Cost of repair or replacement</li> </ul>                                                                           |                     |

| <ul> <li>Indirect costs, such as increase in insurance, damage to<br/>reputation, loss of market share</li> </ul>           |                     |

| Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov) 5 August 8th and 9th, 2018                                                      | Bhanu Sood, NASA GS |

# From 2002 - 2005, Field Failures of These **Devices Amounted to over \$10B in Losses**

| Manufacturer               | IC function                        | Package type   | Final product                              |

|----------------------------|------------------------------------|----------------|--------------------------------------------|

| Motorola                   | Frequency<br>Synthesizer, etc      | Unspecified    | Automotive anti lock brake<br>system (ABS) |

| Philips                    | Unspecified                        | 80 pin QFP     | Quantum, Hard disk drive                   |

| Cirrus Logic               | HDD controller                     | 208 pin QFP    | Fujitsu, Hard disk drive                   |

| Infineon                   | SIPMOS Small-<br>Signal-Transistor | 4 pin SOT 223  | Unspecified                                |

| Fairchild<br>Semiconductor | Low Voltage Buffer<br>Liner Driver | 48 pin TSSOP   | Seagate                                    |

|                            | N-channel MOSFET                   | Various TSSOPs | HP                                         |

| Maxim                      | Unspecified                        | 48 pin TQFP    | Sony                                       |

| Intersil Corp              | LSI's for WLAN                     | 20 pin QFN     | Unspecified                                |

| Conexant                   | Unspecified                        | ETQFP          | Unspecified                                |

| LSA                        | Unspecified                        | 128 pin TQFP   | Unspecified                                |

6

GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

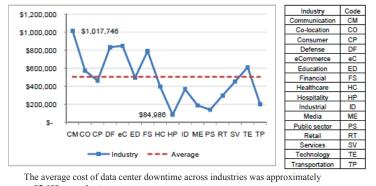

### **Cost of a Single Unplanned Data Center Outage Across 16 Industries**

7

\$5,600 per minute.

Ref: Ponemon Inst., "Calculating the Cost of Data Center Outages," Feb. 1, 2011.

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

# **Electrolytic Capacitors : Field Failures**

One computer company incurred \$300 million financial charges to replace the motherboards having faulty capacitors

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

8

# **Reliability Requires** that we Manage the Supply Chain

- Many companies do not adequately consider • quality and reliability in the creation and management of efficient and cost effective supply chains

- Thus, many companies do not know what they are • getting and what is changing

9

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

10

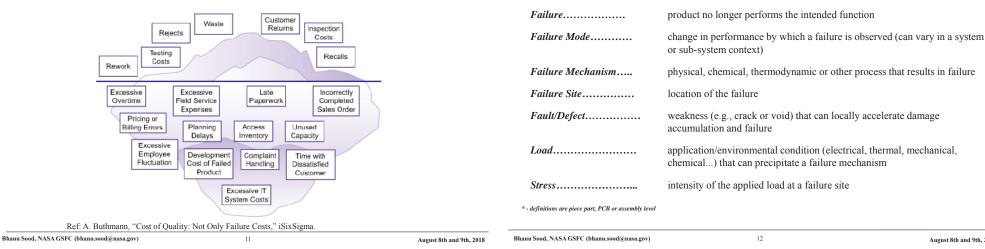

**Some Failure Related Definitions\***

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

#### **Iceberg Model of Cost of Poor Quality**

August 8th and 9th, 2018

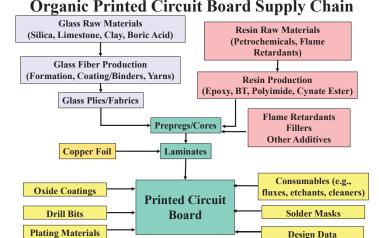

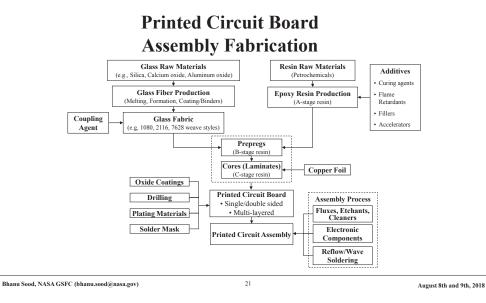

#### **Organic Printed Circuit Board Supply Chain**

August 8th and 9th, 2018

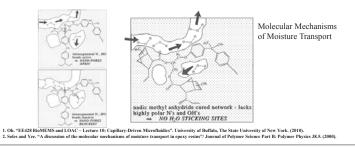

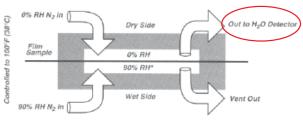

#### **PCB Failures – Moisture**

- Printed circuit board (PCB) quality, reliability and functionality are highly influenced by moisture (both ambient and internal).

- PCBs witness moisture at various stages:

- Lamination Wet process

- Assembly Screening

- Rework Storage

- Transportation Operation

- Maintenance

- Moisture can be initially present in the epoxy glass prepreg, absorbed during the fabrication of PCB or diffuse into PCB during storage

- Presence effects the mechanical properties (Tg, CTE) and electrical performance.

- PCB handling and storage guidelines are required to prevent inadvertent damage and maintain reliability.

#### **PCB Failures – Process**

- The transition to lead-free soldering of printed circuit boards (PCBs) using solder alloys such as Sn/Ag/Cu

has resulted in an increase in peak temperature exposures (by 30-40°C) and longer time above liquidus (by

15-30 seconds) during assembly compared with eutectic Sn/Pb solders.

- · Rework and repair of assembled circuit boards also contributes to additional high temperature exposures.

- The high temperature exposures associated with lead-free soldering can alter the circuit board laminate material properties and can affect the performance and reliability of the PCB and entire electronic assembly.

- Knowledge of laminate material properties and their dependence on the material constituents, combined with their possible variations due to lead-free soldering exposures is an essential input in the selection of laminates for appropriate applications.

14

| Bhanu Sood | NASA GSEC | (bhanu.sood@nasa.gov) |

|------------|-----------|-----------------------|

|            |           |                       |

```

13

```

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

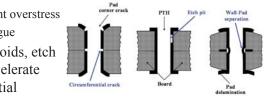

### **Board Level Failures**

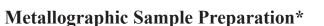

#### Plated Through Hole (PTH)/Via

- Fatigue cracks in PTH/Via wall

Overstress cracks in PTH/Via wall

Land corner cracks

- 4. Openings in PTH/Via wall 5. PTH/Via wall-pad separation

#### Electrical

6. Electrical overstress (EOS)7. Signal interruption (EMI)

#### Board

8. CFF (hollow fiber)

9. CFF (fiber/resin interface)

10. Electrochemical migration

11. Buckling (warp and twist)

#### **Copper Metallization**

12. Cracks in internal trace

13. Cracks in surface trace

14. Corrosion of surface trace

#### **Assembly Level Failures**

#### **Solder Interconnect**

- · Poor Solderability/Wettability

- Tombstoning; Can accelerate other solder failure mechanisms

- Overstress Interconnect Failures

- Solder Fracture (accelerated by intermetallic formation)

- Wearout Interconnect Failures

- Solder Fatigue, Solder Creep

- Solder Bridging

- Component Failure due to Handling

### Common Failures in Today's PCB

- Initiated at plated through holes (PTHs)

- Initiated by handling (bow and twist)

- Pad cratering (stress)

- Conductive filament formation (CFF)

- Electrochemical migration (PCB cleanliness)

#### Section - I

#### Introduction to PCB Technology and PCB Fabrication Materials

18

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

17

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

# **Printed Circuit Board**

Printed circuit boards are the baseline in electronic packaging – they are the interconnection medium upon which electronic components are formed into electronic systems.

FR-4 PCB materials are glass reinforced PCBs.

- Epoxy resin reinforced with woven glass.

- "FR" stands for flame retardant.

# **PCB** Classification

- PCBs are generally classified based on the following criteria:

- Dielectric materials used Epoxy, Bismaleimide Triazine, Cyanate Ester, Polyimide, Polytetraflouroethylene (PTFE), Phenolics, Polyester

- Reinforcement materials Glass fabric, Kevlar fabric, PTFE fabric, Paper, Polyethylene terephthalate (polyester), Silicon carbide

- Circuit type Digital, Analog, Mixed, RF, Microwave

- Electronic components Through-hole, Surface-mount, Mixedtechnology

- Board construction Single-sided, Double-sided, Multilayer, Flex, Rigidflex

- Design complexity Circuit density, and Low, moderate or high manufacturability

- There are differences in materials, processing steps or both depending on the PCB

#### **Constituents of FR-4 Laminates**

| Constituent     | Major function (s)                                                                      | Example material (s)                                            |

|-----------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Reinforcement   | Provides mechanical strength and electrical properties                                  | Woven glass (E-grade) fiber                                     |

| Coupling agent  | Bonds inorganic glass with organic resin<br>and transfers stresses across the structure | Organosilanes                                                   |

| Resin           | Acts as a binder and load transferring agent                                            | Epoxy (DGEBA)                                                   |

| Curing agent    | Enhances linear/cross polymerization in the resin                                       | Dicyandiamide (DICY),<br>Phenol novolac (phenolic)              |

| Flame retardant | Reduces flammability of the laminate                                                    | Halogenated (TBBPA),<br>Halogen-free (Phosphorous<br>compounds) |

| Fillers         | Reduces thermal expansion and cost of the laminate                                      | Silica,<br>Aluminum hydroxide                                   |

| Accelerators    | Increases reaction rate, reduces curing<br>temperature, controls cross-link density     | Imidazole,<br>Organophosphine                                   |

22

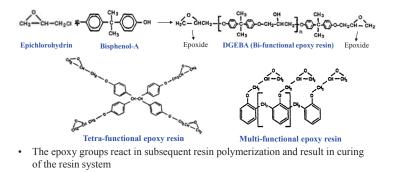

# **Constituents of FR-4 Laminates**

#### -Resin-

- Diglycidyl Ether of Bisphenol-A (DGEBA) is the epoxy resin used in FR-4 laminates

- DGEBA is derived from the reaction of Epichlorohydrin with Bisphenol-A

23

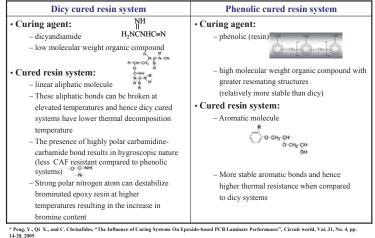

# **Curing Agents Comparison\***

24

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

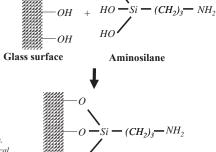

### **Coupling Agents**

- Coupling agents bond inorganic glass fibers to organic epoxy resin

- They take care of high magnitude of shear forces that are established in bonding interface due to a significant difference in the CTE (10X) of glass fibers and epoxy resin, when subjected to high temperatures

- Ex: Organo silanes Y-(CH<sub>2</sub>)<sub>n</sub>-Si (OX)<sub>3</sub> (Y-organo functional group; OX- silicon functional group)

#### Fillers

| Common filler materials | Typical functions                         |

|-------------------------|-------------------------------------------|

| Silica                  | Reduce cost                               |

| Hydrated alumina        | Decrease coefficient of thermal expansion |

| Aluminum Silicate       | Improve flammability                      |

| Ceramic Zircon          | Reduce moisture absorption                |

| Calcium Carbonate       | Increase thermal conductivity             |

| Aluminum Powder         | Increase compressive yield strength       |

| Mica                    | Improve arc resistance                    |

| Magnesium Silicate      | Increase surface hardness                 |

| Zirconium Sulphate      | Improve thermal shock resistance          |

|                         | Reduce tensile strength                   |

|                         | Decrease flexural strength and modulus    |

|                         | Reduce volume resistivity                 |

| 25 |

|----|

|    |

25

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

26

August 8th and 9th, 2018

#### Accelerators

| Туре            | Characteristics                                                                                                                                                              | Chemical Structure                |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Organophosphine | <ul> <li>Storage stability</li> <li>Low water absorption</li> <li>Good acceleration</li> <li>Good electrical property*</li> <li>Good heat and humidity resistance</li> </ul> | p-[()]3                           |

| Imidazole       | <ul> <li>High heat resistance</li> <li>High reactivity</li> <li>Poor electrical property*</li> <li>High water absorption</li> <li>Good acceleration</li> </ul>               | N CH <sub>2</sub> CH <sub>2</sub> |

| Lewis Base Salt | <ul> <li>Good electrical property*</li> <li>Storage stability</li> <li>Low water absorption</li> </ul>                                                                       |                                   |

#### **Flame Retardants**

- FR-4 PCBs, being plastics, are inherently flammable. Flame retardants are added into the resin system to enhance their self-extinguishing property.

- · Typical flame retardants used in PCBs

- Halogenated flame retardants (Brominated and chlorinated)

- Inorganic flame retardants [Aluminum trioxide, Magnesium hydroxide, Ammonium polyphosphate, Red phosphorus (elemental phosphorous-polymeric P<sub>n</sub>)]

- Organophosphorus flame retardants (Phosphate esters)

- Nitrogen-based organic flame retardants

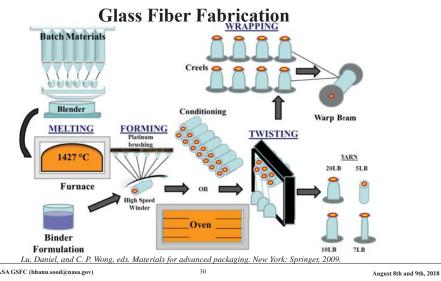

#### **Reinforcement: E-Glass**

Typical composition of E-glass:

| Component                                                             | % Composition |

|-----------------------------------------------------------------------|---------------|

| Silicon dioxide (SiO <sub>2</sub> )                                   | 52-56         |

| • Calcium oxide (CaO <sub>2</sub> )                                   | 16-25         |

| • Aluminum oxide (Al <sub>2</sub> O <sub>3</sub> )                    | 12-16         |

| • Boron oxide (B <sub>2</sub> O <sub>3</sub> )                        | 5-10          |

| • Sodium oxide (Na <sub>2</sub> O)+Potassium oxide (K <sub>2</sub> O) | 0-2           |

| Magnesium oxide (MgO)                                                 | 0-5           |

| • Iron oxide (Fe <sub>2</sub> O <sub>3</sub> )                        | 0.05-0.4      |

| • Titanium oxide (TiO <sub>2</sub> )                                  | 0-0.8         |

| Fluorides                                                             | 0-1           |

# Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

29

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

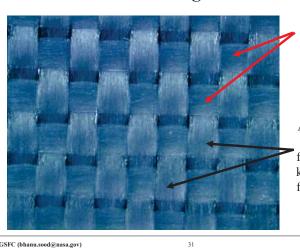

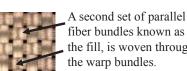

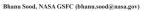

# Woven Fiberglass Fabric The initial set

of parallel fiber bundles is known as the warp, and lie in the machine direction

A second set of parallel fiber bundles known as the fill, is woven through the first set

#### **Glass Fabric Styles\***

106 Style Count: 56x56 (ends/in) Thickness: 0.0015 (in)

1080 Style Count: 60x47 (ends/in) Thickness: 0.0025 (in)

\* - Brist and Long, 2009

2113 Style Count: 60x47 (ends/in) Thickness: 0.0025 (in)

Count: 60x58 (ends/in) Thickness: 0.0038 (in)

7628 Style Count: 60x58 (ends/in) Thickness: 0.0038 (in)

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

32

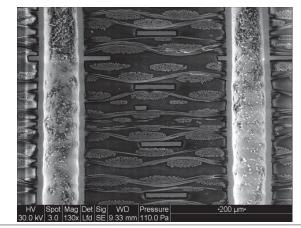

#### **Glass Fabric Styles**

1080 Style Thickness: 63µm Nominal glass dia.: 5µm

2116 Style Thickness: 96µm Nominal glass dia.: 7µm

Initial set of parallel fiber bundles is known as the warp, these lie in the machine direction.

fiber bundles known as the fill, is woven through the warp bundles.

7628 Style

Thickness: 172µm

Nominal glass dia.: 9µm

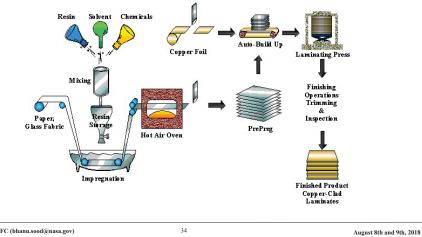

#### Laminate Fabrication

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

33

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

# **Types of PWBs**

#### Complexity

- Single sided ٠

- Double sided •

- Layer count: Multilayer ٠

#### Materials

- Organic

- FR-1, FR-2, CEM, FR-4, FR-5, BT, Polyimide, CE

- Ceramic

- Alumina, Glass-Ceramic, Aluminum Nitride

- Silicon ٠

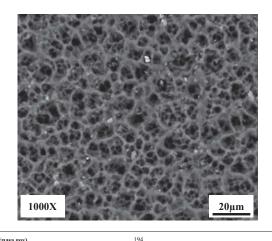

# **E-SEM View of PCB Cross-section - Woven Fabric**

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

#### **Paper Based Materials**

FR1, FR2, FR3, and CEM-1 are examples of paper-based laminates.

- FR1 and FR2 use phenolic resin binder. These two differ in their glass transition temperatures (130°C for FR1 and 105°C for FR2).

- FR3 uses an epoxy resin binder. The basic layer is paper. It is not suitable for plated through holes.

- CEM-1 is a paper based laminate with one layer of woven glass fabric. It is not suitable for plated through holes.

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

37

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

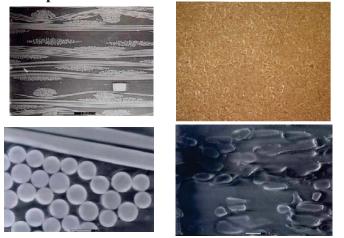

#### Comparison of Woven & Non-woven Fabric

#### **Copper Foil**

Non-woven Aramid Reinforcement

Generally, non-woven laminates have compositions that are more

homogeneous, can be made smoother, and have more isotropic properties

than woven laminates. These properties are all important for fine pitch

key to the ease of manufacture and component attachment (e.g., solder

surface mount applications, where thermal mismatch and coplanarity are

38

Top View

Thickness measured in oz./ft<sup>2</sup>

Side View

joints, direct attach or flip-chip) reliability.

- $-1 \text{ oz/ } \text{ft}^2 => 1.35 \text{ mil}, 2 \text{ oz/ } \text{ft}^2 => 2.70 \text{ mil}$

- · Electrodeposited copper

- formed from plating polished steel drum; smooth and rough side; rough side makes for a good adhesive bond with laminate; grains elongated in direction perpendicular to sheet; not as ductile as rolled foil

- Rolled copper foil

- progressive rolling and annealing; surface needs to be treated to form a good adhesive bond with laminate

#### Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

39

#### Factors in Selecting Circuit Board Materials

- Cost

- Electrical characteristics

- Surface and volume resistivity and dielectric constant

- Mechanical properties

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

Flexural strength, modulus of elasticity, coefficient of thermal expansion (in plane and out of plane), glass transition temperature

41

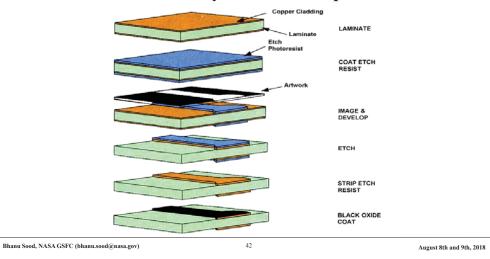

#### **Inner Layer Process Steps**

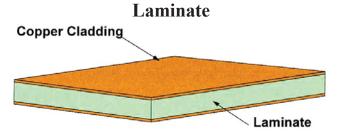

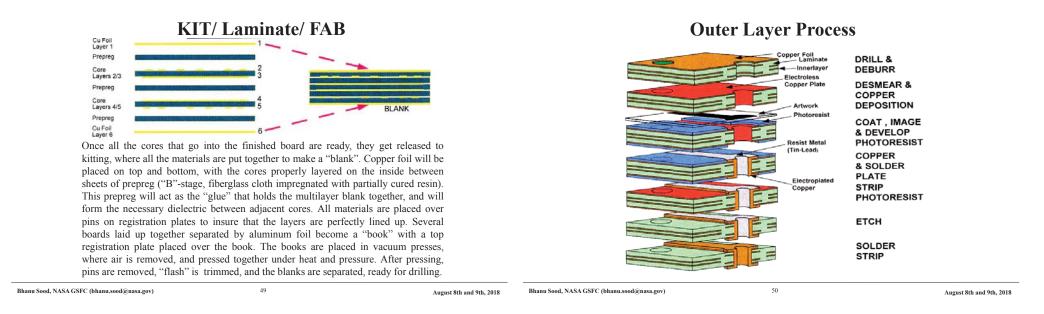

First, the proper laminate (core) is chosen. A core is made up of fully-cured epoxy resin ("C"-stage) sandwiched between two layers of copper cladding. The core must be the proper thickness, along with the required amount of copper cladding. The copper cladding will eventually become two inner layers, and the laminate will act as the dielectric spacing between these layers. The most common copper thickness for inner layers is one ounce of copper per square foot (typically 1.3 mils thick). Core thicknesses can run anywhere from 0.0015" to 0.070". The cores are either cut to size from larger sheets of material, or purchased to the specified panel size.

#### **Coat Etch Resist**

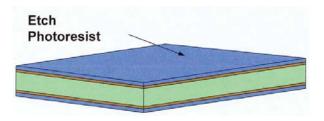

The core is chemically cleaned to remove any copper tarnish. It then passes through a cut sheet laminator where, through heat and pressure, a layer of dry film is placed on both sides of the core. This film will act as an etch resist later in the process, and will be removed after it has served its purpose.

#### **Image and Develop**

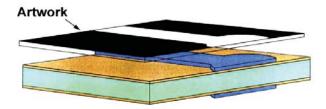

The resist-covered cores are placed into exposure frames where artwork is already in place. UV light is passed through silver halide artwork on both sides of the core simultaneously to expose the resist. This creates the circuit image in the dry film. The clear areas of the artwork through which light is allowed to shine on the film, are polymerized (hardened). Where light is blocked by artwork features, the film underneath stays soft. The soft, non-polymerized film is removed in the first section of the DES (Develop-Etch-Strip) line using a potassium carbonate solution, exposing only the unwanted copper for each layer.

Etch

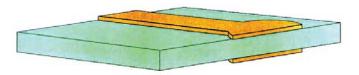

The core continues on through the DES line, passing through an ammoniacal etch, where the exposed, unwanted copper is attacked. The speed of the conveyor through etching is determined by the thickness of the copper being etched.

#### **Strip Etch Resist**

The dry film etch resist has completed its job. It is now removed in the final section of the DES line - the Stripper. Now a copper pattern for each layer can be seen. A Post-Etch Punch places a set of tooling slots in the core, by viewing targets placed precisely relative to the circuits and etched onto the core. These slots will be critical for proper registration of the cores used to construct the multilayer sandwich.

#### **Black Oxide Coat**

Prior to black oxide, the cores have undergone inspection using sophisticated AOI (Automated Optical Inspection) equipment. The inspected cores are then coated with an oxide in a programmed wet process line. The copper is changed to copper oxide, which has a crystal surface and will allow for better bonding when the multilayer is pressed together. The cores are then baked to remove any moisture.

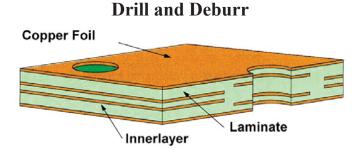

The blanks are pinned in stacks on tooling plates and drilled on multi-spindled drill machines. The computerized drill program determines where the holes are placed, and automatically changes drill sizes when each drill size has completed its path. Holes can be as small as .008" or as large as .250". X-ray and visual inspection are used to verify that the holes are fully drilled and properly aligned to the inner layer pads. Deburring equipment removes any burrs that may have formed.

# **Desmear and Copper Deposition**

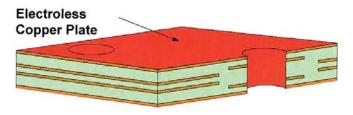

The holes undergo a process to remove any resin smear covering innerlayer connects and to slightly roughen the hole walls to allow for subsequent plating. The deposition process is an electroless plating process in which a very thin layer (80 to 100 millionths thick) of copper is deposited onto the surfaces of the hole wall (and incidentally on the copper foil surface). This will allow for subsequent electroplating of the holes.

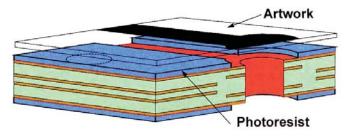

#### **Coat, Image and Develop Dry Film**

Dry film resist is applied to both sides of the panel under heat and pressure, similar to the cores in inner layers. The circuitry pattern of the artwork is aligned to the drilled holes and the panel is exposed to UV light from both sides. Where light is allowed to shine through, the film is polymerized. In the case of outer layers, a reverse artwork image is used, since the dry film is acting as a plating resist as opposed to the dry film being an etch resist in inner layer. The panels are developed, with the unexposed resist being washed away.

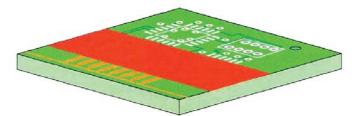

# Copper and Solder Plate Resist Metal (Tin-Lead) Electroplated Copper

All copper exposed will be plated, with .001" nominal of copper in the hole barrels, followed by either tin or tin/lead, which will act as the etch resist further on. The panels are carried on racks by a hoist which is computer-controlled to repeat the same cycle time after time. The hoist places the racks of panels into the solution and rinse tanks for set time periods, so that the chemical solutions can deposit the metals to the traces, pads, and hole barrels electrolytically.

#### **Strip Photoresist**

The dry film resist, which acted as a plating resist, is now stripped away with an alkaline solution in the Strip-Etch-Strip line. This exposed the unplated copper foil underneath on the surface. Any holes that were "tented" (covered) with dry film will have copper barrels from the electroless copper process.

The copper foil is now etched away, using an ammoniacal solution. It is here where "a circuit is born," since the board is electrically functional at this point. There are still, however, several more steps.

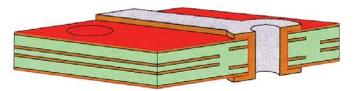

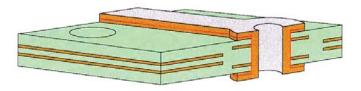

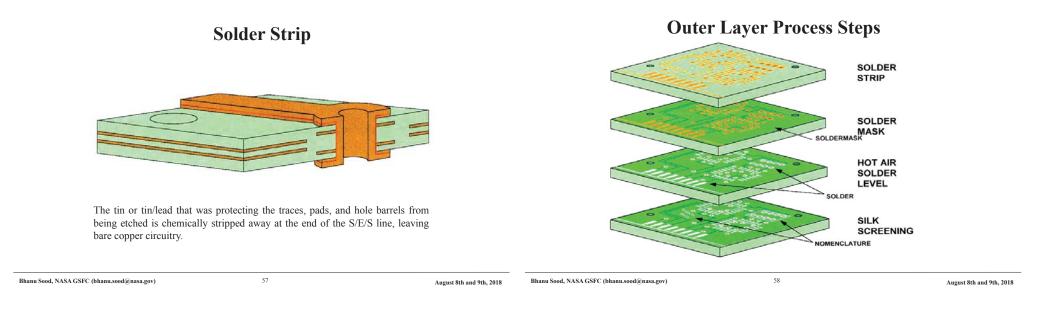

This details of this process, already discussed, involves the removal of the tin or tin/lead protecting the traces, pads, and hole barrels from being etched.

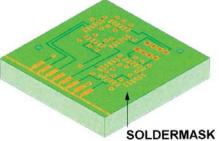

# Soldermask

Soldermask is applied to protect and insulate the circuitry. The panels are cleaned, preheated, and coated with soldermask. Several stages of drying are performed to solidify the mask. The mask now acts much like the dry film in inner and outer layers. Artwork is exposed onto both sides of the panel, and the soft mask is removed where it is not wanted (pads). The panel is then baked for final curing.

60

Hot Air Solder Level (HASL) involves the application of solder to selected board features, wherever copper was left exposed after soldermasking. The copper is cleaned and microetched in a preclean unit, preheated, and fluxed to promote solder wetting. The panel is horizontally immersed in the solder pot, and then excess solder is blown off with air knives. A cool down and cleaning stage follows.

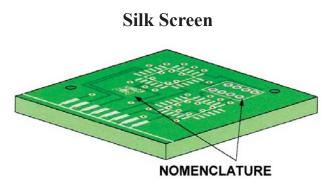

Information needed by the customer for assembly or troubleshooting is screenprinted onto the board. An epoxy ink is applied to the stenciled screen. Using a squeegee, the ink is forced through a screen fabric with a stencil image. The ink is then baked in order to cure the resin. Once baked, the ink is not easily removed.

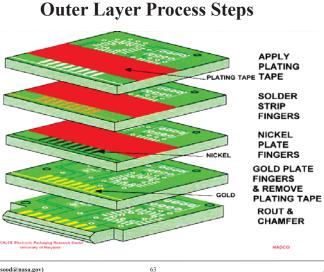

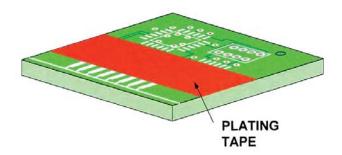

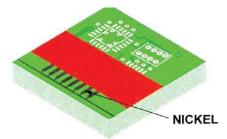

**Apply Plating Tape**

This nickel/gold plating process is used for edge connectors and critical contacts. A pressure tape is applied below the finger area in order to permit solder strip and nickel/gold plating in the finger area only.

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

#### **Solder Strip Fingers**

The boards travel within a conveyorized belt through shallow solution tanks. Solder, which had been leveled onto the connector fingers, is chemically stripped off.

65

#### **Nickel Plate Fingers**

The nickel/gold plating process is electrolytic. As the board edges pass through plating solutions, brushes have made contact with blocks attached to a buss bar feeding to the fingers. This buss bar provides electrical continuity to the fingers and allows for plating. First, a layer of nickel about 100 - 150 microinches thick is plated onto the copper. This nickel increases wear-resistance. It also serves as a barrier to copper migration into the gold.

66

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

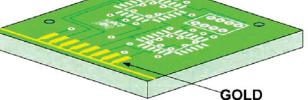

Gold, usually from 30 to 50 micro-inches thick, is plated directly over the nickel. Gold is used on the connector fingers because it is highly conductive and resists tarnishing. The plating tape is then pulled from the board, and the board is degummed.

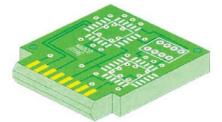

#### **Rout and Chamfer**

Here the board is depanelized. The rout process is similar to the drill process, with the panels being stacked and pinned onto the tooling plates of a multiple spindle router. Utilizing a numerically controlled computer program, specialized carbide router bits are used to machine the edges, slots, and any required internal cutouts. The boards are removed and dimensionally verified to blueprint and shop traveler provided with the job. A bevel, or chamfer, is placed along the finger edge of the board, to remove the buss bar and allow for easier insertion of the card. Some boards with straight edges perpendicular to one another are scored, or V-grooved. The boards undergo a final clean of warm water and high-pressure rinse.

68

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

### Electrical Testing, Final Inspection and Shipping

The boards undergo 100% electrical test on sophisticated simultaneous testers, to parameters set by the customer. This equipment runs from a downloaded program developed from net list or Gerber data. Final inspection looks for cosmetic flaws and performs dimensional checks. The shipping department then packages the boards for shipment to the customer.

69

### Flex and Rigid-Flex Circuits

• Flex Circuits are thin, lightweight, bendable signal traces built on flexible dielectric substrates. Flex circuit technology enables 3D configurations, smaller, lighter and faster products, and can lower total applied cost.

70

Flex, Rigid-Flex Circuits - Materials

- Characteristics

- Meet dynamic flexing requirements: active and passive components can be added directly to the flex.

- Impedance control

- EMI control

Base Material

- Polyester

- Polyimide

- Polyethylene napthalate (PEN)

Board to board connection

-Liquid crystal polymer

-Flouropolymers

```

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

```

August 8th and 9th, 2018 Bha

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

# **Types of Flex Circuits\***

- **Type 1:** One conductive layer, either bonded between two insulating layers or uncovered on one side. (Stiffeners, pins, connectors, components, are optional).

- **Type 2**: Double sided, two conductive layers, PTHs, with or without stiffeners.

- **Type 3:** Multi-layer flexible, three or more conductive layers, PTHs, with or without stiffeners.

- **Type 4**: Multi-layer rigid and flex, three or more conductive layers, PTHs.

- **Type 5:** Flex or rigid-flex, two or more conductive layers, no PTHs.

#### \* - IPC-6013C- Multi-layer rigid and flex, three or more conductive layers, PTHs, Nov 2003.

#### \* - Flexible Circuit Technology, Third Edition, J. Fjelstad, BR Publishing Inc, Sept 2006

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

#### Flex, Rigid Flex - Base Materials

| Substrate    | Dielectric | Dissipation | Dielectric       | Moisture    | Tensile         | Elongation              |

|--------------|------------|-------------|------------------|-------------|-----------------|-------------------------|

| Material     | Constant   | Factor      | Strength (v/mil) | Absorption  | Strength (kpsi) | Liongation              |

| FEP          | 2          | 0.0002      | 5000             | < 0.01%     | 2-3 kpsi        | ~ 300%                  |

| PTFE         | 2.5        | 0.0002      | 5000             | < 0.01%     | 15- 25 kpsi     | N/A                     |

| Polyester    | 3.2        | 0.005       | 7000             | < 0.08%     | 25 kpsi         | ~ 120%                  |

| LCP          | 2.9        | 0.003       | 6000             | 0.02 - 0.1% | 15-25 kpsi      | ~ 15%                   |

| PVC          | 4.7        | 0.093       | 500              | < 0.5%      | 5 kpsi          | $\sim 120\text{-}500\%$ |

| Polyimide    | 3.5        | 0.003       | 7000             | 1.3 – 3%    | 25 kpsi         | $\sim 60\%$             |

| PEN          | 2.9        | 0.004       | 7500             | 1%          | 30-35 kpsi      | ~ 75%                   |

| Aramid Paper | 2          | 0.007       | 380              | 3%          | 11 kpsi         | ~ 10%                   |

#### Flex, Rigid-Flex Circuits - Materials

#### **Bonding Adhesives**

- Polyester

- Acrylic

- Epoxy

- –Polyimide–Butyl phenolic

- -Polythermides

73

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

74

August 8th and 9th, 2018

#### Flex, Rigid Flex - Adhesive Materials

| Adhesive<br>Type     | Peel Strength<br>(post-solder)<br>N/mm | Adhesive<br>Flow<br>mils/mil | Moisture<br>Absorption<br>max % | Surface<br>Resistivity<br>min M W | Dissipation<br>Factor<br>@1MHz | Dielectric<br>Constant<br>@1 MHz |

|----------------------|----------------------------------------|------------------------------|---------------------------------|-----------------------------------|--------------------------------|----------------------------------|

| PTFE                 | > 1 N/mm                               | 125 mm<br>max                | 0.01                            | 1012                              | 0.0007                         | 2.2 nom                          |

| Polyester            |                                        | 250 mm<br>max                | 2                               | 104                               | 0.02                           | 4.0 max                          |

| Butyral-<br>Phenolic | 1.0 N/mm                               | 125 mm<br>max                | 2                               | 104                               | 0.025                          | 3.0 max                          |

| Polyimide            | 1.0 N/mm                               | 125 mm<br>max                | 3                               | 105                               | 0.01                           | 4.0 max                          |

| Epoxy                | 1.4 N/mm                               | 125 mm<br>max                | 4                               | 104                               | 0.06                           | 4.0 max                          |

| Acrylic              | 1.6 N/mm                               | 125 mm<br>max                | 6                               | 107                               | 0.02                           | 3.5 nom                          |

#### Flex, Rigid-Flex Circuits - Materials

Conductors

- Copper foil or electrodeposited -Aluminum

- Annealed copper

- Electroplated copper

- Sputter deposited copper

-Stainless steel

-Beryllium copper

-Polymer thick film

#### Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

79

80

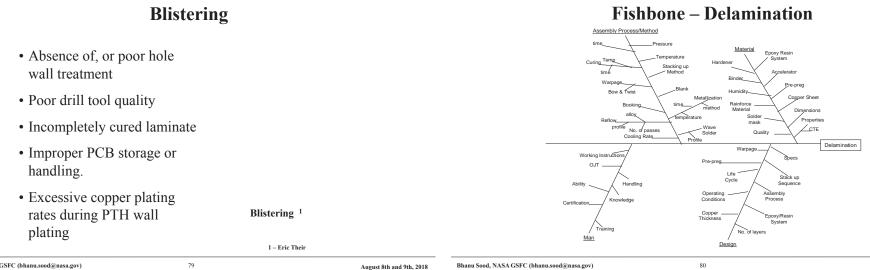

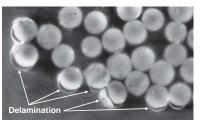

#### Delamination

- Multilayer boards are a stack up composite system

- Bonding strength depends on the strength of the thermo set material

- Which in turn is a function of the thermo-mechanical properties such as Tg, CTE, and stiffness

- · Bonding capacity will also depend upon

- Curing time

- Temperature

- Presence and efficiency of the accelerators, binders, and catalyst in the epoxy system

81

• Failure to hold the stacked layers in the out of plane "z" direction results in delamination

**Section - II**

**Failure Mechanisms**

#### Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018 Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

82

August 8th and 9th, 2018

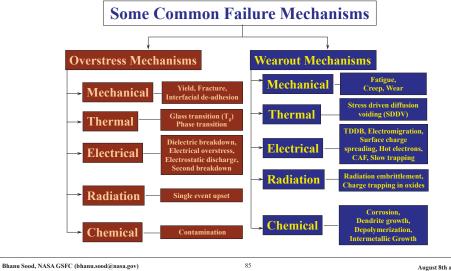

# **Review: Failure Definitions**

FailureA product no longer performs the function for<br/>which it was intendedFailure ModeThe effect by which a failure is observed.Failure SiteThe location of the failure.Failure MechanismThe physical, chemical, thermodynamic or other<br/>process that results in failure.

In principle, it should be possible to develop a **failure model** for a specific failure mechanism, expressing the likelihood of failure (time-to-failure, probability of failure, strength, etc.) as a function of the stresses and characteristics of the material.

#### **Review: Classification of Failures**

Key classes of failure:

- *overstress*: use conditions exceed strength of materials; often sudden and catastrophic

- wearout: accumulation of damage with extended usage or repeated stress

- *infant mortality*: failures early in expected life; typically related to quality issues.

84

#### **Examples of Failure Models**

| Failure Mechanism                       | Failure Sites             | Relevant Stresses                | Sample Model       |

|-----------------------------------------|---------------------------|----------------------------------|--------------------|

| Fatigue                                 | Die attach, Wirebond/TAB, |                                  | Nonlinear Power    |

|                                         | Solder leads, Bond pads,  | Cyclic Deformations              | Law (Coffin-Manson |

|                                         | Traces, Vias/PTHs,        | $(\Delta T, \Delta H, \Delta V)$ |                    |

|                                         | Interfaces                |                                  |                    |

| Corrosion                               | Metallizations            | M, ΔV, T, chemical               | Eyring (Howard)    |

| Electromigration                        | Metallizations            | T, J                             | Eyring (Black)     |

| Conductive Anodic<br>Filament Formation | Between Metallizations    | Μ, ΛV                            | Power Law (Rudra)  |

| Stress Driven<br>Diffusion Voiding      | Metal Traces              | σ, Τ                             | Eyring (Okabayashi |

| Time Dependent                          | Dielectric layers         |                                  | Arrhenius (Fowler- |

| Dielectric Breakdown                    |                           | V, T                             | Nordheim)          |

| Δ: Cycl                                 | ic range                  | V: Voltage                       |                    |

| Λ: grad                                 | ient                      | M: Moisture                      |                    |

|                                         | perature                  | J: Current densit                | У                  |

| H: Hum                                  | idity                     | σ: Stress                        |                    |

86

#### August 8th and 9th, 2018

#### August 8th and 9th, 2018

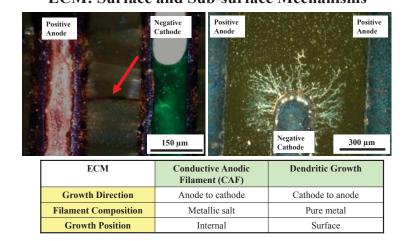

# **ECM: Surface and Sub-surface Mechanisms**

87

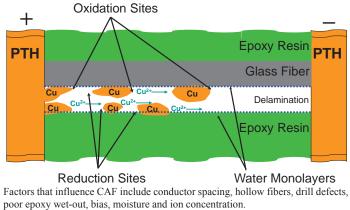

### Formation of Conductive Filaments<sup>[1][2]</sup>

I.Rogers, K., "An Analytical and Experimental Investigation of Filament Formation in Glass/Epoxy Composites." (2005). 2.Sood, B., and Pecht M., "Conductive filament formation in printed circuit boards: effects of reflow conditions and flame retardants." Journal of Materials Science: Materials in Electronics 22.10 (2011): 1602-1615.

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

# **Glass Fibers and Coupling Agents**

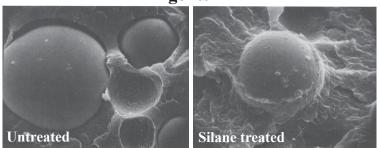

Coupling agents are functionally graded materials that act as adhesion promoters. [1] [2] [3]

- Coupling agents are typically composed of antistats, lubricant, surfactant, silanes and film formers (collectively also called sizing).

- Silane act as molecular bridges between two chemically different materials (glass and epoxy matrix).

- Prior to application of coupling agents, fibers are first heat cleaned at 538C to remove oil coats.

- Organo-functional group bonds to the organic resin.

- Inorganic groups bond to the glass surface.

1.Mishra, Debasmita, and Alok Satapathy. "An Investigation on The Dielectric Properties of Epoxy Filled With Glass Micro-Spheres and Boron Nitride." (2012)

2.Mack, H. "Choosing the Right Silane Adhesion Promoters for SMP Sealants," Adhesive and Sealant Council Meeting, Orlando, FI, Spring 2001.

S.Gelorme, J.Effrey Donald, and Joseph Kuczynski. "Silane Coupling Agents for Printed Circuit Boards." U.S. Patent

Application 12/694,005.

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

# Coupling Agents Used in FR4

92

OH

Dow Corning, BGF, Gelest are key suppliers. Main silane types are:

- Aminosilanes

- Epoxy Silanes

- Vinyl Silanes

- Methacryl Silanes

- Alkylsilane

- Phenyl Silane

- Chlorosilane

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

Mittal, Kashmiri Lal, and Antonio Pizzi, eds. Adhesion promotion techniques: technological applications. CRC Press, 1999.

HO

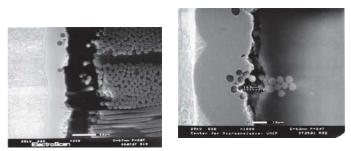

# Visualizing the Effects of Coupling Agents

SEM images of fracture surfaces shows silane treated and untreated fillers [1] in a polyimide composite.

93

**Evidence of Filament Formation**

1. Vanderbilt Minerals, Product Information Document, accessed April 2014.

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

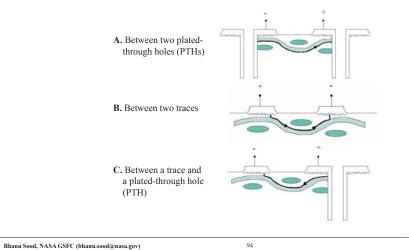

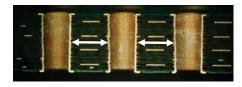

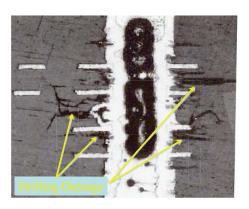

#### Factors Affecting CAF: PCB Internal Conductor Spacings

**PTH-to-PTH spacings**

PTH to plane spacings

Electron micrograph of area of fiber/resin delamination. EDS shows evidence of

copper filaments.

August 8th and 9th, 2018

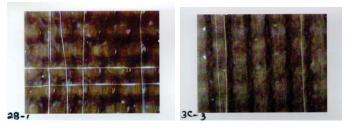

#### **Factors Affecting CAF: Board Orientation Respective to Fabric Weave**

#### Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

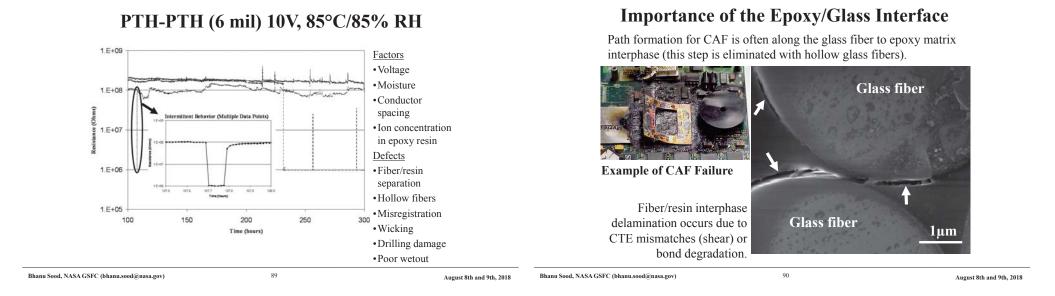

#### **Failure Accelerators of CAF**

#### Decrease in Strength

- · Fiber/resin separation

- Copper/resin separation

- Hollow fibers

- · Misregistration of PTHs/Vias

- · Copper wicking

- Drilling damage

- · Separation of PTH wall from epoxy resin

#### Increase in Stress

- Higher voltage

- Higher moisture concentration

- · Tighter conductor spacing

- · Higher ion concentration in epoxy resin

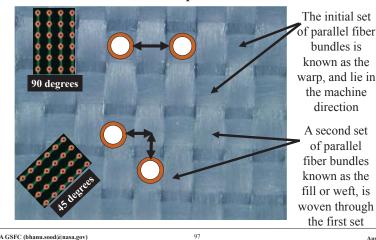

### Effect of Voltage and Humidity on **Time to Failure** 40000

98

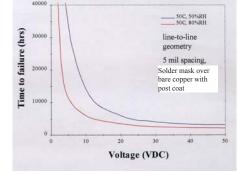

**Fiber/Resin Interface Delamination**

Fiber/resin interface delamination occurs as a result of stresses generated under thermal cycling due to a large CTE mismatch between the glass fiber and the epoxy resin (ratio of <u>1 to 12</u>).

Delamination can be prevented/resisted by selecting resin with lower CTE's and optimizing the glass surface finish. Studies have shown that the bond between fiber and resin is strongly dependent upon the fiber finish.

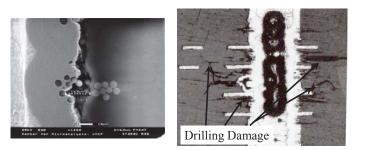

### **Hollow Fibers**

#### Drilling

Hollow fibers are vacuous glass filaments in E-glass laminates which can provide paths for CAF.

With the appearance of hollow fibers inside the laminates, CAF can happen as a one step process. In this case, the number of hollow fibers inside the laminates is most critical to reliability.

# Drilling damage can accelerate CAF through

- · Fiber/resin delamination,

- Creation of paths for moisture to accumulate

- Wicking due to cracking of the board material

| Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov) | 101 | August 8th and 9th, 2018 | Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov) | 102 |

|---------------------------------------------|-----|--------------------------|---------------------------------------------|-----|

|                                             |     |                          |                                             |     |

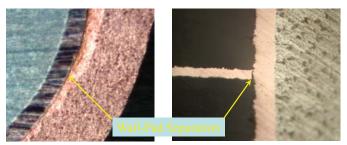

# **PTH-Resin Separation**

In both of these SEM pictures, a separation can be seen at the copper plating to fiber epoxy resin board interface. These gaps provide an accessible path for moisture to accumulate and CAF to initiate. These voids can be adjacent to inner-layer copper foil or to the PTH barrel and normally result from contraction of the epoxy (resin recession) due to the heat of thermal stress.

### **Images of Hollow Fibers**

#### **Background on Dendritic Growth**

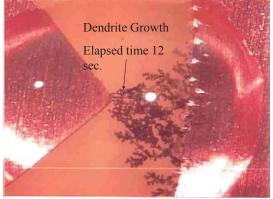

**Dendritic Growth** is a form of electrochemical migration (ECM) involving the growth of conductive filaments on or in a printed circuit board (PCB) under the influence of a DC voltage bias. [IPC-TR-476A]

#### DC voltage source Plating Solder alloy Ion transport Anode (Cu) Cathode (Cu) Adsorbed Moisture Necessary Conditions for ECM Stages of ECM · Electrical carriers (ions). • Path formation A medium, usually water, to dissolve the ionic materials and sustain them in their Electrodissolution mobile ionic state. · Electrical potential between the electrodes to • Ion transport establish an ionic current in the liquid · Electrodeposition medium · Filament growth 105 Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov) August 8th and 9th, 2018

#### **Electrochemical Migration**

106

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

#### **Contaminants**

- Halide residues, such as chlorides and bromides, are the most common accelerators of dendritic growth.

- Chlorides are more detrimental, but easier to clean

- Bromides can resist cleaning; often require DI water with saponifier

- In general, an increased risk of ECM will tend to occur once the levels of chloride exceed 10µg/in<sup>2</sup> or bromide exceeds 15µg/in<sup>2</sup>

- Rapid failure can occur when contaminant levels exceed 50µg/in<sup>2</sup>

# What Are the Sources of Contaminants?

- Board Manufacturing

- Flame-proofing agents

- Copper plating deposits

- Etchants

- Cleaners

- Fluxes (for HASL coatings)

- Poorly polymerized solder masks

- "Fingerprints"

- Assembly

- Fluxes

- Solder paste residues

- "Fingerprints"

- Environmental

- Liquid (i.e., salt spray)

- Gaseous (i.e., Cl<sub>2</sub>)

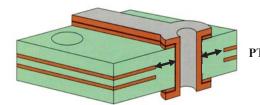

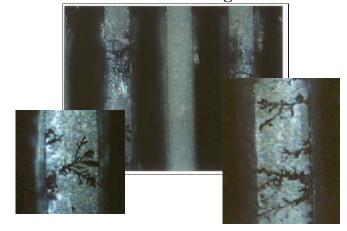

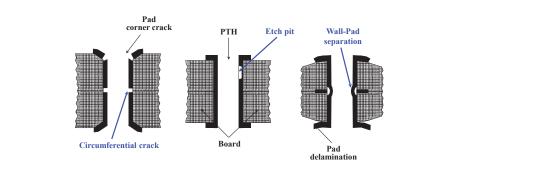

#### **Plated Through Hole (PTH) Failures**

#### **PTH Failures (cont.)**

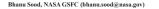

# Circumferential Cracking – Single Event Overstress

Since the difference in the coefficient of thermal expansion (CTE) of the copper plating and the resin system in the PWBs is at least a factor of 13, stress exerted on the plated copper in the plated-through holes in the z-axis can cause cracking.

#### Single Event Overstress (cont.)

- Failure Mode

- Complete electrical open

- · Failure History

- Primarily occurs during assembly; may not be detected until after operation

- Root-Causes

- Excessive temperatures during assembly

- Resin Tg below specification

- Insufficient curing of resin

- Outgassing of absorbed moisture

- Plating folds

- PTH wall recession

- Resin-rich pockets adjacent to PTH

- Insufficient mechanical properties of deposited copper

- Plating voids

- Etch pits

- Insufficient PTH wall thickness

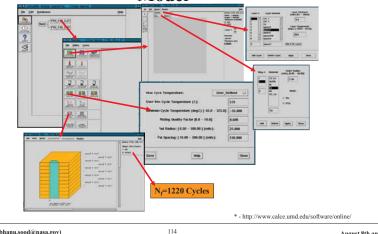

# **Design Considerations to Avoid Fatigue Damage in PTHs**

- PTH Spacing

- Decreasing spacing improves mechanical reliability

- Aspect Ratio

- Decreasing board thickness more effective than increasing hole diameter

- Plating Thickness

- Increasing leads to increasing in fatigue strength

- Nonfunctional Internal Pads

- Minimal effect. Results in localized stress relief; most effective when results in elimination of resin-rich areas

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

113

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

### **Root-Cause Analysis of Circumferential Fatigue Cracking**

- Failure Mode

- Intermittent to complete electrical open

- Failure History

- Requires an environment with temperature cycling; often occurs after extended use in the field ("child" or "teenage" mortality)

- Root-Causes

- Resin CTE below specification

- Plating folds

- PTH wall recession

- Resin-rich pockets adjacent to PTH

- Customer use exceeds expected environment

- Insufficient mechanical properties of deposited copper

- Presence of overstress crack

- Plating voids

- Etch pits ("mouse bites")

- Insufficient PTH wall thickness

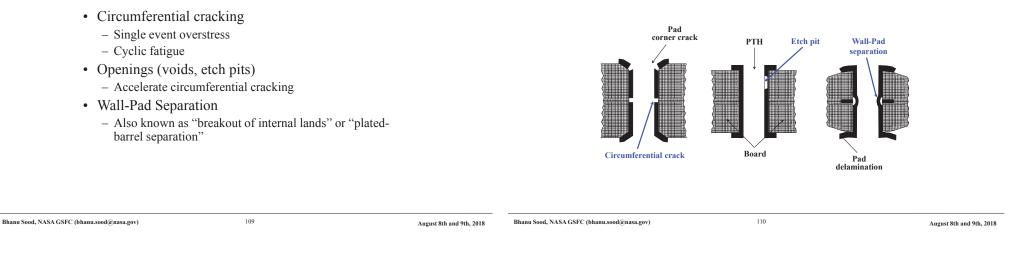

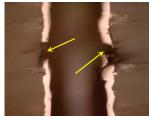

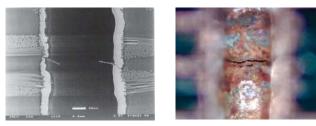

### **Openings in PTH Walls**

Optical micrograph of cross section of PTH with etch damage

Electron micrograph of same PTH shown on left

Overetching can cause electrical opens or induce overstress circumferential cracking

#### **Evidence of Overetching**

Optical micrograph of cross section of PTH with etch damage (bright field)

Optical micrograph of cross section of PTH with etch damage (dark field)

*Evidence of overetching can include reduced plating thickness and discoloration of PTH barrel walls*

### **Opening in PTH/Via**

- Failure Mode

- Complete electrical open

- Failure History

- Often occurs during assembly; may not be detected until after operation

- Root-Causes

- Openings in PTH's/Vias are etch pits or plating voids and often occur because the following manufacturing processes are not optimized:

- Drilling

- Desmear/Etchback

- · Electroless copper plating or direct metallization

- · Electrolytic copper plating

- · Tin resist deposition

- · Etching

- Openings can also occur due to poor design (i.e., single-sided tenting of vias, resulting in entrapment of etchant chemicals)

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

117

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

118

August 8th and 9th, 2018

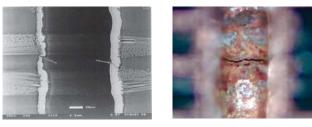

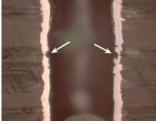

#### PTH/Via Wall-Pad Separation

Optical micrograph of cross section perpendicular to the PTH axis

Optical micrograph of cross section parallel to the PTH axis

#### PTH/Via Wall-Pad Separation

- Failure Mode

- Intermittent or complete electrical open

- Failure History

- Will primarily only occur during assembly

- Root-Causes

- Insufficient Curing of Resin.

- Outgassing of absorbed moisture

- Excessive temperatures during assembly

- Resin CTE or Resin Tg below specification

- Number of nonfunctional lands (only useful for failures during assembly)

- Drilling process resulting in poor hole quality

- Insufficient desmearing process.

- Substandard processes or materials in electroless copper plating

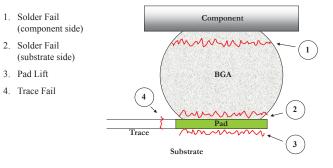

#### Failure Mechanisms due to Handling

- Affects leadless components

- Ball grid arrays (BGAs), Flip Chip on Board

- Affects brittle components

- Insidious

- Failures due to handling tend to difficult to screen and intermittent in nature

- Often occur after testing

## When Do Handling Failures Occur?

- Assembly

- Transfer of product between lines; during rework

- Heatsink Attachment

- Use of screws

- Connector Insertion

- Large press-fit connectors; daughter boards into mother boards

- Electrical Testing

- Bed-of-Nails testing can bend local areas

- Packaging

- Transportation

- Customer Site

- Slot insertion

| Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov) | 121 | August 8th and 9th, 2018 | Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov) | 122 | August 8th and 9th, 2018 |

|---------------------------------------------|-----|--------------------------|---------------------------------------------|-----|--------------------------|

|                                             |     |                          |                                             |     |                          |

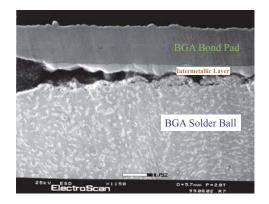

#### Evidence of Damage Due to Handling --BGAs

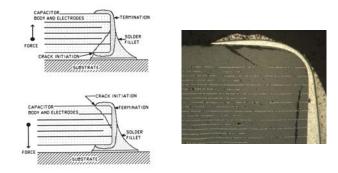

# Evidence of Damage – Ceramic Capacitors

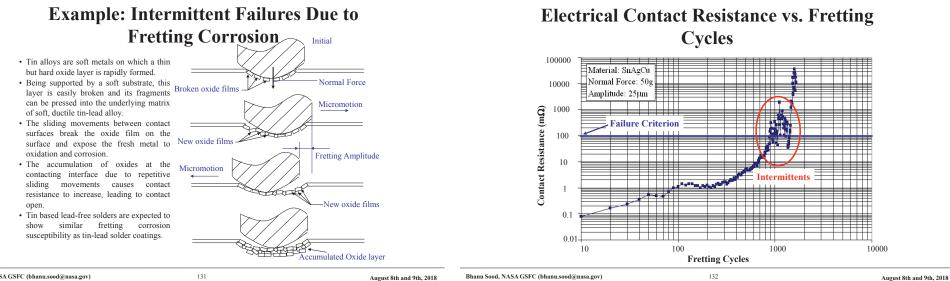

#### **Intermittent Failures**

- An intermittent failure is the loss of some function in a product for a limited period of time and subsequent recovery of the function.

- If the failure is intermittent, the product's performance before, during, or after an intermittent failure event may not be easily predicted, nor is it necessarily repeatable.

- However, an intermittent failure is often recurrent.

### **No Fault Found**

- No-Fault-Found (NFF): Failure (fault) occurred or was reported to have occurred during product's use. The product was tested to confirm the failure, but the testing showed "no faults" in the product.

- Trouble-Not-Identified (TNI): A failure occurred or was reported to have occurred in service or in manufacturing of a product. But testing could not identify the failure mode.

- Can-Not-Duplicate (CND): Failures that occurred during manufacture or field operation of a product cut could not be verified or assigned.

- No-Problem-Found (NPF): A problem occurred or was reported to have occurred in the field or during manufacture, but the problem was not found during testing.

- Retest-OK: A failure occurred or was reported to have occurred in a product. On retesting the product at the factory, test results indicated that there was no problem.

| Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov) | 125 | August 8th and 9th, 2018 | Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov) | 126 | August 8th and 9th, 2018 |

|---------------------------------------------|-----|--------------------------|---------------------------------------------|-----|--------------------------|

|                                             |     |                          |                                             |     |                          |

#### **The Impact of Intermittents**

- Can not determine root cause and thus the reason for the failure (NFF)

- Reliability modeling analysis can be faulty

- Potential safety hazards

- Decreased equipment availability

- Long diagnostic time and lost labor time

- Complicated maintenance decisions

- Customer apprehension, inconvenience and loss of customer confidence

- ➢ Loss of company reputation

- Increased warranty costs

- Extra shipping costs

#### Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

### **Common Examples of Intermittents**

Some common examples of intermittent failures:

- Medical: asthma attacks, allergy attacks, angina, toothaches (especially if food- or temperature- dependent)

- Automotive: squealing sound or failure to charge battery due to loose fan belt

- Utility: brown-outs

- Cell phone or computer: multiple letter entries for a single keystroke, which may be due to bad contact or sticky keys on keypad

- Household: water ingress through leaky roof, especially if leak is winddriven; running toilet, due to problems with mechanism or plunger seal

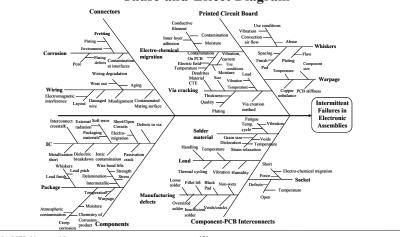

#### **Intermittent Failures in Electronic Assemblies Cause-and-Effect Diagram**

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

129

#### **Characteristics of Intermittent Failures**

- May indicate that a failure has occurred. Intermittent failure may be due to some extreme variation in field or use conditions.

- May indicate the imminent occurrence of failure.

130

• May not leave a failure signature making it difficult to isolate the site.

August 8th and 9th, 2018

#### Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

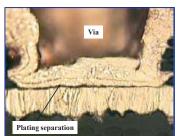

### **Example: Intermittent Failure Due to Improper Micro-via Plating in PCB**

A computer graphics OEM was experiencing intermittent failures on printed circuit boards with chip scale packages (CSPs) and ceramic ball grid array packages (CBGAs). High magnification metallurgical microscope imaging of microetched cross sections of micro-vias in the printed circuit board showed a separation of the via plating from the capture pad [Nektek Inc. Service Report, 2004]. The plating separation was found to be the cause of intermittent failure.

Plating separation at base of micro via [Nektek Inc. Service Report, 2004]

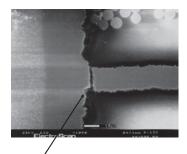

# Example: Intermittent Failure Due to Open Trace in PCB

Open trace can also cause intermittent failures in PCB under environmental loading conditions. Under thermal cycling or vibration loading, the open trace may reconnect with intermittent electrical continuity observations.

**Open Trace**

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

133

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

134

August 8th and 9th, 2018

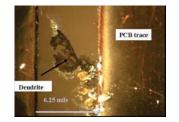

#### **Example: Intermittent Failures Due to Electro-chemical Migration (Surface Dendrites)**

135

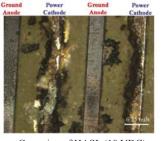

- Electrochemical migration (ECM) can cause shorts due to the growth of conductive metal filaments in a printed wiring board (PWB).

- Surface dendrites can form between the adjacent traces in the PWB under an applied voltage when surface contaminants and moisture are present.

- It is often difficult to identify the failure site because the fragile dendrite structure will burn upon shorting, often leaving no trace of its presence.

Dendritic growth during an ECM test

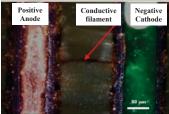

#### Example: Intermittent Failures Due to Electro-chemical Migration (Conductive Anodic Filament Formation)

- Conductive filament is formed internal to the board structure.

- In CAF, the filament is composed of a metallic salt, not neutral metal atoms as in dendritic growth.

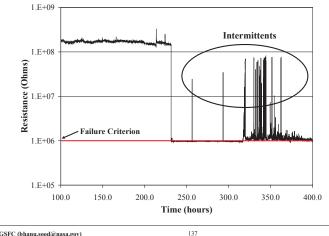

- One of distinct signatures of CAF failures is intermittent short circuiting. The conductive filament bridging the two shorted conductors can blow out due to the high current in the filament, but can form again if the underlying causes remain in place.

A conductive filament bridging two plated through holes in a PWB

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

#### **Electrical Resistance vs. Time Due to CAF**

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

#### **Example: Intermittent Failures Due to Creep** Corrosion

- Definition

- Creep corrosion is a mass transport process in which solid corrosion products migrate over a surface.

- Failure mode

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

- On IC packages, creep corrosion can eventually result in electrical short or signal deterioration due to the bridging of corrosion products between isolated leads.

- Depending on the nature of the environment, the insulation resistance can vary and cause intermittents.

Creep corros Field failure due to creep corrosion [Adtran, 2001]

#### **Example: Intermittent Failures Due to Tin Whiskers**

139

Failed relay due to tin vapor arcing

Whiskers on the armature of a relay Photos Courtesy: Northrop Grumman

- · Whiskers are elongated single crystals of Sn which grow spontaneously out of the surface. Internal stresses within the plated deposit drives growth

- · Tin (and other conductive) whiskers or parts of whiskers may break loose and bridge isolated conductors, resulting in an intermittent short circuit. These field failures are difficult to duplicate or are intermittent because at high enough current the conductive whisker can melt, thus removing the failure condition. Alternatively, disassembly or handling may dislodge a failure-producing whisker. Failure analysis concluded that tin whiskers initiated the current surge to the ground. Once a whisker bridged a terminal stud to the armature, plasma arcing could occur with

enough voltage and current to damage the relay.

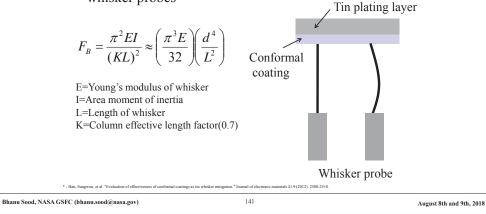

# **Effects of Conformal Coating**

138

- Prevent the whisker penetration

- Block the electrical shorting caused by whiskers

- $\rightarrow$  Measure the breakdown voltage of conformal coating

- Keep whiskers under the conformal coating

- $\rightarrow$  Measure the mechanical properties (Young's modulus, hardness) and adhesion strength of conformal coating

- Slow the whisker growth

- $\rightarrow$  Measure the preferred crystal orientation and residual stresses in tin layer

August 8th and 9th, 2018

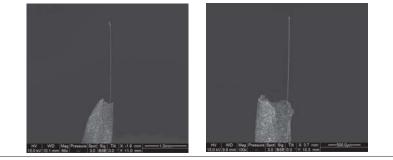

### **Buckling Force 1/2\***

• Measuring the buckling force using various length of whisker probes

# **Buckling Force 1/2**

- Challenge

- Most of whiskers on whisker probe are already buckled.

- Tip of whiskers were damaged during the cut-off process.

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

142

August 8th and 9th, 2018

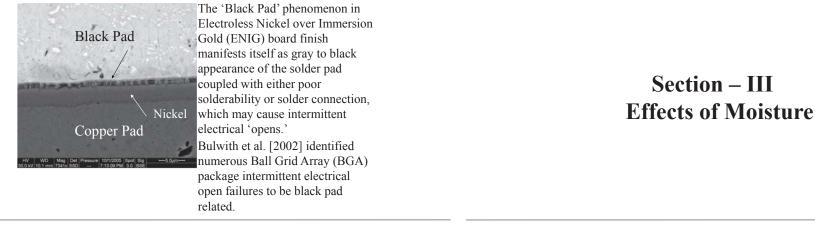

#### Example: Intermittent Failures Due to Black Pad

144

## **Effects of Moisture in PCB**

- Swelling and inner layer delamination

- Blistering

- Reduces glass-transition temperature (Tg) increases stresses on features like PTHs

- Increases dielectric constant  $(D_k)$  and dissipation factor  $(D_f)-\mbox{reducing circuit switching speed}$

- · Oxidation of copper surfaces leading poor wettability of finishes and solder

- Ionic corrosion leading to electrical opens or shorts

- Interfacial degradation leading to conductive filament formation

#### **Inner Layer Delamination – 1**

- Delamination occurs at the interface of adhering materials.

- Work required to separate the interfaces and extend the crack includes:

- Work necessary for de-adhesion, and

- Work required to deform, elastically or inelastically, the separating bulk phases.

Delamination between copper conductors, core and prepreg <sup>1</sup>

1 - Reid, PWB Interconnect Solution

```

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

```

145

```

August 8th and 9th, 2018

```

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

#### **Inner Layer Delamination – 2**

- Partially polymerized or uncured resin, at reflow temperatures, forms shorter chains

- Unbound water molecules exert internal pressure by turning to steam causing localized delamination

- Regions away from PTHs are more prone to delamination

- Moisture can escape more easily close to PTHs

- Additional causes:

- Using prepregs from uncontrolled storage.

- Board lamination in uncontrolled humidity environments.

#### Blistering

148

146

Typically caused by high vapor pressure exerted by

- Moisture trapped between the solder mask and board surface

- Volatiles, retained solvents or resin decomposition products

Blistering <sup>1</sup>

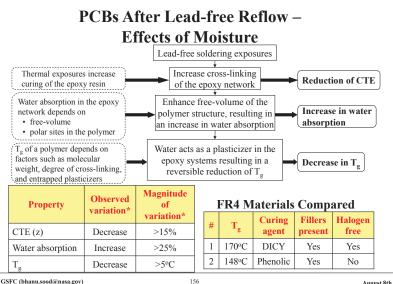

#### **Effect of Lead-free Soldering Exposures on PCB Laminates – 1**

- · Lead-free soldering reflow temperatures are much higher than the T<sub>a</sub> of FR-4 laminates and as the material is heated above T<sub>g</sub>, relative motion of the polymer chains increase

- · If the thermal exposures are sufficiently high, it could lead to the cleavage of bonds (at the chain ends, leading to further curing; or in the polymer backbone, leading to a degraded structure) in the polymer network and as the material is cooled below T<sub>o</sub>, the resulting polymer matrix could be either:

- an 'enhanced-cure' structure

- · More curing, leading to increase in the cross-linking density

- a 'degraded' structure

- · At approximately 240°C, thermal degradation of epoxy network begins through homolytic scission of chemical bonds, which influences its physical properties but does not cause a large weight loss1

- · At approximately 300°C, elimination of secondary alcohol groups as water molecules takes place leading to the formation of less stable allylic C-O linkages2

1-. J. Macan, I. Brnardic, S. Orlic, H. Ivankovic, M. Ivankovic, "Thermal degradation of epoxy-silica organic-inorganic hybrid materials", Polymer degradation and stability, vol. 91, pp. 122-127, 2006

2- S. Levchik, E. Weil, "Thermal decomposition, combustion and flame-retardancy of epoxy resins-a review of the recent literature". Polymer International, vol. 53, pp. 1901-1929, 2004

```

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

```

149

August 8th and 9th, 2018

#### Effect of Lead-free Soldering **Exposures on PCB Laminates – 2**

- · If the material is cured due to lead-free soldering exposures

- Cross-linking density increases due to further curing of the polymer, resulting in a reduction of CTE

- Increase in cross-linking density enhances the free-volume in the polymer structure, allowing for increase in water absorption [water absorption could increase due to increase in polarity of the molecules or due to the presence of more free-volume]

- This increase in water absorption increase the plasticity of the polymer matrix [water acts as a plasticizer]

- The plasticizing effect of water significantly reduces the T<sub>o</sub> of a material

- [plasticizers typically work by embedding themselves between the chains of polymers, spacing them apart, further increasing the free-volume]

- The plasticizing effect also results in softening of the material or a reduction in hardness

- But, with increase in cross-linking density, T<sub>e</sub> and hardness of the material could increase

- $T_{\sigma}$  of polymers is dependent on several parameters such as molecular weight of the material, its tacticity, the degree of cross-linking, and entrapped plasticizers1

Katrin Wondraczek, Jorg Adams, Jurgen Fuhrmann, "Effect of Thermal Degradation on Glass Transition Temperature of PMMA", Macromolecular Chemistry and Physics, vol. 205, issue 14, pp. 1858-1862, 2004 150

#### Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

August 8th and 9th, 2018

#### Effect of Lead-free Soldering **Exposures on PCB Laminates – 3**

- Thus there exist two possible competing mechanisms taking place due to increase in cross-linking, the effects of which counteract each other

- Reduction in T<sub>o</sub> with increase in water absorption leading to reduction in hardness

- Increase in T<sub>a</sub> and hardness

- Overall, the variation in properties due to lead-free soldering exposures can be correlated to the degree of cross-linking and the extent of water absorption in the exposed sample

- DICY cured systems are more hydrophilic to start with, compared to Phenolic cured systems.

## Effects of Moisture on T<sub>a</sub>

- A decrease in T<sub>g</sub> of an epoxy system is usually associated to the entrapped plasticizers.

- Water typically acts as a plasticizer in the epoxy systems resulting in a reduction of  $T_{o}$ .

#### **Effects of Moisture on CTE**

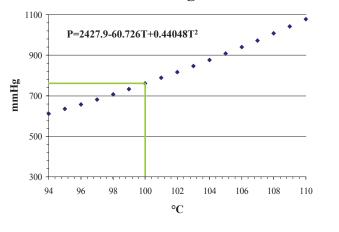

Exposure to humidity has no obvious effect on z-CTE values (below 100°C and above Tg).

- However, moisture causes swelling in PCB laminates between 100°C and the Tg point

- Increases z-axis expansion rates.

#### **Increased Z-Axis Expansion**

- Excessive out of plane expansion can lead to stress build up at PTH

- Circumferential cracking

- Single event overstress

- Cyclic fatigue • Openings (voids, etch pits) can accelerate circumferential cracking.

| Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov) | 153 | August 8th and 9th, 2018 | Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov) | 154 | August 8th and 9th, 2018 |

|---------------------------------------------|-----|--------------------------|---------------------------------------------|-----|--------------------------|

|                                             |     |                          |                                             |     |                          |

## **Circumferential Cracking – Single Event Overstress**

- CTE difference between copper plating and the resin system is at least a factor of 13

- Stress exerted on the plated copper in the plated-through holes in the z-axis can cause cracking.

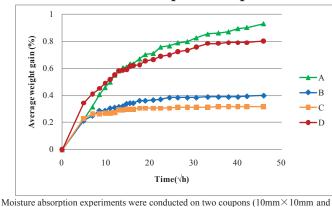

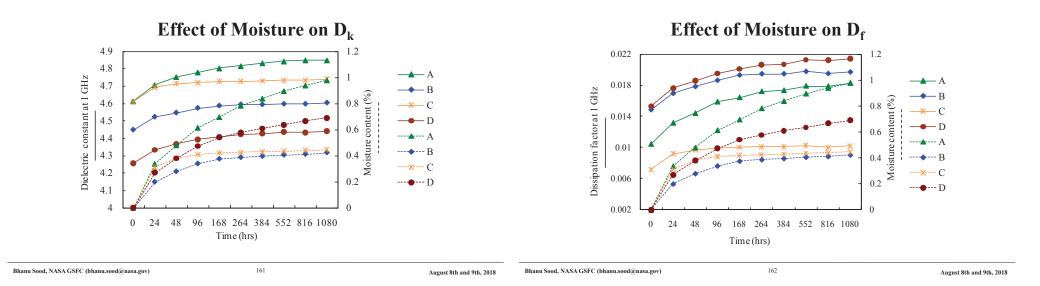

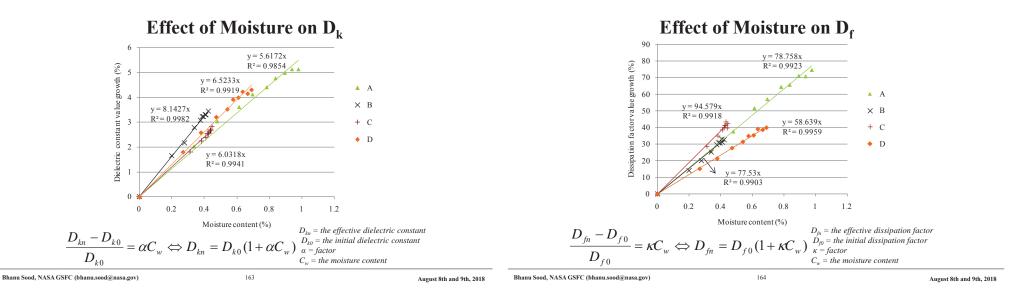

## Effect of Moisture on D<sub>k</sub> and D<sub>f</sub>

- Exposure to humidity impacts PCB materials' dielectric properties

- D<sub>k</sub> and D<sub>f</sub> increase linearly with an increase in the moisture content of the PCB materials. With specimen moisture content increasing from 0 to 0.98%, the  $D_{\mu}$  increased ~5.13% and the D<sub>f</sub> increased ~74.5% [1].

- The two most important phenomena are

- Dipole polarization due to polar molecules and;

- Interfacial polarization caused by inhomogeneities in the material.

L. Ma, B. Sood, and M. Pecht, ECS Transactions Vol. 27, Iss. 1, pp. 227-236; China Semiconductor Technology Int'l Conf. 2010: Metrology, Reliability and Testing, Shanghai, China, March 18-19, 2010.

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

157

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

158

Effect of Moisture on D<sub>k</sub> and D<sub>f</sub>

• Water has extremely polar O-H bonds and a  $D_{\mu}$  value close to

• Even a small amount of absorbed moisture significantly

inhomogeneities in the material.

increases the dielectric properties.

Schematic view of a capacitor

80. Water molecules will increase the dipole polarization due to polar molecules and interfacial polarization caused by

A capacitor with a dielectric medium of

its capacitance will be higher.

higher D<sub>k</sub> will hold more electric charge at the same applied voltage. In other words,

August 8th and 9th, 2018

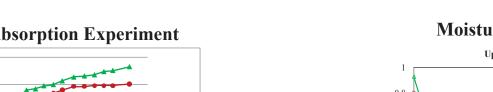

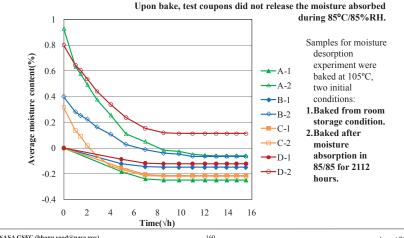

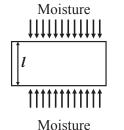

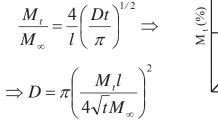

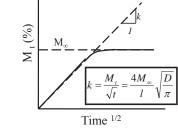

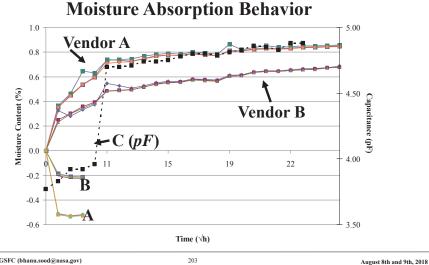

#### **Moisture Desorption Experiment**

#### **Moisture Absorption Experiment**

20mm $\times 20$ mm) of each PCB material, which were exposed in 85°C and 85% RH condition and the coupons were taken out of chamber to measure weight at increasing time intervals.

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

#### **Effects of Adsorbed Moisture** on Traces

- Wet corrosion occurs when two metals/alloys connected by a layer of adsorbed moisture one acts as anode and other act as cathode

- Either due to different materials or same material with different potential bias.

- Ambient RH and temperature dictate amount water adsorbed.

- Ionic contamination enhances conductivity.

- Shorts occur when moisture creates a bridge across traces.

Corrosion of HASL (10 VDC)

## **Process of Corrosion**

Requirements - Aqueous medium (moisture) Red.  $\Leftrightarrow$  Ox. Me  $\Leftrightarrow$ Mg2+ - Metal (solder) -AP - Corrosive agent (flux) Zn 0 Zn2 - Oxygen or carbon dioxide Cr -C2 Fe 0 Cd 0 Cđ - Continuous (corrosive agent is Co 0 Cd 0 Sn - Terminated (creation of a 0 passivation layer on metal) - Terminated (presence of 0 Cu Cur 0 Ae Ac depolarization agent in flux)

#### **Electrochemical potential of** metals in contact with water + e E<sup>0</sup>[Volt] + 2e -2.37 -1,66 + 3e + 2e -1.19-0,76 + 2e -0.74+ 3e -0,44 2e 2e -0,40+ 2e -0.282e -0.23 + 2e -0.14 + 2e -0.13 + 2e 0.00 + 2e +0,34+0.80+ e +0.99 $\Leftrightarrow$ + 2e Pr2+ + 2e +1,20 Pt $\Leftrightarrow$ $\Leftrightarrow Au^{3+}$ +1.50 Au 4 30

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

165

August 8th and 9th, 2018

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

• Outcomes

recycled)

166

August 8th and 9th, 2018

## **Electro-Chemical Migration**

- Electrochemical migration (ECM) is the growth of conductive metal filaments (dendrites) on or through a printed circuit board (PCB) through an electrolytic solution (usually  $H_2O$ ) under the influence of a DC voltage bias [1].

- Surface Insulation Resistance (SIR) is the resistance between two electrical conductors separated by some dielectric material(s) [2].

- · Failure mechanism: ECM through electrodissolution, ion transport, and electrodeposition

- Failure modes: electrical shorts and drops in SIR

- Failure sites: wherever moisture, oppositely biased conductors, and contamination exist simultaneously: e.g., between the traces on a printed circuit board

**Dendritic Growth During a Water Drop Test \***

\*From Contamination Studies Laboratory, Inc., http://www.residues.com

IPC Publication IPC-TR-476A, "Electrochemical Migration: Electrically Induced Failures in Printed Wiring Assemblies," Northbrook, IL, May 1997. 2 IPC Publication IPC-9201, "Surface Insulation Resistance Handbook," Northbrook, IL, July 1996.

#### **Preventative Actions for ECM Factors Influencing ECM Reduce Moisture** · Conductor pre-treatment and • Temperature surface condition Humidity • Ensure proper solder mask coverage - Conductor surface roughness, Voltage Bias/Voltage Gradient scratches/pits, presence of solder • Conformal coatings Conductor Spacing mask and conformal coatings - Barrier to external sources of contamination. • Contamination (type and - Permeability of coatings - Reduce moisture absorption concentration) • Substrate composition (FR-4, - Halide vs non-halide - Ineffective against intrinsic contaminants BaTiO<sub>3</sub>, etc.) - Organics • Electrolyte (e.g., water, rosin) - Delamination of coating from board can accelerate • Conductor material (copper, ECM due to moisture condensation • Gaseous pollutants (Cl<sub>2</sub>, H<sub>2</sub>S, silver, tin/lead, etc.) $SO_2$ ) • Conductor geometry · Ambient air velocity · Surface topology • Conductor configuration (comb) 169 170 Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov) Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov) August 8th and 9th, 2018 August 8th and 9th, 2018

## **Conformal Coating**

- Conformal coating is defined as a thin polymeric layer.

- The application of conformal coating is to protect the components on PCB from the environments.

- The conformal coating is required not only to protect the circuit against the effects of environmental hazards, but also to provide good dielectric characteristics and moisture resistance.

- The selection of conformal coatings is rely on the protection requirement for PCB.

**Introduction to Conformal Coatings**

## **Required Performance for Conformal Coating**

- Excellent dielectric characteristics

- High insulation resistance

- Excellent environmental resistance

- Tenacious adhesion to difficult substrates

- Excellent moisture and thermal shock resistance

- Non-slumping viscosities

- Excellent abrasion resistance

# **Some Conformal Coating Specifications**

- MIL I-46058C: Insulating compound, electrical (for coating printed circuit assembles)

- IPC CC-830: Qualification and performance of electrical insulation compounds for printed board assembles

| Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov) | 173 | August 8th and 9th, 2018 | Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov) | 174 | August 8th and 9th, 2018 |

|---------------------------------------------|-----|--------------------------|---------------------------------------------|-----|--------------------------|

|                                             |     |                          |                                             |     |                          |

|                                             |     |                          |                                             |     |                          |

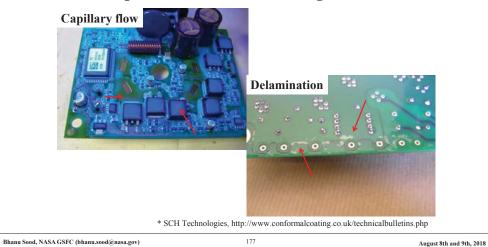

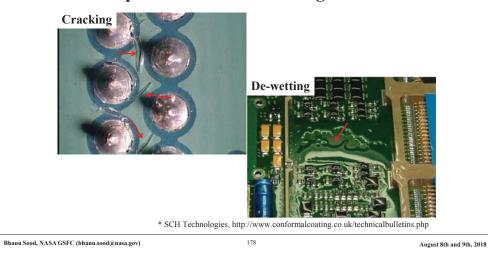

## **Common Coating Failure Mechanism (1/2)**

- Capillary flow: Cause by low viscosity or high surface tension of the conformal coating, surface energy of substrate

- Delamination: Caused by contaminations on substrate, surface energies mismatch (poor adhesion), moisture permeation

- Cracking: Caused by too high cure temp, large CTE mismatch due to the excessive coating thickness

- De-wetting: Caused by residues or contaminatoins on substrate

# **Common Coating Failure Mechanism (2/2)**

- · Corrosion: Caused by improper cleaning method or handling

- Orange Peel: Caused by incorrect thickness of the coating or cure profile

\* SCH Technologies, http://www.conformalcoating.co.uk/technicalbulletins.php

#### **Examples of Common Coating Failure 1/2**

#### **Examples of Common Coating Failure 1/3**

#### **Examples of Common Coating Failure 1/3**

## **Conformal Coating Manufacturers**

- Humiseal

- Dow Corning

- Dymax

- Tech Spray

- Cytec

- Emerson & Cuming

- Loctite

\* SCH Technologies, http://www.conformalcoating.co.uk/technicalbulletins.php

Bhanu Sood, NASA GSFC (bhanu.sood@nasa.gov)

#### **Physical Properties**

- Viscosity

- Hardness

- Adhesion

- Modulus of Elasticity

## **Test Methods – Viscosity**