# NASA/TM-2018-220074 NESC-RP-16-01117

# Guidelines for Verification Strategies to Minimize RISK Based On Mission Environment, -Application and -Lifetime (MEAL)

Oscar Gonzalez/NESC Langley Research Center, Hampton, Virginia

Yuan Chen Langley Research Center, Hampton, Virginia

Raymond L. Ladbury Goddard Space Flight Center, Greenbelt, Maryland

Dwayne R. Morgan Wallops Flight Facility, Wallops Island, Virginia

Christopher M. Green Goddard Space Flight Center, Greenbelt, Maryland

Daniel E. Yuchnovicz/NESC Langley Research Center, Hampton, Virginia

## NASA STI Program . . . in Profile

Since its founding, NASA has been dedicated to the advancement of aeronautics and space science. The NASA scientific and technical information (STI) program plays a key part in helping NASA maintain this important role.

The NASA STI program operates under the auspices of the Agency Chief Information Officer. It collects, organizes, provides for archiving, and disseminates NASA's STI. The NASA STI program provides access to the NTRS Registered and its public interface, the NASA Technical Reports Server, thus providing one of the largest collections of aeronautical and space science STI in the world. Results are published in both non-NASA channels and by NASA in the NASA STI Report Series, which includes the following report types:

- TECHNICAL PUBLICATION. Reports of completed research or a major significant phase of research that present the results of NASA Programs and include extensive data or theoretical analysis. Includes compilations of significant scientific and technical data and information deemed to be of continuing reference value. NASA counter-part of peerreviewed formal professional papers but has less stringent limitations on manuscript length and extent of graphic presentations.

- TECHNICAL MEMORANDUM. Scientific and technical findings that are preliminary or of specialized interest, e.g., quick release reports, working papers, and bibliographies that contain minimal annotation. Does not contain extensive analysis.

- CONTRACTOR REPORT. Scientific and technical findings by NASA-sponsored contractors and grantees.

- CONFERENCE PUBLICATION.

Collected papers from scientific and technical conferences, symposia, seminars, or other meetings sponsored or co-sponsored by NASA.

- SPECIAL PUBLICATION. Scientific, technical, or historical information from NASA programs, projects, and missions, often concerned with subjects having substantial public interest.

- TECHNICAL TRANSLATION.

English-language translations of foreign scientific and technical material pertinent to NASA's mission.

Specialized services also include organizing and publishing research results, distributing specialized research announcements and feeds, providing information desk and personal search support, and enabling data exchange services.

For more information about the NASA STI program, see the following:

- Access the NASA STI program home page at <a href="http://www.sti.nasa.gov">http://www.sti.nasa.gov</a>

- E-mail your question to help@sti.nasa.gov

- Phone the NASA STI Information Desk at 757-864-9658

- Write to:

NASA STI Information Desk

Mail Stop 148

NASA Langley Research Center

Hampton, VA 23681-2199

# NASA/TM-2018-220074 NESC-RP-16-01117

# Guidelines for Verification Strategies to Minimize RISK Based On Mission Environment, -Application and -Lifetime (MEAL)

Oscar Gonzalez/NESC Langley Research Center, Hampton, Virginia

Yuan Chen Langley Research Center, Hampton, Virginia

Raymond L. Ladbury Goddard Space Flight Center, Greenbelt, Maryland

Dwayne R. Morgan Wallops Flight Facility, Wallops Island, Virginia

Christopher M. Green Goddard Space Flight Center, Greenbelt, Maryland

Daniel E. Yuchnovicz/NESC Langley Research Center, Hampton, Virginia

National Aeronautics and Space Administration

Langley Research Center Hampton, Virginia 23681-2199

# Acknowledgments

The team would like to recognize and dedicate this paper in memory of Mr. Robert Kichak. His open-minded nature and objective engineering mentality helped NASA, the space community, and other government agencies negotiate the difficult challenges of ensuring reliable space systems over many decades. His integrity, patience, experience, and deep understanding are a great loss to the community.

The team would like to thank the following for their thorough review of this paper.

Steven Gentz, NESC Chief Engineer, MSFC

Steven Guertin, Parts Radiation, JPL

Timothy Ruffner, Avionics, GRC

Steven Rickman, NASA Technical Fellow for Passive Thermal

Kenneth Johnson, NESC Systems Engineering, MSFC

The use of trademarks or names of manufacturers in the report is for accurate reporting and does not constitute an official endorsement, either expressed or implied, of such products or manufacturers by the National Aeronautics and Space Administration.

Available from:

NASA STI Program / Mail Stop 148 NASA Langley Research Center Hampton, VA 23681-2199 Fax: 757-864-6500

# **NASA Engineering and Safety Center**

Guidelines for Verification Strategies to Minimize RISK Based On Mission Environment, -Application and -Lifetime (MEAL)

**April 5, 2018**

# **Report Approval and Revision History**

NOTE: This document was approved at the April 5, 2018, NRB. This document was submitted to the NESC Director on April 9, 2018, for configuration control.

| Approved: | Original Signature on File | 4/9/18 |

|-----------|----------------------------|--------|

|           | NESC Director              | Date   |

| Version | Description of Revision | Office of Primary<br>Responsibility                            | Effective Date |  |

|---------|-------------------------|----------------------------------------------------------------|----------------|--|

| 1.0     | Initial Release         | Oscar Gonzalez, NASA<br>Technical Fellow for<br>Avionics, GSFC | 4/5/18         |  |

# **Table of Contents**

| Signat  | U       | 2                                                                                     |     |

|---------|---------|---------------------------------------------------------------------------------------|-----|

| 1.0     | Backgi  | ound                                                                                  | 6   |

| 2.0     |         | ive Summary                                                                           |     |

| 3.0     | Verific | ation based on MEAL and Risk Posture                                                  |     |

|         | 3.1     | Understanding MEAL                                                                    |     |

|         | 3.2     | Understanding Risk and Risk Posture                                                   | 11  |

|         | 3.2.1   | Risk – Metrics and Matrices                                                           | 11  |

|         | 3.2.2   | Cost, Schedule and Technical Risks versus Verification Test Level                     | 13  |

|         | 3.3     | Understanding Flight Heritage                                                         | 14  |

|         | 3.3.1   | MEAL & TRL Concepts to Assess Flight Heritage                                         | 15  |

| 4.0     | Verific | ation Test and Inspection Matrix at Part-, Board- and Box-Level                       | 18  |

|         | 4.1     | Verification Test/Inspection Purposes, Capabilities, Advantages, and Limitations      | 18  |

|         | 4.2     | Verification Test/Inspection at Part-, Board-, Box/Subsystem- and System-Level        | 18  |

|         | 4.2.1   | Part-level Verification                                                               | 18  |

|         | 4.2.1.1 | Introduction                                                                          | 18  |

|         | 4.2.1.2 | Parts Testing: Why and How                                                            | 19  |

|         | 4.2.1.3 | Screening for Part Infant Mortality and Other Defects                                 | 19  |

|         | 4.2.1.4 | Major Advantages and Limitations of Part-level Verification                           | 19  |

|         | 4.2.2   | Board-level Verification                                                              | 20  |

|         | 4.2.3   | Box-level or Subsystem-level Verification                                             | 21  |

|         | 4.2.4   | System-level Verification                                                             | 21  |

|         | 4.2.5   | Radiation Effects Verification                                                        | 21  |

|         | 4.2.5.1 | TID, DDD, and SEE                                                                     | 22  |

|         | 4.2.5.2 | Radiation Testing at Different Configuration Levels                                   | 22  |

|         | 4.2.6   | Potential Consequences of Skipping Part-level Testing                                 | 25  |

|         | 4.2.7   | Thermal Impact on Part-, Board- and Box-level Verification - an Example               |     |

| 5.0     | Verific | ation of COTS Part, Board, and/or Box                                                 |     |

|         | 5.1     | Background of COTS Use in Spaceflight Programs                                        | 30  |

|         | 5.2     | Verification Process for COTS Technology                                              |     |

| 6.0     | Examp   | ole Lessons Learned for Verification Based on MEAL and Risk Posture                   |     |

|         | 6.1     | Heritage Misapplication Examples                                                      |     |

|         | 6.2     | Part-level Verification: Enabling Identification of Part Infant Mortality Defects and |     |

|         |         | Failures.                                                                             | 36  |

|         | 6.3     | Challenges of Radiation Testing on COTS Parts: Part-to-Part SEE Variability for       |     |

|         |         | Some COTS Parts                                                                       | 38  |

| 7.0     | Definit | ions                                                                                  | 39  |

| 8.0     | Acrony  | vms List                                                                              |     |

| Append  |         |                                                                                       |     |

| Appen   |         | Matrix for a Set of Common Verification Tests and Inspections: Purposes,              |     |

| • •     |         | Capabilities, Advantages and Limitations of Each Verification Performed at Different  |     |

|         |         | Level of Integration                                                                  |     |

| Append  | dix B.  | Counterfeit Parts                                                                     |     |

| Append  |         | Team List/Acknowledgements                                                            |     |

| 11.     |         |                                                                                       |     |

|         |         | List of Figures                                                                       |     |

| Figure  | 1 NE    | SC Risk Matrix and Related Definitions of the Matrix Element Definitions              | 12  |

| Figure  |         | tional Cost and Schedule Impacts when Performing Testing at Part-, Board-, and Box-   | 1 4 |

| 1 iguic |         | velvel                                                                                | 13  |

|         | LC.     | ·                                                                                     | 10  |

| Figure 3.  | Notional Ability to Detect Parts Defects and Interaction between Parts when Performing                               |    |

|------------|----------------------------------------------------------------------------------------------------------------------|----|

|            | Testing at Part-, Board-, and Box- Level                                                                             |    |

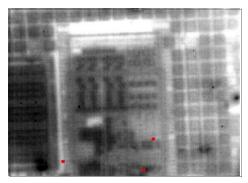

| Figure 4.  | Simulated strikes of ions (red dots) overlaid on a photomicrograph 60 x 70 µm <sup>2</sup> section of                |    |

|            | an Elpida 512 Mbit SDRAM. Left: Recoil Ions due to 10 <sup>10</sup> Protons/cm <sup>2</sup> . Right: 10 <sup>7</sup> |    |

|            | ions/cm <sup>2</sup> Typical of Heavy ion SEE Test                                                                   | 24 |

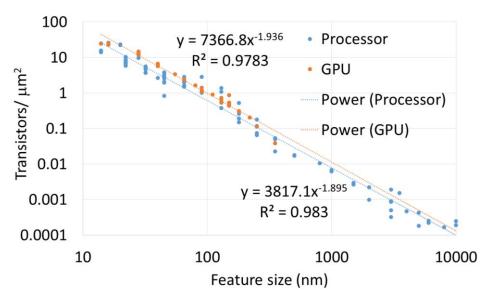

| Figure 5.  | Transistor Count Scales Roughly as the Inverse Square of the Minimum Feature Size of                                 |    |

| -          | the Technology                                                                                                       | 24 |

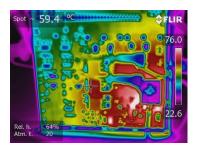

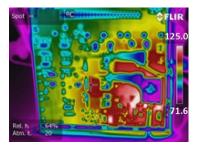

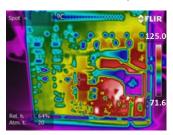

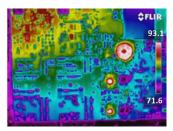

| Figure 6.  | Left: Image of Board #1. Right: Thermal image of the Powered Board #1                                                | 26 |

| Figure 7.  | Board #1 Estimated Temperature Profile with Ambient Temperature of 71.6°C                                            | 26 |

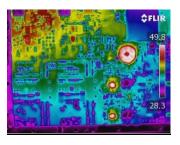

| Figure 8.  | Left: Image of Board #2; Right: Thermal Image of Powered Board #2                                                    | 27 |

| Figure 9.  | Board #2 estimated Temperature Profile with Ambient Temperature of 103.5°C                                           |    |

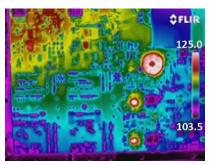

| Figure 10. | Estimated Maximum Boards #1 and 2 Temperature Profile when Tested at the Box-l                                       |    |

|            | Level                                                                                                                | 28 |

| Figure 11. | Notional Bathtub Reliability Curve                                                                                   | 30 |

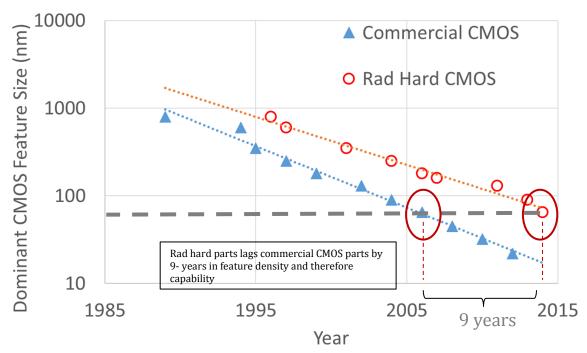

| Figure 12. | Comparison between Commercial and Radiation-Hardened CMOS Technologies                                               | 31 |

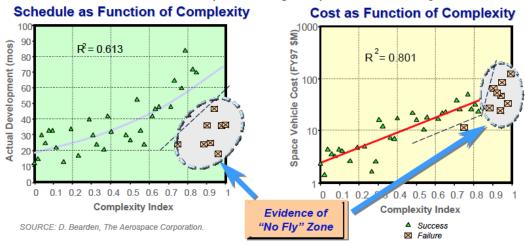

| Figure 13. | Evidence of "No Fly" Zone.                                                                                           | 32 |

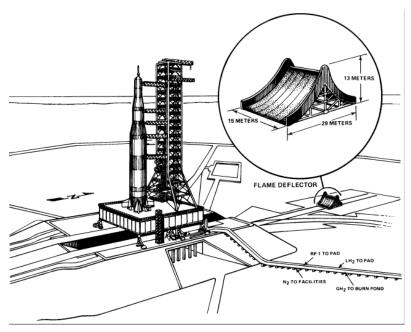

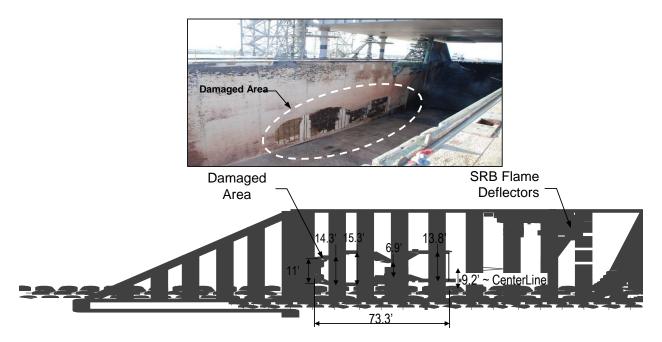

| Figure 14. | Launch Pad 39A Flame Deflector System.                                                                               | 34 |

|            | Image and Sketch of the Launch Pad 39A Flame Trench (SRB side) Affected Area                                         |    |

|            | List of Tables                                                                                                       |    |

| Table 1.   | Elements of Mission Risk Posture Impact/Consequence Areas                                                            | 13 |

| Table 2.   | TRL, Heritage and MEAL Examples                                                                                      |    |

| Table 3.   | Comparison of Acceleration Factors between Single-board and Box-level Thermal Tests                                  | 29 |

| Table 4.   | Comparison of Equivalent Time Corresponding to 168 Hour Burn-in Test on the Hottest                                  |    |

|            | and Coldest Components on the Example Boards and Boxes.                                                              | 29 |

# Signature Page

| Submitted by:                 |         |                          |      |

|-------------------------------|---------|--------------------------|------|

| Team Signature Page on File – | 4/23/18 |                          |      |

| Mr. Oscar Gonzalez            | Date    |                          |      |

| Significant Contributors:     |         |                          |      |

| Dr. Yuan Chen                 | Date    | Dr. Raymond L. Ladbury   | Date |

| Mr. Dwayne R. Morgan          | Date    | Mr. Christopher M. Green | Date |

| Mr. Daniel E. Yuchnovicz      | Date    |                          |      |

|                               |         |                          |      |

See Appendix C for Team List/Acknowledgements.

# 1.0 Background

There is a trend of compromising verification testing to address the cost and schedule constraints, which poses a high-risk posture for programs/projects. Current and emerging aerospace scientific and/or human exploration programs continue to pose new technological challenges. These technological challenges combined with finite budgets and truncated schedules are forcing designers, scientists, engineers, and managers to push technologies to their physical limits. In addition, budget and schedule pressures challenge how those technologies/missions are verified.

A clear understanding of the different verification processes is needed to ensure the proper verification of the technology within the mission (i.e., capabilities, advantages, and limitations). The goal of verification is to prove through test, analysis, inspection, and/or demonstration that a product provides its required *function* while meeting the performance requirements. It is important that verification yield understanding of representative performance under worst-case conditions so that margins to failure can be evaluated for proposed applications. The capabilities, advantages, and limitations of the testing and inspection performed at each level are different, and the risk incurred by omitting a verification step depends on the level of integration as well as Mission, Environment, Application and Lifetime (MEAL).

This paper focuses on verification processes. The goal of the verification process is to ensure the given avionics technology could be safely implemented on the given MEAL consistent with the program/project risk posture.

# 2.0 Executive Summary

This paper describes selection of the verification processes taking into account MEAL and risk posture. This paper compares common verification tests and inspections by describing the capabilities, advantages, and limitations of the verification depending on the level of integration (i.e., part-, board-, box-level, etc.) being used. When properly implemented, these tests ensure that the given avionics system and technology can be safely used on the given human-rated or robotic program with acceptable risks in safety critical spaceflight applications.

As demands for improved performance in spaceflight programs increase, and budget and schedule pressures remain constrained, the temptation has increased to implement new or previously flown avionics technologies, including COTS technologies, into human-rated and robotic spaceflight programs.

Spaceflight programs are incentivized to use these avionics technologies to reduce design, development, test, and evaluation (DDT&E) costs, to meet programmatic schedules, and increase system performance. However, in some cases, these technologies that have not been fully vetted according to procedures appropriate for operation in a different space environment, or for their intended application, environment and life cycle have been inserted into space hardware, introducing risks to the spaceflight systems. To avoid introducing such risks, it is critical to understand the risk impact on the proposed technology in terms of the **M**ission definition and its related **E**nvironment, **A**pplication and **L**ifetime (MEAL) along with the associated **risk** posture.

The motivation is to <u>combat common myths or misunderstandings about verification</u>, such as:

- 1) One size fits all;

- 2) It is not important to understand the verification process including capabilities, advantages and limitation at different integration level;

- 3) New technologies have sufficient reliability built-in and so require no additional screening or qualification;

- 4) There is no need to do any further verification beyond the manufacturer's data on COTS technologies;

- 5) Cost, budget and schedule pressures provide adequate reason for deviating from accepted qualification and screening procedures;

- 6) Flight heritage allows omission of critical verification steps.

This paper describes a MEAL and risk posture base verification process for selection and verification of avionics technology including COTS parts, board and/or box technologies. The paper presents a set of common verification tests and inspections matrix with comparisons of each verification test or inspection by describing the *capabilities, advantages and limitations* of the test or inspection depending on the *level of integration* (i.e., part, board, box, etc.) being used. The paper also uses the concept of technology readiness level (TRL) centered on MEAL to assess flight heritage, providing steps required to qualify any design and to help assess whether the "heritage design" is or not suitable for the given mission.

The paper's strategy focuses on MEAL and verification assurance. When properly implemented, these tests and inspections ensure that the technologies passing these tests can be safely used on the given flight program with acceptable risks even in safety-critical spaceflight applications.

The goal of this paper is to enhance awareness of the: 1) capabilities, advantages, limitations of verification processes; 2) related impact to risks associated with various part-, board-, and box-level verification testing; and 3) how risks can be managed for selection and verification of parts based on an integrated assurance approach focusing on MEAL and verification assurance.

# Key take away messages are:

- 1. MEAL (mission, mission environment, application and lifetime of the mission or application)

- a. The understanding of the MEAL requires a complete picture of how avionics and technologies are to be used effectively. The considerations summarized in the MEAL allow designers to effectively choose parts for their best performance in a given architecture. Emphasizing one of the MEAL elements without understanding the others can compromise the integrity and performance of the parts and the mission success.

# 2. Verification process driven by MEAL and mission risk posture

- a. The MEAL suggests appropriate strategies for mission design, development, implementation, and defines end-of-mission conditions. It also informs/bounds the verification approach and processes through all stages. The selected verification processes must ensure the adequacy of the design is commensurate with the risk that is acceptable to the project.

- b. Verification processes should show that the end product conforms to its specified requirements at all levels (i.e., part-, board-, box-level, subsystem-level, and system-level).

- c. Skipping part-level testing is often done to reduce the cost and schedule of testing. However, cost savings will be realized only if <u>no</u> failures are detected during testing at the higher integration level, assuming this higher integration level testing is sufficient to catch individual parts that could fail during a mission. If there were any failures detected at a higher level, then it would have a <u>negative impact on cost and schedule</u>. Moreover, testing at higher integration levels reduces knowledge of design margin and margin to failures. Vulnerabilities not detected during verification process may lead to adverse consequences ranging from degraded performance to LOM or LOC.

- d. In general, the higher the integration, the lower the overall acceleration factor<sup>1</sup>. If tested at the part level, then each individual part could be subjected to maximum stress to achieve the largest possible acceleration factor.

- e. The same test conducted at different integration levels yields different information, both quantitatively and qualitatively.

<sup>&</sup>lt;sup>1</sup> http://www.itl.nist.gov/div898/handbook/apr/section1/apr14.htm

#### 3. Heritage assessment by the TRL concept centered on MEAL

- a. The use of the TRL concept centered on MEAL to assess flight heritage provides the steps required to qualify any design and could help assess if the "heritage design" is or is not suitable for the given mission.

- b. To claim "heritage", the previous mission's characteristics must bound those of the new mission in terms of environment, application, and lifetime. If these bounds are not realized, then the new system would have to regress to the appropriate TRL and be certified/verified to the predicted conditions of new mission.

- c. As noted in Government Accounting Office Best Practices reports, "The incorporation of advanced technologies before they are mature has been a major source of cost increases, schedule delays, and performance problems on weapon systems. Demonstrating a high level of maturity before new technologies are incorporated into product development programs puts those programs in a better position to succeed".<sup>2,3</sup>

In summary, there is **no unique** (that is, no one size fits all) solution for the selection and verification of the avionics system and technology, including architecture and parts assurance requirements, that ensures reliable safety and mission success. Understanding **MEAL** and **risks**, as well as adopting an attitude of "**always verify**" (trust but verify), is crucial.

- The MEAL and risk posture based verification process applies to any avionics technology system verification, including COTS part-, board-, and box- technology and previously flown technology.

- A comprehensive verification program bounded by MEAL and risk posture requires a

full understanding of the capabilities, advantages, and limitations of verification

testing conducted at different levels of integration.

\_

<sup>&</sup>lt;sup>2</sup> GAO Best Practice, "Better Management of Technology Development can Improve Weapon System Outcomes", NSIAD-99-162, July 30, 1999.

<sup>&</sup>lt;sup>3</sup> GAO Best Practices, "Technology Readiness Assessment Guide – Best Practices for Evaluating the Readiness of Technology for Use in Acquisition Programs and Projects", August 2016.

#### 3.0 Verification based on MEAL and Risk Posture

The selection and verification of the avionics system architecture and parts technology in spaceflight programs begin with the mission definition and its related **m**ission, mission environment, **a**pplication and lifetime of the mission or application (MEAL), along with the accepted **risk** associated with the mission category and/or payload class. These factors influence the design, development, integration, implementation, end-of-mission conditions, and verification process throughout all these stages.

Improper verification of the avionics system and technology can occur due to lack of understanding the program's MEAL, risk posture, or avionics technology, skipping verification testing at different integration level(s), or taking vendor technical and/or qualification data at face value without sufficient evidence or understanding. This can expose programs to unknown risks arising from the implementation/use of these technologies. At the same time, the more complex the avionics system, the more MEAL-dependent will be the conclusion of the analysis of verification data.

In summary, there is **no unique** (that is, no one size fits all) solution for the selection and verification of the avionics system and technology, including architecture and parts assurance requirements, that ensures reliable safety and mission success. Understanding **MEAL** and **risks**, as well as adopting an attitude of "**always verify**" (trust but verify), is crucial.

# 3.1 Understanding MEAL

The selection of the avionics system architecture and parts quality assurance requirements in any spaceflight program begins with the mission definition and its related MEAL, along with the accepted risk associated with the mission category and/or payload class.

#### MEAL is defined as:

**Mission:** The ultimate science goal or objective of the overall effort. The "mission" in the MEAL acronym identifies what type/kind of mission. Is this a human or robotic mission? What are the mission category and payload classifications, and what level of risk is the mission willing to take? This often implies different sets of parts requirements, standards, and test criteria. Understanding the mission helps define the requirements associated with the environment(s), defines the applications to meet the mission goals, and defines the expected progression of the mission from development to the end of the mission. The mission helps management define the risk levels NASA is willing to take (i.e., risk posture is the position the mission is willing to take based on the MEAL risks that have been identified. There is no single, uniform standard for risk posture, and depending on the mission, risk posture is often a tailored approach that is based on the mission applications and needs).

**Environment:** The relevant ambient conditions the system would experience during the life cycle to accomplish the mission (e.g., thermal effects, electromagnetics effects, electrostatic effects, radiation effects, etc.).

The mission environment is critical for parts as it defines the stresses experienced and ensures an understanding of the required operating environment, parts performance thresholds and margins, and non-operating conditions for active and passive parts. Designers must consider the parts environmental performance specifications relative to the mission environment to specify and ensure required design margins.

<u>Application</u>: Specific function(s) to be executed to meet the goals of the mission. The mission application includes the architecture and its redundancy requirements. This enables the parts to be properly applied/used for an application and/or function. Further, this gives designers an understanding of how parts are to be used in a sub-system or system correctly and effectively. Designers must consider how parts interface and interact with the rest of the electrical circuit and other subsystems over the entire mission.

<u>Lifetime</u>: The total time during which the system must perform its intended functions, including subcomponent manufacturing, systems development, system implementation, system execution/operations, and retiring of the system to accomplish the mission.

The mission lifetime defines the criteria for parts to be selected, applied, and tested for missions, so that premature failures do not affect the mission outcome. This gives designers an understanding of how to size the lifespan of parts and utilize them in a given architecture.

The understanding of the MEAL requires a complete synchronous picture of how avionics and parts technologies are to be used effectively. The considerations summarized in the MEAL allow designers to effectively choose parts for their best performance in a given architecture. Emphasizing one of the MEAL elements without understanding the others can compromise the integrity and performance of the parts and the mission success.

The MEAL suggests appropriate strategies for mission design, development, implementation, and defines end-of-mission conditions. It also informs/bounds the verification approach and processes through all stages. The selected verification processes must ensure the adequacy of the design is commensurate with the risk that is acceptable to the project.

# 3.2 Understanding Risk and Risk Posture

For a NASA spaceflight program, the risk matrix is a management tool for communicating how individual issues (e.g., schedule, cost, and technical) related to a given mission are classified and prioritized to one another. The risk matrix main components are: 1) the probability/likelihood of failing to achieve a particular outcome, and 2) the consequence/impact of failing to achieve that outcome. The assessment of risk and its depiction in a risk matrix has been widely accepted by many communities from academia, U.S. government, and industry as a way to show the relative ranking of risks.

#### 3.2.1 Risk – Metrics and Matrices

NASA does not have a specific risk matrix for all missions, but has allowed each program to develop their own matrix to fit their given mission requirements based on the respective MEAL.

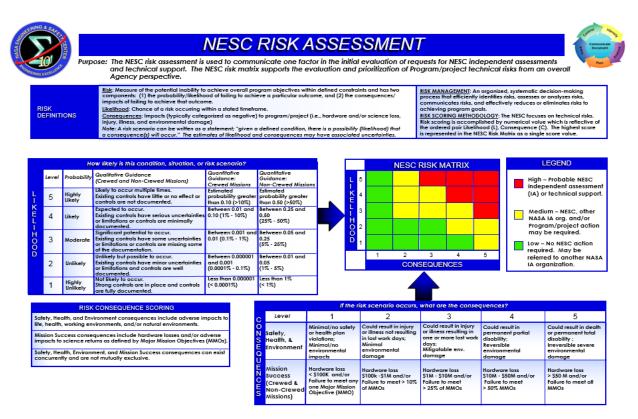

The NASA Engineering and Safety Center (NESC) defined "Risk" as a measure of the potential inability to achieve overall program objectives within defined constraints. For reference, Figure 1 presents the NESC risk matrix and related definitions of the matrix elements.

Updated: July 2016

Figure 1. NESC Risk Matrix and Related Definitions of the Matrix Element Definitions<sup>4</sup>

Risk posture is the position program management is willing to take based on the MEAL and identified risks. There is no standard for risk posture, and depending on the mission, the approach taken is often tailored based on the mission applications and needs (e.g., human-rated versus robotic, launch vehicle versus spacecraft).

The primary risk impact/consequence areas considered in this paper are crew safety and health, mission success or technical performance, and programmatic as listed in the Table 1.

Programmatic risk impact/consequence includes cost and schedule for human-rated and robotic explorations. Risk impact/consequence for human exploration missions include loss of crew (LOC) and loss of mission (LOM) in Safety & Health, and Mission Success or Technical Performance, while robotic exploration missions are focused primarily on LOM impact/consequence.

<sup>&</sup>lt;sup>4</sup> R. W. Malone, "Development of Risk Assessment Matrix for NASA Engineering and Safety Center", January 2004.

Table 1. Elements of Mission Risk Posture Impact/Consequence Areas

|                            | Risk Impact/Consequence |                                             |               |  |  |  |

|----------------------------|-------------------------|---------------------------------------------|---------------|--|--|--|

| Mission Type               | Safety &<br>Health      | Mission Success or<br>Technical Performance | Programmatic  |  |  |  |

| Human-rated<br>Exploration | LOC                     | LOM                                         | COST/SCHEDULE |  |  |  |

| Robotic<br>Exploration     | LOM                     | LOM                                         | COST/SCHEDULE |  |  |  |

# 3.2.2 Cost, Schedule and Technical Risks versus Verification Test Level

Appendix A provides a list of common verification tests and inspections performed at different integration levels (i.e., the part-, board- and box-level, along with the purpose, capabilities, advantages, and limitations for each test and inspection).

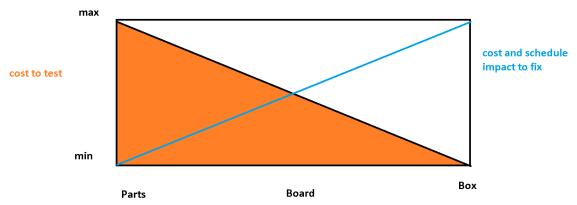

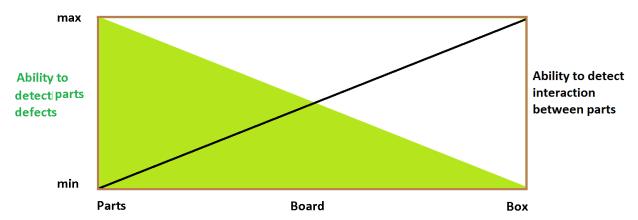

Based on the limitations identified in Appendix A, testing at a higher level of integration results in reduced ability to detect a part defect. Therefore, skipping tests at earlier integration levels increases the probability of a defect not being detected (e.g., Hubble Space Telescope mirrors). Furthermore, a failure detected at a higher integration level impacts cost and schedule due to the rework required to fix the problem. Finding a part issue at the fully integrated system level is usually expensive, time consuming, and adds risk with the disassembly, replacement or repair, reassembly and re-testing of the refurbished assembly (i.e., collateral damage that occurs while repairing the board and/or wear-out). Notional Figures 2 and 3 illustrate this concept.

Figure 2 shows, in a simplified representation, the "cost to test" decreases while "cost and schedule impact to fix" increases as a function of performing testing at part-, board- and box-level. This is partly because of the number of independent tests required decrease when moving to higher level of testing. The test cost can be lower, but the cost and schedule consequences of experincing a failure increase dramatically. The overall cost is only lower if there is no problem or failure is detected at higher levels of testing.

Figure 2. Notional Cost and Schedule Impacts when Performing Testing at Part-, Board-, and Box-Level

Figure 3, in a simplified representation, shows that testing at lower levels of integration improves ability to detect part defects. Many part defects are masked at higher levels of integration, but identifying these defects will increase system reliability by reducing the likelihood of latent

failures. Conversely, testing at higher levels of integration is more effective to detecting interactions between parts and assembly workmanship defects, which impact reliability.

Figure 3. Notional Ability to Detect Parts Defects and Interaction between Parts when Performing Testing at Part-, Board-, and Box- Level

Understanding of the human-rated or robotic mission risk posture, system architecture, and the system effect of part-level errors and failures is critical in selecting the parts for safety critical applications as well as the type of verification required (testing, inspection, screening, qualification, etc.). These types of effects may have impacts to safety and health as well as mission success or technical performance.

Appendix A supports the conclusion that considerations of safety and health, mission success, technical performance, and programmatic risk impacts/consequences are optimized by implementing testing as early as possible during the development process.

# 3.3 Understanding Flight Heritage

Heritage as defined in the Merriam-Webster dictionary is "something transmitted by or acquired from a predecessor," similar to legacy as "something transmitted by or received from an ancestor or predecessor or from the past." In the spaceflight environment, flight heritage commonly refers to a successfully flown design or qualified hardware, and/or software systems. Many programs have used claims of flight heritage to argue that their proposed hardware and/or software are at a technology readiness level (TRL) higher than 6 (TRL>6). It is further argued that minimal review is required, which potentially creates a false sense of security for the use of the respective hardware and/or software in their specific mission.

In the past, NASA has experienced failures rooted on the implementation of flight heritage hardware. Two examples of programs that suffered mission failures are: 1) Genesis Spacecraft, and 2) the Kennedy Space Center (KSC) Launch Pad 39A Flame Trench. In these examples to be discussed in Section 6.1, the Mishap Investigation Boards (MIBs) had common findings including the use of "heritage hardware or design" without properly evaluating the environment, application/implementation and life time, lack of appropriate review by design team and review panels, and lack of effective systems engineering. Expanded Guidance for NASA Systems Engineering<sup>5</sup> has provided guidelines for heritage review and reuse of a product.

-

<sup>&</sup>lt;sup>5</sup> "Expanded Guidance for NASA Systems Engineering", Volume 1: Systems Engineering Practices, March 2016, pages 135, 139 and 142.

As noted in Government Accounting Office Best Practices reports, "The incorporation of advanced technologies before they are mature has been a major source of cost increases, schedule delays, and performance problems on weapon systems. Demonstrating a high level of maturity before new technologies are incorporated into product development programs puts those programs in a better position to succeed".<sup>6,7</sup>

In this paper, the team decided to use **the TRL concept centered on MEAL to assess heritage** since it provides the steps required to qualify any new design and could help assess if the "heritage design" is or is not suitable for the given mission, shown in Table 2.

For any program, the mission characteristics defines MEAL. Thus, to claim "heritage", the previous mission's characteristics must bound those of the new mission in terms of environment, application, and lifetime. If these bounds are not realized, then the new system would have to regress to the appropriate TRL and be certified/verified to the predicted conditions of new mission.

For example, a part in one application may experience different utilization and stress from that in another application, or the radiation environment may be different due to a change in orbit or mission duration. In addition, to say "it flew with no observed anomalies" may be misleading since some anomalies may be hard to detect at system level unless specific monitoring was employed, or because the previous mission duration was insufficient for a latent weakness to surface. In many cases, for complex parts (e.g., field programmable gate arrays (FPGAs)), logical errors are masked and never become apparent to mission operators. Whether the error is detected depends on the state of the device/mission when the error occurs. The same error, occurring at a different time or under different conditions in the mission could have different consequences.

# 3.3.1 MEAL & TRL Concepts to Assess Flight Heritage

The following two notional scenarios illustrate the use of TRL and the MEAL concepts to assess heritage (i.e. successfully flown technologies achieved TRL >6). Each figure represents the respective MEAL boundaries.

• Scenario 1: The Blue Round Mission was successfully flown. The Orange Star Mission wants to use the same technology.

-

<sup>&</sup>lt;sup>6</sup> GAO Best Practice, "Better Management of Technology Development can Improve Weapon System Outcomes", NSIAD-99-162, July 30, 1999.

<sup>&</sup>lt;sup>7</sup> GAO Best Practices, "Technology Readiness Assessment Guide – Best Practices for Evaluating the Readiness of Technology for Use in Acquisition Programs and Projects", August 2016.

- ➤ Since the Orange Star Mission characteristics (i.e., Environment, Application and Lifetime) are bounded within the Blue Round mission, the technology would be considered at TRL 6 or higher.

- Scenario 2: The Grey Square Mission was successfully flown. The Purple Triangle Mission wants to use the same technology.

Although the Application and expected Lifetime characteristics of the Purple Triangle Mission are bounded within the Gray Square Mission, the Environment is not. Therefore, for the Purple Triangle Program, the technology would revert to the appropriate TRL.

As shown in Table 2, although heritage is often taken to apply to any previous successful flight experience, in reality the environment, application, and lifetime of the heritage mission must be equivalent or exceed the mission severity under consideration (i.e., Table 2 TRL, Heritage and MEAL Example (b)).

In the event that the application and lifetime are bounding, but the new mission is in a more severe environment, the assumed TRL is 4 because the technology has not been established at the prototype or breadboard/experimental level (i.e., Table 2 TRL, Heritage and MEAL Example (c)).

If the environment and application are bounding, but the mission life is longer for the new mission, then the assumed TRL is 4 because while the technology is validated in principle, the success of the technology for the new cumulative stresses and failure probabilities have not been (This scenario is not included in Table 2).

If the new application is more severe than that for the heritage mission, then the assumed TRL is 3 because while the mission represents proof of concept, the technology requires validation for the intended application (i.e., Table 2 TRL, Heritage and MEAL Example (d)).

If the environment, application, and mission life of the new mission exceed those of the heritage mission, then the assumed TRL is 1 (i.e., Table 2 TRL, Heritage and MEAL Example (e)).

Table 2. TRL, Heritage and MEAL Examples

|                |             |      |                                                                                      |                                                      |                                                                                                            | Mission Example                                                                                                                                                                                                                            | S                                                                                                                                                                                                                                |                                                                                                                                                    |

|----------------|-------------|------|--------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Description |      | Description                                                                          | (a)                                                  | Environment Application (b)  Lifetime                                                                      | Environment Application (c)                                                                                                                                                                                                                | Environment Application (d)  Lifetime                                                                                                                                                                                            | Environment Application Lifetime (e)                                                                                                               |

|                |             |      | Doddingston                                                                          | New<br>Technology                                    | environment, application and expected lifetime) is equal or a subset of the previously flown mission MEAL, | Proposed New Mission application and expected lifetime is equal or a subset of the previously flown mission, including identical concept, form fit, design, interfaces, etc., but with an environment outside the previously flown mission | Proposed New Mission MEAL is equal or a subset of the previously flown mission MEAL, but with different application implementation (i.e. different design outside the previously flown like mechanical, thermal &/or electrical) | Design previously flown but different application, environment and lifetime (where the original application does not envelope the new application) |

| _              |             | TRL# | Description as stated on 7120.5C                                                     |                                                      |                                                                                                            |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                  |                                                                                                                                                    |

|                | , L         | 1    | Basic principles observed and reported                                               | V&V                                                  | Previous Data Available                                                                                    | Previous Data Available                                                                                                                                                                                                                    | Previous Data Available                                                                                                                                                                                                          | Previous Data Available                                                                                                                            |

|                | Concept     | 2    | Technology concept and/or application formulated                                     | V&V                                                  | Previous Data Available                                                                                    | Previous Data Available                                                                                                                                                                                                                    | Previous Data Available                                                                                                                                                                                                          | V&V                                                                                                                                                |

| (              | 5           | 3    | Analytical and experimental critical function and/or characteristic proof-of-concept | V&V                                                  | Previous Data Available                                                                                    | Previous Data Available                                                                                                                                                                                                                    | Previous Data Available                                                                                                                                                                                                          | V&V                                                                                                                                                |

|                | 70          | 4    | Component and/or breadboard validation in laboratory environment                     | V&V                                                  | Previous Data Available                                                                                    | Previous Data Available                                                                                                                                                                                                                    | V&V                                                                                                                                                                                                                              | V&V                                                                                                                                                |

| ou             | Ground      | 5    | Component and/or breadboard validation in relevant environment                       | V&V                                                  | Previous Data Available                                                                                    | V&V                                                                                                                                                                                                                                        | V&V                                                                                                                                                                                                                              | V&V                                                                                                                                                |

| entati         |             | 6    | System/subsystem model or prototype demonstration in a relevant environment          | V&V                                                  | Previous Data Available                                                                                    | V&V                                                                                                                                                                                                                                        | V&V                                                                                                                                                                                                                              | V&V                                                                                                                                                |

| Implementation |             | 7    | System prototype demonstration in the real environment                               | V&V                                                  | V&V                                                                                                        | V&V                                                                                                                                                                                                                                        | V&V                                                                                                                                                                                                                              | V&V                                                                                                                                                |

| <u>=</u>       | Space       | 8    | Actual system completed and "flight qualified" through test and demonstration        | V&V                                                  | V&V                                                                                                        | V&V                                                                                                                                                                                                                                        | V&V                                                                                                                                                                                                                              | V&V                                                                                                                                                |

|                |             | 9    | Actual system "flight proven" through successful mission operations                  | V&V                                                  | V&V                                                                                                        | V&V                                                                                                                                                                                                                                        | V&V                                                                                                                                                                                                                              | V&V                                                                                                                                                |

|                |             |      | Comments:                                                                            | Must undergo<br>through the<br>entire TRL<br>process | Must verify system/subsystem under relevant environment (acceptance verification test)                     | Must validate component &/or<br>Breadboard under relevant<br>environment.                                                                                                                                                                  | Must validate component &/or<br>Breadboard under laboratory<br>environment.                                                                                                                                                      | Must be treated as the new technology                                                                                                              |

Notes:

| _ | . 101001                |                                                                                                                          |

|---|-------------------------|--------------------------------------------------------------------------------------------------------------------------|

|   | V&V                     | Must be validated and verified as per TRL Definitions and descriptions.                                                  |

|   | Previous Data Available | Validation data available from previously flown/validated system. Requires Verification at all levels of implementation. |

NESC Document #: NESC-RP-16-01117

# 4.0 Verification Test and Inspection Matrix at Part-, Board- and Box-Level

The purpose of verification is to show by analysis, demonstration, inspection, and/or test<sup>8</sup> the satisfactory performance of hardware in the expected MEAL and that minimum workmanship standards have been met in accordance with the program risk posture.

# 4.1 Verification Test/Inspection Purposes, Capabilities, Advantages, and Limitations

The matrix in Appendix A lists common verification tests and inspections, along with the purpose of the procedures, capabilities, advantages, and limitations if performed at part-, board-, and box-level.

- 1. "Purpose" is the reason(s) for which the given test or inspection is performed.

- 2. "Capabilities" describe the ability of the test or inspection to address the elements listed under the purpose if performed at part-, board- and box-level, respectively.

- 3. "Advantages" highlight additional tangible and/or intangible benefits of the given test or inspection.

- 4. "Limitations" describe the shortcomings of the test or inspection to realize the elements of the purpose and any incurred risks associated with the execution of the test or inspection at a given level of testing.

# 4.2 Verification Test/Inspection at Part-, Board-, Box/Subsystem- and System-Level

Verification processes should show that the end product conforms to its specified requirements at all levels (i.e., part-, board-, box-level, subsystem-level, and system-level).

The main threat the verification process seeks to avoid is a cluster of failures escaping prelaunch testing that disables a critical function before achieving mission objectives<sup>9</sup>. Non-random part failures correlated to a cause introduced by infant mortality and/or unexpected environmental impacts through workmanship or handling can introduce common cause failures and defeat redundancy. Redundancy is only effective when failure modes of the redundant components are not subject to failures due to a shared cause, known as common-cause failures (CCF). When redundant systems are alike, they will share the same flaws in design, manufacturing, and quality processes, inviting CCFs. Verification at various levels addresses the threats that can introduce CCFs and therefore removes some threats to mission success. The following sections provide an overview of verification testing at the various levels.

# 4.2.1 Part-level Verification

#### 4.2.1.1 Introduction

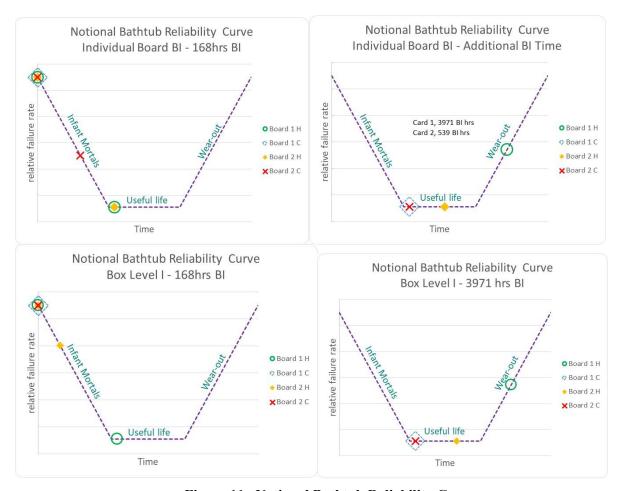

Even with modern mass production manufacturing processes, Weibull distribution and a bathtub curve apply when identifying part failure rates. The bathtub curve plots the number of device

NESC Document #: NESC-RP-16-01117

<sup>&</sup>lt;sup>8</sup> "Expanded Guidance for NASA Systems Engineering", Volume 1: Systems Engineering Practices, March 2016, page 207.

<sup>&</sup>lt;sup>9</sup> NESC-RP-12-00762, "Use of Commercial Electrical, Electronic and Electromechanical (EEE) Parts in NASA's Commercial Crew Program (CCP)", March 2012.

failures in a production lot occurring over a period of time. Initially, there will be a relatively high failure rate (i.e., infant mortality) due to manufacturing defects and non-compliant parts. After a period of time, the failure rate drops to a low level and remains consistent for a long time (i.e., usable life regime). Eventually, at the other end of the bathtub curve, the failure rate begins to increase as materials degrade (i.e., end-of-life wear-out regime).

# 4.2.1.2 Parts Testing: Why and How

Part-level testing is applied in two modes, screening and qualification, which ensure the flight parts from the testing are in the usable life regime.

Screening tests are designed to apply an above normal amount of operating stresses on the parts, to accelerate the period where infant mortality occurs, and eliminate early failures from the lot. It is expected there may be some failures during screening tests, but the surviving parts may be considered to be past the infant mortality stage and into the usable life to achieve the lowest failure rates during mission lifetime.

Parts-level qualification testing is applied to a sample of parts from a production lot that has passed screening. The goal of qualification is to simulate long-term operation through the usable life stage and ensure the parts will not reach the wear-out stage before the end of mission. Many of the tests applied during qualification are similar to screening tests, but are applied at higher acceleration factors or for longer durations. Although it is expected that samples from a "good" lot of parts will pass and be functional after qualification tests, the highly accelerated nature of the test consumes a significant portion of those samples usable life, and are generally considered unsuitable for flight. Inspection type tests such as destructive physical analysis (DPA) can be used to compare pre- and post-qualification samples to identify degradation mechanisms in parts.

The program/project should procure sufficient quantity of parts to meet its needs including spares even after attrition due to screening and provision of qualification samples.

# 4.2.1.3 Screening for Part Infant Mortality and Other Defects

It is important to note that both screening and qualification tests are much more useful when the applied stresses can be increased to achieve an acceleration factor. Under these accelerated conditions, infant mortality failures may occur within 160 hours for example, whereas under normal operating conditions such as at the board- or box-level they may not occur until several months of operation or testing. Part failures that occur during board- or box- testing can have much more drastic impacts than they would if removed during part-level screening. Despite advances in manufacturing automation and mass production, defects still occur and the need to eliminate infant mortality remains.

# 4.2.1.4 Major Advantages and Limitations of Part-level Verification

Part-level testing is the lowest level of integration where part specifications and workmanship can be verified. Testing at the part level is the most effective method to identify part defects from manufacturing and, through screening test such as burn-in, to eliminate infant mortality failures and nonconforming parts from a lot. Part-level testing can be optimized to reveal particular failure mode(s) and has the distinct advantage of allowing the highest acceleration factors possible by tailoring the individual test conditions and stresses (e.g., electrical and environmental) to the limitations of each part. Accelerated test conditions allow for rapid testing and the high stress conditions necessary to force infant mortality failures during early

operation. Reduced stress diminishes the test's ability to fully drive the infant mortals out of the population.

Additionally, testing at the part-level offers the highest level of perceptibility to measure full electrical parameters to detect parametric shifts, which can indicate part degradation. At higher levels of integration, many individual electrical parameters become masked by the overall system operation, and subtle shifts that are important may not be detected until they become so severe the system fails. Part-level testing also increases understanding of the individual part and provides insight into the possible failure mechanisms. For example, there is better understanding of the part's construction quality and susceptibility to environmental conditions when performing part-level testing. Part-level testing increases understanding of the individual part and provides insight into the possible failure mechanisms. For example, there is better understanding of the parts construction quality and susceptibility to environmental conditions when performing part-level testing. Part-level testing also helps the designer understand the circuit design margins and allows "cherry pick" part to maximize performance and reliability.

However, limitations exist. Part-level testing may not verify interactions between parts on a board or in a system/subsystem, and involves more handling of parts, increasing the likelihood they will be damaged.

# 4.2.2 Board-level Verification

Board-level testing is the next lowest level of integration where the functional performance and the workmanship of a circuit (consisting of multiple parts) can be verified.

Board-level testing can be useful for identifying part defects and infant mortality failures, but the capability and perceptivity is significantly reduced compared to part-level testing. To avoid overstressing some parts on the board, environmental stresses need to be limited to the weakest or least capable part or material on the board, and knowing or finding the least capable part *a priori* may be difficult. Additionally, electrical stresses placed on the individual parts within the board usually cannot be adjusted, and remain at nominal operation levels. This means the overall applied stress and life acceleration factor achieved is significantly less than would be possible at each individual part level. The reduced acceleration factor requires a much longer duration test than would be required at the part level.

As mentioned above, once integrated to the board-level, there is limited perceptivity to detect individual part electrical parameters and shifts, which could be indicators of degradation that could lead to a latent failure. Interactions between parts on the board can be verified, but one may not be able to identify a degraded or damaged part. Even if a part degrades to the point where its parametric values are outside of specifications, this could go undetected if the circuit continues to operate. Continued degradation over time could introduce a latent circuit failure late in the verification process.

Another significant disadvantage of moving testing to higher levels of integration is that a failure has increased consequences at this level. At the board-level, the root cause of the failure must be determined, the failed parts must be removed from the board, replaced, and additional testing added to verify the new part performs as required at the board level, all of which augment risks to the rest of the board and may introduce schedule delays. In addition, it is often difficult to determine whether a board/function failure is related to a part failure versus a design issue versus a board manufacturing issue.

Board-level testing does offer selected advantages. Overall testing costs are typically reduced as compared to part level because multiple parts can be tested simultaneously. Additionally, some complex or high-speed parts require significant biasing and support circuitry, and frequency-tuned board characteristics to operate. These conditions are often not feasible to implement with the temporary test fixturing and biasing available for part-level tests. Board-level testing is often the only feasible option for parts such as radio frequency (RF) devices, high-speed analog devices, or complex microprocessors, and FPGAs. An additional benefit of testing at the board-level is that it tests the board assembly workmanship, mechanical and thermal design, and compatibility of materials chosen for assembly, such as solder, epoxy, staking, etc.

# 4.2.3 Box-level or Subsystem-level Verification

Box-level or subsystem-level testing is done to verify the functional performance and the workmanship of a box or subsystem consisting of multiple circuits. Boards' interactions within the box can be verified and many box-level tests can be performed using consolidated autonomous test configurations.

Compared to part- and board-level testing, box-level testing offers even lower perceptivity for detecting part defects and infant mortality, and it has the highest consequences if a failure is observed of any of the configurations considered in this paper. At the box-level, low stress levels can be applied to the parts, both environmentally and electrically, to ensure the weakest parts are not overstressed. Additionally, box-level testing requires larger and more expensive environmental chambers.

Box-level testing offers the lowest ability to measure parameters for individual parts as test points and board traces become inaccessible for probing. Parts failures discovered at box-level integration result in significant de-integration rework and retesting and this in turn results in significant risks and schedule delays. Failures at box-level are also more difficult to diagnose. Was the failure caused by the part, the design, or workmanship? Identifying root cause becomes more problematic. Finally, circuit design margins cannot be determined due to the lack of access to test points to obtain part- and circuit-level timing and voltage measurements.

# 4.2.4 System-level Verification

The purpose of a full-system verification is to test and verify the entire payload under conditions that simulate the flight operations and environment as realistically as practical. Appendix A focuses only at part-, board-, and box-level testing.

#### 4.2.5 Radiation Effects Verification

Threats that the space radiation environment poses to semiconductor devices in space missions can be divided into two broad categories:

- 1. Dose effects (i.e., TID and displacement damage dose (DDD)) result from cumulative exposure to the space radiation environment. As such, they behave like wear-out effects with failure rate increasing as the dose increases.

- 2. In contrast, single-event effects (SEE) are the parts' prompt responses to the passage of a single ionizing particle through a volume in the part sensitive to that SEE mode.

The following subsections describe common types of radiation testing applied to parts.

## **4.2.5.1 TID, DDD, and SEE**

Radiation tests for TID, DDD, and SEE are all at least potentially destructive. Therefore, such testing is done during qualification testing on a sample of parts representative of the flight parts. For TID and DDD, this usually means the test parts must belong to the same wafer diffusion lot as the flight parts. For SEE, lot-to-lot differences in performance are not usually as significant as those for TID or DDD. As long as the test parts are fabricated in the same process and with the same mask set as the flight parts, the test is likely to be valid. Note that in some cases, lot-to-lot and even part-to-part variation is significant for SEE and these situations require a greater level of fidelity between test and flight parts.

Radiation testing for SEE has different goals than that for TID or DDD. TID and DDD are cumulative effects, and failures are usually preceded by gradual parametric and functional degradation. Thus, the goals of TID and DDD testing are to determine which parameters/functions degrade and the part-to-part variation in that degradation at each dose step. If parts are tested to failure (either parametric or functional), then the part-to-part variation in the failure dose is also of interest. Mitigation of TID and DDD involves adding shielding or taking other steps (e.g., selecting operating conditions) to ensure that the dose on the part remains low enough where the probability of failure or degradation affecting the part's ability meet requirements is negligible.

In contrast, SEE can occur at any time in the device with equal probability (per ion). As such, the primary goal of SEE testing is to identify all the SEE modes to which the part may be susceptible. Thus, independent of whether the radiation environment is severe or benign, the test will irradiate the part to ion fluences much higher than will be seen during the mission. SEE test methods are specifically tailored to include conditions where a given SEE mode is likely to occur if the device under test is susceptible. For example, if the device under test includes CMOS (which can be susceptible to single event latch-up — SEL), some test runs will be performed with high fluences (i.e., greater than 10<sup>7</sup> ions per cm<sup>2</sup>) of highly ionizing (i.e., high-linear energy transfer (LET)) ions. These runs would be performed with the worst-case conditions for causing SEL in the DUT. Once this susceptibility is detected, then it is measured for a variety of ion species, energies, LETs, and angles of incidence. These data are used to estimate the probability of each SEE mode occurring in the mission radiation environment.

#### 4.2.5.2 Radiation Testing at Different Configuration Levels

Whether parts are tested at the part-, board-, or box-level affects the extent to which the goals outlined in the previous section can be met by testing. First, board- and box-level studies are often performed with a single sample of the board or box. This makes it impossible to assess how part-to-part variation would affect flight board/box performance unless there is high confidence part-to-part variation is negligible for all parts on the board. Even if multiple test units are irradiated, the interactions between parts with different variability on the boards makes it difficult to interpret the results and bound flight unit performance.

Radiation at higher-level assemblies also precludes optimizing the test to detect particular susceptibilities in any given technology. Moreover, parts on a board may only be susceptible to some failures for a fraction of the boards' operating conditions. For example, if any part on a test board is bipolar, it is potentially susceptible to enhanced low dose rate sensitivity, in which parts degrade more severely at low dose rates (e.g., in space) than at high dose rates (e.g., in an accelerated TID test). This means that the entire test must be conducted at a low dose rate.

Similarly, increasing board temperature and voltage may not be possible, and SEL testing would likely have to be done for realistic missions rather than bounding conditions. Test conditions and levels will be driven by the weakest parts in the test unit rather than by the level of hardness designers desire for the system.

Nondestructive SEE modes and parametric degradation may also remain hidden in tests at the board- and box-level. While it can be argued that such modes are not significant at the system level, they could have consequences if the hardware is in another logical or operating state when they occur. In general, the more complicated the test unit (be it a part or a system), the less likely it is that the tester will be able to cover the full state space of operations in an accelerated test.

Not every radiation tests can be performed at all integration levels. TID tests with gamma rays could be performed even for complex boxes as long as the beam is large enough to expose the entire test unit. X-rays have less penetrating power than gamma rays, but are similarly suitable for part-, board- and box-level testing as long as the penetrating range of the radiation is much longer than the system size. A concern for multi-board systems is that a gamma ray or X-ray beam can be degraded as it passes through the forward boards, resulting in higher doses for the rear boards than the forward boards. Proton TID, DDD, and SEE tests can also be performed on integrated systems although the range of the protons must be considered (the range of a 200-MeV is about 13.7 cm in Si).

Heavy-ion SEE testing at levels of integration higher than the part-level is problematic. Preparing parts on the board to ensure ions from conventional accelerators reach device sensitive volumes can compromise their structural integrity, making them unreliable and vulnerable to mechanical failures. In principle, a sufficiently broad, high-energy heavy-ion beam (e.g., like that at the NASA Space Radiation Laboratory (NSRL)) could effectively test parts at the board-level without modification, albeit with significant amounts of analysis required to account for beam degradation as it traverses various parts. However, heavy-ion SEE testing at the multi-board or box-level is generally not feasible due to limited penetration ranges of the ions and the difficulty of modeling transport of the ions through complicated structures in the test unit.