# High Level Synthesis for Packet Processing Pipelines

Cristian Soviani

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

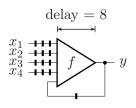

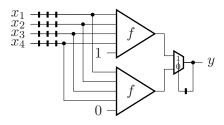

## ABSTRACT

# High Level Synthesis for Packet Processing Pipelines

#### Cristian Soviani

Packet processing is an essential function of state-of-the-art network routers and switches. Implementing packet processors in pipelined architectures is a well-known, established technique, albeit different approaches have been proposed.

The design of packet processing pipelines is a delicate trade-off between the desire for abstract specifications, short development time, and design maintainability on one hand and very aggressive performance requirements on the other.

This thesis proposes a coherent design flow for packet processing pipelines. Like the design process itself, I start by introducing a novel domain-specific language that provides a high-level specification of the pipeline. Next, I address synthesizing this model and calculating its worst-case throughput. Finally, I address some specific circuit optimization issues.

I claim, based on experimental results, that my proposed technique can dramatically improve the design process of these pipelines, while the resulting performance matches the expectations of hand-crafted design.

The considered pipelines exhibit a pseudo-linear topology, which can be too restrictive in the general case. However, especially due to its high performance, such an architecture may be suitable for applications outside packet processing, in which case some of my proposed techniques could be easily adapted.

Since I ran my experiments on FPGAs, this work has an inherent bias towards that technology; however, most results are technology-independent.

# Contents

| 1 | Introduction |                                                          |    |  |

|---|--------------|----------------------------------------------------------|----|--|

|   | 1.1          | Packet processing inside a Switch                        | 1  |  |

|   |              | 1.1.1 FPGA particularities                               | 4  |  |

|   | 1.2          | Packet processing pipelines                              | 6  |  |

|   | 1.3          | Packet editing modules                                   | 7  |  |

|   | 1.4          | Main challenges                                          | 8  |  |

|   | 1.5          | Challenge: Avoiding RTL                                  | 9  |  |

|   |              | 1.5.1 Contribution: high level packet editor description | 10 |  |

|   |              | 1.5.2 Contribution: packet editor synthesis              | 11 |  |

|   | 1.6          | Challenge: Pipeline worst case performance               | 12 |  |

|   |              | 1.6.1 Contribution: pipeline performance analysis        | 14 |  |

|   |              | 1.6.2 Computing minimum FIFO sizes                       | 15 |  |

|   | 1.7          | Challenge: Sequential RTL issues                         | 15 |  |

|   |              | 1.7.1 Contribution: combining Retiming and Shannon       | 17 |  |

|   | 1.8          | Contribution summary. Thesis outline                     | 18 |  |

| 2 | Syn          | nesis of Packet Processing Pipelines 1                   | L9 |  |

|   | 2.1          | Overview                                                 | 19 |  |

|   | 2.2          | Packet Processors and Editing                            | 21 |  |

| 2.3 | Relate         | d work                             | 23 |  |  |  |

|-----|----------------|------------------------------------|----|--|--|--|

| 2.4 | The P          | The Packet Editing Graph           |    |  |  |  |

|     | 2.4.1          | What to expect from the PEG        | 23 |  |  |  |

|     | 2.4.2          | A PEG Example                      | 24 |  |  |  |

|     | 2.4.3          | PEG description                    | 26 |  |  |  |

|     |                | 2.4.3.1 The input subgraph         | 28 |  |  |  |

|     |                | 2.4.3.2 The computation subgraph   | 29 |  |  |  |

|     |                | 2.4.3.3 The output subgraph        | 30 |  |  |  |

| 2.5 | The S          | ynthesis Procedure                 | 32 |  |  |  |

|     | 2.5.1          | The module I/O protocol            | 34 |  |  |  |

|     | 2.5.2          | Core and Wrapper                   | 36 |  |  |  |

|     | 2.5.3          | Splitting Data into Words          | 37 |  |  |  |

|     | 2.5.4          | Assigning Read Cycle Indices       | 40 |  |  |  |

|     | 2.5.5          | Scheduling                         | 42 |  |  |  |

|     | 2.5.6          | Synthesizing the controller        | 43 |  |  |  |

|     | 2.5.7          | Handling the end of a packet       | 45 |  |  |  |

|     | 2.5.8          | Synthesizing the data path         | 47 |  |  |  |

|     | 2.5.9          | Comments on scheduling and binding | 48 |  |  |  |

|     | 2.5.10         | Comments on FSM encoding           | 50 |  |  |  |

| 2.6 | Implementation |                                    |    |  |  |  |

|     | 2.6.1          | Textual frontend                   | 51 |  |  |  |

|     | 2.6.2          | Synthesis steps                    | 51 |  |  |  |

|     | 2.6.3          | Simulation                         | 52 |  |  |  |

|     | 2.6.4          | RTL and Low-Level Synthesis        | 53 |  |  |  |

| 2.7 | Experi         | imental Results                    | 54 |  |  |  |

| 2.8 | Conclu         | isions                             | 55 |  |  |  |

| 3 | Pac | ket Pr | rocessing Pipeline Analysis            | 56 |

|---|-----|--------|----------------------------------------|----|

|   | 3.1 | Overv  | riew                                   | 56 |

|   |     | 3.1.1  | Motivational example                   | 58 |

|   | 3.2 | Relate | ed Work                                | 59 |

|   | 3.3 | Single | e module analysis                      | 61 |

|   |     | 3.3.1  | Defining module performance            | 62 |

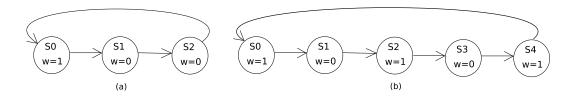

|   |     | 3.3.2  | Computing $R,W$ , and $T$ from the STG | 63 |

|   |     | 3.3.3  | Using Bellman-Ford                     | 66 |

|   |     | 3.3.4  | Abstracting the data path              | 68 |

|   | 3.4 | Conne  | ecting modules                         | 69 |

|   |     | 3.4.1  | The module I/O protocol                | 70 |

|   |     | 3.4.2  | The FIFO implementation                | 72 |

|   | 3.5 | The E  | Big FIFO scenario                      | 73 |

|   |     | 3.5.1  | Computing the worst-case throughput    | 74 |

|   |     | 3.5.2  | Performance issues                     | 75 |

|   |     | 3.5.3  | Module independence                    | 76 |

|   | 3.6 | Verify | ing throughput using model checking    | 76 |

|   |     | 3.6.1  | Comparison with explicit analysis      | 78 |

|   |     | 3.6.2  | Comparison with simulation             | 79 |

|   | 3.7 | Comp   | outing the minimum FIFO sizes          | 79 |

|   |     | 3.7.1  | Computing FIFO Sizes                   | 80 |

|   |     | 3.7.2  | FIFO size monotonicity                 | 80 |

|   |     | 3.7.3  | An exact depth-first search algorithm  | 81 |

|   |     | 3.7.4  | A heuristic search algorithm           | 83 |

|   | 3.8 | Exper  | rimental Results                       | 84 |

|   | 3.9 | Concl  | usions                                 | 86 |

| 4 | Cor | nbining | g Shannon and Retiming                                | 87  |

|---|-----|---------|-------------------------------------------------------|-----|

|   | 4.1 | Introd  | uction                                                | 87  |

|   |     | 4.1.1   | Brief description                                     | 88  |

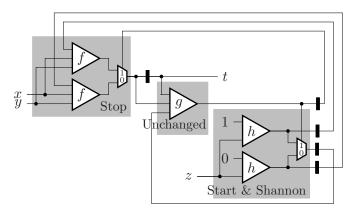

|   |     | 4.1.2   | An example                                            | 89  |

|   |     | 4.1.3   | Overview of the algorithm                             | 91  |

|   |     | 4.1.4   | Related work                                          | 92  |

|   | 4.2 | The F   | irst Phase: Computing Arrival Times                   | 93  |

|   |     | 4.2.1   | Basics                                                | 93  |

|   |     | 4.2.2   | Shannon decomposition                                 | 95  |

|   |     | 4.2.3   | Shannon decomposition as a kind of technology mapping | 97  |

|   |     | 4.2.4   | Redundant encodings and arrival times                 | 98  |

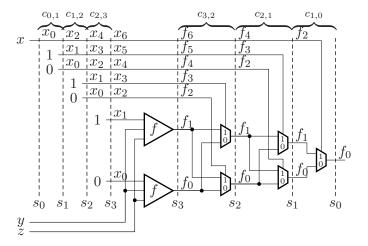

|   |     | 4.2.5   | My family of Shannon encodings                        | 99  |

|   |     | 4.2.6   | Sets of feasible arrival times                        | 102 |

|   |     | 4.2.7   | Pruning feasible arrival times                        | 105 |

|   |     | 4.2.8   | Retiming                                              | 107 |

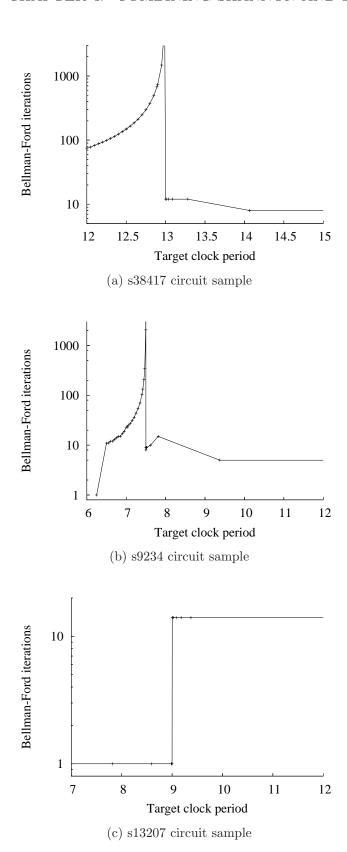

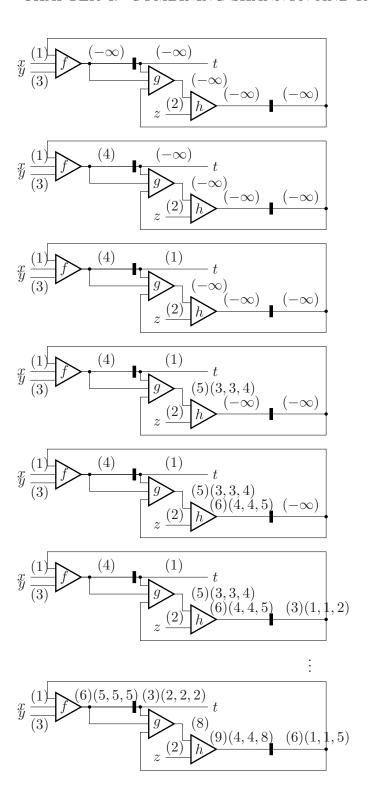

|   |     | 4.2.9   | Using Bellman-Ford to compute arrival times           | 107 |

|   |     | 4.2.10  | Termination of Bellman-Ford and max-iterations        | 111 |

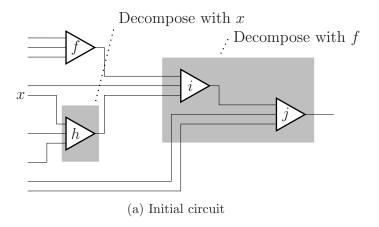

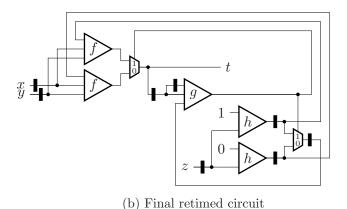

|   | 4.3 | The Se  | econd Phase: Resynthesizing the Circuit               | 112 |

|   |     | 4.3.1   | Cell families                                         | 116 |

|   |     | 4.3.2   | Cell selection                                        | 117 |

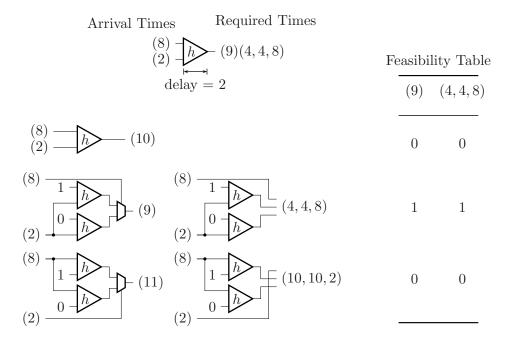

|   |     | 4.3.3   | Propagating required times                            | 118 |

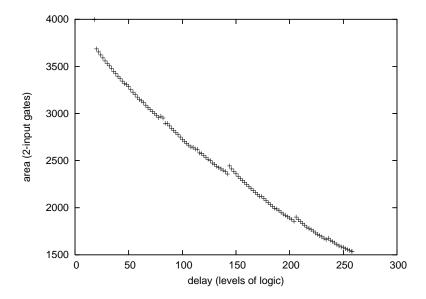

|   | 4.4 | Experi  | ments                                                 | 119 |

|   |     | 4.4.1   | Combinational circuits                                | 119 |

|   |     | 4.4.2   | Sequential benchmarks                                 | 120 |

|   |     | 4.4.3   | Packet processing pipelines                           | 123 |

|   | 15  | Conclu  | sions                                                 | 194 |

| 5 | Final Conclusions                       |                                               |     |  |  |

|---|-----------------------------------------|-----------------------------------------------|-----|--|--|

|   | 5.1                                     | Claim                                         | 126 |  |  |

|   | 5.2                                     | PEG — the human factor                        | 127 |  |  |

|   | 5.3                                     | Synthesis — taking advantage of others        | 128 |  |  |

|   | 5.4 Analysis — choosing what to measure |                                               | 130 |  |  |

|   | 5.5 Logic synthesis — beyond BLIF       |                                               | 130 |  |  |

|   | 5.6 Open issues                         |                                               |     |  |  |

|   |                                         | 5.6.1 Synthesis - Design space exploration    | 131 |  |  |

|   |                                         | 5.6.2 Analysis — Performance under-estimation | 132 |  |  |

|   |                                         | 5.6.3 Low level optimization — Experiments    | 133 |  |  |

| B | ibliog                                  | graphy 1                                      | 133 |  |  |

# List of Figures

| 1.1 | Generic switch architecture                              | 1  |

|-----|----------------------------------------------------------|----|

| 1.2 | A switch with detail of a packet processing pipeline     | 3  |

| 2.1 | Graphic PEG specification for the MPLS module            | 25 |

| 2.2 | Textual PEG specification for the MPLS module            | 27 |

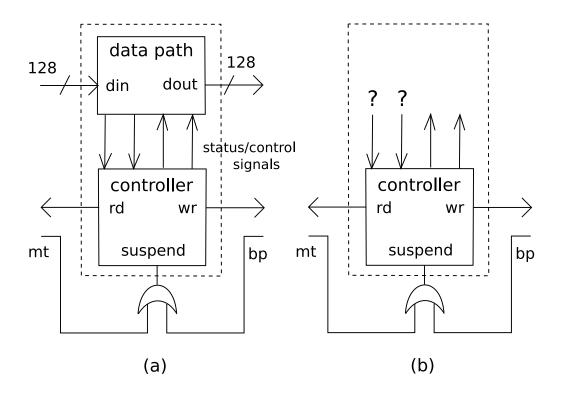

| 2.3 | A module I/O signals and its two components              | 34 |

| 2.4 | Split into 64-bit words                                  | 38 |

| 2.5 | Structuring a packet map into words                      | 39 |

| 2.6 | Read cycle indices and delay bubbles added               | 41 |

| 2.7 | ASM chart for the controller synthesized from Figure 2.6 | 44 |

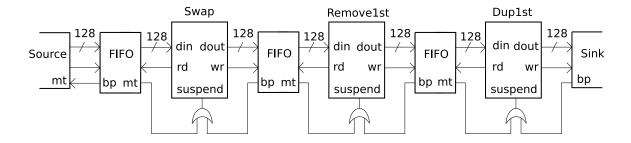

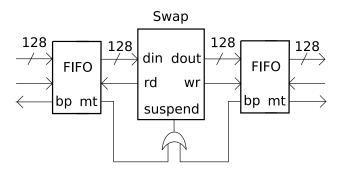

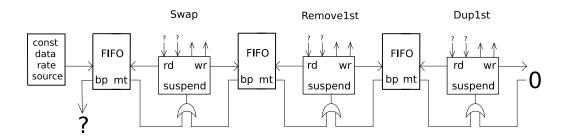

| 3.1 | A packet pipeline: how big should the FIFOs be?          | 58 |

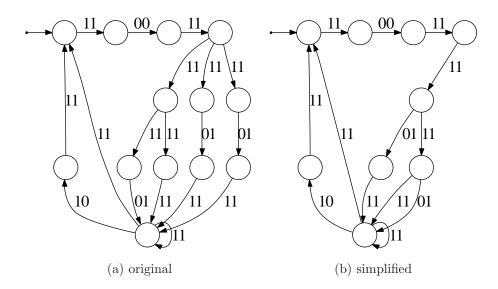

| 3.2 | STGs for the DwVLANproc module                           | 64 |

| 3.3 | Sample STG                                               | 67 |

| 3.4 | Original and simplified module FSM                       | 70 |

| 3.5 | Handshaking between module and adjacent FIFOs            | 71 |

| 3.6 | STG of a 3-place FIFO                                    | 72 |

| 3.7 | Computing $R$ assuming optimally-sized FIFOs             | 75 |

| 3.8 | slightly modified pipeline for the model checker         | 77 |

| 3.9 | Data source FSMs                                         | 77 |

| 3.10 | An exact algorithm for computing minimum FIFOs                                       | 82  |

|------|--------------------------------------------------------------------------------------|-----|

| 3.11 | Greedy Search for minimum size FIFOs                                                 | 83  |

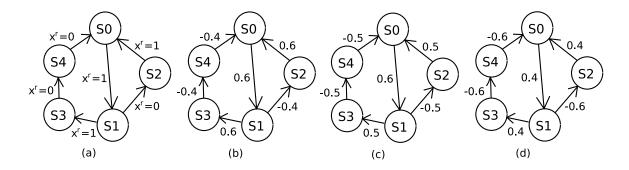

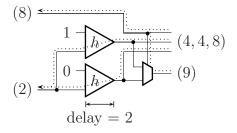

| 4.1  | An example                                                                           | 90  |

| 4.2  | My algorithm for restructuring a circuit $S$ to achieve a period $c  \ldots  \ldots$ | 91  |

| 4.3  | My Bellman-Ford algorithm for computing feasible arrival times                       | 94  |

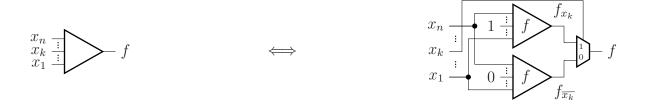

| 4.4  | Shannon decomposition of $f$ with respect to $x_k$                                   | 96  |

| 4.5  | The basic Shannon "cell library"                                                     | 96  |

| 4.6  | Shannon decomposition through node replacement                                       | 97  |

| 4.7  | The Shannon transform as redundant encoding                                          | 98  |

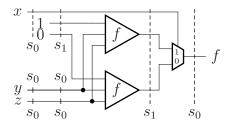

| 4.8  | Encoding $x$ , evaluating $f(x, y, z)$ , and decoding the output for the $s_0$ ,     |     |

|      | $s_1, s_2, \text{ and } s_3 \text{ codes.} \dots$                                    | 100 |

| 4.9  | Computing feasible arrival times for a node $f$                                      | 102 |

| 4.10 | Pruning the feasible arrival times from Figure 4.9                                   | 106 |

| 4.11 | Iterations near the lowest $c$                                                       | 110 |

| 4.12 | Computing feasible arrival times for a circuit                                       | 113 |

| 4.13 | Restructuring a circuit                                                              | 114 |

| 4.14 | Selecting cells for node $h$ in Figure 4.12                                          | 115 |

| 4.15 | Propagating required times from outputs to inputs                                    | 118 |

| 4.16 | The performance/area tradeoff obtained by my algorithm on a 128-bit                  |     |

|      | ripple carry adder                                                                   | 120 |

# List of Tables

| 2.1 | Synthesis results for selected modules       | 54       |

|-----|----------------------------------------------|----------|

| 3.1 | Module statistics                            | 84       |

| 3.2 | Experimental results                         | 8!       |

| 4.1 | Experiments on ISCAS89 sequential benchmarks | 121      |

| 4.2 | Experiments on packet processing pipelines   | $12^{2}$ |

# Acknowledgements

I thank my advisor prof. Stephen A. Edwards for his constant guidance and help during my entire graduate school. Not only was his liberal advice essential for my academic progress but he actively contributed to the research that led to this thesis. Doubtlessly, most of the material presented below as original work was published before at several academic venues; with no exception Stephen has co-authored these publications. But scarcely was Stephen's help strictly academic: he is my friend.

I thank Dr. Ilija Hadzic, my mentor during my two Bell Labs internships. The research started together during the summer of 2005 represents the keystone of this thesis. Without his suggestions and comments, based on a vast engineering experience, my research could have easily strayed away from this physical world.

I thank Dr. Olivier Tardieu for his active contribution to my research. His touch can be easily recognized in the last technical chapter, where a very rigorous mathematical formulation was required.

I thank prof. Luca Carloni for his insightful suggestions and comments on some of the most delicate and convoluted topics of my research.

I thank prof. Jonathan Gross for teaching the most interesting two courses I have ever taken. His teaching is divinely inspired.

I thank the members of my defense committee for their interest in my modest work and for the unforgettable moments they have offered me during my defense.

I thank all faculty of our department for their inestimable advice and help.

Last but not least I wish to thank my family for the irreplaceable and unconditional support during the last thirty-three years of my life.

To Lizi and Valona

Chapter 1

# Chapter 1

# Introduction

### 1.1 Packet processing inside a Switch

A packet switch (or router) is a basic building block of data communication networks. Its primary role is to forward packets based on their content, specifically header data at the beginning of the packets. As part of this forwarding operation, packets are classified, queued, modified, transmitted, or dropped.

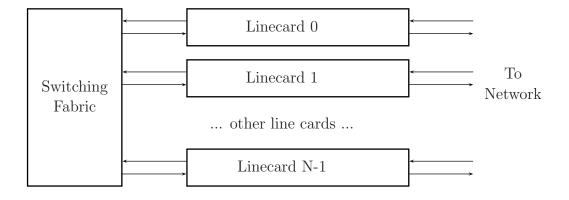

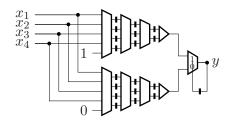

Figure 1.1 shows the simplified architecture of a generic packet switch. Its central

Figure 1.1: Generic switch architecture

component is a switching fabric, which performs the actual switching operation among its N ports. In addition, the switch contains N linecards, one for each fabric port. As can be seen, they are the interface between the switching fabric and the physical network. These linecards are responsible for a large class of operations, such as packet classification, next destination computation, metering, and traffic management.

Packet processing is a very important task for a linecard. According to the network protocol(s) supported by the switch, some header fields of the packets have to be updated, such as decrementing the TTL (Time to Live) count in the IP header (Internet protocol), inserted or removed, such as the MPLS (Multiprotocol Label Switching) labels used by the Martini encapsulation protocol. In addition, some packets have to be dropped (e.g., an IP with a zero TTL value) or forwarded internally to a dedicated component inside the switch, e.g., discovery PPPOE (Point-to-Point over Ethernet) packets. These operations are very common, but this list is far from being exhaustive: the important issue to be noticed is that each network protocol requires its own set of such packet transformations.

The actual operations that can be performed by the packet processor define the overall switch functionality. The other switch components, such as the switching fabric, perform generic tasks. It is mainly the packet processor that makes the difference between a simple Ethernet switch and a more sophisticated one that also supports VLAN (Virtual Local Area Network) and PPPOE traffic.

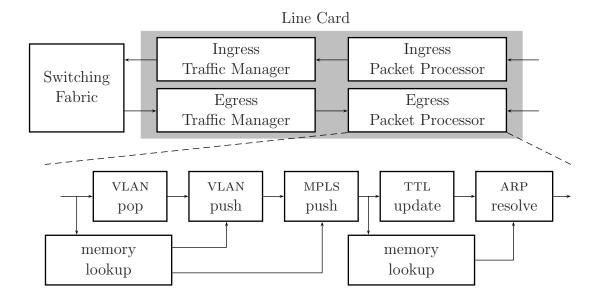

Figure 1.2 shows a more detailed view of a typical linecard. It consists of an ingress path and an egress one, which handle the incoming and the outgoing traffic. Each path contains a packet processor, which performs the abovementioned operations.

As mentioned earlier, the packet processors encapsulate the switch's knowledge of network protocols. Consequently, the complexity of these processors is high, and tends to increase with the deployment of new protocols and multi-protocol network devices. Moreover, these components are the first to require changes due to protocol updates, additional functionality required, or simply because of bugs discovered in the

Figure 1.2: A switch with detail of a packet processing pipeline.

current implementation. It is critical that these changes be done in the field to avoid the physical replacement of the existing product with a new one, and preferably without interrupting the network operation for a long time. The above issues are known as maintainability.

Traditionally, packet processing was done in software, either by general purpose CPUs, or, for increased performance, by specialized NPUs (Network Processor Units). As expected, this approach successfully addresses the maintainability issue. Although the solution is still feasible for low-end network devices, high-end switches, such as those found on network backbones or in data centers, operate today as speeds hard to imagine two decades ago.

In the spring of 2007, it was not uncommon to find linecards working at 40 Gbps. Since the minimum Ethernet packet size is 64 bytes, these cards must work at the incredible rate of 80,000,000 packets per second: each packet has a header that must be handled by the packet processor.

Implementing the packet processors in hardware becomes a very attractive choice, if not the only reasonable one, for any modern high-end networking device.

The imminent drawback is that for classical technologies such as ASIC, the maintainability advantages offered by software are lost. Some vendors (Cisco, Juniper, etc.) build hard-wired ASICs with generic sequences for state machines to achieve field upgrade and maintenance capability, but this is limited.

Fortunately, with the recent growing popularity of FPGA (Field Programmable Gate Array) devices, a compromise solution has been found. Although slower than ASICs, they are much faster than software, and allow the same maintainability as software. ASICs indeed requires less physical resources (in terms of transistors), but due to commercial issues (mainly the quantities in which they are manufactured) FPGAs are often more economical.

#### 1.1.1 FPGA particularities

Although an overview of FPGA technology is outside the scope of this thesis, I will emphasize some of its particularities as they trigger important decisions in the rest of this work.

Due to its programmability, an FPGA uses far more silicon resources than an equivalent ASIC design. For example, a 4-input AND gate is usually mapped in a Xilinx Virtex 4 device to a 4-input LUT (Look-Up Table), which consists mainly of 16 SRAM (Static RAM) cells (used for configuration) and a 16-to-1 multiplexer.

Another particularity, impossible to ignore, is that the "wires" connecting the various logic elements are in fact complex circuits that include buffers and multiplexers.

Consequently, FPGAs are less efficient than ASICs in both area and delay. The difference is not minor: an FPGA is roughly ten times larger and ten times slower than the equivalent ASIC.

It follows that FPGA designs will work at lower clock frequencies (hundreds of MHz), and most operations have to be pipelined and performed on wider data words to be able to perform the same tasks. All FPGAs provide a disproportionately large number of registers relative to the number of combinational logic primitives. For example, all

FPGAs from the Xilinx Spartan and Virtex families provide a register for each four-input LUT. Consequently, adding several pipeline stages to a combinational path is inexpensive.

Applying pipelining and using wide data words leads to very complex sequential networks. Again, an example: if we are given four modules instead of one simple FEC (forward error correction) module, each with four pipeline stages, it is anything but trivial to speed up an existing application by a factor of 16. Assuming that it is possible, one may expect a complex sequential network around the modules, e.g., performing load balancing. To conclude, FPGAs usually require more complex designs than ASICs for solving the same problem.

However, the real advantage of FPGAs is their programmability. Much like software, an FPGA may be updated in a matter of seconds, even when the device is deployed in the field. Thus, not only is the development and testing process dramatically sped up (e.g., the physical boards may be manufactured before the design is complete), but the systems may be maintained dynamically with minimal overhead. This proves to be a crucial advantage for applications such as network devices, when new features and fixes have to be added on a regular basis.

In fact, the bottleneck in the update process is the design time itself. If adding a new feature to the design takes several weeks, the main advantage of this technology could not be exploited to its maximum potential.

There are two different, contradictory issues: FPGA designs require complex designs and design time is critical.

The whole point of my thesis is to balance these issues and the requirement of high performance in modern networking devices.

# 1.2 Packet processing pipelines

The algorithms executed by an ingress or egress packet processor in most switches are very suitable to a pipelined hardware implementation. Figure 1.2 shows an example: a (simplified) pipelined realization of an egress packet processor in a commercial switch.

The core of the packet processor consists of a linear pipeline. The logical flow may have forks and joins but they can be emulated with a linear physical topology. This packet processing pipeline is traversed by all the packets to be processed. Note that there are no forks and no joins. The main property of this linear architecture is that the order in which packets enter and exit the pipeline is exactly the same. For example, if a packet is to be dropped, it is simply marked as such: the actual dropping will be done at the exit of the pipeline. We will argue for the advantages of this simplified architecture in the next chapter.

As a general rule, the overall complex functionality of the pipeline is divided between several modules, each of them performing tasks of small or moderate complexity. These modules are known as packet header editors because they only modify packet headers, not their payloads. In the sequel, I will often refer to them using shorter names such as packet editors, editing modules, or simply modules.

The packet processing pipeline also contains several auxiliary elements, such as the two lookup modules in Figure 1.2. The main traffic does not not traverse them; instead they function as clients of the main pipeline. Such an element takes requests from a pipeline module, performs a specific operation, and returns the results to another downstream module.

Memory lookup elements are probably the most common type. For example, the one in the right of Figure 1.2 performs an ARP (Address Resolution Protocol) lookup: it takes the packet IP destination from the MPLSPUSH module and returns the Ethernet address of the destination interface to ARP resolve. The latter uses this result to update the relevant field of the packet header.

The communication between the pipeline elements, packet editors and auxiliary elements is realized by FIFOs. For simplicity, I represent them as arrows in Figure 1.2.

Since the packet editors can insert or remove header fields, the data flow rate through the pipeline is not constant. Such non-constant rates also arise because some modules or auxiliary elements take extra time to perform some computation.

Thus, a communication link between two components may be active and carry valid information in only certain clock cycles and not on others. Therefore, these FIFOs perform the essential task of compensating for the non-continuous operation of the various components.

### 1.3 Packet editing modules

As seen above, the packet editing modules are critical components of a packet processing pipeline. They are neither more nor less important than the other components (lookup tables, etc.) but they form the backbone of the pipeline.

While the other elements are either simple connecting elements, e.g., FIFOs or perform important but standard operations, e.g., memory look-up modules, the packet editors are the "active" elements that encapsulate the functionality of the pipeline, i.e., its ability to process various types of packets according to different network protocols.

From a high-level view, these modules perform simple transformations on each packet header. They perform simple arithmetic or logical operations, such as decrementing the IP TTL field, inserting or removing data, such as the MPLS labels, setting or reseting some flags, or any combination of those. I will describe the possible operations in Chapter 2. The overall functionality is split among various packet editors in the pipeline, both to keep each module simple and to enable the interaction with auxiliary elements.

To keep these critical modules simple, they are not allowed to perform arbitrary

operations such as dropping packets or creating new ones. Even if these operations are required, they are usually done outside the packet processing pipeline for performance reasons. As a result, the behavior of such module looks simple: read packet, make some simple modifications, write packet, repeat.

However, these modules are not trivial when expressed at the register transfer level in a language such as Verilog or VHDL and do not look similar to each other. Even a simple operation such as adding two fields may have radically different implementations depending on where the fields are in the header, the speed of the add operation, etc.

The RTL design of such a module is not a trivial task; it takes a lot of time even for an experienced engineer, and is prone to errors; their high-level simple and uniform functionality disappears in the RTL domain, where even trivial modules require complex implementations.

# 1.4 Main challenges

Below, I summarize the main challenges in designing a high-performance packet processing pipeline. After this short summary, I will expand each topic, adding a brief description of my contribution in surmounting the respective issues. The next sections are the outline of my thesis.

First, I argue that the design flow for packet editing modules has to start from a high-level specification instead of RTL because the difficulty of RTL design and the big advantages of speeding up the design process. I introduce such a specification model: the PEG (Packet Editing Graph). I show how to translate a PEG specification into an RTL model such as VHDL.

Next, I argue for the importance of analyzing the worst case performance of a packet processing pipeline. I propose a fast method for this analysis. I also argue for the importance of computing the minimum sizes of the interconnecting FIFOs to

guarantee the desired pipeline performance. I also present a model-checking-based algorithm to answer this issue.

Finally, I argue the real performance bottlenecks are the critical loops, which usually spread across the design in a complex sequential system such as one resulting from my synthesis procedure. To address this issue, I propose an algorithm based on a combination of Shannon decomposition and retiming.

### 1.5 Challenge: Avoiding RTL

The specific challenge in designing a packet processing pipeline is the design of its packet editing modules. This is because FIFOs are usually instantiated from an existing library or synthesized by a specialized tool, while auxiliary elements are usually designed using standard techniques, albeit not always simple. Once the pipeline components are available, putting them together according to the pipeline topology is straightforward.

Therefore, I focus mainly on the design of the packet editing modules throughout the rest of this thesis.

First, I identify several particularities of these modules. They are deeply pipelined circuits that operate on many bits in parallel (e.g., 64, 128 or 256 bits). This tendency becomes very visible in FPGA implementations because of their relative lack in performance compared to ASIC. Second, they interact with the adjacent components through FIFO interfaces. To achieve the desired performance, the handshaking signals require very careful handling. The arising problems have a good reputation of being "brain-twisters" for the design engineer. Third, the specifications of these modules are usually long documents written in plain English, designed by network protocol architects with moderate hardware design experience; traditionally, they have a software-centric view of the issue.

Consequently, these modules are tedious to code at the RTL (register transfer level)

by using a hardware description language such as Verilog or VHDL: designing these modules is usually reserved to experienced engineers and takes a lot of time. Since high performance is needed, very aggressive design techniques are often employed. Bugs appear inherently in corner cases, are hard to fix and even harder to detect.

The critical drawback of RTL design is not a purely technical one. I have mentioned the importance of quick development and maintainability. The difficulty of RTL design tends to undermine the advantages brought on by the use of FPGA technology.

#### 1.5.1 Contribution: high level packet editor description

The first contribution of this thesis is PEG, a new high-level DSL (domain specific language) for specifying the functionality of packet editing modules. Using this language, the designer can specify any practical module in a simple and intuitive manner, staying close to the top-level view of the problem that is familiar to the network protocol architect. Since in PEG all the low-level implementation details are abstracted, RTL design experience is unnecessary; the language encourages the designer to express the problem in terms of high-level functionality.

The proposed language does not have a hardware flavor and I also consider it a desirable goal to remove any software flavor as well. It could be easily argued that an abstract view of packet header editing is completely orthogonal with low-level RTL specifications, the latter being a means to physically accomplishing the former on a hardware target. I argue with the same confidence that a software program is also a mean of implementing the same task on a software target: the correct abstraction for packet editing has little in common with the RTL model or with the software sequential model.

The proposed abstract model can be efficiently translated into both software or hardware, depending on the chosen implementation of the packet processor. The hardware translation forms a significant part of this thesis.

The PEG language has a graphical flavor: the operands, computations, results, etc.,

are represented as nodes in a graph and the dependencies between them are modeled by the graph's edges. PEG is chosen to be general enough for describing all practical header editing operations and particular enough to allow the synthesis procedure generate efficient circuits by taking advantage of some domain-specific properties.

#### 1.5.2 Contribution: packet editor synthesis

Starting from a packet editing module described in PEG, the following task consists in synthesizing a RTL model of the module. In particular, my existing implementation generates synthesizable VHDL code.

This RTL code has to be further synthesized for a specific target, by using a traditional low-level synthesis flow. My primarily considered target was FPGA: the generated RTL code is biased towards this technology in some degree. However, this bias is minor and the flow could easily be re-targeted towards different technologies such as ASICs.

To a first approximation, my synthesis steps resemble traditional high-level synthesis. However, the underlying architectural and computational model are totally different from those found in the traditional approach: the resemblance to classical high-level synthesis is helpful for understanding the general issues but proves shallow at the level of technical details.

In traditional high-level synthesis the RTL design looks like a simple CPU: various computational and memory elements are interconnected by buses, multiplexers, etc. Computational units have "random access" to all operands and destinations. Therefore, computation can be divided between different elements and different clock cycles in an a very flexible manner, given that the causality constraints are respected (i.e., an operand is never used before it is produced).

In this thesis, the architecture is a deep pipeline: data flows through all stages and is locally modified by each stage. Since stages are usually light-weight elements, correlated data (e.g., a packet header) may appear simultaneously in several stages

or even in several modules.

Since data enters (and exits) each stage word by word, ordered as they appear in the packet header, not all operands are available exactly when needed: some buffers are sometimes needed to store useful data within a stage for further use and to store already computed results that have to be output later.

Ideally, data passes constantly through the pipeline and is modified on the fly. In practice, the modules use only some fraction of the clock cycles to read or write data: the pipeline works at lower-than-unit efficiency. Obtaining the best possible efficiency becomes the primary synthesis goal.

My experimental results show that packet editing modules synthesized by my proposed technique meet the performance and area requirement that is expected from a hand-written RTL design. I produce circuits targeting Xilinx Virtex4 FPGAs that can sustain 40 Gbps throughput on industrial examples, equal to state-of-the-art switches, and are vastly easier to write and maintain than classic RTL designs.

# 1.6 Challenge: Pipeline worst case performance

Performance-critical pipelines are generally built from a sequence of simple processing modules, connected by FIFOs. I focus on packet processing pipelines such as those found inside a networking device. Here, the processing modules are the packet header editors, which can be synthesized using my synthesis technique above. However, the issues described in this section are more general and can be applied to a broader class of pipelines, as well as my proposed solution.

Given a complex pipeline, an essential issue is to find the overall pipeline throughput. Ideally, all pipeline modules work at full efficiency. Since a valid data-word is transferred between any two stages every cycle, computing the throughput amounts to multiplying the pipeline clock frequency with its data width.

This ideal case does not occur in practice: real modules insert and remove data,

or require several clock cycles for an internal computation.

For real pipelines such as those I encountered, actual throughputs of 30–70% of ideal are not uncommom. Finding out the real pipeline becomes a critical issue, since the ideal throughput can not be used as a realistic estimation, not even in the coarsest sense. A widely-used rule of a thumb estimates the actual throughput to be 50%. This number can be either too optimistic or too conservative. The latter case leads to over-design, the former to a low service quality (i.e., dropped packets).

A widely used performance analysis technique is simulation. The main drawback is that the modules' behavior and consequently the whole pipeline's behavior depends on the processed data itself. The natural response to this issue is to run extensive simulations with different data patterns. They are chosen to cover, as much as possible, all realistic data patterns. This approach is not very different from the well-known technique of estimating the performance of general purpose CPUs by running various benchmarks.

However, in contrast to a CPU, a packet processor is a hard real-time system. For this class of systems the worst case performance is generally more important than the average one. Most benchmarks are designed to cover all possible corner cases, since it is expected that the worst case behavior would correspond to a corner case. For example, a simple Ethernet linecard would be simulated using sequences of minimum size (64 bytes) and maximum size (1500 bytes) packets.

For a modern packet processor, which is more complex, the number of these corner cases is very large and their simulation requires extensive running time. Practically, the simulation is restricted to a limited number of patterns. Consequently, "the field tests always find the bugs in the simulation setup," i.e., often data patterns not considered in simulation occur in practice. The development task becomes an interactive process between the designer, field tester, and worse, the customer.

Naturally, one would be interested in covering all possible cases by using an analytical, surprise-free approach that provides a system performance guarantee.

A related issue is the required sizes of the FIFOs interconnecting the pipeline modules. Their size influences the overall pipeline performance because a full or an empty FIFO stalls the adjacent modules for one or several clock cycles. Large capacity FIFOs successfully decouple the pipeline modules but waste a lot of resources. One would like to know the minimum FIFO sizes for which the pipeline achieves its highest performance.

One approach is to size the FIFOs by using some rough heuristics and to refine the analysis by extensive simulation. This method has the same drawbacks mentioned above.

#### 1.6.1 Contribution: pipeline performance analysis

Computing the worst case throughput of packet processing pipelines is a difficult task because of their complex sequential behavior.

I propose a technique to compute the maximum possible pipeline throughput assuming that the FIFOs are unbounded. First, I analyze each module in isolation: I define some performance metrics for these modules and I show how they can be computed. Second, I focus on the entire pipeline: I assemble the numbers already computed for each individual module to determine the pipeline's worst case throughput.

This proposed algorithm is very fast. As unbounded FIFOs can not be realized in practice—the considered pipelines are not realistic but the computed throughput is known to be achievable by using FIFOs with finite sizes, although the algorithm returns no actual numbers for these sizes.

From the system designer's point of view, the same pipeline functionality can be achieved by using more or fewer modules, by dividing the task between modules in different ways, or by choosing different implementations for each module. Different functionally equivalent designs can be manually or automatically generated and a performance analysis step is required in every case. My proposed algorithm can be

run inside this design exploration loop because of its small running time. Therefore, the algorithm can help indirectly the design and synthesis steps.

#### 1.6.2 Computing minimum FIFO sizes

FIFOs consume a lot of resources: their area sometimes exceeds that consumed by the processing modules themselves. Additionally, large FIFOs require specific implementations such as instantiating block-memory primitives on a FPGA. This decreases the maximum clock period. Since reducing the FIFO sizes helps the design in terms of both area and performance, I treat FIFO sizing as an important topic of my thesis.

I compute the minimum FIFO sizes required by the pipeline for achieving the ideal throughput computed for the case when the FIFOs are unbounded. I propose two algorithms based on model checking: one exact and one heuristic. The heuristic algorithm is faster. This is an advantage for big pipelines where the running time grows rapidly with the design complexity.

Experimental results suggest that my algorithms are applicable to pipelines of at least five modules, for which an optimal or very good solution is found in minutes or less. I consider them practical since they are not invoked repeatedly during a normal design process but only once.

### 1.7 Challenge: Sequential RTL issues

Retiming is a well-known sequential optimization technique. It changes the positions of the registers inside a sequential network by moving them forward or backward. The system functionality is preserved but the resulting performance may be better than the original one.

Although the optimization potential of retiming exists for any sequential network, it becomes immediately visible if a linear pipeline is considered. If each stage takes a certain amount of time for computation, the maximum clock period will be given by

the slower stage. Equalizing the time taken by the pipeline stages by changing the frontiers between them (i.e., the position of the registers) leads to the best outcome that can be achieved by retiming alone: the best performance is the ratio between the total computational time and the number of pipeline stages.

For a high-performance pipeline such as the packet processors considered in this work, retiming is a natural transformation in the optimization step. The RTL designer usually does not spend much time hand-placing the registers carefully but leaves the task to the optimization tool since at the moment of writing the RTL code he does not know exactly the time taken by each pipeline stage.

It can not be overemphasized that the maximum clock period achievable *before* retiming is irrelevant, while the relevant merit figure is the clock period *after* retiming. For example, to correctly compare two equivalent circuits, one has to retime them first: only after retiming is comparing the two clock periods meaningful.

The bottleneck which affects the performance of a high-speed pipeline is generated by the feedback loops. Generally, data flows forward through the pipeline but control and status signals often travel in the reverse direction. Consequently, the pipeline is no longer a simple loop-free sequential network but a complex one.

The performance of a simple linear pipeline may be increased by adding several extra stages and retiming the resulting pipeline. This is not possible if feedback loops are present. Retiming can only move registers, so the number of registers on any loop remains constant: therefore it is not possible to add extra registers inside a loop without altering the network functionality. Retiming remains a powerful technique but it has to be combined with other techniques that also modify the combinational logic.

To summarize, if for a combinational network the optimization priority is to reduce the length of the critical paths, for a high performance sequential network the goal is the reduce the length of the critical feedback loops. This task is more difficult in the sequential case.

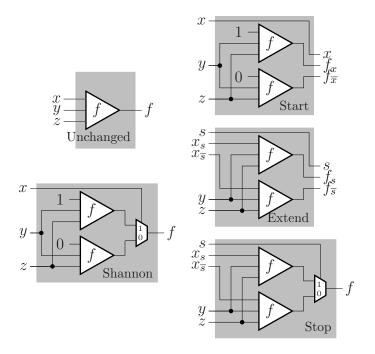

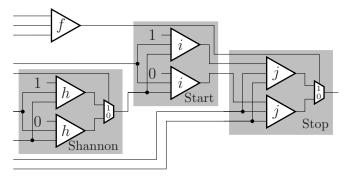

#### 1.7.1 Contribution: combining Retiming and Shannon

Optimizing sequential cycles is essential for many types of high-performance circuits such as pipelines for packet processing. Retiming is a powerful technique for speeding up the pipelines but it is stymied by tight sequential cycles.

The class of techniques that addresses this issue is known as retiming and resynthesis. Theoretically, R&R performs arbitrary logic optimizations plus retiming; it can be shown that this technique can transform a circuit into any equivalent circuit.

Exploring all possible transformations is not practically possible. Real algorithms usually choose some generic transformations and run them iteratively, in a heuristic manner.

Shannon decomposition is a generic transformation that may reduce the length of a critical cycle. It can be seen as a form of speculation. Designers seldom attack such critical cycles by manually combining Shannon decomposition with retiming, since such a manual approach is slow and error-prone.

It can be seen that combining retiming with Shannon decomposition is a special case of the more general R&R technique.

I propose a sequential optimization algorithm that restricts the class of allowable transformations to Shannon decomposition and retiming. The algorithm performs a systematic design space exploration: it finds exactly the best performance circuit that can be obtained by applying these two transformations.

While the algorithm is only able to improve certain circuits (roughly half of the benchmarks I tried), the performance increase can be dramatic (7%–61%) with only a modest increase in area (1%–12%). The algorithm is also fast, making it a practical addition to a synthesis flow.

### 1.8 Contribution summary. Thesis outline

In this thesis I propose a complete design flow for specifying, synthesizing, and analyzing packet processing pipelines, which are performance critical components of a modern network device such as a packet switch.

I propose PEG, a high level domain specific language for specifying the active pipeline elements, the packet header editors. Next, I propose a synthesis technique for transforming PEG into actual RTL code, which can be later mapped on a specific target such as an FPGA.

I claim, based on experiments, that the proposed synthesis flow is practical: using the presented methodology, entire packet processing pipelines belonging to industrial grade networking devices were successfully modeled and synthesized.

The proposed language, as well as the synthesis technique, are described in Chapter 2 of this thesis. Part of the material was published at the Design Automation Conference in 2006 [SHE06].

I introduce an analytic approach for the analysis of packet processing pipelines that offers a worst-case performance guarantee. As a related topic, I address the issue of computing the minimum FIFO sizes in a packet processing pipeline.

The performance analysis and FIFO sizing techniques are detailed in Chapter 3 of this work. Results were published at the International Workshop on Logic and Synthesis in 2007 [SE07].

Finally, I present a low-level sequential optimization algorithm, based on the combination of Shannon decomposition and retiming, which optimizes a certain class of sequential networks such as the high performance packet processing pipelines.

The algorithm is presented in detail in Chapter 4. I published a condensed description at Design, Automation, and Test in Europe in 2006 [STE06] as well as a more complete version in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems in 2007 [STE07].

In the last chapter I summarize the results of the present thesis.

Chapter 2

# Chapter 2

# Synthesis of Packet Processing Pipelines

#### 2.1 Overview

Packet processing pipelines are fundamental blocks of many data communication systems such as switches and routers. For example, the linecard in Figure 1.2 contains two such pipelines: an ingress and an egress one, which handle the incoming and outgoing traffic, respectively.

The core of such a structure is a linear pipeline containing several chained modules: the packets flow from left to right and are transformed on the fly. The function of each module and their order connection give the overall pipeline functionality.

Each module performs some specific transformation of the packet headers. For example, the TTLUPDATE module decrements the TTL field of each header and marks the packet to be dropped if the value reaches zero. The operation performed by a module consists in modifying, adding, and/or removing various fields of the packet header and is hence called packet header editing.

The sequential network implementing such a packet header editor is complex. I have encountered over a dozen of real modules during my experiments (Section 2.7)

and I concluded that an efficient RTL implementation is very convoluted even for modules performing simple operations. A high-level approach for synthesizing these modules brings a lot of advantages compared to manual RTL design (Section 1.5).

However, generic high-level approaches such as synthesizing C-like behavioral models give poor results. It is sufficient to notice that real projects still use traditional RTL design even if behavioral synthesis has been proposed for several decades. The main drawback of a generic method is the low performance obtained after synthesis. In contrast, a custom method can take advantage of the specific particularities of a small class of problems and give good results.

In this chapter, I propose a high-level model, PEG, that can specify the functionality of a given header editing module. I also propose an automated high-level synthesis algorithm that starts from this model and translates it into synthesizable RTL code. This algorithm takes advantage of the specific properties of a header editing module and generates a result comparable to a manual RTL implementation.

The drawback is that my approach has a limited scope. However, a real network device contains several packet editing modules, so my technique covers an important share of the entire design. Moreover, these modules are the components most likely to be altered when specifications are changed. Therefore, it is the synthesis of these modules that gets the most benefits from a high-level approach.

It may be argued that it is desirable to have a uniform high-level description of the entire system. This is not realistic today. It is unlikely that critical components such as memories, transceivers, DDR interfaces, etc., could be synthesized by a generic technique. Practically, each of these has its particularities and is designed manually or using a specialized tool. This observation shows the place of my synthesis technique in the overall picture.

## 2.2 Packet Processors and Editing

Figure 1.2 shows the block diagram of a packet switch consisting of line cards (we only show one) connected to a switching fabric that transfers packets. I focus on designing the line cards, which provide network interfaces, make forwarding and scheduling decisions, and, most critically, modify packets according to their contents.

My synthesis technique builds components in the ingress and egress packet processors. A packet processor is a functional block that transforms a stream of input packets into output packets. These transformations consist of adding, removing, and modifying fields in the packet header. In addition to headers defined by network protocols, the switch may add its own control headers for internal use.

Packet processors perform complex tasks through a linear composition of simpler functions. This model has been used for software implementations on hosts [OP92] and on switches [KMC<sup>+</sup>00]. Another proposed architecture for hardware is a pool of task-specific threads that process the same packet in parallel without moving the packet [BJRKK04].

I use a unidirectional, linear pipeline model that simplifies the implementation without introducing major limitations. For example, Kohler's IP router [KMC<sup>+</sup>00] uses loops only to handle exceptions. I would do this with a separate control processor.

While the logical flow can fork and join, I implement only linear pipelines that can use flags to emulate such behavior. Non-linear pipelines are more complicated and would not improve throughput. If a packet needs to be dropped or forwarded to the control processor, I set flags in the control header and perform the action at the end of the pipeline. This guarantees every processing element sees all the packets in the same order; packet reordering is usually done in a traffic manager, a topic beyond the scope of this thesis.

Figure 1.2 shows a packet processing pipeline that edits the Virtual Local Area Network (VLAN) tag of an Ethernet packet [IEE03] and adds a Multi Protocol Label Switching (MPLS) label [RVC01], based on unique flow identification (FlowID). I

assume a previous stage has performed flow classification and pre-appended a control header with the FlowID.

Both the VLAN push and MPLSPUSH modules insert additional headers after the Ethernet header, while the Time-To-Live (TTL) update and Address Resolution Protocol (ARP) resolution modules only modify existing packet fields. The VLAN pop module removes a header field. While this pipeline is simple, real switches just perform more such operations, not more complicated ones.

Thus, packet processing amounts to adding, removing, and modifying fields. Even the flow classification stage, which often involves a complex search operation, ultimately produces a modified header. I refer to these operations as *packet editing*; it is the fundamental building block of a packet processor.

In addition to the main pipeline, Figure 1.2 shows two memory lookup blocks. These blocks store descriptors that define how to edit the headers (e.g., how many MPLS labels to add). Here, the FlowID is an index into descriptor memory. A memory lookup module is any component that takes selected fields and produces data for a downstream processing element (e.g., IP address search, present in all IP routers, is a form of generalized memory lookup). Flow classification is thus packet editing with memory lookups.

Modules that use memory lookup assume a previous pipeline stage issued the request, which is processed in parallel to hide memory latency. I do not synthesize memory lookup blocks, but can generate requests and consume results. Because our pipelines preserve packet order, simple FIFOs suffice for memory interfaces.

Hence, I model packet processors as linear pipelines whose elements have four types of ports: input from the previous stage, output to the next, requests to memory, and memory results. Each processing element must be capable of editing packets based on their content and data from memory.

#### 2.3 Related work

Kohler et al. [KMC<sup>+</sup>00] propose the CLICK domain-specific language for network applications. It organizes processing elements in a directed dataflow graph. CLICK specifies the interface between elements to facilitate their assembly. Although originally for software, Kulkarni et al. [KBS04] propose a hardware variant called CLIFF, which represents its elements in Verilog. Schelle et al.'s [SG05] CUSP is similar. Brebner et al. [BJRKK04] add speculative multi-threaded execution.

Unlike CLIFF/CUSP, I fully synthesize my modules instead of assembling library components. CLICK, furthermore, defines fine-grained elements whose connection has substantial handshaking overhead. My method synthesizes bigger modules; as fewer handshaking signals are necessary, the above mentioned overhead decreases.

My approach differs from classical high-level synthesis (c.f., De Micheli [De 94]) in important ways. For example, I always use a flavor of as-soon-as-possible scheduling for speed; classical high-level synthesis considers others. Furthermore, most operations are smaller than the muxes needed to share them, so I do not consider sharing.

The main difference is my choice of computational model. Rather than assume data are stored and retrieved from memories, I assume data arrive and depart a word at a time: my scheduling considers the clock cycle in which data arrive and can leave.

### 2.4 The Packet Editing Graph

### 2.4.1 What to expect from the PEG

The Packet Editing Graph PEG is a high-level model designed to specify the operations performed by a packet header editing module. PEG is the format taken as input by my synthesis procedure, which is described in the next sections.

I have designed PEG following two goals. First, it has to offer the right level of abstraction. That is, to offer a familiar view of the problem to the designer who

is most likely to use it. Usually, he has good expertise in system architecture and network protocols but may lack RTL design skills. He sees the packet header editing as a group of arithmetic and logical operations performed on the packet fields. More abstractly, he sees the output data as a function of the input, not as a sequence of C or RTL statements including loops, jumps, pauses between clock cycles, etc.

The model has to be general enough to express any header editing operation. The reverse is more difficult to argue for but it is not less important. Any feature added without a good reason tends to cancel most of the advantages brought by a high-level language: clarity, easiness to debug, etc. Rich languages such as C++ or VHDL have proven this to be true.

Second, performance is critical for many applications such as packet processing pipelines. That is, a good model has to allow an efficient automatic synthesis technique. An elegant approach such as RTL synthesis from a software (C) model may indeed hide all implementation details but existing automatic synthesis algorithms are not very efficient. Even if there is no theoretical barrier against developing efficient algorithms in the future, such an approach is uninteresting today. Another reason for hiding the implementation details is the desire to synthesize to module on different targets with minimum effort.

I believe that PEG answers both issues well, as concluded at the end of this chapter, where experimental data are presented.

# 2.4.2 A PEG Example

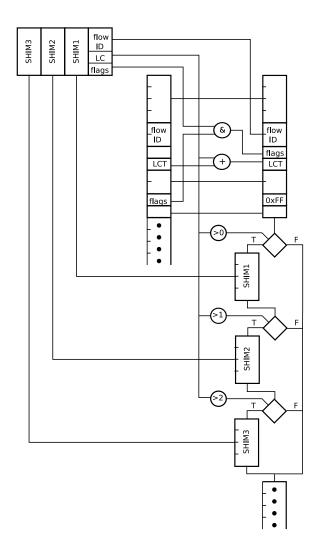

Figure 2.1 shows a PEG for a simplified MPLSPUSH module. The MPLS protocol adds a label to the beginning of a packet that acts as a shorthand for the IP header. When another switch receives the packet, it uses separate rules to forward the packet. As the technique allows stacking, a packet may contain more MPLS labels.

As seen by the MPLSPUSH module a packet starts with a control header, which contains various fields, such as FLOWID, FLAGS, and LCT. This is followed by zero or

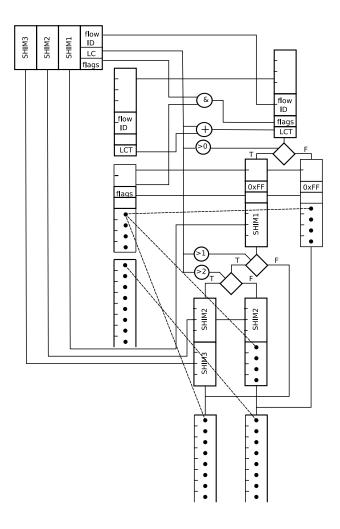

Figure 2.1: Graphic PEG specification for the MPLS module

more MPLS labels and the packet payload, which can be arbitrary data.

The module in Figure 2.1 inserts up to three MPLS labels, immediately after the control header according to a transaction descriptor (TD). The packet processor needs one TD for each processed packet: in this example, it obtains them by issuing requests to a memory lookup engine in a previous pipeline stage. The MPLSPUSH module has accordingly an auxiliary input to receive this TD from the memory lookup.

The module also updates the label count (LCT) of the control header by adding to its current value the label count field (LC) of the TD, so as the new header reflects the correct number of labels. Additionally, it overwrites the FLOWID field with the one from the TD and overwrites a reserved header field with the FLAGS, after they are anded with a mask taken from the TD; the original FLAGS field is overwritten with 11111111. Functionally, these operations map a set of MPLS tunnels to the set of next-hop destinations.

The reader can follow these operations in the PEG graphical representation from Figure 2.1. He can notice an acyclic, directed graph consisting of inputs, arithmetic and logical operators, and outputs, and the connections among those. The inputs are the packet itself and TD coming from the memory lookup engine: they are drawn as rectangles in the top left section. The operators are represented by the circular nodes in the middle of the figure. The output packet corresponds to the packet map (the control-flow graph on the right).

Looking at the figure, the reader can assume that time flows from top to bottom and data flows from left to right.

The packet map is the novel aspect of a PEG. The bits of the output packet are assembled by following a downward path. A diamond-shaped node is a conditional: control flows to one of its successors depending on the value of the predicate. Conditionals allow bits to be inserted and deleted from the output packet. The final node, marked with dots, copies the remainder of the input packet to the output.

# 2.4.3 PEG description

In this section I give a detailed description of PEG. A PEG is an acyclic, directed graph. It consists of three subgraphs: input, computation, and output. Each subgraph contains nodes of several types. In the above example, various types were represented by different shapes. A systematic list of these types and their exact meaning is given below.

Although PEG is conveniently depicted as a graphical model, I introduce in the sequel a text format for rigorously defining the type of the nodes, their attributes

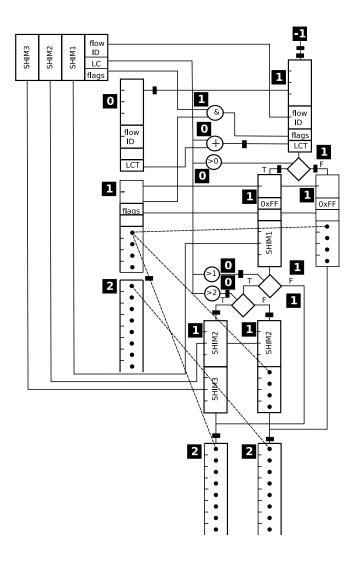

| #the input subgraph                  | alias NEW_HDR 96 \          |

|--------------------------------------|-----------------------------|

| pktin PIN 96                         | H1 0 31 \ TD_FLOWID 0 15 \  |

| auxin TD 128                         | NEW_FLAGS 0 7 NEW_LCT 0 7 \ |

|                                      | H3 0 15 FILL_FF 0 7 H4 0 7  |

| #the computation subgraph            |                             |

| alias H1 32 PIN 0 31                 | const CO 8 0                |

| alias FLOW_ID 16 PIN 32 47           | const C1 8 1                |

| alias H2 8 PIN 48 55                 | const C2 8 2                |

| alias LCT 8 PIN 56 63                | arith GTO 1 > TD_LC CO      |

| alias H3 16 PIN 64 79                | arith GT1 1 > TD_LC C1      |

| alias FLAGS 8 PIN 80 87              | arith GT2 1 > TD_LC C2      |

| alias H4 8 PIN 88 95                 |                             |

| alias SHIM3 32 TD 0 31               | #the output subgraph        |

| alias SHIM2 32 TD 32 63              | pktout POUT OHDR            |

| alias SHIM1 32 TD 64 95              | odata OHDR NEW_HDR BRO      |

| alias TD_FLOWID 16 TD 96 111         | cond BRO GTO OSH1 ! OPD     |

| alias TD_LC 8 TD 112 119             | odata OSH1 SHIM1 BR1        |

| alias TD_FLAGS 8 TD 120 127          | cond BR1 GT1 OSH2 ! OPD     |

|                                      | odata OSH2 SHIM2 BR2        |

| arith NEW_FLAGS 8 and FLAGS TD_FLAGS | cond BR2 GT2 OSH3 ! OPD     |

| arith NEW_LCT 8 + LCT TD_LC          | odata OSH3 SHIM3 OPD        |

| const FILL_FF 8 X''FF''              | payld OPD 96                |

|                                      |                             |

Figure 2.2: Textual PEG specification for the MPLS module (2 columns)

and their functionality. This textual format is not meant to be human writable or readable. It is easy to imagine a GUI for designing a PEG graphically but I consider this beyond the scope of my thesis.

The syntax is trivial. Each line describes a node: it begins with the node type and its name, followed by some fields, according to the node type. The quickest way to understand the PEG syntax is to compare the graphical representation of the MPLS module in Figure 2.1 which the equivalent textual specification in Figure 2.2.

### 2.4.3.1 The input subgraph

This subgraph is trivial, and consists of a PKTIN node, and an optional AUXIN node, which specify the main packet input and the possible auxiliary input, respectively. They are described below:

| Syntax  | pktin | name | size |

|---------|-------|------|------|

| Example | pktin | N    | 128  |

Outcome: N represents the input packet, which has a minimum length of 128 bits. Any PEG has one node, of type PKTIN, which represents the input packet. The size parameter is the minimum packet length.

| Syntax  | auxin | name | size |

|---------|-------|------|------|

| Example | auxin | N    | 112  |

Outcome: N represents the auxiliary input, which has 112 bits.

This node is optional, i.e., is present only for modules that require an auxiliary input such as a reply coming from a memory lookup engine. This input remains constant for all the time a packet is processed and changes only between packets. At most one AUXIN node may be present in a PEG. If several auxiliary inputs are required, they can be merged into a single AUXIN node: the RTL designer must combine the appropriate handshaking signals.

### 2.4.3.2 The computation subgraph

This subgraph is itself a DAG. Its nodes perform various computations such as arithmetic or logic operations, extracting and concatenating bit fields. Custom operations are also supported, assuming that corresponding RTL code (e.g., VHDL) is provided.

Each of the nodes in the computational subgraph take a number of inputs according to their functionality; these inputs may belong to the input subgraph or may be computational nodes themselves.

To avoid a series of ambiguities, PEG requires that each computational node to be assigned a size, which is the size of the computation result. Even if for some operation this size can be inferred from the size of the input operands, this cannot be safely done in the general case.

Below, I describe the type of nodes supported by the computational subgraph:

| Syntax  | const | name | size | const |

|---------|-------|------|------|-------|

| Example | const | N    | 12   | 7     |

Outcome: N is the constant 7 represented with 12 bits

The CONST node is used to represent a constant.

Outcome: N is the bitwise AND of the two inputs A and B, extended or truncated to 8 bits.

The ARITH node takes as many inputs as needed by that particular operation. The operation op can be any arithmetic or logic operation supported in VHDL. Note that the size of the result is unambiguously specified; it is not inferred from the size of the inputs. This avoids a lot of confusion, such as the size resulting from adding two 8-bit numbers.

Syntax alias

$$name$$

$size$   $I_0$   $msb_0$   $lsb_0$  [...]

Example alias N 10 A 0 3 B 10 15

Outcome: N is the concatenation of 4 bits (0:3) of A and 6 bits (10:15) of B.

The ALIAS node concatenates subfields from one or more inputs. The size has to match the sum of the subfield sizes. In particular, this node can have only one input, so it may be used to extract a subfield of a node.

| Syntax  | extern | name | size | expr |

|---------|--------|------|------|------|

| Example | extern | M    | 14   | A    |

Outcome: the computation for M is done by an extern module (M.VHDL)

An external module, from file NAME performs the computation. The input of the module is *expr*. The module has to provide an input *req* and an output *rpy*, whose sizes have to match the size of *expr*, and of the current EXTERN node, respectively. The module may have additional ports, which have to be handled manually. The module may contain sequential logic, but from our point of view it has to behave like a purely combinational node, i.e. its *rpy* output has to reflect the changes of its *req* input in the same clock cycle.

If *expr* is the special symbol "!," the module has no *req* input. This is useful, for example, for storing parameters, which from our point of view behave like constants but can be modified by the configuration circuitry that assists the pipeline.

### 2.4.3.3 The output subgraph

The output subgraph specifies the data that the module writes to the main packet output and, optionally, to the auxiliary output. It contains a PKTOUT node and an optional AUXSC one.

The PKTOUT node is in fact the root of a control-flow subgraph. For each packet, this subgraph is traversed, starting from the root down to one of its leaves. Once a leaf is reached, the process is implicitly repeated to handle to next packet.

When the control flow reaches an ODATA node, the module writes some data to the packet output; this node makes reference to a node in the computation subgraph, which specifies the data to be written. After that, the control is passed to the unique succesor node.

The output subgraph also contains COND nodes, which write nothing to the output but pass control flow to one of their successors, depending on some conditions. These conditions are also nodes from the computation subgraph.

The leaves are always PAYLD nodes, which copy the rest of the input packet (usually the payload) to the output.

Below I describe the nodes supported by the output subgraph.

| Syntax  | pktout | name | dest |

|---------|--------|------|------|

| Example | pktout | N    | N1   |

Outcome: N is the root of the output packet subgraph.

A PEG contains one PKTOUT node, which represents the output packet. The *dest* points to the first active node in the output packet subgraph.

| Syntax  | auxout | name | size expr |   |

|---------|--------|------|-----------|---|

| Example | auxout | N    | 48        | A |

Outcome: the auxiliary output N, of size 48, will output the expression A.

At most one AUXOUT node may be present in a PEG. The node is optional, i.e. is present only for modules which have an auxiliary output, such as a request going to a memory lookup engine. If more auxiliary outputs are needed, please see the description of the AUXIN node.

| Syntax  | odata | name | size | expr | dest |

|---------|-------|------|------|------|------|

| Example | odata | N    | 16   | A    | N1   |

Outcome: if N is reached, the module outputs 16 bits corresponding to expression A, then passes the control to node N1

The ODATA node instructs the module to write some data to the output packet.

The data to be written is taken from *expr*, which is a node from the computational subgraph, such as an arithmetic one. After that, the control is passed to node *dest*

Outcome: when reached, node N transfers the control to N1, if  $A \neq 0$ , and to N2, otherwise.

The COND node behaves like an *if* ... *elsif* ... construct. Note that the condition for the last destination is marked by "!," which I use to denote "always." Indeed, N is required to pass control to some of its successors, for any values of the input conditions.

The main purpose of the COND node is to model conditional field insertions and removals, but its use is not restricted to these operations.

Outcome: when reached, N copies to the output the input packet, starting from offset 128, up to the end.

The PAYLD node is used to handle the payload of the packet, which may have a variable size. Usually, the *offset* points immediately after the packet header. It has to be less than or equal to the minimum input packet size, as specified by the PKTIN node.

# 2.5 The Synthesis Procedure

PEG is an abstract model and can be synthesized to various hardware or software targets. I address the hardware synthesis of modules that belong to a pipeline such as in Figure 1.2 and interact with the environment using the protocol described in Section 2.5.1. This target is an attractive choice for high-performance network de-

vices.

The proposed technique translates the PEG specification to an RTL model, i.e., synthesizable VHDL code. Since all modules and the inter-connecting FIFOs respect the mentioned I/O protocol, assembling the pipeline from its components becomes a mechanical operation.

The synthesis starting point, PEG, offers a flat, implementation-independent view of the module. Inputs and outputs can have different sizes and they are considered to be accessible as operands or destinations at any time. The challenge is to translate this model into RTL, where packets enter and exit the module on the fly, as a sequence of words of fixed size.

Consequently, different fields of the packet are present inside the real module on various clock cycles and the module has to perform the right operations at the right moments.

Fields do not generally fall on word boundaries: some fields of the input packet have to be assembled over several clock cycles and some fields of the output packet have to be output in several clock cycles. Moreover, since PEG allows conditional insertions and removals, there is not always a simple way of deciding when and where a field in the output graph has to be sent to the output.

Inserting and removing data changes the size of the packet. For some clock cycles, the input has to be stalled, the output has to idle, or both. Moreover, some fields in the output packet may depend on fields that arrive later in the input packet: the corresponding output word cannot be generated before the needed input arrives. The data does not flow through the pipeline module uniformly; valid data tokens are interleaved with idle ones.

The main goal of the synthesis technique below is to keep this data flow as close as possible to the ideal case, i.e., to insert as few input/output idle cycles as possible. However, the overall performance depends not only on the number of cycles but also on the cycle period. Therefore, concentrating complex operations inside a single clock

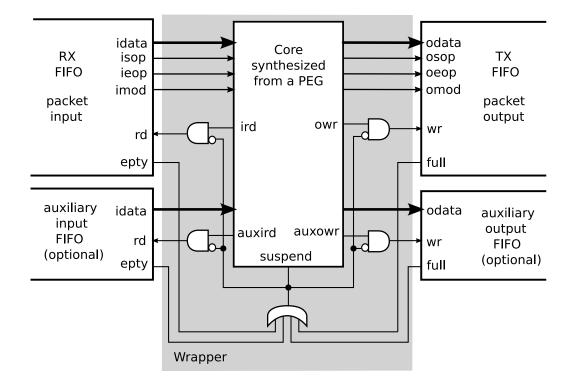

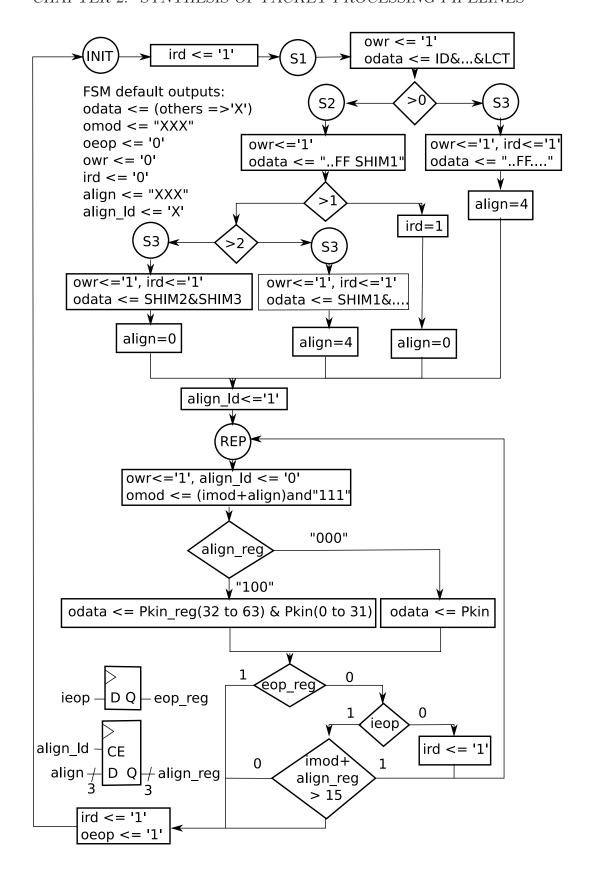

Figure 2.3: A module I/O signals and its two components

cycle may lead to a different outcome than intended.

# 2.5.1 The module I/O protocol

Within the pipeline, the packet editor module interacts with the adjacent FIFOs through four interfaces: the packet input and output, and the optional auxiliary input and output (Figure 2.3, where the module is represented by the gray area).

The module sees the input packet as a sequence of w-byte words arriving on the idata port, where values of 4, 8, 16 (i.e., 32, 64, and 128 bits) are typical for w. Similarly, the output is generated as a sequence of w-byte words on the odata port.

Additionally, data words are accompanied by two framing flags that identify the beginning and the end of the packets. The signal *sop* is asserted for the first word of the Packet and *eop* for the last. Both signals are asserted in the same cycle if the

packet is small enough to be included within one word. All modules assume these signals arrive in a consistent order and generate them as such.

Since the packet may contain a number of bytes that is not multiple of w, the last data word may contain from 1 to w significant bytes. The mod signal, of size  $log_2(w)$ , gives the number of valid bytes in the last data word minus one. This signal is meaningful only when the eop signal is asserted; any pipeline element is free to output undefined data on mod otherwise.

The input interface consist of the *idata*, *isop*, *ieop*, and *imod* signals described above, plus two handshaking signals: *val* and *rd*.

The val signal, generated by the input FIFO, tells the module if data is available at the input: when val is asserted then the  $i^*$  signals carry valid values, otherwise these signals have to be ignored.