# Dynamic Modelling and Control of Dual Active Bridge Bi-directional DC-DC Converters for Smart Grid Applications

A thesis submitted in accordance with the regulations of the Royal Melbourne Institute of Technology University in fulfillment of the requirements for the degree of Doctor of Philosophy.

by

Dinesh Sekhar Segaran BEng(Hons), Monash University, 2006

Supervisor: Prof. Grahame Holmes Associate Supervisor: Dr. Brendan McGrath

School of Electrical and Computer Engineering (SECE), RMIT University.

February 7, 2013

i

© Copyright

by

Dinesh Sekhar Segaran

2013

### Dynamic Modelling and Control of Dual Active Bridge BI-directional DC-DC Converters for Smart Grid Applications

Thesis Acceptance

This student's Thesis, entitled **Dynamic Modelling and Control of Dual Active Bridge Bi-directional DC-DC Converters for Smart Grid Applications** has been examined by the undersigned committee of examiners and has received full approval for acceptance for fulfillment of the requirements for the degree of Doctor of Philosophy.

APPROVAL: Chief Examiner

iii

#### Declaration

I declare that this thesis is my own work and has not been submitted in any form for another degree or diploma at any university or other institute of tertiary education. Information derived from the published and unpublished work of others has been acknowledged in the text and a list of references is given.

> Dinesh Sekhar Segaran February 7, 2013

### Abstract

Since the modern Smart Grid includes highly dynamic energy sources such as wind turbines and solar cells, energy storage is required to sustain the grid in the face of fluctuations in power generation. Possible energy storage elements that have been proposed include Plug-in Hybrid Electric Vehicles (P-HEVs) and battery banks, with power electronic converters employed to link the Direct Current (DC) energy storage elements to the Alternating Current (AC) Smart Grid. These systems all demand bi-directional DC-DC energy transfer capability as well as galvanic isolation as part of their core functionality. At power levels greater than a kilowatt, these complex power flow requirements are typically met with a Dual Active Bridge (DAB) Bi-directional DC-DC converter.

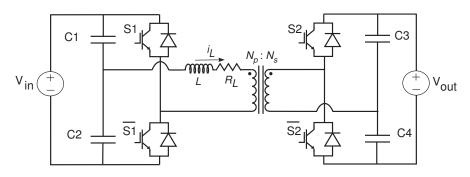

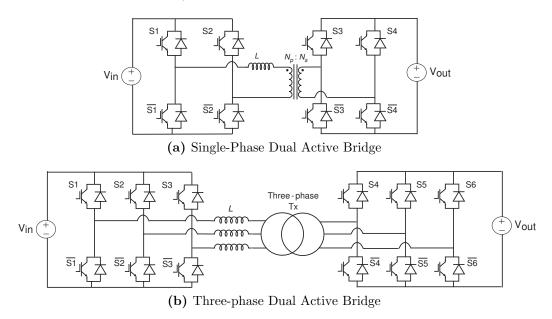

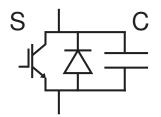

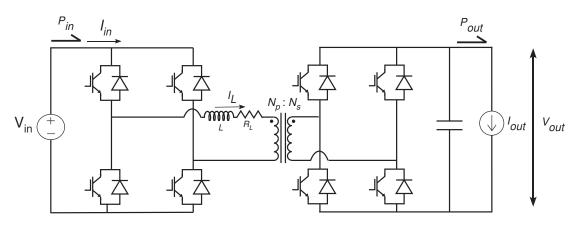

The DAB converter is made up of two single-phase H-bridge converters, connected back-to-back across a high-frequency AC link that is made up of an inductor and an isolation/scaling transformer. Each bridge is modulated using a phase-shifted square wave (PSSW) modulation scheme, where the phase difference between the bridge output voltage waveforms governs the magnitude and direction of power flow. This converter also relies upon a capacitor to provide DC output voltage stabilisation as well as ride-through during transient events (e.g. changes in the desired output voltage or load condition). To guarantee steady state stability and provide a fast transient response, fast and accurate regulation of these converters is essential towards maximising overall grid performance. This makes the DAB converter a more attractive solution at lower power levels and significantly boosts their viability at higher power levels. This thesis therefore aims to maximise closed loop regulator performance for these converters.

To investigate the limits of controller performance, a highly accurate dynamic converter model is required. Previous modelling techniques applied to the DAB converter are complex, computationally intensive and do not easily account for  $2^{nd}$  order effects such as deadtime, which significantly affect the dynamic response of the converter. This thesis presents a novel *harmonic modelling* technique that results in a simple yet accurate and flexible converter dynamic model. The basic premise of

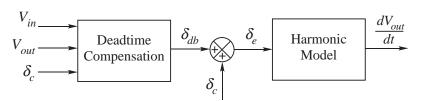

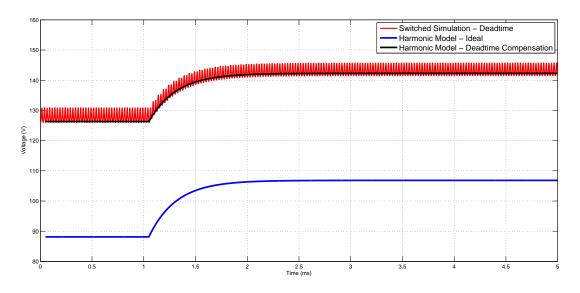

the harmonic model is that the converter modulation functions drive the converter dynamics. Fourier analysis is used to decompose the modulation functions into their harmonic components, so the converter response to each significant harmonic can be determined. These responses are then summed together to give the full dynamic model. It is also identified in this work that deadtime changes the converter operating point, and that its effect is dependent on the AC inductor current. A series of closed form expressions that define the inductor current were developed and used to predict the effect of deadtime across all operating conditions. This prediction was used to extend the harmonic model, achieving a first order, two-input, small-signal state space model that was verified in simulation and then matched to an experimental DAB converter.

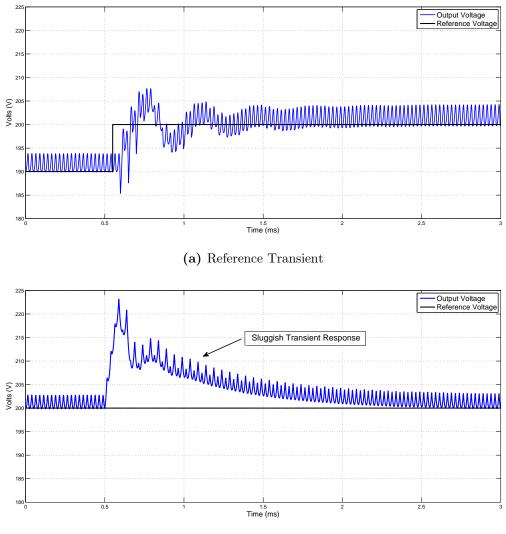

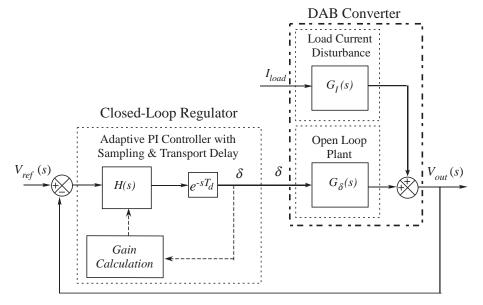

The new harmonic model was then used to investigate the performance limits of a closed loop regulator for the DAB converter. Since the aim of the regulator is DC voltage regulation, a Proportional + Integral (PI) control structure was chosen and implemented using a digital microprocessor. This thesis presents several enhancements to maximise the performance of this controller. First, maximum controller gains are calculated by precisely accounting for the limiting effects of the digital controller implementation (transport delay). Second, the harmonic model identifies that the forward path gain of the converter varies significantly with operating point, so an adaptive gain calculation algorithm was implemented to match the changes in plant characteristics, ensuring consistently high performance across the operating range. Third, the model also identifies that the load current acts as a disturbance input that significantly compromises performance, so a feed-forward disturbance rejection algorithm was implemented to minimise this effect. Finally, an AC load condition was also investigated to guarantee feasibility in a Smart Grid context. The excellent performance achieved by this new DAB voltage regulator minimises the capacitance needed to maintain the DAB output voltage in both steady-state and transient conditions. This offers the potential to eliminate the traditional electrolytic capacitor used in these applications, with associated size, cost and lifetime benefits.

All design, modelling and control ideas presented in this thesis were extensively verified both in simulation as well as on a 1 kW prototype DAB converter.

### Acknowledgements

First and foremost I would like to thank my supervisors, Professor Grahame Holmes and Dr. Brendan McGrath. The Power Electronics Group is a fantastic working environment, and I hope it always will be a centre for excellence. I thank you both for your guidance and knowledge, but most of all for always having faith in me, and for always being the champions for my rights, especially when no one else would.

Among all those I would like to thank, I would like to make special mention of Dr. Peter Freere. Thank you, Peter, for showing us all that engineering, education and understanding all are truly right at our fingertips. Also, to the brilliant and ever helpful people at Creative Power Technologies – Pat, Mac, Mike – thank you for all the support – engineering and otherwise. To the technical and administrative staff of both Monash University and RMIT, thank you. Your tireless efforts make everything I have done possible. In particular, I would like to thank Ivan Kiss for his assistance, technical knowledge and friendship.

I would also like to thank all my contemporary postgraduate associates. Your friendship and understanding of the PhD. burden has helped me shoulder it better. In particular I would like to thank Wang Kong, for all his help and friendship over the years. Sorrell Grogan, I thank you for the gift of laughter and innumerable silly (yet disturbing) jokes. I would also like to extend my thanks to Richard Watson, Reza Davoodnezhad, Carlos Teixeira, Zaki Mohzani and Stewart Parker.

Lastly, but most importantly, I would like to thank my parents, Dr. Segaran Muthu and Dr. Vineetha Das, I add yet another Doctor to the family. *Thank you* is simply not enough to acknowledge your love and support over the years. I am the man I am today because of you both, and you are ever my inspirations. I dedicate this thesis to you.

## **Table of Contents**

| Al            | ostra  | $\mathbf{v}$                                                                                                               | 'n |

|---------------|--------|----------------------------------------------------------------------------------------------------------------------------|----|

| A             | cknov  | $\mathbf{w} \mathbf{l} \mathbf{e} \mathbf{d} \mathbf{g} \mathbf{e} \mathbf{m} \mathbf{e} \mathbf{n} \mathbf{t} \mathbf{s}$ | ii |

| Τa            | able o | of Contents                                                                                                                | v  |

| $\mathbf{Li}$ | st Of  | f Figures                                                                                                                  | x  |

| $\mathbf{Li}$ | st of  | Tables    xxi                                                                                                              | ii |

| G             | lossa  | ry Of Terms                                                                                                                | ii |

| $\mathbf{Li}$ | st of  | $\mathbf{Symbols}$                                                                                                         | v  |

| 1             | Intr   | $\operatorname{roduction}$                                                                                                 | 1  |

|               | 1.1    | Background                                                                                                                 | 1  |

|               | 1.2    | Objectives                                                                                                                 | 3  |

|               | 1.3    | Thesis Structure                                                                                                           | 3  |

|               | 1.4    | Identification of Original Contributions                                                                                   | 5  |

|               | 1.5    | List of publications                                                                                                       | 6  |

| <b>2</b>      | Lite   | erature Review                                                                                                             | 8  |

|               | 2.1    | Topology selection                                                                                                         | 9  |

|               |        | 2.1.1 Generic Structure                                                                                                    | 9  |

|               |        | 2.1.2 Flyback Converters                                                                                                   | 0  |

|     | 2.1.3                                                       | Current fed Push-pull Converters                     | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|-------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 2.1.4                                                       | Bridge Converters                                    | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.1.5                                                       | Summary – Topology                                   | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.2 | Modul                                                       | lation                                               | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.2.1                                                       | Pulse Width Modulation                               | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.2.2                                                       | Block Modulation                                     | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

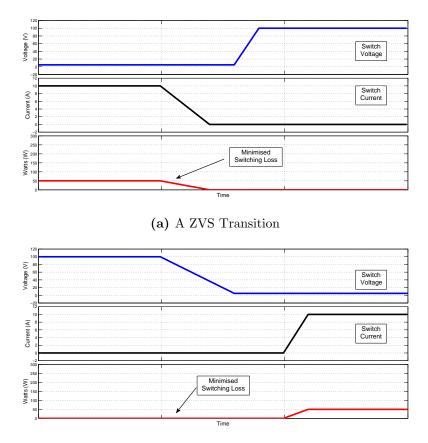

|     | 2.2.3                                                       | Soft-switching                                       | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.2.4                                                       | Summary – Modulation                                 | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.3 | Dynan                                                       | nic Modelling                                        | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.3.1                                                       | State Averaged Models                                | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.3.2                                                       | Fundamental Averaged Models                          | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.3.3                                                       | Non-ideal effects: Deadtime                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.3.4                                                       | Summary – Modelling                                  | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.4 | Closed                                                      | l loop Control                                       | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.4.1                                                       | Non-linear Control                                   | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.4.2                                                       | Linear Control                                       | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.4.3                                                       | Summary – Control                                    | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.5 | Conclu                                                      | usion                                                | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Con | verter                                                      | · Modelling                                          | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.1 | DAB (                                                       | Converter Principles of Operation                    | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.2 | DAB                                                         | Dynamic Equations                                    | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.3 | Derivi                                                      | ng the switching functions                           | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.4 | The C                                                       | Thoice of $N$                                        | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.5 | Harmo                                                       | onic Model Derivation                                | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.6 | Deadt                                                       | ime Compensation                                     | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 3.6.1                                                       | The Deadtime Effect                                  | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 3.6.2                                                       | Converter Behaviour During Deadtime                  | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.3<br>2.4<br>2.5<br>Con<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | <ul> <li>2.1.4 Bridge Converters.</li> <li>2.1.5 Summary – Topology</li> <li>2.2 Modulation</li> <li>2.2.1 Pulse Width Modulation</li> <li>2.2.2 Block Modulation</li> <li>2.2.3 Soft-switching</li> <li>2.2.4 Summary – Modulation</li> <li>2.3 Dynamic Modelling</li> <li>2.3.1 State Averaged Models</li> <li>2.3.2 Fundamental Averaged Models</li> <li>2.3.3 Non-ideal effects: Deadtime</li> <li>2.3.4 Summary – Modelling</li> <li>2.4 Closed loop Control</li> <li>2.4.1 Non-linear Control</li> <li>2.4.2 Linear Control</li> <li>2.4.3 Summary – Control</li> <li>2.4.3 Summary – Control</li> <li>2.4.3 Summary – Control</li> <li>2.4.3 Dynamic Equations</li> <li>3.4 DAB Converter Principles of Operation</li> <li>3.5 Harmonic Kodel Derivation</li> <li>3.6 Deadtime Compensation</li> <li>3.6.1 The Deadtime Effect</li> </ul> |

|          |     | 3.6.3  | Modelling the Deadtime effect                                        | 71  |

|----------|-----|--------|----------------------------------------------------------------------|-----|

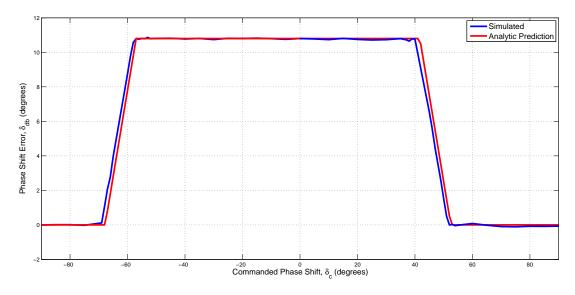

|          |     | 3.6.4  | Analytical calculation of the phase shift error effect $\ldots$ .    | 74  |

|          | 3.7 | Final  | Model Derivation & Validation                                        | 77  |

|          | 3.8 | Summ   | ary                                                                  | 77  |

| 4        | Clo | sed Lo | op Control                                                           | 79  |

|          | 4.1 | Choice | e of Feedback Controller                                             | 80  |

|          | 4.2 | The d  | igital modulator/PI controller & its performance limitations $\ .$ . | 83  |

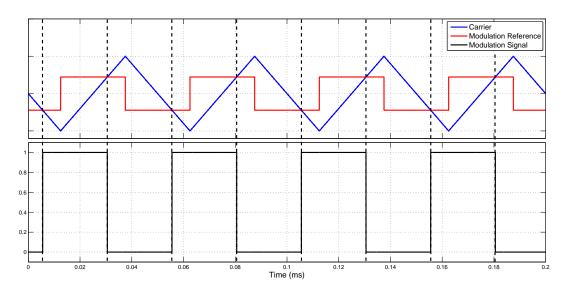

|          |     | 4.2.1  | The Digital Modulator                                                | 83  |

|          |     | 4.2.2  | The Digital PI Controller                                            | 84  |

|          | 4.3 | Delays | s in the Digital Implementation                                      | 85  |

|          |     | 4.3.1  | The Effect of Transport Delay                                        | 86  |

|          | 4.4 | Optim  | nising PI controller gains                                           | 87  |

|          | 4.5 | Load S | Step Performance                                                     | 92  |

|          |     | 4.5.1  | Exploring the load transient                                         | 93  |

|          |     | 4.5.2  | Disturbance Rejection                                                | 95  |

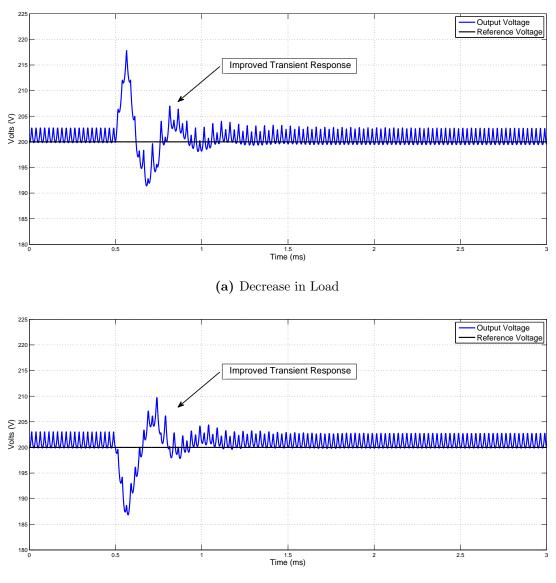

|          |     | 4.5.3  | Improvement in Load Transient Performance                            | 96  |

|          | 4.6 | Summ   | ary                                                                  | 98  |

| <b>5</b> | Sys | tem Pe | erformance with an AC Load                                           | 00  |

|          | 5.1 | Challe | enges of Smart Grid Converter Design                                 | 101 |

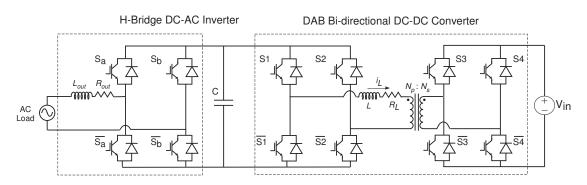

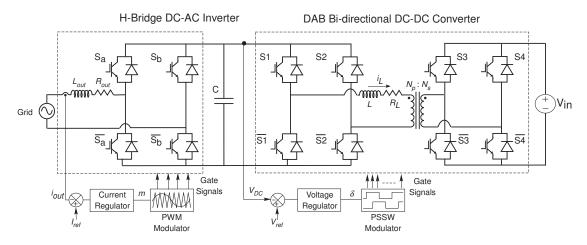

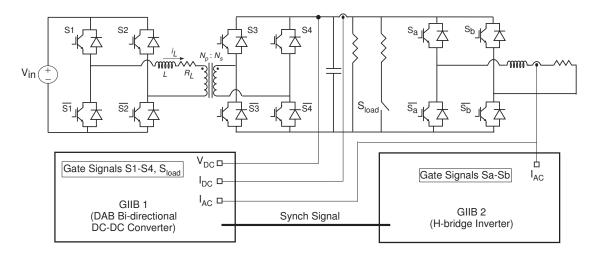

|          | 5.2 | Conve  | erter Principles of Operation                                        | .02 |

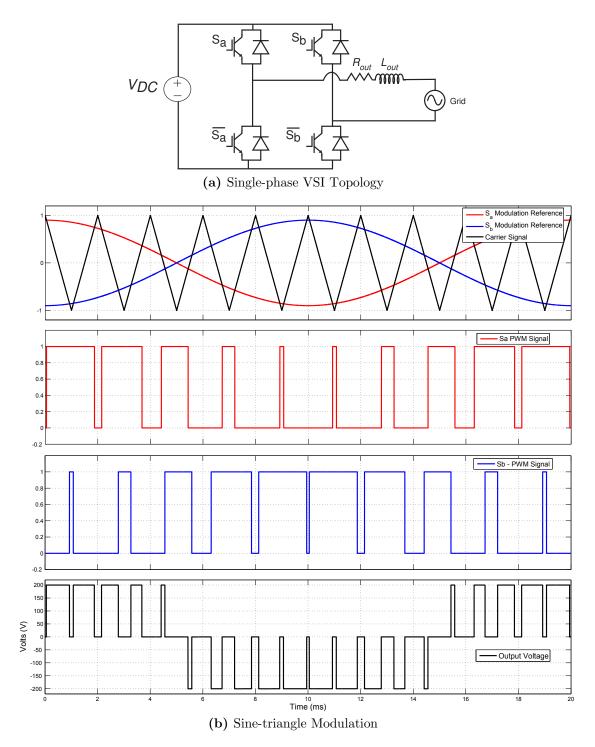

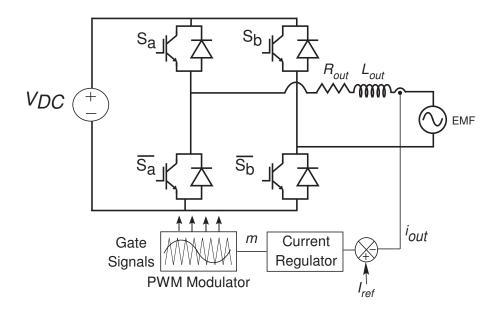

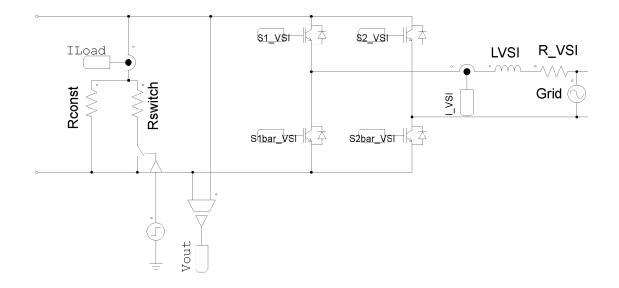

|          |     | 5.2.1  | Single-phase Voltage Source Inverter (VSI)                           | .02 |

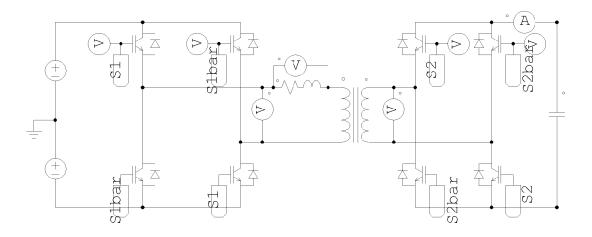

|          |     | 5.2.2  | DAB Bi-directional DC-DC Converter                                   | .05 |

|          | 5.3 | Closed | l loop controller design                                             | .05 |

|          |     | 5.3.1  | Choice of controller architecture                                    | .06 |

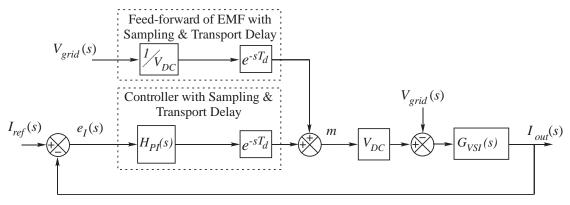

|          |     | 5.3.2  | VSI current regulator                                                | 107 |

|          |     | 5.3.3  | DAB voltage regulator                                                | 10  |

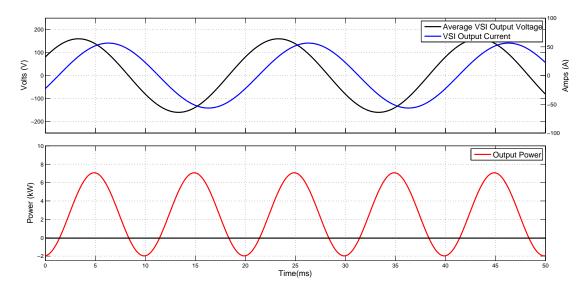

|          | 5.4 | Result | s1                                                                   | 14  |

|          | 5.5 | Summ   | ary                                                                  | 15  |

| 6 | $\mathbf{Des}$ | cription of Simulated & Experimental Systems |

|---|----------------|----------------------------------------------|

|   | 6.1            | Simulated Systems                            |

|   |                | 6.1.1 Overview                               |

|   |                | 6.1.2 Power Stage                            |

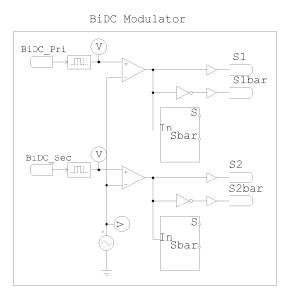

|   |                | 6.1.3 Modulators                             |

|   |                | 6.1.4 Controllers                            |

|   | 6.2            | Experimental Prototype                       |

|   |                | 6.2.1 Overview                               |

|   |                | 6.2.2 Power Stage                            |

|   |                | 6.2.3 Controller Hardware                    |

|   |                | 6.2.4 Inter-GIIB Communication               |

|   | 6.3            | Summary                                      |

| 7 | Sim            | ulation & Experimental Results               |

| • | 7.1            | Overview                                     |

|   | 7.2            | Steady-state Operating Waveforms             |

|   | 7.3            | Open Loop Transients   144                   |

|   | 7.4            | Closed Loop Transients                       |

|   |                | 7.4.1 Voltage Reference Step                 |

|   |                | 7.4.2 Load Change                            |

|   |                | 7.4.3       AC Load       151                |

|   | 7.5            | Summary                                      |

|   |                |                                              |

| 8 | Cor            | m nclusions                                  |

|   | 8.1            | Contributions                                |

|   |                | 8.1.1 Harmonic Model                         |

|   |                | 8.1.2 Deadtime Modelling                     |

|   |                | 8.1.3 Maximised controller gains             |

|   |                | 8.1.4 Adaptive controller gains              |

|       | 8.1.5                              | Improved Load Transient Response                                                                     |

|-------|------------------------------------|------------------------------------------------------------------------------------------------------|

|       | 8.1.6                              | AC Load Condition                                                                                    |

| 8.2   | Future                             | e Work                                                                                               |

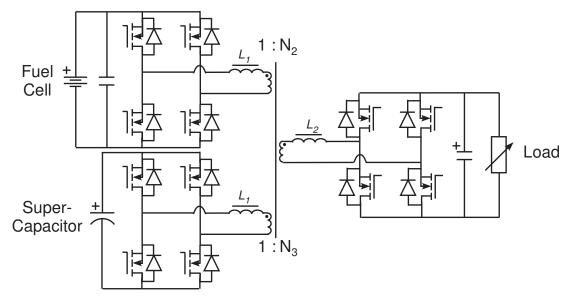

|       | 8.2.1                              | Multiport Converters                                                                                 |

|       | 8.2.2                              | Magnetics Design                                                                                     |

|       | 8.2.3                              | Extending the Harmonic Model                                                                         |

|       | 8.2.4                              | Controller Performance                                                                               |

| 8.3   | Closur                             | e                                                                                                    |

|       |                                    |                                                                                                      |

| Appen | dix A                              | Simulation & Experimental Code                                                                       |

|       |                                    |                                                                                                      |

| A.1   |                                    | ation Code                                                                                           |

|       | Simula                             | -                                                                                                    |

|       | Simula                             | ation Code $\ldots$ |

|       | Simula<br>Experi                   | ation Code                                                                                           |

|       | Simula<br>Experi<br>A.2.1<br>A.2.2 | ation Code                                                                                           |

## List of Figures

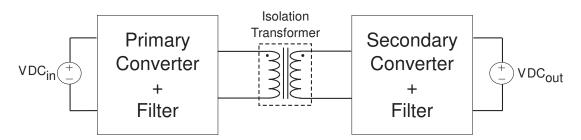

| 2.1  | The Generic Bi-directional DC-DC Converter Topology         | 9  |

|------|-------------------------------------------------------------|----|

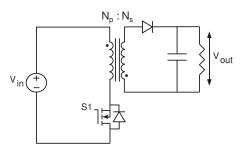

| 2.2  | A simple Flyback Converter                                  | 10 |

| 2.3  | Flyback Converter Operating Waveforms                       | 10 |

| 2.4  | The Actively Clamped Bi-directional Flyback Converter $[1]$ | 11 |

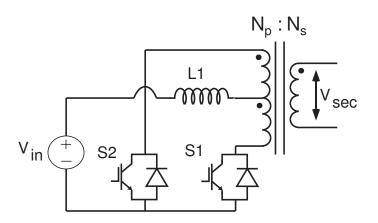

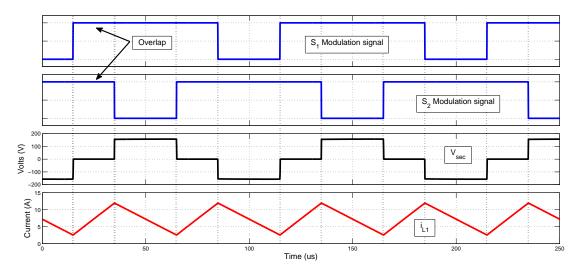

| 2.5  | A Current fed push-pull converter                           | 12 |

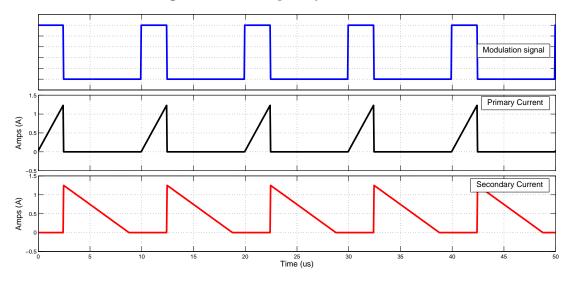

| 2.6  | CFPP Operating Waveforms                                    | 12 |

| 2.7  | Bi-directional CFPP                                         | 13 |

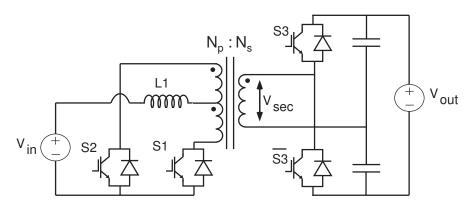

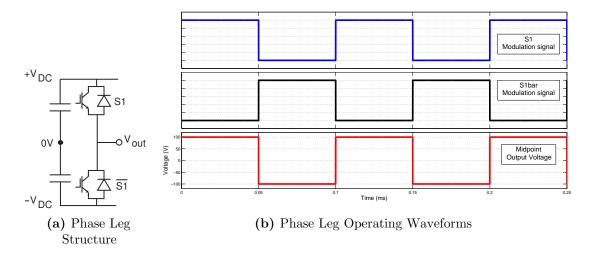

| 2.8  | Phase Leg Topology & Operating Waveforms                    | 14 |

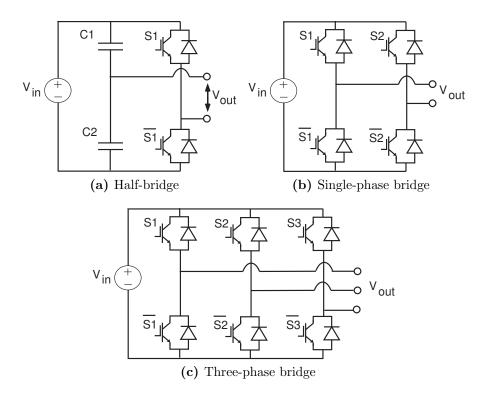

| 2.9  | Bridge Converter Topologies                                 | 15 |

| 2.10 | Bi-directional half-bridge                                  | 15 |

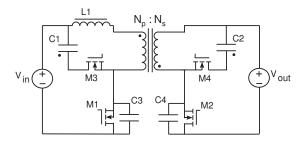

| 2.11 | Dual Active Bridge Converters                               | 16 |

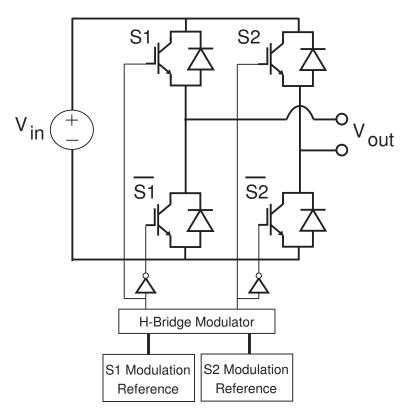

| 2.12 | H-bridge and Modulator                                      | 19 |

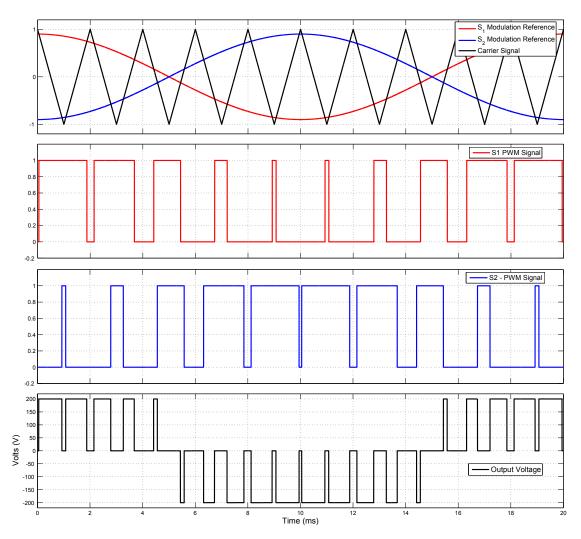

| 2.13 | Pulse Width Modulation                                      | 20 |

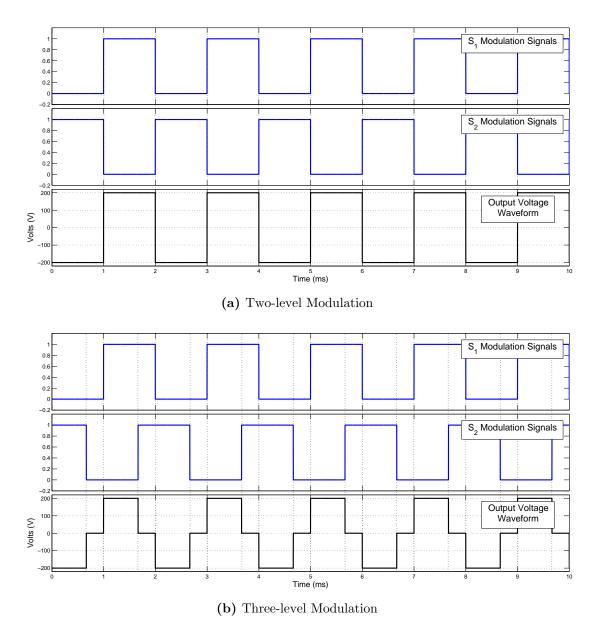

| 2.14 | Block Modulation                                            | 21 |

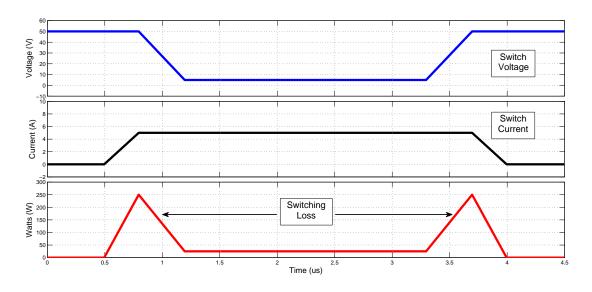

| 2.15 | Switching Loss                                              | 22 |

| 2.16 | Ideal Soft-switching Waveforms                              | 22 |

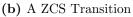

| 2.17 | Parallel Capacitance                                        | 23 |

| 2.18 | Active Clamp                                                | 24 |

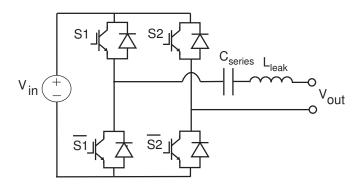

| 2.19 | Series Resonance                                            | 25 |

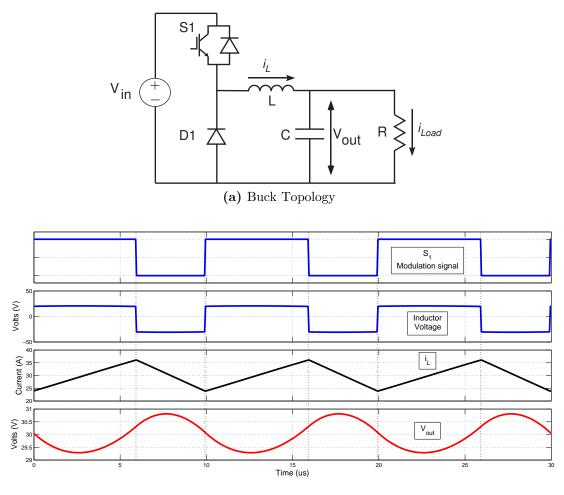

| 2.20 | Buck Converter                                              | 28 |

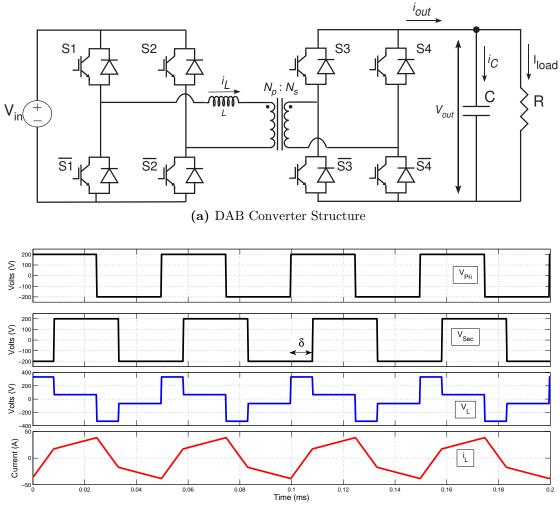

| 2.21 | The DAB Converter & Operating Waveforms                     | 31 |

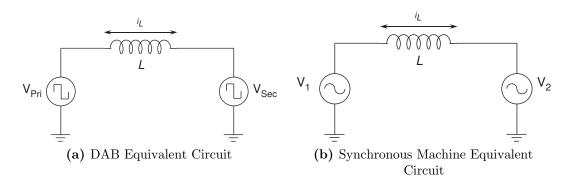

| 2.22 | DAB Equivalent Circuits                                                       | 32 |

|------|-------------------------------------------------------------------------------|----|

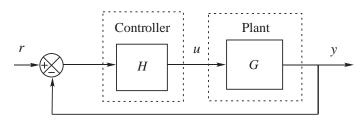

| 2.23 | A Basic Feedback Controller                                                   | 35 |

| 2.24 | Multiport                                                                     | 38 |

| 2.25 | DAB bi-directional DC-DC Converter                                            | 39 |

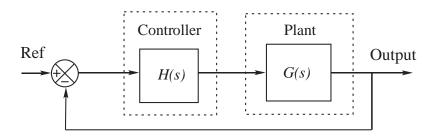

| 2.26 | Single-loop Feedback Controller                                               | 40 |

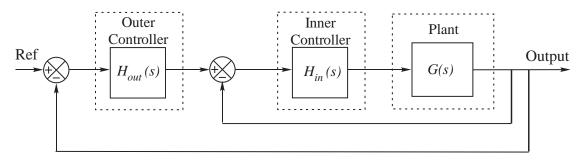

| 2.27 | Dual-loop Feedback Controller                                                 | 41 |

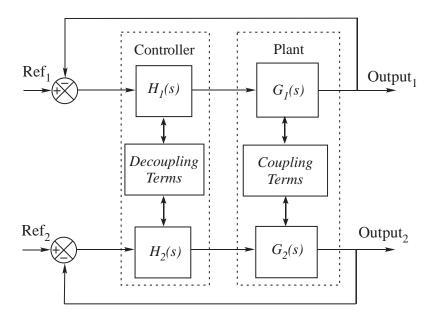

| 2.28 | Parallel-loop Feedback Controller [2]                                         | 41 |

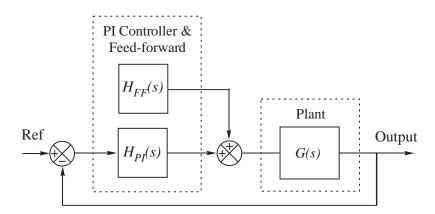

| 2.29 | PI Controller with Feed-forward                                               | 43 |

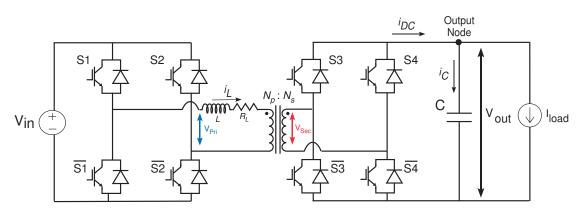

| 3.1  | The DAB Converter                                                             | 46 |

| 3.2  | Phase Leg Structure                                                           | 47 |

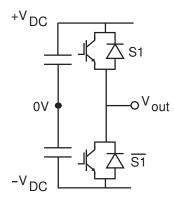

| 3.3  | Phase Leg Equivalent Circuits & Truth Table                                   | 47 |

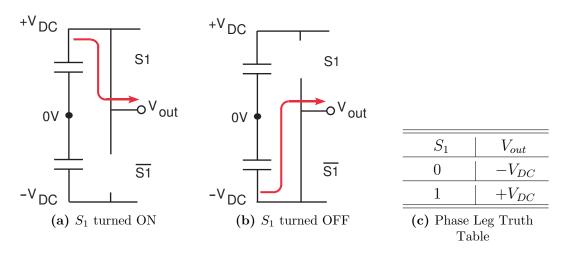

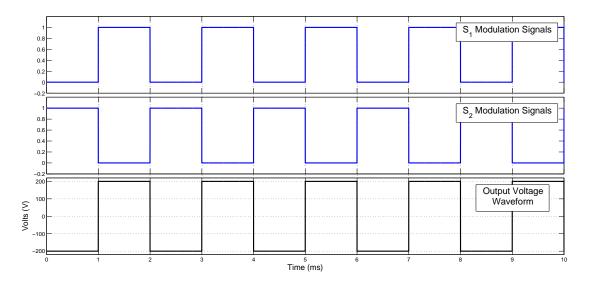

| 3.4  | H-bridge Converter & Truth table                                              | 48 |

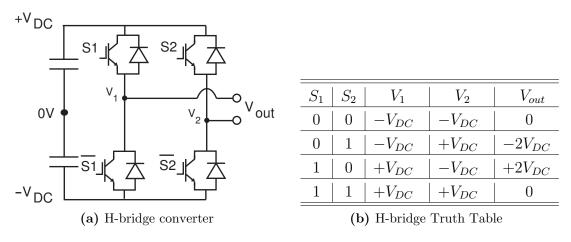

| 3.5  | H-bridge Operating Waveforms                                                  | 48 |

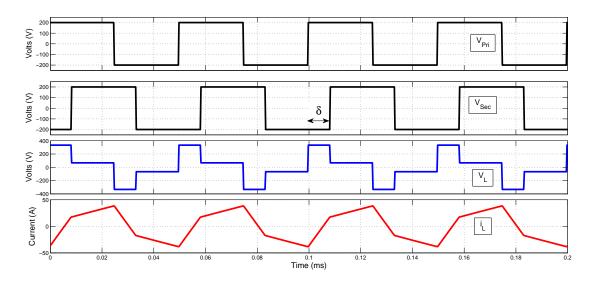

| 3.6  | DAB Operating Waveforms                                                       | 49 |

| 3.7  | KVL of the DAB Converter                                                      | 51 |

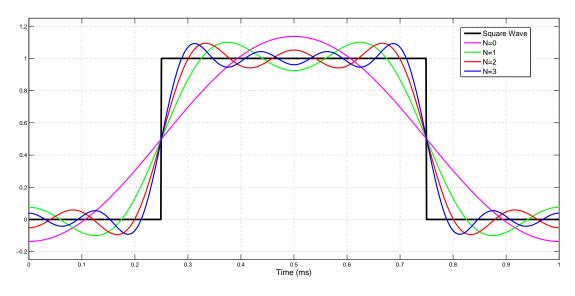

| 3.8  | Square Wave Harmonics                                                         | 53 |

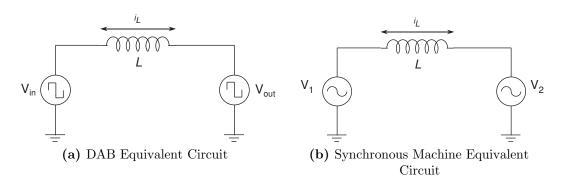

| 3.9  | DAB Converter Equivalent Circuits                                             | 54 |

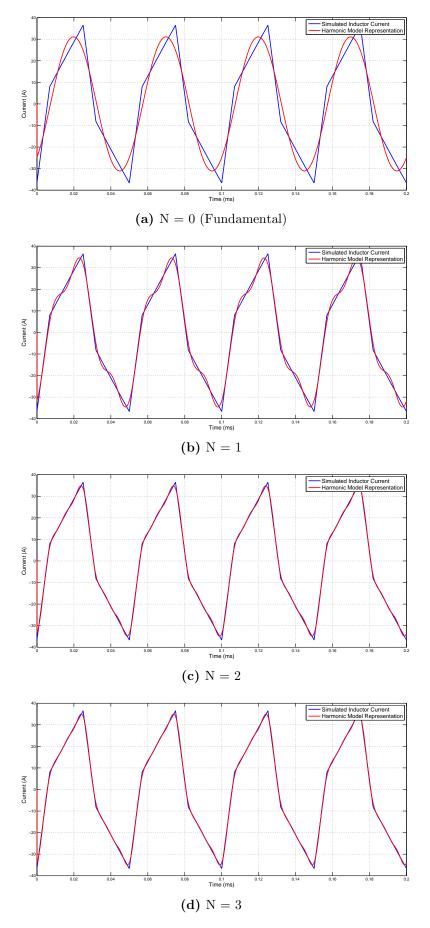

| 3.10 | Harmonic Model Verification: Inductor Current                                 | 59 |

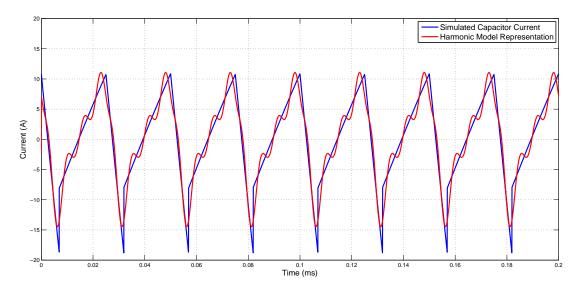

| 3.11 | Harmonic Model Verification: Capacitor Current $(N = 3)$                      | 60 |

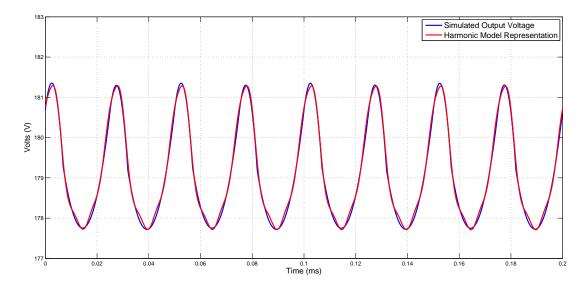

| 3.12 | Harmonic Model Verification: Steady-state Output Voltage $\left(N=3\right)$ . | 61 |

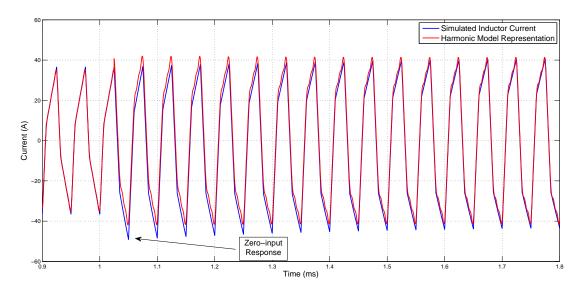

| 3.13 | Harmonic Model Verification: AC Inductor Current (Transient step)<br>(N = 3)  | 62 |

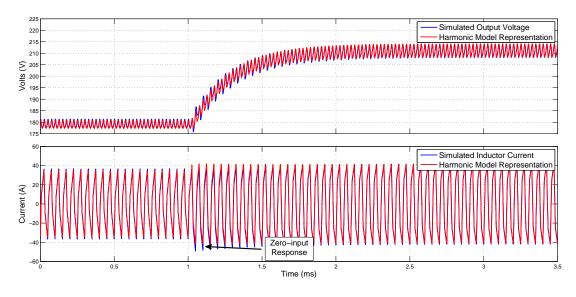

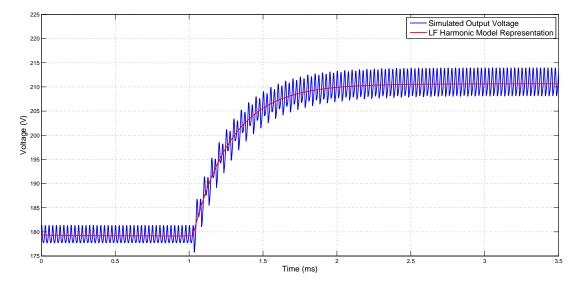

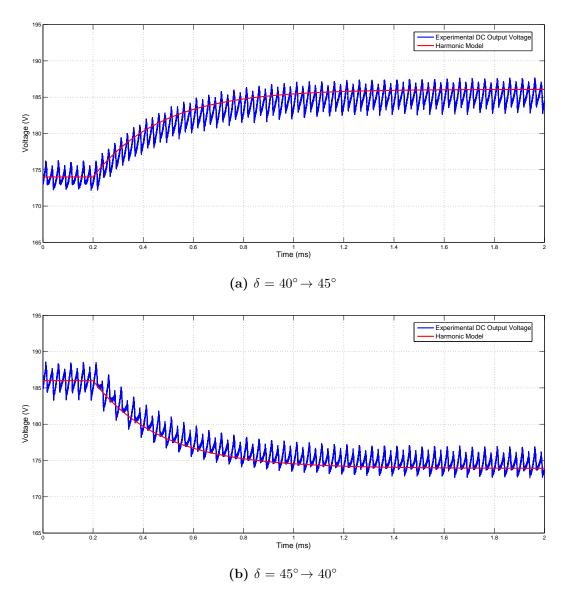

| 3.14 | Harmonic Model Verification: Output Voltage $(N = 3)$                         | 63 |

| 3.15 | Harmonic Model Verification: Output Voltage (DC Terms Only)<br>(N = 3)        | 64 |

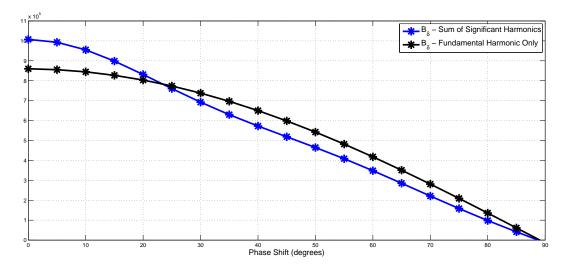

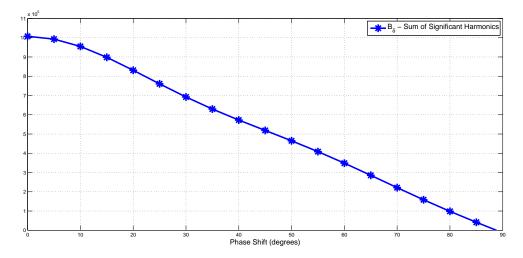

| 3.16 | Variation in $B_{\delta}$                                                     | 65 |

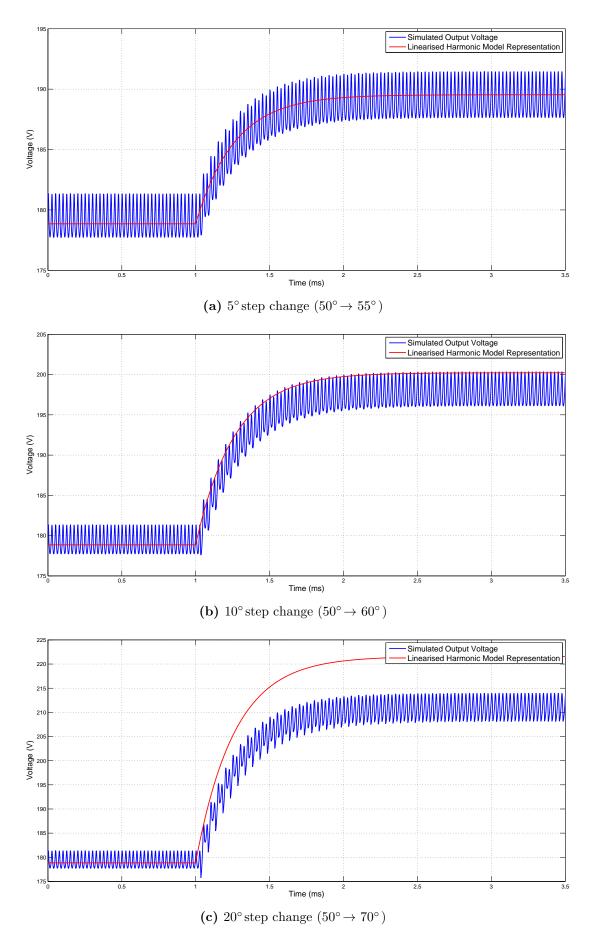

| 3.17 | Harmonic Model Verification: Output Voltage (Linearised Model)<br>(N = 3)     | 66 |

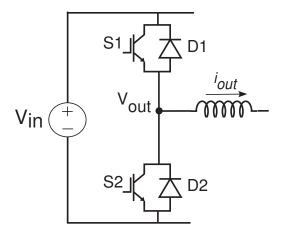

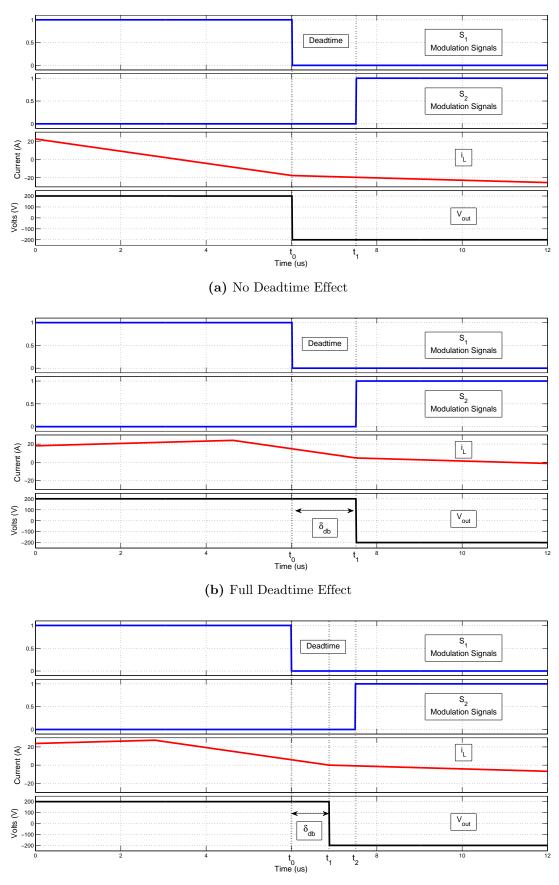

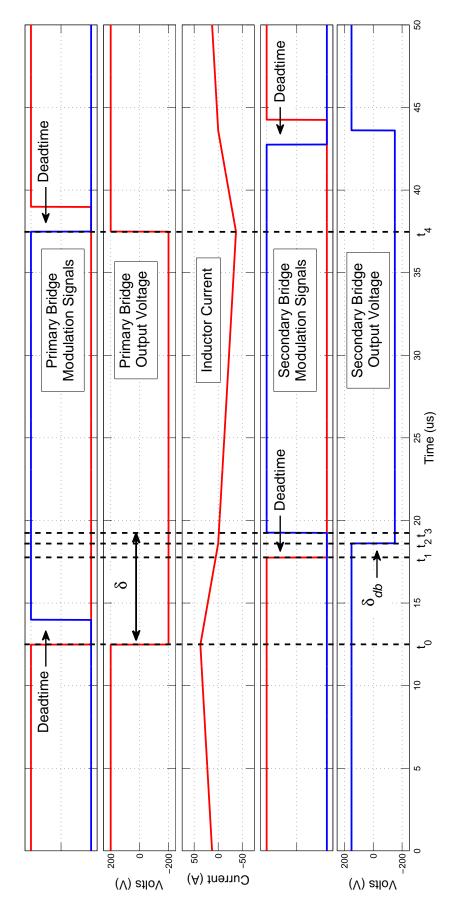

| 3.18 | Operating point dependence of the deadtime effect                                           | 68 |

|------|---------------------------------------------------------------------------------------------|----|

| 3.19 | Single Phase Leg with an Inductive Load                                                     | 69 |

| 3.20 | Deadtime Effect in a Phase Leg                                                              | 70 |

| 3.21 | Deadtime influence - HV bridge <i>lags</i> the LV bridge                                    | 72 |

| 3.22 | Deadtime influence - HV bridge <i>leads</i> the LV bridge                                   | 73 |

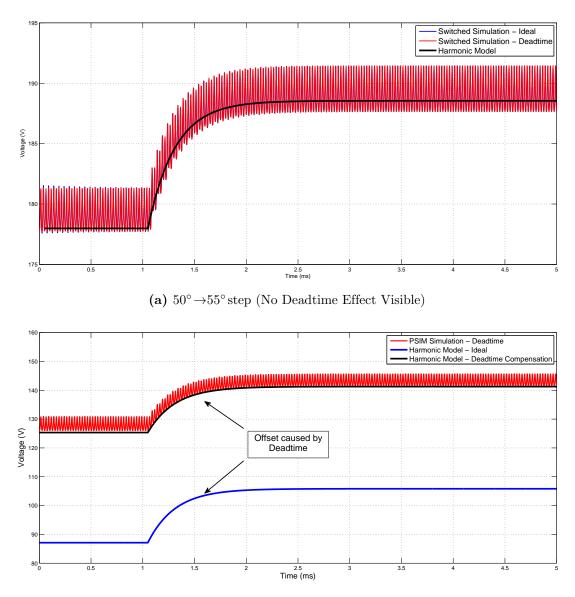

| 3.23 | Deadtime influence in the DAB converter                                                     | 77 |

| 3.24 | Block Diagram of Final Dynamic Model.                                                       | 77 |

| 3.25 | Validating the Final Model $(N = 3)$                                                        | 78 |

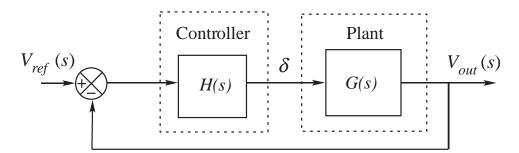

| 4.1  | Basic closed loop block diagram of the DAB converter.                                       | 80 |

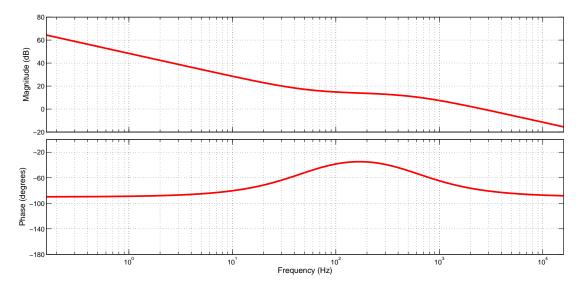

| 4.2  | Ideal Bode plot                                                                             | 82 |

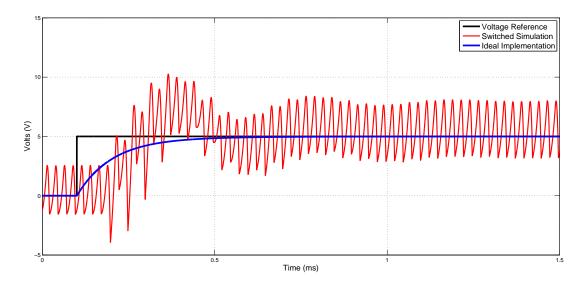

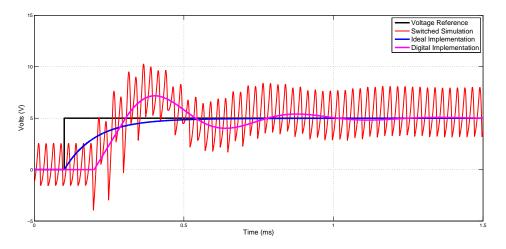

| 4.3  | Transient Responses of Ideal & Digital implementations                                      | 83 |

| 4.4  | Digital PSSW Modulator                                                                      | 84 |

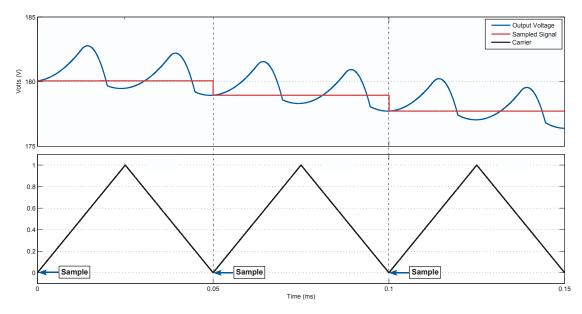

| 4.5  | Sample & Hold                                                                               | 85 |

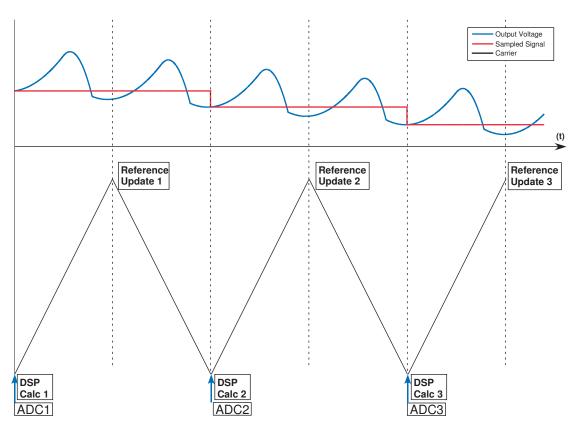

| 4.6  | Controller Calculation & Update                                                             | 86 |

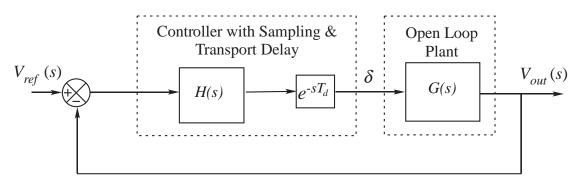

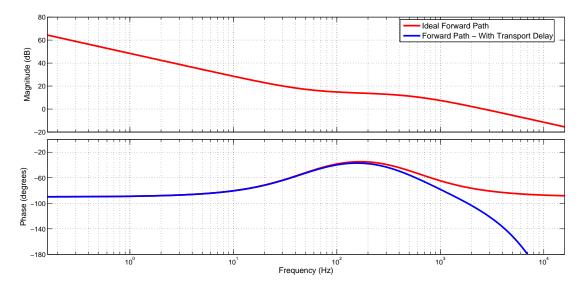

| 4.7  | Closed loop block diagram - Including Transport Delay                                       | 86 |

| 4.8  | Forward Path Bode Plot - Including Transport Delay.                                         | 87 |

| 4.9  | Linearised Transient Responses                                                              | 87 |

| 4.10 | $B_{\delta}$ term variation with operating phase shift $\ldots \ldots \ldots \ldots \ldots$ | 90 |

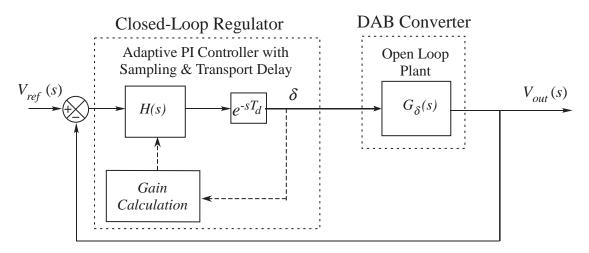

| 4.11 | Closed Loop Block diagram of the DAB converter with an Adaptive<br>PI controller            | 91 |

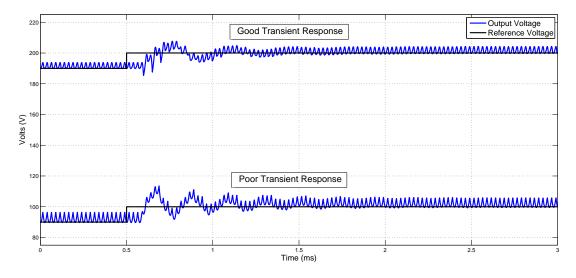

| 4.12 | Closed loop Step Response Comparison                                                        | 91 |

| 4.13 | Comparison of Load & Reference Transient Responses                                          | 92 |

| 4.14 | DAB Block Diagram (with Disturbance)                                                        | 94 |

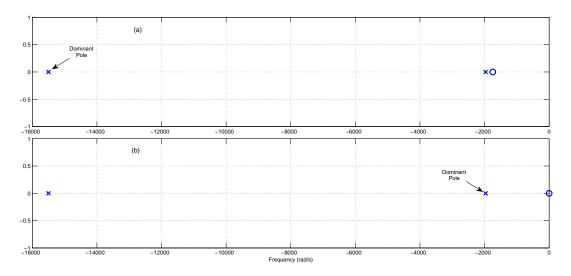

| 4.15 | Pole Zero map of Closed Loop Transfer Functions                                             | 94 |

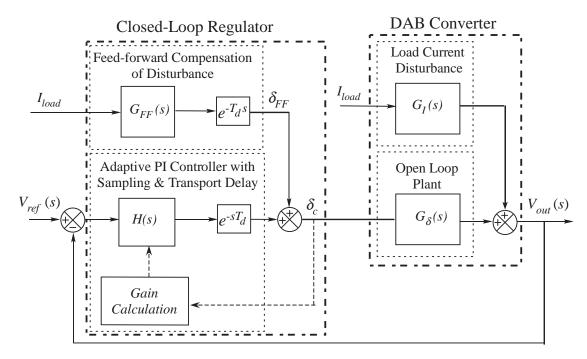

| 4.16 | DAB Closed Loop Block Diagram with Feed-forward                                             | 95 |

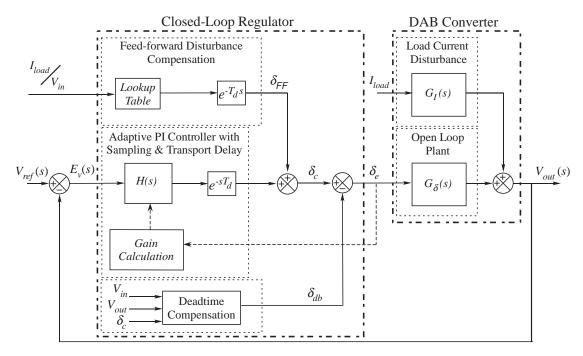

| 4.17 | Final Closed Loop Block Diagram of the DAB Converter                                        | 96 |

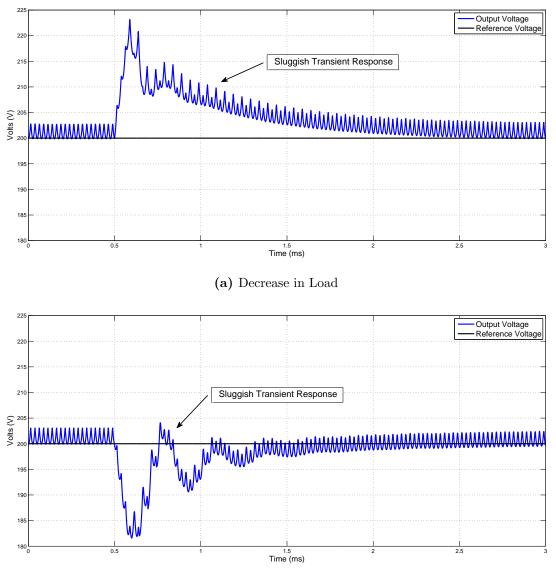

| 4.18 | Load Step Response - Without Feed-forward                                                   | 97 |

| 4.19 | Load Step Response - With Feed-forward                                                      | 99 |

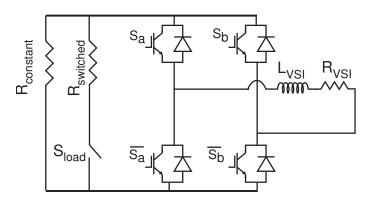

| 5.1  | AC-DC converter topology                                                                                                                                                                            |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2  | Single-phase VSI                                                                                                                                                                                    |

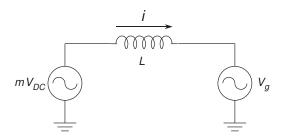

| 5.3  | Fundamental VSI model                                                                                                                                                                               |

| 5.4  | Fundamental VSI Power Flow                                                                                                                                                                          |

| 5.5  | Proposed Closed Loop DC-AC Converter Architecture                                                                                                                                                   |

| 5.6  | Structure of the Current Regulated VSI                                                                                                                                                              |

| 5.7  | Closed-loop block diagram of the Current Regulated VSI $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                                                     |

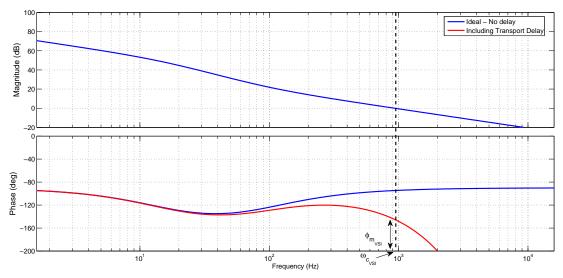

| 5.8  | Forward path Bode plot of the Current-regulated VSI                                                                                                                                                 |

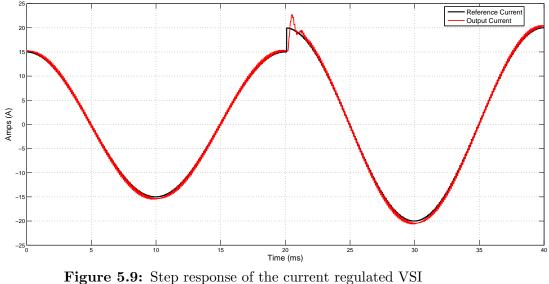

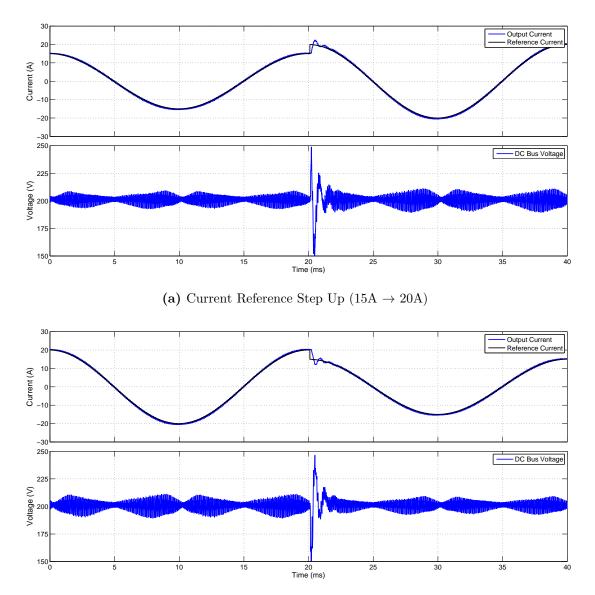

| 5.9  | Step response of the current regulated VSI $[15A \rightarrow 20A \text{ step}] \dots \dots$   |

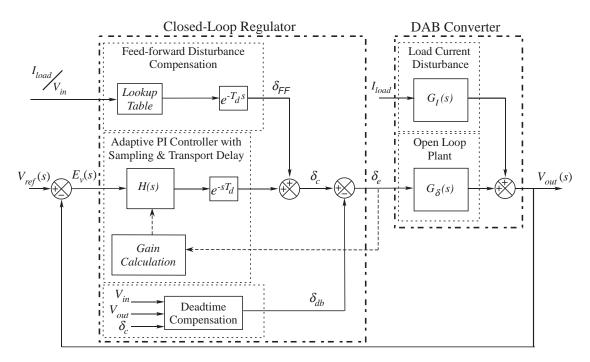

| 5.10 | Closed-loop block diagram of the Voltage Regulated DAB $\ .\ .\ .\ .$ . 110                                                                                                                         |

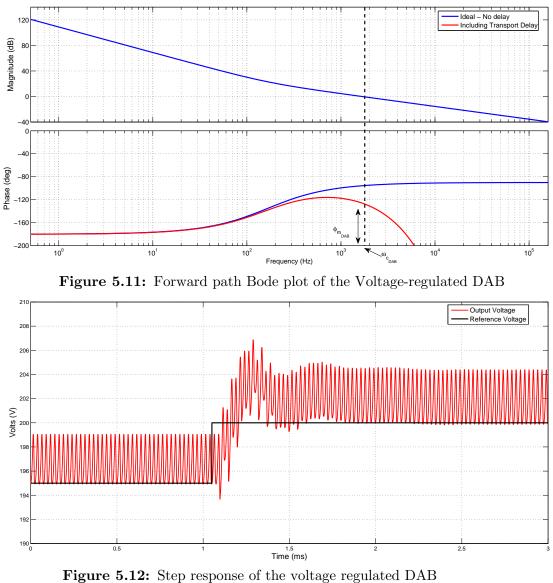

| 5.11 | Forward path Bode plot of the Voltage-regulated DAB                                                                                                                                                 |

| 5.12 | Step response of the voltage regulated DAB $[195V \rightarrow 200V \text{ step}] \dots \dots$ |

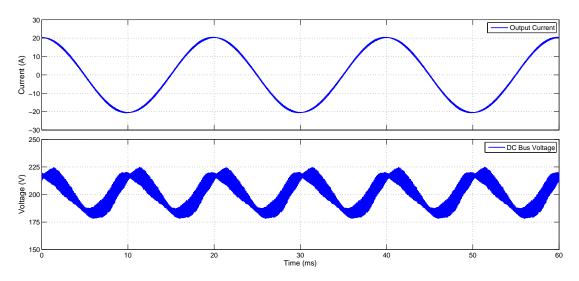

| 5.13 | AC Load - No Feed Forward                                                                                                                                                                           |

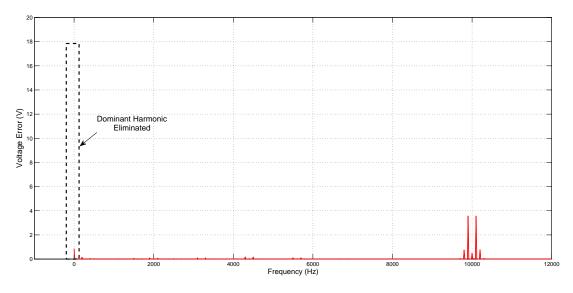

| 5.14 | Harmonic Spectrum - No Feed Forward                                                                                                                                                                 |

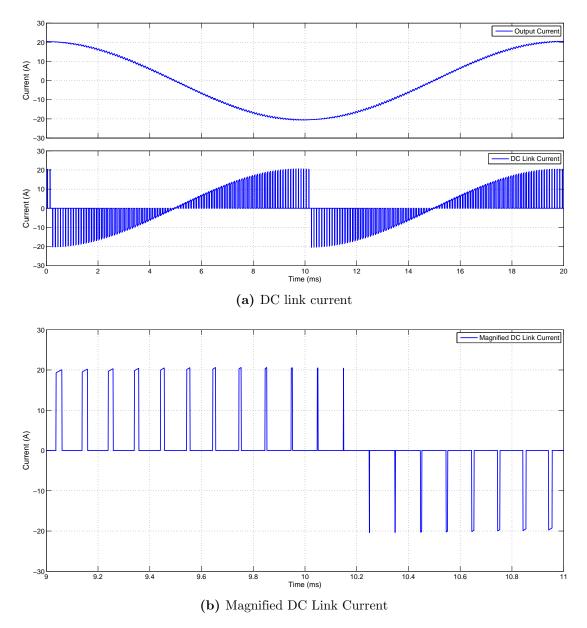

| 5.15 | DAB DC link current                                                                                                                                                                                 |

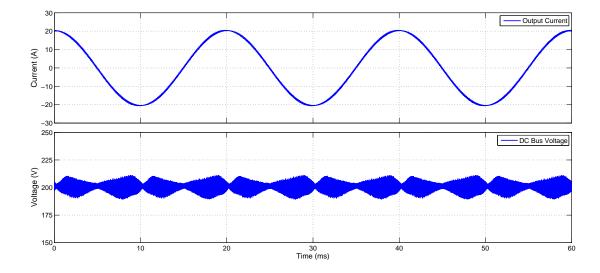

| 5.16 | AC Load - Feed Forward                                                                                                                                                                              |

| 5.17 | Harmonic Spectrum - Feed Forward                                                                                                                                                                    |

| 5.18 | Converter Transient Waveforms                                                                                                                                                                       |

| 6.1  | PSIM Power Stage - DAB Converter                                                                                                                                                                    |

| 6.2  | PSIM Power Stage - DAB Load                                                                                                                                                                         |

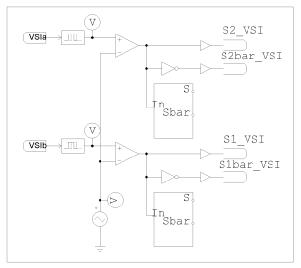

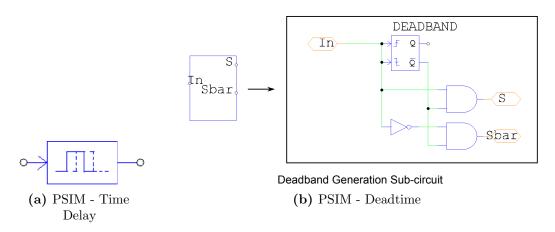

| 6.3  | PSIM - Modulators                                                                                                                                                                                   |

| 6.4  | Modulator Features                                                                                                                                                                                  |

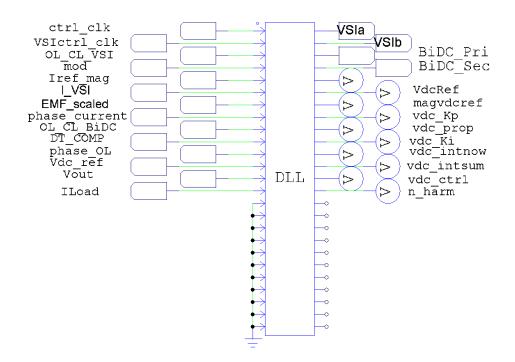

| 6.5  | PSIM Simulation - DLL Block                                                                                                                                                                         |

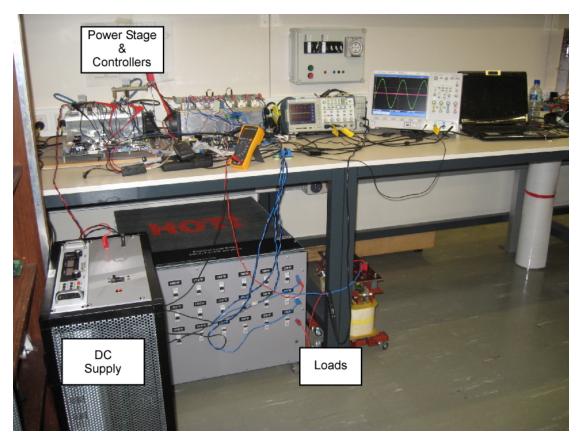

| 6.6  | Experimental Setup                                                                                                                                                                                  |

| 6.7  | Laboratory Setup                                                                                                                                                                                    |

| 6.8  | MagnaPower DC Supply                                                                                                                                                                                |

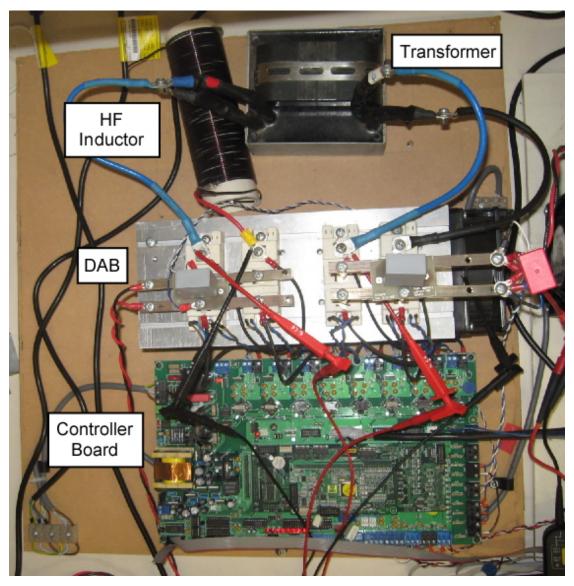

| 6.9                                                                                                                                            | Experimental DAB Converter                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

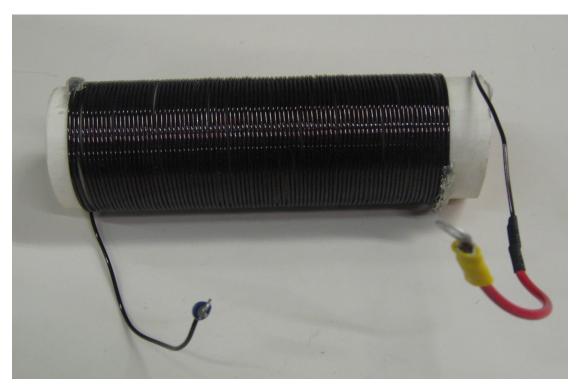

| 6.10                                                                                                                                           | Experimental High Frequency AC Inductor                                                                                                                                                                                                                                                          |

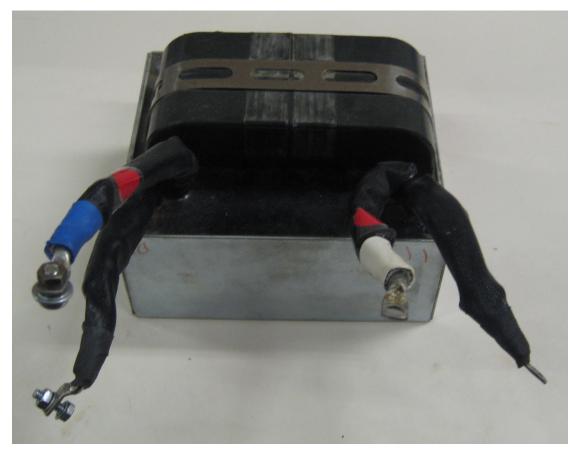

| 6.11                                                                                                                                           | Experimental High Frequency Transformer                                                                                                                                                                                                                                                          |

| 6.12                                                                                                                                           | Experimental Load Circuit Configuration                                                                                                                                                                                                                                                          |

| 6.13                                                                                                                                           | Experimental Load Elements                                                                                                                                                                                                                                                                       |

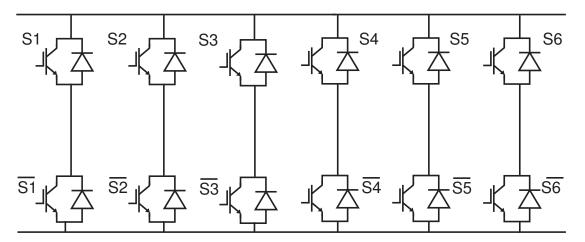

| 6.14                                                                                                                                           | 6 phase leg Circuit Diagram                                                                                                                                                                                                                                                                      |

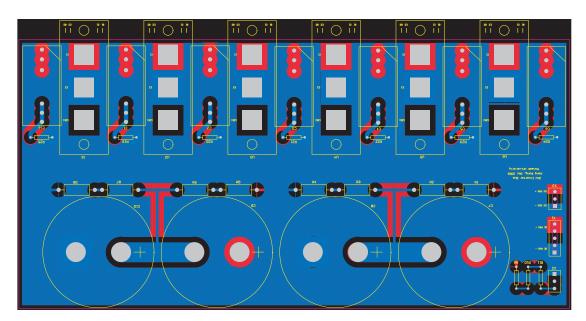

| 6.15                                                                                                                                           | PCB DC Bus Structure                                                                                                                                                                                                                                                                             |

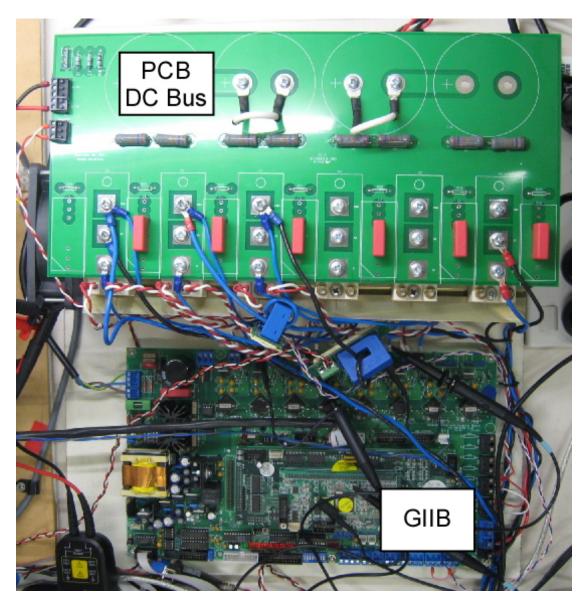

| 6.16                                                                                                                                           | Experimental 6 phase leg IGBT platform                                                                                                                                                                                                                                                           |

| 6.17                                                                                                                                           | DA2810 DSP Controller Board                                                                                                                                                                                                                                                                      |

| 6.18                                                                                                                                           | Mini2810 Controller Board                                                                                                                                                                                                                                                                        |

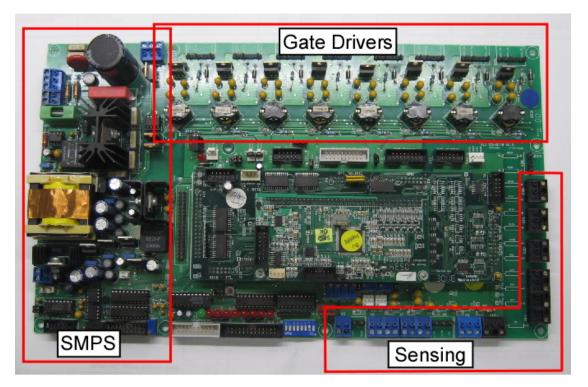

| 6.19                                                                                                                                           | GIIB Inverter Board                                                                                                                                                                                                                                                                              |

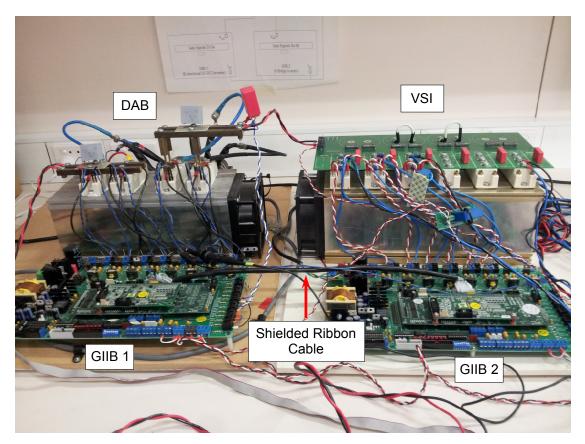

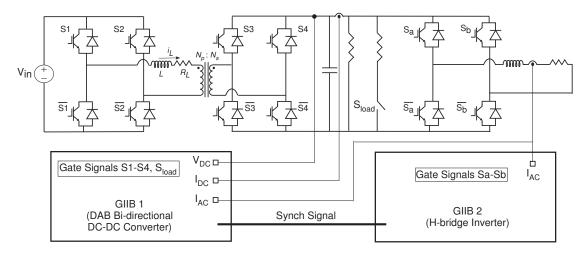

| 6.20                                                                                                                                           | Linked GIIB Boards                                                                                                                                                                                                                                                                               |

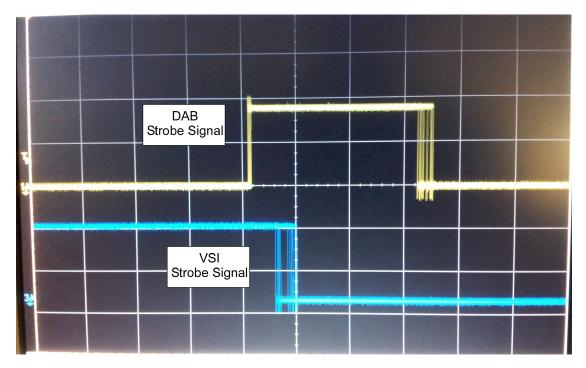

| 6.21                                                                                                                                           | Synchronisation                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                  |

| 7.1                                                                                                                                            | Experimental Setup                                                                                                                                                                                                                                                                               |

| 7.1<br>7.2                                                                                                                                     | Experimental Setup                                                                                                                                                                                                                                                                               |

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                  |

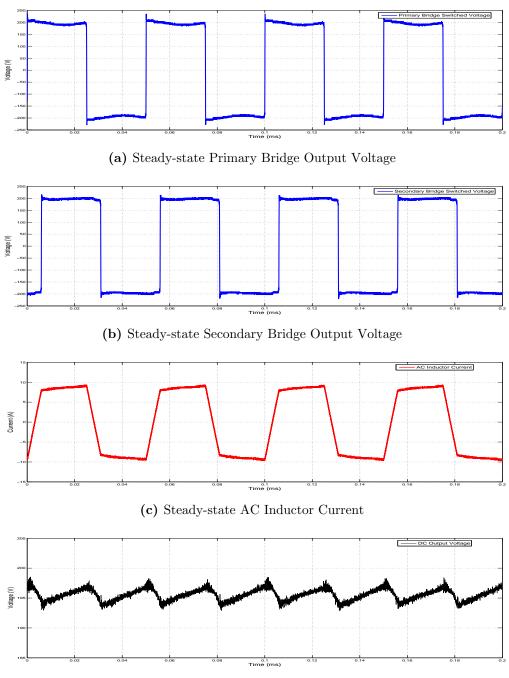

| 7.2                                                                                                                                            | DAB Steady State Operating Waveforms                                                                                                                                                                                                                                                             |

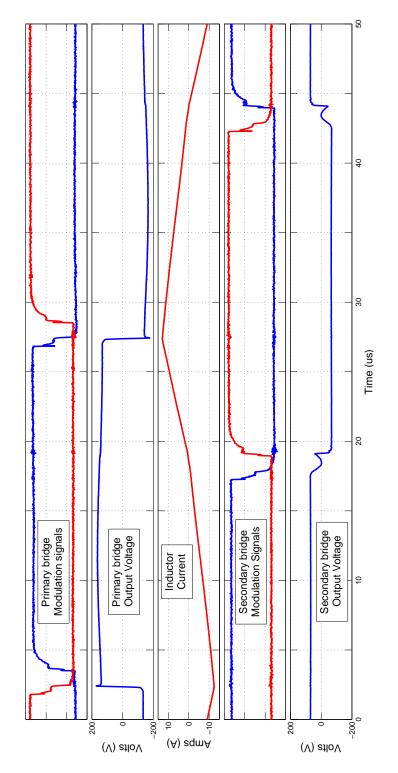

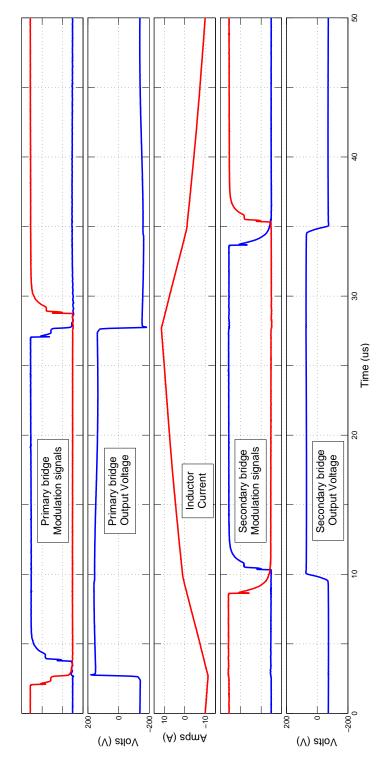

| 7.2<br>7.3                                                                                                                                     | DAB Steady State Operating Waveforms                                                                                                                                                                                                                                                             |

| <ul><li>7.2</li><li>7.3</li><li>7.4</li></ul>                                                                                                  | DAB Steady State Operating Waveforms       141         Deadtime Effect - HV bridge Lagging the LV bridge       142         Deadtime Effect - HV bridge Leading the LV bridge       143                                                                                                           |

| <ol> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> </ol>                                                                                 | DAB Steady State Operating Waveforms       141         Deadtime Effect - HV bridge Lagging the LV bridge       142         Deadtime Effect - HV bridge Leading the LV bridge       143         Open Loop: Deadtime       144                                                                     |

| <ol> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> </ol>                                                                    | DAB Steady State Operating Waveforms141Deadtime Effect - HV bridge Lagging the LV bridge142Deadtime Effect - HV bridge Leading the LV bridge143Open Loop: Deadtime144Open Loop: No Deadtime145                                                                                                   |

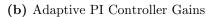

| <ol> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> </ol>                                                       | DAB Steady State Operating Waveforms       141         Deadtime Effect - HV bridge Lagging the LV bridge       142         Deadtime Effect - HV bridge Leading the LV bridge       143         Open Loop: Deadtime       144         Open Loop: No Deadtime       145         Fixed PI       147 |

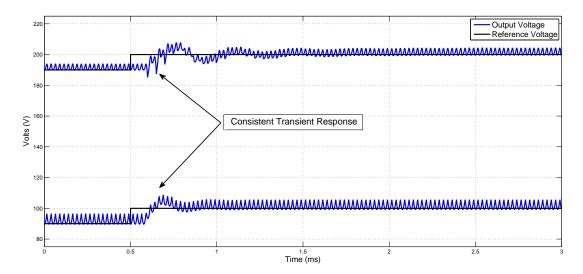

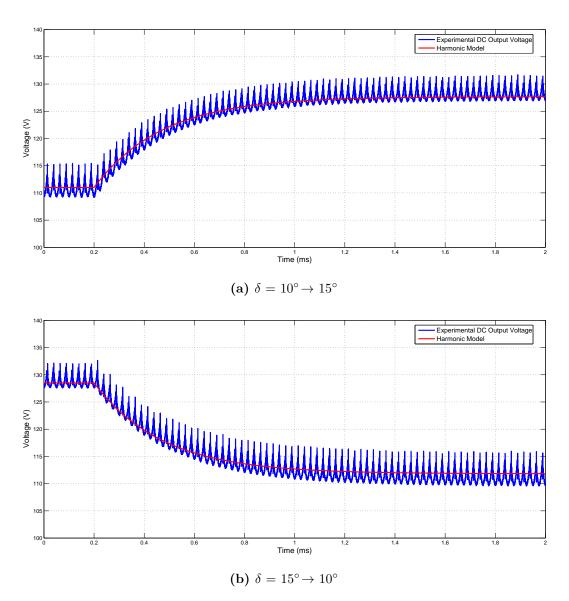

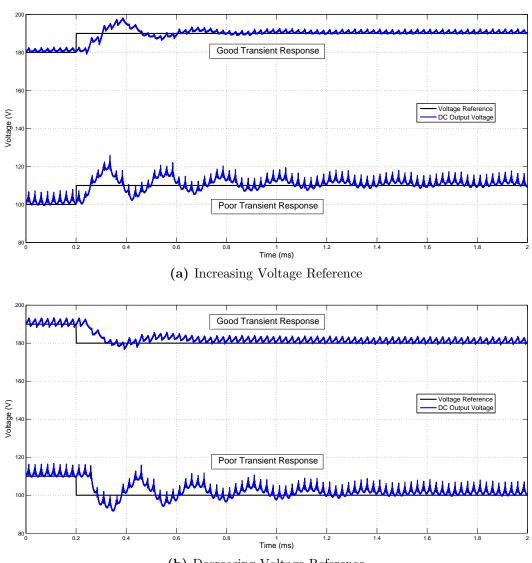

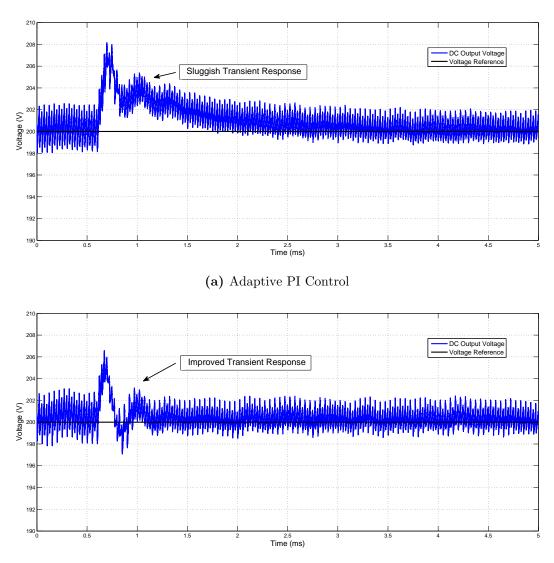

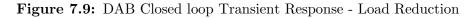

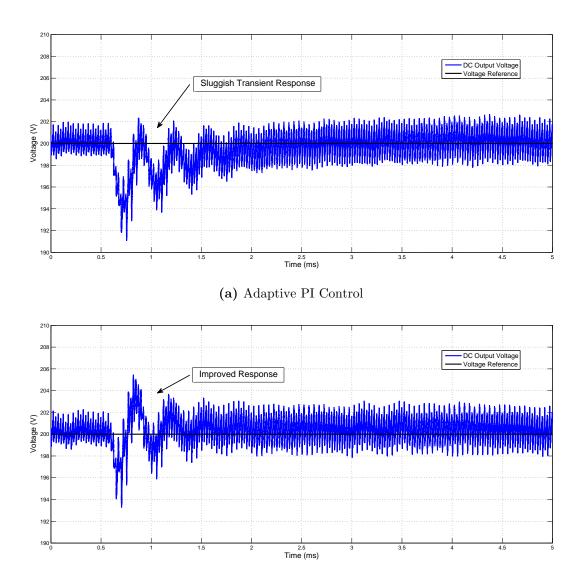

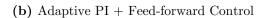

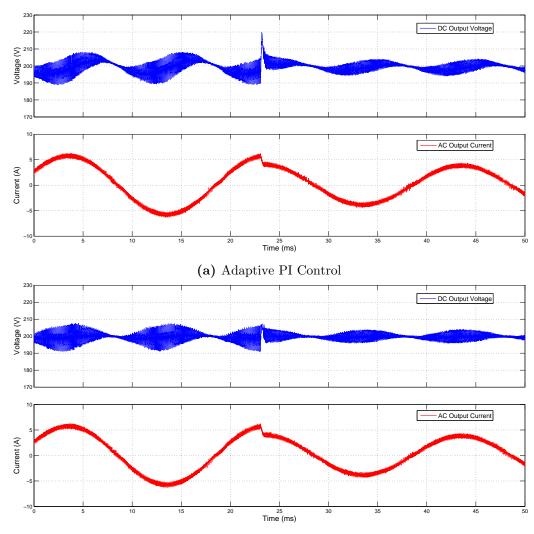

| <ol> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> </ol>                             | DAB Steady State Operating Waveforms141Deadtime Effect - HV bridge Lagging the LV bridge142Deadtime Effect - HV bridge Leading the LV bridge143Open Loop: Deadtime144Open Loop: No Deadtime145Fixed PI147Adaptive PI148                                                                          |

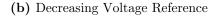

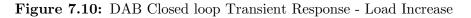

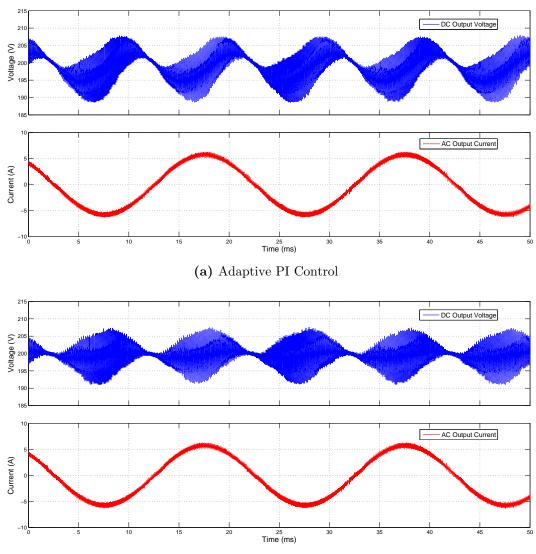

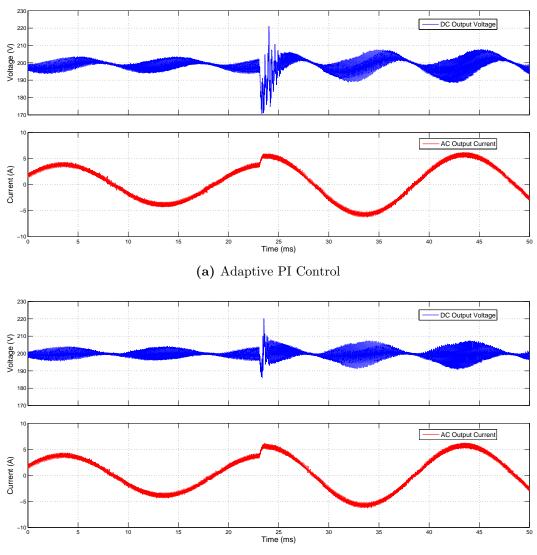

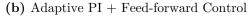

| <ol> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> <li>7.10</li> </ol>               | DAB Steady State Operating Waveforms141Deadtime Effect - HV bridge Lagging the LV bridge142Deadtime Effect - HV bridge Leading the LV bridge143Open Loop: Deadtime144Open Loop: No Deadtime145Fixed PI147Adaptive PI148Reducing Load149                                                          |

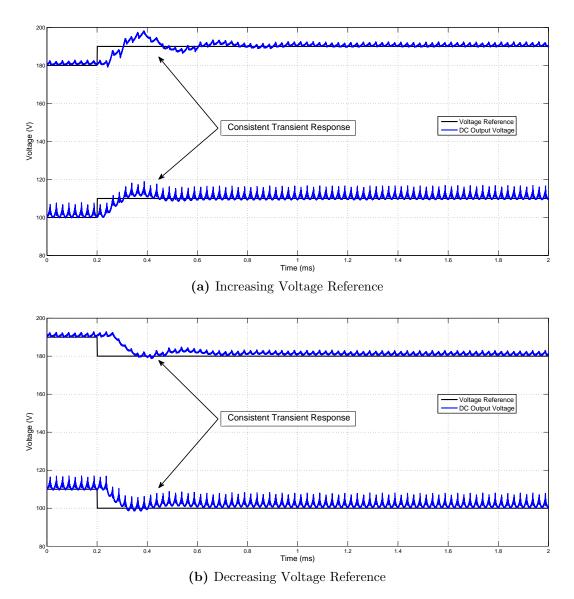

| <ol> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> <li>7.10</li> <li>7.11</li> </ol> | DAB Steady State Operating Waveforms141Deadtime Effect - HV bridge Lagging the LV bridge142Deadtime Effect - HV bridge Leading the LV bridge143Open Loop: Deadtime144Open Loop: No Deadtime145Fixed PI147Adaptive PI148Reducing Load149Increasing Load150                                        |

## List of Tables

| 2.1 | Converter Topology Comparison                                           | 18 |

|-----|-------------------------------------------------------------------------|----|

| 2.2 | State Averaged Models                                                   | 30 |

| 3.1 | DAB Converter Parameters                                                | 46 |

| 3.2 | Switched DC current $(i_{DC})$ based on output bridge switching state . | 50 |

| 3.3 | Choice of $N$                                                           | 56 |

| 3.4 | Piecewise Linear Inductor Current Solutions                             | 75 |

| 3.5 | Phase Shift Error Effect.                                               | 76 |

| 4.1 | DAB Converter PI Controller Parameters                                  | 90 |

| 5.1 | DC-AC Converter Parameters                                              | 07 |

| 5.2 | VSI Current Regulator Parameters                                        | 09 |

| 5.3 | DAB Voltage Regulator Controller Parameters                             | 10 |

| 6.1 | DAB Voltage Regulator Controller Parameters                             |    |

| 6.2 | DC-AC Experimental Converter Parameters                                 | 25 |

| 7.1 | DC-AC Experimental Converter Parameters                                 | 40 |

| 7.2 | DAB Voltage Regulator Controller Parameters                             | 46 |

| 7.3 | H-bridge Current Regulator Parameters                                   | 51 |

## **Glossary Of Terms**

| $\mathbf{AC}$                     | Alternating Current                               |

|-----------------------------------|---------------------------------------------------|

| ADC                               | Analog-to-Digital Converter                       |

| CFPP                              | Current Fed Push-pull                             |

| DAB                               | Dual Active Bridge                                |

| DAC                               | Digital-to-Analog Converter                       |

| $\mathbf{DC}$                     | Direct Current                                    |

| DHB                               | Dual Half Bridge                                  |

| DSP                               | Digital Signal Processor                          |

| $\mathbf{FC}$                     | Fuel Cell                                         |

| $\mathbf{HV}$                     | High Voltage                                      |

| IGBT                              | Insulated Gate Bipolar Transistor                 |

| JTAG                              | Controller board programming device               |

| KCL                               | Kirchoff's Current Law                            |

| $\mathbf{KVL}$                    | Kirchoff's Voltage Law                            |

| $\mathbf{LF}$                     | Low Frequency                                     |

| $\mathbf{LV}$                     | Low voltage                                       |

| MOSFET                            | Metal Oxide Semiconductor Field Effect Transistor |

| MISO                              | Multi Input Single Output                         |

| PCB                               | Printed Circuit Board                             |

| P-HEV                             | Plug-in Hybrid Electric Vehicle                   |

| PI                                | Proportional + Integral                           |

| PLL                               | Phase Lock Loop                                   |

| PSIM                              | PowerSim Switched Simulation package              |

| $\mathbf{PSSW}$                   | Phase-Shifted Square Waves                        |

| $\mathbf{PWM}$                    | Pulse Width Modulation                            |

| $\mathbf{Q}	ext{-}\mathbf{point}$ | Quiescent Point                                   |

| R-L                               | Resistive-Inductive                               |

| $\mathbf{RMS}$                    | Root Mean Square                                  |

| <b>RS-232</b>  | Serial Communication Protocol |

|----------------|-------------------------------|

| SC             | Supercapacitor                |

| SMPS           | Switchmode Power Supplies     |

| SPI            | Serial Peripheral Interface   |

| TAB            | Triple Active Bridge          |

| THD            | Total Harmonic Distortion     |

| $\mathbf{TTL}$ | Truth Table Logic             |

| UC             | Ultracapacitor                |

| UPS            | Uninterruptible Power Supply  |

| VSI            | Voltage Source Inverter       |

| ZCS            | Zero Current Switching        |

| ZIR            | Zero Impulse Response         |

| ZOH            | Zero Order Hold               |

| ZSR            | Zero State Response           |

| ZVS            | Zero Voltage Switching        |

|                |                               |

## List of Symbols

| $\alpha$                   | Relative phase angle                             |

|----------------------------|--------------------------------------------------|

| δ                          | Phase shift                                      |

| $\delta_0$                 | Phase shift Q-point                              |

| $\delta_c$                 | Commanded phase shift                            |

| $\delta_{db}$              | Phase shift error caused by deadtime             |

| $\delta_{DT}$              | Deadtime period in radians                       |

| $\delta_e$                 | Effective applied phase shift                    |

| $\delta_{FF}$              | Feed-forward command                             |

| $\phi_m$                   | Phase margin                                     |

| $\varphi_{z}\left[n ight]$ | Impedance angle at $n^{th}$ harmonic             |

| ω                          | Frequency expressed in rad/s                     |

| $\omega_c$                 | Controller bandwidth (in rad/s)                  |

| $\omega_s$                 | Switching frequency (in rad/s)                   |

| $a_n, b_n$                 | Fourier Series harmonic coefficients             |

| $A, B_{\delta}, B_I$       | State space coefficients                         |

| D                          | Duty Cycle                                       |

| G(s)                       | Laplace domain representation of open loop plant |

| H(s)                       | Laplace domain representation of regulator       |

| $i_{load}$                 | Load current                                     |

| $i_{load_0}$               | Load current Q-point                             |

| $K_p$                      | Proportional Gain                                |

| m                          | Modulation Depth                                 |

| n                          | Harmonic number                                  |

| N                          | Number of significant harmonics considered       |

| $\frac{N_p}{N_s}$          | Transformer turns ratio                          |

| $S_k$                      | Phase leg switch state                           |

|                            | i hase leg switch state                          |

| $S_{k}\left(t\right)$      | Time-domain representation of $S_k$              |

| $T_d$                           | Delay time                                      |