# Design and Analysis of Short Word Length DSP Systems for Mobile Communication

A Thesis Submitted in Fulfillment of the requirements for the Degree of Doctor of Philosophy

> **Tayab Din Memon** PgD, B.ENG

School of Electrical and Computer Engineering College of Science, Engineering and Health RMIT University June 2012

## Declaration

I certify that except where due acknowledgement has been made, the work is that of the author alone; that work has not been submitted previously, in whole or in part, to qualify for any other academic award; the content of the thesis is the result of work which has been carried out since the official commencement date of the approved research program; and any editorial work, paid or unpaid, carried out by a third party is acknowledged.

Signed: .....

Tayab Din Memon

Date:

#### Summary

In last decade, Short Word Length (SWL, often single-bit) processing has proved promising technique in the development of DSP applications with low complexity and high performance. Recently, many general purpose DSP applications such as Least Mean Squares-Like single-bit adaptive filter algorithms have been developed using this SWL technique and have been shown to achieve similar performance as multi-bit systems. The reported benefits of the SWL techniques include their intrinsic simplicity of operation, low power consumption and efficient hardware implementation.

A key function in SWL systems is sigma delta modulation ( $\Sigma\Delta M$ ) that operates at an over sampling ratio (OSR), in contrast to the Nyquist rate sampling typically used in conventional multi-bit systems. Using large over sampling ratios is one way to improve the noise performance of a system, although potentially at the cost of overall throughput.

To date, the analysis of SWL (or single-bit) DSP systems has tended to be performed using high-level tools such as MATLAB, with little work reported relating to their hardware implementation, particularly in Field Programmable Gate Arrays (FPGAs). Two primary areas of interest exist here. The first is the comparative behaviour of SWL and multi-bit systems exhibiting at equal spectral performance in terms of their relative area, power and throughput. Secondly, it remains to be determined how chip area-performance varies with varying OSR and bit-width of the hardware SWL system.

This thesis explores the hardware implementation of single-bit systems in FPGA using the design and implementation in VHDL of a single-bit ternary FIR-like filter as an illustrative example. The impact of varying OSR and bit-width of the SWL filter has been determined, and a comparison undertaken between the area-performance-power characteristics of the SWL FIR filter compared to its equivalent multi-bit filter. Further, an analysis of single-bit adaptive channel equalization in MATLAB has been performed, which is intended to support the design and development of efficient algorithm for single-bit channel equalization.

As the performance of FIR filters is chiefly determined by the throughput of their multiply-accumulate (MAC) stages, an efficient organization for the design and implementation of this block has been proposed and its area-performance characteristics analysed using commercial FPGA devices in Quartus-II<sup>®</sup> and ModelSim<sup>®</sup>. It has been found that SWL filters can achieve clock frequencies in the range of 400 MHz suitable to process, for example, a 6 MHz video signal at an OSR of 64. The proposed adder organization has been used as a baseline for further investigation into the comparison between single-bit FIR-like filters and their conventional multi-bit counterparts.

The proposed ternary filter structure has been merged with IIR re-modulator component and the design and implementation of the overall single-bit FIR filter has been explored in hardware in order to compare its power-area-performance characteristics with approximately equivalent multi-bit FIR filters. Both filters types were designed and simulated in pipelined and non-pipelined mode. In this set of simulations, varying OSR (32 - 256) was used to identify the area-performance-power analysis of two techniques. The simulation results show that single-bit FIR-like filter consistently outperforms the multi-bit technique in terms of its area, performance and power except at the highest filter orders analysed in this work. It was also found that increasing OSR increases SNR at the cost of higher chip-area.

The stability of the single-bit FIR-like filter mainly depends upon IIR remodulator due to its recursive nature. Thus, we have investigated the stability IIR remodulator and propose a new model using linear analysis and root locus approach that takes into account the widely accepted second order sigma-delta modulator state variable upper bounds. Using proposed model we have found new feedback parameters limits that is a key parameter in single-bit IIR remodulator stability analysis.

In the second stage of thesis, three encoding techniques called canonical signed digit (CSD), 2's complement, and Redundant Binary Signed Digit (RBSD) were designed and investigated on the basis of area-performance in FPGA at varying OSR. Simulation results show that CSD encoding technique does not offer any significant improvement as compared to 2's complement as in multi-bit domain. Whereas, RBSD occupies double the chip area than other two techniques and has poor performance.

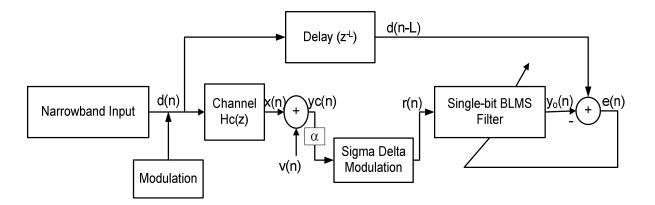

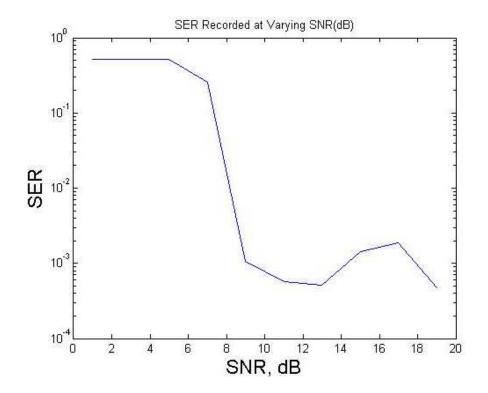

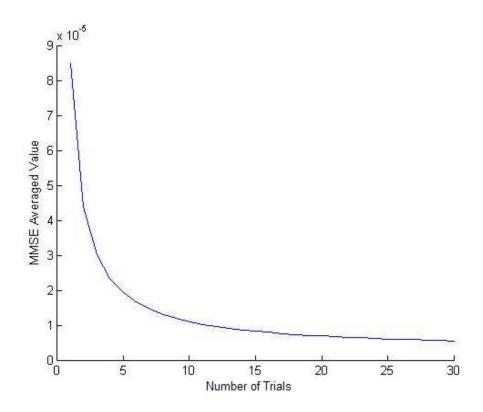

Finally, aspects of single-bit adaptive channel equalization, which is a key element in all the communication systems, have been analyzed. A new mathematical model has been derived with all inputs, coefficients and outputs in single-bit domain. The model was simulated using narrowband signals in MATLAB and investigated on the basis of symbol error rate (SER), signal-to-noise ratio (SNR) and minimum mean squared error (MMSE). The results indicate that single-bit adaptive channel equalization is achievable with narrowband signals but that the harsh quantization noise has great impact in the convergence.

# **Table of Contents**

| Summary                                                               | ii      |

|-----------------------------------------------------------------------|---------|

|                                                                       | iii     |

| Table of Contents                                                     | v       |

| List of Tables                                                        | viii    |

| List of Figures                                                       | ix      |

| Acknowledgments                                                       | xi      |

| Dedication                                                            | xii     |

| 1. Introduction                                                       | 1       |

| 1.1 Introduction                                                      | 1       |

| 1.2 Research Questions and Thesis Objectives                          | 3       |

| 1.2.1 Research Questions                                              | 3       |

| 1.2.2 Aims and objectives                                             |         |

| 1.3 Novel Contributions                                               | 4       |

| 1.1 Thesis Organization                                               | 6       |

|                                                                       |         |

| 2. Conventional and Single-bit FIR Filtering Techniques               | 8       |

|                                                                       |         |

| 2.1 Introduction                                                      |         |

| <ul><li>2.1 Introduction</li><li>2.2 Sigma-Delta Modulation</li></ul> | 8       |

|                                                                       | 8<br>14 |

| 2.2 Sigma-Delta Modulation                                            |         |

| <ul> <li>2.2 Sigma-Delta Modulation</li></ul>                         |         |

| 3. Po | wer-Area-Performance Characteristics of FPGA-based ΣΔ FIR                                              |      |

|-------|--------------------------------------------------------------------------------------------------------|------|

| Filte | rs                                                                                                     | 51   |

| 3.1   | Introduction                                                                                           | 51   |

| 3.2   | FIR Filter Design Techniques                                                                           | 53   |

| 3.3   | Single-Bit Ternary FIR-like filter                                                                     | 56   |

|       | 3.3.1 Ternary FIR Filter (TFF)                                                                         | 57   |

|       | 3.3.2 Generation of Ternary FIR filter in MATLAB                                                       | 59   |

| 2.4   | 3.3.3 IIR Re-modulator                                                                                 |      |

| 3.4   | FIR Filter Design in VHDL                                                                              |      |

|       | 3.4.1 Single-bit Ternary FIR-like Filter Hardware Implementation                                       |      |

|       | <ul><li>3.4.2 Ternary multiplier and adder modules</li><li>3.4.3 Multi-bit FIR filter design</li></ul> |      |

|       | 3.4.4 Spectral Performance Comparison                                                                  |      |

| 3.5   | Simulation Results and Discussion                                                                      | 69   |

|       | 3.5.1 Filter Area-Performance Analysis                                                                 | 69   |

|       | 3.5.2 Filter Power Analysis                                                                            |      |

| 3.6   | Stability Analysis of $\Sigma \Delta M$ Based Single-bit IIR Filter                                    | 79   |

| 3.7   | Stability of Single-bit Ternary FIR-like filter                                                        | 82   |

| 3.8   | Proposed Design of SBTFF                                                                               | 83   |

| 3.9   | Stability Analysis by Root Locus Technique                                                             | 86   |

| 3.10  | Simulation Results and Discussion                                                                      | 87   |

| 3.11  | Summary                                                                                                | 90   |

|       |                                                                                                        |      |

| 4. FF | PGA Analysis of Sigma-Delta Modulated Ternary FIR Filter with                                          |      |

| Alte  | rnative Encoding Techniques                                                                            | 93   |

| 4.1   | Introduction                                                                                           | 93   |

| 4.2   | The Ternary FIR Filter (TFF)                                                                           | 94   |

| 4.3   | Noise Shaping in Sigma-Delta Modulators                                                                | 95   |

|       | 4.3.1 Ternary Filter Design in MATLAB                                                                  | 98   |

| 4.4   | Ternary FIR Filter Design in FPGA                                                                      |      |

| 4.    | 4.1 Two's-complement                                                                                   |      |

|       | 4.4.2 Redundant Binary Signed Digit (RBSD) Representation                                              |      |

|       | 4.4.3 Canonical Signed Digit (CSD) Representation                                                      | .105 |

4.5 4.6

| <b>5. Si</b> | ngle-bit Ternary Adaptive Channel Equalization for Narrowband                                                                                                                   |     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Sign         | als                                                                                                                                                                             |     |

| 5.1          | Introduction                                                                                                                                                                    | 114 |

| 5.2          | System Design                                                                                                                                                                   | 120 |

| 5.3          | Single-bit ternary LMS-like Adaptive Channel Equalization Algorith 123                                                                                                          | m   |

| 5.4          | <ul><li>5.3.1 Wiener Theory and LMS algorithm</li></ul>                                                                                                                         | 127 |

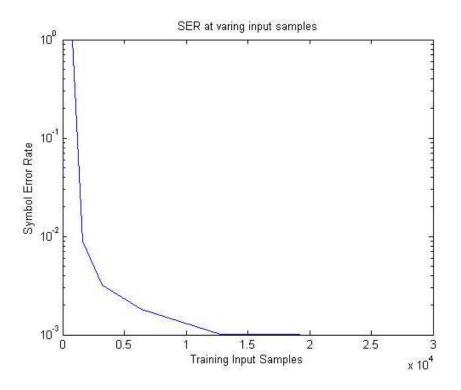

|              | <ul> <li>5.4.1 Symbol Error Rate (SER) at Varying input Training Samples</li> <li>5.4.2 Signal-to-Noise Ratio (SNR)</li> <li>5.4.3 Minimum Mean Squared Error (MMSE)</li> </ul> | 135 |

| 5.5          | Summary                                                                                                                                                                         |     |

| 6. Co        | onclusion and Future Directions                                                                                                                                                 | 140 |

| 6.1          | Introduction                                                                                                                                                                    | 140 |

| 6.2          | Future Directions                                                                                                                                                               | 145 |

# List of Tables

| Table 3.1 | Signal-to-Noise Ratio Comparison of Single-bit and Multi-bit FIR                  |      |

|-----------|-----------------------------------------------------------------------------------|------|

|           | Filter                                                                            | . 67 |

| Table 3.2 | Area-Performance comparison of single-bit FIR vs. multi-bit filter:               |      |

|           | non- pipelined Mode                                                               | . 71 |

| Table 3.3 | Area-Performance Comparison of Single-bit FIR vs. multi-bit Filter                |      |

|           | pipelined Mode                                                                    | . 71 |

| Table 3.4 | Clock Frequency for Ternary and Multi-bit Filters pipelined and                   |      |

|           | non-pipelined modes                                                               | . 75 |

| Table 3.5 | Dynamic Power Dissipation: F <sub>MAX</sub> Process.                              | . 78 |

| Table 3.6 | Dynamic Power Dissipation: F <sub>8K</sub> Process                                | . 79 |

| Table 5.1 | : IIR loop stability analysis using root locus with varying quantizer             |      |

|           | gain ( $\gamma$ ) and feedback loop gain ( $\alpha$ ) parameters with and without |      |

|           | proposed design                                                                   | . 89 |

| Table 5.1 | Improvement in the $SNR_o$ recorded with varying input $SNR_i$                    | 138  |

|           |                                                                                   |      |

# **List of Figures**

| Figure 2.1 General structure of FIR filter |                                                                                     | 9    |

|--------------------------------------------|-------------------------------------------------------------------------------------|------|

| Figure 2.2 B                               | lock Diagram of an IIR direct form II filter                                        | 10   |

| Figure 2.3 G                               | eneral diagram of the sigma-delta modulator                                         | 16   |

| Figure 2.4 L                               | inear Model of Quantizer                                                            | . 19 |

| Figure 2.5 F                               | irst Order Sigma-Delta Modulator Topology                                           | . 22 |

| Figure 2.6 F                               | irst Order Sigma-Delta Modulator Topology with Loop Filter                          |      |

| S                                          | pecified                                                                            | . 25 |

| Figure 2.7 N                               | TF at $1 - 3^{rd}$ orders of the sigma-delta modulator                              | . 26 |

| Figure 2.8 B                               | lock diagram of the error feedback $\Sigma\Delta M$ for requantization              | 31   |

| Figure 2.9 B                               | lock diagram of the FIR filter with $\Sigma\Delta M$ modulated filter               |      |

| C                                          | pefficients                                                                         | . 32 |

| Figure 2.10                                | Block diagram of the decoder used in FIR filter with                                |      |

| Σ                                          | $\Delta M$ modulated filter coefficients and with $\Sigma \Delta M$ modulated input |      |

| si                                         | gnal                                                                                | . 32 |

| Figure 2.11                                | Block diagram of the FIR filter with $\Sigma\Delta M$ modulated input signal        | 33   |

| Figure 2.12                                | Block diagram of the single-bit FIR filter                                          | . 37 |

| Figure 2.13                                | Block diagram of the first order single-bit IIR filter                              | . 38 |

| Figure 2.14                                | General bock diagram of the single-bit ternary FIR filter                           | . 40 |

| Figure 2.15                                | Single-bit narrowband bandpass FIR filter                                           | . 40 |

| Figure 2.16                                | First order digital sigma-delta modulator[50]                                       | . 44 |

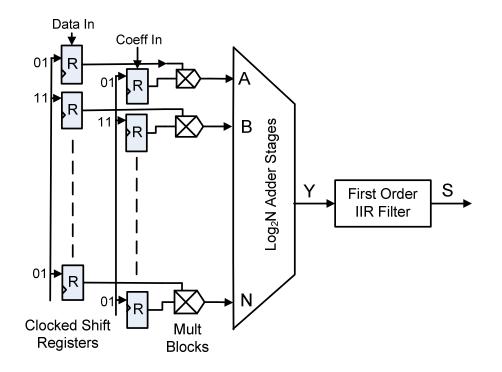

| Figure 3.1 G                               | eneral Block Diagram of Single-bit FIR filter structure (adapted                    |      |

| fr                                         | om [7])                                                                             | 54   |

| Figure 3.2 B                               | lock diagram of Ternary FIR filter (adapted from [11])                              | 54   |

| Figure 3.3 S                               | econd Order $\Sigma \Delta M$ architecture                                          | . 55 |

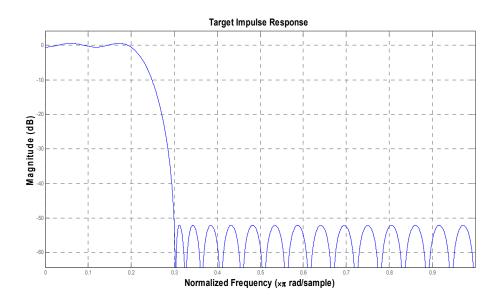

| Figure 3.4 T                               | arget Impulse Response by Remez Exchange Algorithm                                  | . 60 |

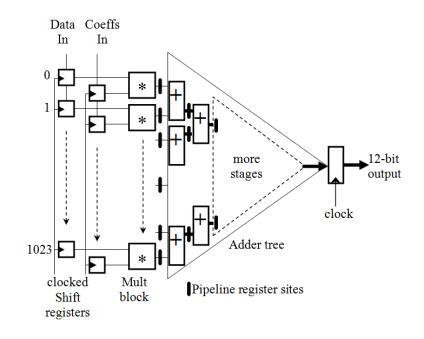

| Figure 3.5 Bl             | ock Diagram of SBTFF in Hardware                                    | 63   |

|---------------------------|---------------------------------------------------------------------|------|

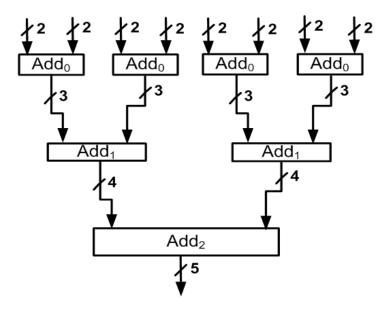

| Figure 3.6 Tw             | vo Level Fragment of the Adder Tree Structure                       | 65   |

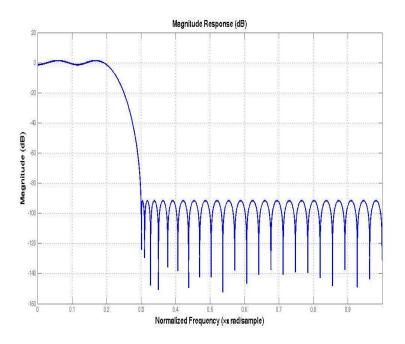

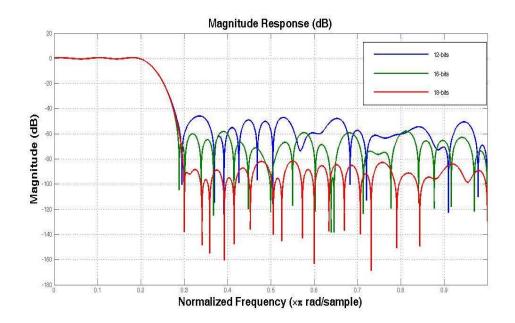

| Figure 3.7 Fre            | equency Response of the Target Filter at various coefficients bit-  |      |

| wi                        | dths (=12, 16 and 18)                                               | 65   |

| Figure 3.8 Pro            | oposed single-bit ternary filter with a gain factor inside the loop | . 81 |

| Figure 3.9 $\Sigma\Delta$ | M quantizer input $g_2(k)$ at sinusoidal excitation                 | . 84 |

| Figure 3.10               | Linear Model of the $2^{nd}$ order $\Sigma \Delta M$                | 88   |

| Figure 3.11 Ro            | oot Locus Plots with and without gain factor $(\phi)$               | . 90 |

| Figure 4.1 Blo            | ock diagram of Ternary FIR filter (adapted from [11])               | . 95 |

| Figure 4.2 Lin            | near Model of Quantizer                                             | . 97 |

| Figure 4.3 Ta             | rget Impulse Response of FIR filter                                 | . 99 |

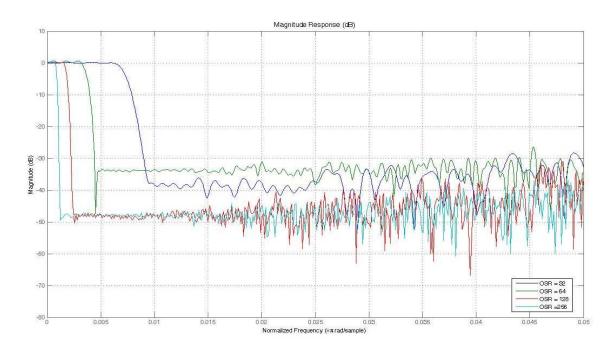

| Figure 4.4 Te             | rnary Filter Impulse Response at OSR = 32, 64,128 and 256           | . 99 |

| Figure 4.5 Fre            | equency Response of a Ternary FIR Filter                            | 100  |

| Figure 4.6 TF             | F hardware architecture                                             | 101  |

| Figure 4.7 RE             | 3SD addition                                                        | 104  |

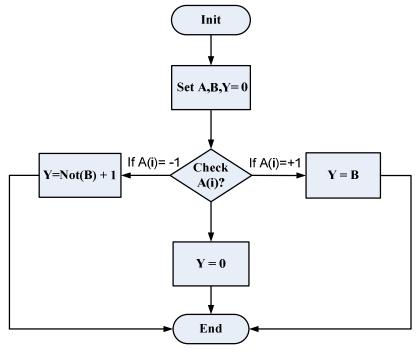

| Figure 4.8 Flo            | ow chart of the single-bit ternary CSD Multiplier                   | 107  |

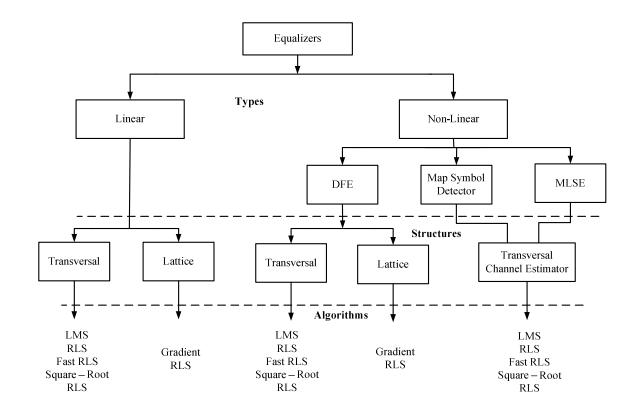

| Figure 5.1. Eq            | ualizers types, structures, and algorithms [100]                    | 118  |

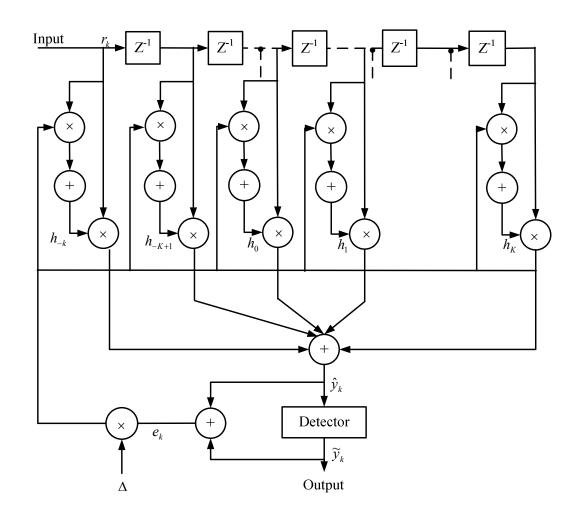

| Figure 5.2.               | Adaptive linear FIR equalizer with LMS algorithms [100]             | 119  |

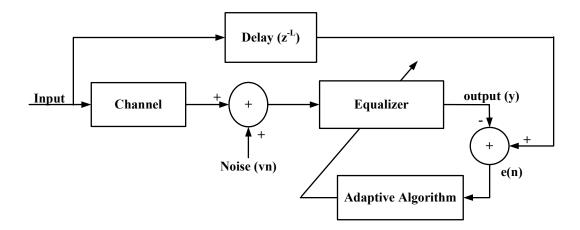

| Figure 5.3. Ge            | neral block diagram of an adaptive equalizer                        | 122  |

| Figure 5.4.               | Block Diagram of Single-bit ternary Adaptive Channel                |      |

| Eq                        | ualization                                                          | 122  |

| Figure 5.5.               | Second order sigma delta modulator                                  | 127  |

| Figure 5.6. Ge            | neral block diagram of single-bit block LMS-like filter [5]         | 129  |

| Figure 5.7. Th            | e proposed SBLMS adaptive algorithm structure                       | 133  |

| Figure 5.8.               | SER at varying input training samples                               | 135  |

| Figure 5.9.               | SER recorded at varying input SNR(dB)                               | 137  |

| Figure 5.10.              | MMSE averaged over 1 to 30 trials                                   | 139  |

#### Acknowledgments

Firstly, I would like to thank Allah who created an opportunity for me to work as PhD candidate at RMIT, Melbourne. Without His support this was an impossible to move forward even a single step. Secondly, I would like to thank my whole family for their continued love and support whilst completing my studies. More important is my wife and three kids whose passions and support throughout this period allowed me to keep on the track and finish this work in the time.

Special thanks to Dr. Paul Beckett, my supervisor and more than a mentor, again without your help and drive I would never have finished this thesis; I value your input, way of working, and arguments. Thanks to Dr. Zahir Hussain who gave a direction to work in this area and supported to kick off in the right direction. Also thanks to Dr. Amin Z Sadik, he has helped a lot throughout this project especially in understanding of single-bit adaptive theory.

I would like to thank my sponsor Mehran University of Engineering and Technology (MUET), Jamshoro and Higher Education Commission (HEC) of Pakistan, who provided funds for PhD studies at RMIT University Melbourne.

Finally I'd like also to thank RMIT University and staff for continual help and support especially in all administrative activities.

Tayab Memon

# Dedication

*This dissertation is dedicated to my wife (Fatima) and my daughters Ureba, Bareera, and Arfa.*

## **Publications**

Below is the list of publications that have resulted directly from the work undertaken by the author for this PhD thesis.

## **Journal Publications**

- Tayab D Memon, Paul Beckett, Amin Z Sadik, "Power-Area-Performance Characteristics of FPGA-based Sigma-Delta FIR Filters", *Journal of Signal Processing Systems Springer (JSPS)*, No. 11265, ISSN: 1939-8018, DOI: 10.1007/s11265-012-0664-8.

- Tayab D Memon, Paul Beckett, Amin Z Sadik, "Efficient Implementation of Ternary SDM Filters using State-of-the-Art FPGA", *Mehran University Research Journal of Engineering & Technology*, Volume 30, No. 2, APRIL, 2011, ISSN 0254-7821.

- Paul Beckett, Tayab Memon, "Reconfigurable Blocks Based on Balanced Ternary", *Journal of Signal Processing Systems Springer (JSPS)*, No. 11265, ISSN: 1939-8018, DOI: 10.1007/s11265-010-0559-5 (First published online).

- 4. Tayab Memon, Paul Beckett, "The Impact of Alternative Encoding Techniques on the FPGA Implementation of Sigma-Delta Modulated Ternary FIR Filter", Institute of Engineers Australia (IEAUST) Electrical and Electronics Journal, E11-061 (Accepted For Publication Feb 2012).

## **Refereed Conference Publications**

Tayab D Memon, Abdullah Al-Hassani, Paul Beckett, "Single-bit Ternary FIR Filter in FPGA Using Canonical Signed Digit", accepted for publication at 2<sup>nd</sup> *International Multi-Topic Conference (IMTIC'12)*, Mehran University Jamshoro, on 28 – 30<sup>th</sup> March, 2012.

- Tayab D Memon, Paul Beckett, "Ternary Sigma-Delta FIR Filters", 17<sup>th</sup> Asia and South Pacific Design Automation Conference (ASP-DAC), Sydney 30<sup>th</sup> Jan – 2<sup>nd</sup> Feb 2012.

- Tayab D Memon, Paul Beckett, Amin Z. Sadik, Peter O'Shea, "Single-bit Adaptive Channel Equalization for Narrowband Signals", 22<sup>nd</sup> IEEE Region 10 conference TENCON (TENCON'12), Bali, Indonesia, Nov, 2011.

- Tayab D Memon, Paul Beckett, Amin Z. Sadik, "Performance-Area Tradeoffs of Ternary and Conventional FIR filter in FPGA", 5<sup>th</sup> IEEE International conference on MEMS, NANO and Smart Systems (ICMENS), Dubai, UAE, 28-30<sup>th</sup> December, 2009.

- Tayab D Memon, Paul Beckett, Amin Z. Sadik, "Performance-Area Tradeoffs in the Design of a Short Word Length FIR Filter", 5<sup>th</sup> IEEE International conference on MEMS, NANO and Smart Systems (ICMENS), Dubai, UAE, 28-30<sup>th</sup> December, 2009.

- Tayab D Memon, Paul Beckett, Zahir M Husain, "Analysis and Design of a Ternary FIR Filter Using Sigma Delta Modulation", 13<sup>th</sup> IEEE International Multitopic Conference (INMIC'09), Islamabad, Pakistan, 2009.

- Tayab D Memon, Paul Beckett, Zahir M. Hussain, "Design and Implementation of Ternary FIR filter using Sigma Delta Modulation", *International Symposium on Computing, Communication and Control (ISCCC'09)*, Singapore, October 9-11, 2009.

## Presentations

1. Tayab D Memon, Paul Beckett, Amin Z. Sadik, "Single-bit and Conventional FIR Filter Comparison in State-of-Art FPGA", *Annual RMIT University HDR Conference, Melbourne,* October 2010.

# Chapter – 1

# Introduction

## **1.1 Introduction**

Although rapid advances in Very Large Scale Integration (VLSI) have made it possible to implement fast and efficient DSP functions in hardware, there is a continuing pressure towards smaller area with high performance at low power consumption in portable devices. As a result, there has been much research into finding optimal hardware implementations that fulfil these competing requirements [1-4]. For example, the characteristics of Finite Impulse Response (FIR) digital filters, which are widely used in signal processing applications, depend directly on the complexity of the essential multiplication steps that, in turn, increase linearly with the order of the filter. Regardless of the many optimizations that have been proposed, a large number of multiplication stages still translates into large area, delay and power consumption. Sigma delta modulation ( $\Sigma\Delta M$ ) based systems have the potential to mitigate the overhead of large multiplications and reduce the complexity of modern DSP systems. Sigma-delta modulators, which have already been widely adopted for A/D or D /A conversion, have recently been utilized for the development of DSP applications. For example, a LMS-Like single-bit adaptive filter has been developed to address the issue of noise cancellation in the real time mobile applications [5].

Despite these advances, there are many issues to be resolved particularly the application of Short Word Length (SWL) systems to VLSI implementations and how these contrast to their equivalent multi-bit system. These issues are addressed in this thesis as a way of promoting the adoption of  $\Sigma\Delta M$  based SWL systems in both communications related and general purpose DSP systems.

The term SWL is generally used to represent a system whose input, intermediate signals and final output can be in short word format i.e., 1 - 3 bits. Often SWL systems are known by the terms (that are even used throughout this thesis are) *binary* (or single-bit or bit-stream), and *ternary*. In the case of a FIR-like filter (see section 3.3) and adaptive channel equalization (see section 5.3) the term *single-bit ternary* has been used to indicate that the filter coefficients are in ternary format while its input is in binary (or single-bit i.e., +1, -1) format.

Following is given the detailed research questions, prospect objectives and novel contribution in the domain of SWL DSP systems.

#### **1.2 Research Questions and Thesis Objectives**

This thesis set out to answer the questions outlined below. To this end, the work has focussed primarily on the hardware characteristics of SWL FIR filters, especially in FPGAs. In addition, single-bit adaptive channel equalization and stability analysis of single-bit ternary FIR-like filter has been addressed in MATLAB.

#### **1.2.1** Research Questions

- How can efficient, fast single bit and ternary filters are organized based on Sigma Delta Modulation to be used for Lowpass, Bandpass and other applications in mobile communication?

- How do single-bit, ternary and multi-bit FIR filters exhibiting equivalent spectral performance compare in terms of their power-area-performance characteristics? In particular, what is the impact of increasing the OSR or bit-width in hardware?

- How can the best possible stability criterion of single-bit ternary FIR filter be achieved?

- Is it possible to utilize LMS adaptive techniques for the design and development of SWL LMS-like adaptive channel equalization? Can we achieve adaptive equalization using coefficients in a ternary format?

#### **1.2.2** Aims and Objectives

The primary aims of this work have been to:

- Design an efficient algorithm for the development of ternary adder circuit in VHDL that can be adopted for the synthesis of ternary FIR filter and investigating its area-performance characteristics

- Analyze the power-area-performance characteristics of single-bit ternary FIRlike filter in FPGA at varying OSRs in order to compare it with its corresponding multi-bit FIR filter

- Design and propose a more reliable stability model for IIR remodulator that takes into account all the stability factors of ΣΔM and that can be applied to the single-bit ternary FIR-like filter

- Investigate the area-performance characteristics of single-bit Ternary FIR filter using the alternative techniques of 2's complement, Canonical Signed Digit (CSD) and RBSD.

- Design and investigate a new single-bit ternary adaptive channel equalization organization using block LMS algorithm

## **1.3 Novel Contributions**

In single-bit FIR filters the requirement for a high OSR rate tends to cause the multiply/accumulate stage to become bulky. As a result, an efficient adder circuit design has been proposed and analyzed for these structures;

- A novel method of finding the power-area-performance characteristic of single-bit and multi-bit FIR filter in hardware at equivalent spectral performance has been determined and used to compare the two approaches with varying OSR;

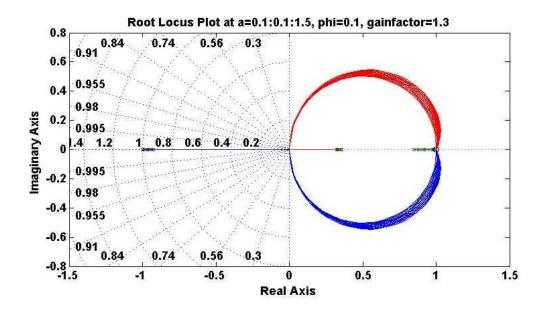

- A new model has been proposed for the stability analysis of single-bit IIR filter using linear analysis and a root locus approach. The model takes into account typical stability upper bounds and achieves better stability results with extended feedback parameters limits;

- An illustrative single-bit Ternary FIR filter has been designed, implemented and simulated on a commercial FPGA range and their area and performance behavior analyzed using 2's complement, canonical signed digit (CSD) and Redundant binary signed (RBSD) representations for data and coefficients;

- The non-trivial task of single-bit adaptive channel equalization has been addressed and a novel model has been proposed and simulated in MATLAB using narrowband signals. The results have shown significant achievement in terms of signal-to-noise ratio (SNR), symbol error rate (SER), and minimum mean squared error (MMSE).

#### **1.1 Thesis Organization**

This thesis is organized as follows. Chapter 2 provides a survey on sigma delta modulation based short word length signal processing techniques, highlighting previous work done in this area. Contemporary multi-bit applications, especially FIR filter design and implementation in FPGAs have been extensively addressed. The architecture level design of single-bit applications is briefly covered.

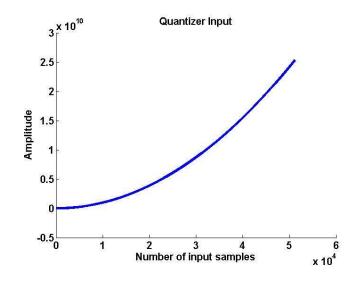

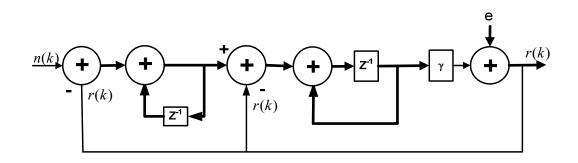

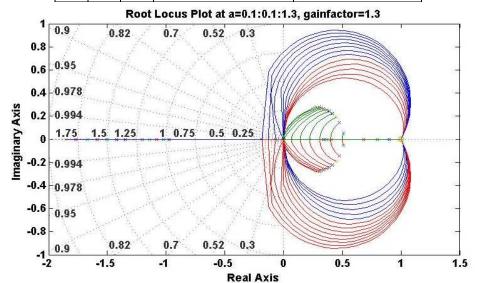

In chapter 3, we present the comparison of single-bit and multi-bit FIR filters in FPGAs on the basis of their power, area and performance characteristics. The comparative filters were coded in VHDL using pipelined and non-pipelined modes and simulations carried out with binary data streams and ternary coefficients. It was found that the single-bit FIR filter offers superior area performance tradeoffs except at very high filter order. Further, the stability of single-bit IIR filter organizations was investigated and a new design proposed. This takes into account the stability upper bounds and enhances the control over sigma-delta modulator and quantizer input so that it becomes easier to control the overall stability of the system. With the proposed design, the upper limits of the feedback parameter increases from 0.16 to 1.5.

In chapter 4, three alternative encoding techniques; Two'2 complement, canonical signed digit (CSD) and Redundant Binary Signed Digit (RBSD) were investigated for the representation of the coefficients and data. Simulations were carried out using small commercial available FPGAs from Altera. The area-performance characteristics of the ternary FIR filter were evaluated and maximum operating frequency ( $F_{MAX}$ ) was

computed for each simulation. Simulation results show that, in contrast to the case with conventional filters, digit encoding techniques such as CSD do not offer significant advantages in the single-bit domain. RBSD has been show to consume twice the chip area and returns no performance advantage.

In chapter 5, a novel approach to single-bit adaptive channel equalization is proposed. All of the inputs are maintained in single-bit format including channel transfer function. MATLAB simulation results shows that equalization filter can achieve significant signal-to-noise ratio (SNR), very small symbol error rate (SER), and minimum mean squared error (MMSE) with narrowband signals. Further work on this topic may leads towards better performance with more features and accuracy.

In chapter 6 we conclude and point to future work.

## Chapter – 2

# **Conventional and Single-bit FIR Filtering Techniques**

#### 2.1 Introduction

In general terms, two classes of digital filters are available: Finite Impulse Response (FIR) and Infinite Impulse Response (IIR). The choice of these filters can be categorized on the basis of speed, chip area, hardware complexity, spectral filtering and linear phase requirements. Both filters have advantages and disadvantages. FIR filters offer linear phase and simple hardware implementation but require a higher filter order to meet a specific application requirements compared to the IIR filter. By contrast, IIR filters exhibit stability problems due to their recursive nature that increases the overall filter gain and exaggerates quantization errors.

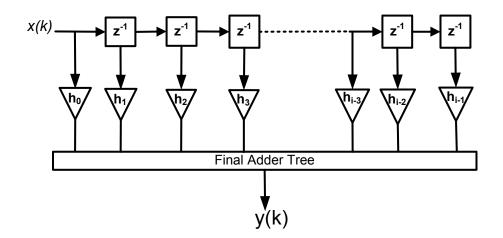

Figure 2.1 General structure of FIR filter

The general structure of a FIR filter is shown in Figure 2.1. The filter comprises a tapped delay line plus a multiply-accumulate (MAC) section. FIR filters operate such that every current sample and all previous input samples are multiplied with the coefficient (i.e., tap) values. This multiplication must take place before the next sampling instant requiring very fast multipliers that may consist of individual elements or a group of extremely fast multiplexed multiplier blocks. Mathematically, the FIR filter output y(k) can be described by the convolution of the filter coefficients  $\{h_i | i = 0, 1, \dots, N\}$  and the input signal  $\{x(k)\}$  as follows:

$$y(k) = \sum_{i=0}^{N} h_i x(k-i)$$

(2.1)

where N is the order of the filter.

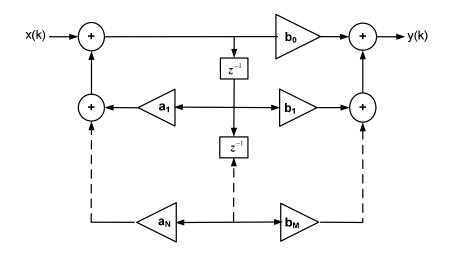

The operation of IIR filters is inherently recursive in nature and consequentially they exhibit a more complex structure than the FIR. Their operation is given by the recursive formula:

$$y(k) = \sum_{i=0}^{N} b_i x(k-i) - \sum_{j=1}^{M} a_j y(k-j)$$

(2.2)

where  $\{b_i\}$  and  $\{a_i\}$  are the filter coefficients. An IIR filter structure with direct form-II is shown in Figure 2.2. Unlike a FIR filter, the IIR equation contains poles. Unless the filter poles are confined within the z-domain unit circle, filter stability cannot be assured.

Figure 2.2 Block Diagram of an IIR direct form II filter

It is evident that FIR and IIR filter structures contains many multiplication and summation operations. When realized in integrated circuits multiplication operations typically require complex logic and a large amount of silicon area. As an example, for a k-bit multiplication, approximately 20K<sup>2</sup> transistors are required [6]. The efficiency of these traditional filters can be improved by reducing the number of transistors required for the multiplication operation. This reduction can be achieved by reducing the number of bits of both the input and its coefficients. However, simply reducing the filter coefficient or input word length will have a detrimental affect on the filtering capabilities or the output signal dynamic range.

An appropriate way to achieve this objective can be to use sigma-delta modulators that are already widely accepted for in the ADC/DAC domain. The use of Short wordlength, particularly single-bit techniques derived from sigma-delta modulators greatly simplifies the arithmetic processing within filter systems. The main attraction of SWL and especially single-bit systems is their intrinsic simplicity of operation, low power consumption and stability. SWL filters can exhibit excellent area-performance tradeoffs when implemented in hardware [7].

By their very nature, short word-length systems do not require the complex integer multiplication that can be a limiting factor in contemporary multi-bit signal processing. Single-bit multiplier design can easily be implemented by simple AND/OR logic, multiplexers or small LUT blocks. This simplified design is highly attractive for hardware implementation using Field Programmable Gate Arrays (FPGA) and especially ASIC, as reducing the number of general-purpose digital multipliers in the chip is a major challenge in both these domains. Initially, the applications of single-bit sigma delta modulated ( $\Sigma\Delta M$ ) systems to mobile communications tended to be restricted to audio processing because it had proved difficult to perform complicated DSP tasks efficiently using 1-bit processing. However, in last two decades a new generation of short word-length (SWL) systems have been developed that can perform general-purpose DSP functions, including classical and adaptive LMS filtering [8-14]. The design of single-bit ternary FIR-like filter have been at the forefront of this research [10].

Ternary is a term used to describe the format of coefficients that are drawn from the set {+1, 0, -1}. In abstract analyses such as using MATLAB, the physical hardware implementation is typically ignored, but this can include conventional 2 bit binary (using three of the four available symbols) or single-line multi-level encoding [15]. Numerous ternary algorithms have been published (see section 2.3.2) that have been found to be difficult in implementation [16-18]. Various MATLAB analyses of these algorithms have been reported along with more general issues related to sigma-delta modulators such as: stability, limit cycles, chaos, idle tones, integrator spans, adaptation etc. However, the hardware implementation of bit-stream filters is rarely reported and there are still unresolved issues that need to be addressed. Some of these issues, which are investigated later in this thesis, are as follows. First of all, the efficient design of single-bit ternary FIR filters is difficult due to the requirement for high oversampling ratios that, in turn, require a large number of coefficients. Secondly, it is unclear to how to compare single-bit and multi-bit approaches in hardware as the

analysis of the relative area, power and performance of these filters tends to be a cumbersome task.

Recent rapid changes in wireless communication have increased the role of adaptive filters and channel equalizers. Many adaptive algorithms have been proposed that may be well suited to a SWL channel equalization approach [19-21]. However it is still unclear what form such a SWL adaptive channel equalizer might take and its analysis is challenging due to the single-bit nature of the adaptive coefficients that are derived after coarse quantization. In addition, rigorous stability analysis of the singlebit ternary FIR filter is still an open question that requires detailed consideration. This may lead to a modified robust design of overall single-bit ternary filters.

As a result, this thesis aims to extend the theoretical work into SWL filters to support the development of efficient ternary FIR Filter algorithms in the form of small, fast filter modules that can be used in mobile communication applications. The application of such systems can be predicted to lead to substantial reduction in hardware size and execution time. This may lead to mobile phones that are smaller, lighter, cheaper, and that run for longer on a battery charge.

This chapter presents a comprehensive survey of efficient bit-stream signal processing that encompasses sigma-delta as an integral part. This survey begins with brief introduction of short word length (often single-bit) systems and importance in the current systems. This introduction is followed by a short review of sigma-delta

13

modulation and its signal and noise transfer functions derivations, followed by in investigation of fast and efficient filter design algorithms based on  $\Sigma\Delta M$ . Finally, some single-bit  $\Sigma\Delta M$  are discussed along with their VLSI analysis and the literature survey is summarised.

## 2.2 Sigma-Delta Modulation

Oversampled sigma-delta modulators have numerous advantages over Nyquist rate conversion devices. For example, they are simple in nature, offering low cost hardware design, robust behaviour in the face of analog component imperfection and reduced complexity of the anti-aliasing filter [22]. One major advantage of  $\Sigma\Delta M$  is their inherent noise shaping that is accomplished by coarse quantization (e.g., a coarse ADC) with a feedback loop around the quantizer that suppresses the quantization noise power within frequency band of interest [23]. This important aspect of the  $\Sigma\Delta M$  that supports a good balance between bandwidth and quantization noise [24]. Hence, quantization noise is moved away from the band of interest, which allows the input signal information to be passed towards the output with minimal alteration and behaves as high pass filter for the quantization noise (or quantization spectral density).

Typically  $\Sigma\Delta M$  conversion is achieved by the oversampling ratio and noise shaping effects [25]. As a result,  $\Sigma\Delta Ms$  are being proposed as alternate solutions to contemporary multi-bit signal processing designs [7, 10, 26]. Their applications are now found in diverse fields. For example, wired and wireless communication systems

[23, 27-28], DC blockers [11], arithmetic processing modules [29], neural networks [30], and audio processing, to name a few. For example, in [10] the conflicting requirements of high sampling rate, large dynamic range, and removal of the power interference before the amplification are managed by the use of sigma delta ADCs.

Typically,  $\Sigma\Delta M$  blocks are used to convert multi-bit output into single-bit format. This single-bit format generated by the sigma-delta modulators is normally filtered through a lowpass filter to reduce the quantization noise affects called demodulator and convert back the bitstream format (i.e., single-bit) into its original format. The collective filtering and down sampling operation after  $\Sigma\Delta M$  is known as decimator [25].

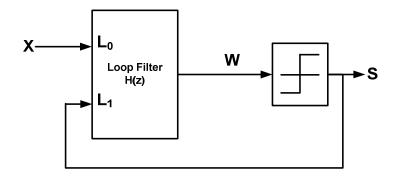

#### 2.2.1 Sigma-Delta Modulator Block Diagram

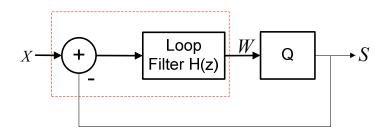

The general block diagram of the sigma-delta modulator is shown in figure 1. This diagram may be divided into two parts i.e., linear and nonlinear. Loop filter is a linear part with memory element and quantizer is a nonlinear part that is without memory. The linear part is a two input system where the single output (W) can be expressed as a linear combination of its input X and S. Generally, the sigma-delta modulator loop filter has a low pass characteristic for low frequency applications such as audio processing. This low pass modulator can be manipulated to create a band pass modulator such as reported in [31].

Figure 2.3 General diagram of the sigma-delta modulator

Sigma-delta modulators operate at an oversampling ratio that defines how much faster the oversampled modulator operates compared to a Nyquist-rate converter [31]. The term oversampling is a ratio between the sampling frequencies divided by the Nyquist rate that can be written as  $OSR = f_s/2f_o$ . Here  $f_s$  is the sampling frequency and  $f_o$  represents the maximum input signal frequency (i.e., Nyquist criterion  $2 \times f_o$ ). The oversampling ratio reduces the non-shaped in-band noise by 3 dB for every doubling of the sampling frequency [25]. Thus, doubling the sampling rate from  $f_s$  to  $f_{s1}$  causes the in-band quantization noise that was previously spread over  $[-f_s/2, f_s/2]$  to be spread over double the frequency i.e.,  $[-f_{s1}/2, f_{s1}/2]$ . Hence, the noise power spectral density is reduced to half its previous value. This reduction is in addition to the noise shaping affect that is an inherent part of the  $\Sigma\Delta M$ due to its built-in filtering action. This noise shaping affect may become more clear from the in-band noise spectrum approximation that is derived by considering error as white noise assumption [25, 31]:

$$Q \approx \left(\frac{\pi^{2N}}{2N+1}\right) \left(\frac{1}{OSR^{2N+1}}\right) \frac{\Delta^2}{12}$$

(2.3)

where Q represents the in-band quantization noise, N is the order of the modulator, and  $\Delta^2/12$  is the white noise mean square value. It can easily be seen that in-band quantization noise can be reduced by increasing either or both the order of the sigmadelta modulator or the oversampling ratio. From (2.3) it is clear that the typical number of bits added to the resolution by doubling the OSR is N+0.5 for first order sigmadelta modulators and 2N+0.5 for second order sigma-delta modulator and so on.

#### 2.2.2 Trade-offs Between ΣΔM OSR and Modulator Order

There is a direct trade-off between the OSR and order of the sigma-delta modulator. With lower order of the sigma-delta modulators, higher OSRs are needed to suppress the in-band noise [31]. For example considering N=2 in(2.3) i.e., second order  $\Sigma \Delta M$ , gives a decrease of in-band noise by 15dB at each doubling of OSR as compared to the 9dB that is achieved by first order  $\Sigma \Delta M$ . Thus the increase in OSR required by lower order  $\Sigma \Delta M$ s is a limiting factor that may restrict their use in broadband applications.

Three different approaches have been proposed for obtaining the better noise shaping with lower oversampling ratio [32]. One of them is to accommodate higher order of the sigma-delta modulators which gives higher noise transfer functions and reduces the noise power spectral density. The major problem with higher order of the sigma-delta modulators is their inherent instability. Employing a multi-bit quantizer is another approach but at the cost of higher insensitivity of the quantizer itself. A third approach is to cascade the sigma-delta modulators, a technique also known as multistage or MASH (i.e., Multi-stage noise SHaping). Many alternate  $\Sigma\Delta M$  structures have been proposed with various orders; a good survey of these structures can be found in [31].

#### 2.2.3 Quantizer Behaviour in $\Sigma \Delta M$

The overall behaviour of the sigma-delta modulators has to be considered to be non-linear due to its quantizer, thus its stability is a major concern. Normally, first and second order modulators are considered stable in nature but offer lower noise suppression. On the other hand, higher order of the sigma-delta modulators offer better in-band noise suppression but it becomes increasingly complicated to predict the quantizer behaviour.

Generally, the single-bit quantizer i.e., one that has only two possible options  $\{+1,-1\}$  is preferred in  $\Sigma\Delta M$  systems due to its superior linearity compared to the multi-bit quantizer [31, 33]. However, their major problem is their higher level of quantization noise. The multi-bit quantizer has advantages over single-bit unless the quantizer does not overload, something that is less likely in higher order modulators (e.g.,  $\geq 3$ ) [34].

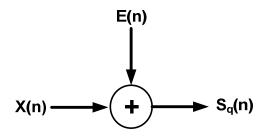

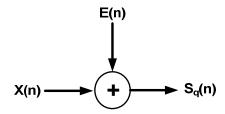

Figure 2.4 Linear Model of Quantizer

#### 2.2.4 Linear and Non-Linear Models of $\Sigma \Delta M$

The design and analysis of  $\Sigma \Delta M$  can be accomplished by considering both linear and non-linear models [34-35]. The linear model of the  $\Sigma \Delta M$  quantizer is often preferred due to its greater simplicity [34]. While this linearization gives insight into the quantizer behaviour, it does not account for signal dependent quantization noise. In the linear model, the 1-bit quantizer is replaced by a quantizer variable gain that is followed by an additive white noise source with variance calculated as:

$$e_{rms}^{2} = \frac{1}{\Delta} \int_{-(\Delta/2)}^{+(\Delta/2)} e^{2} de = \frac{\Delta^{2}}{12}$$

(2.4)

where  $\Delta$  represents the quantization interval and e represents the quantization error term (shown in Figure 2.4) that is added to the quantizer input. It states that the error is bounded in the range  $\pm \Delta / 2$ , until and unless the quantizer is not saturated. Hence, the quantizer gain is the ratio of quantizer output voltage to the quantizer input voltage as given below:

$$\gamma = \frac{Sq(n)}{X(n)} \tag{2.5}$$

#### 2.2.5 Sigma-Delta Modulator Z-domain Analysis

Based on a linear model in the z-domain, a  $\Sigma\Delta M$  system (see Figure 2.3) can be described by [31]:

$$W(z) = L_0(z)X(z) + L_1(z)S(z)$$

(2.6)

where the S(z) represents the quantizer output that can be described as the quantizer input plus the quantizer error signal (i.e., E) so that:

$$S(z) = W(z) + E(z)$$

(2.7)

Using these relationships, the output S can be written as a linear combination of two signals, namely the modulator input X and the quantization error E:

$$S(z) = STF(z)U(z) + NTF(z)E(z)$$

(2.8)

where,

$$NTF(z) = \frac{1}{1 - L_1(z)}$$

(2.9)

and

$$STF(z) = \frac{L_0(z)}{1 - L_1(z)}$$

(2.10)

With given desired *NTF* and *STF*, loop filter transfer function can be computed by the following relationships:

$$L_0(z) = \frac{STF(z)}{NTF(z)}$$

(2.11)

and

$$L_1(z) = 1 - \frac{1}{NTF(z)}$$

(2.12)

These relationship can be applied regardless of the structure of the loop filter and input-output characteristics of the  $\Sigma\Delta M$  are determined by solely *STF*, *NTF* and the properties of the quantizer [31]. In the simplest case, the signal is delayed by *j* clock periods in the modulator so that the STF satisfies |STF| = 1, and the *NTF* requires the quantization noise to be differentiated *N* times. Then,

$$STF(z) = z^{-j} \tag{2.13}$$

$$NTF(z) = (1 - z^{-1})^{N}$$

(2.14)

By replacing these terms in (2.10) and (2.11), we get:

$$L_0(z) = z^{-j} (1 - z^{-1})^{-N}$$

(2.15)

and

$$L_1(z) = 1 - (1 - z^{-1})^{-N}$$

(2.16)

Considering the first order  $\Sigma \Delta M$  loop filter (shown in Figure 2.5) that has a single input and only the difference x(n) - s(n) enters the loop filter. Then

$L_o = H(z)$  and  $L_1 = -H(z)$ , and *STF* and *NTF* of the 1st order modulator are given below:

$$NTF(z) = \frac{1}{1 + H(z)}$$

(2.17)

$$STF(z) = \frac{H(z)}{1 + H(z)}$$

(2.18)

where H(z) is the transfer function of the common portion of the loop filter. Now, H(z) along with the quantizer, determines all the important properties i.e., stability, signal and noise transfer functions of the modulator [31]. From the above given NTF relationship it is evident that quantization error Q(z) is spectrally filtered.

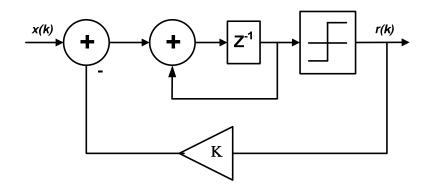

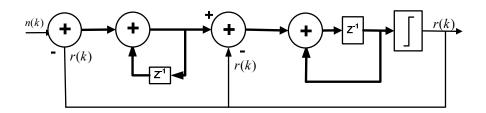

Figure 2.5 First Order Sigma-Delta Modulator Topology

To illustrate this spectral filtering let us replace the loop filter H(z) by its equivalent transfer function i.e.,

$$H(z) = \frac{z^{-1}}{1 - z^{-1}}$$

(2.19)

where H(z) is an integrator. However, more accurate models have been proposed that take into account the non-linear behaviour of the quantizer (e.g., [35]) but the model presented here (Figure 2.6) is a workable mechanism for understanding the behaviour of the  $\Sigma\Delta M$  [36]. If we now replace the H(z) term in (2.17) and (2.18), then the following first order sigma-delta modulator transfer functions are achieved:

$$STF(z) = z^{-1}X(z)$$

(2.20)

$$NTF(z) = (1 - z^{-1})E(z)$$

(2.21)

where STF(z) is purely a delayed version of the input that does not change the form of input signal. On the other hand, the quantization noise is filtered with the differentiator  $(1-z^{-1})$  that has a high pass filter response and shapes the quantization noise away from the (low frequency) band of interest. Therefore, if the input signal is in a lower frequency range then it will be modulated in single-bit format with reduced quantization noise [23]. With a uniform distribution between the +1 and -1 for quantization noise, overall z-domain linear model that relates the output (*S*) to the input (*X*) is given as:

$$S(z) = z^{-1}X(z) + (1 - z^{-1})E(z).$$

(2.22)

Similarly for the  $N^{th}$  order loop filter input-output relationship can be described as:

$$S(z) = z^{-N} X(z) + (1 - z^{-1})^{N} E(z).$$

(2.23)

Here, the term N denotes the order of the modulator and  $(1-z^{-1})$  is the inherent filtering term that suppresses the in-band quantization noise. As given in (2.3), the traditional linear model for Nth-order modulator relates the output to the input spectrum according to:

$$S(e^{j\Omega}) = S_x(e^{j\Omega}) + \frac{1}{3} \left[ 2\sin(\frac{\Omega}{2}) \right]^{2N}$$

(2.24)

where  $S(e^{,\alpha})$  and  $Sx(e^{,\alpha})$  denotes the output and input signal power spectral densities of the  $\Sigma\Delta M$ . The term  $\frac{1}{3}\left[2\sin(\frac{\Omega}{2})\right]$  is the squared magnitude of the NTF in the frequency band (i.e., noise spectral density) and  $\frac{1}{3}$  is the error term with  $\Delta = 2$  (i.e.,  $\left(\Delta^2/12\right) = 1/3$ ).

In general terms, quantization error is dependent on its input and is defined as difference between quantizer output and its input (i.e.,  $e_q(n) = q_o(n) - q_{in}(n)$ ). Quantization error is considered as noise when the error has statistical properties that are independent of the signal, and error samples are highly uncorrelated from sample-to-sample. Hence, the ideal in-band *SNR* (i.e., SNR<sub>in</sub>) achieved by the  $N^{th}$  order  $\Sigma \Delta M$  is given below [25]:

$$SNR = 10 \log_{10}(\sigma_{xy}^{2}) - 10 \log_{10}(\sigma_{qy}^{2}) - 10 \log_{10}\left(\frac{\pi^{2N}}{2N+1}\right) + (20N+10) \log_{10}\left(\frac{f_{s}}{2f_{B}}\right) (dB)$$

$$(2.25)$$

where  $\sigma_{xy}^2$  is the signal power at the output and  $\sigma_{qy}^2$  is the in-band noise power at the output assuming zero mean. As the signal power is assumed to occur only in the specified signal band, it is not modified in any way, and the signal power at the output  $\sigma_{xy}^2$  is the same as the input signal power  $\sigma_x^2$ . Thus for every doubling of the oversampling ratio (OSR), this modulator provides an extra (6*N*+3) dB of SNR [25].

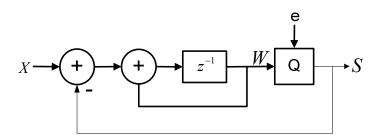

Figure 2.6 First Order Sigma-Delta Modulator Topology with Loop Filter Specified

Quantization noise can further be reduced by exploiting the noise transfer function zero locations of the typical  $\Sigma\Delta M$  topology. In [37], with fixed pole locations optimum zero locations up to 8th order of the  $\Sigma\Delta M$  are given that offers significant SNR improvement. With optimum zero locations by increasing the order of the  $\Sigma\Delta M$  (i.e.,  $1 \rightarrow 2 \rightarrow 3$ ) an additional 5-dB SNR improvement was observed in [37]. The Butterworth configuration has been the well-known choice for the pole location of the NTF. These may be described for the  $N^{th}$  order  $\Sigma \Delta M$  topology as:

$$NTF(z) = \frac{\prod_{i=1}^{N} (z - z_i)}{\prod_{i=1}^{N} (z - p_i)} = \frac{1}{1 + H(z)}$$

(2.26)

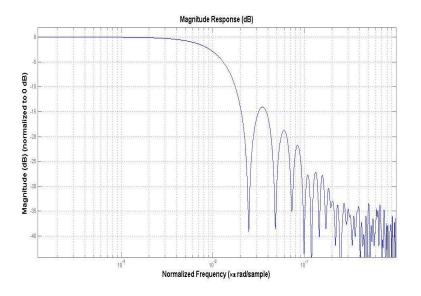

Figure 2.7 NTF at  $1 - 3^{rd}$  orders of the sigma-delta modulator

By increasing the order of the  $\Sigma \Delta M$  (i.e., the number of integrators) better noise suppression can be obtained. This is evident from the *NTF* relationship given in (2.26).

In order to estimate the in-band power of the quantization noise, it is useful to find the squared magnitude of NTF in the frequency domain, by setting  $z = e^{j2\pi f}$ . For first, second and third order sigma-delta modulators the NTF is plotted and shown in Figure 2.7. It can be seen that third order has double the stop band attenuation than second order and second order has double the stopband attenuation of the first order.

Of course, the output signal from the modulator is in a single-bit format. However, general trend is to filter that output bit-stream using traditional IIR and FIR filtering to remove the quantization noise and then to re-sample and decimate to the Nyquist frequency. Hence, once the  $\Sigma\Delta M$  output is filtered using one of these traditional techniques, the signal is again in a multi-bit format. However, the aim of SWL DSP techniques is to avoid, as far as possible, multi-bit stage(s) throughout the system design using  $\Sigma\Delta M$ .

## 2.3 Fast and Efficient FIR Filter Design Techniques

It is no surprise that many signal processing tasks can be accomplished by a microprocessor or a digital signal processor (commonly called DSP kits). Built-in multiplication modules are the core element of these devices. Furthermore, implementation of multiply and accumulate (MAC) circuits within signal processors can significantly improves the throughput of FIR and IIR digital filters structures (see Figure 2.1 and Figure 2.2) that requires large number of multiply and accumulation operations per sampling period.

An alternative solution is to use gate-level programmable devices such as field programmable gate arrays (FPGAs) to perform the digital filtering tasks. Concurrent (i.e. parallel) mode of operations of these devices is of great interest as it can improve the throughput of the digital signal processing circuits especially digital filtering modules. This higher throughput can be achieved at the cost of higher chip area compared to the serial implementation of the circuits. Nonetheless, many of these FPGA devices also possess higher number of built-in multipliers that requires large amount of silicon space within in the FPGA. The most recent FPGA devices have include resources that easily support general purpose signal processing tasks even within mid-range commercial devices.

However, there is direct trade-off between chip area and throughput in these devices. Some obvious applications that require fast and efficient digital filters are decimation filters, audio filter banks, charge-coupled-device filters and software defined radio, all of which require high throughput. To achieve fast and efficient implementations, many techniques have been proposed. The overarching theme of these techniques has been to reduce the complexity of the multiplication process in any way possible. One method of reducing the complexity of the multiplier is to reduce the word length in both input and the filter coefficients. The preferred approach is to utilize the sigma-delta modulation to reduce the word length; this thesis will focus on these methods. Here are many techniques that use some form of sigma-delta modulation or the like to improve the efficiency of the digital filtering operations. Examples of such techniques were reported in [26, 36, 38-44].

#### 2.3.1 Fast FIR Filters

Fast and efficient filters generally fall in two classes: sigma-delta modulation based and optimization techniques within a multi-bit format. A brief description of both these methods is given below.

#### 2.3.2 Sigma-delta Modulation Based Fast Filters

Much work has been reported on the design and implementation of the sigma-delta modulation based FIR and IIR filters encompassing various forms. The work that was commenced by [16], and progressed by [43, 45] has been reported by many, such as [17, 24, 36, 38-40, 42, 46-47]. More recently sigma-delta modulation based bit-stream adder and multiplier modules have been described in [48-49].

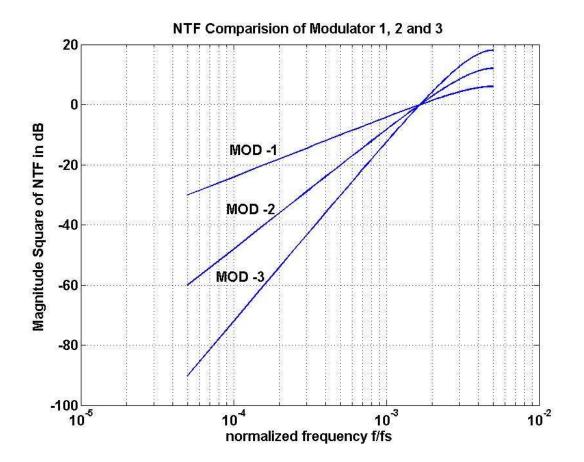

In [40, 42, 46], the efficient FPGA implementation of a narrowband FIR filter is achieved by simplifying the MAC operation using a lower precision input to the filter. This filtering operation requires that the input to the filter should be oversampled and re-quantized through the error feedback  $\Sigma\Delta M$  as shown in Figure 2.8. Using Authors have used distributed arithmetic (DA) approach to design error prediction FIR filter that has been placed in negative feedback path (see Figure 2.8). This prediction filter has a flat pass band and leading phase shift in the band of interest. The paper also discusses the optimum prediction filter design based on statistics and a minimummean-squared error (MMSE) calculation. For FIR filter input, only 3 - 4 bits in the requantizer output were processed as compared to the original 16-bit input bit-stream to the  $\Sigma\Delta M$  (i.e., re-quantizer).

Overall, an efficient implementation of a narrowband digital filter through a requantizing operation has shown a 50% reduction in logic resources as compared to a traditional FIR filter implementation using a FPGA. This filter shows a great promise for FIR filter implementation. Further reduction in complexity can be gained through harsher requantization to lower precision words.

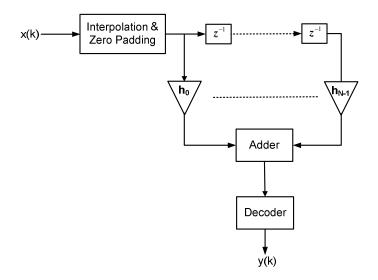

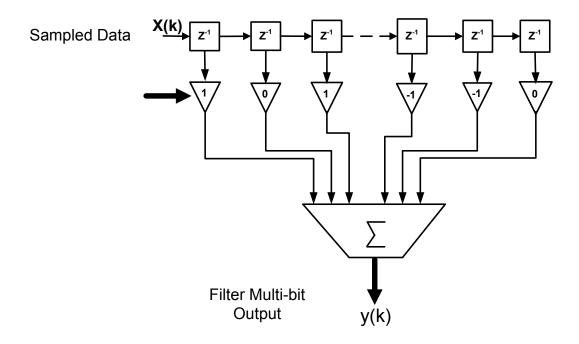

In [45] and [43] fast and efficient FIR filters are presented. The authors discussed two sigma-delta filtering approaches. In first approach, FIR filter coefficients are encoded using first order sigma-delta modulator. Hence, the input to the filter must be interpolated and zero-padded to *R* times sampling frequency. An efficient two step interpolation process was proposed that required firstly interpolating the original signal  $(x_n)$  by 4 times at a sampling frequency of  $4f_N$  resulting in  $x_{of}$ . This signal  $(x_{of})$  was then up-sampled by R/4 times (R is the typical OSR) to give  $\hat{x}_n$  by appending zeros. The proposed structure is shown in Figure 2.9. The decoder for this filter is used to reconstruct the original signal by resampling to the Nyquist rate and removing quantization noise by using a low pass filter and decimator.

Figure 2.8 Block diagram of the error feedback  $\Sigma\Delta M$  for requantization

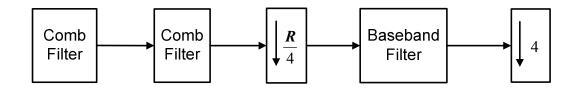

The use of cascaded comb filters as reported in [50] was adopted to further simplify the decoder design whilst removing any alias introduced into the system from the FIR filter. Only two cascaded comb filters were used in design (shown in Figure 2.10) because the authors found that using more than two cascaded comb filters did not improve the trade-off between signal-to-noise ratio of the coded output and the OSR.

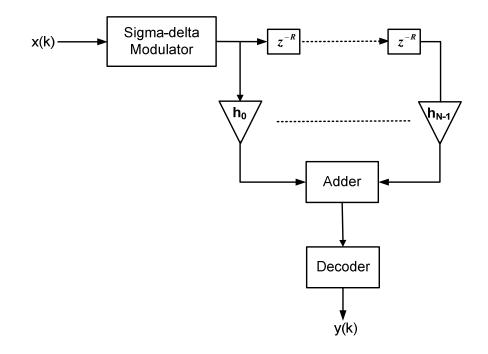

In a second approach (Figure 2.11), input data was encoded into single-bit format through sigma-delta modulator whereas the filter coefficients were kept in PCM format. The decoder for this structure was identical to the one shown in Figure 2.10. Signal encoding with sigma-delta modulator worked as an ADC and single-bit coder so there is no longer a requirement for a conventional ADC. Further, no input interpolation is required in this setup as the signal passing through  $\Sigma\Delta M$  will be oversampled. To perform the filtering operation, full precision filter coefficients were zero padded by R to match the oversampling ratio of the  $\Sigma\Delta M$ . Decoder circuits comprising cascaded comb and baseband filters were used to remove the quantization noise and aliases from the filtered output signal. However, the output signal was in multi-bit format in these schemes.

Figure 2.9 Block diagram of the FIR filter with  $\Sigma\Delta M$  modulated filter coefficients

Figure 2.10 Block diagram of the decoder used in FIR filter with  $\Sigma\Delta M$  modulated filter coefficients and with  $\Sigma\Delta M$  modulated input signal

In [43] the authors also propose a fully sigma-delta modulated FIR filter. In this instance, it was recognized that filter performs well if both the input and filter

coefficients are sigma-delta encoded in single-bit format. A similar structure was utilized to that shown in Figure 2.9 except that the interpolator was replaced with a sigma-delta modulator. It was found using simulation that the design exhibits a flat input spectrum in the Nyquist frequency range and the latter approach (Figure 2.11) performed well in comparison to the former (Figure 2.10). This structure was found to further reduce the complexity of the filter's hardware implementation.

Figure 2.11 Block diagram of the FIR filter with  $\Sigma\Delta M$  modulated input signal

A ternary format has an extra symbol for input and filter coefficients and has been found to offer better stop band attenuation and dynamic range flexibility compared to the binary format [7, 43]. While that work illustrates the potential benefits of ternary encoded filters, the final decoder leaves the output in a multi-bit format that again requires complex hardware to process.

A slightly different fast and efficient FIR filter design using sigma-delta encoding is presented in [17] in which a Look-Ahead Decision Feedback (LADF) approach is used to encode the filter coefficients into a single-bit format. In that work, the proposed technique is compared with two other  $\Sigma\Delta M$  architectures: the multi stage (MASH) and double loop (DSM2). It was found that the proposed architecture outperforms in comparison to double loop but has poor performance against the MASH architecture. Given the lower complexity implementation of the proposed architecture, the author argues that the method is appropriate for filter encoding. However, the quantizer stage with LADF architecture is more complex than the single-bit quantizer and its associated  $\Sigma\Delta M$  architecture.

The last group of fast and efficient filters designs use a canonical signed digit (CSD) quantizer with signed powers of two  $\Sigma\Delta M$  output [47]. It is argued that the CSD quantizer provides many more quantization levels than a single-bit quantizer, which suits the linear modelling of the system design and can improve the system stability. Thus an output in CSD format obtained from the  $\Sigma\Delta M$  can be used as the FIR filter coefficients and the multiplication operation becomes simple shifts. Another, promising scheme, presented in [51] uses a slightly more complex architecture but is essentially the same technique.

## 2.4 Single-bit Filtering Techniques

Regardless of the many optimizations that have been proposed, a large number of multiplication stages still translates into large area, delay and power consumption. One-bit  $\Sigma\Delta$  modulators are widely used in AD and DA conversion stages due to their inherent linearity and precision. However, it is less common for the entire digital processing path to operate on single bit data. The more usual approach has been to decimate the signal data stream after conversion and for the remaining processing to be performed in standard binary at the Nyquist rate and with a resolution mandated by dynamic range and noise considerations.

Sigma Delta Modulation ( $\Sigma\Delta M$ ) encoding of the FIR filter coefficients has shown to be efficient way to reduce the complexity of the multiplier and improve its area– performance tradeoffs [52]. The simple arithmetic of single-bit DSP systems results in efficient hardware implementations that map well to FPGA resources, which comprise flip-flops plus simple logic blocks and/or look-up tables. The advantages of single-bit systems were first identified by [16] and further developed in [45, 53] and [47]. Recently, general purpose Short Word Length (SWL) DSP applications including classical LMS algorithms have been described in [10, 14]. In this section we introduce and describe the techniques that have been used to filter whilst maintaining a single-bit output. This section is further divided into two sections i.e., simulation based single-bit techniques analysis and its VLSI analysis.

#### 2.4.1 Single-bit techniques

As the name suggests the single-bit filters produce single-bit output. In last decade various general purpose DSP applications are reported using single-bit sigma-delta modulation encoding including classical FIR filter in [10-11, 14, 54-55]. This single-bit approach was first reported for IIR and FIR filtering in [39] and [36].

In [36], single-bit FIR filtering technique is proposed with bit-stream input and fixed or floating point coefficients similar to the one reported in [43, 45]. However, the major contribution is the replacement of the decoder in [43] by a  $\Sigma\Delta M$  that has a low pass signal transfer function. The single-bit FIR filter as proposed in [36] is shown in Figure 2.12.

Similarly, in the second approach presented in [45], the input is assumed to be in single-bit format, while full precision filter coefficients are generated at the Nyquist rate. This newly generated impulse response was interpolated by R times, where R is the oversampling ratio of the input signal, via zero-interleaving. The R aliases that were introduced due to zero-interleaving in [45], were removed by decoder comprising of cascaded comb filters and baseband filter. However, in [36],  $\Sigma\Delta M$  was used instead of a decoder. This  $\Sigma\Delta M$  was used to remove the aliasing created by the zero-interleaving process and served to re-modulate the multi-bit output signal from the FIR filter back into the single-bit domain.

The VLSI analysis of the proposed design was carried out and authors found that single-bit design to be more efficient in silicon resources than a PCM digital filter up to 80 taps. The structure still has the complexity of a full precision filter coefficients, this can also increase the word length of the FIR filter output.

The re-modulator complexity is discussed by the same authors in [56]. Digital  $\Sigma \Delta M$  low pass frequency responses are typically not easy to find in the current literature. A fourth order  $\Sigma \Delta M$  was used for this purpose with various powers of two multiplications that created more complex SDM structure than standard one. Therefore, low pass modulator structure presented in [56] is very complex for single-bit filters.

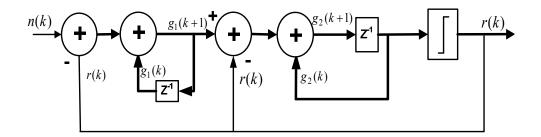

Figure 2.12 Block diagram of the single-bit FIR filter

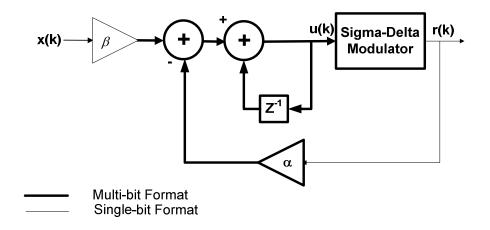

The core idea of the IIR single-bit  $\Sigma \Delta M$  presented in [6, 39] was to multiply one-bit oversampled input signal with a multi-bit fixed coefficient. The resulting multi-bit output must be applied to the sigma-delta modulator to get back the single-bit output. Initially the model was tested without the feed-forward integrator which resulted in a large noise gain due to higher oversampling ratio transfer function. A modified version with an integrator inside the loop that resulted noise reduction and keeping the STF and NTF same is shown in Figure 2.13. In this model, the  $\Sigma \Delta M$  is assumed to be a single delay element, hence, the system is a basic first-order recursive filter [6, 39].

The stability of the system in Figure 2.13 was assumed to be determined by a rule of thumb with an assumption that second order sigma-delta modulators will remain stable. But due to an extra integrator inside the loop the overall NTF becomes equivalent to a third order  $\Sigma\Delta M$ , making it more difficult to analyse the stability of the overall system [39]. Therefore, this system was not further studied by those authors.

However, a quasi-orthonormal state space IIR architecture was shown to have good filtering abilities with good stop band attenuation by the same authors in [57]. The downside of this structure is that it requires  $N \Sigma \Delta M$  blocks for an Nth - order IIR filter and the structure becomes very complex as the number of order increases. The proliferation of  $\Sigma \Delta M$  blocks only adds to the quantization noise in the band of interest and makes any stability analysis very difficult [39].

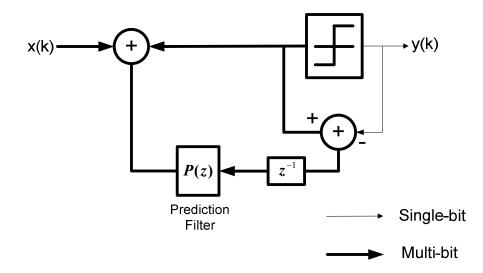

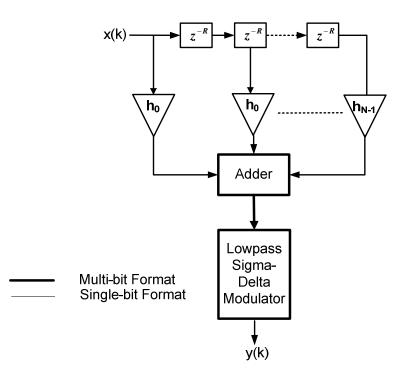

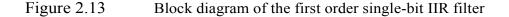

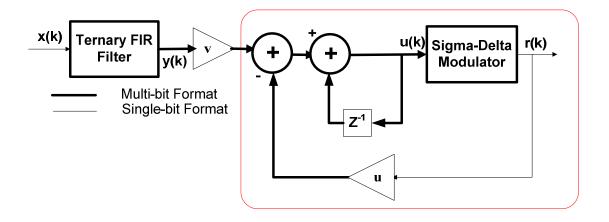

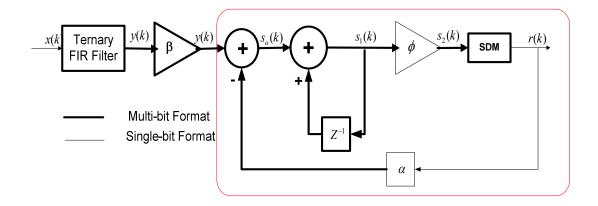

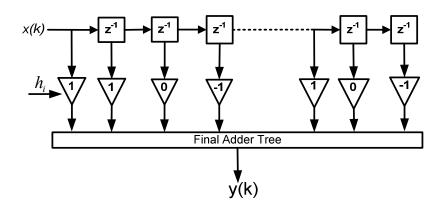

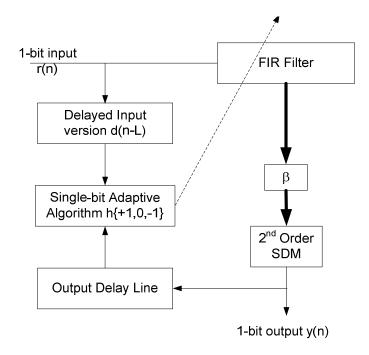

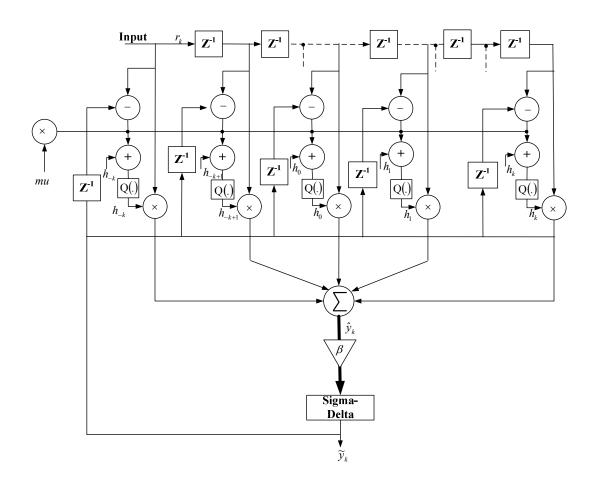

Recently, new DSP design techniques called short word length (SWL) have been reported in [5, 10-11, 13]. Of these SWL techniques, the so-called single-bit ternary FIR filter was first proposed in [10]. This design is comprised of two parts: the ternary filter and the IIR remodulator as shown in Figure 2.14. A new method to generate the single-bit ternary filter was also proposed that starts with the selection of the target impulse response. This target impulse response must undergo an interpolation stage before the ternary sigma-delta modulated form of the filter can be generated. The generated ternary format of coefficients must have flat pass band frequency response in the frequency band of interest (i.e.  $0 \rightarrow f_0$ ). The transfer function of the overall design was derived and the filter was simulated at a number of OSR values. It was found that the resulting single-bit filter produced an equivalent output to the target impulse response. Hence, it appears that single-bit ternary filters can take over the bulky multi-bit systems that include complex multiplication.

Figure 2.14 General bock diagram of the single-bit ternary FIR filter

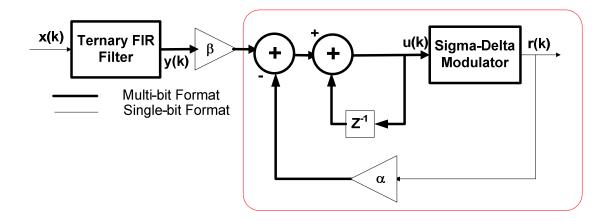

Using the same approach, a narrowband band pass  $\Sigma\Delta M$  was proposed in [13] (Figure 2.15). Again it comprises two parts: the ternary filter followed by the remodulation of the multi-bit into single-bit format. Unlike low pass single-bit filter, these authors have proposed a re-modulation by a simple band pass  $\Sigma\Delta M$  that has efficient architecture and less stability sensitivity compared to the IIR re-modulator. Coefficients were encoded into ternary format by passing the band-pass target impulse response through an 8<sup>th</sup> order  $\Sigma\Delta M$  with optimum coefficients. Through MATLAB simulation it was found that the overall frequency response of the proposed method as was very similar to the original target impulse response.

Figure 2.15 Single-bit narrowband bandpass FIR filter

The performance of the proposed method is also discussed in [58]. It was found that FFT and spline interpolation techniques offer superior stop band attenuation performance to other techniques. Following the same approach, single-bit resonators and BFSK demodulator designs have been reported in [28, 55]. However, this short word length approach was not verified through hardware synthesis nor was its area-performance-power compared with contemporary multi-bit techniques. Furthermore, that work does not extend to a rigorous stability analysis of the SWL filtering techniques.

Further to this work, a LMS-like single-bit adaptive filtering structure for noise cancelling has been presented in [5, 14, 59], in which all input, output, and filter coefficients are in single-bit format. Overall, three short-word length adaptive structures were proposed: namely, ternary, single-bit and 2-bit. The overall weight vector equation was derived by using block LMS algorithm which has advantage of accommodating more data samples and better performance than a sample-by-sample LMS algorithm. Through MATLAB simulation it was found that 2-bit single-bit adaptive filter has superior performance than others i.e., single-bit and ternary at the cost of prospect more chip area.

However, much work is still needed to explore the design using random input with higher noise environment. In addition, it is still unclear what might be the optimum coefficient update rate or range of the convergence parameter (mu) or shape of the learning curves.

#### **2.5** VLSI Analysis of $\Sigma \Delta M$ based bit-stream circuits