# Predicting Power Scalability in a Reconfigurable Platform

A thesis submitted in fulfillment of the requirements of the degree of Doctor of Philosophy

August 2007

Paul Beckett

B. Eng (Comm.), M. Eng.

School of Electrical & Computer Engineering

Science, Engineering and Technology Portfolio

**RMIT University**

## Contents

| Contents                                                                                                        |                                                                                                                                                                                                                                                                             | iii                                                            |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| List of Figure                                                                                                  | es                                                                                                                                                                                                                                                                          | vi                                                             |

| List of Table                                                                                                   | S                                                                                                                                                                                                                                                                           | ix                                                             |

| Declaration                                                                                                     |                                                                                                                                                                                                                                                                             | х                                                              |

| Copyright                                                                                                       |                                                                                                                                                                                                                                                                             | xi                                                             |

| Acknowledg                                                                                                      | ements                                                                                                                                                                                                                                                                      | xii                                                            |

| Summary                                                                                                         |                                                                                                                                                                                                                                                                             | 1                                                              |

| Chapter 1.                                                                                                      | Introduction                                                                                                                                                                                                                                                                | 2                                                              |

| <ul><li>1.3 Thes</li><li>1.4 Rese</li><li>1.5 Spec</li><li>1.6 Disse</li></ul>                                  | view ration and Scope is Statement arch Approach ific Outcomes and Contributions ertation Outline cations                                                                                                                                                                   | 2<br>4<br>6<br>6<br>9<br>10                                    |

| Chapter 2.                                                                                                      | Scaling Issues for Future Computer Architecture                                                                                                                                                                                                                             | 12                                                             |

| 2.2 Mate 2.3 CMO 2.3.1 Silico 2.3.2 Extre 2.3.3 Devic 2.4 Interc 2.4.1 Interc 2.5 Perfc 2.5.1 Satur 2.5.2 Subtl | amental Limits to Device Scaling rial Limits S Device Scaling on-on-Insulator ome Device Scaling—Schottky Barrier MOSFETs be Variability connect Scaling Limits connect Delay Scaling ormance Modeling in Advanced CMOS ration Drain Current Models oneshold Current Models | 12<br>15<br>17<br>19<br>20<br>21<br>27<br>30<br>33<br>34<br>36 |

| 2.6.1 Reco<br>2.6.2 Relia<br>2.6.3 Issue<br>2.7 Power                                                           | Level Technology Drivers Infigurable Hardware Ibility and Defect Tolerance Is in Design for Manufacture Informance Scaling Insurer Circuit Techniques                                                                                                                       | 37<br>38<br>44<br>46<br>48                                     |

| <ul><li>2.7.2 Adial</li><li>2.7.3 Archi</li></ul>                                                               | Power Circuit Techniques patic Systems tectural Level Power/Energy Scaling Models rging Computer Architecture                                                                                                                                                               | 51<br>55<br>56<br>62                                           |

Contents

| 2.8.1<br>2.8.2<br>2.8.3<br>2.9                                                                                                                       | Parallelism Spatial Architectures Asynchronous Architectures Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 62<br>67<br>71<br>74                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Chapte                                                                                                                                               | er 3. A Double-Gate Reconfigurable Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77                                                                                                    |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.4                                                     | Thin-Body Double-Gate SOI Thin-Body Silicide Source/Drain Devices TCAD Modeling of TB-DGSOI Threshold Behavior of Thin-Body Devices Physically Based SPICE Models for TB-SOI A Reconfigurable Array based on TBDGSOI Devices Reconfigurable Double-Gate Cell Reconfigurable Array Topology Logic and Interconnect Mapping Combinational/Sequential Logic Mapping Registered or Non-Registered Logic? Summary                                                                                                                                  | 79<br>81<br>81<br>85<br>88<br>92<br>93<br>97<br>102<br>107<br>109                                     |

| Chapte                                                                                                                                               | er 4. An Area-Power-Performance Model for CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 116                                                                                                   |

| 4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.4<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.6<br>4.4.7<br>4.5 | Architecture Level Area—Power—Delay Tradeoffs Scaling with Constant Performance Modeling Power vs. Area in CMOS Subthreshold Leakage Saturation Drive Current Modeling Variability Short Circuit Power Gate Leakage Gate Induced Drain Leakage (GIDL) Dynamic and Subthreshold Power/Energy Scaling vs. Area Capacitance Scaling Dynamic and Subthreshold Scaling Models Supply and Threshold Scaling vs. Area Total Power vs. Area Power and Energy vs. Area—Examples from the Roadmap Node Capacitance Estimates Applying the Model Summary | 117<br>120<br>121<br>122<br>125<br>127<br>129<br>131<br>136<br>137<br>139<br>142<br>144<br>147<br>156 |

| Chapte                                                                                                                                               | er 5. Power Scaling in the Reconfigurable Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 166                                                                                                   |

| 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.4                                                                       | VHDL-AMS Device/Circuit Level Modeling The EPFL Double-Gate Transistor Model Device/Circuit Level Parameter Extraction An Architectural Scaling Model VHDL Behavioral Model Parallel Architectures and $\sigma$ Scalability Estimates for the Reconfigurable Platform Power-Performance Tradeoffs in Future Technology Summary                                                                                                                                                                                                                | 167<br>168<br>168<br>173<br>177<br>177<br>180<br>184<br>188                                           |

Contents

| Chapter    | 6. Summary, Conclusions and Future Work                                                                               | 193                             |

|------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 6.2<br>6.3 | Summary Conclusions Summary of the Scalability Analysis Methodology Summary of Contributions Proposed Future Research | 193<br>195<br>198<br>199<br>200 |

| Referen    | ces                                                                                                                   | 202                             |

| Append     | ix A: TCAD Input Decks                                                                                                | 223                             |

| Append     | ix B: SPICE Input Decks                                                                                               | 225                             |

| Append     | ix C: VHDL-AMS 6-NOR Adder Description                                                                                | 229                             |

Contents v

# List of Figures

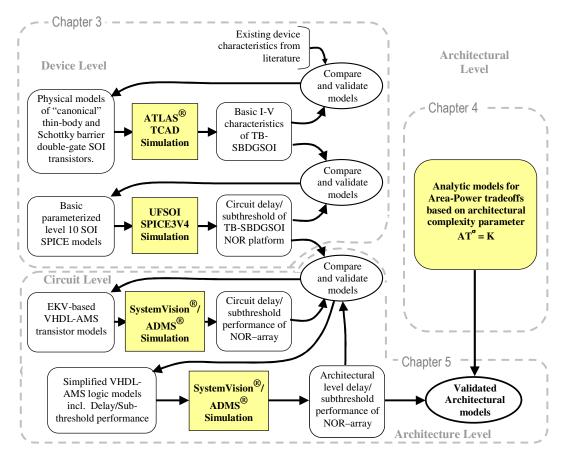

| Figure 1.    | Research approach and objectives                                                                    | 7  |

|--------------|-----------------------------------------------------------------------------------------------------|----|

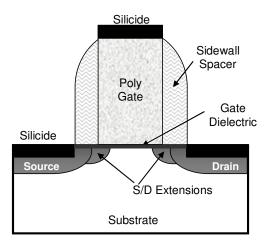

| Figure 2.    | Simplified cross section of a modern MOS transistor.                                                | 16 |

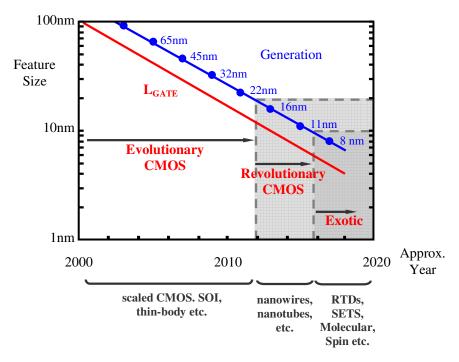

| Figure 3.    | Predicted evolution of CMOS technology                                                              | 18 |

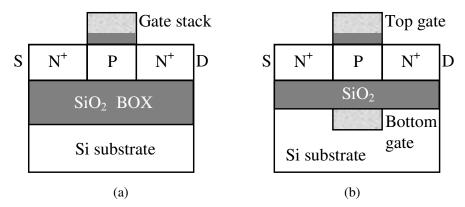

| Figure 4.    | Conventional Silicon On Insulator (SOI) device topology                                             | 19 |

| Figure 5.    | A Schottky barrier CMOS inverter                                                                    | 20 |

| Figure 6.    | DIBL mechanisms in (a) Double-gate MOSFETs and (b) Schottky barrier FETs                            | 20 |

| Figure 7.    | Random placement of impurities in device channel                                                    | 22 |

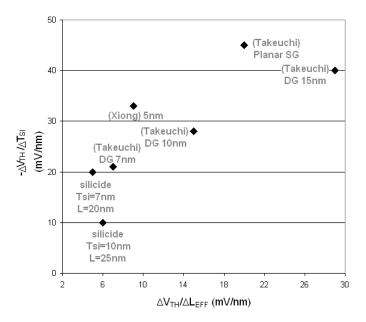

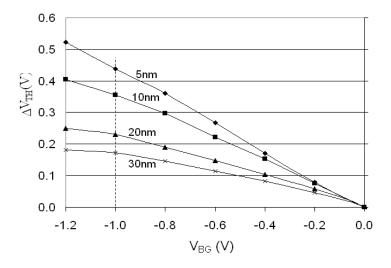

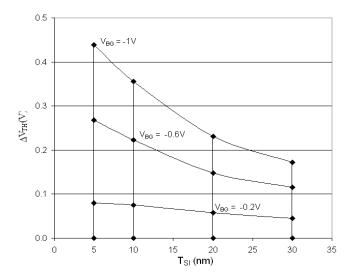

| Figure 8.    | V <sub>TH</sub> sensitivity for ultra-thin-body double gate devices (T <sub>SI</sub> as shown).     | 24 |

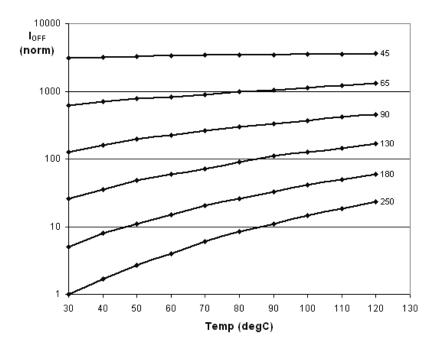

| Figure 9.    | Leakage current temperature characteristics                                                         | 26 |

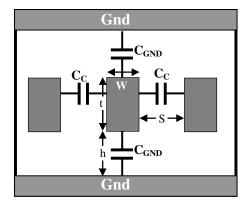

| Figure 10.   | Interconnection capacitance model                                                                   | 28 |

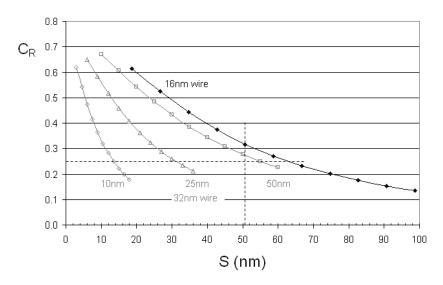

| Figure 11.   | Crosstalk ratio ( $C_R = V_n/V_{DD}$ ) vs. interconnect separation (S)                              | 30 |

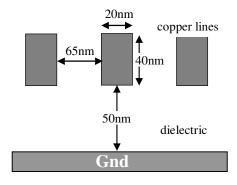

| Figure 12.   | Example interconnect topology                                                                       | 33 |

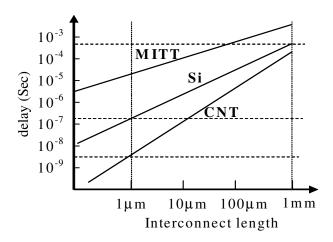

| Figure 13.   | Estimated interconnect delay based on 10nm technology                                               | 33 |

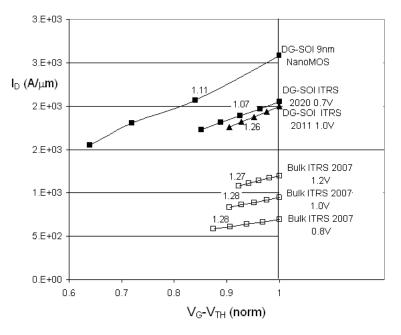

| Figure 14.   | $I_D$ (sat) vs. normalized gate overdrive ( $V_{G}$ - $V_{TH}$ )                                    | 35 |

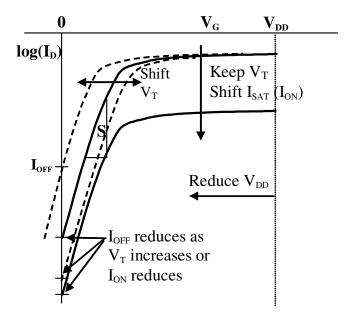

| Figure 15.   | The general impact of shifts in transistor characteristics.                                         | 36 |

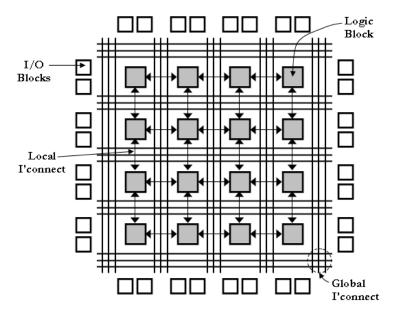

| Figure 16.   | Basic FPGA architecture                                                                             | 39 |

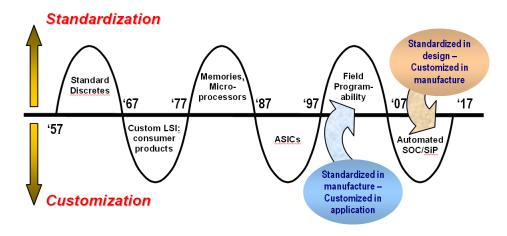

| Figure 17.   | Cyclical semiconductor trends- Makimoto's Wave                                                      | 40 |

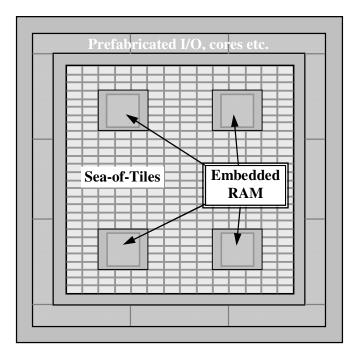

| Figure 18.   | The Structured ASIC concept                                                                         | 42 |

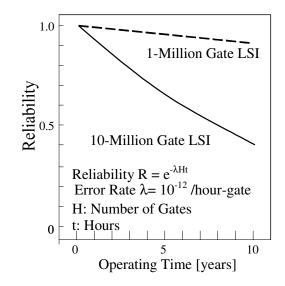

| Figure 19.   | ULSI reliability curves                                                                             | 45 |

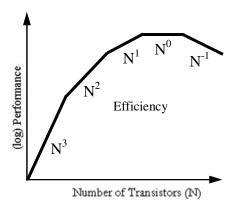

| Figure 20.   | Jouppi's "Eras of Microprocessor Efficiency"                                                        | 49 |

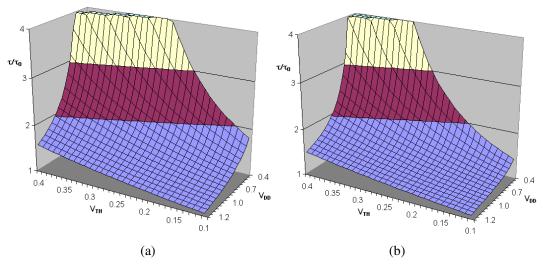

| Figure 21.   | Delay scaling $\tau/\tau_0 \propto V_{DD}/(V_{DD}-V_{TH})^{\alpha}$ vs. $V_{DD}$ and $V_{TH}$       | 51 |

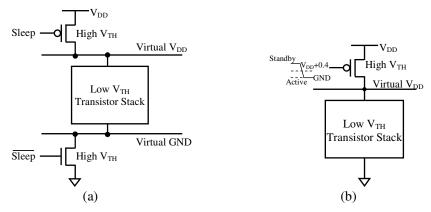

| Figure 22.   | Alternative power-down circuits using high $V_{TH}$ sleep-mode transistors                          | 53 |

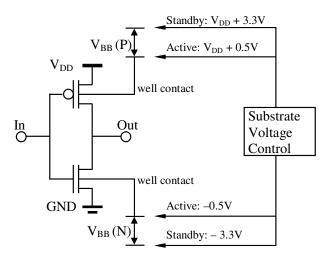

| Figure 23.   | Variable threshold CMOS (VTCMOS)                                                                    | 54 |

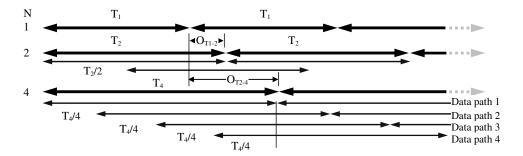

| Figure 24.   | Overall performance speedup using parallel data paths.                                              | 60 |

| Figure 25.   | An area-frequency scaling example showing the area—performance tradeoff                             | 60 |

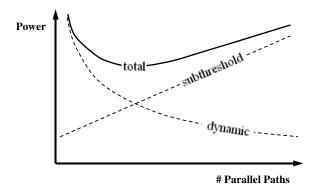

| Figure 26.   | Generalized total power trajectory with parallel data paths                                         | 61 |

| Figure 27.   | A processing graph fragment.                                                                        | 68 |

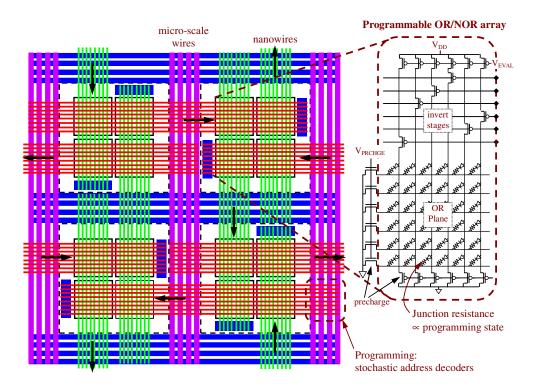

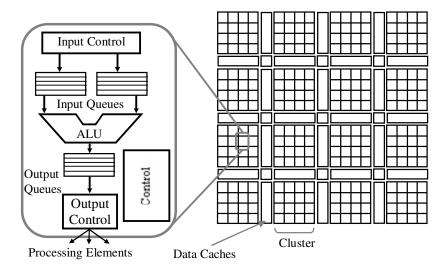

| Figure 28.   | Nanoscale PLA architecture                                                                          | 70 |

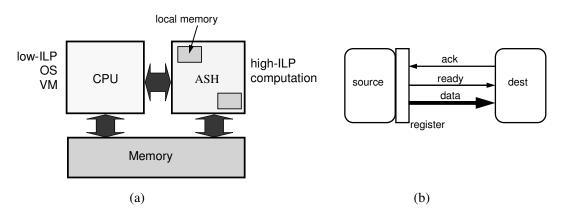

| Figure 29.   | Application-specific hardware (ASH)                                                                 | 71 |

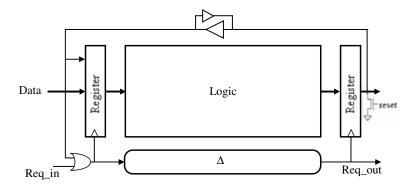

| Figure 30.   | Generic asynchronous wave-pipeline                                                                  | 73 |

| Figure 31.   | A WaveScalar processor implementation                                                               | 73 |

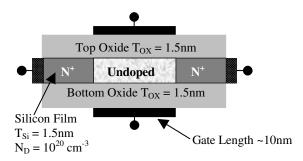

| Figure 32.   | "Canonical" thin-body SOI double-gate NMOSFET                                                       | 79 |

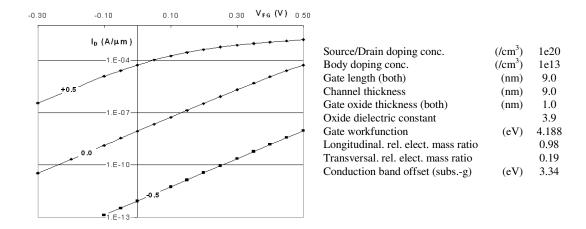

| Figure 33.   | Simulated I <sub>D</sub> -V <sub>FG</sub> characteristics of an ultra-thin body FD-DGSOI            |    |

|              | transistor                                                                                          | 80 |

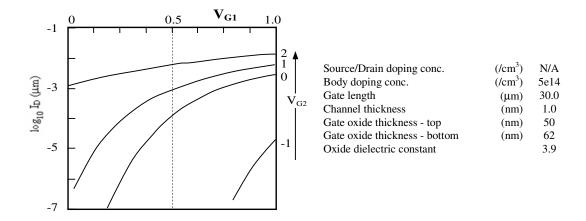

| Figure 34.   | Measured $I_D$ -V <sub>G1</sub> characteristics of DGSOI transistor, $T_{SI} = 1$ nm.               | 80 |

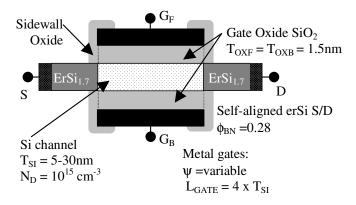

| Figure 35.   | Simplified view of a double-gate n-channel TBFDSBSOI transistor.                                    | 82 |

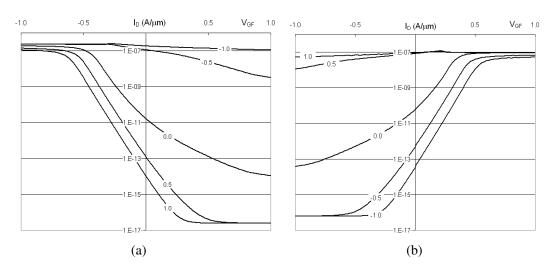

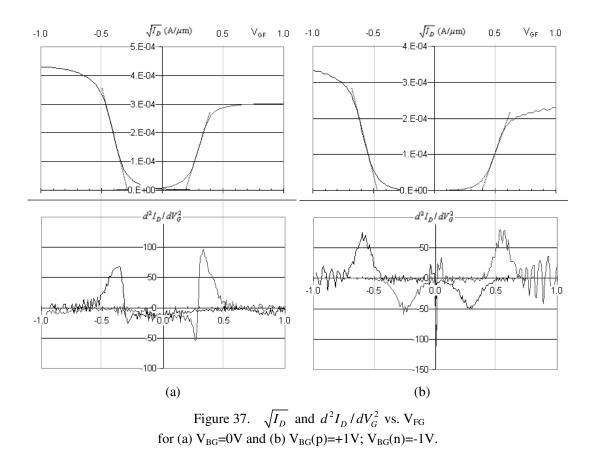

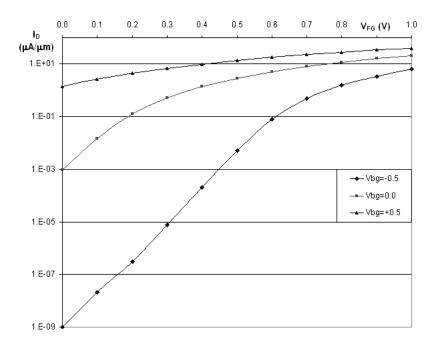

| Figure 36.   | Simulated $I_D/V_{FG}$ Characteristics with -1.0 $\leq$ $ V_{BG}  \leq$ 1.0 (a) P-Type; (b) N-Type. | 82 |

| Figure 37.   | $\sqrt{I_D}$ and $d^2I_D/dV_G^2$ vs. $V_{FG}$                                                       | 84 |

| Figure 38.   | Threshold voltage change ( $\Delta V_{TH}$ ) vs. back gate voltage                                  | 86 |

| Figure 39.   | $\Delta V_{TH}$ vs. silicon film thickness, 5nm $\leq T_{Sl} \leq 30$ nm.                           | 86 |

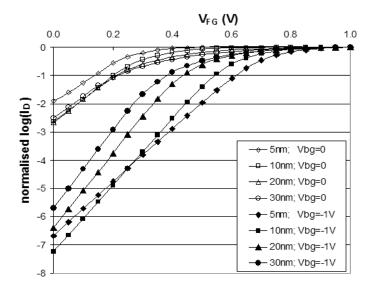

| Figure 40.   | TCAD simulated $log(I_D)$ vs. $V_{FG}$ (n-type) for various body thickness                          | 00 |

| i igui e +0. | values $(T_{SI})$ .                                                                                 | 88 |

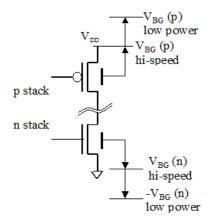

| Figure 41.   | The general form of the double-gate CMOS transistor stack.                                          | 89 |

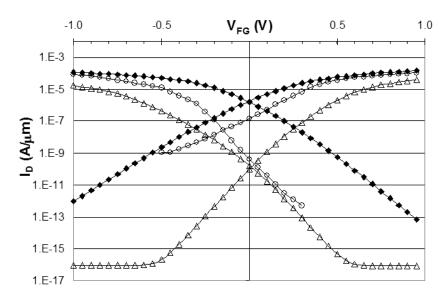

| Figure 42.   | SPICE simulated $I_D$ vs. $V_{GS}$ for p and n-type double gate silicide S/D                        |    |

| J            | devices                                                                                             | 89 |

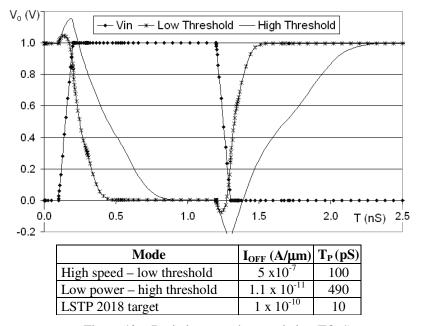

| Figure 43.   | Basic inverter characteristics (FO-4):                                                              | 90 |

List of Figures vi

| Figure 44.            | 2-NAND gate characteristics (all transistors: L=350nm, W=1.4μm).                                                                                             | 91         |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

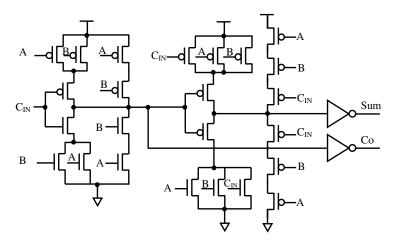

| Figure 45.            | 28 transistor static CMOS Full Adder circuit                                                                                                                 | 92         |

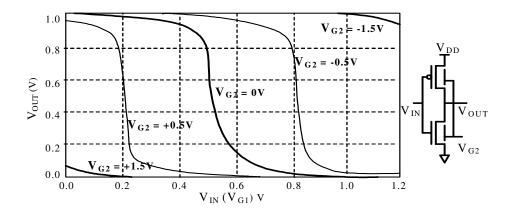

| Figure 46.            | DC transfer characteristics of a variable switching threshold inverter                                                                                       | 93         |

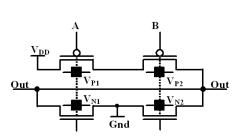

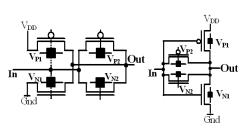

| Figure 47.            | TB-DGSOI transistor circuits                                                                                                                                 | 95         |

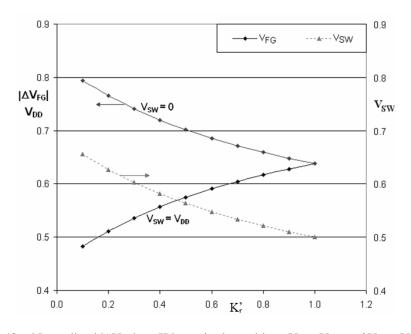

| Figure 48.            | Normalized $ \Delta V_{FG} $ vs. $K_r$ required to achieve $V_{SW} = V_{DD}$ or $0V$ at                                                                      | t          |

|                       | $\varepsilon V_{TH}=\pm 25\%$ .                                                                                                                              | 97         |

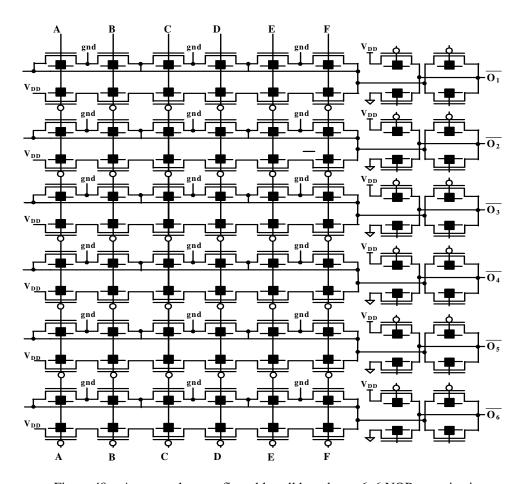

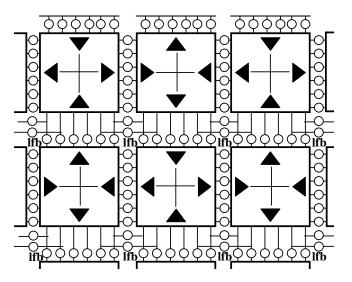

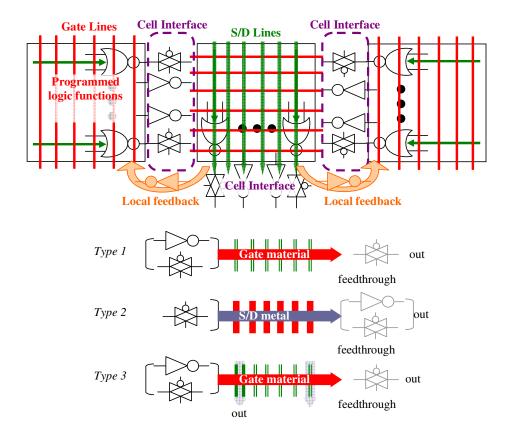

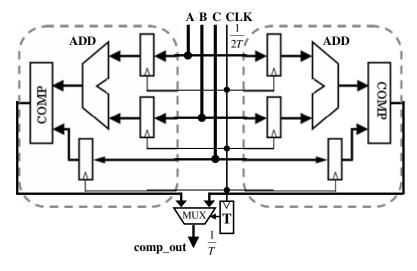

| Figure 49.            | An example reconfigurable cell based on a 6x6 NOR organization.                                                                                              | 98         |

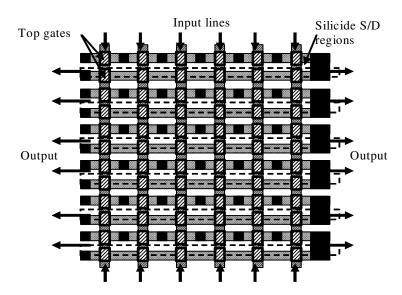

| Figure 50.            | Simplified symbolic layout of the 6-input, 6-output array.                                                                                                   | 99         |

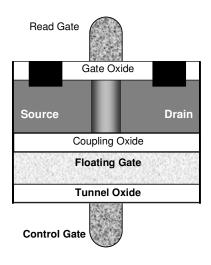

| Figure 51.            | Layout cross-section of Opposite-Side Floating-Gate FLASH Memory                                                                                             | 100        |

| Figure 52.            | Simplified partial view of the array connectivity.                                                                                                           | 100        |

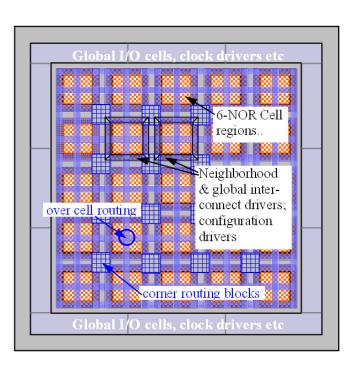

| Figure 53.            | Generic floorplan of a reconfigurable fabric.                                                                                                                | 101        |

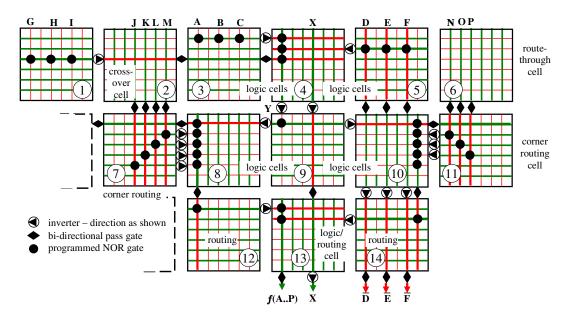

| Figure 54.            | Example logic cell and interconnect topologies                                                                                                               | 103        |

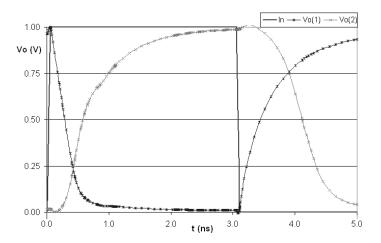

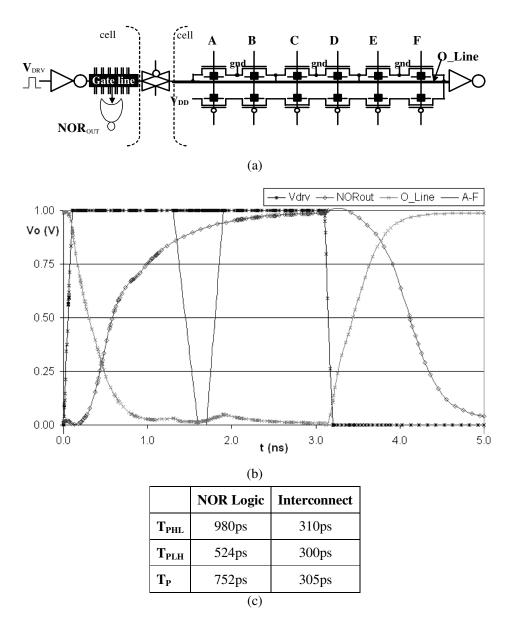

| Figure 55.            | Simulated transient response of a single 6-NOR pair                                                                                                          | 103        |

| Figure 56.            | Interconnect signals compared to basic NOR operation.                                                                                                        | 105        |

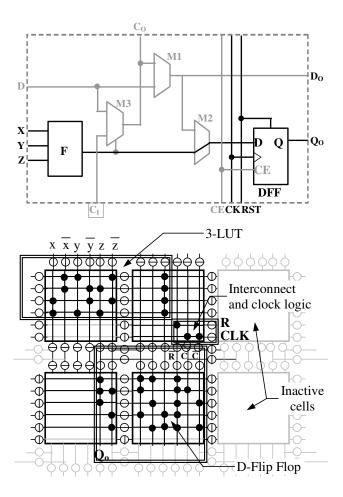

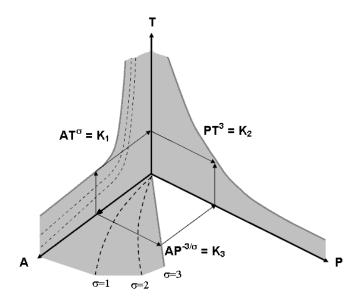

| Figure 57.            | A configured logic cell forming a 3-LUT and Flip-Flop.                                                                                                       | 106        |

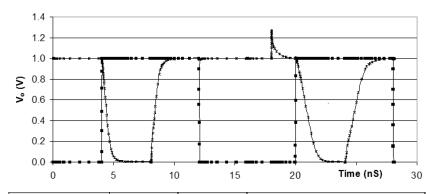

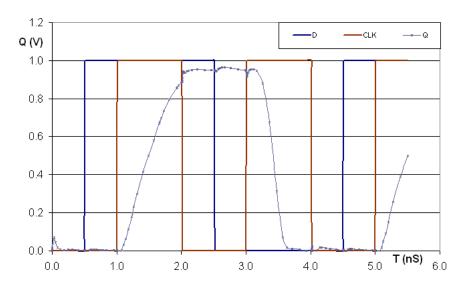

| Figure 58.            | Simulated D-type FF operation.                                                                                                                               | 107        |

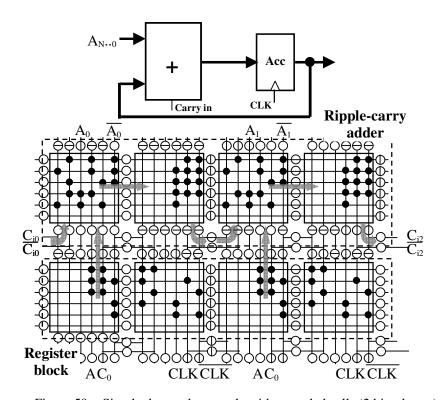

| Figure 59.            | Simple data path example with cascaded cells (2 bits shown)                                                                                                  | 108        |

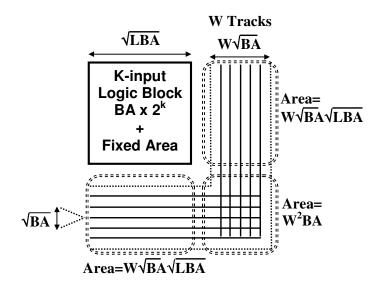

| Figure 60.            | Interconnect area model of Rose et al.                                                                                                                       | 109        |

| Figure 61.            | Modified interconnect area model                                                                                                                             | 110        |

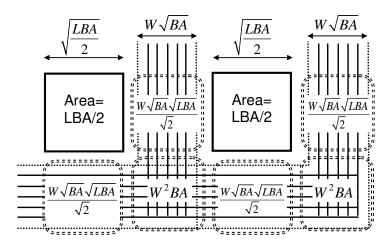

| Figure 62.            | Basic Logic Element (BLE)                                                                                                                                    | 111        |

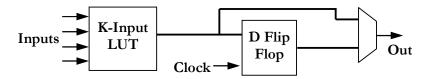

| Figure 63.            | A hypothetical 3-dimensional Area-Time-Power space                                                                                                           | 118        |

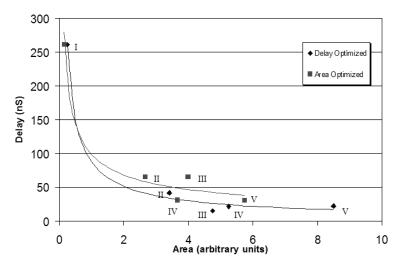

| Figure 64.            | Area vs. Delay for five 32-bit adder styles                                                                                                                  | 119        |

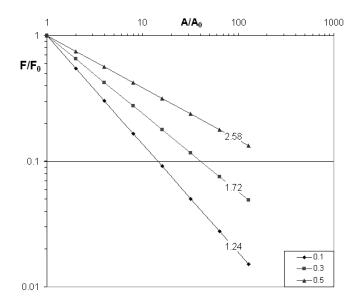

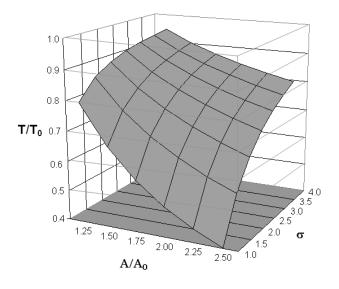

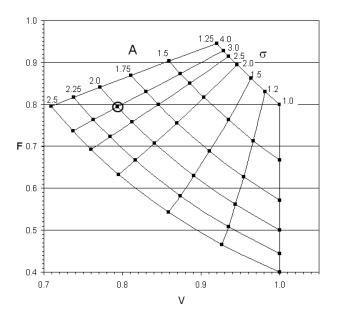

| Figure 65.            | $T/T_0$ vs. $(A/A_0)^{-1/\sigma}$ for $1 \le \sigma \le 4$ .                                                                                                 | 119        |

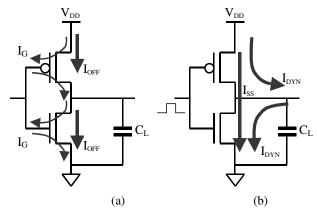

| Figure 66.            | (a) Static and (b) Dynamic power loss mechanisms in CMOS $I_{SUB}/I_{SO} = e^{-40a}  e^{40bV_{DD}}$ (solid lines) and $V^{n}_{DD}$ (dotted lines) for n=2-4. | 122        |

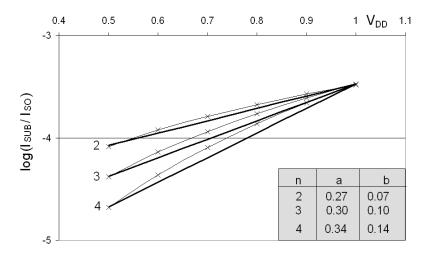

| Figure 67.            |                                                                                                                                                              | 124        |

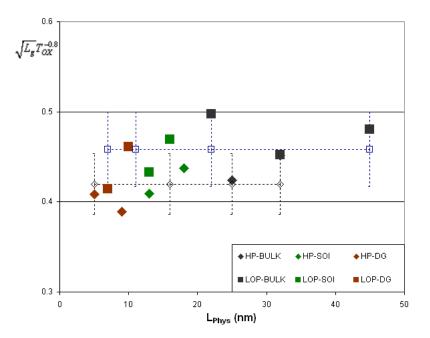

| Figure 68.            | $\sqrt{L_{ m g} T_{OX}^{-0.8}}$ vs. L <sub>Phys</sub> for some selected ITRS technologies.                                                                   | 126        |

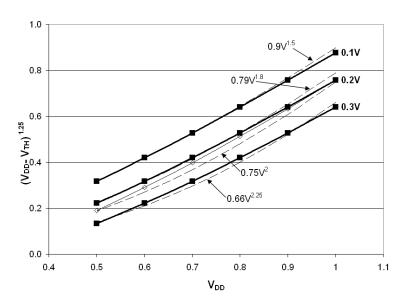

| Figure 69.            | $(V_{DD} - V_{TH})_3^{1.25}$ vs. $V_{DD}$ with $V_{TH} = 0.1$ , 0.2 and 0.3V (filled squares).                                                               | 126        |

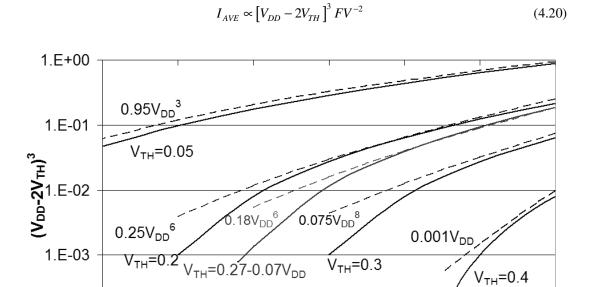

| Figure 70.            | $(V_{DD}-2V_{TH})^{\circ}$ vs. $V_{DD}$ for various $V_{TH}$ functions                                                                                       | 130        |

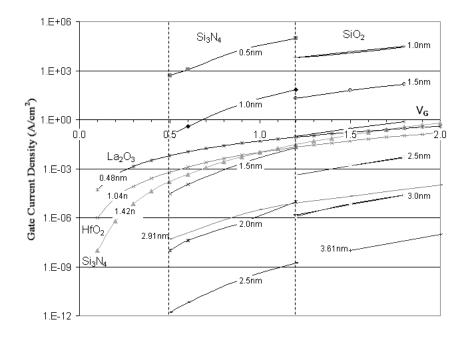

| Figure 71.            | Gate current density (Amp/cm <sup>2</sup> ) vs. gate voltage                                                                                                 | 132        |

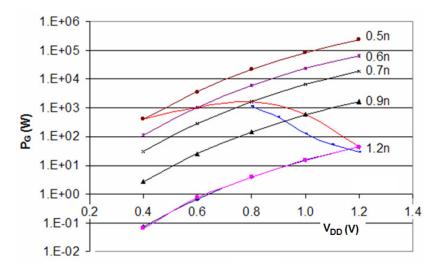

| Figure 72.            | Total gate leakage power vs. supply $(V_{DD})$ at various $T_{OX}$ as shown.                                                                                 | 133        |

| Figure 73.            | Total gate leakage power (a) vs. N and (b) vs. V <sub>DD</sub>                                                                                               | 135        |

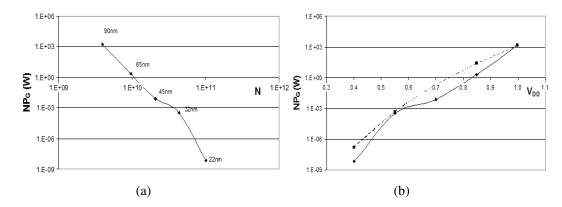

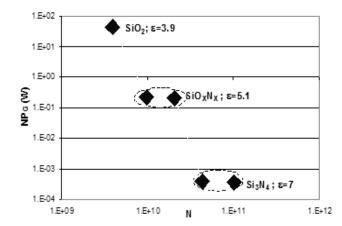

| Figure 74.            | Total gate leakage power vs. N – gate materials as shown.                                                                                                    | 136        |

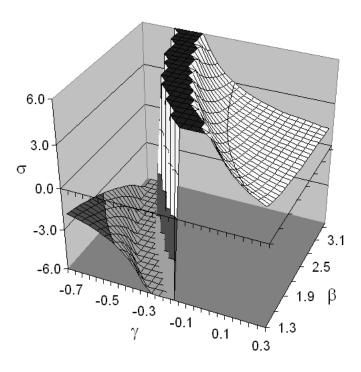

| Figure 75.            | Surface defining $\sigma = \chi/(\chi \gamma + 1)$ as a function of $\beta$ and $\gamma$                                                                     | 141        |

| Figure 76.            | A constant dynamic power scaling surface defined by $F=A^{-1/\sigma}$ vs. $V=A^{-(\sigma-1)/2\sigma}$                                                        |            |

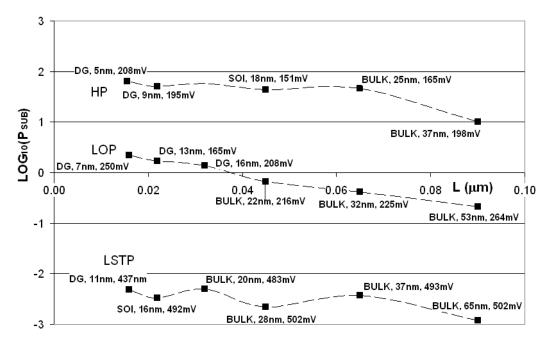

| Figure 77.            | Some ITRS subthreshold current predictions vs. gate length                                                                                                   | 144<br>145 |

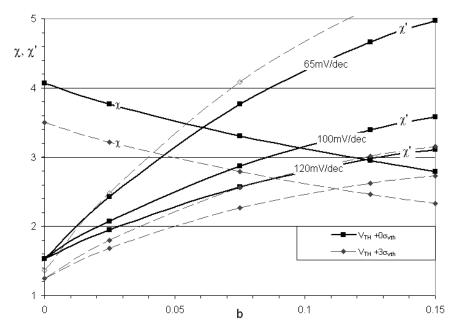

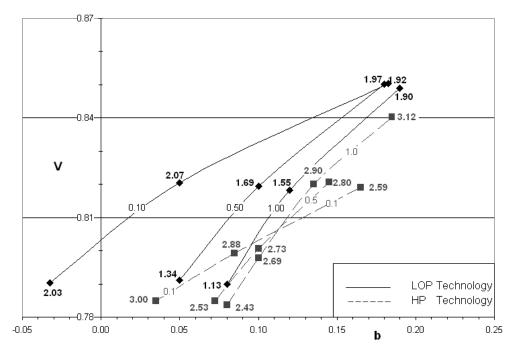

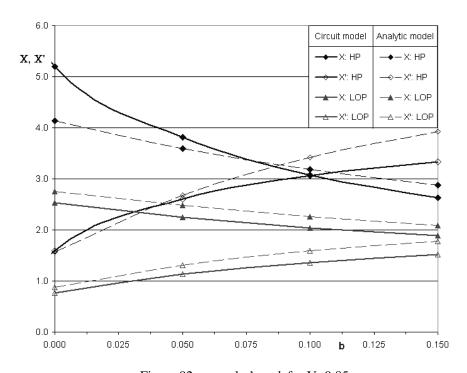

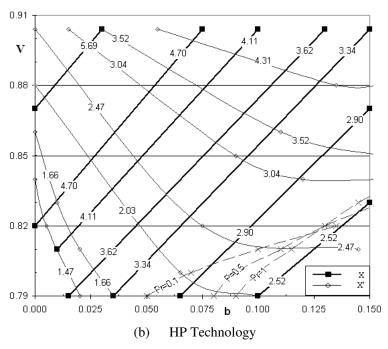

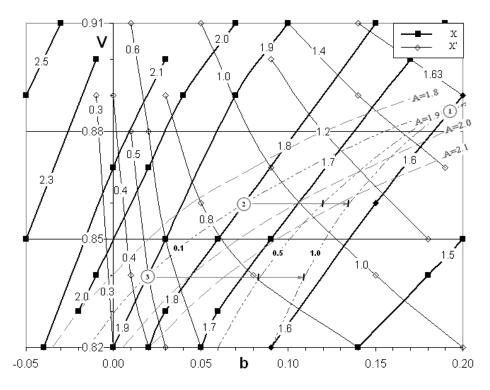

| Figure 78.            | $\chi$ and $\chi'$ vs. b for supply scaling (V) = 0.84                                                                                                       | 150        |

| •                     | Contour plots of $\beta$ (filled squares) and $\eta$ (open diamonds)                                                                                         | 151        |

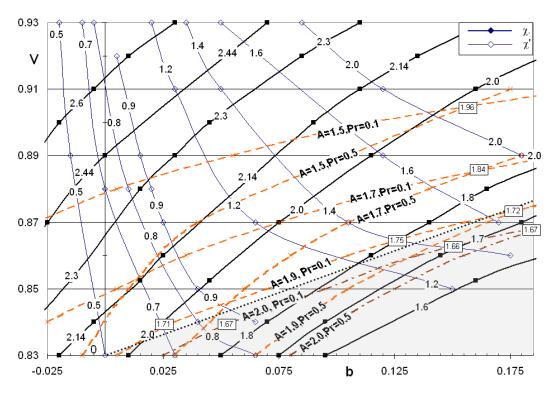

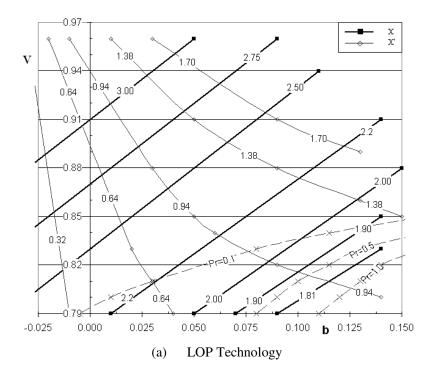

| Figure 79.            |                                                                                                                                                              | 152        |

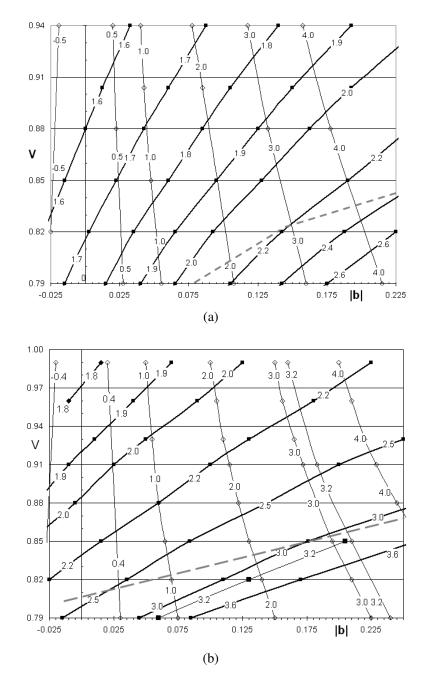

| Figure 80. Figure 81. | Approximate loci of $P_T$ =1.0 in (4.45) for LOP and HP technologies,<br>Contour plots of $\chi$ (filled squares) and $\chi$ ' (open diamonds)               | 154        |

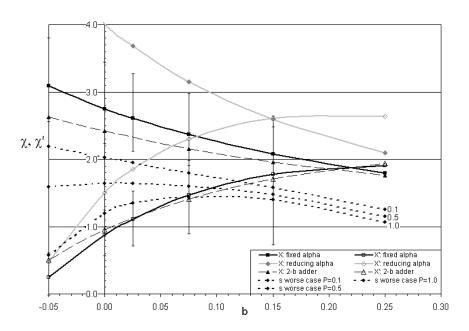

| Figure 82.            |                                                                                                                                                              | 155        |

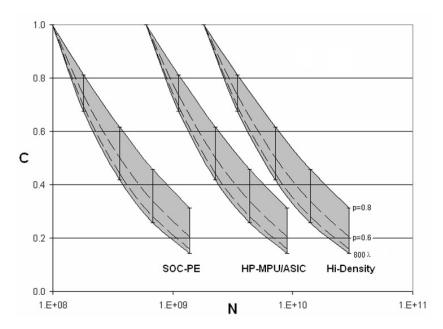

| Figure 83.            | $\chi$ and $\chi$ ' vs. <i>b</i> for supply scaling V = 0.85<br>Interconnect capacitance (C) at successive technology nodes                                  | 155        |

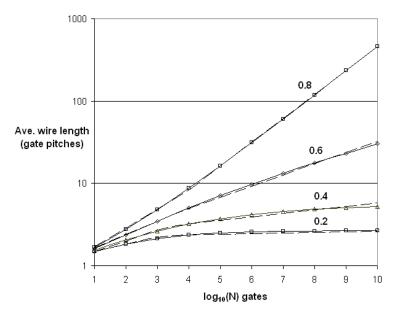

| Figure 84.            | Average wire length as predicted by model of [334]                                                                                                           | 158        |

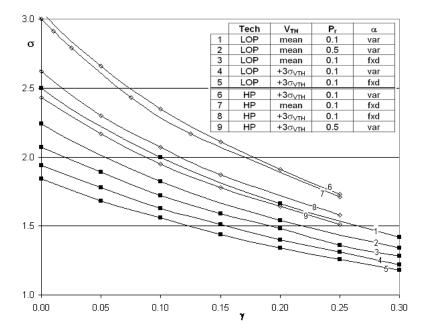

| Figure 85.            | $\sigma(\text{max})$ vs. $\gamma$ over a range of technology conditions.                                                                                     | 162        |

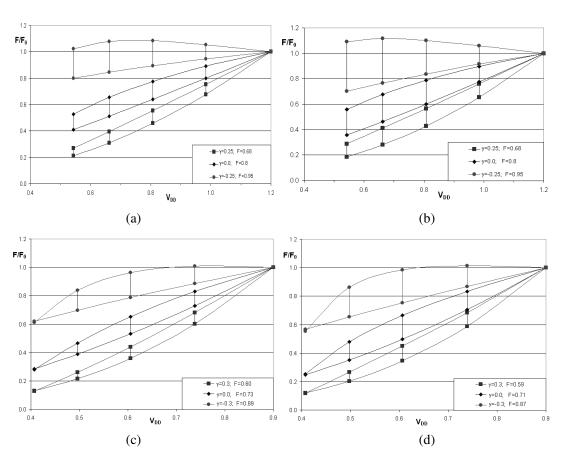

| Figure 86.            | Frequency scaling vs. $V_{DD}$ for $P_T=1.0$ , $P_R=0.1$                                                                                                     | 163        |

| Figure 87.            | $I_D$ vs. $V_{BG}$ for the modified EPFL DGSOI model ( $V_{FG}$ =0).                                                                                         | 169        |

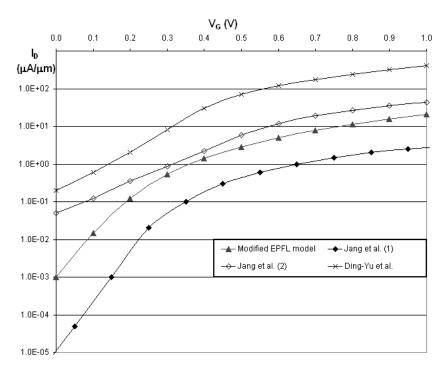

| Figure 88.            | Modified EPFL double-gate model.                                                                                                                             | 171        |

| Figure 89.            | $I_D$ (sat) vs. $V_{GS}$ for the modified EPFL model.                                                                                                        | 172        |

| Figure 90.            | Interface quantities for nMOS and pMOS models.                                                                                                               | 173        |

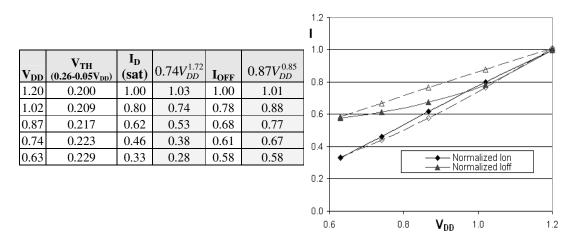

| Figure 91.            | Normalized $I_D(sat) \propto kV_{DD}^{\beta}$ and $I_{OFF} \propto kV_{DD}^{\eta}$ with $V = 0.85$ , $b = 0.05$ .                                            | 174        |

| Figure 92.            | $\chi$ and $\chi'$ vs. $b$ for V=0.85.                                                                                                                       | 174        |

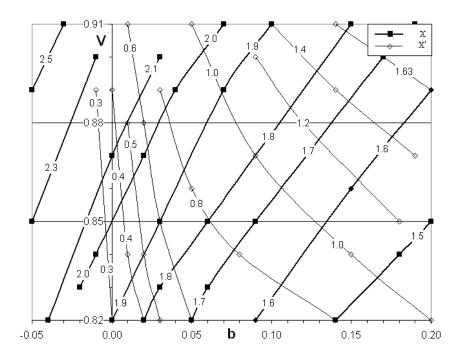

| Figure 93.            | Contour plots of $\chi$ & $\chi$ ' vs. supply (V) and threshold scaling (b), no                                                                              |            |

| riguio 50.            | variability                                                                                                                                                  | ,<br>175   |

List of Figures vii

| Figure 94.  | $\chi$ & $\chi$ ' vs. supply and threshold scaling, variability = +25% $\sigma_{VTH}$ | 176 |

|-------------|---------------------------------------------------------------------------------------|-----|

| Figure 95.  | Delay calculation and application in VHDL-AMS                                         | 178 |

| Figure 96.  | Abstract cell organization and interconnect types                                     | 179 |

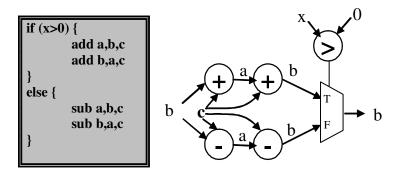

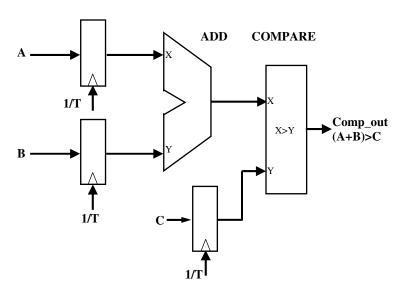

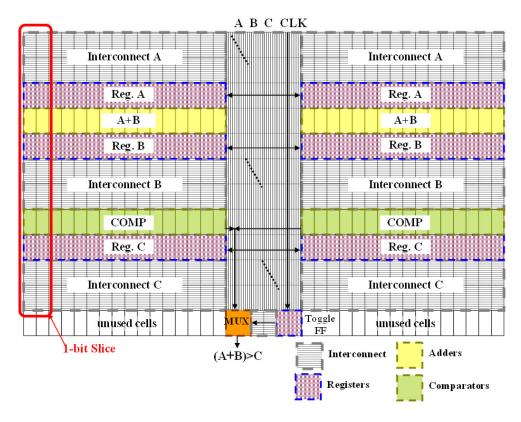

| Figure 97.  | A simple data path (from [209]).                                                      | 180 |

| Figure 98.  | A duplicated version of the simple data path                                          | 181 |

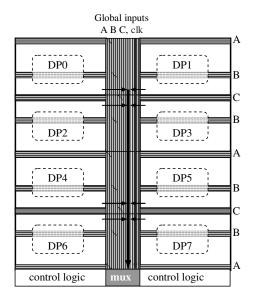

| Figure 99.  | Simplified floorplan for parallel data path of Figure 98                              | 182 |

| Figure 100. | 8-way replicated data path layout.                                                    | 182 |

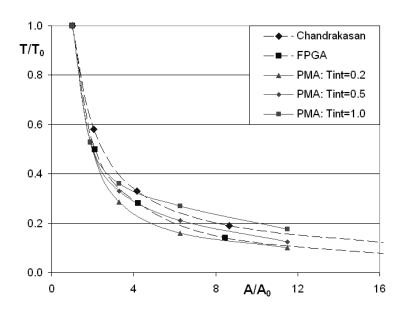

| Figure 101. | Area-Time relationship for the examples of Table 14.                                  | 185 |

| Figure 102. | Contour plots for $\gamma$ (filled squares) and $\gamma$ ' (open diamonds)            | 186 |

List of Figures viii

## List of Tables

| Table 1  | Comparing Minimum Effective Output Resistance (R <sub>ON</sub> ) to Estimated Z <sub>0</sub> |     |

|----------|----------------------------------------------------------------------------------------------|-----|

|          | of M1 for some High Performance Technologies from the ITRS.                                  | 28  |

| Table 2  | Estimated RC values of some potential implementation technologies                            | 33  |

| Table 3  | Approximate technology scaling with time (adapted from [113])                                | 38  |

| Table 4  | Example Area and Time Scaling vs. Delay Overhead.                                            | 60  |

| Table 5  | A Comparison of three parallel architecture classes (from [217])                             | 63  |

| Table 6  | Dynamic Instruction frequency of MIPS-R3000 (based on [234])                                 | 68  |

| Table 7  | Subthreshold leakage power vs. supply voltage, 1-bit CMOS full-adder                         | 91  |

| Table 8  | Subthreshold current vs. back-gate voltage for a simple inverter.                            | 94  |

| Table 9  | Area Comparison for LGSynth93 circuits                                                       | 111 |

| Table 10 | Area results for arithmetic circuit mappings                                                 | 113 |

| Table 11 | Indicative dynamic and subthreshold power estimates for ITRS HP                              |     |

|          | technology.                                                                                  | 146 |

| Table 12 | Example supply-threshold voltage scaling, approximations                                     | 149 |

| Table 13 | Maximum σ Resulting in $P_T=1$ for various $(P_R)_0$ , $\beta$ , $\eta$ and $\gamma$ .       | 161 |

| Table 14 | Normalized scaling characteristics of the simple parallel data path.                         | 183 |

| Table 15 | Predicted voltage and power scaling at numbered points on Figure                             |     |

|          | 102.                                                                                         | 187 |

| Table 16 | Baseline LOP scaling scenario.                                                               | 189 |

| Table 17 | Some example power and performance predictions.                                              | 190 |

List of Tables ix

**Declaration**

This is to certify that:

1. This dissertation comprises only my original work towards the PhD degree carried out

since the official commencement date of the research program;

2. Due acknowledgement has been made in the text to all other material used;

3. No portion of the work referred to in this thesis has been submitted in support of an appli-

cation for another degree or qualification of this or any other University or Institute of

learning.

4. No specific editorial assistance, either paid or unpaid, has been received during the prepa-

ration of this manuscript.

5. Ethics procedures and guidelines have been followed.

**Paul Beckett**

30 August 2007

Declaration x

## Copyright

- The Author asserts copyright over the text of this dissertation. Copies by any process either in full, or of extracts may be made only in accordance with instructions given by the Author.

- 2. Permission to make digital or hard copies of all or part of this work for personal or class-room use is granted provided that copies are not made or distributed for profit or commercial advantage and that the author's copyright is shown on the first page. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission.

- 3. A non-exclusive license is hereby granted to RMIT University or its agents to:

- a. archive and to reproduce this thesis in digital form;

- b. Communicate it to the public by making it available online through the Australian Digital Thesis Program. The author warrants that the thesis does not infringe the intellectual property rights of any person, and indemnifies RMIT University against any loss or liability it may incur in respect of a breach of this warranty.

- 4. The ownership of and rights to any intellectual property that may be described in this dissertation is vested in the RMIT University, subject to any prior agreement to the contrary, and may not be made available for use by third parties without permission of the University, which will prescribe the terms and conditions of any such agreement. Further information on the conditions under which disclosures and exploitation may take place is available from the Head of School, Electrical and Computer Engineering, RMIT University.

Copyright xi

## Acknowledgements

"Sometimes a scream is better than a thesis."

Ralph Waldo Emerson (1803-1882)

This work has relied heavily on simulation facilities provided by the Network for Computational Nanotechnology (NCN) at <a href="http://nanohub.org">http://nanohub.org</a>. It came as something of a surprise to realize that I had made it into the top 50 users launching jobs on the Nanohub, but I'm sure I needed every one of those 2900 runs to make sense of it all.

I have also used some of the Berkeley Predictive Technology Model (BPTM) work, now supported as an online simulation site by the Nanoscale Integration and Modeling (NIMO) Group at the Arizona State University, <a href="http://www.eas.asu.edu/~ptm/">http://www.eas.asu.edu/~ptm/</a>.

All of the curve-fits in Chapters 3–5 were performed at <a href="http://zunzun.com">http://zunzun.com</a>, a brilliant online curve fitting and statistics site created and maintained by James R. Phillips.

The ITRS predictive tool MASTAR (version 4.1.0.5, 2005 as well as the earlier version 2.0.7, 2003) was written by the Advanced Devices Research Team at STMicroelectronics. The tool was downloaded from the ITRS site at <a href="http://www.itrs.net/models.html">http://www.itrs.net/models.html</a>.

I would like to thank Christophe Lallement, Fabien Prégaldiny and the others in the Electronics Group at EPFL for providing two of their advanced, "work-in-progress" versions of the EKV model written in VHDL-AMS. The symmetric double-gate model was particularly important to the final stage of this work.

I would particularly like to thank Dr. Seth Copen Goldstein, Carnegie Mellon University, for providing the original spark for the power-area-performance model and for allowing me to work on developing it into a more complete theory.

Acknowledgements

Dr. Mark Lundstrom, Purdue University, took time out of his busy schedule for some useful early discussions.

Finally, thanks to my two supervisors, Dr. Andrew Jennings and Dr. Mike Austin for their support over the past six years.

And special and heartfelt thanks to my wife, Alexis, for ongoing support and encouragement—and for kicks at just the right moments.

Acknowledgements

## Summary

This thesis focuses on the evolution of digital hardware systems. A reconfigurable platform is proposed and analysed based on thin-body, fully-depleted silicon-on-insulator Schottky-barrier transistors with metal gates and silicide source/drain (TBFDSBSOI). These offer the potential for simplified processing that will allow them to reach ultimate nanoscale gate dimensions.

Technology CAD was used to show that the threshold voltage in TBFDSBSOI devices will be controllable by gate potentials that scale down with the channel dimensions while remaining within appropriate gate reliability limits. SPICE simulations determined that the magnitude of the threshold shift predicted by TCAD software would be sufficient to control the logic configuration of a simple, regular array of these TBFDSBSOI transistors as well as to constrain its overall subthreshold power growth. Using these devices, a reconfigurable platform is proposed based on a regular 6-input, 6-output NOR LUT block in which the logic and configuration functions of the array are mapped onto separate gates of the double-gate device.

A new analytic model of the relationship between power (P), area (A) and performance (T) has been developed based on a simple VLSI complexity metric of the form  $AT^{\sigma}$  = constant. As  $\sigma$  defines the performance "return" gained as a result of an increase in area, it also represents a bound on the architectural options available in power-scalable digital systems. This analytic model was used to determine that simple computing functions mapped to the reconfigurable platform will exhibit continuous power-area-performance scaling behavior.

A number of simple arithmetic circuits were mapped to the array and their delay and subthreshold leakage analysed over a representative range of supply and threshold voltages, thus determining a worse-case range for the device/circuit-level parameters of the model. Finally, an architectural simulation was built in VHDL-AMS. The frequency scaling described by  $\sigma$ , combined with the device/circuit-level parameters predicts the overall power and performance scaling of parallel architectures mapped to the array.

Summary 1

## Chapter 1. Introduction

"...transistor scaling is approaching its limit. When that limit is reached, things must change, but that does not mean that Moore's law has to end."

Mark Lundstrom in [1]

#### 1.1 Overview

transistor, announced to the world on June 30, 1948, was a lump of germanium crystal that took its inventors more than four years to perfect. The first commercially available planar integrated circuit (IC), shipped by Fairchild Semiconductor Corporation in March 1961, comprised one transistor, three resistors and a capacitor [2]. It was largely ignored. To really consolidate the success and scalability of the IC took the development and refinement of processes such as masked diffusion, lithography, planar technology, isolation, high-quality oxide and epitaxy [3] but since then it has been a story of smaller, faster, cheaper to a point where in 2005, world semiconductor capacity was estimated to be more than 1.5 million wafers per week [4]—well over seventy billion transistors per second—in a global market worth more than \$1 trillion a year.

This extravagant abundance has driven the emergence of the modern VLSI microprocessor in which vast numbers of practically identical transistor switches are interconnected to form complex computational networks. For example, in 1999 constructing the Alpha 21264 processor took some 15 million transistors [5]. By 2001 this had grown to 130 million in the 4th-generation Alpha [6]. In 2003, Intel released the Itanium® II processor with 410 million transistors on a single 374mm² chip [7] and the 2005 Montecito® processor contained 1.7 billion-transistors in a multi-core architecture operating at 1.8GHz [8]. It has been predicted that by 2012 a CMOS (or more likely SiGe) chip may comprise some 10<sup>10</sup> transistors operating at speeds in the order of 10–15GHz [9], although this now appears unlikely due to power density constraints.

Devices with gate lengths of less than 100nm were commercially shipped in the year 2000, signal-ling the end of the "Microelectronics Era" and the start of the age of "Nanoelectronics" [10]. As a result, the International Technology Roadmap for Semiconductors (the ITRS, which focuses mainly on CMOS) [11] is now predicting what appears to be the end of the development path for silicon by 2020, when effective gate lengths are likely to be less than 5nm. There is anecdotal evidence to suggest that funding for silicon research is already diminishing as the hunt intensifies for the next technology that will take the integrated circuit beyond that point.

However, even to reach the end of the silicon roadmap the challenges will be formidable.

Amongst a long list of technical difficulties, the ITRS identifies the following issues:

- the rapid growth in power consumption at each successive technology node;

- the need for new architectures to overcome bottlenecks at interconnects;

- escalating difficulties in both lithography and fabrication, leading to spiralling costs.

- the need for more complex structures such as SOI or dual-gate transistors to work around the limitations of short device channels;

The likely nexus between power consumption and architecture has been articulated by the 2003 ITRS as follows: "Below 65 nm, MPU designs hit fundamental walls of performance, power consumption and heat dissipation....Power consumption can be managed only by careful application of on-chip processing parallelism...the future goal of system-level design is to map a maximally parallel function to a maximally parallel implementation....Methodologically, this defines a new design domain that emphasizes distributed implementation over centralized implementation;...Given such trends, standalone MPU design style will likely evolve into a sea-of-processing elements design style." [12].

It is this link between power and parallelism, especially in the context of very fine-grained computing structures built using simplified manufacturing technologies, which has been the primary motivation for this thesis.

Introduction 3

1

<sup>&</sup>lt;sup>1</sup> Dr. Mark Lundstrom, Purdue University, personal communication, 2003

#### 1.2 Motivation and Scope

This work is concerned with the evolution of digital hardware systems as devices scale towards the end of the CMOS roadmap. Although there is a truly vast literature related to the problems to be overcome in order to reach this point, a number of general observations are already possible and these have motivated this research:

- Although the continued scaling of conventional CMOS will eventually reach fundamental

physical limits, forcing a move to alternative materials and structures, there is currently

still scope in CMOS for improved performance at nanoscale dimensions.

- Power density, both static and dynamic, will become the critical issue as device numbers scale that, in itself, has the potential to prevent the deployment of architectures at nanoscale dimensions [13].

- Even taking into account the impact of low-κ interconnect dielectrics, transistor delay

will continue to improve with scaling at a faster rate than wire delay. As a result, communications will increasingly replace processing performance as the limiting factor in

computer architectures [14].

- The rapidly escalating costs of IC design, fabrication and test will increasingly favour simple, regular structures that support flexible hardware configuration and design reuse and that may be reprogrammed and/or reconfigured post-manufacture. This appears to be inevitable for two main reasons:

- Foundry Overheads: as technology moves past the 90nm node, the high costs of

establishing and running an advanced foundry as well as increasing non-recurrent

engineering costs (mainly driven by lithography) mean higher fixed overheads on

each chip produced.

- 2. *Device Reliability:* The manufacture of chips at nanoscale dimensions with 100% working transistors will be prohibitively expensive, if not impossible. Devices

and their interconnections will exhibit lower intrinsic reliability and increased variability. To achieve reasonable yields will require flexible architectures that can "configure around the defects" [15].

• A strong case is emerging for the integrated use of reconfiguration in future nanoscale systems (e.g. [15-18]). While fine-grained array-based reconfigurable systems, such as field-programmable gate arrays, already offer the ability to customize a device to a specific application, their limitations are well known: poor area-delay performance, high (relative) power consumption and large reconfiguration and routing overheads (often more than 10 times the area of the logic [19]) making them a poor match to dense, regular computational structures such as ALUs or memory.

Based on these observations, the research described in this dissertation addresses the following questions:

- Does the escalating cost of design, fabrication and test in future nanoscale systems justify a re-evaluation of homogeneous reconfigurable meshes and can nanoscale electronic devices offer new opportunities for developing these into low-power, low-overhead reconfigurable systems?

- 2. Can a simple, homogeneous, mesh-connected array of reconfigurable components efficiently support the sort of complex heterogeneous processing organizations that characterize typical high-performance computer architectures?

- 3. Can the scalability of reconfigurable meshes be predicted from an architectural perspective?

- 4. Can reconfigurable structures of this type be made sufficiently scalable in terms of performance and power such that very high levels of integration (e.g. >10<sup>11</sup> devices) might be achievable?

#### 1.3 Thesis Statement

As CMOS technology scales towards the end of the silicon roadmap, simple reconfigurable logic function arrays with predominately nearest neighbour connectivity will become feasible building blocks for scalable, low-power digital hardware.

#### 1.4 Research Approach

The issues raised in the research questions above have been addressed at both a device and architectural level, reflecting the observation made by the 2005 ITRS that: "[t]hese challenges demand ...continued mergers between traditionally separated areas of [design technology]" [11]. A hierarchical simulation approach has been used in this thesis work, with each simulation stage being used to validate the models for the next and, at the same time, being cross-checked against results presented in the literature, where available.

As it is difficult to anticipate the impact of future materials and device-level discoveries, current predictions for highly scaled silicon devices must be considered to be speculative. On the other hand, the 2005 ITRS places the end of the silicon roadmap at around 2019–2020 which at the time of writing is at most four scaling generations away. Although it remains to be seen which of the many competing approaches will be successfully integrated into commercial CMOS fabrication lines, it is likely that the most *plausible* technology drivers (i.e., those with the highest likelihood of contributing to so-called "end-of-roadmap" devices) have already been described in some form or other. It is therefore possible to make some realistic predictions about these ultimately scaled devices and the architectures that will be created from them.

To answer the questions outlined in Section 1.2 above, this research has proceeded in four stages, as outlined below. The approach and objectives are summarized in Figure 1.

## 1. Can simple CMOS logic arrays become feasible building blocks at nanoscale dimensions?

The first stage of this research involved setting up a demonstration reconfigurable platform based on a hypothetical thin-body fully-depleted silicon-on-insulator transistor with

metal-gate and silicide source/drain (TBFDSBSOI). These were chosen to represent a plausible end-of-roadmap device technology. At the time this work was undertaken, a small number of planar devices with silicide source/drain had already been reported in the literature, and a similarly small number of nanoscale double-gate silicon devices, but no examples had been published of double-gate silicided source/drain transistors. Thus, the objective here was to characterize the likely performance of this technology and to use it to develop a reconfigurable test platform. The Technology Computer Aided Design (TCAD) results, derived in this work from a commercial TCAD simulator <sup>2</sup>, predict that the threshold voltage in TBFDSBSOI devices will be able to be controlled by gate potentials that scale down with the channel dimensions and that are within appropriate gate reliability limits.

Figure 1. Research approach and objectives encompassing Device, Circuit and Architectural-level simulation.

<sup>&</sup>lt;sup>2</sup> Atlas/SPisces from Silvaco Inc., http://www.silvaco.com/products/device\_simulation/atlas.html

## 2. Can heterogeneous processing organizations be set up using homogeneous meshes of reconfigurable components?

The approximate I-V characteristics derived from TCAD simulation were used to characterize SPICE models that, in turn, were used to show that the magnitude of the threshold shift will be sufficient to constrain the overall subthreshold power of arrays of these TBFDSBSOI transistors, as well as providing a mechanism to control the logic configuration. The result of this stage was the analysis of a highly regular 6-input, 6-output NOR LUT block in which the logic and configuration functions of the array are mapped onto separate gates of a double-gate device. In this way, the array can be configured using the threshold shifts seen at the logic gate resulting from bias changes on the configuration gate. An overall objective here was to determine how this simple array organization might support both combinational and sequential logic.

## 3. Is it possible to predict the scalability of these reconfigurable systems at an architectural level?

An analytic relationship between power (P), area (A) and performance (T) was developed based on a simple VLSI complexity metric of the form:  $AT^{\sigma} = \text{constant}$ . The complexity metric  $\sigma$  defines a bound on the architectural options available in power-scalable digital systems. The objective of this stage was to develop a set of metrics that could be used to evaluate the scaling performance of the reconfigurable array at an abstract level and to determine how the threshold/supply voltage relationship of future technology might impact on this behavior.

#### 4. Can simple reconfigurable arrays scale with high performance and low power?

For this final stage, the model developed previously was used to determine under what circumstances the computing functions mapped to the reconfigurable platform would exhibit continuously scalable power-area-performance characteristics. This comprised two interrelated levels of simulation. Firstly, a device/circuit level simulation was created using simplified EKV transistor models [20] written in the VHDL-AMS mixed-signal lan-

guage (i.e., VHDL with Analog and Mixed-Signal extensions [21]). A representative arithmetic circuit was mapped to the array and its performance used to predict the technology-related parameters for the model designed in the previous stage. Finally, an architectural model was built, also in VHDL-AMS, and used to predict the power-area-performance characteristics of the reconfigurable fabric over the supply range expected for the remaining nodes of the CMOS roadmap.

#### 1.5 Specific Outcomes and Contributions

The work reported in this dissertation has resulted in the following specific outcomes, many of which have been previously reported in the publications listed in Section 1.7:

- The demonstration, by TCAD simulation, that ultra-thin body, double-gated fully depleted SOI transistors will exhibit novel operating behavior that will, in turn, support simple reconfigurable computing meshes.

- The specification and analysis of a regular, mesh-connected array based on the TBFD-SBSOI devices, firstly by low-level TCAD and SPICE simulation and then via a register transfer level (RTL) simulation using behavioral models derived from the previous TCAD and SPICE work.

- A demonstration via high level simulation that this mesh-connected array is logically equivalent to more complex FPGA-like organizations and will support power-scalable reconfigurable systems.

- The development of a new analytic approach to power and energy vs. area based on a traditional architectural complexity metric of the form AT<sup>σ</sup> = K. This defines the limits on the area-performance tradeoffs for architectures that will support massive area scaling.

- The verification by simulation that architectures mapped to the array may be described by the analytic relationship developed between area and power/energy, and that this will predict their ultimate scalability.

#### 1.6 Dissertation Outline

This document is organized as follows:

- Chapter 2 first presents an overview of the general issues that are expected to impact on computer architecture as devices scale to the end of the silicon roadmap. This necessarily encompasses a fairly broad range of device/circuit/architecture considerations.

- Chapter 3 focuses on the *device* and *circuit* level. It describes and analyses the performance of a reconfigurable mesh based on thin-body, double gate silicide devices. This chapter includes TCAD results that characterize the basic TBDGSBSOI devices, as well as the SPICE simulations describing the circuit-level performance of combinational and sequential devices built using a simple 6-NOR building block.

- In Chapter 4, encompasses an architectural level analysis. A new theoretical framework

is described that supports the evaluation of power-area-performance tradeoffs in future

digital logic systems.

- Chapter 5 draws these device/circuit and architecture threads together by applying the

analytic model of Chapter 4 to an evaluation of the scalability of the mesh-connected reconfigurable system proposed in Chapter 3.

- Finally, an overall summary, conclusions and outline for future work can be found in Chapter 6.

#### 1.7 Publications

The following publications have resulted directly from the work described in this dissertation.

P. Beckett and A. Jennings, "Towards Nanocomputer Architecture", presented at the Seventh Asia-Pacific Computer Systems Architecture Conference, ACSAC'2002, Melbourne, Australia, 2002.

- P. Beckett, "A Fine-Grained Reconfigurable Logic Array Based on Double Gate Transistors", presented at IEEE International Conference on Field-Programmable Technology, FPT2002, Hong Kong, 2002.

- P. Beckett, "A Polymorphic Hardware Platform", presented at the 10th Reconfigurable Architectures Workshop, RAW 2003, Nice, France, 2003.

- P. Beckett, "Exploiting Multiple Functionality for Nano-Scale Reconfigurable Systems", presented at the Great Lakes Symposium on VLSI, Washington, USA, 2003.

- P. Beckett, "Low-Power Circuits using Dynamic Threshold Devices", presented at the Great Lakes Symposium on VLSI, Chicago, Il, 2005.

- P. Beckett and S. C. Goldstein, "Why Area Might Reduce Power in Nanoscale CMOS", Presented at IEEE International Symposium on Circuits and Systems, ISCAS'05, Kobe, Japan, May 2005.

- P. Beckett, "A Nanowire Array for Reconfigurable Computing", presented at TenCon 2005,

Melbourne, 21-24 November, 2005.

- P. Beckett, "A Low-Power Reconfigurable Logic Array Based on Double Gate Transistors",

IEEE Transactions on Very Large Scale Integration (VLSI) Systems, accepted for publication

February 2007.

# Chapter 2. Scaling Issues for Future Computer Architecture

"It would appear that we have reached the limits of what it is possible to achieve with computer technology, although one should be careful with such statements, as they tend to sound pretty silly in 5 years."

> Attributed to John von Neumann (1903-1957) http://en.wikiquote.org/wiki/John\_von\_Neumann

This chapter examines a range of issues that will impact on computer architecture as it moves further into deep sub-micron and ultimately the nanoscale domain. There is a rich literature on the likely effect of technology scaling and the particular trends driving it. Broadly, the issues may be divided into fundamental, material/device and circuit/architecture considerations. The fact that many of these are interrelated and therefore cannot be considered in isolation is becoming a problem in itself as technology scales and many of the abstractions that have served the design community well in the past 20–30 years begin to break down. The following analysis is based very loosely on Meindl's hierarchy of limits [22], starting with *fundamental* (physical), *material* and *device* issues and concluding with some of the more abstract issues in nanoscale *circuits* and *architectures*.

#### 2.1 Fundamental Limits to Device Scaling

The primary objective of any system for electronic information processing is the creation of controllable electron barriers [23]. The limits to maximum performance, density and minimum energy arise from the characteristics of these barriers and are ultimately constrained by the basic principles of thermodynamics, quantum mechanics and electromagnetics [22].

#### Thermodynamic Limits

Thermal noise will exist in any electronic system operating above a temperature of absolute zero. Thus, at a given temperature, T, an electron has a finite probability that it will be able to transition *over* a barrier with height  $E_b$  that is given by the classic models as:

$$\Pi = \exp\left(-\frac{E_b}{k_B T}\right) \tag{2.1}$$

$(k_B$  is the Boltzmann constant). In a binary system, it is reasonable to treat a probability of  $\Pi=0.5$  as the point at which it becomes impossible to distinguish between one logic level and another (i.e. between the cases where the information-carrying electron is confined or not). This leads directly to the *Shannon-von Neumann-Landauer (SNL)* expression for the smallest energy required to process a bit at temperature T:  $E_b = kT \ln(2) \approx 17 \text{meV}$  at 300 K [24]. Energy transitions in CMOS right now are typically in the region of  $10^7$  times greater than this. Meindl and Davis [25] use this expression to compute an absolute minimum supply voltage  $(V_{DD})$  for an ideal MOS device (i.e. one with a subthreshold slope of 60 mV/decade at 300 K) of  $V_{DD}(\min) \approx 2(kT/q) \ln(2) \approx 36$  mV at 300 K. Similarly, it was determined in [26] that a  $V_{DD}(\min)$  of approximately 83 mV at 300 K is necessary to maintain a logic gain (A) > 4 in a standard CMOS gate with a fanin of 3.

#### Quantum Mechanical Considerations

A second fundamental limit arises from quantum mechanics, or more particularly from the limitations imposed by quantum mechanical tunneling through the barrier. The (Heisenberg) uncertainty in momentum corresponding to a barrier of height  $E_b$  sets a lower bound on the barrier width  $(a_{min})$  such that [24]:

$$a_{\min} \cong \frac{\hbar}{\sqrt{2m_e E_b}},\tag{2.2}$$

( $m_e$  is the effective electron mass and  $\hbar$  the reduced Planck constant) which sets a minimum room temperature barrier width of:

$$a_{\min} \cong \frac{\hbar}{\sqrt{2m_e k_B T \ln 2}} \approx 1.45nm. \tag{2.3}$$

The smallest transit time for an electron through this barrier results in an absolute minimum delay time and is derived in [23] as:

$$\tau_p = \frac{\pi\hbar}{\Delta E} = \frac{\pi\hbar}{k_b T \ln 2} \approx 0.11 pS , \qquad (2.4)$$

which is (coincidentally) almost the same as the ITRS prediction for gate delay at the 2018 (16nm) node. In contrast, using a method based on material electrostatics, Meindl has calculated a slightly higher unit transit time of 0.33pS for silicon and 0.25pS for GaAs [22].

Meindl also showed that the uncertainty in momentum leads to a bound on the average power (P) transferred during a switching transition ( $\Delta t$ ), i.e., the switching transition of a single electron wave packet, such that:

$$P \ge \frac{h}{(\Delta t)^2} \,. \tag{2.5}$$

As the operation of *all* devices based on charge transport, including Field Effect Transistors plus all of the more esoteric technologies—Resonant Tunneling Devices, Single Electron Transistors, Quantum Cellular Arrays etc.—involves the charging and discharging of capacitances to change the height of the controlling barrier, the energy required to move the barrier is equivalent to the energy required to charge these control capacitances. This energy is eventually dissipated as heat. Using the smallest energy dissipation given by the SNL expression (~17meV), the maximum power density is derived in [23] as:

$$P = \frac{3 \times 10^{-21} \text{J}}{a_{\min}^2 \tau_p} \approx 1.2 \times 10^6 \text{W/cm}^2.$$

(2.6)

Given that current cooling methods are limited to a few hundred watts/cm<sup>2</sup>, this power density is clearly too large to be physically achievable. The inescapable conclusion is that all charge-based nanoscale electronic systems will be ultimately limited by power/energy density regardless of their implementation technology. It is worth noting that although (2.1) exhibits an exponential sensitivity to temperature, cryogenic operation will not change these energy constraints as it

simply exchanges chip dissipation for cooling energy. Refrigeration losses will always result in a substantial increase in the overall "wall-socket" power [23].

#### **Electromagnetics**

Electromagnetic considerations limit the propagation velocity (v) of a pulse to less than the speed of light in free space so that:

$$v = \frac{L}{\tau} \le c_0 \tag{2.7}$$

where L is the line length and  $\tau$  is the transit time across the line. While the free space limit is independent of materials or implementation structure, the propagation of an electromagnetic wave across an interconnect line will be ultimately constrained by the dielectric constant ( $\kappa$ ) of the material surrounding the line. As a rule of thumb, propagation velocity is proportional to  $3.3\sqrt{\kappa}$ , which is approximately 6.5ps/mm for a SiO<sub>2</sub> with  $\kappa \approx 3.9$ .

#### 2.2 Material Limits

Most of the major advances in semiconductor technology over the past 50 years have been achieved using the same basic metal oxide semiconductor [MOS] switching element and with a limited number of materials (primarily Si, SiO<sub>2</sub>, Al, Cu, Si<sub>3</sub>N<sub>4</sub>, TiSi<sub>2</sub>, TiN, and W) [27]. Manufacturing processes have obviously improved over that period, so that feature sizes have reduced by four orders of magnitude while wafer areas have grown by a factor of around 600. However, until the recent (2007) announcement of 45nm processes using a dual-metal gate with hafnium-based hi-κ dielectric [28], no fundamentally new materials or fabrication processes had been introduced that altered the basic transistor topology (Figure 2). To date, there are no obvious successors to silicon MOS technology that offer sufficient improvements to justify their costs. The run to the end of the roadmap will therefore comprise increasingly difficult incremental improvements to MOS, such as high and low-κ dielectrics, silicon-on-insulator and multiple-gate topologies (see Section 2.3, below).

The limits imposed by materials are determined by the properties of the particular materials but are essentially independent of the particular structural features and/or device dimensions [27, 29]. A key limitation to future scaling is the dielectric constant of the insulator materials used in the gate stack and as part of a multi-level interconnection network. The continued use of silicon also imposes limits on the basic switching energy, transit time and thermal conductance as well as on the fluctuations caused by dopant atoms.

Figure 2. Simplified cross section of a modern MOS transistor. (based on [27])

The interface between silicon and its native oxide,  $SiO_2$ , is atomically abrupt and is relatively easy to fabricate with small defect and charge trap densities. It will be difficult for any alternative material to match these almost ideal characteristics. To maintain good channel control, and restrict short-channel effects, the oxide thickness  $(T_{OX})$  must scale with channel length. Various "rules-of-thumb" have been proposed, but it appears that roughly  $T_{OX} < L_g/4$  will ensure adequate gate control. Gate oxide thicknesses will be ultimately constrained by quantum mechanical tunneling of carriers through the insulator. The direct tunneling probability (T) for a rectangular barrier has an exponential form similar to that of (2.1), i.e.:

$$T = e^{\left(-2\sqrt{\frac{2m^*qE_b}{\hbar^2}}T_{OX}\right)} \tag{2.8}$$

where  $m^*$  is the electron effective mass,  $E_b$  the barrier height for the tunneling particle and  $\hbar$  the reduced Planck's constant. Thus, gate current will increase exponentially with decreasing oxide

thickness,  $T_{\rm OX}$ , resulting in excessive standby power at oxide dimensions of less than 1.0–1.5nm (about 5–7 atomic layers). Further, at these dimensions the wave functions of the gate and the silicon substrate begin to overlap, causing scattering and reduced mobility, significantly degrading the switching performance [30]. Insulators with higher dielectric constants will allow the same effective electric field at a thicker  $T_{\rm OX}$ , thus reducing tunneling currents. Silicon nitride ( $\kappa \approx 7.4$ ) is likely to be the first hi- $\kappa$  dielectric to be widely adopted in mass-production, at the 65nm node [31, 32].

#### 2.3 CMOS Device Scaling

CMOS has been the dominant technology in commercial VLSI systems for more than 25 years, during which time transistor gate lengths have shrunk from several microns to typical commercial dimensions of 180 to 130nm [33] and to 90–65nm in high performance systems [34]. Although the semiconductor industry ultimately expects to be able to scale CMOS gate lengths to a few nanometers [11], it is far from clear how this might be achieved. In the near term, it is almost certain to exploit what the ITRS calls "enhanced CMOS" i.e., the integration of new technologies into the standard CMOS fabrication process (Figure 3).

Some early predictions (e.g. [35]) suggested that gains in FET device performance might eventually stall as the minimum effective channel length approaches 30nm at a supply voltage of 1.0V and a gate oxide thickness of about 1.5nm. However, this shows no sign of occurring. Devices with physical gate lengths as small as 10nm have already been built on research lines (e.g. [36-39]) and by mid to late 2006 [40] manufacturers such as Intel, TSMC and Toshiba had successfully mass-produced transistors with sub-25nm gate lengths (i.e. at the 65nm node) and with core voltages of 1.0V. Intel's mass-produced 45nm transistor mentioned above was developed some 2–3 years before the ITRS prediction for this technology, on bulk silicon rather than SOI. The 2005 ITRS now predicts that supply voltage scaling will tend to level out at about 0.5V for low-operating power (LOP) and 0.7V for high performance technology. This can be compared to the theoretical minimum of 2–3kT/q. It is suggested in [41] that when devices operate within their

ballistic region, the optimum value of  $V_{DD}$  *increases* slightly as the channel length decreases due to the effect of increasing static leakage power as gate length reduces, although the effect is small relative to the supply voltage.

Figure 3. Predicted evolution of CMOS technology (adapted from [11] and [42]).

In order to constrain escalating power-densities and at the same time maintain adequate reliability margins, traditional CMOS scaling has relied on the simultaneous reduction of device dimensions, isolation, interconnect dimensions, and supply voltages [35]. Eventually, FET scaling will be limited by a combination of high fields in the gate oxide and channel plus short channel effects that reduce device thresholds and increased subthreshold leakage currents [43]. By 2020 the ITRS is predicting effective gate lengths of 7–12nm (Figure 3) with equivalent gate oxide thicknesses of 5–8Å. Beyond this point, any further performance growth will need to rely on either increased functional integration with an emphasis on circuit and architectural innovations, or on a move to a technology that is not based on the transfer of charge.

#### 2.3.1 Silicon-on-Insulator

Silicon-on-Insulator (SOI) has been suggested as a solution for many of the problems with scaled CMOS. The ITRS predicts its commercial application as early as 2011. Theoretically, small SOI devices do not need channel doping and can therefore be scaled to dimensions below 10nm without running into problems of uncontrollable parameter variations due to the random distribution of dopant atoms [44]. However, difficulties in controlling device parasitics plus the need for tight dimensional control may sabotage potential performance gains [45]. Figure 4a shows a simple SOI device structure in which the thin film channel is totally isolated from the body by a thick oxide (the body oxide, or BOX).

Figure 4. Conventional Silicon On Insulator (SOI) device topology (a) Single-gate SOI and (b) Double-gate SOI.

The double-gate SOI transistor (Figure 4b) is inherently resistant to short-channel effects and can exhibit close to ideal subthreshold performance [46]. Ultra-thin body, fully-depleted, double-gate SOI has already been suggested as an effective low power technology [47] and double-gate devices exhibit additional functionality that make them well suited to reconfigurable architectures. In particular, they can theoretically be built on top of other structures in three-dimensional layouts and they do not require ancillary structures such as body contacts and well structures that enlarge traditional CMOS layouts. Finally, the second (back) gate offers a means of controlling the threshold of the logic device in a way that can used to configure the system. This threshold control mechanism forms the basis of operation of the reconfigurable mesh that will be described in Chapter 3.

#### 2.3.2 Extreme Device Scaling—Schottky Barrier MOSFETs

The increased difficulty in maintaining low off currents (I<sub>OFF</sub>) as channel lengths scale below 50nm has resulted in a revival of interest in Schottky barrier MOSFETs, first described almost 40 years ago [48], in which metal silicides (e.g. PtSi, ErSi etc.) replace the heavily doped silicon source and drain regions (Figure 5) [49-51]. Metal silicides form natural Schottky barriers to silicon substrates, acting to confine carriers and reducing or eliminating the need for impurities in the channel to prevent current flow in the "off" condition [52]. They exhibit several advantages when compared with conventional devices, including the elimination of punch-through and latchup as well as offering a significantly simpler processing technology. As shown in Figure 5, they are also potentially more compact than conventional CMOS due to the elimination of the well(s), body contacts and isolation regions.

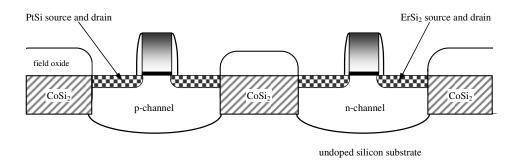

Figure 5. A Schottky barrier CMOS inverter with buried epitaxial self-planarized CoSi<sub>2</sub> local interconnects (adapted from [49]).

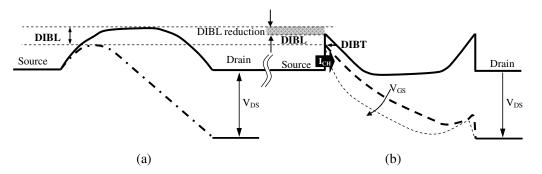

Figure 6. DIBL mechanisms in (a) Double-gate MOSFETs and (b) Schottky barrier FETs showing DIBL reduction in SBFETs (adapted from [53] and [54]).

In conventional short channel MOS devices, an increase in the drain voltage will cause a decrease in the built-in potential between the source and the channel resulting in increased subthreshold current due to DIBL (Drain-Induced Barrier Lowering). In contrast, the subthreshold characteristics of a SB-MOSFET (including DIBL and subthreshold slope) are mainly determined by the barrier itself [53]. The primary switching mechanism (Figure 6) involves a reduction in the thickness of the tunneling barrier between the source and channel under the influence of the gate potential. It can also be seen that an increase in the drain voltage will cause both DIBL and Drain-Induced Barrier Thinning (DIBT) [54] effects to occur simultaneously. The DIBL effect increases the thermionic current over the barrier, whereas DIBT causes a decrease in threshold voltage due to the thinner tunneling barrier.

At the ultimate dimensions for this technology (i.e., gate lengths below 10nm [55]), the channels would effectively become undoped silicon wires with regular silicide patterns forming the source/drain regions. At this scale it is conceivable for them to approach densities of  $10^8$  gates/mm<sup>2</sup>. However, this comes at a cost. The overall current drive of Schottky barrier devices can be significantly lower than MOS due to the very high resistance of their source/drain regions at low supply voltages [56] although it was shown in [57] that the barrier height (and therefore the junction resistance) can be substantially reduced by the inclusion of a thin insulating layer at the metal/semiconductor contact. Any loss in performance implied by an increased  $\tau = CV/I$  would have to be made up either by reducing C (by using local interconnect, for example) or at other levels in the design hierarchy.

#### 2.3.3 Device Variability

Uncontrolled variations in device performance are already critical to analog circuits and, as devices move into the nanoscale domain, they will become increasingly important to digital logic. Three main sources of variability are considered here: global manufacturing uncertainty, local random fluctuations and temperature. As scaling continues, new sources of variability that were negligible in previous generations will increase the local component of the total variance. In [58] it is suggested that the following effects will become dominant: over/under etching of small geometries, proximity effects, doping fluctuations along the channel and lateral diffusion of

dopants between adjacent high-energy implanted wells. To this list can be added atomic scale interface and line edge roughness and increased charge trapping [59, 60].

Traditionally, die-to-die (D2D) variation has been the primary concern although systematic within-die (WID) variation is likely to have a greater effect on future device scaling [61]. In addition, elevated operating temperatures and the presence of "hot-spots" will cause changes to mobility, threshold voltage and subthreshold slope across the surface of the chip. The cumulative effect of all of these variations will be to cause increasingly large uncertainty in key performance metrics including intrinsic delay, switching threshold, noise margins and dynamic and static power.

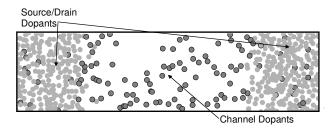

Figure 7. Random placement of impurities in device channel based on [66].

#### Doping Variability