# Signal Processing Using Short Word-Length

A Thesis Submitted in Fulfillment of the Requirements for the Degree of Doctor of Philosophy

Amin Z. Sadik

School of Electrical and Computer Engineering Science, Engineering and Technology Portfolio RMIT University July 2006 © Copyright by Amin Z. Sadik 2006 All Rights Reserved

# Declaration

I certify that except where due acknowledgement has been made, the work is that of the author alone; the work has not been submitted previously, in whole or in part, to qualify for any other academic award; the content of the thesis is the result of work which has been carried out since the official commencement date of the approved research program; and, any editorial work, paid or unpaid, carried out by a third party is acknowledged.

Amin Z. Sadik July 2006 This dissertation is dedicated to my dearest wife Asma and my lovely daughters Samar, Sara, Tara, and Heifa

# Acknowledgements

I would like to thank my family for their endless support and understanding. Special thanks are to my supervisor, Associate Professor Zahir M. Hussain for his generosity and support during my PhD program.

I am also thankful to Associate Professor Peter O'Shea (from Queensland University of Technology, Brisbane) for his support.

Last but not least, I am grateful for the financial support of the Australian Research Council (ARC), which was funding my study and supporting my living expenses during my PhD candidature.

# Publications and Awards

Below are the publications and the awards in conjunction with the author's PhD candidacy:

### Journal Publications

- A. Z. Sadik, Z. M. Hussain, and P. O'Shea, "An adaptive algorithm for ternary filtering," *IEE Electronics Letters*, vol. 42, issue 7, pp. 420-421, March 2006.

- Amin Z. Sadik, Zahir M. Hussain, Xinghuo Yu, and Peter O'Shea, "An approach for stability analysis of a single-bit high-order digital sigma-delta modulator," *Elsevier Journal on Digital Signal Processing*, in press, 2007.

- A. Z. Sadik, Z. M. Hussain, and P. O'Shea, "A Multiplierless DC-blocker for single-bit sigma-delta modulated signals," *EURASIP Journal on Applied Signal Processing*, in press, 2007.

- A. Z. Sadik, Z. M. Hussain, and P. O'Shea, "DC cancellation in the single-bit domain using ternary filtering," *Elsevier Journal on Signal Processing*, Submitted, 2006.

- Amin Z. Sadik, Zahir M. Hussain, Peter O'Shea, and Xinghuo Yu, "Approximate analysis for the dynamics of a third-order sigma-delta modulator," *Signal Processing Journal*, Submitted, 2006.

- A. Z. Sadik and Z. M. Hussain, "A single-bit adaptive LMS-like filtering," IEEE Transactions on Signal Processing, Submitted, 2006.

#### **Refereed Conference Publications**

- A. Z. Sadik, Z. M. Hussain, and P. O'Shea, "Structures for single-bit digital comb filtering," *IEEE Asia-Pacific Conference on Communications* (APCC 2005), pp. 545-548, Perth, Oct. 2005.

- A. Z. Sadik, Z. M. Hussain, and P. O'Shea, "A single-bit digital DCblocker using ternary filtering," *IEEE TENCON 2005*, pp. 1793-1798, Melbourne, Nov. 2005.

- A. Z. Sadik, Z. M. Hussain, and P. O'Shea, "Efficient structure for single-bit digital comb filters and resonators," *IEEE TENCON 2005*, pp. 2061-2065, Melbourne, Nov. 2005.

- 4. A. Z. Sadik, Z. M. Hussain, and P. O'Shea, "Adaptive LMS ternary filtering," *IEEE TENCON 2005*, pp. 2004-2006, Melbourne, Nov. 2005.

- Amin Z. Sadik, Zahir M. Hussain, and Xinghuo Yu, "Stability analysis of a third-order digital sigma-delta modulator," *APCC 2006*, Accepted, 2006.

- Amin Z. Sadik and Zahir M. Hussain, "Limit cycle investigation in a ternary structure," *IEEE TENCON 2006*, Accepted, 2006.

- Amin Z. Sadik and Zahir M. Hussain, "New DSP Using Short Word-Length," International DSP Creative Design Contest (DSPCDC'2006), Southern Taiwan University of Technology (STUT), Ministry of Education, R.O.C., Nov 20-22 2006.

- Amin Z. Sadik and Zahir M. Hussain, "Short Word-Length LMS Filtering," International Symposium on Signal Processing and its Applications (ISSPA 2007), Accepted, UAE, Sharjah, February, 2007

#### Awards

Best Paper Award in IEEE TENCON 2005 (Melbourne, Australia, Nov. 2005) for my paper "A Single-Bit Digital DC-Blocker Using Ternary Filtering."

#### Publications and Awards

- Best Paper Award in the International DSP Creative Design Contest (DSPCDC'2006), Southern Taiwan University of Technology (STUT), Ministry of Education, R.O.C., Nov 20-22 2006 for my paper "New DSP Using Short Word-Length"

- 3. The Technical Award of the International DSP Creative Design Contest (DSPCDC'2006), Southern Taiwan University of Technology (STUT), Ministry of Education, R.O.C., Nov 20-22 2006 for the creativity in the proposed 1b/2b systems as an alternative to existing multibit DSP systems.

# Keywords

Ternary filtering, single-bit sigma-delta modulator, comb filtering, DC blocker, Digital Phased-locked loop (DPLL), circle map, limit cycle, stability, leastmean-square algorithm (LMS), block-LMS (BLMS), ternary adaptive filter, single-bit adaptivity, 2-bit adaptive filter.

# Preface

The well-known multi-bit digital signal processing (DSP) suffers mainly from the complexity of the multipliers and the inefficient chip area utilization in VLSI technology. In the last two decades, single-bit and ternary processing systems, based on sigma-delta modulating (SDM), have been presented as potential alternatives to the conventional DSP. The increased effective speed expected for the new short word-length techniques should translate into massive cost savings and increased flexibility for many electronic systems. Unfortunately, there are many issues in the above alternatives that are unresolved.

This thesis is primarily concerned with the development of an efficient DSP using ternary and single-bit techniques which would hopefully be equivalent to the conventional DSP in future. It is expected that developments in this area would result in VLSI chip economy and reduced cost for electronics consumers.

I hope that this work will help researchers working in DSP, communications, and related topics and inspire further research in these fields.

Amin Z. Sadik

Melbourne July 2006

# Contents

| De       | eclara         | ation i                            |  |

|----------|----------------|------------------------------------|--|

| Ac       | knov           | vledgements iii                    |  |

| Ρu       | ıblica         | ations and Awards iv               |  |

| Ke       | eywo           | rds vii                            |  |

| Pr       | eface          | e viii                             |  |

| Lis      | st of          | Acronyms and Principal Symbols xxi |  |

| Ał       | Abstract xxiii |                                    |  |

| 1        | Intr           | oduction 1                         |  |

|          | 1.1            | The Conventional Multi-Bit DSP     |  |

|          | 1.2            | Thesis Objectives                  |  |

|          |                | 1.2.1 Research Questions           |  |

|          |                | 1.2.2 Research Aims 3              |  |

|          | 1.3            | Original Contributions             |  |

|          | 1.4            | Thesis Organization                |  |

| <b>2</b> | Lite           | rature Review 9                    |  |

|          | 2.1            | Introduction                       |  |

|          | 2.2            | Sigma-Delta Modulation             |  |

|          |      | 2.2.1 The Limit Cycle Behavior in $\Sigma \Delta M$                       |           | 18 |

|----------|------|---------------------------------------------------------------------------|-----------|----|

|          |      | 2.2.2 Problems with $\Sigma \Delta M$ Analysis                            |           | 20 |

|          |      | 2.2.3 The Alternative Analysis Approaches                                 |           | 21 |

|          |      | 2.2.4 Adaptive Scaling Schemes in $\Sigma \Delta M$ 's                    |           | 22 |

|          | 2.3  | Efficient Filters                                                         |           | 24 |

|          |      | 2.3.1 Fast FIR Filters                                                    |           | 26 |

|          |      | 2.3.2 Single-Bit Filtering Techniques                                     |           | 31 |

|          | 2.4  | Summary                                                                   |           | 34 |

| 3        | Sing | le-Bit Ternary Filtering Using Sigma-Delta Mo                             | dulation  | 35 |

|          | 3.1  | Introduction                                                              |           | 35 |

|          | 3.2  | Ternary FIR Filter                                                        |           | 36 |

|          | 3.3  | Summary                                                                   |           | 41 |

| 4        | DSI  | Applications Using Single-Bit Filtering: Comb                             | Filtering | 43 |

|          | 4.1  | Introduction                                                              |           | 43 |

|          | 4.2  | A Proposed Ternary-Sigma-Delta Comb Filter                                |           | 44 |

|          |      | 4.2.1 Design and Simulation of Ternary Sigma-Del                          | ta Comb   |    |

|          |      | Filter                                                                    |           | 47 |

|          | 4.3  | A Proposed Sigma-Delta Comb Filter                                        |           | 50 |

|          | 4.4  | A Proposed Design Approach                                                |           | 52 |

|          |      | 4.4.1 Theory and Design                                                   |           | 55 |

|          |      | 4.4.2 The Proposed Structure                                              |           | 57 |

|          |      | 4.4.3 Simulation and Discussion                                           |           | 59 |

|          | 4.5  | Stability of the Proposed Structures                                      |           | 60 |

|          | 4.6  | Summary                                                                   |           | 61 |

| <b>5</b> | DSI  | • Applications Using Single-Bit Filtering: DC B                           | locking   | 66 |

|          | 5.1  | Introduction                                                              |           | 66 |

|          | 5.2  | $\Sigma\Delta\text{-}\mathrm{Ternary}$ DC Blocker: System Design $\hdots$ |           | 68 |

|          |      | 5.2.1 The Ternary Filtering Stage                                         |           | 68 |

|          |      | 5.2.2 The $\Sigma\Delta$ Modulator Stage                                  |           | 71 |

|   |     | 5.2.3   | The DC Blocker                                                             | . 72  |

|---|-----|---------|----------------------------------------------------------------------------|-------|

|   |     | 5.2.4   | Simulation and Discussion                                                  | . 74  |

|   | 5.3 | A Pro   | posed Structure for DC Canceling in Single-Bit Domain                      | . 82  |

|   |     | 5.3.1   | Design and Analysis                                                        | . 82  |

|   |     | 5.3.2   | Simulation and Discussion                                                  | . 86  |

|   |     | 5.3.3   | Stability                                                                  | . 89  |

|   | 5.4 | Summ    | nary                                                                       | . 95  |

| 6 | Lin | nit Cyc | cle Behavior in Ternary Structures                                         | 96    |

|   | 6.1 | Introd  | luction                                                                    | . 96  |

|   | 6.2 | Analy   | sis of a Third-Order $\Sigma\Delta$ Topology $\ldots \ldots \ldots \ldots$ | . 97  |

|   | 6.3 | The H   | High-Order $\Sigma\Delta$ Topology                                         | . 101 |

|   | 6.4 | Behav   | vior of the System's Limit Cycles                                          | . 102 |

|   |     | 6.4.1   | Limit Cycle Notation                                                       | . 102 |

|   |     | 6.4.2   | Zero-Input Limit Cycles                                                    | . 105 |

|   |     | 6.4.3   | Limit Cycles for Non-Zero DC Input                                         | . 108 |

|   | 6.5 | Concl   | usion                                                                      | . 111 |

| 7 | A S | tabilit | y of Sigma-Delta Modulators in Ternary Structure                           | es113 |

|   | 7.1 | Introd  | luction                                                                    | . 113 |

|   | 7.2 | Stabi   | ility Analysis of the Third-Order Topology                                 | . 114 |

|   |     | 7.2.1   | Non-Linear Dynamics Modeling                                               | . 116 |

|   |     | 7.2.2   | Traditional Stabilizing Design Approach                                    | . 117 |

|   |     | 7.2.3   | Fixed Point Approximation: An Analogy with DPLL .                          | . 118 |

|   | 7.3 | Summ    | nary                                                                       | . 124 |

| 8 | Sho | ort-Wo  | rd Length LMS-Like Adaptive Filtering                                      | 125   |

|   | 8.1 | Introd  | luction                                                                    | . 125 |

|   | 8.2 | An Ao   | daptive Ternary Algorithm:                                                 | . 128 |

|   |     | 8.2.1   | Simulation and Discussion:                                                 | . 131 |

|   |     | 8.2.2   | Discussion:                                                                | . 132 |

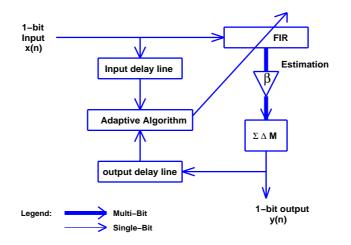

|   | 8.3 | A Sin   | gle-Bit Adaptive Approach                                                  | . 135 |

|              |       | 8.3.1   | Gradient Approximation                                   | . 136 |

|--------------|-------|---------|----------------------------------------------------------|-------|

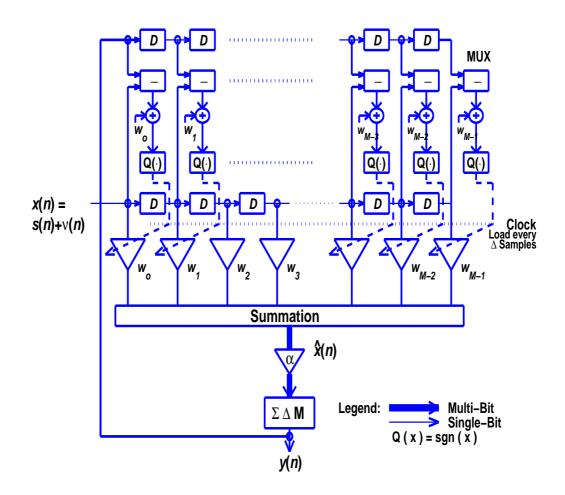

|              |       | 8.3.2   | System Design                                            | . 139 |

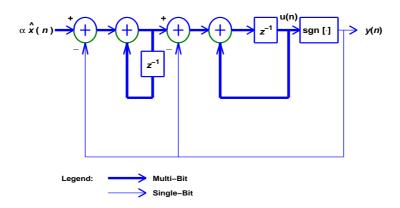

|              | 8.4   | Stabili | ty of SBLL                                               | . 143 |

|              |       | 8.4.1   | Dynamic Range of the SD Modulator                        | . 144 |

|              |       | 8.4.2   | The Updating Step-Size                                   | . 144 |

|              | 8.5   | Simula  | tion and Discussion                                      | . 145 |

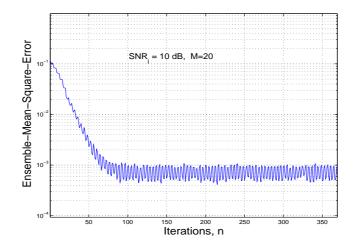

|              |       | 8.5.1   | Learning Curves                                          | . 146 |

|              |       | 8.5.2   | Signal-to-Noise Ratio (SNR)                              | . 148 |

|              |       | 8.5.3   | Non-Stationary Inputs                                    | . 150 |

|              | 8.6   | A Two   | -Bit LMS-Like Adaptive Filtering                         | . 152 |

|              |       | 8.6.1   | Performance Comparison                                   | . 153 |

|              | 8.7   | Summ    | ary                                                      | . 154 |

| 9            | Con   | clusio  | ns and Future Work                                       | 158   |

|              | 9.1   | Conclu  | isions                                                   | . 158 |

|              | 9.2   | Future  | e Work                                                   | . 160 |

| $\mathbf{A}$ | Rec   | ursive  | Equation of Third-Order $\Sigma\Delta$ Topology          | 162   |

| в            | The   | Equiv   | valent Function $f(k)$                                   | 166   |

| $\mathbf{C}$ | Diff  | erence  | Equation of $M^{\text{th}}$ -Order $\Sigma\Delta$ System | 169   |

| Bi           | bliog | graphy  |                                                          | 171   |

| V            | [TA   |         |                                                          | 187   |

# List of Figures

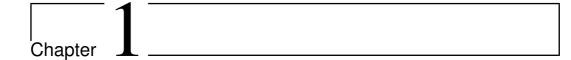

| 2.1  | Block diagram of the basic $\Sigma \Delta M$                                       | 11 |

|------|------------------------------------------------------------------------------------|----|

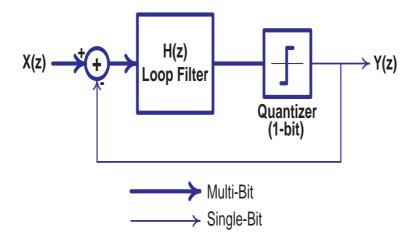

| 2.2  | Linear model of a quantizer.                                                       | 15 |

| 2.3  | Block diagram of the first-order $\Sigma\Delta M$ with a linear model for the      |    |

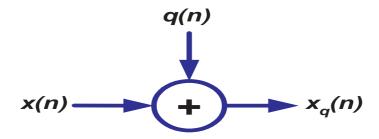

|      | quantizer                                                                          | 16 |

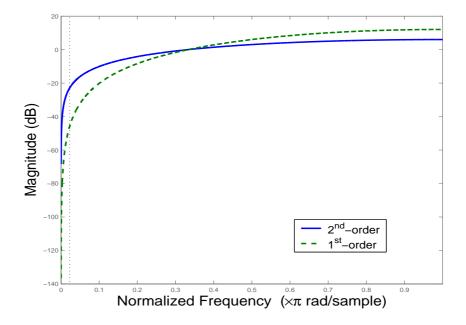

| 2.4  | A comparison between the NTF for a first- and second-order $\Sigma\Delta M.$ .     | 17 |

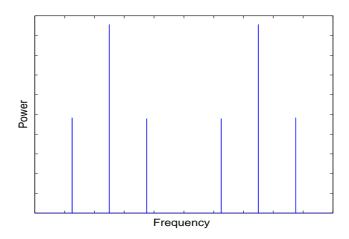

| 2.5  | Limit cycles consist of discrete lines in the frequency spectrum                   | 18 |

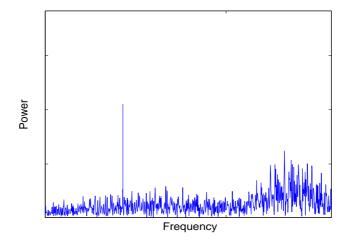

| 2.6  | Idle tones are peaks in the frequency spectrum but superimposed on                 |    |

|      | a noise background.                                                                | 19 |

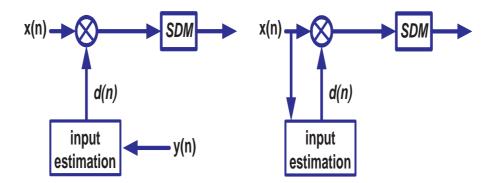

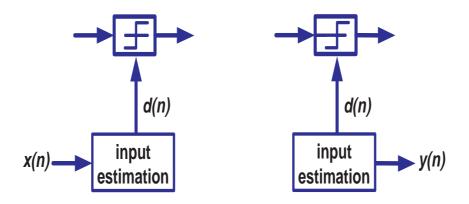

| 2.7  | Adaptation schemes used in ASA: Input scaling                                      | 23 |

| 2.8  | Adaptation schemes used in ASA: output scaling                                     | 24 |

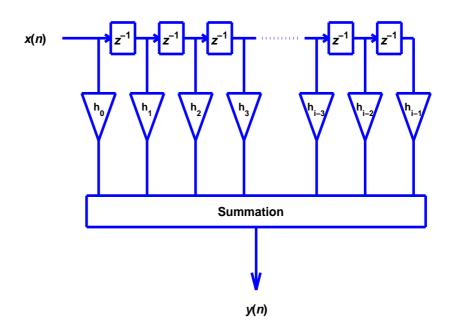

| 2.9  | Block diagram of a traditional FIR filter                                          | 25 |

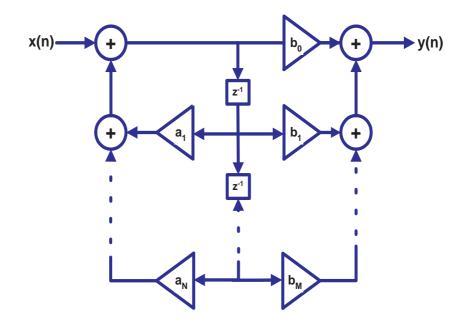

| 2.10 | Block diagram of an IIR direct form II filter                                      | 26 |

| 2.11 | Block diagram of the error feedback $\Sigma\Delta M$                               | 28 |

| 2.12 | Block diagram of the FIR filter with $\Sigma\Delta$ modulated filter coefficients. | 29 |

| 2.13 | Block diagram of the decoder used in FIR filter with $\Sigma\Delta$ modulated      |    |

|      | filter coefficients and with $\Sigma\Delta$ modulated input signal                 | 29 |

| 2.14 | Block diagram of the FIR filter with $\Sigma\Delta$ modulated input signal         | 30 |

| 2.15 | Block diagram of the single-bit FIR filter.                                        | 32 |

| 2.16 | Block diagram of the first order single-bit IIR filter                             | 33 |

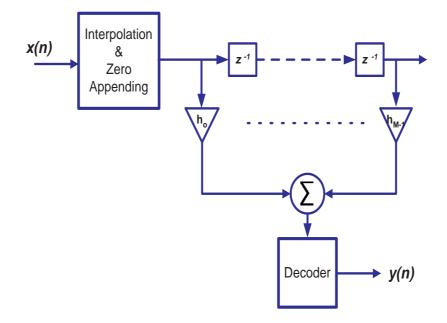

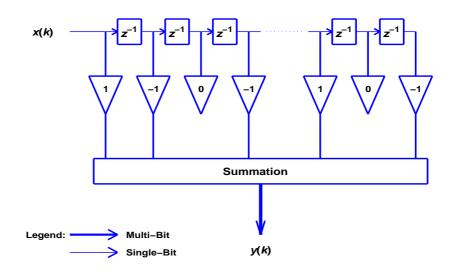

| 91   | Plack diamana of a tannamy FID filton                                              | 26 |

| 3.1  | Block diagram of a ternary FIR filter.                                             |    |

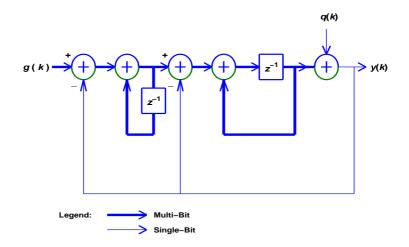

| 3.2  | Block diagram of the 2nd-order $\Sigma\Delta$ modulator.                           | 37 |

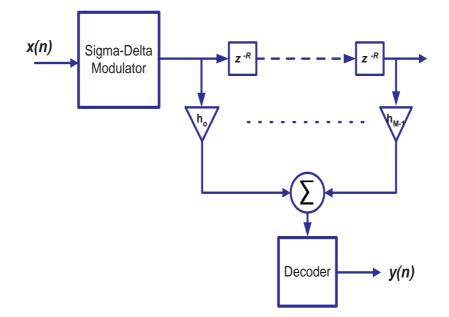

| 3.3  | Block diagram of the digital $\Sigma\Delta$ FIR-like bit-stream filter proposed              |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | in [4]                                                                                       | 38 |

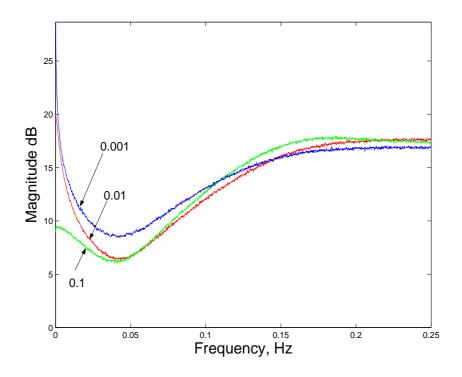

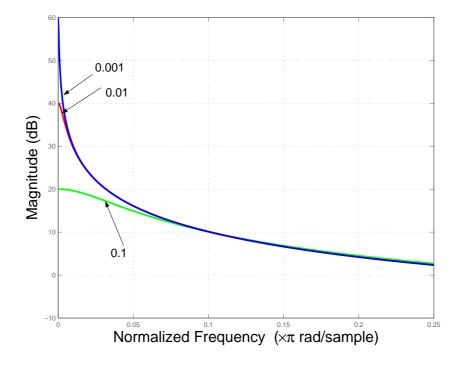

| 3.4  | Simulated frequency response of the single-bit IIR filter for different                      |    |

|      | values of $\alpha = 0.1, 0.01$ , and 0.001                                                   | 41 |

| 3.5  | Theoretical frequency response of the single-bit IIR filter with $\alpha$ =                  |    |

|      | 0.1, 0,01, and 0.001                                                                         | 42 |

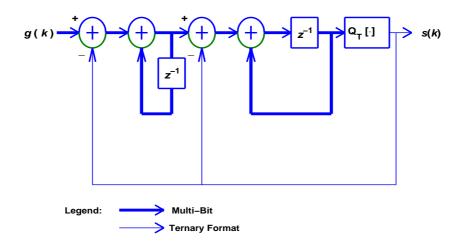

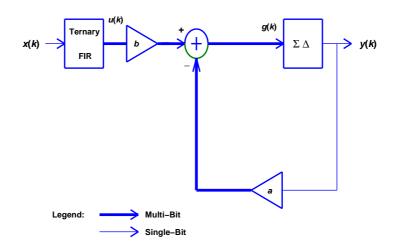

| 4.1  | Block diagram of the ternary $\Sigma\Delta$ filter.                                          | 44 |

| 4.2  | Block diagram of a ternary FIR filter.                                                       | 45 |

| 4.3  | Block diagram of a second-order $\Sigma\Delta M$ with ternary quantizer $Q_T[.]$ .           | 45 |

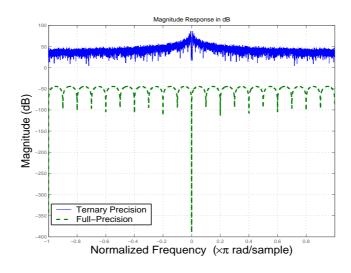

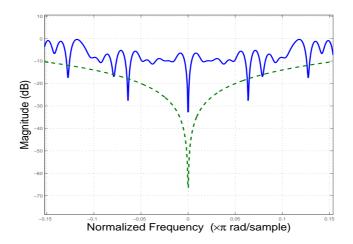

| 4.4  | Frequency response of the ternary filter in the proposed comb structure.                     | 48 |

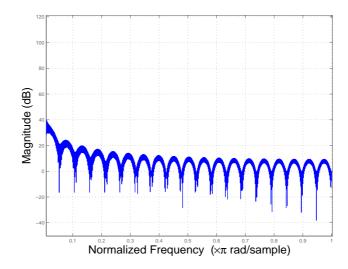

| 4.5  | Frequency Response of the proposed ternary- $\Sigma\Delta$ single-bit comb fil-              |    |

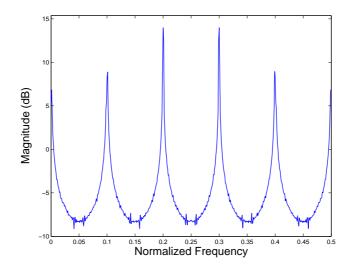

|      | ter with $OSR = 128.$                                                                        | 49 |

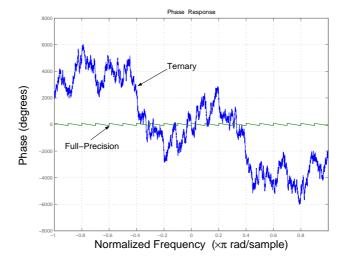

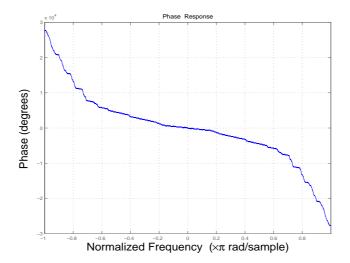

| 4.6  | Phase response of the proposed single-bit ternary- $\Sigma\Delta$ comb filter                | 49 |

| 4.7  | Block diagram of the proposed $\Sigma\Delta M$ structure.                                    | 51 |

| 4.8  | Noise and signal transfer functions of the proposed $\Sigma\Delta$ single-bit                |    |

|      | comb filter                                                                                  | 51 |

| 4.9  | Frequency Response of the proposed $\Sigma\Delta$ single-bit comb filter                     | 52 |

| 4.10 | Phase Response of the proposed $\Sigma\Delta$ single-bit comb filter                         | 53 |

| 4.11 | Block diagram of a second-order $\Sigma \Delta M$                                            | 54 |

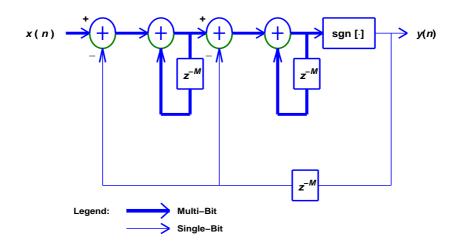

| 4.12 | Block diagram of the proposed single-bit $\Sigma\Delta$ based digital comb filter.           | 58 |

| 4.13 | Block diagram of the designed M-period resonator.                                            | 63 |

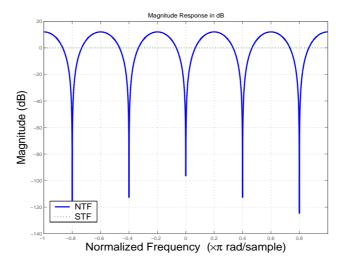

| 4.14 | Noise transfer function, $NTF(e^{j\Omega})$ and signal transfer function, $STF(e^{j\Omega})$ | )  |

|      | for the designed single-bit M-period resonator                                               | 63 |

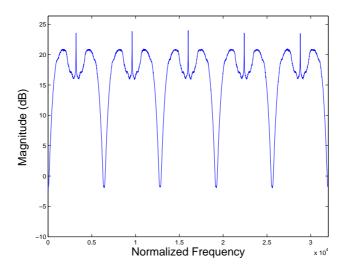

| 4.15 | Frequency Response of the proposed single-bit M-period resonator                             |    |

|      | filter order $M = 10$ and OSR, $R = 64$                                                      | 64 |

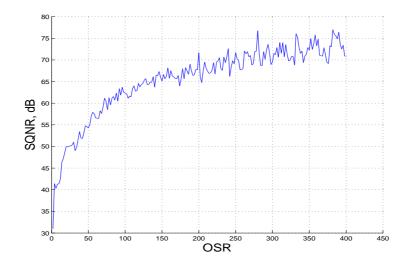

| 4.16 | SQNR against OSR with input signal amplitude of 0.5                                          | 64 |

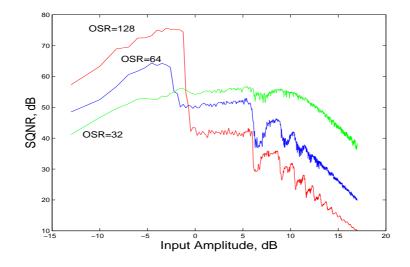

| 4.17 | SQNR of the proposed single-bit comb filter versus the input ampli-                          |    |

|      | tude for different values of OSR                                                             | 65 |

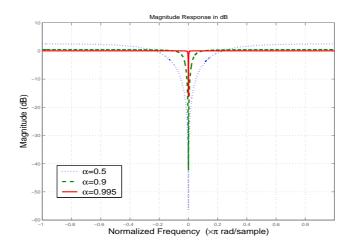

| 5.1  | Frequency response of ideal multi-bit DC blocker for different values             |    |

|------|-----------------------------------------------------------------------------------|----|

|      | of the gain parameter $\alpha$ =0.5, 0.9, and 0.995                               | 69 |

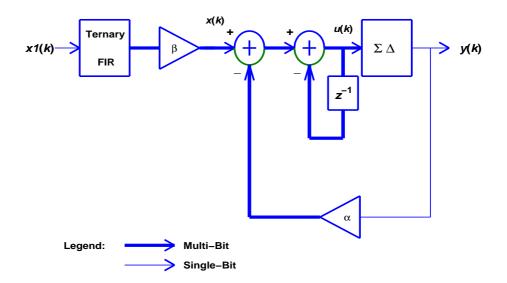

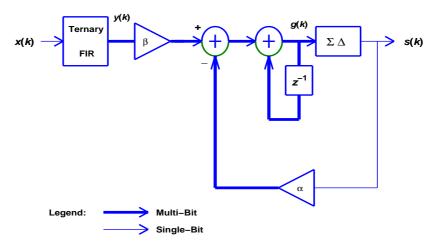

| 5.2  | Structure of the proposed single-bit ternary DC blocker                           | 74 |

| 5.3  | A block diagram of the linear model for a second-order $\Sigma\Delta$ modulator.  | 75 |

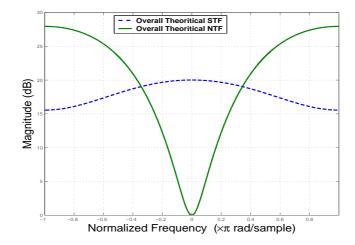

| 5.4  | Frequency response of the theoretical STF (dotted) and NTF (solid) $\$            |    |

|      | for $b=10$ and $a=0.001$ .                                                        | 75 |

| 5.5  | Frequency response of the ternary filter stage using Remez technique,             |    |

|      | compared with the target response (dashed line)                                   | 76 |

| 5.6  | Frequency response of the ternary filter stage using IFIR technique               | 76 |

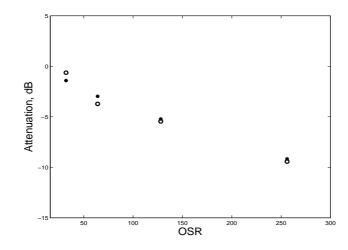

| 5.7  | Signal attenuation in ternary filter stage against the OSR for $b = 1.6$          |    |

|      | and $a = .01$ . (*) Remez. (o) IFIR                                               | 78 |

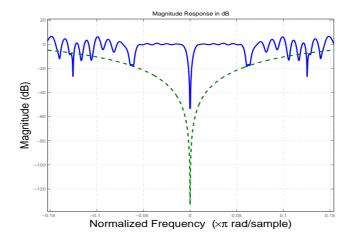

| 5.8  | The overall frequency response of the ternary- $\Sigma\Delta M$ single-bit DC     |    |

|      | blocker.                                                                          | 79 |

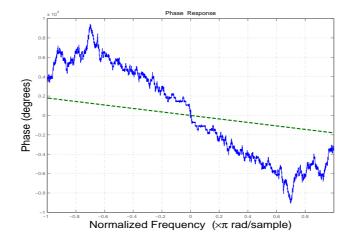

| 5.9  | The overall phase response of the ternary- $\Sigma\Delta M$ single-bit DC blocker |    |

|      | (solid), compared with the phase response of the target impulse re-               |    |

|      | sponse (dashed).                                                                  | 79 |

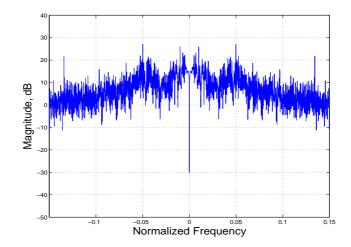

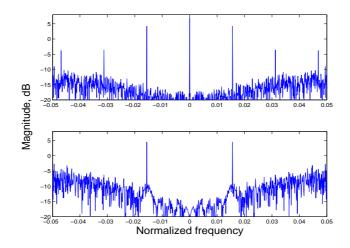

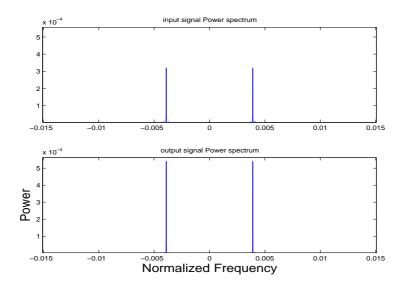

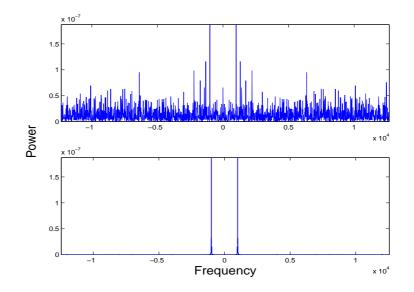

| 5.10 | Spectra of the single-bit input and the single-bit output of the pro-             |    |

|      | posed DC blocker. Above: noisy sinusoid input spectrum. Below:                    |    |

|      | output spectrum.                                                                  | 80 |

| 5.11 | Spectra of the single-bit input FM and the single-bit output of the               |    |

|      | proposed DC blocker. Above: input spectrum. Below: output spec-                   |    |

|      | trum                                                                              | 80 |

| 5.12 | Spectra of the single-bit input AM-FM and the single-bit output of                |    |

|      | the proposed DC blocker. Above: input spectrum. Below: output                     |    |

|      | spectrum                                                                          | 81 |

| 5.13 | Reconstructed sawtooth DC-biased input signal from the single-bit                 |    |

|      | DC blocker                                                                        | 81 |

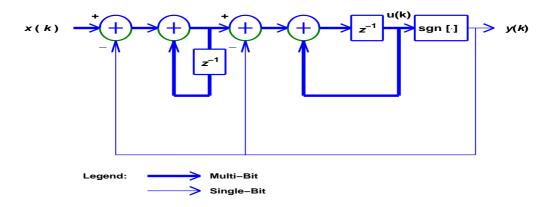

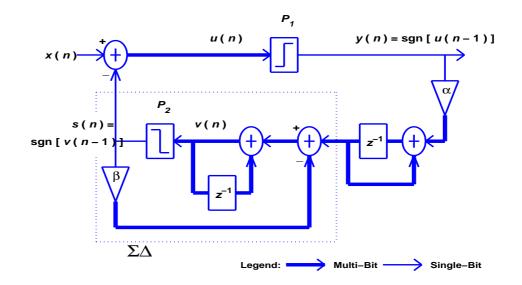

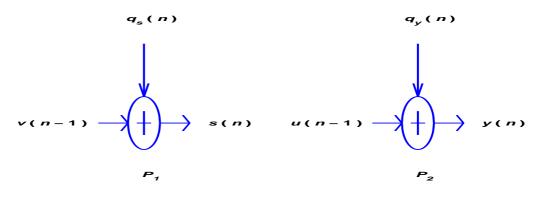

| 5.14 | The proposed DC-blocker.                                                          | 83 |

| 5.15 | Linear model approximation of the system quantizers                               | 83 |

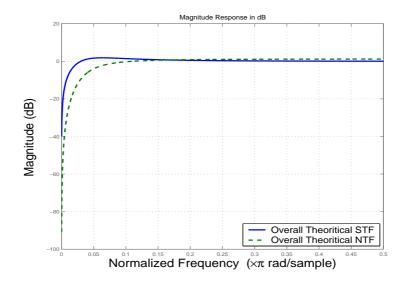

| 5.16 Signal and noise transfer functions, $\text{STF}(e^{j\Omega})$ and $\text{NTF}_y(e^{j\Omega})$ , of the                                   | е      |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| DC blocker using first-order SDM with $\alpha = 0.0205$ and $\beta = 0.2705$ .                                                                 | . 85   |

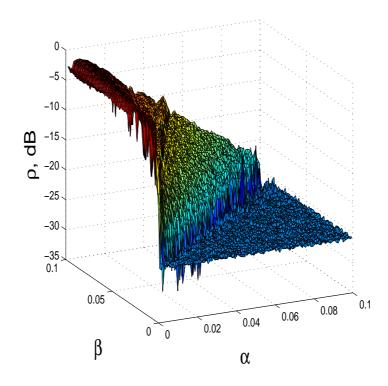

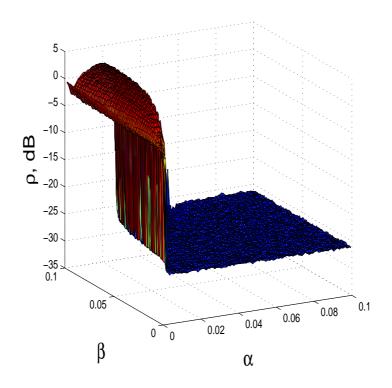

| 5.17 The ratio $\rho = \text{SNR}_{\text{ovo}}/\text{SNR}_{\text{ovi}}$ (in dB) versus the gain parameters $\sigma$                            | χ      |

| and $\beta$ using 10-bit resolution.                                                                                                           | 87     |

| 5.18 The ratio $\rho$ versus the gain parameters $\alpha$ and $\beta$ (10-bit resolution                                                       | )      |

| of the DC blocker using a second-order SDM                                                                                                     | 88     |

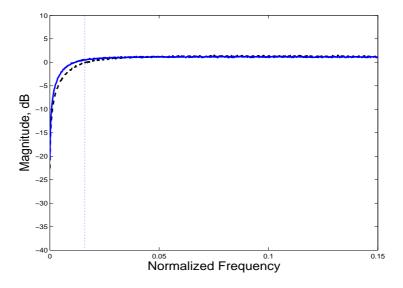

| 5.19 Frequency response of the simulated DC-blocker: (solid) using second                                                                      | 1-     |

| order SDM ( $\alpha_m = 0.0127, \beta_m = 0.0508$ ); (dashed) using fist-orde                                                                  | r      |

| SDM ( $\alpha_m = 0.0205, \beta_m = 0.2705$ )                                                                                                  | 89     |

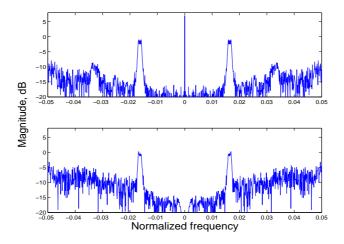

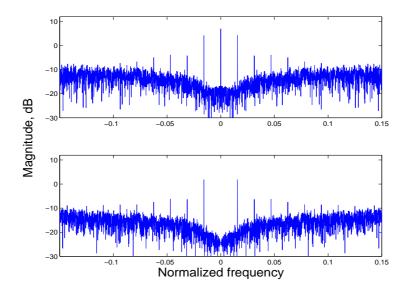

| 5.20 Input and output spectra of the DC blocker (using a second-orde                                                                           | r      |

| SDM) for an FM input.                                                                                                                          | 90     |

| 5.21 Input and output spectra of the DC blocker (using a second-orde                                                                           | r      |

| SDM) for an FM input.                                                                                                                          | 90     |

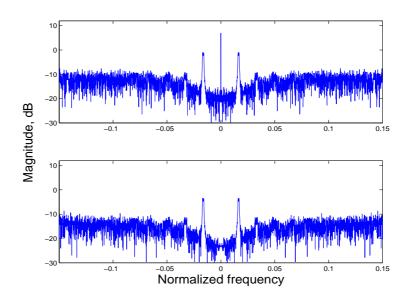

| 5.22 Input and output spectra of the DC blocker for a noisy AM-FM input                                                                        | ut. 91 |

| 5.23 Input and output spectra of the DC blocker for a noisy sawtooth                                                                           | 1      |

| $\operatorname{input}$                                                                                                                         | 91     |

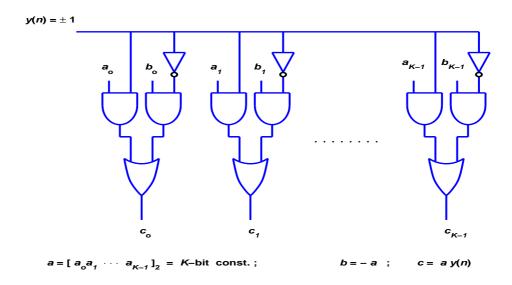

| 5.24 Multiplication of a single-bit signal by a multi-bit constant                                                                             | 92     |

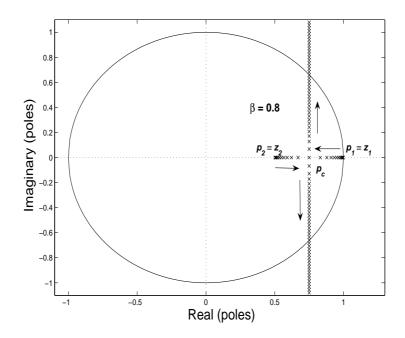

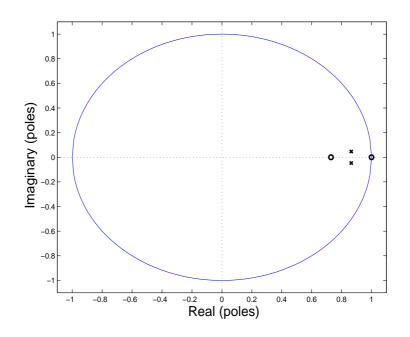

| 5.25 Root-locus of the proposed DC blocker with $\beta$ =0.8                                                                                   | 94     |

| 5.26 Pole-zero plot of the DC-blocker with first-order SDM at $\rho = \rho_n$                                                                  | ı      |

| using $\alpha$ =0.0205 and $\beta$ =0.2705                                                                                                     | 94     |

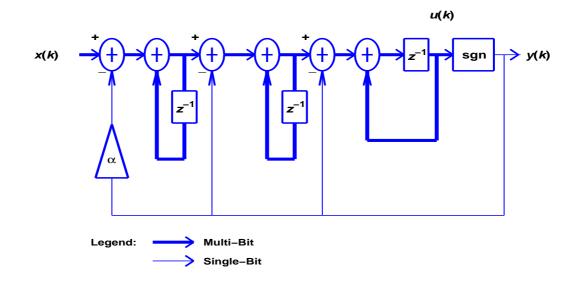

| 6.1 Structure of the third-order $\Sigma\Delta$ modulator under consideration.                                                                 | 98     |

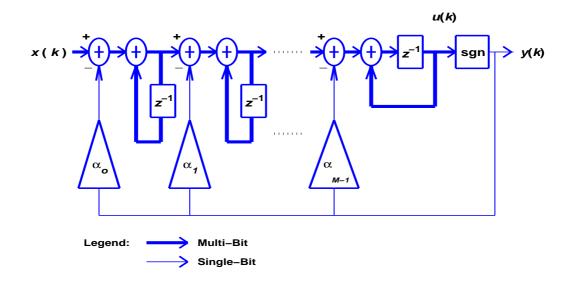

| 6.2 Structure of the $M^{\text{th}}$ -order $\Sigma\Delta$ modulator under investigation.                                                      | 102    |

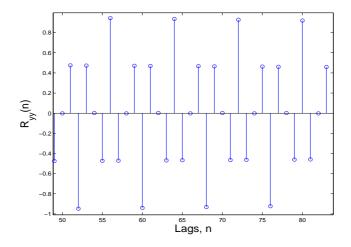

| 6.3 The autocorrelation function $R_{yy}(n)$ of the structure output for zero                                                                  | С      |

| input. The initial conditions are: $u_o = .2$ , $u_1 = .4$ , and $u_2 = 0$ , and                                                               | ł      |

| $\alpha = 0.1. \ldots $ | 103    |

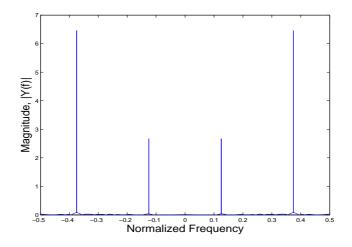

| 6.4 The output frequency spectrum under same parameters                                                                                        | 103    |

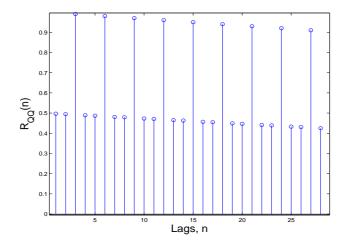

| 6.5 The autocorrelation function $R_{QQ}(n)$ representing the number of                                                                        | f      |

| transitions within the limit cycle period                                                                                                      | 104    |

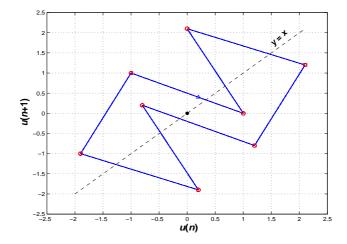

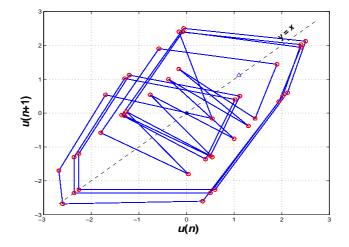

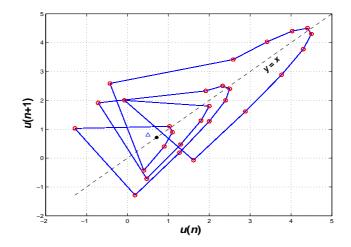

| 6.6                                                                                      | Phase-plane portrait of the third-order structure for $x = 0$ . The                                                        |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|                                                                                          | initial conditions are: $u_o = .2$ , $u_1 = .4$ , and $u_2 = 0$ , and $\alpha = 0.1$ (the                                  |

|                                                                                          | diagonal straight line represents $y = x$ )                                                                                |

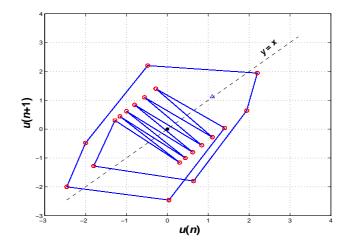

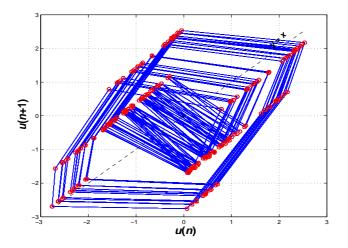

| 6.7                                                                                      | The system phase portrait with $\alpha = 0.1$ and initial conditions: $u_o =$                                              |

|                                                                                          | 1.1, $u_1 = 1.11$ , $u_2 = 1.2$                                                                                            |

| 6.8                                                                                      | The system phase portrait with $\alpha = 0.2$ and initial conditions: $u_o =$                                              |

|                                                                                          | 1.1, $u_1 = 1.11$ , $u_2 = 1.2$                                                                                            |

| 6.9                                                                                      | The phase portrait for $\alpha = 1/6$ and initial conditions of: $u_o = 1.1$ ,                                             |

|                                                                                          | $u_1 = 1.11, u_2 = 1.2.$                                                                                                   |

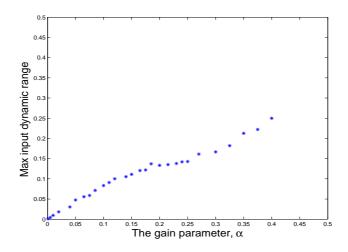

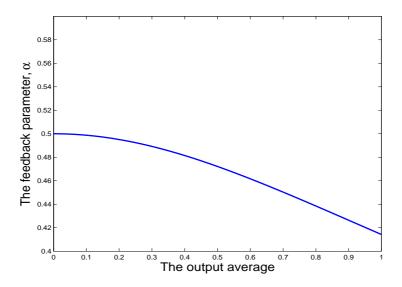

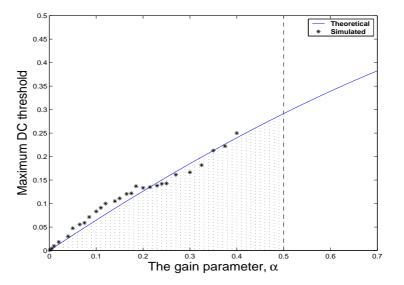

| 6.10                                                                                     | The parameter $\alpha$ versus the maximum threshold dc input beyond                                                        |

|                                                                                          | which no stability is guaranteed                                                                                           |

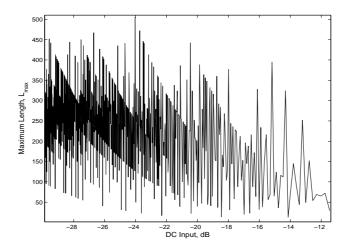

| 6.11                                                                                     | The maximum limit cycle length $L_{\max}$ as a function of the dynamic                                                     |

|                                                                                          | range input under fixed initial conditions and for $\alpha = 0.1.$                                                         |

| 6.12                                                                                     | The phase plane for x=1/14, $\alpha = 0.1$ with initial conditions $u_o = 0.5$ ,                                           |

|                                                                                          | $u_2 = 0.8$ , and $u_3 = 0.8$                                                                                              |

|                                                                                          |                                                                                                                            |

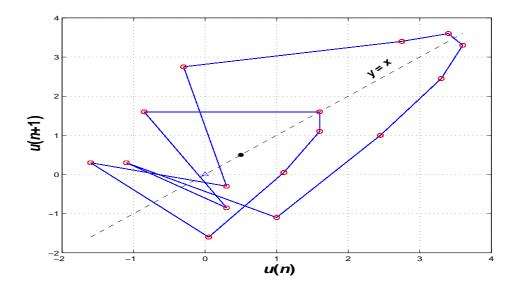

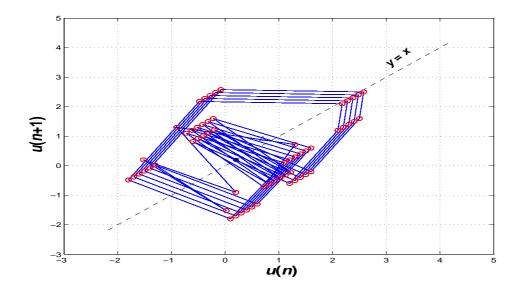

| 7.1                                                                                      | An attractor of third-order $\Sigma\Delta$ system with $x=1/20, \alpha=0.1$ , and                                          |

| 7.1                                                                                      |                                                                                                                            |

| 7.1<br>7.2                                                                               | An attractor of third-order $\Sigma\Delta$ system with $x{=}1/20, \ \alpha{=}0.1$ , and                                    |

|                                                                                          | An attractor of third-order $\Sigma\Delta$ system with $x=1/20$ , $\alpha=0.1$ , and<br>initial condition set $(0,0,-0.3)$ |

|                                                                                          | An attractor of third-order $\Sigma\Delta$ system with $x=1/20$ , $\alpha=0.1$ , and<br>initial condition set $(0,0,-0.3)$ |

| 7.2                                                                                      | An attractor of third-order $\Sigma\Delta$ system with $x=1/20$ , $\alpha=0.1$ , and<br>initial condition set $(0,0,-0.3)$ |

| 7.2<br>7.3                                                                               | An attractor of third-order $\Sigma\Delta$ system with $x=1/20$ , $\alpha=0.1$ , and<br>initial condition set $(0,0,-0.3)$ |

| 7.2<br>7.3                                                                               | An attractor of third-order $\Sigma\Delta$ system with $x=1/20$ , $\alpha=0.1$ , and<br>initial condition set $(0,0,-0.3)$ |

| <ul><li>7.2</li><li>7.3</li><li>7.4</li></ul>                                            | An attractor of third-order $\Sigma\Delta$ system with $x=1/20$ , $\alpha=0.1$ , and<br>initial condition set $(0,0,-0.3)$ |

| <ul><li>7.2</li><li>7.3</li><li>7.4</li><li>7.5</li></ul>                                | An attractor of third-order $\Sigma\Delta$ system with $x=1/20$ , $\alpha=0.1$ , and<br>initial condition set $(0,0,-0.3)$ |

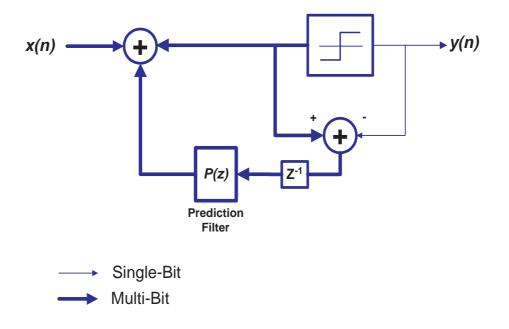

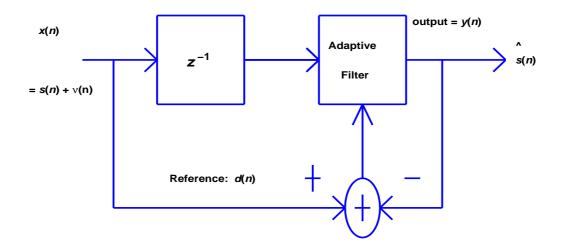

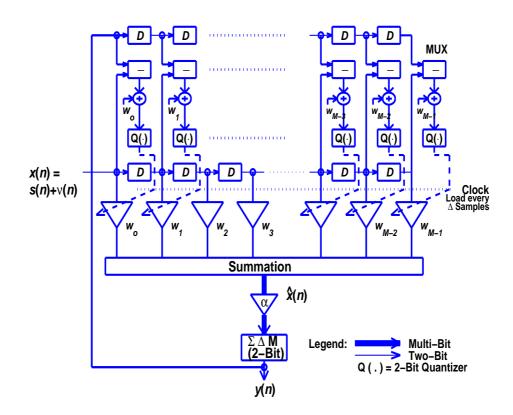

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>8.1</li> </ul>              | An attractor of third-order $\Sigma\Delta$ system with $x=1/20$ , $\alpha=0.1$ , and<br>initial condition set $(0,0,-0.3)$ |

| <ul><li>7.2</li><li>7.3</li><li>7.4</li><li>7.5</li></ul>                                | An attractor of third-order $\Sigma\Delta$ system with $x=1/20$ , $\alpha=0.1$ , and<br>initial condition set $(0,0,-0.3)$ |

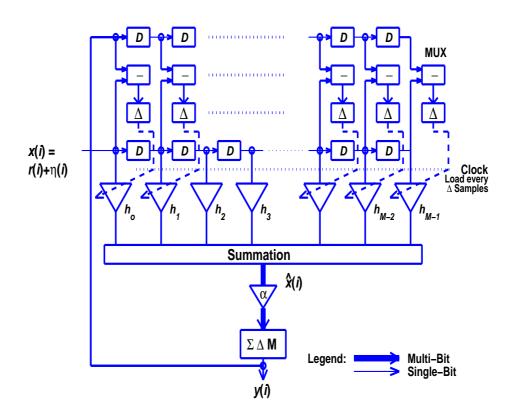

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>8.1</li> <li>8.2</li> </ul> | An attractor of third-order $\Sigma\Delta$ system with $x=1/20$ , $\alpha=0.1$ , and<br>initial condition set $(0,0,-0.3)$ |

| <ul> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>8.1</li> </ul>              | An attractor of third-order $\Sigma\Delta$ system with $x=1/20$ , $\alpha=0.1$ , and<br>initial condition set $(0,0,-0.3)$ |

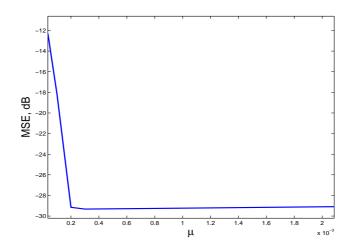

| 8.4  | The step-size $\mu$ versus the mean-square error of the LMS Wiener                                                                                                |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | algorithm                                                                                                                                                         |

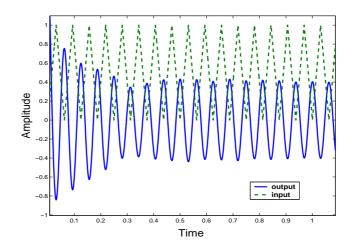

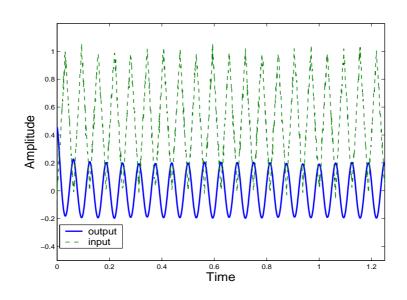

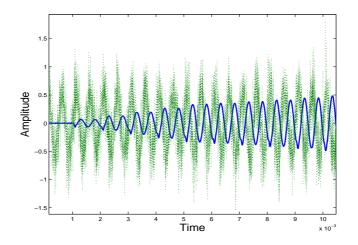

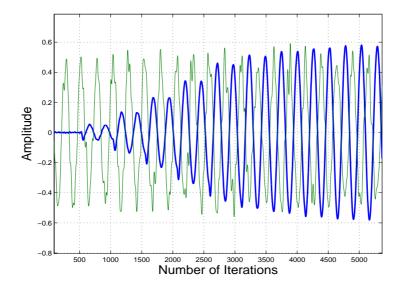

| 8.5  | The tracking response of the adaptive ternary filter. (solid):estimated                                                                                           |

|      | output, (dotted):received input                                                                                                                                   |

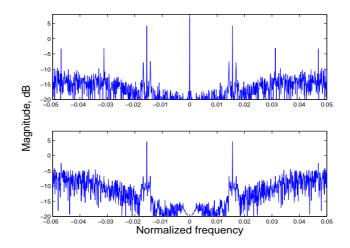

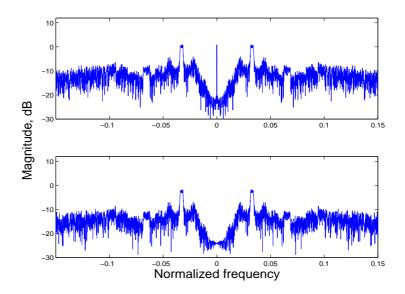

| 8.6  | The frequency spectra of the received signal (upper), and the esti-                                                                                               |

|      | mated signal (lower)                                                                                                                                              |

| 8.7  | Learning curve of the proposed structure for a noisy sinusoid 134                                                                                                 |

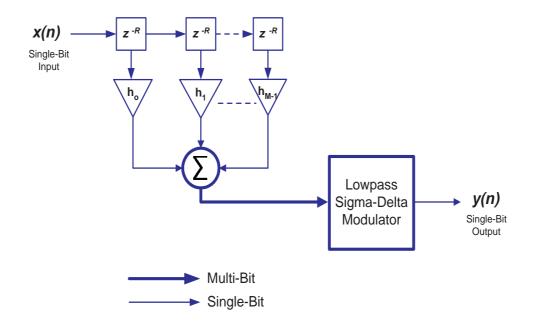

| 8.8  | A proposed block-diagram for single-bit LMS-like adaptive filtering $136$                                                                                         |

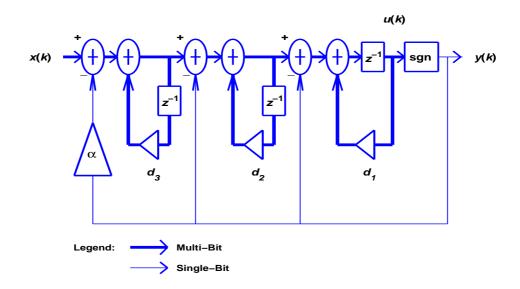

| 8.9  | The proposed single-bit block LMS-like (SBLL) adaptive structure. $\ . \ 143$                                                                                     |

| 8.10 | The second-order SD modulator used in Fig.(8.9)                                                                                                                   |

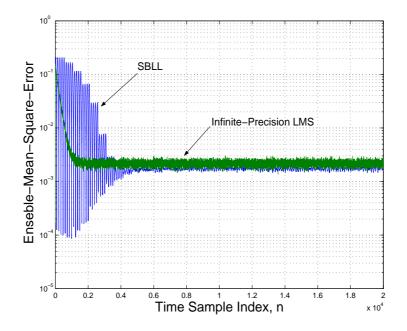

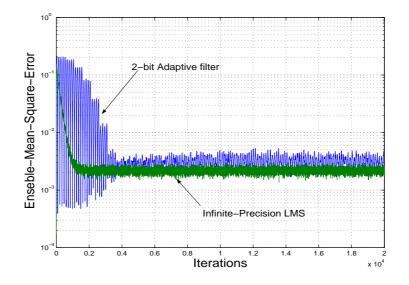

| 8.11 | A comparison between the (undecimated) learning curves of the single-                                                                                             |

|      | bit adaptive filter SBLL and the conventional LMS for a noisy sinu-                                                                                               |

|      | so<br>idal input with $m=20$ , $\mathrm{SNR}_i=24.6~\mathrm{dB},$ and noise power -27.6 dB                                                                        |

|      | for both cases                                                                                                                                                    |

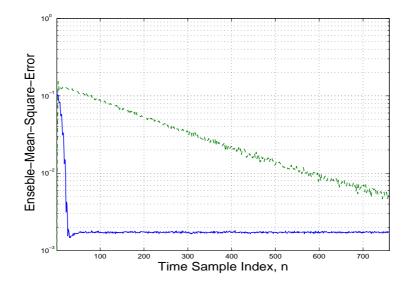

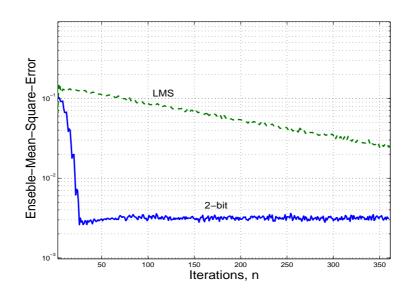

| 8.12 | A comparison between decimated learning curves of the single-bit                                                                                                  |

|      | adaptive filter SBLL (solid) and the conventional LMS (dashed) with                                                                                               |

|      | $m{=}20,{\rm SNR}_i=24.6$ dB, and noise power -27.6 dB for both cases 147                                                                                         |

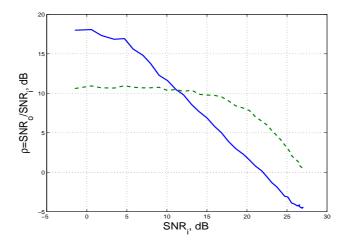

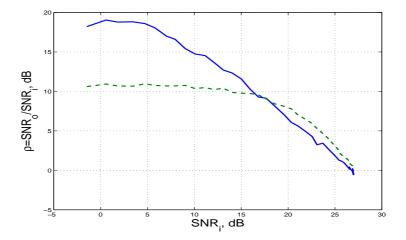

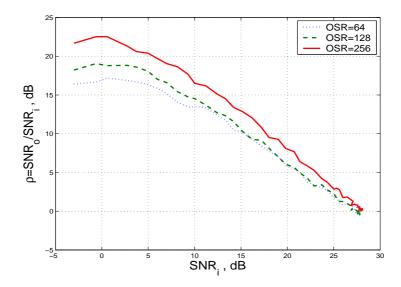

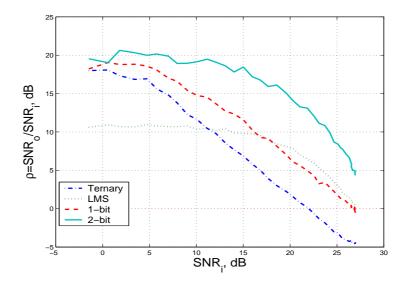

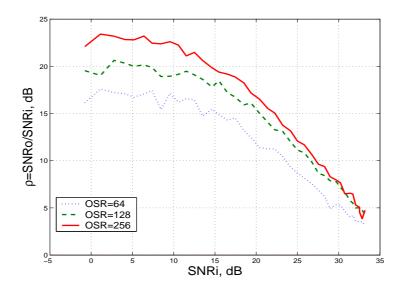

| 8.13 | A comparison in SNR improvement $(\rho)$ between the SBLL (solid)                                                                                                 |

|      | and the corresponding standard infinite-precision LMS algorithm                                                                                                   |

|      | (dashed) ( $m=20$ , OSR = 128)                                                                                                                                    |

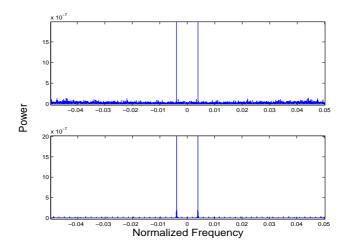

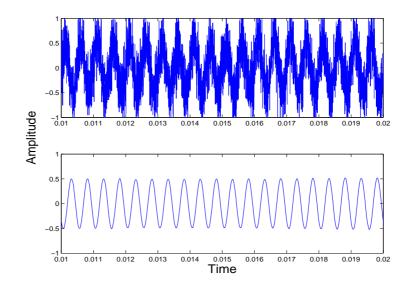

| 8.14 | A comparison between the the original analog noisy sinusoid, i.e.,                                                                                                |

|      | before SD modulation (above) with $SNR = 10 \text{ dB}$ , and the output                                                                                          |

|      | of the SBLL filter (below)                                                                                                                                        |

| 8.16 | Tracking response of the adaptive single-bit filter: (dark) estimated                                                                                             |

|      | output; (light) received AM-FM input; $\text{SNR}_i = 10 \text{ dB.}$                                                                                             |

| 8.15 | ${\rm SNR}$ improvement using the SBLL as a function of OSR: (solid) OSR                                                                                          |

|      | = 256, (dashed) OSR = 128, (dotted) OSR = 64. $\dots \dots \dots$ |

| 8.17 | Power spectra of the AM-FM input (above, with $SNR_i = 10 \text{ dB}$ ) and                                                                                       |

|      | the output (estimation) signal (below)                                                                                                                            |

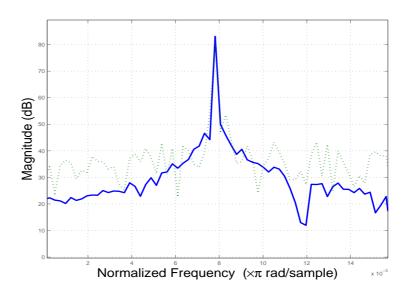

| 8.18 | Spectrum of the estimated signal using single-bit adaptive filter SBLL          |

|------|---------------------------------------------------------------------------------|

|      | (solid) in response to a single-bit AM-FM input (dotted) 151                    |

| 8.19 | The proposed 2-bit block LMS-like (SBLL) adaptive structure 154                 |

| 8.20 | A comparison between the (undecimated) learning curves of the single-           |

|      | bit adaptive filter SBLL and the conventional LMS for a noisy sinu-             |

|      | so<br>idal input with $m=20$ , $\text{SNR}_i = 24$ dB, and noise power -25.2 dB |

|      | for both cases                                                                  |

| 8.21 | A comparison between decimated learning curves of the single-bit                |

|      | adaptive filter SBLL (solid) and the conventional LMS (dashed) with             |

|      | $m{=}20,{\rm SNR}_i=24$ dB, and noise power -25.2 dB for both cases 155         |

| 8.22 | A comparison among the proposed LMS-Like adaptive filters and                   |

|      | the conventional LMS algorithm (in terms of improvement in SNR                  |

|      | represented by $\rho$ )                                                         |

| 8.23 | SNR improvement using the proposed 2-bit adaptive filter as a func-             |

|      | tion of OSR: (solid) $OSR = 256$ , (dashed) $OSR = 128$ , (dotted) $OSR$        |

|      | = 64                                                                            |

| 8.24 | Power spectra of a sinusoid input (above, with $SNR_i = 10.4 \text{ dB}$ ) and  |

|      | the corresponding output (estimation) signal (below)                            |

# List of Tables

| 5.1 | A Comparison between Remez and IFIR techniques (OSR=32). 77 |

|-----|-------------------------------------------------------------|

| 7.1 | Routh-Hurwitz array                                         |

| A.1 | Coefficients of the initial conditions                      |

| A.2 | Coefficients of the signum terms                            |

# List of Acronyms and Principal Symbols

| $\alpha$        | Gain parameter                                                                 |

|-----------------|--------------------------------------------------------------------------------|

| $(.)^T$         | Transposition                                                                  |

| $(.)^{*}$       | Conjugation                                                                    |

| $(.)^H$         | Hermitian transposition                                                        |

| Ω               | Normalized Radian Frequency                                                    |

| $\mu$           | Step-size of algorithm adaptation                                              |

| $\sigma$        | Variance of a signal                                                           |

| $\rho$          | SNR improvement                                                                |

| M               | Length of an oversampled FIR filter                                            |

| m               | Length of Nyquist rate FIR filter                                              |

| $\mathbf{h}(n)$ | Vector of an FIR impulse response Coefficients at sample time $\boldsymbol{n}$ |

| $\mathbf{w}(n)$ | Vector of an adaptive FIR filter coefficients at ample time $n$                |

## List of Acronyms and Principal Symbols

| ADC                         | Analog-to-Digital Converter            |

|-----------------------------|----------------------------------------|

| $\Sigma \Delta M$ , SDM     | Sigma-Delta Modulator                  |

| BLMS                        | Block Least-Mean Square                |

| f                           | Frequency                              |

| $f_s$                       | Sampling Frequency                     |

| FPGA                        | Field Programmable Gate Array          |

| FIR                         | Finite-Impulse Response                |

| FIRb                        | Single-bit FIR filter                  |

| IIR                         | Infinite-Impulse Response              |

| mse                         | Mean-Square Error                      |

| NTF                         | Noise Transfer Function                |

| PCM                         | Pulse Code Modulation                  |

| DSP                         | Digital Signal Processing              |

| PLC                         | Power On-Line Communication            |

| PLL                         | Phase-Locked Loop                      |

| OSR                         | Oversampling ratio                     |

| SBLL                        | Single-Bit LMS                         |

| SNR                         | Signal-to-noise ratio                  |

| SQNR                        | Signal-to-noise and quantization ratio |

| STF                         | Signal-Transfer Function               |

| $\mathrm{SNR}_{\mathrm{i}}$ | Input in-band SNR                      |

| $\mathrm{SNR}_{\mathrm{o}}$ | output in-band SNR                     |

| SNR                         | Signal-to-noise ratio                  |

|                             |                                        |

# Abstract

**R** ecently, short word-length (often single-bit) processing has become a very promising technique as it can implement many important DSP tasks with significant efficiency. The increased effective speed expected for the new short word-length techniques should translate into massive cost savings and increased flexibility for many electronic systems. Short word-length systems have already made a huge impact on industry. The core element in these systems is the single-bit sigma-delta modulator (SDM). Sigma-delta devices are based on oversampling techniques and have the capability of quantization noise shaping.

Despite the large body of work that has been done so far, there are many illunderstood and unresolved issues in sigma-delta modulation, and consequently in single-bit systems. These issues hindered the full adoption of single-bit techniques in industry. Among these problems are the stability of high-order modulators and their limit cycle behaviour. More importantly, there is *no* adaptive LMS structure of any kind for short-word length (ternary or singlebit) systems. The challenge in this problem is the harsh quantization that prevents straightforward LMS application.

In this thesis, the focus has been made upon three axes, namely, designing new single-bit DSP applications, proposing novel approaches for stability analysis, and tackling the unresolved problem of single-bit and short-word length adaptive filtering.

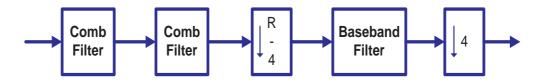

Two structures for single-bit digital comb filtering are proposed. The first

#### Abstract

structure is based on ternary filtering, however, the output of the filter is in single-bit format. The second structure is based on second-order sigma-delta modulation SDM. These filters can be utilized in a wide range of promising applications.

Another design technique for single-bit digital comb filter is presented. The proposed filter response and performance are assessed in terms of signal-toquantization-noise ratio (SQNR) and stability. It is found that the comb filter possesses a distinct frequency response in broadband signal applications. The same technique is utilized to design and simulate a single-bit N-period digital resonator. Feedback loop filters can be used to tune the frequency response of the sigma-delta modulators.

The DC content in single-bit domain is both undesirable and hard to remove. A ternary DC blocker structure is presented. This type of filtering is useful in practice to improve the stability and dynamic range of single-bit systems. The DC blocker is essentially a ternary filtering structure whose input and output are both assumed to have single-bit format. Performance is tested for different kinds of input signals, including sinusoidal, FM, and AM-FM signals.

We also proposed a single-bit multiplierless DC-blocking structure. The input is assumed to be a sigma-delta modulated bitstream. This DC-blocker is designed using a delta modulator topology with sigma-delta modulation embedded in its feedback path. Its performance is investigated in terms of the overall signal-to-noise ratio, the effectiveness of DC removal and the stability.

The above proposed structures would be very efficient to realize (as they contain no multi-bit multiplication) in hardware and can easily be implemented with FPGA.

On the second axis of this thesis, we considered the stability of a singlebit high-order sigma-delta modulator under dc input. A new approach for stability analysis is proposed. A nonlinear circle map is suggested to model the dynamics of the modulator. An analogy between the dynamics of the sigma-

#### Abstract

delta modulator and the sinusoidal digital phase-locked loop (DPLL) is studied and an approximate fixed point solution is presented with stability criteria. Suggestions for designing stabilized high-order systems are also presented.

Despite their major advantage of hardware simplicity, ternary and singlebit systems have limited useability in practice due to their unresolved problem of adaptivity. The conventional LMS family of adaptive algorithms fail to converge if translated to the single-bit domain.

On the third axis of this work we tackled this challenging problem by introducing three short-word length LMS-Like adaptive filtering schemes.

First, an adaptive ternary LMS-like algorithm is proposed. Performance assessment using a sinusoidal input distorted by additive white Gaussian noise showed that the proposed algorithm is comparable to the traditional multi-bit Wiener-Widrow LMS algorithm.

Second, a single-bit-domain LMS adaptive filtering structure for noise cancelling is proposed, where all input, output, and filter coefficients are in singlebit format. The proposed structure is designed and analyzed, and its performance has been evaluated (and compared to the conventional Widrow-Hoff multi-bit LMS algorithm) in terms of convergence properties, signal-to-noise improvement, and computational complexity. Simulation results showed that the proposed adaptive structure exhibits performance that is equivalent to the infinite-precision LMS algorithm.

Finally, a 2-bit LMS-Like structure is introduced and its performance is compared with the ternary and single-bit adaptive algorithms. The reason behind presenting this structure is to find out the optimal word-length in the tradeoff between complexity and performance. As long as noise-cancelling adaptive filtering is concerned, the 2-bit adaptive filter outperforms the other algorithms. We expect that these adaptive algorithms will open the door for short word-length systems to be ready as a practical alternative for multi-bit signal processing systems.

Twelve papers have been published/ submitted during this candidature.

## Introduction

## 1.1 The Conventional Multi-Bit DSP

In traditional PCM technique, the input analog signal is sampled at the Nyquist rate and then represented by a multi-bit word through multi-bit quantization process (8 bit, 16 bit, or more). This technique, however suffers mainly from the complexity of the multipliers and the inefficient chip area utilization in VLSI technology. In the last two decades, sigma-delta modulation ( $\Sigma\Delta$  M) technique has been presented as an alternative approach to conventional PCM techniques. In  $\Sigma\Delta$  approach, the input analog signal is oversampled (many times greater than Nyquist rate) and coarsely quantized to short-length word, often single-bit. The output of the  $\Sigma\Delta$ M is a high-rate bit-stream -1, +1 and can be decimated and filtered to extract a good approximation to the input.

$\Sigma\Delta M$  is an efficient technique to quantize an analog signal and has been used recently in a growing number of DSP applications. However, a comprehensive understanding of  $\Sigma\Delta M$  behavior is not achieved yet due to the presence of a non-linear element within its structure, i.e., the quantizer.

A ternary filter, which is an FIR filter with it's coefficients confined to -1, 0, +1, has been presented, as well, to increase the efficiency of the hardware implementation and power consumption. Single-bit digital systems based on  $\Sigma\Delta$  modulation and ternary filtering have been found to be extremely efficient from the hardware implementation viewpoint. Unfortunately, there are many issues in  $\Sigma\Delta M$  and ternary filters that are considered unresolved till now. These issues will be pointed out in the next Sections.

## 1.2 Thesis Objectives

Despite the revolutionary progress in digital systems in the past two decades, there is currently a limit to the applicability of digital systems. They can only be used where digital processing is able to "keep up with" the required tasks. Processing of very high frequency wideband signals, for example, is typically out of range of the conventional digital processing. To increase the range of applications that can be implemented digitally, it is crucial to increase the effective speed of digital processing. Short word-length (often single-bit) processing is a very promising technique in this regard, firstly because it lends itself well to parallel processing realizations, and secondly because short wordlength operations can implement many important DSP tasks with remarkable efficiency. The increased effective speed expected for the new short word-length techniques should translate into massive cost savings and increased flexibility for many electronic systems. Short word-length system implementations have already made a huge impact on industry. For instance, short word-length A/D and D/A converters, and increasingly, digital audio systems using short wordlength amplifiers, are common. Very promising applications based on singlebit  $\Sigma\Delta M$  systems have already been presented. Examples of such applications are video A/D conversion [1], wideband applications [2, 97], and ultrasonic beamforming [46]. Research on these systems is therefore critically important. Outcomes in this area will result in reduced costs for electronics consumers and increase the quality of life. It is the aim of this thesis to contribute to the body of knowledge in this direction.

#### 1.2.1 Research Questions

The proposed PhD program attempts to answer the following questions:

- Can single-bit systems be designed to perform or approximate the functions of existing multi-bit systems?

Initial attempts are successful but an extensive research is required.

- 2. Does a ternary filter possess limit cycles similar to the case of  $\Sigma \Delta M$ ? If yes, what laws would the limit cycles follow?

- Is it possible to utilize LMS adaptive techniques (e.g., for communication channel noise canceling) in ternary filtering?

Adaptivity in ternary and single-bit systems is an unresolved problem and represents the major practical obstacle towards their wide spread usage in communications.

- 4. Can ternary filtering be utilized efficiently in broadband and other communication applications?

- 5. What is the optimal word-length that makes these systems capable of replacing existing multi-bit systems?

### 1.2.2 Research Aims

The specific objectives arising from these questions have been addressed. These can be summarized as follows:

- 1. Designing new single-bit (or short word-length) systems using both ternary filtering and  $\Sigma\Delta$  modulation.

- 2. Investigating the occurrence of limit cycles in ternary filters.

- 3. Investigating the LMS adaptation of ternary and single-bit filtering.

- 4. Investigating the optimal (shortest) word-length that suits various DSP applications.

- Investigating the stability issues of the designed short word-length systems.

## **1.3** Original Contributions

This thesis makes many original contributions to the body of signal processing knowledge both in theory and in implementation. A number of novel algorithms and techniques to model and design new short word-length systems have been presented.

The main contributions of this dissertation are summarized below:

- Designing new single-bit and ternary DSP applications. A single-bit ternary and ΣΔM-based comb filtering and DC-Blockers are proposed. The work led to publications in Eurasip Journal on Applied Signal Processing, as well as in APCC 2005 and TENCON 2005 Conferences.

- 2. The limit cycle behavior in ternary structures has been explored and shown to exist. This led to a publication in TENCON 2006.

- 3. A novel approach in the stability analysis of the ternary structure is proposed, which invokes the analogy between the operation of the  $\Sigma\Delta$ and the digital phase-Locked Loop (DPLL) systems. This approach can be expanded to include higher (>3)  $\Sigma\Delta$  modulators. This led to publication in Digital Signal Processing Journal.

- 4. The unresolved issue of LMS adaptivity in short-word length digital filtering has been addressed. Impressive results are obtained and adaptive structures (ternary and single-bit) are designed, analyzed and simulated. It is expected that this achievement would open the door for the short-word length techniques to replace the traditional multi-bit PCM counterparts in the near future. This led to a publication in IEE Electronics Letters.

## 1.4 Thesis Organization

This thesis is comprised of nine chapters, which can be divided in three parts. The first part includes development of new single-bit DSP applications as in Chapters 4 and 5. The second part contains the study of limit cycle behavior and stability analysis of ternary topology and higher-order  $\Sigma\Delta$  systems in Chapters 6 and 7. The third part consists of a proposed short-word length adaptive filtering approach as explained in chapter 8.

The dissertation is organized as follows:

#### **Chapter 2: Literature Review**

Literature survey on single-bit processing techniques is made in this chapter. As the single-bit processing techniques almost entirely involve the utilization of sigma-delta modulation at some stage, the single-bit format is inherently related to sigma-delta modulators ( $\Sigma\Delta M$ ). The main obstacles that hindered the full adoption of these techniques in industry and life are addressed as well. Emphasis has been put on the inherent problems regarding  $\Sigma\Delta Ms$  behavior. Issues such as limit cycle behavior and stability of high-order  $\Sigma\Delta$  systems are considered as not fully understandable. The topic of single-bit adaptivity is quite a challenging task, both in theory and implementation, and is regarded as an unresolved problem.

## Chapter 3:Single-Bit Ternary Filtering Using Sigma-Delta Modulation

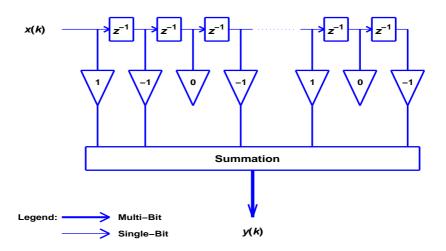

In this chapter a bit-stream filtering structure is introduced. It consists of a ternary FIR filter cascaded with an IIR  $\Sigma\Delta M$  structure. This structure is being the basis of many single-bit DSP applications. Since many of the ternary filter tap values are zero and each non-zero tap requires only very simple multiplication hardware, the system is very resource efficient and fast, as no complex mathematical operations are required. Performance enhancement is possible through increasing the oversampling ratio, however, this requires increasing the number of taps and the sampling rate of the system, hence, there is an inherent trade-off between hardware efficiency and performance.

## Chapter 4: DSP Applications Using Single-Bit Filtering: Comb Filtering

In this chapter, two structures for single-bit output comb filtering are pro-

posed and simulated. The first structure is a combination of a ternary filtering stage and a  $\Sigma\Delta M$ . The second structure which is based on a secondorder  $\Sigma\Delta M$ , is designed and its performance is evaluated in terms of signalto-quantization noise ratio (SQNR), the dynamic range (input signal level), and stability. Moreover, it is shown that the same design technique can be used for other single-bit systems, where we used it to design a multi-period resonator. It was shown that the proposed filters lend themselves very well to broadband input signals and can be utilized in emerging technologies such as the Broad-Band Power-line Communication (BPL).

## Chapter 5: DSP Applications Using single-Bit Filtering: DC Blocking

In this Chapter, two efficient multiplierless structures for DC-canceling in the single-bit domain has been proposed. The first consists of a ternary filtering stage followed by a sigma-delta modulator stage. Two design techniques were utilized to generate the ternary taps. For each technique, the associated ternary filer stage was assessed in terms of DC attenuation and hardware efficiency. The simulated system response has been studied through the application of various DC-biased, noisy signals. The DC content was removed completely from all kinds of input signals.

The second is a novel single-bit domain DC canceling structure. It is evaluated in terms of the overall SNR and the magnitude of DC attenuation. The role of the gain parameters is investigated and optimal performance has been reached. The system is examined using different types of signals.

#### Chapter 6: Limit Cycle Behavior in Ternary Structures

The difference equation and the iterative solution that describe its operation are developed in this chapter. It is shown that the system exhibits limit cycle behavior under certain conditions of the system parameters. The  $M^{\text{th}}$ -order difference equation of similar  $\Sigma\Delta$  topologies are also developed. Moreover, a general formula for obtaining the average output of these systems is derived. The system was then simulated extensively and a random search method is utilized to discover and extract the limit cycles and identify their features. It seemed that this topology, which is a third-order  $\Sigma\Delta$  modulator, possesses a highly non-linear behavior.

## Chapter 7: A Stability Analysis Approach for Sigma-Delta Modulators in Ternary Structures

In this chapter, we attempt to set out a comprehensive analysis to the third-order  $\Sigma\Delta$  topology utilized in ternary filters, both mathematically and by simulation. This is done by utilizing the circle map dynamics to accurately model the operation of the  $\Sigma\Delta$  structure, which is treated as a third-order sinusoidal digital phase-locked loop system. Accordingly, the stability topic is addressed using the fixed point techniques. This analysis would be of remarkable importance to other higher-order  $\Sigma\Delta$  structures after some appropriate modifications.

#### Chapter 8: Short-Word Length LMS Adaptive Filtering

In this chapter we tackle the unresolved problem of ternary and single-bit LMS adaptive filtering. We propose an approach for LMS adaptive ternary filtering. Despite the simple structure, simulation results showed that the proposed algorithm is parallel in performance to the standard multi-bit LMS algorithm. We expect that this approach will open the door for a wide range of applications for ternary systems.

In addition, a single-bit-domain LMS adaptive filtering structure for noise canceling is presented, where all input, output, and filter coefficients are in single-bit format. The proposed structure is analyzed and its performance is evaluated (in comparison to the conventional Widrow-Hoff multi-bit LMS algorithm) in terms of convergence properties, signal-to-noise ratio improvement, and computational complexity. Simulation results showed that the proposed adaptive structure exhibits performance that is equivalent to the infiniteprecision LMS algorithm.

#### Chapter 9: Conclusions and Future Work

This chapter summarizes the main conclusions of this dissertation and presents possible future directions.

# Chapter 2

## Literature Review

## 2.1 Introduction

The short word-length (often single-bit) format generated by sigma-delta modulator ( $\Sigma\Delta M$ ) makes for greatly simplified arithmetic processing. For hardware implementation, this simplified processing implies reduced silicon space and reduced power consumption [4].

Processing tasks which are rich in multiplications are particularly strong beneficiaries of the use of single-bit signal representation. This is so because multi-bit multiplications require complex hardware implementation, whereas in the single-bit domain, multiplications can simply be implemented using a couple of gates or a very simple look-up table [5]. An efficient hardware implementation of  $\Sigma\Delta$  systems can be attained if both the input signal and the transverse FIR filter impulse response representations are in binary or ternary format [6]. Both  $\Sigma\Delta$ M and ternary filters use coarse quantization to enable simple hardware implementation. Ternary filters have an architecture similar to FIR transversal filters, however, the tap values are limited to {-1, 0, +1}.

Although there are several algorithms presented to design ternary filters [7, 8, 9, 10, 11], the design techniques are particularly difficult to implement. Moreover, techniques to predict the performance of a ternary filter are not often presented. Developing an easily implemented, optimal ternary filter de-

sign algorithm will allow signal processing designers to get the best possible performance from ternary filters, causing them to become more widely used and offering more possibilities for increased hardware efficiency [12].

Unlike ternary filters,  $\Sigma\Delta Ms$  have been extensively analyzed using different techniques. Yet,  $\Sigma \Delta M$  system understanding is far from complete [13]. Issues related to  $\Sigma\Delta M$  such as noise performance, instability, integrator spans, idle tones, limit cycle behavior, chaos, and adaptation have been often addressed. Ternary filters, on the other hand, have undergone very limited analysis and there are many unresolved issues that should be addressed. Some of these issues, which are to be investigated in this research, are listed below. First of all, it is unknown whether ternary systems have limit cycles similar to those in  $\Sigma \Delta M$ , and if they have, what is the law that these limit cycles may follow? Second, adaptive ternary filtering is an unresolved issue. Adaptive filtering is a vital topic in modern signal processing and digital systems. However, due to the short word length nature of single-bit systems, this issue is quite a challenging task, both in theory and implementation. Third, there is a need to investigate the possibilities of designing new single-bit  $\Sigma\Delta M$  ternary systems suitable for broadband applications such as RF and the promising technology of Broadband Power-Line Communication (BPLC). This is a promising avenue because ternary filters lend themselves well to low frequency applications.

In this chapter, we attempt to conduct a comprehensive literature survey on the single-bit processing techniques and, as the single-bit processing techniques almost entirely involve the utilization of sigma-delta modulation at some stage, the single-bit format inherently related to sigma-delta modulators ( $\Sigma\Delta M$ ). The main obstacles that hindered the full adoption of these techniques in industry and theory are addressed as well.

## 2.2 Sigma-Delta Modulation

Oversampled  $\Sigma\Delta$  modulators are becoming a standard high-resolution data conversion element [14]. These oversampled data convertors have several advantages over conventional Nyquist-rate convertors, including insensitivity to analog component imperfections [15], their high linearity, reduced complexity of the anti-aliasing filter, and lower cost of implementation.  $\Sigma\Delta$ Ms have fast become one of the dominant data conversion elements in the low frequency range of the market. They come in one of two varieties: digital to analog (DAC) and analog to digital (DAC) conversion elements. A typical trademark that provides evidence of a  $\Sigma\Delta$  data converter in consumer audio equipment is the "1-bit" advertisement.

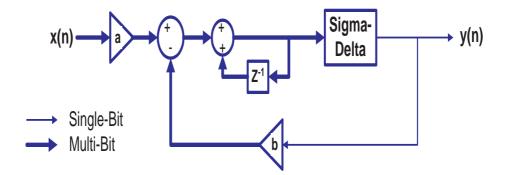

Typically,  $\Sigma\Delta M$ 's are used to convert a signal from multi-bit resolution to a single-bit resolution with little or no loss of dynamic range. This conversion, or modulation, is achieved through oversampling and noise shaping techniques [16]. The  $\Sigma\Delta M$  trades resolution in time for resolution in amplitude. Since these modulators can convert multi-bit signals to single-bit signals, they are at the cornerstone of single-bit digital signal processing [17, 18]. The general structure of a basic  $\Sigma\Delta M$  is shown in Fig.(2.1).

Figure 2.1: Block diagram of the basic  $\Sigma \Delta M$ .

This structure must be operated at an oversampled rate. The oversampling

ratio R is defined as  $R = \frac{f_s}{2f_B}$ , where  $f_s$  is the sampling frequency and  $f_B$  represents the input signal bandwidth. Oversampling decreases the non-shaped in-band noise by 3 dB for every doubling of the sampling frequency  $(f_s)$  [19]. By increasing the sampling rate from  $f_s$  to  $f_{s1} = 2f_s$ , the in-band quantization noise, previously spread over  $[-\frac{f_s}{2}, \frac{f_s}{2}]$ , is now spread over a larger frequency range  $[-\frac{f_{s1}}{2}, \frac{f_{s1}}{2}]$ , reducing the noise power spectral density to half the previous value. In addition to this reduction, there is a more significant attenuation in the in-band quantization noise power due to the inherent noise-shaping filtering action in  $\Sigma\Delta M$ . This is obvious from the in-band noise approximation which results from the white-noise assumption [20], that is

$$S_B \approx \left(\frac{\pi^{2M}}{2M+1}\right) \left(\frac{1}{R^{2M+1}}\right) \frac{\Delta^2}{12}$$

(2.1)

where  $S_B$  is the power of the in-band noise, M is the order of modulator, R is the oversampling ratio, and  $\Delta$  is the quantization step. Equation (2.1) reveals that the attenuation of the in-band quantization noise due to increasing he oversampling ratio is exponentially improved as the modulator order increases. It is noteworthy that the above approximation has a practical limitation as it suggests that the precision can be improved indefinitely by increasing the order of noise shaping [20].

Given that  $\Sigma\Delta$ Ms can only provide a relatively small bandwidth in comparison to the sampling frequency, noise shaping can result in significant reductions in quantization noise over the bandwidth of the interest. This is evident as  $\Sigma\Delta$ Ms are typically operated with oversampling ratios ranging from 32 to 256. However, high oversampling ratios are a major obstacle towards the utilization of  $\Sigma\Delta$  systems in broadband applications. Three different approaches have been proposed for obtaining good noise attenuation with low oversampling ratios [20]. The first approach is based on adopting higher-order transfer functions to increase the order of noise shaping (see equation 2.1). Utilizing a multibit quantizer is the second approach, while the third approach is the cascading of multiple stages.

There are many  $\Sigma\Delta Ms$  architectures for different orders; a good summary of these architectures can be found in [16] and [21].

In general, the quantizer utilized within  $\Sigma\Delta Ms$  is a single-bit quantizer. Hence, the only possible outputs of such a quantizer are  $\{1,-1\}$ . This single-bit quantizer has superior linearity qualities as compared to multi-bit quantizers, making it an extremely desirable quantization element in  $\Sigma\Delta M$ 's [16]. This highly linear quantizer does not come without limitations. As only two output levels are possible, the quantization noise introduced is usually large.

The use of negative feedback in  $\Sigma\Delta M$ 's is central to their operation.  $\Sigma\Delta M$ 's typically operate by using negative feedback to suppress the quantization errors in the region of the loop filters passband. This negative feedback has also been found to provide some insensitivity to manufacturing imperfections within ADC's, unlike traditional multi-bit ADC's [16, 22].

The loop filter for low frequency applications such as audio have lowpass functions. Bandpass modulators can be created also through manipulation of the loop filter [22, 23]. Increasing the loop filter order in  $\Sigma\Delta M$ 's can significantly improve the noise shaping capabilities. Such increases can lead to higher dynamic ranges at lower oversampling ratios and wider passband widths [16, 21].

Since the single-bit quantizer is a non-linear element within a negative feedback loop, the design and subsequent stability analysis of  $\Sigma\Delta$ M's is inherently complicated. Analysis and design of these structures is further complicated by increasing the order of the loop filter. This is evidenced by the large body of literature concerning design rules of thumb and stability issues (e.g. [24]). Systems with high-order loop filters and non-linear elements (such as the single-bit quantizer) in the feedback loop can be unstable.

$\Sigma\Delta M$  design and analysis can be significantly simplified by linearizing the quantizer. While this linearization does not properly model the signaldependent quantization noise, it has been found insightful [16, 22]. The 1bit quantizer is modelled by an additive white noise source with variance  $\sigma_q = \Delta^2/12$ , where  $\Delta$  represents the quantization interval. This white noise model introduces the quantization error signal q(n) and adds this to the quantizer input as shown in Fig.(2.2). Assuming a uniform distribution between -1 and +1 for quantization noise, the traditional linear model for  $M^{\text{th}}$ -order modulator relates the output spectrum  $S_y(e^{j\Omega})$  to the input spectrum  $S_x(e^{j\Omega})$  according to [25]

$$S_y(e^{j\Omega}) = S_x(e^{j\Omega}) + \frac{1}{3} [2\sin(\frac{\Omega}{2})]^{2M}$$

(2.2)

Assuming that the quantization noise is highly uncorrelated from one sample to the other and statistically independent of the signal, the ideal in-band SNR, SNR<sub>in</sub>, achieved by an  $M^{\text{th}}$ -order  $\Sigma\Delta M$ , can be calculated as [21]

$$SNR_{in} = 10 \log_{10}(\sigma_{xy}^2) - 10 \log_{10}(\sigma_{qy}^2) - 10 \log_{10}(\frac{\pi^{2M}}{2M+1}) + (20M+10) \log_{10}(\frac{f_s}{2f_B}) (dB)$$

(2.3)

where  $\sigma_{xy}^2$  is the signal power (variance) at the output and  $\sigma_{qy}^2$  is the in-band noise power at the output assuming zero mean. As the signal power is assumed to occur over the signal band only, it will not be subjected to any modification, and the signal power at the output  $\sigma_{xy}^2$  is the same as the input signal power  $\sigma_x^2$ . The achieved SNR<sub>in</sub> depends on the noise-shaping function of the modulator, which can be described in terms of z-domain poles  $p_i$  and zeros  $z_i$ . For an  $M^{\text{th}}$ -order modulator, the noise-transfer function NTF can be expressed as

$$NTF(z) = \frac{\prod_{i=1}^{M} (z - z_i)}{\prod_{i=1}^{M} (z - p_i)} = \frac{1}{1 + H(z)}.$$

(2.4)

A well-known choice for the noise-shaping pole locations is to arrange them in Butterworth configuration, whereas improved SNRs are achieved if noise shaping zeros are distributed across the baseband in conjugation pairs [26]. A  $\Sigma\Delta$  structure with controllable SNR has been reported in [27, 28].

If we now return to Fig.(2.1) to mathematically describe the general  $\Sigma \Delta M$

Figure 2.2: Linear model of a quantizer.

output using the linear model in the z-domain, the system can be described by:

$$Y(z) = \frac{H(z)}{1 + H(z)}X(z) + \frac{1}{1 + H(z)}Q(z)$$

(2.5)

where X(z), Y(z), H(z) and Q(z) represent input, output, loop filter and quantization signals and functions in the z-domain, respectively.

From equation 2.5, we can obtain signal and noise transfer functions (abbreviated as STF and NTF) as shown below.

$$STF(z) = \frac{H(z)}{1 + H(z)}$$

(2.6)

$$NTF(z) = \frac{1}{1 + H(z)}$$

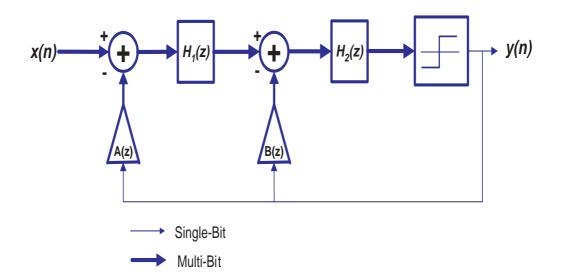

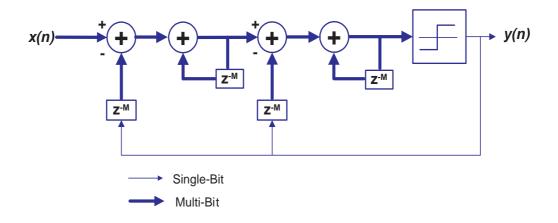

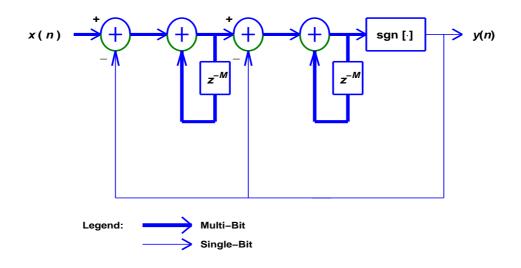

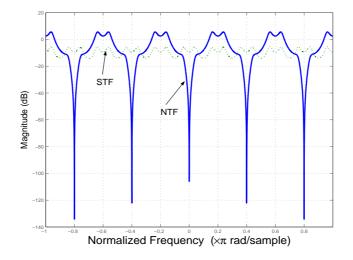

(2.7)