# **Simplifying ARM Concurrency:**

# Multicopy-Atomic Axiomatic and Operational Models for ARMv8

CHRISTOPHER PULTE, University of Cambridge, UK SHAKED FLUR, University of Cambridge, UK WILL DEACON, ARM Ltd., UK JON FRENCH, University of Cambridge, UK SUSMIT SARKAR, University of St. Andrews, UK PETER SEWELL, University of Cambridge, UK

ARM has a relaxed memory model, previously specified in informal prose for ARMv7 and ARMv8. Over time, and partly due to work building formal semantics for ARM concurrency, it has become clear that some of the complexity of the model is not justified by the potential benefits. In particular, the model was originally non*multicopy-atomic*: writes could become visible to some other threads before becoming visible to all — but this has not been exploited in production implementations, the corresponding potential hardware optimisations are thought to have insufficient benefits in the ARM context, and it gives rise to subtle complications when combined with other ARMv8 features. The ARMv8 architecture has therefore been revised: it now has a multicopy-atomic model. It has also been simplified in other respects, including more straightforward notions of dependency, and the architecture now includes a formal concurrency model.

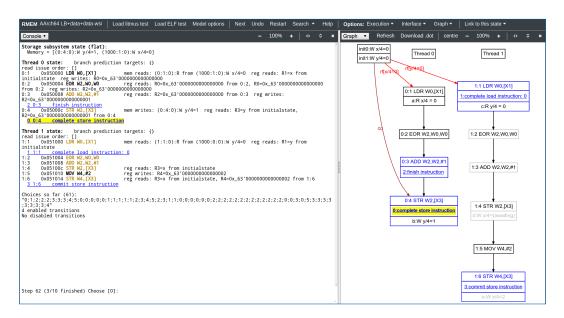

In this paper we detail these changes and discuss their motivation. We define two formal concurrency models: an operational one, simplifying the Flowing model of Flur et al., and the axiomatic model of the revised ARMv8 specification. The models were developed by an academic group and by ARM staff, respectively, and this extended collaboration partly motivated the above changes. We prove the equivalence of the two models. The operational model is integrated into an executable exploration tool with new web interface, demonstrated by exhaustively checking the possible behaviours of a loop-unrolled version of a Linux kernel lock implementation, a previously known bug due to unprevented speculation, and a fixed version.

CCS Concepts: • Computer systems organization → Architectures; • Theory of computation → Concurrency; Semantics and reasoning; • Software and its engineering → Concurrent programming languages; Assembly languages;

Additional Key Words and Phrases: Relaxed Memory Models, Semantics, Operational, Axiomatic

#### 1 INTRODUCTION

What is the semantics of concurrent ARM machine-code programs? The vendor architecture manuals for ARMv7 and early ARMv8 described a relaxed memory model, with programmer-visible out-of-order and speculative execution, that was *non-multicopy-atomic*: a write could become visible to some other threads before becoming visible to all threads. In this it was broadly similar to the IBM POWER architecture. The two were unfortunately also alike in another way: their memory models were expressed as prose definitions that were hard to interpret precisely. (x86 and MIPS are similarly imprecise, while SPARC and Itanium have precise vendor-defined models.) This prompted extensive work to establish mathematically precise models for ARM and for IBM POWER, initially based on the vendor texts, but later, as the deficiencies of those became apparent, relying more heavily on experimental investigation of the behaviour of processor implementations, and on discussion with ARM and IBM architects of their architectural intent: Flur et al. [2017, 2016b]; Gray et al. [2015]; Alglave et al. [2014]; Maranget et al. [2012]; Sarkar et al. [2012]; Alglave et al. [2011]; Sarkar et al. [2011]; Alglave et al. [2010, 2009]; Sarkar et al. [2009]; Chong and Ishtiaq [2008]; Adir et al. [2003]; Corella et al. [1993].

Broadly speaking, over time these models have become more complete, covering more relaxed-memory phenomena and larger fragments of the architectures, and more accurate, with respect both to experimental results and to the architects' intentions. They have also become more complex — partly due to the increased coverage, but also as they have exposed more of the complexity implicit in those intentions.

This complexity has a cost, especially for architectures implemented by multiple vendors, and ARM has recently made a significant shift to a simpler model. In particular, while non-multicopyatomic (non-MCA) behaviour is observable on IBM POWER implementations, the hardware implementation freedom it permits has not been exploited on production ARMv8 implementations, by any of the several vendors thereof. This was previously suggested by experimental data for some implementations [Maranget et al. 2012; Alglave et al. 2014; Flur et al. 2016b, 2017], and has been confirmed by discussion with ARM Architecture Partners; it is thought that in the ARM context the potential hardware performance benefits of non-MCA do not justify the ensuing complexity of implementation, validation and reasoning. Allowing non-MCA behaviour gives rise to substantial complexity in the model, especially when combined with the previous architectural desire for a model that provided as much implementation freedom as possible, and with the store-release/load-acquire instructions added in ARMv8. Accordingly, ARM have now revised their ARMv8 specification to prohibit non-MCA behaviour: when a write is visible to some other thread, it is now guaranteed to be visible to all [ARM Ltd. 2017, BS-84,90]. Further, the revised ARMv8 specification document now includes, for the first time, a formal memory model to specify (for a fragment of the architecture) exactly what behaviour is and is not allowed; the architecture contains a prose version of the formal model by Deacon [2016]. The specification is also being clarified in various other respects, including the definition of inter-instruction dependencies.

In this paper we detail these changes to the ARMv8 concurrency architecture and discuss the motivation for them. We define two formal concurrency models: an operational model that simplifies the Flowing model of Flur et al. [2016b, 2017], and the axiomatic model of the revised ARMv8 specification. The two models were developed by an academic group and by ARM staff, respectively, with an extended collaboration and discussion of examples that started for non-MCA ARMv8 and partly motivated the shift to MCA ARMv8. We then prove the two models equivalent, establishing the correspondence between particular operational model transitions and axiomatic model events. This increases confidence in both formal models and in the architecture itself, providing a clear operational intuition for the axiomatic model. The operational model is integrated into an executable

rmem tool, with a new web interface for interactive, pseudo-random, and exhaustive exploration of litmus tests and small ELF binaries. The tool can be used for testing and understanding the concurrency model, and for exploring the behaviour of concurrent software, at least in small instances. We demonstrate the latter for a Linux kernel lock implementation, by exhaustively checking the reachable states of a loop-unrolled version. In short, this paper contributes:

- discussion of the motivation for the new MCA ARMv8 concurrency architecture, including complexities that arose in the non-MCA case (§3);

- an informal description of the new architecture (§4);

- a formal semantics for MCA ARMv8 expressed as an operational model, with an abstract microarchitectural flavour (§5,6);

- a formal semantics for MCA ARMv8 expressed as an axiomatic model, as presented in the new architecture document and by Deacon [2016] (§5,7);

- proof of equivalence of the two models (§8);

- experimental validation of that equivalence and of the model soundness with respect to hardware (§9);

- a verification, simulation, and debugging tool, rmem, based on the operational model (§10);

- a demonstration of rmem in use, for verifying a lock implementation from the Linux kernel with respect to the MCA ARMv8 architecture semantics (§11).

The supplementary material includes details of the operational model, proof, and tests, at http://www.cl.cam.ac.uk/~pes20/armv8-mca/. The rmem tool is available at http://www.cl.cam.ac.uk/~pes20/rmem/, including the tests mentioned in the paper (best viewed in chrome/chromium). The new models should aid future work on reasoning about and verification of concurrent ARM code, as these become considerably simpler in the MCA case.

Caveats. The two formal semantics do not have identical coverage, and so our proof addresses the intersection of the two. The operational model is integrated with semantics for a substantial fragment of the instruction set, and supports mixed-size accesses. The axiomatic model does not include that ISA integration or support mixed-size, but it does cover the more relaxed form of load-acquire (LDAPR) introduced in ARMv8.3 and the atomic read-modify-write instructions introduced in ARMv8.1, which are not in the operational model. We believe that the operational model and proof could be straightforwardly extended to cover the LDAPR and read-modify-write instructions. Integrating the axiomatic model with the full ISA model requires work on the axiomatic model and tooling to support mixed-size (to the best of our knowledge no existing axiomatic model or tool does), including some open questions concerning the allowed behaviour, and work to handle the full ISA intra-instruction semantics.

The operational model can deadlock in cases where there are memory accesses or barriers between load/store-exclusive pairs, or when the store-exclusive has extra dependencies (these two are cases that are not really intended to be supported by the architecture), and when a load and a store-exclusive are paired successfully but have different addresses, which is still being clarified.

Neither model addresses systems aspects of the architecture, e.g. virtual memory. Finally, our proof is a hand proof, not mechanised, and currently is limited to finite executions.

# 2 BACKGROUND: THE NON-MCA FLOWING MODEL

We briefly recall how the Flowing model exhibits non-MCA, as it was the model most often referred to in discussions with architects, matching their intuitions, and is simple to understand. We refer to Flur et al. [2016b] for a more complete description of this and the associated POP model. Flowing comprises an operational semantics for each hardware thread, with explicit out-of-order and speculative execution for each, connected via a storage subsystem comprising an arbitrary

tree-structured hierarchy of queues, of writes, read requests, and barriers, above a simple memory. When the storage subsystem receives a memory access or barrier, it is placed at the top of the queue that is associated with the submitting thread. The bottom-most event in a queue can "flow" to the top of the next queue in the topology. The memory is a map from byte locations to the most recent write events to those locations. The bottom-most event in the bottom-most queue can "flow" to memory: for a write event, updating the memory mapping; for a read event, sending a read-response to its thread with the appropriate value from the memory map; and, for a barrier event, removing the barrier. A read event may also be satisfied from within a queue if the event immediately below it is a write event to the same location. Finally, adjacent events in a queue (even if from different threads) may switch places with each other (reorder), subject to some constraints.

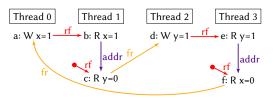

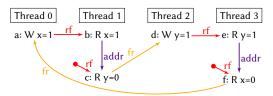

To demonstrate how Flowing exhibits non-MCA, consider the classic non-MCA IRIW+addrs<sup>1</sup> litmus test (WRC+addrs is similar but with (d) merged into (c)). Here Threads 0 and 2 write to the memory locations x and y, respectively, which are then read by Threads 1 and 3, in opposite orders; the intra-

thread order of each pair of reads is preserved by address dependencies. In the execution shown, each thread observes the new value in its first read and the initial-state value in its second read. The vertical arrows are program-order (po) edges, describing the particular control-

flow unfolding of the execution, including address (addr), data (data), and control (ctrl) dependencies; the reads-from (rf) edges indicate the source write (or initial state) for each memory read; and coherence order (co) indicates the order in which writes to the same location are sequentialised. The derived *from-reads* relation (fr) [Ahamad et al. 1995; Alglave et al. 2010] relates a read to all writes that are later in the coherence order than the write from which it read, defined as rf<sup>-1</sup>; co.

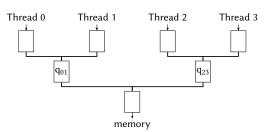

This behaviour can be observed in Flowing with the topology below. After Threads 0 and 2 perform their writes, the write x=1 of Thread 0 can flow to the queue  $q_{01}$  that is shared between Threads 0 and 1, and the write y=1 of Thread 2 can flow to the queue  $q_{23}$  that is shared between Threads 2 and 3. Now Thread 1 can perform its first read, which flows down until it reaches the write x=1 (in queue  $q_{01}$ ) and then it performs its second read which flows down

all the way to memory, reordering with the write x=1 on the way, and reads y=0. Finally Thread 3 performs its first read which flows down until it reaches the write y=1 (in queue  $q_{23}$ ) and then performs its second read which flows down all the way to memory, reordering with the write y=1 on the way, and reads x=0.

## 3 COMPLEXITIES ARISING IN THE NON-MCA ARMV8 ARCHITECTURE

For regular memory accesses Flowing captures the original non-MCA intent with straightforward rules: memory accesses can be reordered only if to distinct memory locations. The strong memory barrier (dmb sy) is also straightforward: it cannot be reordered with any event. Flowing can exhibit non-architectural asymmetry between threads, which was addressed by the POP model.

<sup>&</sup>lt;sup>1</sup>Throughout the paper, litmus test names highlighted in blue link to a state of rmem with the test loaded.

Things become more complex when considering other kinds of memory accesses that guarantee stronger properties (store-release, load-acquire and load/store-exclusive), and weaker kinds of barriers (dmb st and dmb ld). When the vendor documentation does not clearly define the architectural intent, our normal, and previously effective, strategy has been to create litmus tests that demonstrate the phenomenon, run those on real hardware using the litmus tool [Alglave et al. 2011], discuss with architects what microarchitectural mechanisms they implement (or think might reasonably be implemented) that would give rise to the phenomenon, and finally, adapt an operational model with abstractions of those mechanisms. For example, the "PPOCA" test of Sarkar et al. [2011] is observable on ARM and POWER because, microarchitecturally, reads can be satisfied from writes in thread-local store queues, even on speculative paths (if the write and read follow an as-yet-uncommitted conditional branch); that can be smoothly modelled with write-forwarding in the operational models, giving a clean envelope around all anticipated implementations.

For non-MCA ARM, however, the lack of non-MCA processor implementations meant that experiment was not informative, and indeed the space of hypothetical microarchitectural implementations was not clear. Our discussions did not identify realistic mechanisms that are exactly as relaxed as the architectural intent, and in fact, the lack of MCA in the ARM architecture was motivated by a general desire for implementation freedom rather than specific microarchitectural designs. Broadly, non-MCA permits two hardware optimisations: (1) a shared, pre-cache store-buffer that allows early forwarding of data between a subset of the system threads, and (2) the ability to post snoop invalidations to other caches participating in a cache-coherence protocol without waiting for their acknowledgement. Whilst these optimisations may be worthwhile (or even necessary) in some contexts, for ARM there was a clear internal conclusion that these optimisations offer little benefit in ARM's context, partly because the ARM bus architecture (AMBA) has always been MCA. In this light, the greater flexibility was not considered to outweigh the complexities that non-MCA added in ARMv8.

The rest of this section describes some of the issues we encountered during work to establish formal models for non-MCA ARMv8: refining the Flowing and POP models of Flur et al. [2016b, 2017], developing axiomatic models (within ARM), and trying to establish the correspondence between the two. The complexity this uncovered was part of the motivation for the shift to the new MCA ARMv8 model we address in the rest of the paper, where these issues disappear. The discussion may also be instructive for those developing other memory models.

**MCA of store-release.** The non-MCA ARMv8 documentation stated [ARM Ltd. 2016, B2.7.3] "A Store-Release instruction is multicopy atomic when observed with a Load-Acquire instruction". When this line was discussed with ARM architects they explained that this would be achieved in practice by allowing a load-acquire read to be satisfied from a store-release write only after that write has propagated to all cores. In the Flowing model this is expressed by forbidding load-acquire reads from reading from store-release writes in a queue; they can only read from such writes in memory.

As intended, this forbids a version of IRIW where all the stores are store-release and all the loads are load-acquire (Test IRIW+poaas+LL). However, it unintentionally also forbids the variant where all the stores are store-release and just the first load of each thread is a load-acquire (IRIW+poaps+LL), which the original architectural intent would allow (as the MCA of the store-releases is not guaranteed for the regular loads). Our discussions did not identify a reasonable non-MCA microarchitectural mechanism that would forbid IRIW+poaas+LL and still allow IRIW+poaps+LL. This issue does not arise for MCA ARMv8: the architecture is now defined to be MCA for all memory accesses, irrespective of whether they are release/acquire or not, which forbids both these litmus tests.

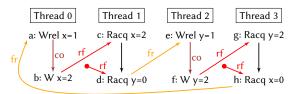

**Vanishing reads and acquire tokens.** In actual implementations, a read request leaves no trace in the caches or buffers after it is satisfied. This could be matched in Flowing by removing the

read request from the queues. By itself, however, this would lead to behaviour that is unsound w.r.t. C/C++11. Consider a C/C++11 version of IRIW where all the loads are sequentially consistent (SC) and each writing thread performs two stores, the first one being SC and the second one relaxed (to the same location), with the loads reading from the latter. As those relaxed stores are the immediate modification-order successors of the SC store from the same thread, they form a release sequence [Batty et al. 2011; Becker 2011]. C/C++11 guarantees SC behaviour in this case, and therefore this execution is forbidden. The mapping of this litmus test to ARMv8 is below, using store-release and load-acquire instructions (the C and ARM versions are named WW+RR+WW+RR+wsiscrlx+poscsc+wsiscrlx+poscsc.c and WW+RR+wsilp+poaa+wsilp+poaa, in the supplementary material). As with the §2 example, the first reads of each thread can read from the

intermediate-level queues. If those reads were removed at this point, nothing would prevent the following reads from flowing all the way to memory and reading from the initial state, making this behaviour allowed. To avoid this, the flowing model introduced "acquire

tokens": it kept the satisfied read in the queue, but below the write it was satisfied from [Flur et al. 2016a, Satisfy read from segment]. This gave the extensional behaviour originally intended by the architects, but it did not abstract from any known or imagined microarchitecturally reasonable mechanism, reducing confidence in the model, and highlighting the difficulty of establishing good architecture models unguided by plausible implementation practice.

Cumulativity for dmb ld and dmb st. A similar vanishing-reads issue arose for dmb ld. The dmb sy barrier orders arbitrary memory actions that are thread-locally before and after it, and it also has cumulativity properties. Among other things, it orders stores that the barrier thread reads from, before the dmb sy, w.r.t. stores that it performs after (A-cumulativity), and orders stores (from the barrier thread) that occur before the barrier w.r.t. stores (from any thread) that appear logically after the barrier (B-cumulativity). For regular accesses, this worked straightforwardly in the non-MCA architecture.

For dmb ld, on the other hand, it was unclear from the ARM documentation which cumulative properties dmb ld enforced. Following discussion, ARM decided (for the earlier non-MCA architecture) that dmb ld should not be cumulative in any way. Instead, it was made similar to an address dependency, which is reflected in Flowing by making dmb ld handled entirely in the thread semantics (not submitted to the queues), thus eliminating the issue of vanishing reads for dmb ld. In the non-MCA architecture, this weakening would make dmb ld unsound as a mapping of the C11 fence-acquire. Initially, ARM believed that this should be fixed by changing either the mapping or the semantics of the C/C++11 fence-acquire. Instead, shifting to MCA for all memory accesses strengthens dmb ld and makes the mapping sound.

For dmb st, the ARM conclusion for the non-MCA architecture was to make dmb st be only B-cumulative, again following extended discussion. That was straightforward to express in Flowing. Again, in the MCA model the question is moot.

Partially satisfying reads. Mixed-size accesses also present unique challenges in the non-MCA context. To guarantee single-copy atomicity in the Flowing model (a read that reads from any byte of a write cannot also read from any coherence-hidden byte of another write), when a read is partially satisfied by a write with a smaller memory footprint, the unsatisfied part of the read and the write are reordered and never allowed to be reordered with each other again. This reordering has no analogy in real microarchitecture, as current implementations typically do not allow partial

satisfaction of reads, yet the architecture intentionally did not forbid it. In fact, one of the processor implementation errata mentioned by Flur et al. [2017], #855830 of ARM Ltd. [2017], was found by noticing the issue for a previous version of the Flowing model, conjecturing that it would be a likely hardware bug, and trying the corresponding test on hardware.

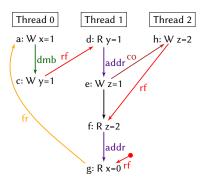

**Big detour.** One can create order between memory accesses from the same thread using intervening memory accesses from another thread. For example, the litmus test on the left is a version of MP with the order in Thread 0 enforced by a barrier and the order in Thread 1 enforced by a combination of address dependencies and a "detour" [Alglave et al. 2014] via Thread 2. In the general case the detour

might involve dependencies or other means of creating order in the third thread, including nested detours. Capturing such "big detour" examples in axiomatic models required the definition of the relations in the model to be mutually recursive. This was the straw that broke the camel's back in terms of readability among industry colleagues: it meant that one could not easily incrementally build up a picture of the relations; instead one had to iterate to a (global) fixed point.

**Write subsumption.** Another key difficulty in axiomatic modelling for the non-MCA ARMv8 architecture was handling *write subsumption*. In that architecture, and in the Flowing and POP models of Flur et al. [2016b, 2017], a write was allowed to propagate to other threads before program-order

preceding writes to the same location were committed: the earlier write could be *subsumed* by the later ones. For example, the illustrated variant of LB, with data dependencies and with a second non-dependent write on the right thread (LB+data+data-wsi), was allowed. This was handled in the axiomatic model with a variant of the usual coherence order, but again proved challenging to explain.

# 4 THE MCA ARMv8 ARCHITECTURE

The most notable change in the revised ARMv8 architecture is the switch to an MCA model.<sup>2</sup> This makes tests such as IRIW+addrs and WRC+addrs forbidden, together with all but the last test named in §3, and means that the concept of barrier cumulativity is no longer required. The remaining relaxed-memory effects (which are still subtle) are all due to thread-local out-of-order and speculative execution and thread-local buffering. Writes can still be visible to program-order later reads on the same thread (even on speculative paths, as in PPOCA) before becoming visible to other threads.

The second change is a strengthening of the order preserved in the threads: the revised ARMv8 memory model forbids write subsumption, and thereby creates order from a data-dependent write to program-order successor writes to the same address, forbidding also the last test from §3.

<sup>&</sup>lt;sup>2</sup>Terminology: the ARM documentation calls this an "other multicopy-atomic" model (to distinguish from the original definition of multicopy atomicity by Collier [1992], which required atomicity w.r.t. reads by all threads, including the writer thread), while here we simply say "multicopy-atomic", for consistency with the more recent normal usage.

The third change is concerned with the definition of dependencies (read-to-read address and control+isb/isync dependencies³, and read-to-write address, data, and control dependencies). Historically other architectures, e.g. IBM POWER, have explicitly respected all syntactic dependencies. Previous versions of the ARM architecture text introduced notions of "true" and "false" dependencies, aiming to require processors only to preserve "true" dependencies, to allow optimisations in value computations (such as x AND 0 = 0): "A False Register data dependency is a Register data dependency where no register in the system holds a variable for which a change of the first data value causes a change of the second data value." [ARM Ltd. 2016, B2-92]. It is unclear how this could be made precise in a satisfactory way, as "causes a change" itself involves the whole concurrency and nondeterministic semantics. Recent work on C/C++ concurrency illustrates the difficulties of defining envelopes around such optimisations [Batty et al. 2015; Pichon-Pharabod and Sewell 2016; Kang et al. 2017]. The revised ARMv8 architecture makes no such distinction.

Since no production hardware implementations have exploited the relative weakness of early ARMv8 compared with the revised architecture, all these changes have been "backported" — they apply to already-existing ARMv8 hardware, and the ARMv8.0 architecture has been revised.

# 5 INTRODUCING THE TWO FORMAL MODELS

We capture the ARM architectural intent for MCA ARMv8 with two formal models, an operational model and an axiomatic model, that are proved equivalent (for the instruction-set features covered by both, and for finite executions). Both have their advantages, as we discuss below, so having such an equivalence result is the ideal situation, not often achieved.

The operational model builds on Flur et al. [2017, 2016b]; Gray et al. [2015]; Sarkar et al. [2012, 2011]. The MCA architecture could be captured using the Flowing model of Flur et al. [2017, 2016b], as recalled in §2, by choosing a flat topology in which all hardware threads are siblings. However, that would have internal redundancy, as some relaxed behaviours could be exhibited either by out-of-order execution within a thread or by reordering in its queue. One of the key observations of the current work is that the necessary relaxations can (with some care) be made admissible in the thread semantics alone. That means the hierarchical interconnect can be replaced by a memory which essentially just records the most recent write to each location. This simplifies both the operational model itself and the relationship between it and the axiomatic model.

The operational model supports incremental construction of arbitrary allowed executions. It is a nondeterministic labelled transition system, of states and transitions between them, expressed as a function that computes the possible transitions of each state. That makes it usable in several ways. Given an initial program, memory, and register state:

- (1) one can explore the possible executions interactively;

- (2) for small litmus-test examples, one can calculate the set of all allowed outcomes by an exhaustive search; and

- (3) for larger examples, e.g. for small instances of concurrent algorithms, one can explore longer randomly-chosen single traces, or sets thereof.

Importantly, the operational model aims to explain and define the envelope of architecturally allowed relaxed-memory behaviour in an "abstract microarchitectural" style, with relaxed-memory behaviour arising in the model in essentially the same way that it does in hardware implementations. (Of course, an actual hardware implementation that extensionally conforms to the model could be less aggressive than the model, or it could be more aggressive internally, as some are, so long as it does not extensionally allow more programmer-visible behaviours.) Accordingly, the model makes out-of-order and speculative execution explicit, as these are essentially what give rise to the relaxed

<sup>&</sup>lt;sup>3</sup>a control dependency followed by an isb (ARMv8)/isync (POWER) instruction barrier

behaviour allowed by the ARM architecture and observed on ARM hardware. Similarly following conventional hardware practice, the model does not involve value speculation (except of computed branch addresses, where our tool necessarily approximates), or let writes be speculatively visible to other threads

Given that, the model aims to abstract as much as possible from the lower-level microarchitectural detail of actual implementations, while keeping the intended envelope of programmer-visible behaviour: out-of-order and speculative execution are explicit, but in terms of an abstract tree or list of instruction instances, not a concrete pipeline; the instruction semantics are specified in terms of execution of their instruction-description pseudocode from the ARM manual (manually or automatically translated from the ASL used there into the Sail language of Gray et al. [2015] and [Flur et al. 2016b]), rather than hardware operations; the observable effects of shadow registers and register renaming are included by having instruction instances read from their predecessors rather than having explicit register files and renaming; there are no explicit buffers (of writes, read requests, or barriers); and there is no cache hierarchy or cache protocol.

Supporting incremental construction of executions with explicit speculative execution requires the operational model to roll-back and restart instructions in certain circumstances, and to discard speculative paths that turn out to be mistaken. That adds some complexity, but keeps the clear correspondence with microarchitecture. (One could define an operational model that just deadlocks in such cases, effectively a roll-back to the initial state; that would support exhaustive search but be awkward in interactive exploration.) The fact that the operational model constructs candidate executions incrementally means that it can execute the pseudocode of each instruction instance on concrete values; it does not require symbolic execution of the ASL or Sail metalanguage used for instruction description (modulo calculation of some register and memory footprint information).

Following Flur et al. [2017], the operational model supports mixed-size and misaligned accesses: aligned memory accesses of different sizes (e.g. 1, 2, 4, 8, or 16 bytes) can overlap, single load and store instructions can (e.g. if misaligned) give rise to many memory read and write accesses, and register accesses can touch different parts of registers. This also adds complexity, but it is necessary for defining the semantics of real code, rather than just non-mixed-size litmus tests.

The abstract-microarchitectural nature of the model has made it malleable in the face of architectural changes over time, and the fact that we have to define the model behaviour in any model state has helped identify previously unconsidered subtleties, including some of those of §3.

The axiomatic model, on the other hand, is expressed as a predicate that defines which candidate complete executions are permitted, where a candidate execution is a graph of memory-access and barrier events, related by program-order, dependency, coherence, and atomicity relations. This model is expressed using the herd tool of Alglave and Maranget [2017]; Alglave et al. [2014].

The axiomatic model does not describe the incremental construction of partial executions; only the successful complete executions. For small litmus-test examples, one can calculate the set of all allowed outcomes using herd, analogous to (2) above, but it does not support the interactive or single-random-trace exploration of (1) and (3). Historically the axiomatic computation of allowed outcomes has been considerably faster than the exhaustive memoised search used for operational models, which is especially combinatorially challenging for non-MCA models. The shift to MCA has made this less of an issue, as both computations are fast enough to allow easy iteration during model development: the operational model 55 minutes while herd takes 7 minutes, for our entire non-mixed test suite of around 9 000 tests. In contrast, the non-MCA Flowing and POP models took days, with some tests still not terminating.

The two models differ in their temporal granularity: the axiomatic model has a single event for each memory access instruction, while in the operational model each instruction gives rise to many transitions. For example, for a load instruction there are transitions for the instruction fetch/decode, for register reads and writes, for instruction-internal steps of the ASL/Sail pseudocode, for announcing the memory footprint (when that becomes provisionally known), for each individual read being satisfied (from memory or by forwarding), for the point at which all reads are satisfied, and for the point when the instruction is finished and cannot be restarted. One can single-step through each of these, if desired, but all the transitions except those for read-satisfaction can be taken eagerly, as soon as they are enabled, without excluding other behaviour; this is important for performance of the exhaustive search.

This structure of the operational model is desirable in several ways. It arises from the choice of an abstract microarchitectural style, which gives a clear operational intuition and correspondence to plausible hardware implementations; from incremental construction of partial possibly-speculative executions; from the handling of mixed-size; and from the integration with the instruction-description ASL/Sail semantics. But it does introduce complexity with respect to the axiomatic model, which defines the thread-local memory ordering between (non-mixed-size) memory accesses in a more direct way. Axiomatic modelling is much simplified in the MCA setting, just as operational modelling is: those thread-local ordering properties are now the only things the axiomatic model has to handle, without non-MCA propagation and cumulativity effects. Pleasingly, the main part of the axiomatic model fits on a single page. A priori one may find it surprising that one can define a satisfactory axiomatic model in terms of just a single event for each memory access instruction; this paper may help explain why that is so, by showing how certain causal dependencies that involve many steps in the operational model are collapsed to access-to-access relational constraints in the axiomatic model.

Note also that the axiomatic model relies on primitive notions of address, data, and control dependencies (hard-coded into the herd implementation), while in the operational model these arise from the instruction semantics and from the thread-semantics treatment of register accesses and conditional branches (taking them as primitive simplifies the concurrency model, but is less foundational). The axiomatic model can then be expressed using just inductive definitions of binary relations, e.g. as in the herd model definition language, whereas the enumeration of operational model transitions requires a more expressive metalanguage — it is essentially a typed pure terminating functional program (or higher-order-logic definition), in lem [Mulligan et al. 2014].

The two models differ in the features they cover, for historical reasons: they both cover memory accesses (regular, release/acquire, and exclusives) and barriers (dmb sy, dmb st, and dmb ld), but the axiomatic model does not cover mixed-size accesses, while the operational model does not cover the more relaxed form of load-acquire (LDAPR) introduced in ARMv8.3, or the atomic readmodify-write instructions introduced in ARMv8.1. Neither covers load/store-pair instructions, exceptions, interrupts, floating-point, vector instructions, MMU behaviour, self-modifying code, or other systems aspects. The operational model is integrated with a more authoritative instruction semantics, derived from the ARM-internal specification, for a larger fragment of the ISA (including, e.g., all the instructions used in compiling simple C code), while the axiomatic model currently relies on the smaller and more ad hoc instruction semantics built into herd. Currently, herd's instruction semantics differs from that of the operational model in that the success bit of a successful store-exclusive introduces address/data/control dependencies from the load-exclusive it is paired with. This does not match the intention of the ARMv8 architecture where the success bit is not supposed to introduce any dependencies.

Each style has advantages for certain kinds of proof: the operational model supports induction on traces, while the axiomatic model directly gives one explicit properties of complete executions.

#### 6 AN OPERATIONAL MODEL FOR MCA ARMy8

In the following we give a prose description of our formal operational model for multicopy-atomic ARMv8, the *Flat model*. For brevity we omit load/store-exclusive instructions; the full description, including those, is in the supplementary material, as is the formal model. The full description also includes remarks about the difficulties in modelling ARMv8 exclusive instructions operationally (due to the architecture's intention to allow store exclusives to promise success/failure very early).

To see the model's behaviour on example programs, using the web interface, we give a step-by-step execution of how the model allows the PPOCA test as an example (press 'Enter' repeatedly to follow the steps): https://is.gd/qSJM6H.

The operational model is expressed as a state machine, with states that are an abstract representation of hardware machine states. We first introduce the model states and transitions informally.

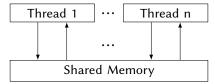

Model states. A model state consists just of a shared memory and a tuple of thread model states:

The shared memory state effectively just records the most recent write to each location, together with some additional data for exclusives.

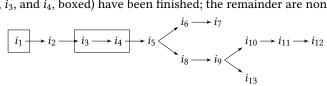

Each thread model state consists principally of a list or tree of instruction instances, some of which have been finished, and some of which have not. For example, below we show a thread model state with instruction instances  $i_1, \ldots, i_{13}$ , and the program-order-successor relation between them. Three of those  $(i_1, i_3, \text{ and } i_4, \text{ boxed})$  have been finished; the remainder are non-finished.

Non-finished instruction instances can be subject to restart, e.g. if they depend on an out-of-order or speculative read that turns out to be unsound. The finished instances are not necessarily contiguous: in the example,  $i_3$  and  $i_4$  are finished even though  $i_2$  is not, which can only happen if they are sufficiently independent. Instruction instances  $i_5$  and  $i_9$  are conditional branches for which the thread has fetched multiple possible successors. When a conditional branch is finished, any untaken alternative paths are discarded, and instruction instances that follow (in program order) a non-finished conditional branch cannot be finished until that conditional branch is. One can choose whether or not to allow simultaneous exploration of multiple successors of a conditional branch (as shown above); this does not affect the set of allowed outcomes.

The intra-instruction behaviour of a single instruction can largely be treated as sequential (but not atomic) execution of its ASL/Sail pseudocode. Each instruction instance state includes a pseudocode execution state, which one can think of as a representation of the pseudocode control state, pseudocode call stack, and local variable values. An instruction instance state also includes information, detailed below, about the instruction instance's memory and register footprints, its register and memory reads and writes, whether it is finished, etc.

**Model transitions.** For any state, the model defines the set of allowed transitions, each of which is a single atomic step to a new abstract machine state. Each transition arises from the next step of a single instruction instance; it will change the state of that instance, and it may depend on or change

the rest of its thread state and/or the shared memory state. Instructions cannot be treated as atomic units: complete execution of a single instruction instance may involve many transitions, which can be interleaved with those of other instances in the same or other threads, and some of this is programmer-visible. The transitions are introduced below and defined in  $\S6.4$ , with a precondition and a construction of the post-transition model state for each. The transitions labelled  $\circ$  can always be taken eagerly, as soon as they are enabled, without excluding other behaviour; the  $\bullet$  cannot.

#### Transitions for all instructions:

- Fetch instruction: This transition represents a fetch and decode of a new instruction instance, as a program-order successor of a previously fetched instruction instance, or at the initial fetch address for a thread.

- Register read: This is a read of a register value from the most recent program-order predecessor instruction instance that writes to that register.

- Register write

- Pseudocode internal step: this covers ASL/Sail internal computation, function calls, etc.

- Finish instruction: At this point the instruction pseudocode is done, the instruction cannot be restarted or discarded, and all memory effects have taken place. For a conditional branch, any non-taken po-successor branches are discarded.

#### Load instructions:

- Initiate memory reads of load instruction: At this point the memory footprint of the load is provisionally known and its individual reads can start being satisfied.

- Satisfy memory read by forwarding from writes: This partially or entirely satisfies a single read by forwarding from its po-previous writes.

- Satisfy memory read from memory: This entirely satisfies the outstanding slices of a single read, from memory.

- Complete load instruction (when all its reads are entirely satisfied): At this point all the reads of the load have been entirely satisfied and the instruction pseudocode can continue execution. A load instruction can be subject to being restarted until the Finish instruction transition. In some cases it is possible to tell that a load instruction will not be restarted or discarded before that, e.g. when all the instructions po-before the load instruction are finished. The Restart condition over-approximates the set of instructions that might be restarted.

#### Store instructions:

- Initiate memory writes of store instruction, with their footprints: At this point the memory footprint of the store is provisionally known.

- Instantiate memory write values of store instruction: At this point the writes have their values and program-order-subsequent reads can be satisfied by forwarding from them.

- Commit store instruction: At this point the store is guaranteed to happen (it cannot be restarted or discarded), and the writes can start being propagated to memory.

- Propagate memory write: This propagates a single write to memory.

- Complete store instruction (when its writes are all propagated): At this point all writes have been propagated to memory, and the instruction pseudocode can continue execution.

### Barrier instructions:

Commit barrier

## 6.1 Intra-instruction Pseudocode Execution

To link the model transitions introduced above to the execution of the instructions an interface is needed between Sail and the rest of the concurrency model. For each instruction instance this

intra-instruction semantics is expressed as a state machine, essentially running the instruction pseudocode, where each pseudocode execution state is a request of one of the following forms:

Read\_mem(read\_kind, address, size, read\_continuation) Read request

Write\_ea(write\_kind, address, size, next\_state) Write effective address

Write\_memv(memory\_value, write\_continuation) Write value

BARRIER(barrier\_kind, next\_state) Barrier

READ\_REG(reg\_name, read\_continuation)

Register read request

Write\_reg(reg\_name, register\_value, next\_state) Write register

Internal(next\_state) Pseudocode internal step

Done End of pseudocode

Each of these states is a suspended computation with a request for an action or input from the concurrency model and, except in the case of Done, a continuation for the remaining execution.

Here memory values are lists of bytes, addresses are 64-bit numbers, read and write kinds identify whether they are regular, exclusive, and/or release/acquire operations, register names identify a register and slice thereof (start and end bit indices), and the continuations describe how the instruction instance will continue for any value that might be provided by the surrounding memory model. This largely follows Gray et al. [2015, §2.2], except that memory writes are split into two steps, WRITE\_EA and WRITE\_MEMV. We ensure these are paired in the pseudocode, but there may be other steps between them: it is observable that the WRITE\_EA can occur before the value to be written is determined, because the potential memory footprint of the instruction becomes provisionally known then.

We ensure that each instruction has at most one memory read, memory write, or barrier step, by rewriting the pseudocode to coalesce multiple reads or writes, which are then split apart into the architecturally atomic units by the thread semantics; this gives a single commit point for all memory writes of an instruction.

Each bit of a register read should be satisfied from a register write by the most recent (in program order) instruction instance that can write that bit, or from the thread's initial register state if there is no such. That instance may not have executed its register write yet, in which case the register read should block. The semantics therefore has to know the register write footprint of each instruction instance, which it calculates when the instruction instance is created. We ensure in the pseudocode that each instruction does exactly one register write to each bit of its register footprint, and also that instructions do not do register reads from their own register writes. In some cases, but not in the fragment of ARM that we cover at present, register write footprints need to be dynamically recalculated, when the actual footprint only becomes known during pseudocode execution.

Data-flow dependencies in the model emerge from the fact that a register read has to wait for the appropriate register write to be executed (as described above). This has to be carefully handled in order not to create unintentional strength. First, for some instructions we need to ensure that the pseudocode is in the maximally liberal order, e.g. to allow early computed-address register writebacks before the corresponding memory write. Leaving load-pair aside (which we do not cover), and the treatment of the multiple reads or writes that can be associated with a single load or store instruction (which we do), we have not so far needed other intra-instruction concurrency. Second, the model has to be able to know when a register read value can no longer change (i.e. due to instruction restart). We approximate that by recording, for each register write, the set of register and memory reads the instruction instance has performed at the point of executing the write. This information is then used as follows to determine whether a register read value is final: if the instruction instance that performed the register write from which the register reads from is finished, the value is final; otherwise check that the recorded reads for the register write do not include

memory reads, and continue recursively with the recorded register reads. For the instructions we cover this approximation is exact.

We express the pseudocode execution semantics in two ways: a definitional interpreter for Sail [Gray et al. 2015], with an exhaustive symbolic mode to (re)calculate an instruction's memory and register footprints, and as a shallow embedding, translating Sail into directly executable code, with separate hand-written definitions of the footprint functions. The two are essentially equivalent: the first lets one small-step through the pseudocode interactively, while the second is more efficient and should be more convenient for proof.

#### 6.2 Instruction Instance States

Each instruction instance *i* has a state comprising:

- program\_loc, the memory address from which the instruction was fetched;

- *instruction\_kind*, identifying whether this is a load, store, or barrier instruction, each with the associated kind; or a conditional branch; or a 'simple' instruction.

- regs\_in, the set of input reg\_names, as statically determined;

- regs\_out, the output reg\_names, as statically determined;

- pseudocode\_state (or sometimes just 'state' for short), one of

- *PLAIN next\_state*, ready to make a pseudocode transition;

- PENDING\_MEM\_READS read\_cont, performing the read(s) from memory of a load; or

- *Pending\_mem\_writes write\_cont*, performing the write(s) to memory of a store;

- reg\_reads, the accumulated register reads, including their sources and values, of this instance's execution so far;

- reg\_writes, the accumulated register writes, including dependency information to identify the register reads and memory reads (by this instruction) that might have affected each;

- mem\_reads, a set of memory read requests. Each request includes a memory footprint (an address and size) and, if the request has already been satisfied, the set of write slices (each consisting of a write and a set of its byte indices) that satisfied it.

- *mem\_writes*, a set of memory write requests. Each request includes a memory footprint and, when available, the memory value to be written. In addition, each write has a flag that indicates whether the write has been propagated (passed to the memory) or not.

- information recording whether the instance is committed, finished, etc.

Read requests include their read kind and their memory footprint (their address and size), the as-yet-unsatisfied slices (the byte indices that have not been satisfied), and, for the satisfied slices, information about the write(s) that they were satisfied from. Write requests include their write kind, their memory footprint, and their value. When we refer to a write or read request without mentioning the kind of request we mean the request can be of any kind. A load instruction which has initiated (so its read request list *mem\_reads* is not empty) and for which all its read requests are satisfied (i.e. there are no unsatisfied slices) is said to be *entirely satisfied*.

## 6.3 Thread States

The model state of a single hardware thread includes:

- *thread\_id*, a unique identifier of the thread;

- register\_data, the name, bit width, and start bit index for each register;

- *initial\_register\_state*, the initial register value for each register;

- initial\_fetch\_address, the initial fetch address for this thread;

- instruction\_tree, a tree or list of the instruction instances that have been fetched (and not discarded), in program order.

#### 6.4 Model Transitions

**Fetch instruction.** A possible program-order successor of instruction instance i can be fetched from address loc if:

- (1) it has not already been fetched, i.e., none of the immediate successors of *i* in the thread's *instruction\_tree* are from *loc*;

- (2) *loc* is a possible next fetch address for *i*:

- (a) for a non-branch/jump instruction, the successor instruction address (i.program\_loc+4);

- (b) for an instruction that has performed a write to the program counter register (\_PC), the value that was written;

- (c) for a conditional branch, either the successor address or the branch target address<sup>4</sup>; or

- (d) for a jump to an address which is not yet determined, any address (this is approximated in our tool implementation, necessarily); and

- (3) there is a decodable instruction in program memory at *loc*.

Note that this allows speculation past conditional branches and calculated jumps.

Action: construct a freshly initialized instruction instance *i'* for the instruction in the program memory at *loc*, including the static information available from the ISA model such as its *instruction\_kind*, *regs\_in*, and *regs\_out*, and add *i'* to the thread's *instruction\_tree* as a successor of *i*.

This involves only the thread, not the storage subsystem, as we assume a fixed program rather than modelling fetches with memory reads; we do not model self-modifying code.

**Initiate memory reads of load instruction.** An instruction instance *i* with next state *READ\_MEM*(*read\_kind*, *address*, *size*, *read\_cont*) can initiate the corresponding memory reads. Action:

- (1) Construct the appropriate read requests *rrs*:

- if address is aligned to size then rrs is a single read request of size bytes from address;

- otherwise, *rrs* is a set of *size* read requests, each of one byte, from the addresses *address...address+size-1*.

- (2) set i.mem\_reads to rrs; and

- (3) update the state of *i* to *PENDING\_MEM\_READS read\_cont*.

**Satisfy memory read by forwarding from writes.** For a load instruction instance *i* in state *PENDING\_MEM\_READS read\_cont*, and a read request, *r* in *i.mem\_reads* that has unsatisfied slices, the read request can be partially or entirely satisfied by forwarding from unpropagated writes by store instruction instances that are po-before *i*, if the *read-request-condition* predicate holds. This is if:

- (1) all po-previous dmb sy and isb instructions are finished;

- (2)  $\left[\begin{smallmatrix} dmb \ ld' \\ dmb \ st \end{smallmatrix}\right]$  all po-previous dmb ld instructions are finished;

- (3)  $\begin{bmatrix} \text{release/} \\ \text{acquire} \end{bmatrix}$  if i is a load-acquire, all po-previous store-releases are finished; and

- (4) [release/] all non-finished po-previous load-acquire instructions are entirely satisfied.

Let wss be the maximal set of unpropagated write slices from store instruction instances po-before i, that overlap with the unsatisfied slices of r, and which are not superseded by intervening stores that are either propagated or read from by this thread. That last condition requires, for each write slice ws in wss from instruction i':

- that there is no store instruction po-between i and i' with a write overlapping ws, and

- that there is no load instruction po-between i and i' that was satisfied from an overlapping write slice from a different thread.

<sup>&</sup>lt;sup>4</sup>In AArch64, all the conditional branch instructions have statically determined addresses.

#### Action:

- (1) update r to indicate that it was satisfied by wss; and

- (2) restart any speculative instructions which have violated coherence as a result of this, i.e., for every non-finished instruction *i'* that is a po-successor of *i*, and every read request *r'* of *i'* that was satisfied from *wss'*, if there exists a write slice *ws'* in *wss'*, and an overlapping write slice from a different write in *wss*, and *ws'* is not from an instruction that is a po-successor of *i*, restart *i'* and its data-flow dependents (including po-successors of load-acquire instructions).

Note that store-release writes cannot be forwarded to load-acquires: a load-acquire instruction cannot be satisfied before all po-previous store-release instructions are finished, and wss does not include writes from finished stores (as those must be propagated).

**Satisfy memory read from memory.** For a load instruction instance *i* in state *Pending\_mem\_reads* read\_cont, and a read request *r* in *i.mem\_reads*, that has unsatisfied slices, the read request can be satisfied from memory.

If: the read-request-condition holds (see previous transition).

Action: let *wss* be the write slices from memory covering the unsatisfied slices of *r*, and apply the action of Satisfy memory read by forwarding from writes.

Note that Satisfy memory read by forwarding from writes might leave some slices of the read request unsatisfied. Satisfy memory read from memory, on the other hand, will always satisfy all the unsatisfied slices of the read request.

**Complete load instruction (when all its reads are entirely satisfied).** A load instruction instance *i* in state *Pending\_mem\_reads* read\_cont can be completed (not to be confused with finished) if all the read requests *i.mem\_reads* are entirely satisfied (i.e., there are no unsatisfied slices).

Action: update the state of *i* to *PLAIN* (*read\_cont* (*memory\_value*)), where *memory\_value* is assembled from all the write slices that satisfied *i.mem\_reads*.

**Initiate memory writes of store instruction, with their footprints.** An instruction instance *i* with next state *Write\_EA*(*write\_kind*, *address*, *size*, *next\_state'*) can announce its pending write footprint. Action:

- (1) construct the appropriate write requests:

- if address is aligned to size then ws is a single write request of size bytes to address;

- otherwise ws is a set of size write requests, each of one byte size, to the addresses address...address+size-1.

- (2) set i.mem\_writes to ws; and

- (3) update the state of *i* to *PLAIN next\_state'*.

Note that at this point the write requests do not yet have their values. This state allows non-overlapping po-following writes to propagate.

**Instantiate memory write values of store instruction.** An instruction instance *i* with next state *Write\_memory\_value, write\_cont*) can initiate the corresponding memory writes. Action:

- (1) split memory\_value between the write requests i.mem\_writes; and

- (2) update the state of *i* to *PENDING\_MEM\_WRITES write\_cont*.

**Commit store instruction.** For an uncommitted store instruction i in state  $PENDING\_MEM\_WRITES$  write\_cont. i can commit if:

- (1) i has fully determined data (i.e., the register reads cannot change, see §6.5);

- (2) all po-previous conditional branch instructions are finished;

- (3) all po-previous dmb sy and isb instructions are finished;

- (4) [ dmb ld/ dmb st] all po-previous dmb ld instructions are finished;

- (5) [release/acquire] all po-previous load-acquire instructions are finished;

- (6) all po-previous store instructions have initiated and so have non-empty mem\_writes;

- (7)  $\begin{bmatrix} release/ \\ acquire \end{bmatrix}$  if i is a store-release, all po-previous memory access instructions are finished;

- (8)  $\begin{bmatrix} \frac{dmb \, Id}{dmb \, st} \end{bmatrix}$  all po-previous dmb st instructions are finished;

- (9) all po-previous memory access instructions have a fully determined memory footprint; and

- (10) all po-previous load instructions have initiated and so have non-empty mem\_reads.

Action: record *i* as committed.

**Propagate memory write.** For an instruction *i* in state *Pending\_mem\_writes* write\_cont, and an unpropagated write, *w* in *i.mem\_writes*, the write can be propagated if:

- (1) all memory writes of po-previous store instructions that overlap w have already propagated

- (2) all read requests of po-previous load instructions that overlap with w have already been satisfied, and the load instruction is non-restartable (see §6.5); and

- (3) all read requests satisfied by forwarding w are entirely satisfied.

#### Action:

- (1) restart any speculative instructions which have violated coherence as a result of this, i.e., for every non-finished instruction *i'* po-after *i* and every read request *r'* of *i'* that was satisfied from *wss'*, if there exists a write slice *ws'* in *wss'* that overlaps with *w* and is not from *w*, and *ws'* is not from a po-successor of *i*, restart *i'* and its data-flow dependents;

- (2) record w as propagated; and

- (3) update the memory with w.

**Complete store instruction (when its writes are all propagated).** A store instruction *i* in state *PENDING\_MEM\_WRITES write\_cont*, for which all the memory writes in *i.mem\_writes* have been propagated, can be completed. Action: update the state of *i* to *PLAIN*(*write\_cont*(*true*)).

**Commit barrier.** A barrier instruction *i* in state *PLAIN next\_state* where *next\_state* is *BARRIER*(*barrier\_kind*, *next\_state'*) can be committed if:

- (1) all po-previous conditional branch instructions are finished;

- (2)  $\begin{bmatrix} \frac{dmb}{dmb} \frac{Id}{st} \end{bmatrix}$  if i is a dmb ld instruction, all po-previous load instructions are finished;

- (3)  $\begin{bmatrix} \frac{dmb}{dmb} \frac{1d'}{st} \end{bmatrix}$  if *i* is a dmb st instruction, all po-previous store instructions are finished;

- (4) all po-previous dmb sy barriers are finished;

- (5) if *i* is an isb instruction, all po-previous memory access instructions have fully determined memory footprints; and

- (6) if *i* is a dmb sy instruction, all po-previous memory access instructions and barriers are finished.

Note that this differs from the previous Flowing and POP models: there, barriers committed in program-order and potentially re-ordered in the storage subsystem. Here the thread subsystem is weakened to subsume the re-ordering of Flowing's (and POP's) storage subsystem.

Action: update the state of *i* to *PLAIN next\_state'*.

**Register read.** An instruction instance *i* with next state *Read\_reg(reg\_name, read\_cont)* can do a register read if every instruction instance that it needs to read from has already performed the expected register write.

Let *read\_sources* include, for each bit of *reg\_name*, the write to that bit by the most recent (in program order) instruction instance that can write to that bit, if any. If there is no such instruction, the source is the initial register value from *initial\_register\_state*. Let *register\_value* be the assembled

value from read sources. Action:

- (1) add reg\_name to i.reg\_reads with read\_sources and register\_value; and

- (2) update the state of *i* to *PLAIN* (*read\_cont*(*register\_value*)).

**Register write.** An instruction instance *i* with next state *Write\_reg(reg\_name, register\_value, next\_state')* can do the register write. Action:

- (1) add reg\_name to i.reg\_writes with write\_deps and register\_value; and

- (2) update the state of *i* to *PLAIN next\_state'*.

where *write\_deps* is the set of all *read\_sources* from *i.reg\_reads* and a flag that is set to true if *i* is a load instruction that has already been entirely satisfied.

**Pseudocode internal step.** An instruction instance *i* with next state *Internal(next\_state')* can do that pseudocode-internal step. Action: update the state of *i* to *Plain next\_state'*.

**Finish instruction.** A non-finished instruction *i* with next state DONE can be finished if:

- (1) if i is a load instruction:

- (a) all po-previous dmb sy and isb instructions are finished;

- (b) [ dmb ld/ dmb st] all po-previous dmb ld instructions are finished;

- (c) [release/acquire] all po-previous load-acquire instructions are finished;

- (d) it is guaranteed that the values read by the read requests of *i* will not cause coherence violations, i.e., for any po-previous instruction instance *i'*, let *cfp* be the combined footprint of propagated writes from store instructions po-between *i* and *i'* and fixed writes that were forwarded to *i* from store instructions po-between *i* and *i'* including *i'*, and let *cfp'* be the complement of *cfp* in the memory footprint of *i*. If *cfp'* is not empty:

- (i) i' has a fully determined memory footprint;

- (ii) i' has no unpropagated memory write that overlaps with cfp'; and

- (iii) If i' is a load with a memory footprint that overlaps with cfp', then all the read requests of i' that overlap with cfp' are satisfied and i' can not be restarted (see §6.5).

Here a memory write is called fixed if it is the write of a store instruction that has fully determined data.

- (e)  $\begin{bmatrix} release/ \\ acquire \end{bmatrix}$  if i is a load-acquire, all po-previous store-release instructions are finished;

- (2) i has fully determined data; and

- (3) all po-previous conditional branches are finished.

# Action:

- (1) if *i* is a branch instruction, discard any untaken path of execution, i.e., remove any (non-finished) instructions that are not reachable by the branch taken in *instruction\_tree*; and

- (2) record the instruction as finished, i.e., set finished to true.

# 6.5 Auxiliary Definitions

**Fully determined.** An instruction is said to have fully determined footprint if the memory reads feeding into its footprint are finished: A register write w, of instruction i, with the associated  $write\_deps$  from  $i.reg\_writes$  is said to be fully determined if one of the following conditions hold:

- (1) i is finished; or

- (2) the load flag in write\_deps is false and every register write in write\_deps is fully determined.

An instruction *i* is said to have *fully determined data* if all the register writes of *read\_sources* in *i.reg\_reads* are fully determined. An instruction *i* is said to have a *fully determined memory footprint*

if all the register writes of *read\_sources* in *i.reg\_reads* that are associated with registers that feed into *i*'s memory access footprint are fully determined.

**Restart condition.** To determine if instruction i might be restarted we use the following recursive condition: i is a non-finished instruction and at least one of the following holds,

- (1) there exists an unpropagated write *w* such that applying the action of the Propagate memory write transition to *s* will result in the restart of *i*;

- (2) there exists a non-finished load instruction l such that applying the action of the Satisfy memory read from memory transition to l will result in the restart of i (even if l is already entirely satisfied); or

- (3) there exists a non-finished instruction i' that might be restarted and i is in its data-flow dependents (including po-successors of load-acquire instructions).

# 7 AN AXIOMATIC MODEL FOR MCA ARMv8

Unlike the operational model, where the behaviour of a program is an emergent property of the model's execution, the axiomatic model is a predicate over candidate complete executions, each consisting of its memory and barrier events and binary relations over them, largely as in Alglave et al. [2010, 2014]: program order (po), reads-from (rf), coherence order (co), and read-modify-write (rmw). Here rmw contains the successful read/write-exclusive pairs. The rf, co, and derived fr relations are each subdivided into their "internal" (same-thread) and "external" (different-thread) parts, suffixed i and e respectively. A candidate execution also specifies the address (addr), data (data), and control (ctrl) dependency relations.

The ARMv8 architecture reference manual defines (in text) additional relations in terms of these and uses them to define a predicate capturing when a given candidate execution is architecturally permitted. The main part of the corresponding herd model, by Deacon [2016], is below.

```

let ca = fr | co

(* Coherence-after *)

let obs = rfe | fre | coe

(* Observed-by *)

let dob = addr | data

(* Dependency-ordered-before *)

| ctrl; [W]

| (ctrl | (addr; po)); [ISB]; po; [R]

| addr; po; [W]

| (ctrl | data); coi

| (addr | data); rfi

let aob = rmw

(* Atomic-ordered-before *)

| [range(rmw)]; rfi; [A | Q]

let bob = po; [dmb.full]; po

(* Barrier-ordered-before *)

| [L]; po; [A]

| [R]; po; [dmb.ld]; po

| [A | Q]; po

| [W]; po; [dmb.st]; po; [W]

| po; [L]

| po; [L]; coi

let ob = (obs | dob | aob | bob)+

(* Ordered-before *)

acyclic po-loc | ca | rf     as internal

```

Here [, &, ;, and + are relational union, intersection, composition, and transitive closure, [W], [R], [L], [A] and [Q] are the identity relations over all write, read, release, acquire and acquirePC events respectively, and [ISB], [dmb.full], [dmb.st], [dmb.ld] are the singleton identity on the corresponding barrier events; po-loc relates two same-address memory accesses in program order.

**Per-location relations.** The *coherence-after* relation is the union of the *from-reads* and *coherence-order* relations and represents the order in which writes must propagate with respect to other accesses to the same location as a result of coherence.

The *observed-by* relation is the union of the external subsets of the *reads-from*, *from-reads* and *coherence order* relations and represents inter-thread communication through shared variables. It is therefore not possible for an access to be *observed-by* another access from the same thread.

Intra-thread ordering relations. Intra-thread order can be established using instruction dependencies, atomic instructions or barrier instructions (including load-acquire/store-release instructions). These are described by the *dependency-ordered-before* (dob), *atomic-ordered-before* (aob) and *barrier-ordered-before* (bob) relations respectively, which together form an externally-ordered subset of program order. For example, the [L];po;[A] case of the bob relation describes a store-release appearing in program order before a load-acquire, which is required to be observed in order by all threads as a result of the sequentially-consistent semantics of ARMv8's release/acquire instructions.

**Relational constraints.** The ARMv8 architecture places two constraints on the relations of a candidate execution: the *internal visibility requirement* requires uniprocessor ("SC per location") semantics and the *external visibility requirement* requires that intra-thread ordering respects multicopy atomicity. The axiomatic model expresses the former by prohibiting cycles in the transitive closure of program order, coherence-after and reads-from for a given location, and the latter by requiring that the transitive closure of the intra-thread ordering relations and observed-by forms a partial order, known as *ordered-before* (ob). There is also an additional constraint to ensure that the atomicity of a successful load/store-exclusive pair or an ARMv8.1 atomic RMW instruction

(e.g. cas) is enforced by requiring that the atomic read is not related to the atomic write by an external *from-reads*; *coherence-order* sequence, although this is handled separately by the architecture. To illustrate the definition, recall the previous IRIW+addrs example. This

non-multicopy-atomic behaviour exhibits a cycle of the shape rfe; addr; fre; rfe; addr; fre, which can be expressed as a cycle in ob: (a) is observed-by (b); (b) is dependency-ordered-before (c); (c) is observed-by (d); (d) is observed-by (e); (e) is dependency-ordered-before (f) and (f) is observed-by (a). The external axiom requires ob's acyclicity, and so this candidate execution is forbidden.

## 8 PROOF OF EQUIVALENCE

The basic problem in relating the Flat operational model of §6 and the MCA ARMv8 axiomatic model of §7 [ARM Ltd. 2017; Deacon 2016] (ARMv8-ax for short) is the mismatch between the events the two models refer to: where the axiomatic model has a single event per instruction (one read per load, one write per store) the operational model has several transitions associated with each instruction. Moreover, those transitions have subtle ordering properties: for example, a write

can be read from by forwarding after its instantiate-memory-write transition (when an address and value are provisionally available), which is before it is propagated (and hence visible to be read from memory by other threads), while it can be propagated only when (among other conditions) all previous memory writes have announced their address. The idea underlying the equivalence proof is that there is a correspondence between particular Flat transitions and events in ARMv8-ax's ob relation:

| ARMv8-ax event | Flat transition                                          |

|----------------|----------------------------------------------------------|

| Write          | Propagate memory write                                   |

| Read           | final Satisfy memory read (from memory or by forwarding) |

| Barrier        | Commit barrier                                           |

Under this correspondence the relations of ARMv8-ax can be viewed as describing the order of transitions in a Flat trace for a given execution. For example, [L];po;[A] can be read as saying: in Flat an acquire read can only be satisfied if all program-order preceding release writes are propagated. The proof establishes that under this interpretation the axioms of ARMv8-ax are a sound and complete characterisation of Flat, for finite executions.

However, to state this formally we have to define under which conditions executions of ARMv8-ax and Flat should be considered equivalent, since the two models have different notions of execution: ARMv8-ax has candidate executions; Flat has traces from the initial state. To relate the two notions of executions, we define how a Flat trace induces po, co, rf, and rmw of the ARMv8-ax candidate execution, and then call a Flat trace equivalent to a candidate execution for the same input program if their po, co, rf, and rmw relations are the same.

Let *t* be a finite Flat trace for the given program to a final state. Define:

- $(E, E') \in po_t$  for two events (E, E') if E is before E' in the instruction tree after t (in a final state all instructions are finished, and since finished branch instructions have only one successor in the tree, the tree is a linear order of instructions)

- $(W, W') \in co_t$  for two writes W and W' if W propagates to memory before W' in t

- $(W, R) \in \mathsf{rf}_t$  for a write W and a read R if, in the final satisfy-read transition of R in t, the read R is satisfied by W (we say "final" since if the trace t involves a restart of R it might be satisfied multiple times)

- $(RE, WE) \in rmw_t$  for a read-exclusive RE and write-exclusive WE if in t the write-exclusive WE is successfully paired with the read-exclusive RE.

Given this definition we can state:

THEOREM 8.1. Let x = (po, co, rf, rmw) be a finite candidate execution of ARMv8-axiomatic for a given program P. The execution x is valid under ARMv8-axiomatic if and only if there exists a valid finite trace t of Flat-operational for the program P such that  $(po_t, co_t, rf_t, rmw_t) = (po, co, rf, rmw)$ .

We now give the high-level ideas of the proof for both directions of the implication.

# 8.1 "If": Flat Operational Behaviour Included in ARMv8 Axiomatic

To show that the candidate execution  $x = (po_t, co_t, rf_t, rmw_t)$  induced by an arbitrary valid Flat trace t is allowed by ARMv8-ax we need to prove that any such x satisfies the three axioms: external, internal, and atomic. We first consider external (which can be regarded as the main axiom). We assume that for any trace of Flat there is an equivalent one that has no restarts, which intuitively holds because restarts are down-closed with respect to the information flow in the model, and hence, without loss of generality, that t involves no restarts.

The basic idea of this direction of the proof is that, interpreting ob as a relation between Flat transitions using the correspondence given above, we show that t (viewed as a relation) contains each edge of ob for the candidate execution x. Since Flat traces with no restarts are acyclic by construction, it follows that ob as a subset of t must be acyclic as well. To illustrate the proof of ob  $\subseteq t$  consider an edge  $e \in \mathsf{addr};\mathsf{po}; [\mathsf{ISB}];\mathsf{po}; [\mathsf{R}]$ . Then e = (R, R') for a read R and a polater read R', there is an isb R' pobetween R' and R', and R' is a memory read that feeds into the address of a memory instruction pobefore R'. Under the above correspondence R' is an edge from the satisfaction of R' to that of R'. The proof is now as follows: in Flat

- for R' to be satisfied, all po-earlier isbs, including B, must be finished and hence committed;

- for *B* to commit (since *B* is an isb) all memory reads feeding into the address of a memory instruction po-before *B*, including *R*, have to be finished;

- and hence each of those memory reads, including R, has to be satisfied.

Therefore R is satisfied before R', and t contains all edges of addr;po;[ISB];po;[R]. The proof proceeds in this way for the other edges to show that ob is a subset of t, and hence that ob is acyclic.