### RICE UNIVERSITY

# New Architectures and Mechanisms for the Network Subsystem in Virtualized Servers

by

### Kaushik Kumar Ram

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE

**Doctor of Philosophy**

APPROVED, THESIS COMMITTEE:

Alar L Con

Alan L. Cox, Chair Associate Professor of Computer Science and Electrical and Computer Engineering

Scott Rixner Associate Professor of Computer Science and Electrical and Computer Engineering

Peter J. Varman Professor in Electrical and Computer Engineering

Houston, Texas November, 2012

#### ABSTRACT

New Architectures and Mechanisms for the Network Subsystem in Virtualized Servers

by

### Kaushik Kumar Ram

Machine virtualization has become a cornerstone of modern datacenters. It enables server consolidation as a means to reduce costs and increase efficiencies. The communication endpoints within the datacenter are now virtual machines (VMs), not physical servers. Consequently, the datacenter network now *extends into the server* and *last hop switching* occurs inside the server. Today, thanks to increasing core counts on processors, server VM densities are on the rise. This trend is placing enormous pressure on the network I/O subsystem and the last hop virtual switch to support efficient communication—both internal and external to the server. But the current state-of-the-art solutions fall short of these requirements. This thesis presents new architectures and mechanisms for the network subsystem in virtualized servers to build efficient virtualization platforms.

Specifically, there are three primary contributions in this thesis. First, it presents a new mechanism to reduce memory sharing overheads in driver domain-based I/O architectures. The key idea is to enable a guest operating system to reuse its I/O buffers that are shared with a driver domain. Second, it describes *Hyper-Switch*, a highly streamlined, efficient, and scalable software-based virtual switching architecture, specifically for hypervisors that support driver domains. The Hyper-Switch combines the best of the existing architectures by hosting the device drivers in a driver domain to isolate any faults and placing the virtual switch in the hypervisor to perform efficient packet switching. Further, the Hyper-Switch implements several optimizations—such as virtual machine state-aware batching, preemptive copying, and dynamic offloading of packet processing to idle CPU cores—to enable efficient packet processing, better utilization of the available CPU resources, and higher concurrency. This architecture eliminates the memory sharing overheads associated with driver domains. Third, this thesis proposes an alternate virtual switching architecture, called *sNICh*, which explores the idea of server/switch integration. The sNICh is a combined network interface card (NIC) and datacenter switching accelerator. This takes the Hyper-Switch architecture one step further. It offloads the data plane of the switch to the network device, eliminating driver domains entirely.

## Acknowledgments

Over the course of my PhD, several people have played a direct or indirect role in helping me cross the finish line. I have no doubt in my mind that without them, I would not have been successful in this endeavor. Unfortunately, it is not possible to name every one of them here, for there were too many. However, I would like to take this opportunity to thank a few among them.

First and foremost, I thank my advisor, Prof. Alan Cox, for his support, guidance, motivation, and inspiration during my stay at Rice University. His insights, suggestions, and feedback have shaped this thesis in many ways. I am grateful for the opportunity to work with Alan. I thank Prof. Scott Rixner for co-advising and helping me with all my research and publications. It was never easy facing Scott during the practise talks, proposals, or defenses! Nevertheless, it was a great learning experience. I thank Prof. Peter Varman for being a part of the thesis committee and for providing feedback on the thesis.

I also had the opportunity to collaborate with several researchers from HP Labs including Jose Renato Santos, Yoshio Turner, Jayaram Mudigonda, and Partha Ranganathan—over many projects. I learned a lot from all of them. I also gained valuable experience when I worked with them as an intern at HP Labs.

I am grateful to have been a part of the Rice Computer Systems group that included several outstanding students and faculty members. Specifically, I thank Brent Stephens, Jeff Shafer, Mike Foss, and Thomas Barr for their help, advise, and feedback on many occasions. I thank everyone in the Rice Computer Science department for making it an amazing place to study and work.

I had the pleasure of being surrounded by wonderful friends who were with me

during the good times and helped me through some of the difficult times at Rice. I cannot thank them all enough.

Finally, I sincerely thank my parents for always being there for me, for supporting me, and for trusting me do to the right thing. I thank my sister for her love and support. I am excited for the new beginnings in my life, both personally and professionally.

# Contents

|   | Abs                   | tract   |                                      | ii   |  |

|---|-----------------------|---------|--------------------------------------|------|--|

|   | Acknowledgments       |         |                                      |      |  |

|   | List of Illustrations |         |                                      |      |  |

|   | List                  | of Tabl | es                                   | xiii |  |

| 1 | Int                   | roduc   | etion                                | 1    |  |

|   | 1.1                   | Contri  | butions                              | 5    |  |

|   | 1.2                   | Organ   | ization                              | 8    |  |

| 2 | Ba                    | ckgro   | und                                  | 9    |  |

|   | 2.1                   | Datace  | enter Networking Challenges          | 9    |  |

|   | 2.2                   | I/O V   | irtualization Architectures          | 12   |  |

|   |                       | 2.2.1   | Driver Domain I/O Model              | 13   |  |

|   |                       | 2.2.2   | Hypervisor-based I/O Model           | 15   |  |

|   |                       | 2.2.3   | Direct I/O Model                     | 16   |  |

|   | 2.3                   | Last H  | Iop Virtual Switching Architectures  | 17   |  |

|   |                       | 2.3.1   | Purely Software Approaches           | 18   |  |

|   |                       | 2.3.2   | Network Interface-based Approaches   | 19   |  |

|   |                       | 2.3.3   | External Switching Approaches        | 21   |  |

| 3 | Re                    | thinki  | ing Memory Sharing with I/O Devices  | 23   |  |

|   | 3.1                   | Introd  | uction and Motivation                | 23   |  |

|   | 3.2                   | Memo    | ry Sharing in Xen                    | 26   |  |

|   | 3.3                   | Memo    | ry Sharing with Pass-through Devices | 31   |  |

| 3.4 | The Design |                                    |    |

|-----|------------|------------------------------------|----|

|     | 3.4.1      | Initialization                     | 34 |

|     | 3.4.2      | Creating Shared Memory             | 35 |

|     | 3.4.3      | Revoking Shared Memory             | 36 |

| 3.5 | Reuse      | of Grants                          | 38 |

|     | 3.5.1      | Reuse Scheme                       | 39 |

|     | 3.5.2      | Tracking Grant Use                 | 40 |

| 3.6 | Evalu      | ation                              | 41 |

|     | 3.6.1      | Experimental Setup and Methodology | 41 |

|     | 3.6.2      | Experimental Results               | 44 |

| 3.7 | Concl      | usions                             | 54 |

# 4 Hyper-Switch - A Scalable Software Virtual Switching

| Arc | Architecture |                                      |    |  |  |

|-----|--------------|--------------------------------------|----|--|--|

| 4.1 | Introduction |                                      |    |  |  |

| 4.2 | Motiva       | ation                                | 59 |  |  |

| 4.3 | Hyper        | -Switch Design                       | 63 |  |  |

|     | 4.3.1        | Basic Design                         | 66 |  |  |

|     | 4.3.2        | Preemptive Packet Copying            | 70 |  |  |

|     | 4.3.3        | Batching Hypervisor Entries          | 70 |  |  |

|     | 4.3.4        | Offloading Packet Processing         | 75 |  |  |

|     | 4.3.5        | More Packet Processing Opportunities | 80 |  |  |

| 4.4 | Impler       | nentation Details                    | 81 |  |  |

|     | 4.4.1        | Open vSwitch Overview                | 81 |  |  |

|     | 4.4.2        | Porting Open vSwitch's Datapath      | 84 |  |  |

|     | 4.4.3        | Para-virtualized Network Interface   | 85 |  |  |

|     | 4.4.4        | Hypervisor Integration               | 85 |  |  |

|     | 4.4.5        | Offloading Packet Processing         | 86 |  |  |

|          | 4.5 | Evalua  | tion                                                                    | 87  |

|----------|-----|---------|-------------------------------------------------------------------------|-----|

|          |     | 4.5.1   | Experimental Setup and Methodology                                      | 88  |

|          |     | 4.5.2   | Experimental Results                                                    | 94  |

|          | 4.6 | Discus  | sion and Future Work                                                    | 118 |

|          |     | 4.6.1   | Offloading Packet Copies to DMA Engines                                 | 118 |

|          |     | 4.6.2   | Zero-copy Transmission for External Traffic                             | 119 |

|          |     | 4.6.3   | Handling Congestion                                                     | 120 |

|          |     | 4.6.4   | Reducing the Impact on Scheduling Latency                               | 121 |

|          | 4.7 | Conclu  | nsions                                                                  | 123 |

| <b>5</b> | sNI | Ch:     | Leveraging Switch-Server Integration                                    | 125 |

|          | 5.1 | Introd  | uction and Motivation                                                   | 125 |

|          | 5.2 | sNICh   | Architecture                                                            | 127 |

|          |     | 5.2.1   | Separation of Control and Data Planes                                   | 129 |

|          |     | 5.2.2   | Flow-based Packet Switching                                             | 131 |

|          |     | 5.2.3   | Offloading Packet Copies to Host-Side DMA Engines $\ . \ . \ .$         | 133 |

|          | 5.3 | sNICh   | Prototype                                                               | 136 |

|          | 5.4 | Evalua  | tion                                                                    | 140 |

|          |     | 5.4.1   | Experimental Setup and Methodology                                      | 141 |

|          |     | 5.4.2   | Experimental Results                                                    | 142 |

|          | 5.5 | Conclu  | nsions                                                                  | 147 |

| 6        | Rel | ated    | Work                                                                    | 148 |

|          | 6.1 | Reduc   | ing Software I/O Virtualization Overheads $\ldots \ldots \ldots \ldots$ | 149 |

|          | 6.2 | Direct  | Device Access Proposals                                                 | 151 |

|          | 6.3 | Memor   | ry Sharing During I/O                                                   | 153 |

|          | 6.4 | Last H  | lop Virtual Switching                                                   | 156 |

|          | 6.5 | Distrib | outing Network Packet Processing                                        | 158 |

|          | 6.6 | Flow-b  | based Packet Switching                                                  | 162 |

|   | 6.7 Miscellaneous     | 163 |

|---|-----------------------|-----|

| 7 | Conclusions 1         | 65  |

|   | 7.1 Future Directions | 168 |

|   | Bibliography 1        | 71  |

ix

# Illustrations

| 2.1  | Driver Domain I/O Model                                                                   | 13 |

|------|-------------------------------------------------------------------------------------------|----|

| 2.2  | Hypervisor-based I/O Model                                                                | 14 |

| 2.3  | Direct I/O Model                                                                          | 15 |

| 2.4  | Purely Software Approaches for Last Hop Virtual Switching                                 | 17 |

| 2.5  | Network Interface-based Approaches for Last Hop Virtual Switching .                       | 19 |

| 2.6  | External Switching Approaches for Last Hop Virtual Switching $% \mathcal{S}_{\mathrm{S}}$ | 20 |

| 3.1  | Memory Sharing in Driver Domain I/O Model                                                 | 25 |

| 3.2  | Memory Sharing Interface using Grant Mechanism in Xen                                     | 27 |

| 3.3  | Memory Sharing Interface when using Pass-through Devices                                  | 28 |

| 3.4  | New Unified Memory Sharing Interface                                                      | 33 |

| 3.5  | Grant Address Space                                                                       | 34 |

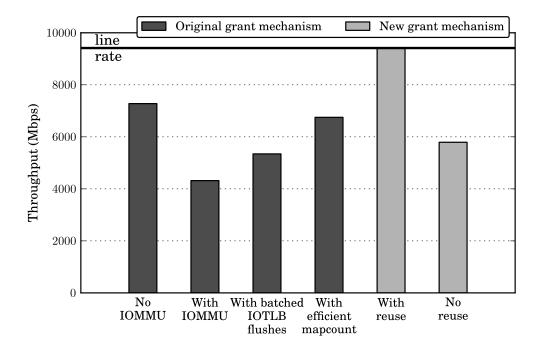

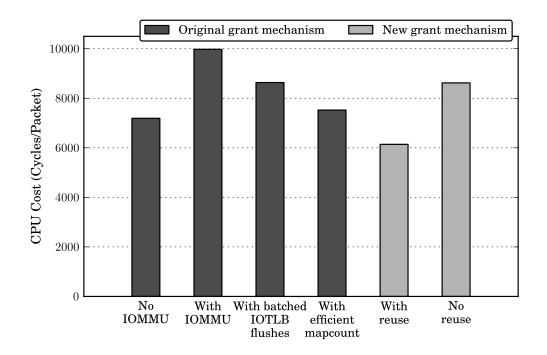

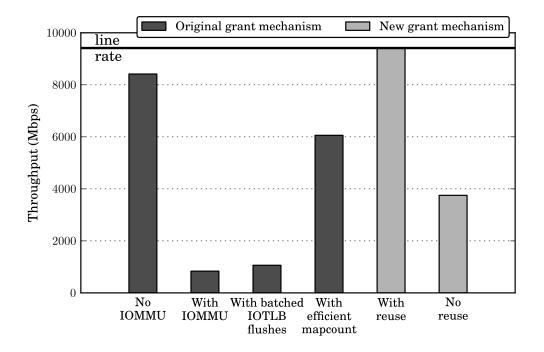

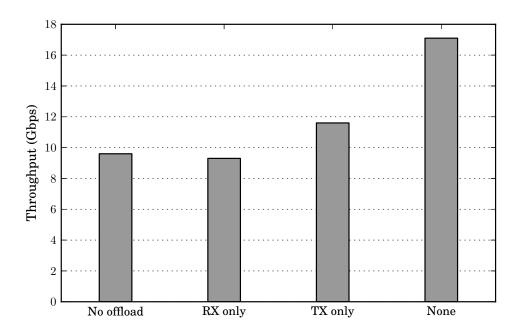

| 3.6  | RX Experiments - Throughput Results                                                       | 45 |

| 3.7  | RX Experiments - CPU Cost Results                                                         | 45 |

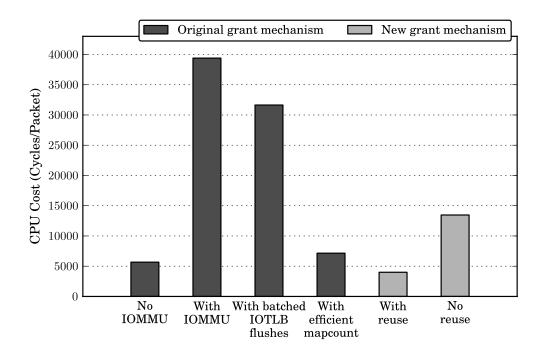

| 3.8  | TX Experiments - Throughput Results                                                       | 46 |

| 3.9  | TX Experiments - CPU Cost Results                                                         | 46 |

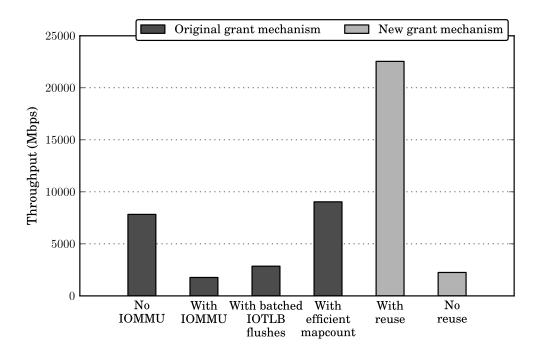

| 3.10 | Inter-VM Experiments - Throughput Results                                                 | 47 |

| 3.11 | Inter-VM Experiments - CPU Cost Results                                                   | 47 |

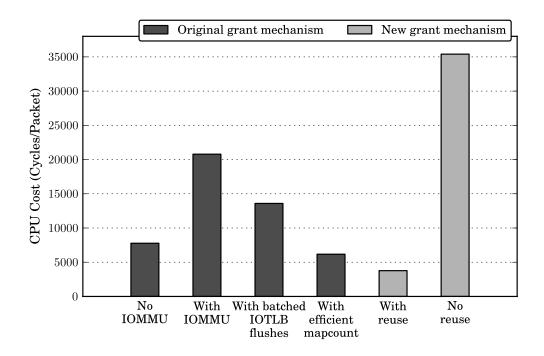

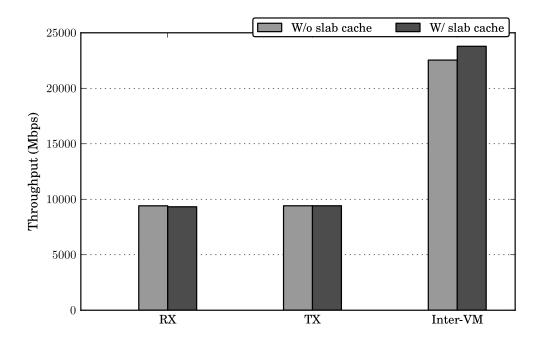

| 3.12 | Effect of Slab Cache - Throughput Results                                                 | 52 |

| 3.13 | Effect of Slab Cache - CPU Cost Results                                                   | 52 |

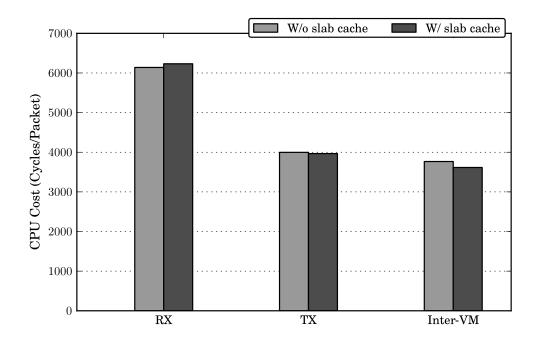

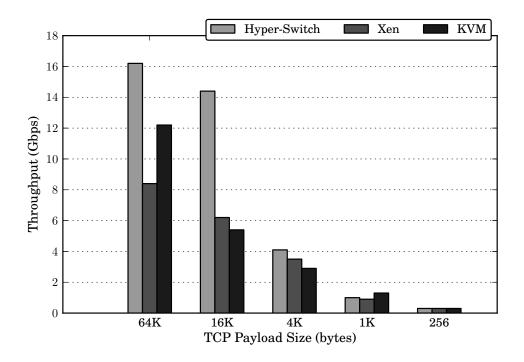

| 4.1  | KVM vs Xen: Network Performance                                                           | 59 |

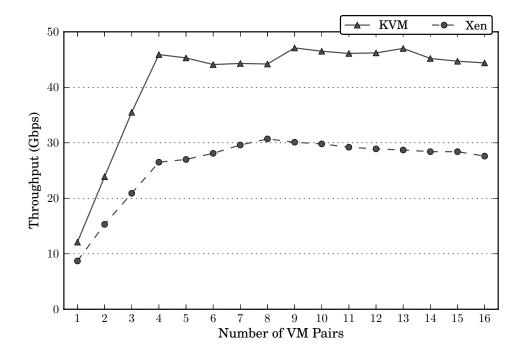

| 4.2  | The Hyper-Switch Architecture                                       | 64  |

|------|---------------------------------------------------------------------|-----|

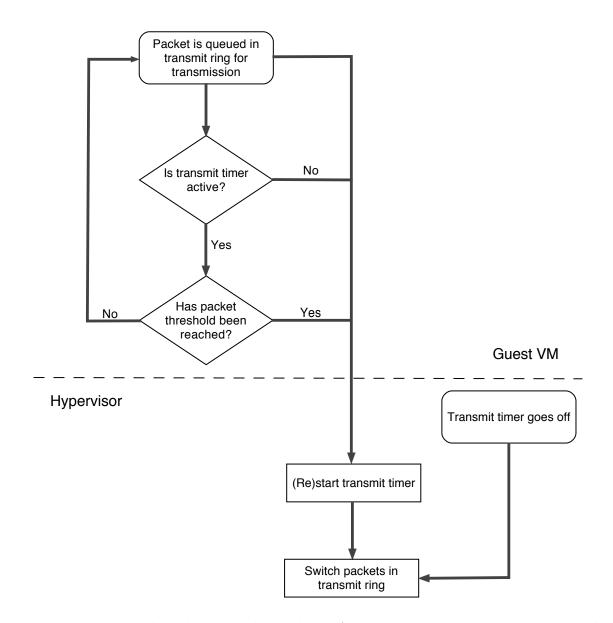

| 4.3  | Flow Chart Depicting the Working of Transmit Timers                 | 71  |

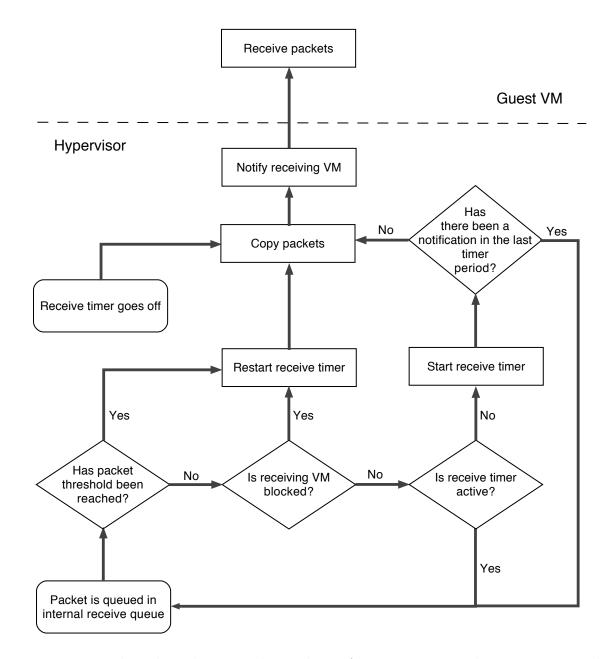

| 4.4  | Flow Chart Depicting the Working of Receive Timers                  | 72  |

| 4.5  | Flow Chart Depicting the Packet Processing on Idle Cores            | 76  |

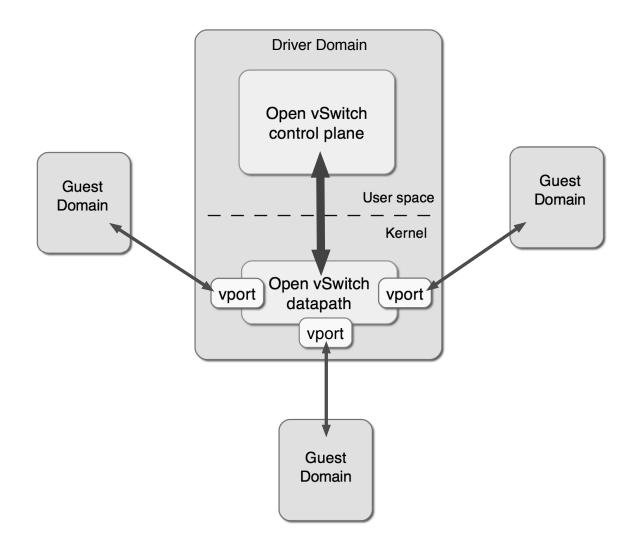

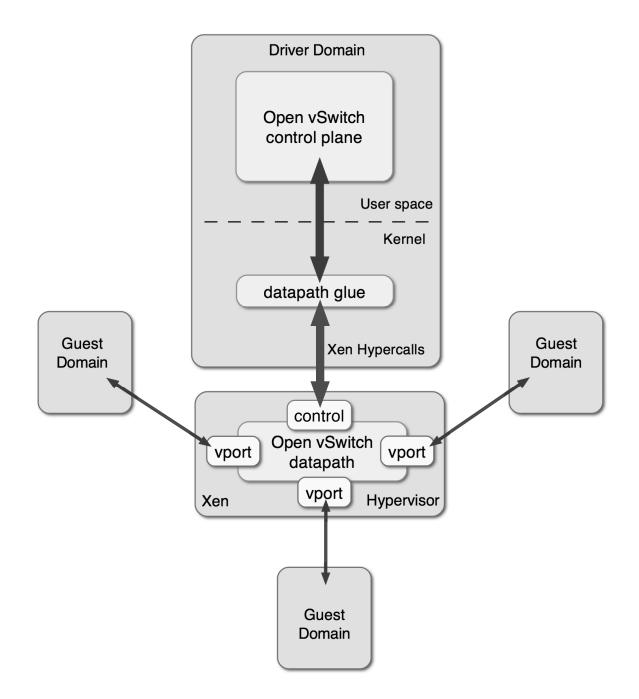

| 4.6  | Open vSwitch as a Last Hop Virtual Switch                           | 82  |

| 4.7  | Hyper-Switch Prototype                                              | 83  |

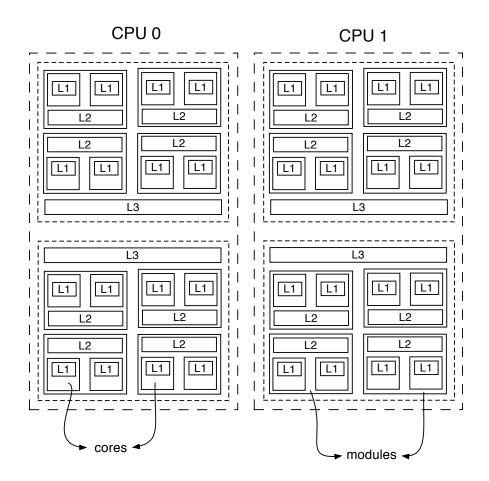

| 4.8  | Hyper-Switch Evaluation - Server CPU Cache Hierarchy                | 90  |

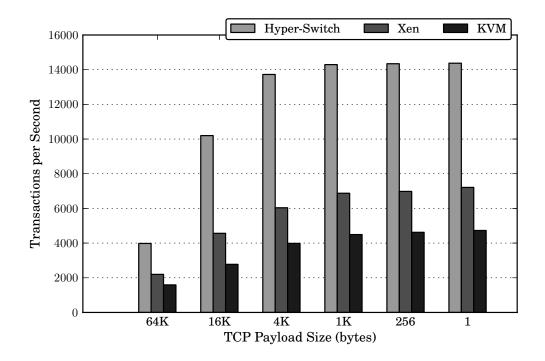

| 4.9  | Hyper-Switch Inter-VM Throughput Performance (Single Pair)          | 95  |

| 4.10 | Hyper-Switch Inter-VM Latency Performance (Single Pair)             | 95  |

| 4.11 | Hyper-Switch Pairwise Performance Scalability Evaluation -          |     |

|      | Throughput                                                          | 102 |

| 4.12 | Hyper-Switch Pairwise Performance Scalability Evaluation -          |     |

|      | Processor Stalls During Reads and Writes                            | 102 |

| 4.13 | Hyper-Switch All-to-All Performance Scalability Evaluation -        |     |

|      | Throughput                                                          | 106 |

| 4.14 | Hyper-Switch All-to-All Performance Scalability Evaluation -        |     |

|      | Processor Stalls During Reads and Writes                            | 106 |

| 4.15 | Effect of Pinning under Hyper-Switch - Pairwise Experiments         | 108 |

| 4.16 | Effect of Pinning Under Hyper-Switch - All-to-All Experiments       | 108 |

| 4.17 | Hyper-Switch External Throughput Performance Evaluation             | 111 |

| 4.18 | Hyper-Switch Offload Evaluation I                                   | 114 |

| 4.19 | Hyper-Switch Offload Evaluation II                                  | 114 |

| 4.20 | Hyper-Switch Offload Evaluation III                                 | 116 |

|      |                                                                     |     |

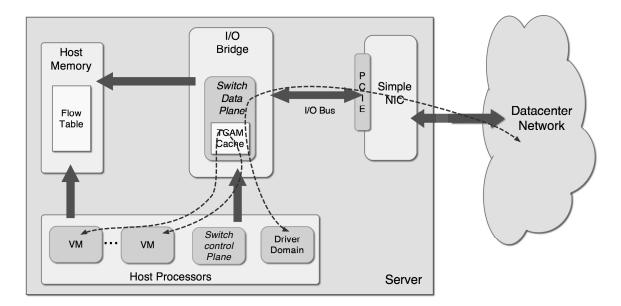

| 5.1  | sNICh's High-Level Architecture                                     | 128 |

| 5.2  | Steps Involved in Switching a Packet Through sNICh                  | 139 |

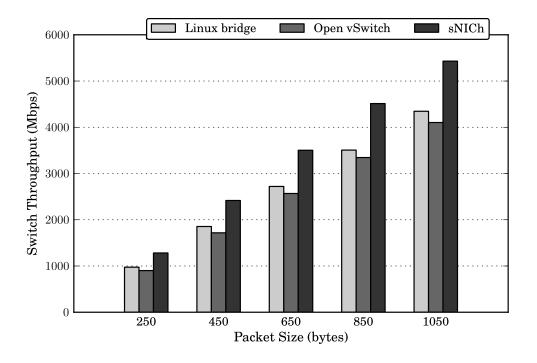

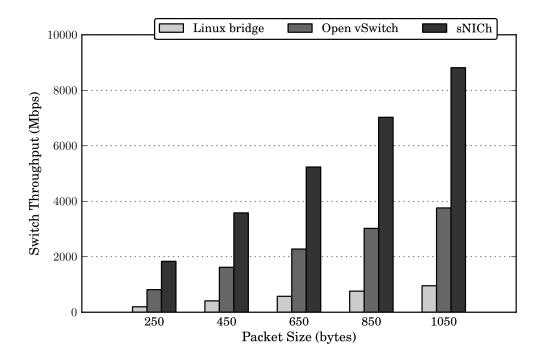

| 5.3  | Packet Throughput at Switch (without Packet Filtering)              | 143 |

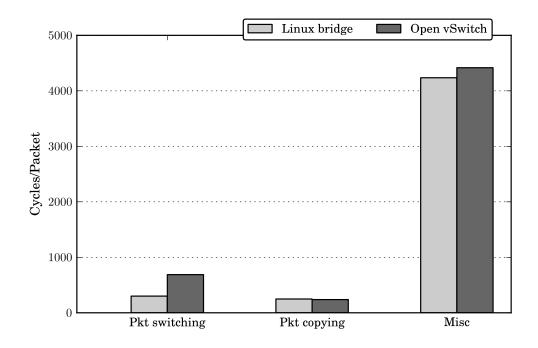

| 5.4  | Packet Processing Cost in Driver Domain (without Packet Filtering). | 143 |

xi

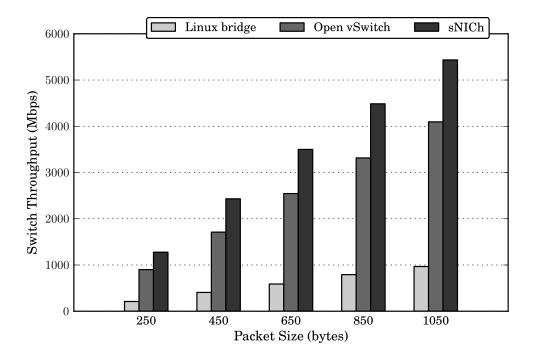

| 5.5 | Packet Throughput at Switch (with Packet Filtering) $\ldots \ldots \ldots$ | 145 |

|-----|----------------------------------------------------------------------------|-----|

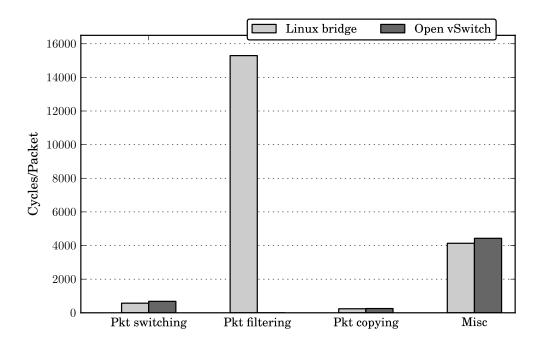

| 5.6 | Packet Processing Cost in Driver Domain (with Packet Filtering) $~$ .      | 145 |

| 5.7 | Packet Throughput at Switch with 2 TX Guest VMs (with Packet               |     |

|     | Filtering)                                                                 | 146 |

|     |                                                                            |     |

7.1 Future: Dedicated Switching Hardware on Server Platforms . . . . 168

# Tables

| 3.1 | New Memory Sharing Mechanism Evaluation - Server Configuration . | 42  |

|-----|------------------------------------------------------------------|-----|

| 3.2 | New Memory Sharing Mechanism Evaluation - External Server        |     |

|     | Configuration                                                    | 43  |

|     |                                                                  |     |

| 4.1 | Hyper-Switch Prototype Parameters                                | 87  |

| 4.2 | Hyper-Switch Evaluation - Server Configuration                   | 89  |

| 4.3 | Hyper-Switch Evaluation - Client Configuration                   | 89  |

| 4.4 | Inter-VM Single Pair Experiments - Pinning Configuration         | 96  |

| 4.5 | Inter-VM Scalability Experiments - Pinning Configuration         | 98  |

| 4.6 | Hyper-Switch External Latency Performance Evaluation - Latency   | 110 |

|     |                                                                  |     |

## Chapter 1

## Introduction

Machine virtualization has become a cornerstone of modern datacenters. It enables server consolidation as a means to reduce costs and increase efficiencies [1]. The cloud-based service infrastructures, such as Amazon EC2 [2], Rackspace Cloud [3], Windows Azure [4], and numerous others, use machine virtualization as one of their fundamental building blocks. Further, it is also being used to support the utility computing model where users can "rent" time in a large-scale datacenter [2]. These benefits of machine virtualization are now widely recognized. Consequently, the number of virtual servers in production is increasing rapidly. Specifically, the research firm IDC announced in December 2010 that more than 23% of all servers and more than 70% of all workloads on new machines will be virtualized [5].

Machine virtualization has led to considerable changes to the datacenter network and the I/O subsystem within virtualized servers. In particular, the communication endpoints within the datacenter are now virtual machines (VMs), not physical servers. Consequently, the datacenter network now *extends into the server* and *last hop switching* occurs within the physical server. Further, the server's I/O subsystem has to virtualize the devices to safely share them among the VMs hosted on the server. This thesis focuses on architectures and mechanisms for the network subsystem in virtualized servers to support efficient network communication.

The machine virtualization technology has come a long way since it was first used in IBM mainframes in the 1970s. Today, thanks to advances in both software and hardware, processor and memory virtualization have been heavily optimized to provide excellent performance. Unfortunately, the virtualization of devices, especially network devices, has lagged behind. Further, until recently, there has not been a lot of interest in the industry to explore new I/O virtualization architectures. This was primarily because the existing solutions, despite their drawbacks, were deemed good enough for most machine virtualization deployments. But, today, this situation is changing, primarily due to the ever increasing processor core counts on servers and the resulting increase in server VM densities.

In modern datacenters, the amount of inter-server communication is already significant and is expected to rise further [6, 7]. As virtualization spreads throughout the datacenter, and as more and more VMs are hosted within a server, this trend is expected to translate into significant inter-VM communication. So the network I/O subsystem and the last hop virtual switch within the server need to be able to keep up to support efficient communication—both internal and external to the server. Otherwise, the network will be a performance bottleneck, and this will in turn significantly impact the server VM densities. Further, in a virtualized datacenter, a physical server is likely to be shared by several applications, across multiple customers. So the mechanisms that aid in isolating network traffic must now operate all the way to the VMs through the last hop switch.

The existing support for I/O device virtualization comes in many forms. While these solutions have improved over the years, a single solution has not emerged as the best. Instead, all the solutions have their pros and cons. For instance, pure software approach to support I/O virtualization is commonly used in many virtualization platforms. This is due in part to the rich set of features—including security, isolation, and mobility—that software-based solutions offer. These solutions can be broadly classified into driver domain and hypervisor-based I/O models based on how the devices are virtualized in software.

The driver domain I/O model provides a safe execution environment for physical device drivers by hosting them in a dedicated VM<sup>1</sup> (a driver domain). This I/O model is supported by hypervisors like Xen [8] and Hyper-V [9]. Alternatively, hypervisors like VMware's ESX server [10] and Linux KVM [11], locate their device drivers within the hypervisor. This inflates the size of the trusted computing base (TCB) and therefore, reduces the reliability of the system.

While the driver domain model offers several benefits, it also incurs significant CPU overheads. One of the major sources of overhead is the mechanism that is used to share memory between VMs. The memory sharing mechanism is needed to allow the driver domain to access the network packets in a guest VM's memory, to perform I/O on its behalf. For instance, in Xen, the memory sharing overheads account for nearly 60% of the CPU cycles consumed in the driver domain while processing network packets. The hypervisor-based model avoids these overheads since the hypervisor has direct access to all guest VMs' memory. So, currently, depending on which software I/O model is chosen, one can achieve either higher fault isolation and system reliability or higher performance but not both.

Yet another point in this design space is the direct I/O model that has been proposed as a way to eliminate most the software overheads associated with I/O virtualization and thus, to close the gap with native I/O performance [12–16]. However, direct I/O solutions sacrifice device transparency since they require device-specific code within the guest VM. Also, it also does not offer the same flexibility as softwarebased solutions to support features like VM migration. Despite these drawbacks,

<sup>&</sup>lt;sup>1</sup>The terms domains and virtual machines are used interchangeably in this thesis.

direct I/O solutions are used in some virtualization platforms for their high performance.

There have also been several proposals for implementing the last hop virtual switch in virtualized servers. Typically, the virtual switch is implemented in software within the hypervisor or the driver domain [17, 18]. In fact, Cisco and VMware have also made this last hop switch look and behave similarly to other switches in the datacenter [19]. However, there are significant software overheads inherent in this approach that make it an inefficient solution. The primary problems involve the more advanced features of a datacenter switch, including packet processing—e.g., access control list (ACL) matching—and security operations—e.g., DHCP and ARP.

There have been efforts, primarily from industry, in developing alternate solutions that leverage the functionalities in existing switches. The fundamental idea entails routing all traffic, even traffic among VMs co-located on the same physical server, to an external switch [20,21]. So the external switch also performs all the last hop switch-related packet processing. While this solution eliminates most of the software overheads, it inherently wastes network link bandwidth between the server and the external switch. A middle ground in the design space is to switch packets within the server's network interface cards (NICs). The NICs that implement the direct I/O model, also implement a last hop switch. However, they only implement rudimentary switching functionalities due to their limited packet processing capabilities.

This thesis presents a spectrum of I/O virtualization solutions for the network subsystem in virtualized servers to build efficient virtualization platforms. Specifically, it proposes architectures and mechanisms that overcome the drawbacks in the existing I/O device virtualization and last hop switching solutions. The proposed solutions span both hardware and software, and illustrate the various bottlenecks and trade-offs inherent in I/O virtualization. The first two contributions of the thesis show that it is feasible to achieve high performance without sacrificing system reliability or fault isolation when using pure software solutions. The third contribution of this thesis shows that it is feasible to implement a NIC-based solution that supports all datacenter switching functionalities. Finally, this thesis concludes with a vision for the future of networking in virtualized systems that is based on the contributions presented in this thesis.

### 1.1 Contributions

#### A New Memory Sharing Mechanism

First, this thesis presents a new memory sharing mechanism that is designed specifically for driver domain-based I/O architectures. The new mechanism significantly reduces the overheads incurred when memory is shared between the driver domain and the guest VMs during I/O operations. The key idea is to enable a guest operating system to reuse the shared I/O buffers across multiple I/O operations. This is achieved by taking advantage of temporal and/or spatial locality in a guest VM's use of I/O buffers. The new mechanism makes it simple for a guest OS to implement a reuse scheme. Specifically, it allows the guest OS to unilaterally revoke access to the shared I/O buffers at any time. Another benefit of the new mechanism is that it provides a unified interface for memory sharing, whether between guest VMs and driver domains, or between guest VMs and I/O devices using the IOMMU hardware. The new mechanism was evaluated in the Xen virtualized platform using Linux VMs, where it reduced the CPU cost during I/O operations by up to 45% and increased the throughput by up to 150%.

#### The Hyper-Switch Architecture

Second, this thesis introduces *Hyper-Switch*, a highly streamlined, efficient, and scalable software-based last hop virtual switching architecture, specifically for hypervisors that support driver domains. While the first contribution reduces the memory sharing overheads, the Hyper-Switch architecture eliminates them entirely. Traditionally, in virtualization platforms that use driver domains, the last hop switch is implemented inside the driver domain along with the device drivers. Instead, the key idea in proposed architecture is to move the virtual switch from the driver domain to the hypervisor. In particular, the hypervisor implements a fast, efficient data plane of a flow-based software switch while the driver domain continues to safely host just the device drivers.

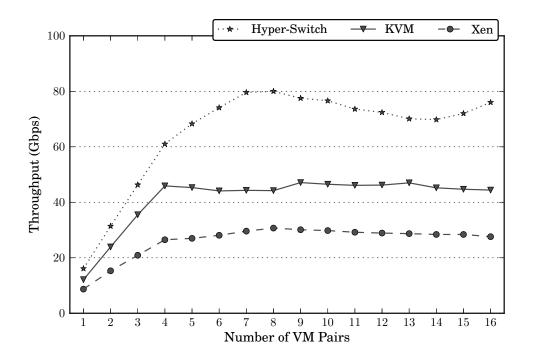

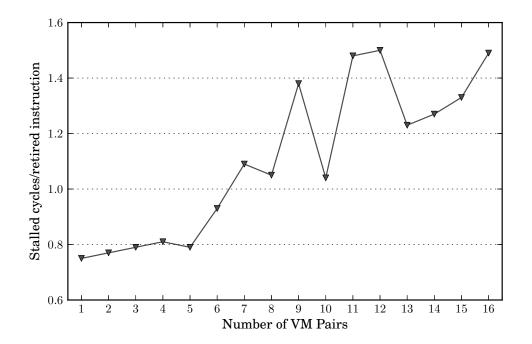

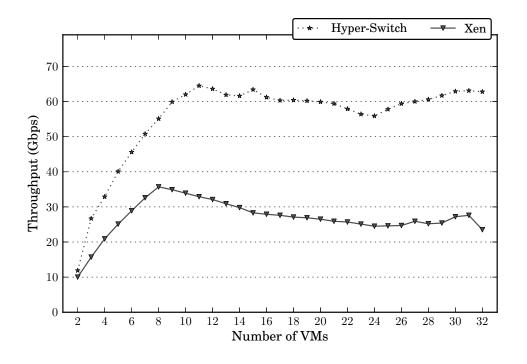

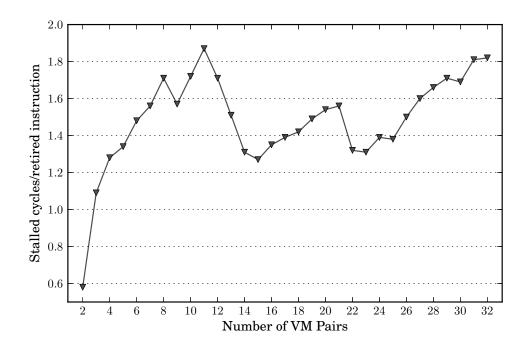

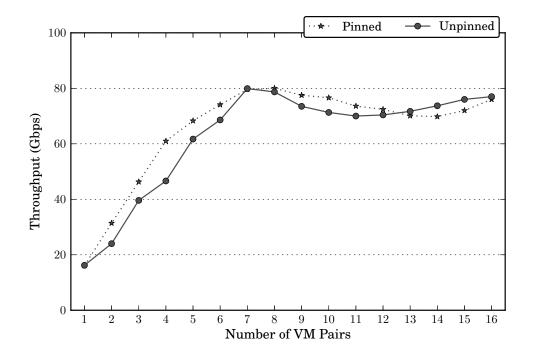

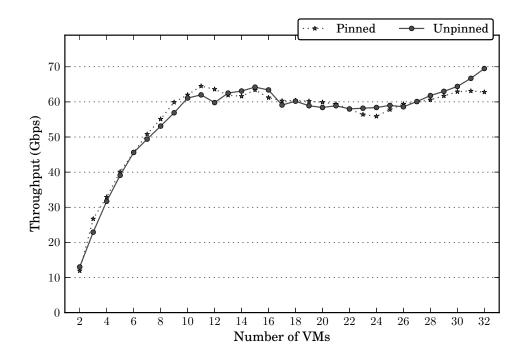

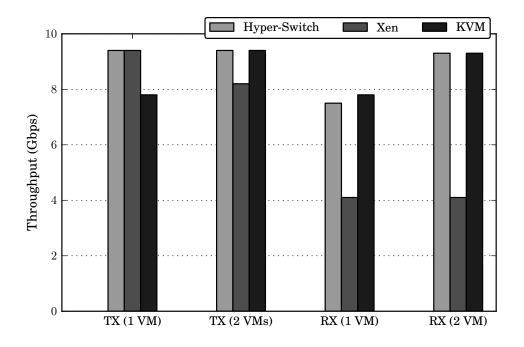

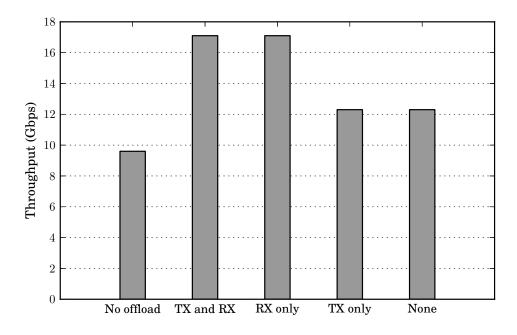

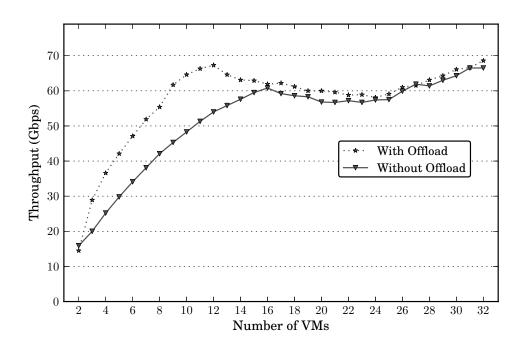

Further, this thesis also presents several optimizations that enable high performance. This includes virtual machine state-aware batching of packets to mitigate the cost of hypervisor entries and guest notifications. Preemptive copying and immediate notification of blocked guest VMs to reduce packet processing latency. Further, whenever possible, the network packet processing is dynamically offloaded to idle CPU cores in the system. These optimizations enable efficient packet processing, better utilization of the available CPU resources, and higher concurrency. As a result, the proposed architecture enables much improved and scalable inter-VM network performance, while still maintaining the fault isolation property of driver domains. A Hyper-Switch prototype was implemented in the Xen virtualization platform. The Hyper-Switch architecture was evaluated using this prototype where it outperformed Xen's default network I/O architecture and KVM's vhost-net architecture. For instance, in the pairwise scalability experiments the Hyper-Switch achieved a peak net throughput of ~81 Gbps as compared to only ~31 Gbps and ~47 Gbps under Xen and KVM respectively.

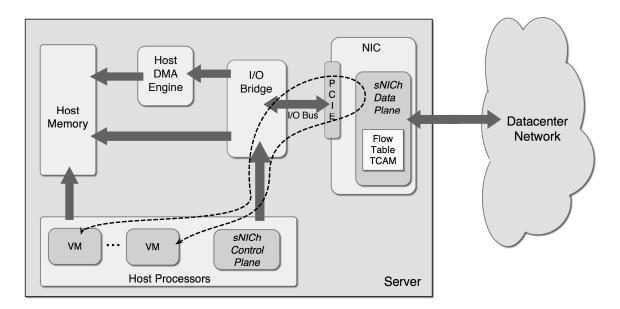

#### The sNICh Architecture

Third, this thesis proposes an alternate last hop switching architecture called *sNICh*, which explores the idea of server/switch integration. In this architecture, the proposal in the second contribution is taken one step further by offloading the data plane of the switch to the network device and thereby, eliminating the need for driver domains entirely. As the name implies, the sNICh is a combined NIC and datacenter switching accelerator. But using a hardware-only approach it is not feasible to incorporate advanced switching functionalities in a NIC without making it expensive and/or limiting its scalability. The sNICh solution overcomes these limitations to implement a full-fledged switch while enabling a low cost NIC solution, by exploiting its tight integration with the server internals. This makes sNICh more valuable than simply a combination of a network interface and a datacenter switch.

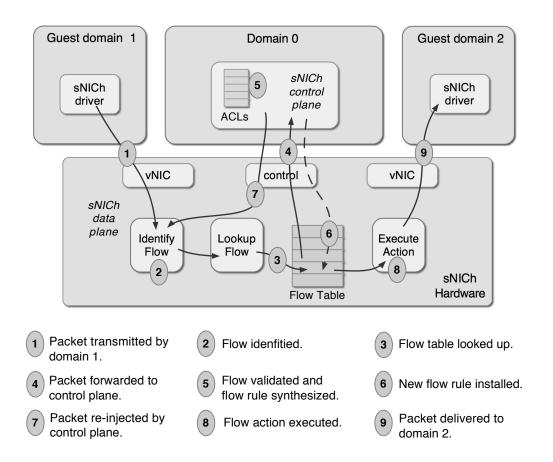

The sNICh architecture diverges from a conventional switch-on-the-NIC architecture in three ways. First, it separates the control and data planes in the last-hop switch. Whereas the data plane is implemented in hardware within the NIC, the control plane is implemented in host software. Second, it supports flow-based packet switching to ensure that the software path is not traversed on every packet. Finally, it takes advantage of DMA engines on the host-side of the I/O bus to avoid wasting I/O bus bandwidth. The sNICh architecture was evaluated using a software prototype where the sNICh hardware was emulated in software. The sNICh prototype outperformed and scaled better than the existing solutions.

### 1.2 Organization

This thesis is organized as follows:

- Chapter 2 provides background information on the current state-of-the-art solutions for networking in virtualized datacenters. It presents existing solutions for virtualizing I/O devices and for last hop switching in virtualized servers.

- Chapter 3 describes the first contribution of this thesis. It presents the existing memory sharing mechanism, its drawbacks, and finally, the new mechanism. It also provides a comprehensive evaluation of the new mechanism.

- Chapter 4 describes the Hyper-Switch architecture, the second contribution of this thesis. It presents a detailed description of the new architecture, some details of its prototype implementation, and a complete evaluation of the proposed architecture.

- Chapter 5 introduces the sNICh, the third contribution of this thesis. It explains the sNICh architecture in detail. It also provides an evaluation of this architecture using software emulation.

- Chapter 6 discusses prior research that closely relate to the contributions of this thesis.

- Finally, Chapter 7 offers concluding remarks and directions for future research.

# Chapter 2

## Background

This chapter provides background information on the current state-of-the-art solutions for networking in virtualized datacenters. It is organized as follows. Section 2.1 explains the challenges due to the increasing adoption of virtualization in datacenters. Section 2.2 presents the current solutions for safely virtualizing and sharing I/O devices. Finally, Section 2.3 describes the existing solutions for last hop switching in virtualized servers.

### 2.1 Datacenter Networking Challenges

The datacenter is becoming one of the most critical components of the modern computing infrastructure. This trend has manifested in several ways. Primarily, data intensive applications, such as Google's search engine, can only operate in large scale datacenters. However, even smaller applications—workplace applications, such as document editors and spreadsheets, are migrating to the datacenter as a part of the *cloud* environment. Further, the *utility computing* model is emerging, whereby it is cost efficient to "rent" time in a large scale datacenter, enabling clients to quickly scale up or down the amount of computing resources at their disposal.

To efficiently serve this ever increasing number and diversity of applications and customers, datacenters must address two inefficiencies: server sprawl and multiple poorly utilized networks. Historically, physical servers were rarely shared across multiple clients, and in many cases not even across application instances of the same client, so that the necessary performance SLAs and the inter-customer isolation can be achieved. Typically, these servers are under-utilized and wasteful of power [22].

Most datacenters also contain several parallel networks: a traditional Ethernet, a Fibre Channel network for storage traffic, and an InfiniBand fabric to support cluster traffic. These parallel networks are not cost-effective for several reasons; they cost more to build, require multiple administrators, complicate cabling, and waste rack space and energy.

Virtualization offers a promising avenue towards reducing server sprawl, particularly when combined with many-core processors. Modern virtualization systems allow several servers to be effectively consolidated onto a single physical machine. Similarly, advances in Ethernet networking offer a promising avenue towards increasing network utilization in the datacenter. The rapid rise of Ethernet network link bandwidths combined with the advent of sophisticated switch-based mechanisms—such as VLANs, ACLs, and link schedulers— for safely multiplexing different clients and traffic types can facilitate fabric consolidation.

The networking subsystems of virtualized servers, however, present a major impediment for both server and fabric consolidation. Datacenter networks and the server I/O subsystems are both architected in a way that expects the physical server to be an *end-point* in the network, and do not efficiently support a virtualized server, which is in reality a *network* in itself of virtual machines (VMs). Lack of efficient support for switching and for mechanisms that aid in ensuring isolation (such as ACLs, VLANs and QoS) causes the following three major problems in datacenter networks:

1. Lack of efficient switching support within the server can affect server densities in

the near-future for two reasons. First, in most modern datacenters, inter-server communication is already significant, and is expected to increase further [6,7]. For instance, in Amazon's EC2 utility datacenter, a request from an external client machine can make as many as 100 different servers exchange messages among them [23]. Second, the increasing core counts on processor chips can easily be utilized by co-locating the servers of such applications on the same physical machine. However, this will not be possible if the networking subsystem cannot keep up to provide efficient inter-VM packet switching.

- 2. Lack of efficient access control within a server complicates fabric consolidation. The central problem in fabric consolidation is to isolate different clients and traffic types from hurting each other when forced to share a common switch or link. For instance, a buggy (or malicious) client should not be allowed to direct its storage traffic to another client's parallel program VMs, leading to serious packet loss in their synchronization traffic. To fully ensure such isolation, one must enforce the access restrictions (and QoS guarantees) on *all* hops of an end-to-end path. However, in virtualized servers, the real end-points are the VMs, and hence the end-to-end path extends through the server, involving the I/O subsystem in the last-hop. If the I/O subsystem does not extend the isolation and instead, allows traffic from different clients and different types to interact, it renders the isolation enforced in the greater datacenter network completely useless and makes fabric consolidation impossible.

- 3. Lack of consistent management primitives that work over the entire end-to-end path substantially complicates management. Today, most data center administration is spread over two main organizations within the IT department: the

server admin group and the network admin group. In traditional datacenters, for the most part, these groups are able to work independently of each other. In a virtualized datacenter, however, the roles of these admin groups get intertwined leading to much manual configuration and inter-group communication. For instance, the server admin that previously never had to deal with the details of the network must now configure the I/O subsystem to extend the isolation (and QoS) between different traffic types and clients. Further, to make this configuration effective the server admin must understand how the network itself is handling this separation (for instance which VLAN with which set of ACLs is being used in the network for one client vs another). This today requires close manual co-operation between the administrators. Even today's automated management systems are not designed to handle this blurred line between server and network administration.

The network subsystem in a virtualized server has two major components. The first component is the I/O virtualization architecture that is used to share the I/O devices among the VMs. The second component is the last hop virtual switching architecture used to switch network packets within the server. Both these components have to be taken into consideration to solve the datacenter networking problems. However, the management problem is not discussed in this thesis.

### 2.2 I/O Virtualization Architectures

The I/O virtualization architectures used in virtualized servers can be broadly classified into three models. While these models are discussed in the context of network devices, they are applicable to all I/O devices.

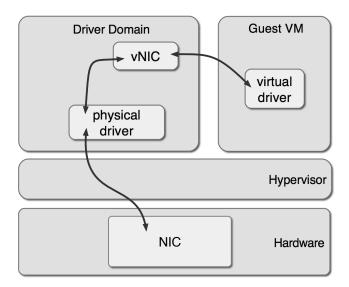

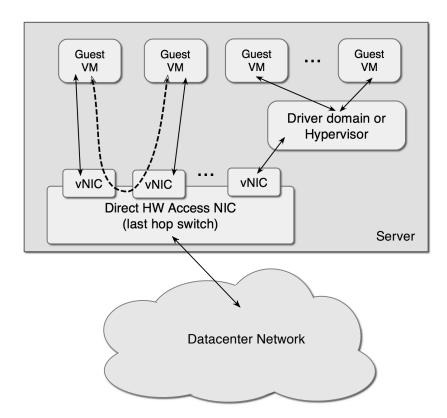

Figure 2.1 : Driver domain I/O model. The driver domain, a dedicated VM, implements the virtual devices and also hosts the physical device drivers.

#### 2.2.1 Driver Domain I/O Model

In this I/O model, each guest VM is provided a virtual network interface (vNIC), which is implemented completely in software within a dedicated VM called a *driver domain* (shown in Figure 2.1). The driver domain is given direct access to the hardware and performs I/O operations on behalf of the guest VMs. So the driver domain also hosts the physical device drivers needed to access the I/O devices. During network I/O, all packets traverse the driver domain to be either forwarded to the physical device or delivered to a destination domain. Xen [8,24], the L4 microkernel [25], and Microsoft Hyper-V [9] are examples of hypervisors that use this I/O model.

The primary benefit of this model is that the driver domains provide a safe execution environment for the device drivers, the biggest source of OS bugs [26]. This ensures that any bugs in the device drivers are contained within the driver domain

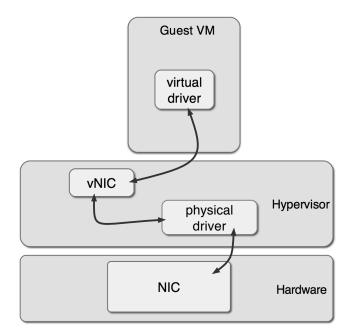

Figure 2.2 : Hypervisor-based I/O model. The hypervisor implements the virtual devices and also hosts the physical device drivers.

and cannot corrupt or crash the hypervisor and the other VMs running in the system. Although driver domain crashes can still affect the guest VMs due to interrupted I/O service, this is a more tolerable failure mode. It usually only lasts a short period of time since I/O service can be rapidly restored by simply rebooting a faulty driver domain.

Also, the driver domain runs a largely unmodified operating system. Consequently, it is able to use all of the device drivers that are available for that operating system. This greatly simplifies the complexity of providing support for a wide variety of devices in a virtualized environment. Further, it minimizes the cost to develop and maintain new device drivers.

While the driver domain model provides several desirable properties, it also incurs

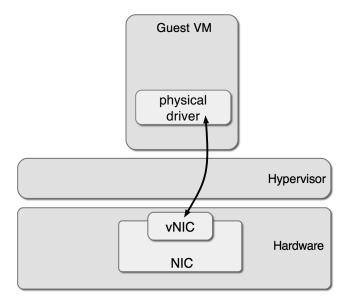

Figure 2.3 : Direct I/O model. The I/O device is logically partitioned into multiple virtual devices. The guest VM hosts the physical device drivers and has direct access to the device.

significant CPU overheads. One of the major sources of overhead is the mechanism that is used to share memory between VMs. The memory sharing mechanism is needed to allow the driver domain to access the guest I/O buffers. For example, Xen uses the *grant mechanism* to support the sharing of memory.

### 2.2.2 Hypervisor-based I/O Model

In this I/O model, the virtual devices are implemented, again in software, but within the hypervisor (shown in Figure 2.2). Further, the hypervisor also hosts the physical device drivers needed to access the I/O devices. VMware's ESX server [10] and Linux KVM [11] are examples of hypervisors that supports this I/O model.

The hypervisor has access to all guest VMs' memory. Therefore, this I/O model

does not incur any of the memory sharing overheads. Instead, it sacrifices fault isolation for better performance. Since the device drivers are hosted within the hypervisor, a device driver bug can potentially crash the entire system or corrupt the hypervisor itself. Moreover, this model also increases the size of the trusted computing base (TCB).

#### 2.2.3 Direct I/O Model

In this I/O model, the virtual devices are implemented in hardware by the I/O devices [12–16] (shown in Figure 2.3). In other words, the I/O devices are logically partitioned into multiple contexts which present virtual device interfaces to individual VMs. So the guest VMs can directly communicate with the I/O device bypassing any software intermediary. Hence these devices are also called *pass-through* devices. Today, there exists an industry-wide standard called *single root I/O virtualization* (*SR-IOV*), which has been adopted by several network interface vendors to implement this I/O model [27–30].

The primary benefit of this I/O model is that it eliminates most of the software overheads, and therefore, supports near-native performance. But, unlike the software I/O virtualization models, this model lacks support for fault isolation and device transparency. In particular, direct I/O requires device-specific code in the guest VM which has several negative consequences. It increases guest image complexity, reduces guest VM portability, and complicates live guest migration [31–33] between systems with different devices. Moreover, devices which support this I/O model only provide a limited number of virtual contexts. Therefore, scalability can also be an issue.

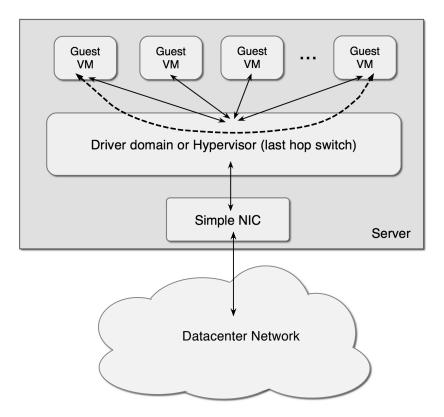

Figure 2.4 : Purely software approaches for last hop virtual switching. These architectures rely on software-either the hypervisor or a driver domain—to virtualize a simple standard NIC. As the dashed arrow shows, the packet switching happens entirely in the software intermediary.

### 2.3 Last Hop Virtual Switching Architectures

The current state-of-the-art last hop virtual switching solutions for datacenter servers can be classified into three main categories.

#### 2.3.1 Purely Software Approaches

The first category of systems (shown in Figure 2.4) implement the last hop virtual switch completely in software within the server. Typically, this solution is used in systems which include a simple NIC that is virtualized by a software intermediary, either using the hypervisor-based or the driver domain I/O model. The Linux bridge [18] and VMware's vSwitch [17] are examples of software switches used in such systems. Cisco and VMware have also made this last hop switch look and behave similarly to other switches in the datacenter [19]. Further, since these implementations are in software, they tend to have a rich set of packet processing functionalities such as ACL matching and link-scheduling.

However, the purely software approaches for last hop virtual switching cannot sustain high throughput for three reasons. First, the cost of supporting advanced switching functionalities like packet filtering using conventional approaches can be expensive in software. Second, regardless of how expensive the packet processing itself is, merely getting the packet to and from the software intermediary can be very resource intensive [34]. Third, parallelizing these software implementations to take advantage of multiple processor cores remains challenging; it has been shown that even a judicious mapping of multiple driver domain threads to cores can often result in a net throughput *loss* [35].

Recently, flow-based switching has been used to address the first of these three issues. The fundamental idea is that the packets are switched on a per-flow basis instead of the conventional per-packet switching. This can have a substantial impact on performance since many operations, such as packet filtering, can then be performed per-flow. As a result, the software overheads due to these operations can be significantly reduced. Open vSwitch [36] is an example of a software switch which

Figure 2.5 : Network interface-based approaches for last hop virtual switching. These architectures employ sophisticated NICs that allow a subset of the VMs to directly access the hardware and support rudimentary switching. As the dashed arrow shows, the packet switching happens entirely inside the NIC.

implements flow-based packet switching.

### 2.3.2 Network Interface-based Approaches

The second category of systems (shown in Figure 2.5) employ more sophisticated NICs which implement the direct I/O model. These NICs also implement switching internally, that is within the hardware. However, today most of them only implement a rudimentary form of a switch that does not support any advanced switching features.

Figure 2.6 : External switching approaches for last hop virtual switching. The servers blindly forward all packets to the external switch which then manages the traffic on a per-VM basis to ensure isolation and QoS guarantees.

While features like packet filtering using TCAMs are being added to some of these NICs [29], such solutions will neither be scalable nor cost-effective. Further, these NICs waste substantial I/O bandwidth while switching inter-VM packets because they always transfer the full packet payload twice over the I/O bus (to and from the NIC).

Another network interface-based approach for last hop switching involves multi-

queue NICs, such as Intel's 10 GbE VMDq NICs [34, 37]. Multi-queue NICs can be used to accelerate the purely software-based network I/O virtualization models. Unlike a direct I/O NIC, a multi-queue NIC does not allow direct access by guest VMs. Instead, it can be used by a driver domain or the hypervisor to allocate a unique hardware TX/RX queue to each guest VM. Then the NIC de-multiplexes the incoming packets and directly DMAs them to the destination VM. Essentially, the NIC implements a very simple switch, which suffers from the same disadvantages as with the direct I/O NICs.

#### 2.3.3 External Switching Approaches

The third approach tries to leverage the functionalities that already exist in today's datacenter switches. This approach uses an external switch for switching *all* packets including those belonging to inter-VM network traffic (as shown in Figure 2.6). In this architecture, a server agent and the external switch attach a special label to each packet that identifies the VM the packet belongs to. While the server agent uses this label to de-multiplex the packets into per-VM receive queues, the external switch uses it to enforce per-VM access controls and QoS. This also simplifies management, since *all* traffic from within the server now transits a traditional switch and hence can be managed by a network manager system. Today, there are two competing standards to implement this approach—Virtual Ethernet Port Aggregator (VEPA) [20] and VN Tagging [21].

Fundamentally, this approach results in a wastage of network bandwidth since even packets from inter-VM traffic always travel all the way to the external switch. Further, similar to the network interface-based approaches, this approach can also result in a wastage of I/O bus bandwidth. Today, there are not many systems of this kind available for experimentation, however, a server agent implemented in software is very likely to incur a good fraction of the CPU overhead of the software-based approaches discussed above (category 1). In particular, the packets have to still traverse either the hypervisor or a driver domain. However, a server agent implemented in hardware, *i.e.*, within direct I/O NICs, can potentially eliminate these overheads.

## Chapter 3

# Rethinking Memory Sharing with I/O Devices

### **3.1** Introduction and Motivation

In I/O virtualization architectures that use driver domains, memory sharing during I/O operations occurs in two levels, as shown in Figure 3.1. First, I/O buffers in guest domains' memory have to be safely shared with virtual I/O devices implemented in the driver domain. This allows the driver domain to perform I/O operations on behalf of the guest virtual machines (VMs). For example, during network I/O, the driver domain needs write access to the I/O buffers in a guest VM's memory so that it can copy the contents of packets arriving for that guest VM. Similarly, for packets that are transmitted by a guest VM, the driver domain needs read access to the guest I/O buffers so that it can parse the packet headers and determine where to route them. Second, the I/O buffers have to be safely shared with physical I/O devices. For example, during network I/O, the I/O device needs DMA write access to the I/O buffers so that it can copy the contents of incoming packets into them. Similarly, for packets that are transmitted, the I/O device needs DMA read access to the I/O buffers so that it can copy the contents of incoming packets from them.

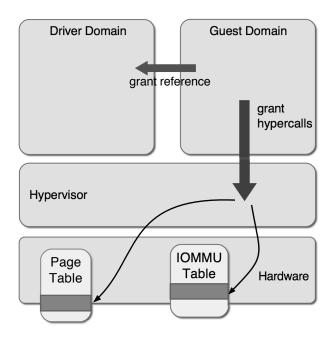

In the Xen virtualization platform, the first level of memory sharing between VMs is supported using the *grant mechanism* [8,24]. The grant mechanism allows a source domain to control which of its memory pages can be accessed by a specified destination domain. In addition, it allows the destination domain to validate that the

shared memory pages belong to the source domain. During I/O, the grant mechanism is used by the guest domain to *grant* the driver domain access to its I/O buffers.

The second level of memory sharing with I/O devices is supported using I/OMemory Management Units (IOMMUs) [38,39]. The IOMMUs are used to perform address translation and validation of all memory accesses from devices, through DMA, using IOMMU tables (I/O page tables). A DMA operation fails if a valid translation (mapping) does not exist in the IOMMU table or if a valid translation exists but the access permissions are not sufficient. Thus the IOMMUs can protect against incorrect or malicious memory accesses by the I/O devices. In Xen, the IOMMU mappings are setup and torn down during the grant operations from the driver domain [40].

Previous work [34,41] has shown that the grant mechanism incurs significant overhead when performing network I/O, and has also shown that most of this overhead is incurred in the driver domain. This is mostly due to the overheads of grant hypercalls and of the high cost of page mapping/unmapping operations executed in these hypercalls. For instance, in the experiments, the memory sharing overheads accounted for nearly 60% of the CPU cycles consumed in the driver domain while processing network packets and the driver domain CPU was a performance bottleneck in all the experiments. Consequently, this limited the rate at which a guest domain can transmit/receive packets since it was not able to utilize the processor to the maximum extent possible. Additionally, the setting up and tearing down of IOMMU mappings further increased this overhead.

A grant reuse scheme can greatly reduce the number of grant issue and revoke operations that are needed for I/O by taking advantage of temporal and/or spatial locality in a guest domain's utilization of I/O buffers. The guest domain can issue a grant for a page containing I/O buffers, then use the page several times for I/O, and

Figure 3.1 : Two level memory sharing in driver domain I/O model. First, I/O buffers are shared with the virtual device (vNIC). Second, they are shared with the physical device (NIC).

finally revoke access to that page. In contrast, in the existing implementation every I/O involves grant issue and revoke operations. So the grant reuse scheme reduces the number of grant hypercalls and page mapping/unmapping operations needed for I/O. Further, the IOMMU mappings can also be reused when the corresponding grants are reused.

To support the grant reuse scheme, a new mechanism is proposed that replaces the existing grant mechanism in Xen. Whereas the existing grant mechanism requires the guest domains to coordinate with the driver domain to revoke a grant, the key idea of the new mechanism is to enable the guest domains to *unilaterally* issue and revoke grants. By breaking this dependency, the new mechanism avoids the need for a handshake protocol between the guest and driver domains to revoke the grant to a page, as would be needed with the existing grant mechanism. More generally, using the new mechanism to control memory sharing between two arbitrary guest domains has the advantage that each guest domain can stop sharing its pages with its peer at any time. In particular, each guest domain can forcibly revoke its grants in case its peer misbehaves.

Additionally, the new mechanism provides a *unified interface* that can extend the control of memory sharing to I/O devices using the IOMMU hardware, for both pass-through device access (*i.e.*, direct I/O) [13,27] and when using an intermediary driver domain [8].

While this work only explores the use of the new mechanism for network I/O, we believe that it can completely replace the existing mechanism in Xen. The new mechanism is no less general than the existing mechanism in Xen, and the ability to unilaterally revoke grants provides greater robustness against non-cooperative peers. In general, the new mechanism is applicable to any driver domain-based I/O architecture.

The rest of this chapter is organized as follows. Section 3.2 describes how memory is shared between domains using the existing grant mechanism in Xen. Section 3.3 describes how memory is shared with pass-through devices. Section 3.4 describes the new mechanism and Section 3.5 presents the grant reuse scheme under the new mechanism. Finally, Section 3.6 presents an evaluation of the grant reuse scheme when performing network I/O operations.

## 3.2 Memory Sharing in Xen

The grant mechanism in Xen allows the driver domain to access the guest I/O buffers in a safe manner and the guest domain to limit the memory pages shared with

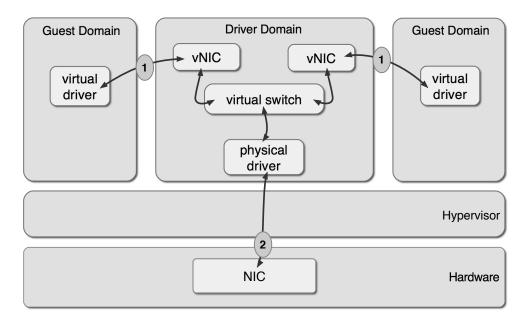

Figure 3.2 : Memory sharing interface using grant mechanism in Xen. Guest domains interact indirectly with the hypervisor through the grant table. The driver domain interacts directly with the hypervisor through grant hypercalls.

the driver domain to only those containing the buffers being used for I/O operations.

**Creating Shared Memory:** The existing memory sharing interface using the grant mechanism is illustrated in Figure 3.2. A guest domain shares one of its memory pages in two stages. In the first stage, the guest domain simply indicates the page it desires to share as follows:

- First, the guest domain allocates a *grant reference* for that memory page. The grant reference points to a unique entry in a *grant table*, which is shared between the guest domain and the hypervisor.

- The grant entry contains the shared memory page address, the driver domain id, and the access permissions (read-only or read-write). The guest domain fills

Figure 3.3 : Memory sharing interface when using pass-through devices. Guest domains interact directly with the hypervisor to manipulate the IOMMU table.

the grant table entry using simple memory writes.

The guest domain then passes the grant reference to the driver domain via Xen's inter-domain network I/O channel called *net-channel*. In the second stage, the driver domain uses the grant reference to access the shared memory. This stage requires hypervisor intervention. This involves the following steps:

- The driver domain issues a grant hypercall, to enter the hypervisor, passing the grant reference and a virtual address as arguments.

- The hypervisor first checks whether the grant reference is valid. It reads the guest domain's grant table entry and checks whether the domain that invoked the hypercall is the intended destination. It then obtains the machine address of the shared page and checks if that page is owned by the guest domain.

- If all the tests pass, the hypervisor then pins the memory page and maps the page within the driver domain's address space at the given virtual address. This requires adding a new entry (driver domain virtual address → guest domain machine address) to the driver domain's page table.

- Finally, the hypervisor adds an entry to the IOMMU table. This entry is an identity mapping (guest domain machine address → guest domain machine address).

- Now the driver domain and the I/O device can safely access the shared memory page.

Page pinning ensures that the page ownership does not change while a page is shared. Otherwise, memory corruption is possible. Consider the scenario where a guest domain gives up a shared page to the hypervisor, without the driver domain's knowledge. The hypervisor might then allocate this page to another guest domain. Now if the driver domain inadvertently copies an incoming packet into that page, it will end up corrupting the other guest domain's memory.

**Revoking Shared Memory:** A shared memory page is revoked, again, in two stages. In the first stage, the driver domain stops accessing the shared page as follows:

- The driver domain issues another grant hypercall, to enter the hypervisor, passing the grant reference as an argument.

- The hypervisor first removes the IOMMU mapping. It also performs the required IOTLB invalidation.

- Then it unmaps the page from the driver domain's address space and unpins the shared memory page. It also performs the required TLB invalidation.

Subsequently, in the second stage, the guest domain revokes the shared page as follows:

• It invalidates the corresponding grant table entry (again, through simple memory writes).

In the standard network I/O model in Xen, the guest domain creates grants for its receive/transmit I/O buffers to provide shared access to the driver domain. During packet transmission, the driver domain first issues the grant *map* hypercall. Once the I/O has completed, the driver domain issues the grant *unmap* hypercall. Then the driver domain notifies the guest domain that the I/O operations have completed. This also serves as a notification that the guest domain can revoke the grant for the corresponding page.

During packet reception, the incoming packets are copied into local driver domain buffers first. Once the destination of the packet is determined, the packets are copied into that guest domain's I/O buffers. So, unlike packet transmission, the guest I/O buffers are not shared all the way to the I/O device. Further, typically the I/O device is given access to all of driver domain's memory during initialization. So IOMMU mappings are not setup during packet reception. Once a packet is received, the driver domain performs a single grant *copy* hypercall. The hypervisor then validates the grant and pins the page. Then it copies the packet and finally, unpins the page. Then as before, the driver domain notifies the guest domain and the guest domain revokes the grant.

Essentially, a grant is issued and revoked for each and every I/O operation, leading to significant performance overhead for memory sharing. Some of these overheads, especially the cost of issuing hypercalls, can be reduced by batching the grant operations. But despite this optimization, the overheads remain high.

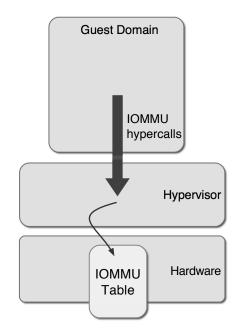

## 3.3 Memory Sharing with Pass-through Devices

The main feature of pass-through devices is that they bypass the driver domain and have direct access to the hardware. Here, a guest domain directly shares its I/O buffers with the I/O device. In this scenario, an IOMMU is essential to restrict the device's access only to the memory of the guest domain to which it is assigned. Otherwise, memory isolation cannot be enforced since a malicious guest domain can setup DMA operations to other guest domains' memory.

In Xen, each pass-through device is configured with an IOMMU table which is used to provide *coarse-grained protection*. In this mode, the IOMMU table is configured with valid translations for exactly all the pages that belong to the guest domain accessing that device. So the IOMMU table is mostly static and does not change unless the set of pages assigned to the guest domain changes.

To provide a higher level of protection against buggy device drivers or to enable user-level drivers, the set of valid IOMMU translations can be limited to only a small set of pages which contain I/O buffers that need to be accessed by the device. In this mode, which is referred as *fine-grained protection*, the guest domain needs to invoke the hypervisor so that it can add the corresponding page mappings to the IOMMU table before programming a device DMA operation, and remove the page mappings after the DMA operation is completed. (Figure 3.3) and this can incur significant overheads [40, 42].

## 3.4 The Design

A grant reuse scheme can significantly reduce grant overheads by reusing the same grant for multiple I/O operations. A guest domain can issue a grant for a page

containing I/O buffers, then use the page several times for I/O, and finally revoke access to the page. Thus under the reuse scheme the overheads of the grant hypercalls and the mapping/unmapping operations are not incurred on every I/O operation.

In the grant reuse scheme, the domain initiating the sharing (the source domain) should be able to revoke a grant at any given time. For example, suppose a guest OS shares a page with a driver domain for network I/O, and then later the guest OS repurposes the page, say to assign the page to a user-level process. Before re-purposing the page, the guest OS might want to revoke the grant to prevent subsequent access to the page by the driver domain. In general, a source domain should have the flexibility to revoke a grant from various OS subsystems running in that domain. Using the existing grant mechanism in Xen, this would require the source domain to carry out a protocol handshake with the destination domain via an inter-domain I/O channel (like net-channel) to revoke the grant. This handshake protocol prevents the source domain from completing the grant revocation until the destination domain unmaps the page and notifies the source domain that the unmapping is complete. If the destination domain, for some reason, is unable to respond, there is no way for the source domain to revoke access to the shared page.

Instead, a new mechanism is proposed that breaks this dependency by allowing the source domain to unilaterally issue and revoke grants. This means that the guest domain can issue and revoke grants, during I/O, using a simple hypercall interface without requiring driver domain participation. This avoids the handshake protocol completely. Moreover, the new mechanism has the benefit of reducing the trust required between any two domains that are sharing memory. Either guest domain can unilaterally remove access privileges to its pages from the other guest domain, without requiring the cooperation of the other guest domain to unmap the pages.

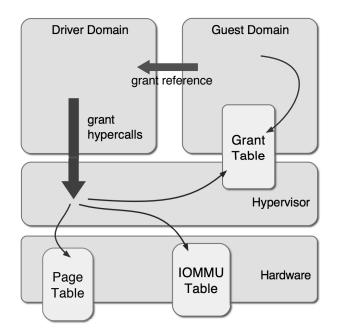

Figure 3.4 : New unified memory sharing interface. Guest domains interact directly with the hypervisor, via grant hypercalls, to issue and revoke grants.

This is particularly useful in case the other guest domain misbehaves.

It turns out that the guest interface to the new mechanism is very similar to an interface needed to add and remove page mappings from an IOMMU table when using the fine-grained protection mode. Thus the grant interface can be used to issue/revoke grants and/or add/remove entries to/from an IOMMU table. This unification simplifies I/O support in the guest OS, to share memory either with driver domains or with devices directly. For example, for guest domains running Linux this can be supported by a common implementation of the DMA API interface [40, 42]. Additionally, this allows the same "grant" reuse scheme to be used both for driver domains and directly accessed I/O devices, providing performance benefits in both cases.

The new memory sharing interface is illustrated in Figure 3.4. In the proposed

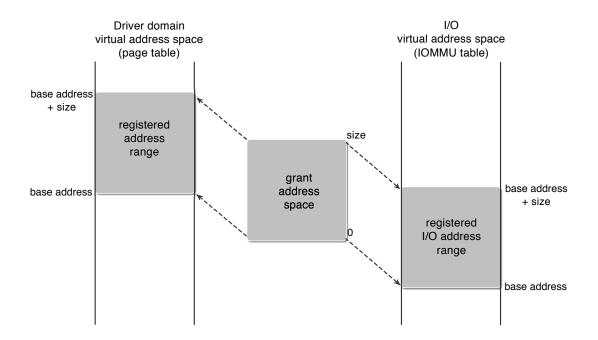

Figure 3.5 : Grant address space. The guest pages are mapped within the registered virtual and I/O virtual address ranges.

mechanism, the guest domain directly interacts with the hypervisor, via hypercalls, to issue and revoke grants. Further, a common interface is presented for both passthrough and standard I/O devices. The subsequent sections explain the design in greater detail.

#### 3.4.1 Initialization

The initialization occurs in one or two stages depending on whether the guest domain has direct access to the I/O device or not. In the first stage, the destination domain (driver domain) issues a hypercall to begin initialization. The driver domain passes a virtual address range in its address space (base virtual address and size) and a device id as arguments to the hypervisor. The hypervisor registers this virtual address range for the specified device. The driver domain can also, optionally, specify a different I/O virtual address range in the IOMMU's address space. But the size of both the address ranges must be identical. This stage is not required if the guest domain has direct access.

In the second stage, the guest domain issues a hypercall passing the device id as an argument. There are two cases here:

- If the device id corresponds to a physical device and if that device has been directly assigned to that domain, then the hypervisor initializes an IOMMU table for that domain/device pair. The hypervisor specifies a *grant address space*, which, in this case, is same as the IOMMU's address space.

- If the device id corresponds to a virtual device, then the hypervisor checks if the corresponding driver domain has performed the registration. If so, it uses the size of the registered address ranges to specify the grant address space (*i.e.*, 0 → size of the address range).

The grant address space is illustrated in Figure 3.5. Finally, the hypervisor returns a handle back to the guest domain which is used by it for all future grant operations.

#### 3.4.2 Creating Shared Memory

Shared memory is created using the new interface as follows:

• The guest domain issues a grant hypercall, to enter the hypervisor, passing the handle, the address of the page to be shared, the access permissions, and a grant reference. The notion of a grant reference is retained from the existing mechanism. But under the new mechanism, the grant reference is an offset within the grant address space.

- The hypervisor first obtains the machine address of the shared page and validates that the page is owned by that guest domain. If the validation succeeds, it pins the page.

- Then the hypervisor maps the page within the registered virtual address range in the driver domain's address space. The hypervisor computes this virtual address as the sum of: (a) the base address of the registered virtual address range, and (b) an offset equal to the grant reference. This requires adding a new entry (computed virtual address → guest domain machine address) to the driver domain's page table. This step is not needed when using pass-through devices.

- Finally, the hypervisor adds a mapping within the registered I/O virtual address range. It again computes the I/O virtual address as the sum of: (a) the base address of the registered I/O virtual address range, and (b) an offset equal to the grant reference. This again requires adding a new entry (computed I/O virtual address) to the IOMMU table.

The guest domain passes the grant reference to the driver domain via the netchannel. The overhead of using grants in the driver domain is very low since the guest pages are already mapped. Now the driver domain can obtain the virtual address to access the guest page by using the grant reference as an offset within the virtual address range it registered with the hypervisor. Similarly, it can also obtain the I/O virtual address to setup DMA operations by using the grant reference as an offset within the I/O virtual address range. Essentially, the driver domain has to only perform simple arithmetic operations.

#### 3.4.3 Revoking Shared Memory

Shared memory is revoked using the new interface as follows:

- The guest domain issues another grant hypercall, to enter the hypervisor, passing the handle, and the grant reference corresponding to the shared page to be revoked.

- The hypervisor first removes the IOMMU mapping. It also performs the required IOTLB invalidation.

- Then it unmaps the page from the driver domain's address space. It also performs the required TLB invalidation. This step is not needed when using passthrough devices.

- Finally, it unpins the shared memory page.

So a guest domain can use the new memory sharing interface to revoke a grant, at any time, without any cooperation with the driver domain. While this would work properly under normal error-free conditions, it can lead to problems when a guest domain misuses the new interface. In particular, consider the scenario when a buggy or malicious guest domain revokes a grant while the corresponding page is still being used for an active I/O operation. Even under such conditions the grant revocation will succeed, and as a result, the guest page will not be accessible to neither the driver domain nor the device. But since the driver domain is not aware of the revocation, it might inadvertently try to read or write the page. It might have also programmed the device to DMA packets to or from that memory page. But since the guest page is no longer mapped in the driver domain's address space or the IOMMU's address space, these memory accesses will result in a fault—a page fault or an IOMMU fault. Such faults might render the driver domain unusable. Though the driver domain can be restarted under such conditions, the resulting I/O interruption it far from ideal.

A potential solution is to use *dummy* pages to replace the real pages when their grants are revoked by a guest domain. So the hypervisor allocates a dummy page for every device—virtual or physical—in the system. Now when the grant to a page is revoked by a guest domain, the associated dummy page is atomically swapped into both the driver domain's and the IOMMU's address pace. Therefore, any future accesses to that page will no longer result in a fault. But the driver domain and the device might have to deal with corrupted packets, and typically, they are robust enough to do so.

## **3.5** Reuse of Grants

The cost of using the grant mechanism can be reduced by enabling the reuse of the same grant across multiple I/O operations, taking advantage of locality in the use of I/O buffers, whether spatial locality—multiple I/O buffers sharing a page—or temporal locality. This allows a grant acquired for a guest domain's memory page to be reused for future I/O operations. A grant associated with a guest domain's memory page can be revoked at any given time.

Grant reuse is effective at reducing grant overhead only if the reused page remains mapped in the driver domain's address space since page mapping and unmapping are expensive operations. When the guest domain desires to revoke a grant, the page must be unmapped from the driver domain's and IOMMU's address spaces. In the proposed mechanism, this can be done unilaterally by the guest domain without driver domain's cooperation. In contrast, in the original grant mechanism, grants can be revoked only with the cooperation of the driver domain which has to issue the hypercall to unmap the guest pages from its address space.

While the new mechanism enables simple and unilateral grant revocation under the grant reuse scheme, the performance benefits are predominantly provided by the grant reuse scheme itself.

#### 3.5.1 Reuse Scheme

A guest domain can employ different schemes to reuse grants for minimizing the grant related overheads. These schemes are essentially a trade-off between performance and security. Coarse-grained protection, where all the guest pages are shared persistently, provides the best performance but the least security. This scheme is currently used with pass-through devices in Xen. Strict fine-grained protection, where a guest page is only shared for the duration of a single I/O operation, provides the best security but the least performance. This scheme is used under the standard network I/O model in Xen. Several other schemes have been proposed in the past, such as shared mappings, delayed invalidations, and optimistic tear down [43, 44]. All these schemes use a relaxed fine-grained protection mode to achieve better performance, without necessarily resorting to the coarse-grained protection mode.

In this implementation, the default reuse scheme was to just limit the number of pages shared by a guest domain at any given time. The size of the grant address space, as registered by the driver domain, defines the maximum number of pages which can be shared by a guest domain. A guest domain can either choose to use the entire grant address space or use only a part of the address space to further limit the number of shared pages. When the grant address space is full, existing grants are revoked to make space for new grants.

An alternate scheme is to revoke a grant to a page when the page is re-purposed

to be used for a non-I/O operation. This scheme is used only for grants associated with I/O buffers shared as read-write with the driver domain (receive I/O buffers). The rationale behind this scheme is that a read-write buffer which is re-purposed can be corrupted if its still shared with the driver domain. This scheme is implemented using the Linux slab cache mechanism, which is used to create a dedicated read-write I/O buffer pool. The I/O buffers are allocated from the pool when needed for receive operations and are returned to the pool afterward. Further, the guest OS revokes the grant associated with a guest domain's memory page when it is released from the slab cache. As an added benefit, recycling buffers from the pool can also promote locality leading to a higher degree of grant reuse.

#### 3.5.2 Tracking Grant Use

While different mechanisms can be used in different guest domains to keep track of grant use, the guest OS in the prototype implementation uses a hash table for each virtual device. Each entry in the hash table corresponds to a grant reference. The table is divided into two halves, one half is used to track read-only grants and the other half is used to track read-write grants. If a grant is issued, the hash table entry contains the guest page frame number (pfn), and a reference counter that records the number concurrent active uses of a grant. The pfn is used to resolve hash collisions and the counter is used to check if a grant is active or not. Each entry is treated as a single 8 byte word to facilitate efficient atomic memory accesses.

The guest domain checks whether a grant already exists for a page by looking up the hash table as follows:

• First, the pfn of the page is fed into a hash function. The hash function returns a *hash set* which is a set of contiguous locations in the hash table which can

potentially contain a grant for that page.

- Then each entry in this set is checked to see if it contains a grant for the page. If a grant already exists, then the grant can be reused. So the guest domain increments the reference counter and simply reuses the grant.