# FORESTRY AND NATURAL SCIENCES

MARTTI PENTTONEN (ED.)

# Computer Science I Like

Proceeding of Miniconference 4.11.2011

PUBLICATIONS OF THE UNIVERSITY OF EASTERN FINLAND Reports and Studies in Forestry and Natural Sciences

MARTTI PENTTONEN (EDITOR)

## Computer Science I Like

Proceedings of Miniconference on 4.11.2011

Publications of the University of Eastern Finland Reports in Forestry and Natural Sciences No 6 Kopijyvä Kuopio, 2011 Editor: Prof. Pertti Pasanen

Distribution: University of Eastern Finland Library / Sales of publications P.O. Box 107, FI-80101 Joensuu, Finland http://www.uef.fi/kirjasto

> ISBN: 978-952-61-0635-9 (printed) ISSNL: 1798-5684 ISSN: 1798-5684 ISBN: 978-952-61-0636-6 (pdf) ISSN: 1798-5692 (pdf)

# Preface

This proceedings is outcome of a miniconference held on 4.11.2011, at the University of Eastern Finland. The editor of this book, before retirement a month later, invited his former PhD students to give a talk under title *Computer Science I Like*. The point behind the title was that scientific research is not just work but also a vocation. As an event, the miniconference was a more or less regular scientific conference, although only one day long and with a wider scope. For students it offered a window into the world of research. Also, it was fun to meet. I thank all those, who made this miniconference and proceedings possible.

Kuopio, 5 December, 2011

Martti Penttonen

## Contents

| Anne Eerola: Why do we need software engineering1                     |

|-----------------------------------------------------------------------|

| Martti Forsell: <i>Computer architecture re(de)fined — the era of</i> |

| parallel computing23                                                  |

| Keijo Haataja, Konstantin Hyppönen, Pekka Toivanen:                   |

| <i>Ten years of Bluetooth security attacks: lessons learned</i> 45    |

| Marko Hassinen: Non-repudiation and smart cards                       |

| Risto Honkanen: Matrix based calculation of all-pairs shortest        |

| paths on the GPU87                                                    |

| Konstantin Hyppönen: XML and RDF for semantic                         |

| interoperability in public administration                             |

| Simo Juvaste: Teaching performance113                                 |

| Anssi Kautonen: Routing on the OCPC                                   |

| Marja Kuittinen: Learning and teaching computer science               |

| Ville Leppänen: Moving threads and parallel thick control flows 159   |

| Martti Penttonen: How to invent and prove a result                    |

## Why do we need software engineering?

Anne Eerola School of Computing University of Eastern Finland P.O. Box 1627, 70211 Kuopio, Finland

Abstract. The background of the modern software engineering is based on the software crisis. It was noticed that the quality of software is not as good as it should be. Since then, we have got a lot of methods and tools, but we still have challenges to build up high quality software that can be maintained, too. Difficulties occur especially in developing large, heterogeneous, and distributed information systems. In this paper, we emphasize some of the most important concerns of software engineering. We cover a path from requirements engineering, through architecture development and testing, to component-based software. We highlight the methods and practices which promote the production of software fulfilling the requirements of business and stakeholders. Additionally, we propose that IT Service Management is an important part of software engineering.

## **1** INTRODUCTION

Information systems are nowadays complex, distributed, and they need to be changed and maintained according business requirements. Additionally, many information systems, for example, in health care and banking domains are critical and require high quality of software and its production process. In this paper, we consider why software engineering is needed and how does it assist the development of information systems.

The background of the modern software engineering is based on Year 1968 as an answer to the software crisis. It was noticed that it is difficult to write correct and understandable computer programs, which take into consideration change management, too. *Software Engineering* (SE) is an engineering discipline which focuses on cost effective development of high-quality software systems [32]. While computing concentrates on computers, programming languages and algorithms SE emphasizes tools to solve problems in software industry or customer organizations [28].

Software Engineering investigates software production (requirements engineering, analysis, design, implementation, software testing and inspection, deployment, and maintenance). Moreover, quality management, product management, and the structure of software systems, i.e. architectures, components, frameworks, and patterns are considered [9, 32]. The emphasis is mainly on technical aspects of software systems. However, most software engineers agree that it is not possible to start a software development project without considering carefully the requirements of the stakeholders. After deployment, customers and users need support in using software systems. Hence, we develop methods, techniques, and processes of IT service management and propose that IT service management is an important part of SE [13, 14].

Intelligent thinking requires that a designer focuses his/her attention upon some aspect and follows the *separation of concerns principle*: "We know that a program must be correct and we can study it from that viewpoint only; we also know that it should be efficient and we can study its efficiency on another day" [4]. *Concerns* can be responsibilities, functions, data, features, tasks, qualities, transactions, services, or any aspect of the requirements or design [3,28].

*Modularization* is concerned with the meaningful decomposition of the software system and with its grouping into subsystems, components, and services [3,24]. Since structured design [40] emerged, high cohesion and low coupling have been attributed to indicate high quality of software. The term module can be defined as "a syntactical or conceptual entity of a software system" [3]. A mod-

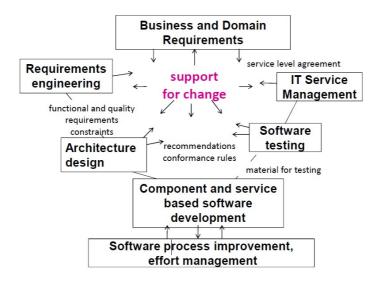

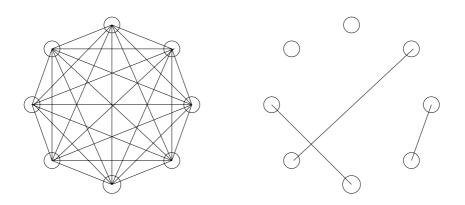

Figure 1: Research in Software Engineering

ule is a component, a class inside a component, or a service using which the functionality is offered to the customer.

Research in software engineering at the University of Kuopio (now University of Eastern Finland) started in 1990s. In our research group requirements engineering, architecture design, software testing, IT service management, and effort management are emphasized (see Fig. 1). Typical research methods are case studies, action research, and constructive research. Data collection is based on multiple sources of evidence (field visits, workshops, participative observation in meetings, interviews, access to organizations tool applications, and internal documentation). The research results can involve, for example, identification of process challenges; creation of new methods, and models; providing process implementation guidelines and recommendations; as well as improving data, quality, and service management. The group belongs to Information Systems and Software Engineering research group.

In this paper the research question is: Why do we need software engineering? We aim to answer the question by highlighting research results that from our opinion are typical and important to software engineering. Additionally we give an overview of our research results. The rest of this paper is organized as follows: Chapter 2 considers effort management as a basis of software process management. In Chapter 3, we consider requirements engineering as a collection of stakeholders wants and needs. Chapter 4 discusses software architecture development, especially component based software development and integration. Chapter 5 emphasizes software testing and its importance. Chapter 6 introduces IT service management. Chapter 7 concludes the paper.

## 2 EFFORT MANAGEMENT

Usually a software project starts with feasibility study and effort estimation. Accurate effort estimation is important because it enables to keep project schedule, budget, and time-to-market calculations. Successful resource allocation decreases working pressure and haste of software engineers, too. Haapio proposed that non-construction activities should be taken into account in addition to the constructive and project activities [7]. Non-constructive activities are, for example, configuration management, customerrelated activities, documentation, orientation, and quality management. Effort management continues through the whole software development project and we should help software engineers to adopt general project activities in order to increase reliability of registered effort in time-booking entries.

Haapio et al. [8] proposed a novel stepwise method for assessing software project effort. The method provides necessary tools for the effort management and assessment. When utilized for post-mortem analysis, the method can be used for deciding on the project result and how the project differs from other projects (quantity, quality, and effort views).

Virtanen [38] has considered effort estimation in component based software development. He has strived to increase reusability and productivity in software development. The starting points in

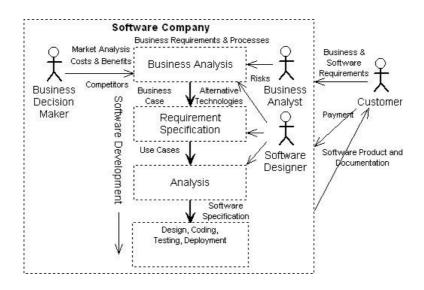

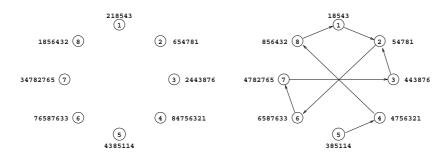

Figure 2: Business case as a starting point for requirements engineering [15]

method are product structure and history data of projects. The average effort of components is after calculation corrected emphasizing project and human effects.

### **3 REQUIREMENTS ENGINEERING**

The gap, between business decision making and software engineering, causes inefficiency and quality problems in software development. Software engineers do not understand organization's value creation objectives and their influence on software production and structure. For this reason, software does not fulfil business requirements and software quality is inadequate too often. Hence, we utilize a business case as a starting point for requirements engineering (see Fig. 2).

Software systems must fulfill the requirements of the stakeholders. Stakeholders are people, who have interest in the product or who will be affected by products use [30]. "A requirement is a condition or capability of the software or its component needed by a

user to solve a problem or achieve an objective" [11]. A requirements specification describes what the system must do and which properties the system must have to satisfy a contract, a standard, or other user requirements [11,30]. Requirements errors are the most expensive and the most dangerous software errors [21]. It is important to gather, analyze, validate, and master the requirements carefully.

*Functional requirements* define functions of a software system, or its component and services, that the system must provide [32]. Additionally, functional requirements are data requirements (i.e. the system must store, maintain, and managed data) and things that the system is not allowed to do [30]. These requirements are currently most often presented in the form of *use cases* described in the almost standard Unified Modeling Language UML [5].

*Quality requirements* of software are product, organizational, and external requirements, for example, usability, standardization, and safety [32]. One component of the software needs not to be as high quality as another, if the components do not depend on each other and if there is no side-effect. Quite often, quality attributes of software cannot be pinpointed to a certain component [2]. Prioritization and definition of *sensitivity points* for quality attributes is needed [17]. *Quality requirements of a production process* are qualities that software engineers appreciate, for example, maintainability and reusability [2]. As before, one step of the production process needs not to achieve as high quality as another, if the importance and risks of steps differ. A research problem is, how we can find the components and production steps that are most important to be emphasized.

We strive to improve requirements engineering (RE) processes and models through following ways:

- We have derived guidelines for managing requirement process in case of large information systems and different professionals (e.g. nurses, doctors, software engineers, researchers).

- We keep in mind that software requirements should be de-

scribed in such a way that architecture and forthcoming software are convenient to design (although the process may stop, if it turns out after the RE-process that software is not a right solution to current problems).

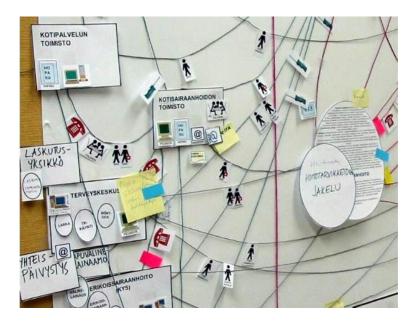

• We have generated understandable models for requirements specification contributing architecture design decisions and detailed requirements specifications (e.g. see Fig. 3).

One problem is that we need a common language for all the stakeholders in the RE-process and forthcoming software development project. Another great problem in RE is that information systems development processes of customer organizations and software providers do not meet each other. Hence, the interaction between the software provider and its actual client does not occur in the software providers RE phase. It may happen the product is built before its requirements are specified [22]. Component based software development, generic products, and parameter utilization assist this problem, but do not solve it thoroughly.

## 4 SOFTWARE ARCHITECTURE DEVELOPMENT

## 4.1 Software architecture, architectural styles, and patterns

Architectures and design models are important tools to assure software quality and to improve software reuse. IEEE Standard 1471-2000 defines the *software architecture* as "The fundamental organization of a system embodied in its components, their relationships to each other and to the environment, and the principles guiding its design and evolution". The software architecture consists of statements describing how a system is decomposed into its component parts and how the functionality is allocated among those parts. Smolander [31] has considered the role of architecture in systems development in several organizations. For example, the usage of architectural viewpoints and the rationale of architecture design and description are considered.

Figure 3: Home Care -case [34]

Architecture analysis and design offer means to understand business goals and stakeholder concerns and map these onto an architectural representation, and assess risks associated with this mapping [17]. The architecture is a blueprint and an implicit high-level plan for software construction [19].

Software engineering team can use architectural styles, first proposed by Perry and Wolf [27]. The *architectural style* defines types of components and connectors (i.e. building blocks), constraints for using the building blocks, vocabulary, and analysis to reason critical and risky properties of the solution [2,3]. Examples of architectural styles are Pipes and Filters, Broker, Repository, and Layered styles.

In addition to styles, software engineers utilize patterns, for example, architectural, design, usability, security, and organizational patterns [3,6]. The described "*pattern* is a general and proven solution to a frequently occurring architecture or design problem in a context" [1,6,18]. Examples of patterns are Proxy, State, Facade, Why do we need software engineering

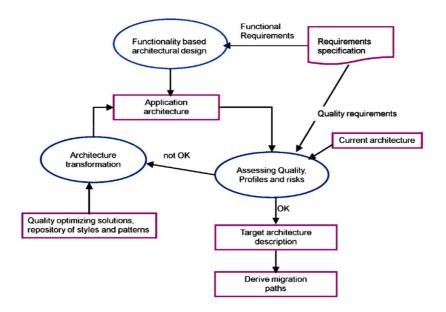

Figure 4: Target architecture design

Role, and Undo.

The functionality of the component based system can be offered to the customers using service oriented architecture. This supports generation of modifications. "A Service-Oriented Architecture (SOA) is an architecture that is based on the key concepts of a user interface, service, service repository, and service bus." [19].

The *target architecture* defines the vision where we want to develop our information system. Usually it is not possible to move to the target state at once but we need a *migration path* from the current legacy system to the target architecture [25]. Architecture design, assessment, and evolution are described in Fig. 4.

### 4.2 Component and service based software development

The structure of software is defined using components and services. Component based software development (CBSD) and service oriented architectures (SOA) have emerged perhaps to the most pop-

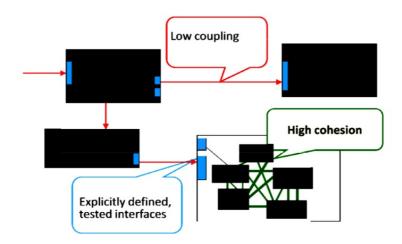

ular software development approach today: In CBSD software is constructed using self-made and commercial off-the-shelf (COTS) components and glue code if needed. The idea is not new, but McIlroy [23] proposed mass-production of components already in 1969. A software component is a binary unit for composition according to the contract and explicit dependencies [33]. It is self-contained piece of software, which encapsulates a set of related functions and data and can be independently deployed and plugged into a compatible environment [10]. At run-time the component is accessed through a set of interfaces [32]. Similarly build-time interfaces (proxy export) are advantageous to be utilized in order to shorten time-tomarket [10]. A component has no persistent state. The relationships and interfaces between components and the internal structure of each component can be described with UML Diagrams and XML document type definitions (DTD) [20]. While designing component based systems we should strive to low coupling and high cohesion (see Fig. 5).

Component based systems are often object oriented. In object oriented approach, things in the real world are abstracted as objects, which encapsulate attributes and methods. Objects communicate with each other by sending messages. These objects can be related to each other by aggregation, by association, and by classification. Objects are defined in a class. Classes, in turn, form a class hierarchy, in which subclasses inherit properties, i.e. attributes and methods from super classes [5,29].

A *service* fulfils a contract and it has one or more interfaces and an encapsulated implementation [19]. Each service is a software component of distinctive functional meaning (business logic and data) and is found from a repository. Services are typically not linked as code libraries but are bound to at runtime.

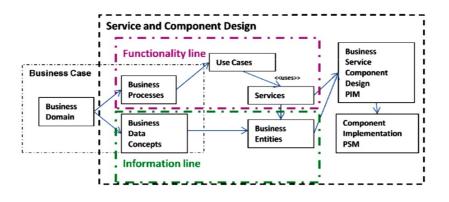

Our goal has been to develop methods and tools for serviceoriented software development emphasizing business aspects and quality of software structure (see Fig. 6). We propose a service map for service workflow definitions, utilize Service Level Agreement (SLA) based on IT Service management framework [12], and Why do we need software engineering

Figure 5: Low coupling, high cohesion, and explicitly defined and tested interfaces

clarify protocol requirements using distributed coordination in the SOA environment. In addition, software service identification and design has been studied.

## 4.3 Integration

The focus of the software development process has moved from separate and independent applications to the integrated and distributed software systems. Vänttinen [39] has strived to provide quicker and more effective way, with smaller resources to launch software products to the markets, and to enable the integration between software systems, provided by different vendors.

His thesis introduces enterprise application integration (EAI) and service oriented architectures (SOA) and analyzes three reallife case studies to find out how principles of EAI, SOA, and software product families can be used efficiently in software industry.

Acquired components and legacy systems are integrated according to the target architecture [26] in order to get the software system, which fulfils the requirements of stakeholders. Integration

Figure 6: Framework for service oriented software development [15]

of software pieces can be done by third party using interface definition language (IDL or XML) and tested interfaces [33]. Additionally, conformance to the standards is advantageous to be tested [36].

Mykkänen [25, 26] has considered health information systems. He has proposed methods, models, and guidelines for developing reusable integration solutions using a component-based and modeldriven approach:

- Methods to improve interoperability of software system

- A generic integration process with integration specification levels that support collaborative integration definition,

- A method for stepwise migration from current legacy architecture to component-based target architecture, and

- Experiences and recommendations for integration based on several pilot projects in software industry and healthcare/welfare service providers.

## 5 SOFTWARE TESTING

Nowadays software systems are not built in green field but software is constructed from ready-made COTS (commercial off the shelf) which must cooperate with each other. Hence, interoperability between applications is important. High quality and reliability requirements of software systems cause that software testing is important and testing techniques should be practical and easy to use. However, in network of organizations it is often impossible to test all side-effects when a change is accomplished in requirement specifications or code.

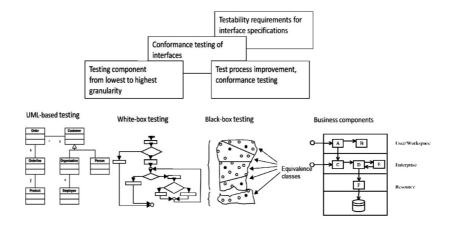

We have strived to improve software testing policy and methods. Components of different granularities were tested level by level leading to integration and conformance testing (see Fig. 7). We defined test cases based on UML diagrams and contracts of components. The dependency graph was used to assure that the whole functionality of the system has been covered. Usually, the internal logic of components is object-oriented and component systems are distributed.

Toroi [35,37] has proposed methods to help software companies to apply testing theory efficiently in practice and to improve interoperability by standards and conformance testing. The research questions were: How can we be sure that the product or an interface conforms to standards? How the recommendations, standards, and interface specifications should be defined, when we strive for testability? We considered three viewpoints: integrator, customer, and service provider.

Additionally, Toroi has considered test process improvement in industry and given a list of recommendations for improving test processes. She proposed that organizations have to pay more attention to the following issues: test case documentation, regression testing, the level of training in testing, clarity of specifications, and guidance of the test process improvement models.

## 6 IT SERVICE MANAGEMENT

In software industry there is a strong business need for IT service management (ITSM) research. Thousands of IT organizations worldwide have started to implement ITSM processes and organi-

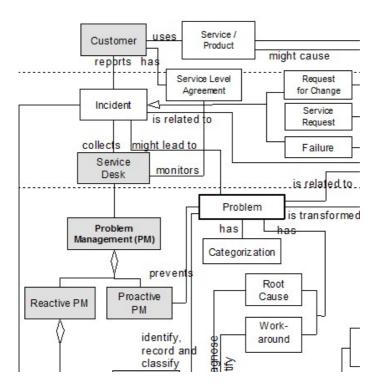

Figure 7: Testing Component-Based Systems

zations face several challenges while implementing processes. Jäntti [13] has considered difficulties in managing software problems and defects, which number has increased due to complex IT systems, new technologies, and tight project schedules. Regarding emerging new research topics it is common that the concepts are undefined, inconsistent, and inaccurate. Hence, conceptual model for IT Service Problem Management was proposed (see Fig. 8).

In our research projects MaISSI (Managing IT Services and Service Implementation) and KISMET (Keys to IT Service Transition) we have derived recommendations and guidelines for IT services and ITSM processes. Our viewpoints have been on designing, implementation, maintaining, and improvement. We have examined service implementation technologies and tools in close cooperation with industrial partners, i.e. IT service provider companies, software companies, and IT customer organizations. We have helped industrial organizations to identify challenges in their current activities. The goal has been to share knowledge on ITSM standards and frameworks.

The research validation is carried out in pilot projects that aim to solve problems that industrial partners have met in their service

Figure 8: A part in a conceptual model of IT Service Problem management [14]

management business. For example, we have developed process descriptions for service support processes (incident management, problem management) and service transition processes (change management, configuration management, and continual service improvement). We have helped organizations in configuring service desk tools, examined how to measure the performance of support processes, and organized research workshops and seminars regarding ITSM. Industrial partners have utilized research results to increase the quality of ITSM processes, to identify the challenges in their current activities, to improve the performance and usability of the tools, and to enable effective knowledge sharing on service management standards and frameworks.

## 7 CONCLUSIONS

In this paper, we have emphasized research results that we propose are important for software engineers in research and industry. We have described the path from requirements engineering, through architecture design and software testing to software products and services. The presented research results form a toolbox needed to build on time and cost high quality software that fulfills stakeholders requirements. After deployment, software needs to be changed and evolved according to business requirements. Hence, IT service management is important.

## References

- [1] Alexander C., Ishikawa S., Silverstein M., Jacobson M., Fiksdahl-King I., and Angel S., A Pattern Language, Oxford University Press, New York, 1977

- [2] Bosch J.: Design and use of software architectures, Addison-Wesley, 2000

- [3] Buschmann F., Meunier R., Rohnert H., Sommerland P., and Stal M., Pattern-Oriented Software Architecture A System of Patterns, John Wiley & Sons, 2001

- [4] Dijkstra, E., W., "On the role of scientific though, 1974" In Dijkstra, E. W. Selected Writings on Computing: A Personal Perspective. New Yourk: Springer-Verlag, 1982

- [5] Fowler M.: UML Distilled A Brief Guide to the Standard Object Modeling Language, Addison-Wesley, 2004

- [6] Gamma E., Helm R., Johnson R., and Vlissides J., Design Patterns Elements of reusable Object-Oriented Software, Addison-Wesley, 1995

- [7] Haapio Topi: Improving Effort Management in Software Development Projects, Doctoral dissertation, University of Eastern Finland, 2011

- [8] Haapio T., Eerola A.: Software Project Effort Assessment. Journal of Software Maintenance and Evolution: Research and Practice. 22(8), pp 629-652, 2010.

- [9] Haikala I., Märijärvi J., Ohjelmistotuotanto, 1998, 2004,

- [10] Herzum P., Sims O.: Business Component Factory A Comprehensive Overview of Component-Based Development for the Enterprise, Wiley Computer Publishing, 2000

- [11] IEEE. IEEE Standard Glossary of Software Engineering Terminology. New York: IEEE, 1983. Leite, J. Viewpoint Resolution in Requirements ANSI/IEEE Std. 729-1983.

- [12] IT Infrastructure Library, Office of Government Commerce (OGC), 2002 Continual Service Improvement, OGC 2007

- [13] Jäntti Marko: Difficulties in Managing Software Problems and Defects, Doctoral dissertation, Department of Computer Science, University of Kuopio, 2008.

- [14] Jäntti M., Eerola A.; A Conceptual Model of IT Service Problem Management, Proceedings of the IEEE International Conference on Service Systems and Service Management ICSSM06, 2006

- [15] Karhunen H., Jäntti M., Eerola A.: Service-Oriented Software Engineering (SOSE) Framework, International Conference on Service Systems and Services Management 2005, Proceedings ICSSSM05, 2005

- [16] Kazman R., The Essential Components of Software Architecture Design and Analysis, Proceedings of the 12th Asia-Pacific Software Engineering Conference (APSEC05), 2005

- [17] Kazman R., Bass L., Abowd G., Webb M., SAAM: A Method for Analyzing the Properties of Software Architectures http://www.sei.cmu.edu/library/assets/ICSE16.pdf, referred 11.4.2011

- [18] Koskimies K., Mikkonen T.: Ohjelmistoarkkitehtuurit, Talentum Media Oy, 2005

- [19] Krafzig D., Banke K., and Slama D., Enterprise SOA Service-Oriented Architecture Best Practices, Prentice Hall, Pearson Education, 2005

- [20] Kuikka E., Eerola A., A Correspondence between UML Diagrams and SGML/XML DTDs, Lecture Notes in Computer Science, Springer-Verlag, 2023/2004

- [21] Axel van Lamsweerde: Requirements Engineering, John Wiley Sons Ltd, 2009

- [22] Luukkonen I., Eerola A.: Improving requirements Engineering from the clients perspective in the health care domain, Proceedings of the 25th conference on IASTED International Multiconference: Software Engineering, 2007

- [23] McIlroy M., D., Mass produced software components. In Naur P. and Randell B., Software Engineering, Report on a conference sponsored by the NATO Science Committee, Garmisch, Germany, 7th to 11th October 1968, Scientific Affairs Division, NATO, Brussels, 1969,138-155.

- [24] Meyer B., Object-Oriented Software Construction, Prentice Hall International, 1988

- [25] Mykkänen Juha: Specification of Reusable Integration in Health Information Systems, Doctoral dissertation, Department of Computer Science, University of Kuopio 2007

- [26] Mykkänen J., Tikkanen T., Rannanheimo J., Eerola A., Korpela M.: Specification Levels and Collaborative Definition for the Integration of Health Information Systems, In Baud R, Fieschi M, Le Beux P, Ruch P, eds. The New Navigators: from Professionals to Patients, Proceedings of MIE2003, Saint-Malo, France, 4-7 May 2003

- [27] Perry D.E. and Wolf A.L., Foundations for the Study of Software Architecture, ACM Software Engineering Notes, 17, 4,October 1992, 40-52

- [28] Pfleger S.,L., and Atlee J.M., Software Engineering Theory and Practice, Pearson Education, Prentice Hall, 2010

- [29] Putkonen A.: A Methodology for Supporting Analysis, Design and Maintenance of Object-oriented Systems, Academic Dissertation, Department of Computer Science and Applied Mathematics, University of Kuopio, 1994

- [30] Robertson S., Robertson J.: Mastering the Requirements Process, Addison-Wesley, 1999

- [31] Smolander Kari: On the Role of Architecture in Systems Development, Department of Information Technology, Lappeenranta University of Technology, 2003

- [32] Sommerville I., Software Engineering, Eight Edition, PearsonEducation, 2011 Software Architecture Definitions, http://www.sei.cmu.edu/architecture/start/community.cfm and IEEE Standard 1471-2000

- [33] Szyperski C., Component Software Beyond Object-Oriented Programming, Addison-Wesley, 1999

- [34] Toivanen M.: Home Care -case [PlugIT-hanke], 2004

- [35] Toroi T.: Testing Component-Based Systems Towards Conformance Testing and Better Interoperability, Doctoral dissertation, Department of Computer Science, University of Kuopio, 2009.

- [36] Toroi T., Eerola A., Mykkänen J., Conformance Testing of Interoperability in Health Information Systems in Finland. In: Kuhn K., Warren J., Leong T-Y, eds. Medinfo 2007, Brisbane, Australia, August 20-24, 2007, p. 127-131. Amsterdam: IOS Press, 2007.

- [37] Toroi T., Eerola A.: Requirements for the Testable Specifications and Test Case Derivation in Conformance Testing, In: Dasso A, Funes A, eds. Verification, Validation and Testing in Software Engineering, P. 118-135. Hershey: Idea Group Publishing, 2006

- [38] Virtanen, P., 2003. Measuring and Improving Component-Based Software Development. Doctoral dissertation, Finland: University of Turku.

- [39] Vänttinen Pasi: Integrating Applications in Software Company, Licentiates thesis, Department of Computer Science, University of Kuopio, 2008

- [40] Yourdon E., and Constantine L, Structured Design, Fundamentals of a Discipline of Computer Program and Systems Design, Englewood Cliff, NJ: Prentice Hall, 1978

Reports in Forestry and Natural Sciences No 6

## Computer Architecture Re(de)fined —the Era of Parallel Computing

Martti Forsell<sup>1</sup>

<sup>1</sup> VTT, Computing Platforms, Box 1100, FI-90571 Oulu, Finland Martti.Forsell@VTT.Fi http://www.ee.oulu.fi/~mforsell/work.html

Abstract. Now that all the major general purpose processor manufacturers have irreversibly switched to multicore processor architectures with aims to increase the number of processor cores per processor chip as fast as evolving silicon technologies makes it possible to pack more transistors on them, it is time to take a look at the architectural ideas behind them. A simple classification of architectural approaches in current multicores reveals that the symmetric multiprocessor and non-uniform memory access, which lend most of their performance enhancement techniques from sequential computers, are by far the two most common ones. Since our measurements and also wide-spread consensus indicate that the performance and programmability of these approaches is far from perfect, we ask wether these techniques suit best to multicore style threadlevel parallel execution or are there possibly other/new techniques that would provide better performance. Based on our on-going analysis of parallel execution techniques, we are tempted to answer negatively to this question. More specificly, we claim that techniques, like multithreading assisted high-throughput computing providing scalable latency hiding, chained static superscalar execution allowing easy exploitation of low-level virtual instruction-level parallelism, combining/active memory techniques enabling concurrent memory access and multioperations, and wave based light-weight implicit synchronization making possible to emulate strong synchronous models of computation, provide much higher gains in performance and programmability especially for general purpose computation than current ones. Even though this is partially based on preliminary models and on-going work we believe that they already point relatively well to the right direction. Detailed and verified analytic performance models of TLP approaches and thorough discussion on implications will be published in the later phases of this research.

## Martti Forsell

## 1. Introduction

Computer architecture is a branch of science focusing on the theory and practice of designing, selecting and interconnecting hardware components to create computers that meet functional, performance and cost goals and the formal modelling of those systems [Hennessy03]. An abstract (sequential) computer consists of a processor that is connected to the memory and input/output data. The processor is able to read and execute instructions one by one from the memory. While executed, instructions read one or more input data or memory location values, do a simple computation for this data, and write the result to output data or memory. A program is a sequence of instructions that alters the state of the memory so that the output data (results) can be obtained from the input data. A realization of a computer consists of these basic components typically manufactured from semiconductor elements, like transistors, wires, insulators, resistors, and condensators that in turn form basic building blocks of digital systems known as logic gates, memory cells, and registers. These blocks will then be used to build up a processor, memory and input/output devices. As a physical device, this kind of a computer takes always some space (or area on silicon), consumes some power, and is able to execute instructions with some bounded rate. The laws of physics and properties of the used (silicon) manufacturing technology set practical limits to the performance of the processor and size and speed of the memory as well as to the bandwidth of input/output data. The first computers were build according to this kind of Von Neumann architecture, where both the program and data resided on the same memory so that instruction execution involving fetch of instruction and actual execution can not happen in parallel (the Von Neumann bottleneck). The key techniques to improve the performance of this kind of a basic execution engine connected to the memory and input/output devices include the Harward architecture, pipelining, dynamic superscalar execution, caching, and various speculations. The Harward architecture removes the Von Neumann bottleneck by separating the data and instruction memory accesses with a help of dedicated paths. Pipelining [Bloch59, Bucholz62]

### Computer Architecture Re(de)fined

and dynamic superscalar execution [Thornton64, Anderson67, Tomasulo67] improve the throughput of instruction execution and exploitation of available *instruction-level parallelism* (ILP). They make use of various speculations [Johnson89, Hennessy03] to reduce the delays due to memory access, control transfer, and pipelining. Caching [Kilburn62] is used for hiding the latency of the memory systems and balancing the speed difference between processor and memory devices.

In the early 2000's, the clock frequency development of processors and memories almost halted after being exponential for decades since the power density of ever tightly packed semiconductor elements reached its upper limit [Mazke97, Brooks00, Mudge01, Intel06, ITRS10]. As a results, all major processor manufacturers switched irreversibly to multicore processor architectures and thus to the *thread-level parallel* (TLP) computing paradigm with aims to increase the number of cores per processor chip as fast as the silicon technology makes it possible to pack more transistors on a single chip. The manufacturers naturally hope that by increasing the number of cores, users of multicore processor based computers get respectively more performance.

Currently by far the two most popular architectural approaches for multicore computing are *symmetric multiprocessor* (SMP) and *non-uniform memory access* (NUMA) both making use of the shared memory intercommunication scheme but lending most of their performance enhancement techniques from sequential computers. Since our measurements [Forsell02, Forsell11a, Forsell11c] and also wide-spread consensus among parallel computer experts indicate that the performance and programmability of these approaches is far from perfect, we ask wether these techniques suit best to multicore style thread-level parallel execution or are there possibly other/new techniques that would provide better performance. Based on our on-going analysis of parallel execution techniques, we are tempted to answer negatively to this question and claim that techniques, like multithreading assisted high-throughput computing providing scalable latency hiding, chained static superscalar execution allowing easy exploitation of low-level virtual instruction-level paral-

### Martti Forsell

lelism, combining/active memory techniques enabling concurrent memory access and multioperations, and wave based light-weight implicit synchronization making possible to emulate strong synchronous models of computation, provide much higher gains in performance and programmability especially for general purpose computation. Even though this is based on preliminary models and on-going work we believe that they point already to the right direction. Detailed and verified analytic performance models of TLP approaches and thorough discussion on implications will be published in the later phases of this research.

The rest of the paper is organized so that in Section 2 we will take a look at existing TLP architectures, in the Sections 3-7 we discuss performance enhancement techniques for latency hiding, synchronization, virtual ILP exploitation, concurrent memory access and multioperations respectively, and finally, in Section 8 we give our conclusions.

## 2. Existing approaches to thread-level parallel execution

The main approaches to TLP computing, classified according to the used intercommunication mechanism, are message passing and shared memory. In the message passing approach processor cores have local memories only and computational subtask communicate by sending messages to each other. The dataflow computing can be seen as a variant of this approach. In the shared memory approach cores are connected to either unified or distributed shared memory and they communicate via variables on it. Since virtually all current general purpose multicore processors provide a shared memory abstraction, we focus here on the two most popular variants of it—symmetric multiprocessor and non-uniform memory access.

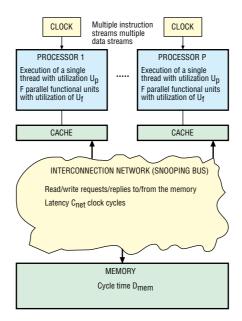

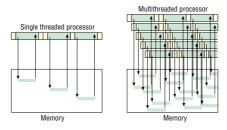

*Symmetric multiprocessor* (SMP) is a simple architectural approach for thread-level parallel computing that is being used typically for a small number of processor cores. An SMP consists of a number of identical (often superscalar) processors with local caches, which are connected to the main memory via a bus (unified case) or crossbar (distributed case)

## Computer Architecture Re(de)fined

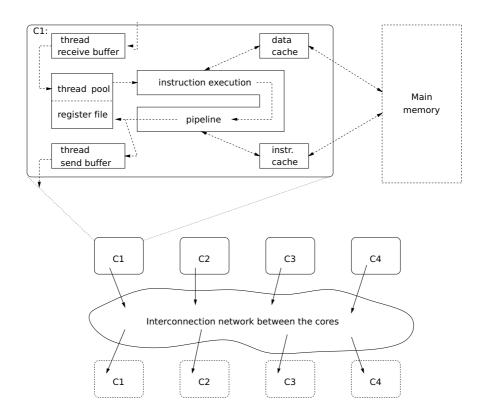

(see Fig. 1). All memory locations are equidistant to all processors, thus access is symmetric. Caches are used in between the processors and the main memory and they are kept coherent using a bus snooping mechanism [Culler99, Hennessy03].

**Fig. 1.** Block diagram of the SMP approach. (*P*=number of processors, *F*=number of functional units,  $C_{net}$ =latency of the intercommunication network,  $D_{mem}$ =cycle time of the memory,  $U_p$ =utilization of processors,  $U_f$ =utilization of functional units.)

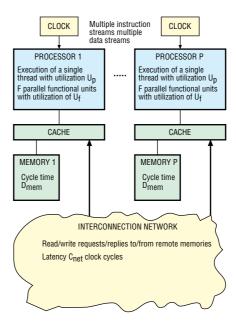

*Non-uniform memory access* (NUMA) is a distributed shared memory approach in which multiple identical (often superscalar) processors with their local caches and memory banks are connected together via an intercommunication network (memory is distributed, only local memory is cached, see Fig. 2). Non-local memory accesses have higher (distance and traffic situation dependent) latency than local accesses [Swan77]. It is believed to provide a more realistic memory accesses take longer than local ones is projected at the architectural approach level— making it much easier to

## Martti Forsell

retain the clock rate of the design fixed as the number of processor cores increases.

**Fig. 2.** Block diagram of the NUMA approach. (*P*=number of processors, *F*=number of functional units,  $C_{net}$ =latency of the intercommunication network,  $D_{mem}$ =cycle time of the memory,  $U_p$ =utilization of processors,  $U_l$ =utilization of functional units.)

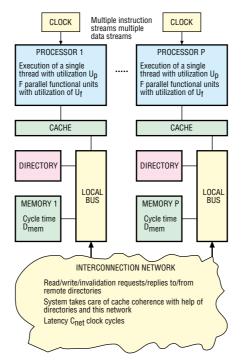

*Cache coherent non-uniform memory access* (CC-NUMA) is a variant of NUMA in which multiple processors with coherent caches and memory banks are connected together via a intercommunication network (memory is distributed, also remote memory is cached, coherence is managed by distributed directories, see Fig. 3) [Lenoski92]. Non-local memory accesses have higher (distance and traffic situation dependent) latency than local accesses. A typical CC-NUMA system consists of interconnected nodes, which have a processor, local caches and a local portion of main memory [Lenoski92, Agarwal95]. Introducing caching of remote memory leads to the issue of cache coherence. A cache line can have multiple copies distributed in all the caches in the system. Updating these cache

lines on writes to make the write visible to all processors in the system is no trivial task. The cache coherence protocol specifies how the memory is maintained coherent. CC-NUMA cache coherence protocols are typically based on directories to keep track of the cache line copies in the system. The local cache controller in each node must consult a directory to fetch the most recent copy of the cache line on cache misses. Cache coherence protocols are known to be complicated and require advanced cache controllers.

**Fig. 3.** Block diagram of the CC-NUMA variant. (*P*=number of processors, *F*=number of functional units,  $C_{net}$ =latency of the intercommunication network,  $D_{mem}$ =cycle time of the memory,  $U_p$ =utilization of processors,  $U_t$ =utilization of functional units.)

In our earlier performance evaluations and in an on-going efforts we model(ed) the performance and in some cases also silicon area and power consumption of different processor organizations in single and

# Martti Forsell

multiprocessor constellations, different approaches for TLP computing executing parametric benchmark application. In the following we summarize some findings/early results that reveal interesting things about the performance of the SMP and NUMA approaches with respect to other existing approaches and our proposals for efficient TLP-aware architectures:

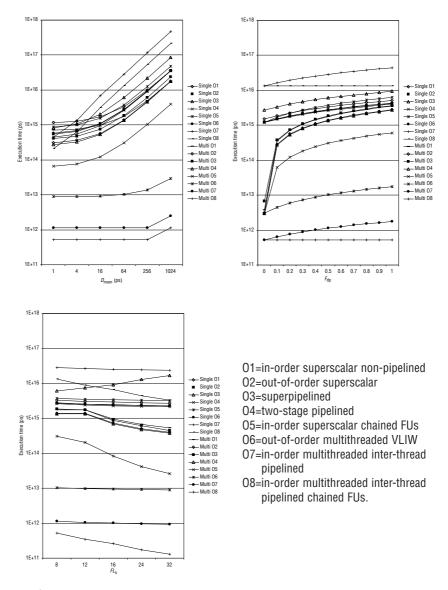

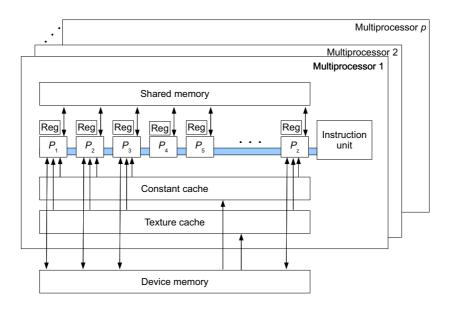

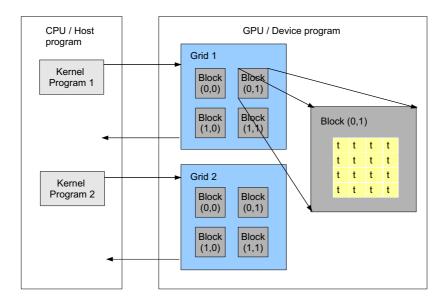

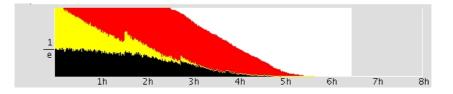

• In [Forsell02] we modeled analytically the performance of eight processor organizations in both single processor-memory and high-bandwidth multiprocessor constellations with different pipeline, ILP exploitation, and threading schemes (see Fig.4). With the used parameters, these models suggest that memory delays in multiprocessor systems are hidden best with multithreading and that the more dependencies the weaker performance except for the in-order multithreaded inter-thread pipelined chained FUs organization.

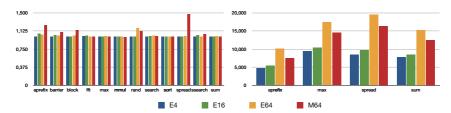

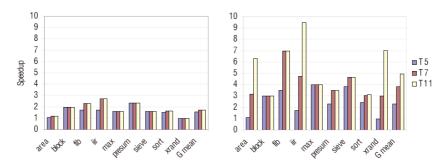

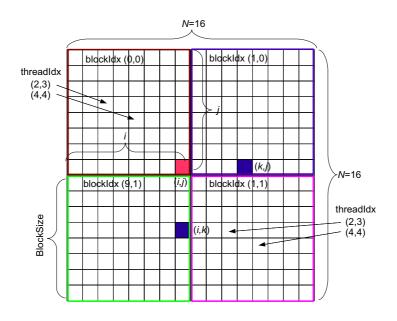

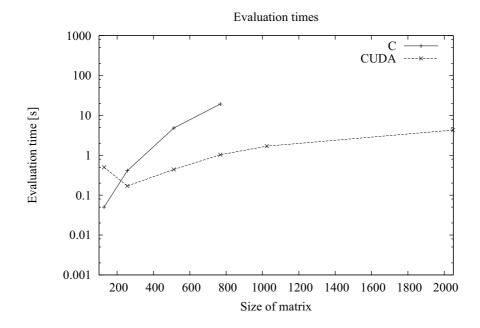

• In [Forsell11a] we measured the performance of multicore machines with different approaches to TLP, on-chip intercommunication topology, hashing schemes, and memory module organizations (see Fig. 5).

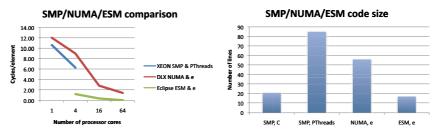

• In [Forsell11c] and related deliverables we are studying the performance of SMP, NUMA and ESM machines and code size with respect to different versions of parallel algorithms (see Fig. 6 for the very first results). The ESM approach makes use of the techniques explained in Sections 3-7 [Forsell06].

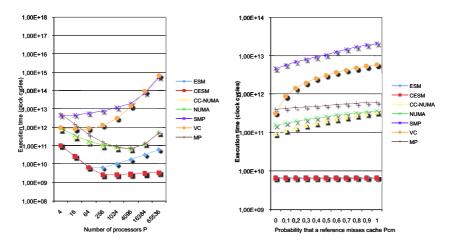

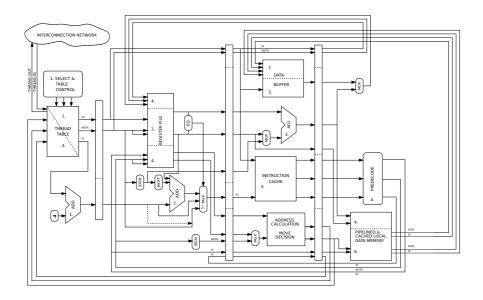

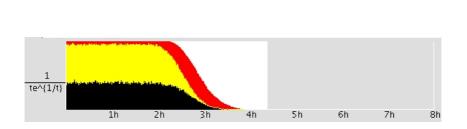

• In an on-going effort we are modeling analytically the performance of seven TLP approaches with a parametric workload (see Fig. 7 for early results). The ESM and CESM are approaches making use of the techniques explained in Sections 3-7 [Forsell06, Forsell09, Forsell10].

**Fig. 4.** Execution time as a function of the memory system delay  $D_{\text{mem}}$ , the fraction of dependent parallel code  $F_{\text{dp}}$ , and the number of pipeline segments  $FL_{\text{s}}$  in single and multiprocessor constellations of eight processor organizations. For more details, see [Forsell02].)

#### Martti Forsell

**Fig. 5.** Shared memory emulation overheads for certain simple functionalities optimized for MCRCW ESM and NUMA approaches. E4, E16 and E64 are 4, 16, and 64-core systems with a sparse mesh-based interconnect, M64 is a 64-core system with a multimesh interconnect, (For more details, see [Forsell11a].)

**Fig. 6.** Execution time and number of source code line of the aprefix benchmark in Xeon SMP using PThreads, DLX NUMA using the e-language and Eclipse ESM using the e-language. (For more details, see [Forsell11c].)

Since these studies are pointing to huge performance differences between the current SMP and NUMA approaches and new ESM and CESM approaches, we will take a closer look at computing and parallelism and architectural techniques needed to implement it efficiently. Generally speaking, the essence of parallel computing is to divide the computational problem at hand to subproblems that can be solved in parallel and to somehow solve the original problems with a help of these. This requires granting sufficient bandwidth for interprocessor communication, providing fast synchronization mechanism between subproblem executions, and making use of computational patterns that are specific to parallel computing only. These are discussed in the following four sections.

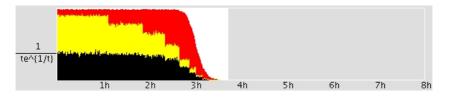

**Fig. 7.** Early estimations of the execution time of a parametric benchmark program as a function of number of processors (10% of code is sequential, 45% independent parallel, 45% dependent parallel, 20% of code is non-vectorizable, 10% accesses miss the cache, there are 8192 software threads) and the cache miss rate (10% of code is sequential, 45% independent parallel, 20% of code is non-vectorizable, there are 8192 software threads and 64 processors). (ESM=emulated shared memory, CESM=configurable emulated shared memory, CC-NUMA=cache coherent non-uniform memory access, NUMA=non-uniform memory access, VC=vector computing, MP=message passing)

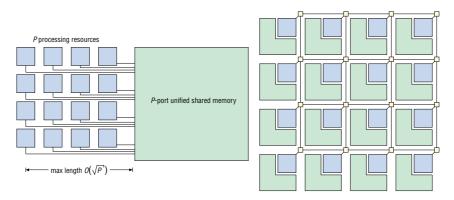

# 3. Hiding the latency

As explained in Section 2, shared memory can be unified or distributed. A simple lay-out analysis reveals that unified shared memory will lead to delays proportional to the square root of the number of processor cores slowing down the memory system clock cycle and/or increasing the latency with respect to that of distributed shared memory interconnected with a mesh-like network (see Fig. 8). Another problems is the implementation of multiported memory. According to our studies the wiring of P-ported memory takes  $P^2$  times more space than that of a single port memory of the same size. Thus, in the following we focus on distributed shared memory implementation.

#### Martti Forsell

Fig. 8.A unified shared memory and distributed shared memory organization.

Accessing the memory on a distributed shared memory system takes time for communication and memory access on the target module. There are two principal means for hiding the latency of the memory system caches and exploitation of parallel slackness.

Caches are small and fast associatively accessed memories that are widely used to balance the speed difference between processors and the main memory by keeping the potentially most frequently used data in the cache from which it can be quickly retrieved [Kilburn62]. In a case of a memory access, data is first searched from or stored to the cache. If it is found, a cache hit occurs and data can be delivered fast back to the processor. If data is not found, a cache miss occurs and an access to the slower main memory is performed. After the access is completed data is delivered to both the processor and stored into the cache so that further references to the same data can be performed faster. The main problem with caching applied to distributed shared memory is that if caches are placed in the front of the network, there is a need for cache coherency maintenance dropping the performance of the system with communication intensive algorithms [Lenoski28, Forsell10], or if caches placed in the behind of the network next to memory modules, they are not able to hide the latency of the intercommunication network.

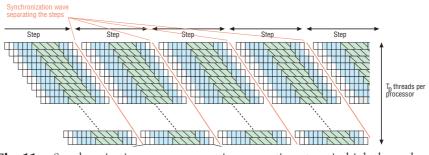

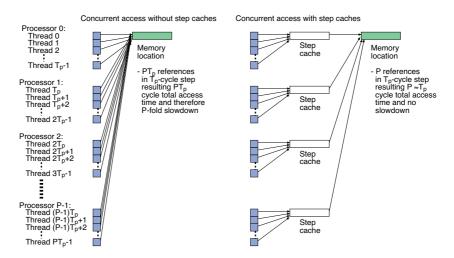

The idea of latency hiding with *exploitation of parallel slackness* (or *high-throughput computing*) is that if multiple (denoted with  $T_p$ ) threads

### Computer Architecture Re(de)fined

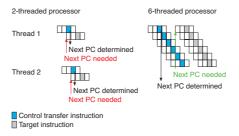

are assigned to a single physical processor it is possible to execute other threads while a thread is accessing memory or committing communication (see Fig. 9). Special multithreaded processors and a pipelined memory system are needed to implement this efficiently [Ranade91, Leppänen96, Sun05]. Another advantage of high-throughput computing is that it slows down the execution of individual threads which helps to eliminate the pipeline hazards that slow down execution in single threaded architectures except in the minimal pipeline architecture in which there are not hazards [Forsell96, Forsell02] (see Fig. 10).

**Fig. 9.**Single and multithreaded execution and latency hiding with parallel slackness in the latter.

**Fig. 10.** Increasing the number of threads per processor from 2 to 6 eliminates control hazards in a 4-stage pipeline.

The effect of using high-throughput computing instead of caching is shown in Fig. 4 for different processor organizations and in Fig. 7 for TLP different approaches.

# 4. Synchronization

Synchronization is one of the most expensive operations in current parallel architectures. Even in a small multicore machine using the SMP or NUMA paradigm, a barrier synchronization can easily take hundreds of clock cycles. This rules fine-grained parallel algorithms useless for these architectures. There exists, however, very efficient synchronization techniques, e.g. the *synchronization wave*, for high-throughput architectures dropping the cost of implicit synchronization down to  $1/T_p$  [Leppänen96] (see Fig.11).

**Fig. 11.** Synchronization waves separating execution steps in high-throughput computing.

In it special synchronization messages are sent by the processors to the memory modules and vice versa. The idea is that when a processor has sent all its messages belonging to a single step on their way, it sends a synchronization message. Synchronization messages from various sources push on the actual messages, and spread to all possible paths, where the actual messages could go. When a switch receives a synchronization message from one of its inputs, it waits, until it has received a synchronization message from all of its inputs, then it forwards the synchronization wave to all of its outputs. The synchronization wave may not bypass any actual messages and vice versa. When a synchronization wave sweeps over a network, all switches, modules and processors receive exactly one synchronization message via each input link and send exactly one via each output link. This kind of a cheap implicit synchronization

#### Computer Architecture Re(de)fined

makes it possible to emulate the easy-to-program PRAM abstraction [Fortune78] efficiently and therefore these architectures are called emulated shared memory machine (ESM).

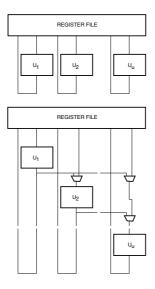

# 5. Exploitation of low-level parallelism

The amount of available ILP is often severely limited, especially if independent operations are not seek beyond the basic block boundaries [Jouppi89, Smith89, Forsell02]. Extracting larger amounts of ILP from a single threaded general purpose program is possible, but it requires very complex compilation algorithms like trace scheduling [Fisher81], superblock scheduling [Hank93] or percolation scheduling [Nicolau85, Moon93] seeking independent instructions across the boundaries of basic blocks. Even these advanced techniques fail, if instructions of the code are excessively dependent on each other. In high-throughput computing architectures it is possible to exploit ILP-style low level parallelism that often exists between the threads using the chained organization of functional units rather than traditional parallel organization [Forsell97] (see Fig. 12). The idea is to divide an instruction to a fixed number of subinstructions, which are executed in the corresponding functional units in a chain-like manner sequentially. This kind of technique, *chaining*, allows a unit to use the results of the preceding units so that a portion of strictly sequential subinstruction can be executed during a single instruction [Forsell97]. This is not possible with models based on parallel organization of functional units. We call the obtained ability to execute multiple subinstructions during a step as *virtual ILP*.

We have evaluated the effect of chaining both with analytic modeling [Forsell02] (see Fig. 4) and simulations [Forsell03] (see Fig. 13). Note that synchronous high-throughput computing works poorly with dynamic superscalar execution since the scheduler can easily change the ordering and timing of memory accesses so that the dependencies are violated and erroneous result is obtained.

### Martti Forsell

Fig. 12. Parallel and chained organization of functional units.

**Fig. 13.** Speedup of achieved by using parallel and chained organization of functional units with 5, 7 and 11 functional units per processor with respect to standard pipelined processor organization.

# 6. Concurrent memory access

Memory access is said to be *concurrent* if at least two processors are accessing the same location during the same step. Naturally, this kind of concurrence is meaningful only in the case of synchronous TLP execu-

#### Computer Architecture Re(de)fined

tion, e.g. in the synchronous high-throughput computing making use of parallel slackness in latency hiding and synchronization wave as described above but not in SMP and NUMA. According to the theory of parallel algorithms [Jaja92], concurrent memory accesses can be used to speed up execution by a logarithmic factor for a class of parallel algorithms. There are efficient techniques for concurrent memory access even if we limit the number of ports per memory module to one—namely combining and step caches [Keller01, Forsell05].

*Combining* is a technique in which memory references targeted to the same location are combined during routing so that traffic to the final destination is reduced [Ranade91]. Unfortunately, there is a need to sort the references made during a step of (multithreaded) execution on a processor prior sending them to the network, a need for machinery in the routers comparing references on their way to destinations, and a need to store combined read messages so that their common reply can be split back to actual replies targeted to processing resources [Keller01]. All this makes implementation of combining expensive and tricky.

Step caches [Forsell05] are special caches that operate like normal caches but data stored to a step cache remains valid only until the end of ongoing step of multithreaded execution during which the references are independent by the definition of parallel computing so that there is no need to maintain any kind of cache coherence. In a system with  $P T_{p}$ threaded processor cores, step caches help concurrent memory accesses by reducing the number of references per a location from  $PT_p$  to P, which allows the memory system to work without a noticeable performance penalty if  $T_p \ge P$  even if all the threads are referring to the same location in parallel (see Fig. 14). Compared to combining, step caches operate faster due to elimination of the sorting phase but require more parallelism and operate more arbitrarily, e.g. not preserving the ordering of memory references and thus making in more difficult to implement e.g. the Priority variant of the concurrent memory access aware PRAM in which the thread with the lowest id wins in the case of a concurrent write. Fig. 15 shows our simulation results [Forsell08a] for a step cached ESM as the speedups achieved with a help of concurrent memory access in the case of 4, 16 and 64 processor cores with respect to 4-core exclusive access.

**Fig. 14.** Concurrent memory access in high-throughput computing approach with and without step caches.

|         | E4   | C4    | E16  | C16    | E64   | C64     |

|---------|------|-------|------|--------|-------|---------|

| aprefix | 1.00 | 1.41  | 3.18 | 4.83   | 9.49  | 14.63   |

| max     | 1.00 | 1.38  | 3.16 | 4.74   | 12.75 | 16.31   |

| search  | 1.00 | 12.09 | 3.26 | 48.12  | 12.37 | 189.07  |

| spread  | 1.00 | 72.00 | 3.18 | 287.43 | 11.16 | 1136.46 |

| sum     | 1.00 | 1.41  | 3.18 | 4.83   | 11.13 | 14.63   |

**Fig. 15.** Speedup provided by concurrent memory access with respect to E4. (Ex=exclusive memory access with x processor cores, Cx=concurrent memory access with x processor cores)

# 7. Multioperations

According to the theory of parallel algorithms the logarithmic speedup provided by concurrent memory access (CRCW) can be extended to a wider set of algorithms if efficient implementation of multi(prefix)operations operations is provided for synchronous TLP machines [Jaja92]. A *multioperation* is a special operation involving participation of multiple

### Computer Architecture Re(de)fined

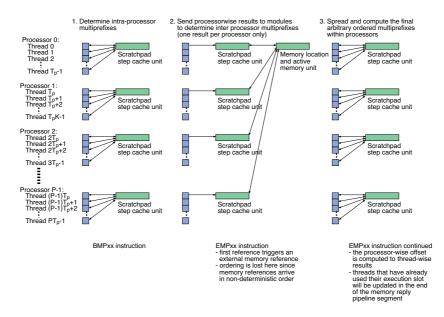

threads and a single memory location, e.g. summing up to P data values to a memory location in parallel. *Multiprefix operations* are like multioperations, but each processor receives a cumulative intermediate result of the operation. Both multioperations and multiprefix operations can be implemented in constant time with a combining networks technique [Ranade91] or with step caches/scratchpad and active memory units [Forsell06, Forsell11b]. The difference of combining and step cache/scratchpad-based techniques is that while the latter takes potentially less silicon area and performs faster in cases not requiring full concurrency, it is not able to provide unbounded number of concurrent ordered multiprefixes like combining. Fig. 16 illustrates an implementation of ordered multiprefix with a help of step caches, scratchpads and active memory unit ordering buffers. Fig. 17 shows our simulation results [Forsell08a] as the speedups achieved with a help of multioperations in the case of 4, 16 and 64 processor cores with respect to 4-core exclusive access without multioperations.

# 8. Conclusions

Based on our recent and on-going analysis of TLP execution techniques, we have tried to answer the question why the approaches used in current multicore machines, making use of performance enhancement techniques primarily developed for sequential computers, are not efficient in TLP execution. For that we have introduced alternative/new TLP-aware techniques that give much higher performance for many general purpose TLP computing patterns. The performance advantage comes from scalable latency hiding, radically faster synchronization, more efficient exploitation of low-level parallelism, and special synchronous TLP execution aware techniques like concurrent memory access and multi(prefix)operations. Thus, preliminary speaking we can say that high-throughput computing style interleaved multithreading could replace caching as a primary latency hiding mechanism for shared memory access but caching would remain important at the level of memory hierarchy related

### Martti Forsell

**Fig. 16.** Ordered multiprefix in high-throughput computing approach with and without step caches.

|         | E4   | M4    | E16  | M16    | E64   | M64     |

|---------|------|-------|------|--------|-------|---------|

| aprefix | 1.00 | 11.99 | 3.18 | 47.27  | 9.49  | 184.07  |

| max     | 1.00 | 9.85  | 3.16 | 39.05  | 12.75 | 151.90  |

| search  | 1.00 | 12.08 | 3.26 | 44.83  | 12.37 | 188.90  |

| spread  | 1.00 | 71.93 | 3.18 | 287.17 | 11.16 | 1135.45 |

| sum     | 1.00 | 14.39 | 3.18 | 56.02  | 11.13 | 221.74  |

**Fig. 17.** Speedup provided by multioperations. (Ex=exclusive memory access with x processor cores, Mx=multioperation and concurrent memory access aided execution with x processor cores)

accessing slower/secondary memories from distributed memory modules, and chained static virtual superscalar execution could replace dynamic superscalar execution as the most efficient techniques for lowlevel parallelism exploitation. Techniques not familiar from sequential nor current TLP machines—concurrent memory access and multioperations—could provide further boost enabling advanced parallel patterns. Likewise, techniques that would become less important include some standard pipeline hazard prevention mechanisms and speculations. Since

#### Computer Architecture Re(de)fined

this kind of elimination of performance bottlenecks makes it possible to use fine-grained TLP programming patterns efficiently, this will also simplify programming considerably. All this may considerably change the theory and practice of parallel computing in the near future.

Even though this paper is based on partially preliminary models and on-going work we believe that they point already relatively well at the right direction. Detailed and verified analytic performance models of TLP approaches and thorough discussion on implications of these will be published in the later phases of our research.

### References

- [Agarwal95] A. Agarwal et al., The MIT Alewife machine: Architecture and Performance, Proceedings of the 22nd annual international symposium on computer architecture (ISCA), 1995, pp. 2-13.

- [Bloch59] E. Bloch, The engineering design of the Stretch computer, Proceedings of the Fall Joint Computer Conference, 1959, 48-59.

- [Brooks00] D. Brooks, P. Bose, S. Schuster, H. Jacobson, P. Kudva, A. Buyuktosunoglu, J. Wellman, V. Zyuban, M. Gupta and P. Cook, Power-Aware Microarchitecture: Design and Modeling Challenges for Next Generation Microprocessors, IEEE Micro 20, 6 (November-December 2000), 26-32.

- [Bucholz62] W. Bucholz, Planning a Computer System: Project Stretch, McGraw-Hill, New York, 1962.

- [Culler99] D. Culler and J. Singh, Parallel Computer Architecture—A Hardware/ Software Approach, Morgan Kaufmann Publishers Inc., San Fransisco, 1999.

- [Fisher81] J. Fisher, Trace Scheduling: A Technique for Global Microcode Compaction, IEEE Transactions on Computers C-30, 7 (July 1981), 478-490.

- [Forsell96] M. Forsell, Minimal Pipeline Architecture-an Alternative to Superscalar Architecture, Microprocessors and Microsystems 20, 5 (1996), 277-284.

### Martti Forsell

- [Forsell97] M. Forsell, MTAC—A Multithreaded VLIW Architecture for PRAM Simulation, Journal of Universal Computer Science 3, 9 (1997), 1037-1055.

- [Forsell02] M. Forsell, Architectural differences of efficient sequential and parallel computers, Journal of Systems Architecture 47, 13 (July 2002), 1017-1041.

- [Forsell05] M. Forsell, Step Caches—a Novel Approach to Concurrent Memory Access on Shared Memory MP-SOCs, In the Proceedings of the 23th IEEE NORCHIP Conference, November 21-22, 2005, Oulu, Finland, 74-77.

- [Forsell06] M. Forsell, Realizing Multioperations for Step Cached MP-SOCs, In the Proceedings of the International Symposium on System-on-Chip 2006 (SOC'06), November 14-16, 2006, Tampere, Finland, 77-82.

- [Forsell08a] M. Forsell, On the performance and cost of some PRAM models on CMP hardware, In the Proceedings of the 10th Workshop on Advances in Parallel and Distributed Computational Models (in conjunction with the 22th IEEE International Parallel and Distributed Processing Symposium, IPDPS<sup>\*</sup>08), April 14, 2008, Miami, USA.

- [Forsell08b] M. Forsell, V. Leppänen and M. Penttonen, Rinnakkaistietokoneen uusi tuleminen, Tietojenkäsittelytiede 28, (Joulukuu2008), 55-65.

- [Forsell09] M. Forsell, Configurable Emulated Shared Memory Architecture for general purpose MP-SOCs and NOC regions, In the Proceedings of the 3rd ACM/IEEE International Symposium on Networks-on-Chip, May 10-13, 2009, San Diego, USA, 163-172.

- [Forsell10] M. Forsell, A PRAM-NUMA model of computation for addressing low-TLP workloads, in The Proceedings of the 12th Workshop on Advances in Parallel and Distributed Computational Models (in conjunction with the 24th IEEE International Parallel and Distributed Processing Symposium, IPDPS'10), April 19, 2010, Atlanta, USA, 1–8.

- [Forsell11a] M. Forsell, Performance comparison of some shared memory organizations for 2D mesh-like NOCs, Microprocessors and Microsystems 35, 2 (March 2011), 274-284.

# Ten Years of Bluetooth Security Attacks: Lessons Learned

Keijo Haataja, Konstantin Hyppönen, Pekka Toivanen School of Computing University of Eastern Finland P.O. Box 1627, 70211 Kuopio, Finland Keijo.Haataja@uef.fi, Konstantin.Hypponen@uef.fi, Pekka.Toivanen@uef.fi

**Abstract.** In this paper, a literature review based comparative analysis of Bluetooth security attacks over the past ten years (2001-2011) is provided. In addition, a new practical countermeasure against Man-In-The-Middle attacks on Bluetooth Secure Simple Pairing is proposed. Moreover, a novel attack that works against all existing Bluetooth versions is proposed. Furthermore, some new ideas that will be used in our future research work are presented.

#### **1** INTRODUCTION

*Bluetooth*<sup>1</sup> is a technology for short range wireless data and realtime two-way audio/video transfer providing data rates up to 24 Mb/s. Bluetooth operates at 2.4 GHz frequency in the free Industrial, Scientific, and Medical (ISM) band. Bluetooth devices that communicate with each other form a *piconet*. The device that initiates a connection is the piconet *master* and all other devices within that piconet are *slaves*.

Already in 2006, the one billionth Bluetooth device was shipped [1]. Less than five years later in 2011, the four billionth Bluetooth device was shipped<sup>2</sup>, and the volume is expected to increase rapidly in the near future. According to In-Stat, the eight billionth Bluetooth device is expected to be shipped by the end of 2013<sup>3</sup>. Therefore, it is very important to keep Bluetooth security issues up-to-

<sup>&</sup>lt;sup>1</sup>https://www.bluetooth.org/Technical/Specifications/adopted.htm

date.

**Our results**: In this paper, we provide a literature review based comparative analysis of Bluetooth security attacks over the past ten years (2001-2011). In addition, we propose a new practical countermeasure against Man-In-The-Middle (MITM) attacks on Bluetooth Secure Simple Pairing (SSP). Moreover, we propose a new practical attack that works against all existing Bluetooth versions. Furthermore, we present some new ideas that will be used in our future research work.

The rest of the paper is organized as follows. Section 2 gives an overview of Bluetooth security. A literature review based comparative analysis of Bluetooth security attacks over the past ten years (2001-2011) is provided in Section 3: the attacks are designed against Bluetooth versions up to 2.0+EDR (Enhanced Data Rate), but some of them work also against all existing Bluetooth versions up to 4.0. Since MITM attacks are also possible and dangerous against the latest SSP-enabled Bluetooth versions (i.e. Bluetooth versions 2.1+EDR – 4.0), MITM attacks on Bluetooth are explained in a separate attack section (Section 4). The section also provides a comparative analysis of the all existing Bluetooth MITM attacks over the past ten years (2001-2011). Section 5 proposes a new practical countermeasure against MITM attacks on SSP. A new practical attack that works against all existing Bluetooth versions is proposed in Section 6. Finally, Section 7 concludes the paper and sketches future work.

### 2 OVERVIEW OF BLUETOOTH SECURITY

The basic Bluetooth security configuration is done by the user who decides how a Bluetooth device will implement its connectability and discoverability options. The different combinations of connectability and discoverability capabilities can be divided into three categories, or *security levels:*<sup>1</sup> [1]

<sup>&</sup>lt;sup>2</sup>http://www.bluetooth.com/Pages/Press-Releases-Detail.aspx?ItemID=126

<sup>&</sup>lt;sup>3</sup>http://www.instat.com/press.asp?Sku=IN1104968MI&ID=3238

Ten Years of Bluetooth Security Attacks: Lessons Learned

- 1. *Silent:* The device will never accept any connections. It simply monitors Bluetooth traffic.

- 2. *Private:* The device cannot be discovered, i.e. it is a so-called *non-discoverable device*. Connections will be accepted only if the *Bluetooth Device Address (BD\_ADDR)* is known to the prospective master. A 48-bit BD\_ADDR is normally unique and refers globally to only one individual Bluetooth device.

- 3. *Public:* The device can be both discovered and connected to. It is therefore called a *discoverable device*.

Bluetooth security is based on building a chain of events, none of which should provide meaningful information to an eavesdropper. All events must occur in a specific sequence for security to be set up successfully. In order for two Bluetooth devices to start communicating, a procedure called *pairing* must be performed. As a result of pairing, two devices form a trusted pair and establish a link key which is used later on for creating a data encryption key for each session.<sup>1</sup> [1]

In Bluetooth versions up to 2.0+EDR, pairing is based exclusively on the fact that both devices share the same *Personal Identification Number (PIN)*, or *passkey*, that is used for generating several 128-bit keys. When the user enters the same passkey in both devices, the devices generate the same shared secret which is used for authentication and encryption of traffic exchanged by them. The PIN is the only source of entropy for the shared secret in Bluetooth versions up to 2.0+EDR. As the PINs often contain only four decimal digits, the strength of the resulting keys is not enough for protection against passive eavesdropping on communication. Even with longer 16-character alphanumeric PINs, full protection against active eavesdropping cannot be achieved: it has been shown that MITM attacks on Bluetooth communications (versions up to 2.0+EDR) can be performed [1-4].<sup>1</sup> [1]

Bluetooth versions 2.1+EDR, 3.0+HS (High-Speed), and 4.0 add a new specification for the pairing procedure, namely SSP<sup>1</sup>. Its

main goal is to improve the security of pairing by providing protection against passive eavesdropping and MITM attacks. Instead of using (often short) passkeys as the only source of entropy for building the link keys, SSP employs Elliptic Curve Diffie-Hellman (ECDH) public-key cryptography. To construct the link key, devices use public-private key pairs, a number of nonces, and Bluetooth addresses of the devices. Passive eavesdropping is effectively thwarted by SSP, as running an exhaustive search on a private key with approximately 95 bits of entropy is currently considered to be infeasible in short time.<sup>1</sup> [1]

In order to provide protection against MITM attacks, SSP either uses an OOB channel (e.g., Near Field Communication, NFC), or asks for the user's help: for example, when both devices have displays and keyboards, the user is asked to compare two six-digit numbers. Such a comparison can be also thought as an OOB channel which is not controlled by the MITM. If the values used in the pairing process have been tampered with by the MITM, the six-digit integrity checksums will differ with the probability of 0.999999.<sup>1</sup> [1]

SSP uses four *association models*. In addition to the two association models mentioned previously, *OOB* and *Numeric Comparison*, models named *Passkey Entry* and *Just Works* are defined. The Passkey Entry association model is used in the cases when one device has input capability, but no screen that can display six digits. A six-digit checksum is shown to the user on the device that has output capability, and the user is asked to enter it on the device with input capability. The Passkey Entry association model is also used if both devices have input, but no output capabilities. In this case the user chooses a 6-digit checksum and enters it in both devices. Finally, if at least one of the devices has neither input nor output capability, and an OOB cannot be used, the Just Works association model is used. In this model the user is not asked to perform any operations on numbers: instead, the device may simply ask the user to accept the connection.<sup>1</sup> [1]

SSP is comprised of six phases:<sup>1</sup> [1]

Ten Years of Bluetooth Security Attacks: Lessons Learned

- 1. *Capabilities exchange:* The devices that have never met before or want to perform re-pairing for some reason, first exchange their Input/Output (IO) capabilities to determine the proper association model to be used.

- 2. *Public key exchange:* The devices generate their public-private key pairs and send the public keys to each other. They also compute the Diffie-Hellman key.

- 3. *Authentication stage 1:* The protocol that is run at this stage depends on the association model. One of the goals of this stage is to ensure that there is no MITM in the communication between the devices. This is achieved by using a series of nonces, commitments to the nonces, and a final check of integrity checksums performed either through the OOB channel or with the help of user.

- 4. *Authentication stage 2:* The devices complete the exchange of values (public keys and nonces) and verify the integrity of them.

- 5. *Link key calculation:* The parties compute the link key using their Bluetooth addresses, the previously exchanged values, and the Diffie-Hellman key constructed in phase 2.

- 6. *LMP authentication and encryption:* Encryption keys are generated in this phase, which is the same as the final steps of pairing in Bluetooth versions up to 2.0+EDR.

Even though SSP improves the security of Bluetooth pairing, it has been shown that MITM attacks against Bluetooth 2.1+EDR, 3.0+HS, and 4.0 devices are also possible by forcing victim devices to use the Just Works association model [1,5–9]. Thus, the security of SSP should be further improved.

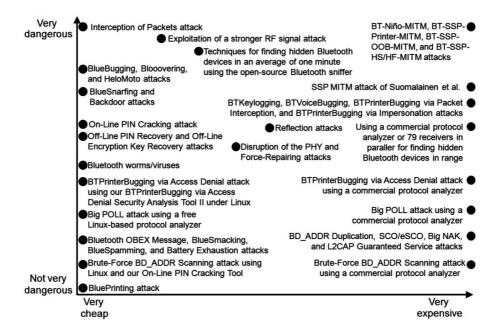

### 3 COMPARATIVE ANALYSIS OF BLUETOOTH SECURITY ATTACKS

Security threats in distributed networks (such as Bluetooth) can be divided into three categories: disclosure threat, integrity threat, and Denial-of-Service (DoS) threat. *Disclosure threat* means that information can leak from the target system to an eavesdropper that is not authorized to access the information. *Integrity threat* concerns the deliberate alteration of information in an attempt to mislead the recipient. *DoS threat* involves blocking access to a service, making it either unavailable or severely limiting its availability to an authorized user. Disclosure and integrity attacks typically compromise some sensitive information and therefore can be very dangerous, while DoS attacks typically only annoy Bluetooth network users and are considered to be less dangerous. [1,10]

Sections 3.1, 3.2, and 3.3 explain some typical disclosure, integrity, and DoS threats, respectively. Some typical threats which cannot be classified as only one single threat (so-called *multithreats*) are explained in Section 3.4.

#### 3.1 Disclosure Threats

*BlueSnarfing attack*<sup>4,5</sup> (also referred to as *BlueStumbling attack*) means that an attacker connects to the target device without alerting its owner and steals some sensitive information, such as entire phonebook, calendar notes, and text messages. At least three BlueSnarfing applications exist: Adam Laurie's *BlueSnarf*<sup>5</sup>, Ollie Whitehouse's *RedSnarf*<sup>6</sup>, and Bluediving Project's *Bluediving*<sup>7</sup>. The success of BlueSnarfing attack depends very much on the vendor's implementation of the Bluetooth protocol stack for the target device. Therefore, the attack works only if the protocol stack of the target device is poorly implemented, i.e. there are serious flaws in the authentication and data transfer mechanisms of some Bluetooth devices. A list of the devices known to be vulnerable to BlueSnarfing attack

without firmware/software update can be found in <sup>5</sup>. [1]