### University of Groningen

### Charge transport in high-performance ink-jet printed single-droplet organic transistors based on a silvlethynyl substituted pentacene/insulating polymer blend

Li, Xiaoran; Smaal, Wiljan T.T.; Kjellander, Charlotte; Putten, Bas van der; Gualandris, Kevin; Smits, Edsger C.P.; Anthony, John; Broer, Dirk J.; Blom, Paul W.M.; Genoe, Jan Published in: Organic Electronics

DOI: 10.1016/j.orgel.2011.04.020

IMPORTANT NOTE: You are advised to consult the publisher's version (publisher's PDF) if you wish to cite from it. Please check the document version below.

Document Version Publisher's PDF, also known as Version of record

Publication date: 2011

Link to publication in University of Groningen/UMCG research database

Citation for published version (APA): Li, X., Smaal, W. T. T., Kjellander, Ć., Putten, B. V. D., Gualandris, K., Smits, E. C. P., ... Gelinck, G. (2011). Charge transport in high-performance ink-jet printed single-droplet organic transistors based on a silylethynyl substituted pentacene/insulating polymer blend. Organic Electronics, 12(8), 1319-1327. DOI: 10.1016/j.orgel.2011.04.020

#### Copyright

Other than for strictly personal use, it is not permitted to download or to forward/distribute the text or part of it without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license (like Creative Commons).

Take-down policy If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from the University of Groningen/UMCG research database (Pure): http://www.rug.nl/research/portal. For technical reasons the number of authors shown on this cover page is limited to 10 maximum.

Contents lists available at ScienceDirect

### **Organic Electronics**

journal homepage: www.elsevier.com/locate/orgel

### Charge transport in high-performance ink-jet printed single-droplet organic transistors based on a silylethynyl substituted pentacene/insulating polymer blend

Xiaoran Li<sup>a,b</sup>, Wiljan T.T. Smaal<sup>a</sup>, Charlotte Kjellander<sup>a</sup>, Bas van der Putten<sup>a</sup>, Kevin Gualandris<sup>a</sup>, Edsger C.P. Smits<sup>a</sup>, John Anthony<sup>c</sup>, Dirk J. Broer<sup>b</sup>, Paul W.M. Blom<sup>a</sup>, Jan Genoe<sup>d</sup>, Gerwin Gelinck<sup>a,\*</sup>

<sup>a</sup> Holst Centre/TNO, High Tech Campus 31, Eindhoven 5656 AE, The Netherlands

<sup>b</sup> Department of Chemical Engineering and Chemistry, Eindhoven University of Technology, P.O. Box 513, Eindhoven 5600 MB, The Netherlands

<sup>c</sup> Department of Chemistry, University of Kentucky, Lexington, KY 40506, USA

<sup>d</sup> Department of Large Area Electronics, imec vzw, Kapeldreef 75, Leuven B3001, Belgium

#### ARTICLE INFO

Article history: Received 29 November 2010 Received in revised form 23 February 2011 Accepted 27 April 2011 Available online 10 May 2011

Keywords: Blend Organic transistor Substituted pentacene Single-droplet ink-jet printing Contact barrier

#### 1. Introduction

### ABSTRACT

We present a systematic study of the influence of material composition and ink-jet processing conditions on the charge transport in bottom-gate field-effect transistors based on blends of 6,13-bis(triisopropyl-silylethynyl) pentacene (TIPS-PEN) and polystyrene. After careful process optimizations of blending ratio and printing temperature we routinely can make transistors with an average mobility of 1 cm<sup>2</sup>/Vs (maximum value 1.5 cm<sup>2</sup>/Vs), on/off ratio exceeding 10<sup>7</sup>, and sharp turn-on in current (sub-threshold slopes approaching 60 mV/decade). These characteristics are superior to the TIPS-PEN only transistors. Using channel scaling measurements and scanning Kelvin probe microscopy, the sharp turn-on in current in the blends is attributed to a contact resistance that originates from a thin insulating layer between the injecting contacts and the semiconductor channel. © 2011 Elsevier B.V. All rights reserved.

Mixing of two or more material components is a common industrial route to produce materials with tailor-made properties such as improved stiffness, impact strength, permeability, and/or electrical and optical properties. Polymer/ polymer blends are commonly used as the active layer in organic solar cells [1,2]. Goffri et al. made organic transistors in which the active layer was a two-component blend based on polythiophenes and different insulating polymers [3]. This concept has also been applied successfully for smallmolecule organic semiconductors such as 6,13-bis(triisopropyl-silylethynyl) pentacene (TIPS-PEN), blended with insulating or other semiconducting polymers [4,5]. Depending on the active materials, process conditions, and taking into account the thermodynamical driving force towards the most energetically favorable state and that most of the parent components in the blend are thermodynamically immiscible or partially-miscible, a vertical stratified morphology was achieved that leads to mobilities in field-effect transistors as high as the devices based on pure semiconductors, or even higher [5,6]. In most previous studies, blends were either spin-cast [7-9] or drop-cast [10,11]. High mobility (>1 cm<sup>2</sup>/Vs) transistors were reported only in the top-gate device geometry when spincasting a small-molecule organic semiconductor blended with a semiconducting polymer [7,12–14]. These techniques require additional patterning steps after deposition if the transistors were to be integrated into circuits or display backplanes.

With drop-on-demand ink-jet printing the materials can be deposited locally, resulting in efficient material

<sup>\*</sup> Corresponding author. Tel.: +31 (0)40 4020448; fax: +31 (0)40 4020699.

E-mail address: gerwin.gelinck@tno.nl (G. Gelinck).

<sup>1566-1199/\$ -</sup> see front matter  $\circledcirc$  2011 Elsevier B.V. All rights reserved. doi:10.1016/j.orgel.2011.04.020

usage and a simpler process for device integration [15]. The challenge is to print well-defined structures from dilute inks. By blending the molecular semiconductor with a polymer, the viscosity of the printing solution can be varied. Blending, however, is also expected to impact the electrical performance of the final deposited transistor. This interplay is in fact the topic of this paper.

Two different approaches of ink-jet printing small-molecule semiconductors have been used: printing multiple droplets which coagulate into a film covering a relatively large area on the substrate, or single-droplet printing where each droplet forms an individual functional deposit. The former was adopted in a recent study by Madec et al. [16]. They ink-jet printed multiple droplets of inks containing TIPS-PEN and an amorphous and electrically insulating polymer, polystyrene (PS), at a blending ratio of 1/1 (w/w). By printing from a specific binary solvent mixture and/or using a multilayer printing method, a continuous layer with improved morphology was achieved, and they found an increased mobility of up to  $10^{-2}$  cm<sup>2</sup>/Vs (±71-80% variance) in bottom-gate/top-contact transistors. These mobilities are however much lower than the values of  $0.12 \text{ cm}^2/\text{Vs}$  reported by Lim et al. [17] for single-droplet printing of pure TIPS-PEN from a solvent mixture, making it thus far unclear if blending with an insulating polymer can result in a further improvement in high-performance ink-jet printed transistors.

In this paper, we investigate single-droplet ink-jet printing of TIPS-PEN/PS blends, with each printed single droplet being an individual transistor [6,18]. This eliminates the need for additional patterning steps. As in the previous work of Lim [17], we use a bottom-gate/bottomcontact device geometry. This device architecture offers a straightforward route for downscaling of the transistor channel length to a few micrometers. In contrast to Lim's work, we did not rely on the unusual concentric ring arrangement of source and drain electrodes, because that configuration does not allow simple device integration. Here, we use conventional interdigitated comb structure for the source and drain electrodes.

To gain insight into the charge-transport properties of our devices, we study the differences between the transistors based on pure TIPS-PEN and TIPS-PEN/PS blends with respect to macroscopic device operation and local chargetransport properties, by using channel scaling studies and surface potential profilometry, respectively, and relate them to the morphology of the devices. The fundamental understanding of device operation obtained for our blend transistors provides valuable guidelines to the development of next generation transistors based on small-molecule semiconductor and insulating polymer blends.

#### 2. Experimental

6,13-Bis(triisopropyl-silylethynyl)pentacene (TIPS-PEN) was synthesized according to literature [19]. Polystyrene (PS), Mw = 9.58 kDa (Mn = 9.32 kDa, PDI = 1.03), was purchased from Fluka. 1,2,3,4-tetrahydronaphtalene (tetralin, purchased from Merck) was used as the solvent.

An ink-jet printing setup with a high-precision vertical translation stage and a Microfab glass nozzle (type MJ-ATP-01-50-DLC, 50  $\mu$ m orifice diameter) was used to

print inks with a constant TIPS-PEN concentration of 20 mg/ml and varied PS concentrations according to their blending weight ratios. Each droplet with a typical volume of 50 pL was jetted on demand and aligned to the transistor channel region to form an individual device, on substrates that were kept at 70 or 20 °C. All printing experiments were performed in ambient cleanroom conditions.

Bottom-contact/bottom-gate transistors were printed on Si (n++)/SiO<sub>2</sub> substrates with an oxide thickness of 140 nm and photolithographically patterned Au as source and drain electrodes. A pentafluorobenzenethiol monolayer was deposited on Au electrodes [20]. The SiO<sub>2</sub> was treated with trichlorophenylsilane. The transistor channel length was varied between 2 and 40 µm. Device characteristics were measured at room temperature in inert atmosphere using an Agilent 4155C semiconductor parameter analyser. The field-effect mobilities of our transistors in linear ( $\mu_{lin}$ ) and saturation ( $\mu_{sat}$ ) regime were calculated from the two equations as follows, with  $V_{DS} = -1$  V and -10 V, respectively [21]:

$$\mu_{lin}(V_G) = \frac{L}{W \cdot C_i} \frac{1}{V_{DS}} \left( \frac{\partial I_{SD}}{\partial V_G} \right) \tag{1}$$

$$\mu_{sat}(V_G) = \frac{2L}{W \cdot C_i} \left( \frac{\partial \sqrt{I_{SD}(V_G)}}{\partial V_G} \right)^2$$

(2)

where  $C_i$  is the capacitance per unit area of the gate dielectric layer, and *L* and *W* are channel length and width, respectively. The threshold voltage ( $V_{th}$ ) of our devices is extracted by extrapolating the square root (SQRT) of  $|I_{SD,sat}|$  vs.  $V_G$  plot to  $I_{SD,sat} = 0$  (as depicted in the plots in Fig. 1a). The sub-threshold slope (*SS*) value was calculated from the measured  $I_{SD}$  values over more than two decades above noise level, using the following equation:

$$SS = \frac{V_{G_1} - V_{G_2}}{\log_{10} \left(\frac{I_{SD_1}}{I_{SD_2}}\right)}$$

(3)

Optical micrographs were taken on a Leica DM2500M Microscope with cross-polarizers. SKPM was performed using a Veeco Dimension 3100 with a NanoScope IVa controller operating in the lift mode. For the comparison of contact resistance in the pure and blend transistors, a maximized scan size of  $80 \times 80 \ \mu m^2$  was used here to span over three active channels in the transistors to rule out any local effects. To avoid any effect of morphological anisotropy due to the direction of crystal growth from periphery towards centre of the droplets, the scanning regions of SKPM on two groups of devices (pure vs. blend) were chosen at the same location relative to the exact centre of the droplets, and with the same scanning direction with respect to the orientation of interdigitated electrodes of the devices. First, the height profile was recorded with tapping-mode atomic force microscopy (AFM). In the second pass the tip is lifted at a fixed height of 50 nm above the surface, and a voltage is applied to the tip, to record the local surface potentials. Several effects can influence the accuracy of SKPM measurements, e.g. the distance between SKPM tip and the sample surface, the geometry of the tip and cantilever, and the relative in-plane positioning of the cantilever with respect to the interdigitated electrodes of transistors

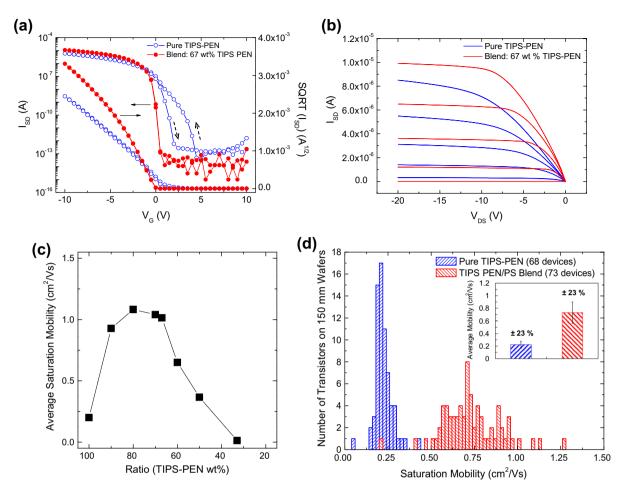

**Fig. 1.** (a) Transfer characteristics in saturation regime ( $V_{DS} = -10$  V) for two representative transistors with pure TIPS-PEN channel (open circles in blue) and blend channel of 67 wt.% TIPS-PEN and 33 wt.% PS (solid circles in red). Channel length and width are 10 and 200 µm, respectively. The two dashed arrows indicate the counter-clockwise hysteresis for the pure device (gate swept from +10 V  $\rightarrow -10$  V  $\rightarrow +10$  V). The plot of the square root (SQRT) of  $I_{SD}$  vs.  $V_G$  was used to extract mobility as well as the threshold voltage ( $V_{th}$ ): the blend device shows a mobility of  $1.04 \text{ cm}^2/\text{Vs}$  and a near-zero  $V_{th}$ , while the pure one has a mobility of 0.29 cm<sup>2</sup>/Vs and a  $V_{th}$  of 2.5 V. (b) Output characteristics of the same two transistors as shown in (a).  $V_G$  was varied between 0 and -10 V at a step of -2.5 V. (c) Average saturation mobilities as a function of TIPS-PEN weight ratios in TIPS-PEN/PS blend transistors (averaged from >10 devices for each ratio). All devices were printed on 15 mm × 15 mm square substrates at 70 °C. (d) Histograms of saturation mobilities of 8 pure TIPS-PEN transistors and 73 blend (67 wt.% TIPS-PEN) transistors printed on 150 mm wafers. The inset shows their average mobility values. The relative variance (standard deviation divided by the average value) is 23% for pure TIPS-PEN as well as the blend devices. Transistors were printed at 70 °C. Channel length and width are 5 and 1400 µm, respectively. (For interpretation of the references to color in this figure legend, the reader is referred to the web version of this article.)

[22–24]. The accuracy of our SKPM measurements is comparable to earlier reports on working organic transistors [22,25,26], with observed voltage drop from source to drain electrodes slightly lower than the actual bias applied ( $V_{DS}$ ). Here we tend to attribute this smaller measured potential drops to the effect of non-local coupling between the entire cantilever/tip and the microscopic device surface, and/or a relatively high tip-sample distance of 50 nm in our measurements [23,24,27,28].

#### 3. Results and discussion

# 3.1. Effect of insulating polymer (PS) on transistor device performance

Our transistors were independently processed over a period of 14 months on substrates that were prepared

under identical conditions. Over time no significant drift in transistor parameters was observed. Representative transfer characteristics in saturation ( $V_{DS} = -10$  V) for pure TIPS-PEN transistors printed at 70 °C are shown in Fig. 1a (open circles in blue). Non-ideal sub-threshold behavior was observed in the form of 'shoulder-like' ISD, with an obvious hysteresis between the forward and backward sweeps. This phenomenon was also reported by Lee et al. [29]. The average saturation mobility of pure TIPS-PEN transistors is 0.20 cm<sup>2</sup>/Vs, comparable with earlier reports of ink-jet printing pure TIPS-PEN [6,17]. Adding a polymer binder to the pure TIPS-PEN ink dramatically improves the device characteristics (solid circles in red, Fig. 1a): the transistors switch on sharply at  $\sim 0$  V, the on-current and mobility are higher than the pure TIPS-PEN devices and no hysteresis is observed. The sharp turn-on is a desirable device property for a switching transistor as it allows high-speed and low-power operation. Typical output characteristics for pure TIPS-PEN and blend (67% TIPS-PEN) transistors are compared in Fig. 1b. No notable non-linearity of  $I_{SD}$  is observed for the pure or blend transistor; not even when the output characteristics are plotted in the form of  $\Delta I_{SD}/\Delta V_{DS}$  vs.  $V_{DS}$  (graphs not shown). Next, we found that the device mobility is a function of relative weight ratio of TIPS-PEN/PS (Fig. 1c). For blends with 90-67 wt.% of TIPS-PEN, the average mobility has increased up to  $\sim 1 \text{ cm}^2/\text{Vs}$ , a factor of 5 higher than the pure TIPS-PEN (0.20 cm<sup>2</sup>/Vs). At lower concentration of TIPS-PEN (e.g. 60 wt.%) the mobility decreases. The average value and standard deviation of mobility ( $\mu$ ) in linear and saturation regime, on-current  $(I_{on})$ , and on/off ratio  $(I_{on}/I_{off})$  for transistors (channel length: 10  $\mu$ m, on 15 mm  $\times$  15 mm square substrates) printed at 70 °C with different blending ratios are summarized in Table 1. At a processing temperature of 20 °C we obtain typically lower device performance (Table 2). To further study large area uniformity, we printed 68 pure TIPS-PEN and 73 blend (67 wt.% TIPS-PEN) transistors with a channel length of 5 µm on 150 mm diameter wafers at 70 °C. The histograms in Fig. 1d clearly demonstrate enhanced mobilities of our blend transistors over the entire wafer, with the relative variance (standard deviation divided by the average value) at the same level as the pure TIPS-PEN devices (±23% in the inset of Fig. 1d). This demonstrates the potential of our blend inks for applications in large-area and low-cost organic electronics.

The observation that the mobility is increased by the presence of an insulator up to a critical blending ratio demonstrates that introducing an insulating polymer does not negatively affect the charge transporting layer in the device. This implies that in particular the composition and morphology of the first few nanometers of our TIPS-PEN/ PS blend are similar to that of pure TIPS-PEN, as charge transport takes place at this zone in the semiconductor layer [30]. Similar behavior was recently reported for spin-cast blends of TIPS-PEN with  $poly(\alpha$ -methylstyrene) [8,9], and blends of TIPS-PEN or fluorinated 5,11-bis(triethvlsilylethynyl) anthradithiophene (diF TES-ADT) with a semiconducting polymer, polytriarylamine [7,12]. The results were explained by the occurrence of vertical stratification upon casting and solvent evaporation. During solvent drying TIPS-PEN is predominantly expelled to both top and bottom interfaces of the deposited films [8,9,12]. As long as phase separation leads to almost pure phase of

X. Li et al. / Organic Electronics 12 (2011) 1319-1327

Summary of transistor parameters for TIPS-PEN/PS transistors with different blending ratios printed on 15 mm × 15 mm square substrates at 20 °C, under the same processing conditions. Field-effect mobilities were extracted in linear ( $\mu_{lin}$ ) and saturation ( $\mu_{sat}$ ) regime, on-current ( $I_{on}$ ) was measured at  $V_{C} = -10$  V, with  $V_{DS} = -10$  V. Data was obtained for >10 transistors of each ratio.

| Ratio (TIPS-PEN wt.%) | $\mu_{lin}  (\mathrm{cm}^2/\mathrm{Vs})$ | $\mu_{sat}$ (cm <sup>2</sup> /Vs) | $I_{on}$ ( $\mu A$ ) |

|-----------------------|------------------------------------------|-----------------------------------|----------------------|

| 100                   | $0.17 \pm 0.03$                          | $0.15 \pm 0.05$                   | $4.4 \pm 0.9$        |

| 67                    | 0.53 ± 0.13                              | $0.55 \pm 0.14$                   | 7.8 ± 1.7            |

| 50                    | $0.58 \pm 0.47$                          | $0.65 \pm 0.51$                   | 8.3 ± 6.6            |

| 33                    | $0.02 \pm 0.02$                          | $0.04 \pm 0.04$                   | $0.3 \pm 0.3$        |

TIPS-PEN at the two interfaces, it should be possible to realize transistors with good performance. This hypothesis can explain why the mobility decreases at too high weight fraction of the polymer in our blends: phase separation is incomplete and no continuous film of TIPS-PEN is formed at the bottom interface of our devices. It can however not explain why the maximum mobility of the blends is higher than that of the pure TIPS-PEN transistors. At least two explanations have been proposed for the improved charge transport in the blend transistors. Ohe et al. suggested that the addition of polymer binder leads to slower drying and hence to a different morphology of the TIPS-PEN film [9]. Yoon et al. proposed that the polymer binder influences the film formation process of the small-molecule organic semiconductors and acts indirectly as a purification method [31].

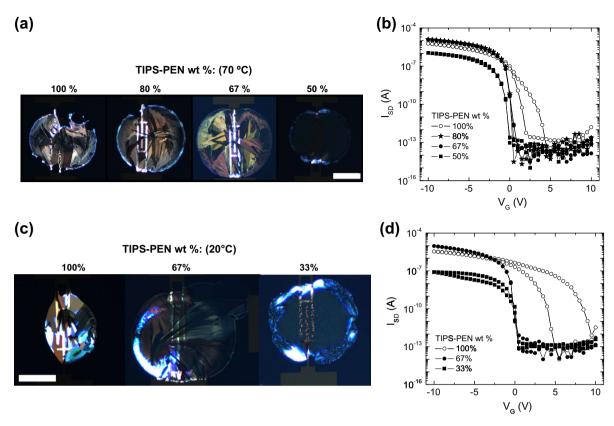

Typical optical micrographs (cross-polarized reflection mode) in Fig. 2a present the morphology evolution of TIPS-PEN/PS blends printed at 70 °C, with TIPS-PEN weight ratios ranging from 100% to 50%. Pure TIPS-PEN devices have irregular shaped crystalline deposit attributed to the de-pinning of the contact line during solvent drying (image of 100 wt.%). leading to limited crystal coverage on transistor channels. The addition of PS up to  $\sim$ 40% gives circular deposits with large crystals of TIPS-PEN that cover the whole device area with an improved crystal morphology (images of 80 and 67 wt.% of TIPS-PEN). Devices with this type of morphology have high mobility. At further higher concentration of PS, small and isolated TIPS-PEN crystals in a matrix of amorphous materials are observed (images of 50 wt.%). The lack of crystalline TIPS-PEN in this deposit explains the lower transistor performance and large parameter spread (Table 1). Corresponding transfer characteristics for the four transistors of Fig. 2a are compared in

Table 1

Summary of transistor parameters for TIPS-PEN/PS transistors with different blending ratios printed on 15 mm × 15 mm square substrates at 70 °C, under the same processing conditions. Field-effect mobilities were extracted in linear ( $\mu_{lin}$ ) and saturation ( $\mu_{sat}$ ) regime, on-current ( $I_{on}$ ) and off-current were measured at  $V_G = -10$  V and +10 V, respectively, with  $V_{DS} = -10$  V. Data was obtained for >10 transistors of each ratio.

| Ratio (TIPS-PEN wt.%) | $\mu_{lin}$ (cm <sup>2</sup> /Vs) | $\mu_{sat}$ (cm <sup>2</sup> /Vs) | <i>I</i> <sub>on</sub> (μA) | On/off ratio                          |

|-----------------------|-----------------------------------|-----------------------------------|-----------------------------|---------------------------------------|

| 100                   | 0.23 ± 0.06                       | $0.20 \pm 0.07$                   | 4.5 ± 1.1                   | $4.9\times10^6\pm3.0\times10^6$       |

| 90                    | $0.72 \pm 0.14$                   | 0.93 ± 0.23                       | 8.6 ± 1.7                   | $1.2\times10^7\pm1.0\times10^7$       |

| 80                    | $0.90 \pm 0.14$                   | $1.08 \pm 0.16$                   | $9.4 \pm 1.7$               | $3.0\times10^7\pm1.8\times10^7$       |

| 70                    | $0.83 \pm 0.22$                   | $1.04 \pm 0.26$                   | $9.7 \pm 2.8$               | $2.9\times10^7\pm1.7\times10^7$       |

| 67                    | $0.85 \pm 0.09$                   | $1.01 \pm 0.12$                   | $10.8 \pm 1.3$              | $4.9\times10^7\pm2.3\times10^7$       |

| 60                    | 0.53 ± 0.24                       | 0.66 ± 0.30                       | 5.7 ± 2.5                   | $3.8 \times 10^7 \pm 6.6 \times 10^7$ |

| 50                    | $0.30 \pm 0.27$                   | 0.37 ± 0.33                       | $3.6 \pm 3.4$               | $2.2 \times 10^7 \pm 3.1 \times 10^7$ |

| 33                    | 0.005 ± 0.003                     | $0.01 \pm 0.009$                  | $0.06 \pm 0.04$             | $2.1 \times 10^5 \pm 1.6 \times 10^5$ |

**Fig. 2.** (a) Representative cross-polarized optical micrographs showing the morphology transition of TIPS-PEN/PS blends with different TIPS-PEN concentrations printed at 70 °C. The scale bar indicates 100  $\mu$ m. (b) Transfer characteristics in saturation regime ( $V_{DS} = -10$  V) for transistors corresponding to the optical micrographs in (a). (c) Representative cross-polarized optical micrographs showing the morphology transition of TIPS-PEN/PS blends printed at 20 °C with decreased TIPS-PEN weight ratio from 100% to 33%. The scale bar indicates 100  $\mu$ m. (d) Transfer characteristics in saturation regime ( $V_{DS} = -10$  V) for the three transistors corresponding to the optical micrographs in (c).

Fig. 2b. Similar trends in contact-line pinning, transition of crystal morphology, and transistor performance as a function of polymer content were also observed when printing at a lower substrate temperature of 20 °C (Fig. 2c and d). The de-pinning effect, however, is more dominant for 20 °C: the lack of positioning control with ill-defined crystal coverage on transistor channels results in their lower device performance and larger spread (Table 2).

#### 3.2. Channel scaling studies

In relation to the phase separation mentioned above, the steep on-switch of current ( $I_{SD}$ ) of the blend devices is also informative. Steep sub-threshold slopes are observed for all blend transistors, i.e. independent of the TIPS-PEN/PS ratios and process temperatures. Steep sub-threshold slope and low threshold voltage ( $V_{th}$ ) are usually taken as evidence of a high quality gate dielectric-semiconductor interface with few charge trapping centers [32,33]. This suggests that the polymer binder modifies the interface either directly, for instance, by forming a very thin wetting layer between the silane-treated dielectric and the molecular semiconductor, or indirectly, by influencing the molecular packing of the semiconductor leading to fewer grain boundaries. Meanwhile, reduced charging

effects at the top surface of the semiconductor channel ('backchannel effect') by the passivation/encapsulation of phase-separated insulating polymer can also explain the improved characteristics [29]. Although these explanations can play a role also in our blend devices, we propose a third explanation below.

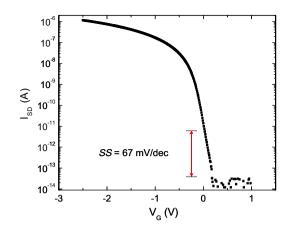

The sub-threshold slope in most blend transistors is very close to the theoretical minimum of 60 mV/decade (=  $kT/q \times ln10$ ) for an Ohmic charge injection from a metal into a semiconductor at room temperature [34,35]. Fig. 3 shows a representative sub-threshold slope as steep as 67 mV/decade in saturation regime for a blend transistor, calculated over more than 2 decades of  $I_{SD}$ . This points towards the existence of a tunneling barrier at the metal contacts, which is characterized by a highly non-linear *I*–*V* behavior in transfer characteristics [35–38].

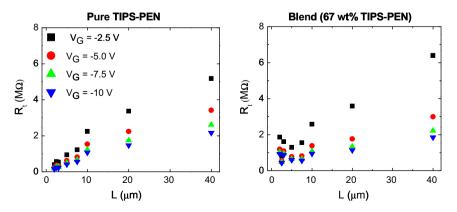

We measured the channel length (*L*) dependence of the total resistance ( $R_t = V_{DS}/I_{SD}$ ) at different gate biases ( $V_G$ ) in linear regime ( $V_{DS} = -1$  V) for two groups of transistors: pure TIPS-PEN vs. blend (67 wt.% TIPS-PEN) (Fig. 4). For the sake of comparison we choose the device series to have similar extracted mobilities. This implies that this group of blend transistors has below-average mobilities. As compared in Fig. 4,  $R_t$  decreases linearly with *L* for the pure transistors, down to a channel length of 2 µm. In contrast,

**Fig. 3.** A representative TIPS-PEN/PS blend (67 wt.% TIPS-PEN) transistor showing the extremely steep sub-threshold slope (*SS*) of 67 mV/decade in saturation regime ( $V_{DS} = -10$  V). The *SS* value was calculated from the measured  $I_{SD}$  values over more than two decades above noise level, as indicated by the red arrows. The *I*–V curve was measured with 0.01 V increment per step of  $V_{C}$ . (For interpretation of the references to color in this figure legend, the reader is referred to the web version of this article.)

for the blend transistors,  $R_t$  does not decrease further if we decrease *L* below 10 µm, illustrating the importance of a parasitic contact resistance,  $R_{sd}$ , in series with the channel resistance. Apparently the influence of  $R_{sd}$  for the extraction of intrinsic channel mobility is substantial for the blend but relatively small for the pure TIPS-PEN transistors. From similar analysis for other blend device series, we know that in all cases the blend transistors are influenced by contact resistance (contact limited) and that the variation in  $R_{sd}$  is one of the major causes for the variation in mobility reported in Table 1. This makes it particularly relevant to study the origin of the parasitic contact resistance.

#### 3.3. Contact resistance identified by SKPM

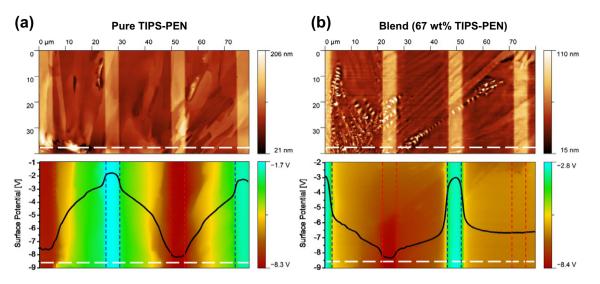

To study the origin of parasitic contact resistance in our devices and correlate it to local charge-transport properties, scanning Kelvin probe microscopy (SKPM) measurements were performed during device operation [39]. As shown in the potential image of Fig. 5a, the pure TIPS-PEN transistors show typical parabolic potential profiles from source to drain electrodes when devices were operated in saturation regime, with a small voltage drop at the source electrode, <15% relative to the voltage drop across the channel. Some negligible potential steps along the channel can be discerned and attributed to the grain boundary effects (see corresponding topography image in Fig. 5a), in line with previous studies [25]. In contrast, the potential profiles of the blend (67 wt.% TIPS-PEN) transistors show significant voltage drops at the electrodes (Fig. 5b). Because >80% of the voltage drastically drops at the source electrodes, the profile inside the channel is absent of details.

This high-Ohmic spatial zone close to the source electrodes of blend devices suggests a substantial barrier for charge injection from the contacts into the channels. Based on the potential profiles in Fig. 5, we can quantitatively compare the contact resistance ( $R_{sd}$ ) for pure and blend devices operated at the 'on-state' (bias conditions:  $V_{DS} = -10$  V and  $V_G = -10$  V [22,40]) using [22,39]:

$$R_{sd} = \frac{\Delta V_S + \Delta V_D}{I_{on}} \tag{4}$$

where  $\Delta V_S$  and  $\Delta V_D$  are the voltages drops at the source and drain electrodes (in Fig. 5), respectively, and  $I_{on}$  is the measured 'on-state' source-drain current  $I_{SD}$ . With such calculations we found  $R_{sd}$  for pure (~0.13 M $\Omega$ ) and blend (~0.51 M $\Omega$ ) devices, respectively, much higher in the blend.

# 3.4. Charge-trapping at the edges of Au electrodes in blend transistors

Recently electric force microscopy (EFM) was adopted to study charge trapping in TIPS-PEN transistors by Jaquith et al. [41]. Clear evidence of long-lived charge trapping was observed. In their study the films were prepared using different processing conditions, leading to different mobilities  $(10^{-4}-10^{-3} \text{ cm}^2/\text{Vs})$ . In that work frequency-shift EFM images were recorded to reflect the variations in local trap density. Here, we use SKPM to directly monitor the possi-

**Fig. 4.** Channel length dependence of total resistance ( $R_t$ ) in linear regime ( $V_{DS} = -1$  V) at different gate biases ( $V_G$ ) for pure TIPS-PEN and blend (67 wt.% TIPS-PEN) transistors.

**Fig. 5.** 2D topography and corresponding surface potential images measured with SKPM of pure TIPS-PEN (a) and blend (67 wt.% TIPS-PEN) transistors (b), as shown in the upper and lower panels, respectively. White dashed lines indicate the positions where the potential cross-sections were taken. Solid black lines denote the cross-section potential profiles along the positions indicated by the dashed white lines. In the potential images, parallel dotted lines in the vertical direction indicate the positions of the edges of source (in blue) and drain (in red) electrodes. Channel length is 20  $\mu$ m. The transistors were biased in saturation regime ( $V_{DS} = -10$  V) and  $V_G = -10$  V). (For interpretation of the references to color in this figure legend, the reader is referred to the web version of this article.)

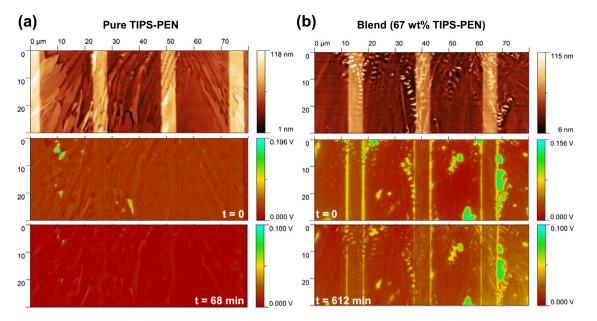

bly trapped charges by measuring their local surface potentials with time. To (possibly) create long-lived trapped charges in our samples, a gate bias of  $V_G = -10$  V was applied for  $\sim 10$  min. During this time, some of the mobile charges may become trapped. The biases were then set to zero in order to extract the mobile charges from the transistor channel, and the local electrostatic potential was measured immediately. Recorded potential images of a pure TIPS-PEN and a blend (67 wt.% TIPS-PEN) transistor are compared. As shown in Fig. 6a (middle image: t = 0), only few spots with slightly higher potentials are identified in pure TIPS-PEN channels. These can be correlated to grain boundaries or material voids from the corresponding topography image. The potential differences at these spots disappear on a time scale of  $\sim 1$  h (bottom image in Fig. 6a: t = 68 min). In comparison, in the blend device we observed noticeable local surface potential variations (middle image in Fig. 6b: t = 0). If we attribute the contrast in these potential images to trapped positive charges (holes), then we observe substantial hole trapping at the edges of Au electrodes in the blend devices. These trapped holes in the blend films are very long-lived (bottom image in Fig. 6b: t = 612 min). For more than 10 h we observed no significant decrease of trapped charges as evidenced by the essentially unchanged potential image.

It has recently been shown that insulating polymer such as poly( $\alpha$ -methylstyrene) can trap charges (holes) in pentacene-based organic transistors [42], and these holes remain trapped in the insulating polymer until sufficient counter charges (electrons) can tunnel into the polymer from the channel [43]. Based on the clear differences of trapped charges in terms of locations, areal densities and life-times between our pure TIPS-PEN and blend devices, we argue that the hole trapping in our blend films is related to the local presence of insulating polymer (PS). The potential variations in the blend films (Fig. 6b) are explained by a lateral phase-separation between TIPS-PEN enriched crystal grains and PS enriched regions. In particular, our SKPM results reveal obvious hole trapping effects exactly at the edges of the source/drain Au electrodes with no apparent correlation with its local crystal morphology. This strongly suggests the presence of a thin film of PS (or PS enriched phase) at the Au electrodes. Such an insulating barrier can explain the differences in sub-threshold slope of the *I*–*V* characteristics, contact resistance observed in channel scaling measurements, potential drops and hole trapping at the electrodes observed by SKPM, between our pure TIPS-PEN and blend devices.

# 3.5. Discussion on the relation between charge-trapping, threshold voltage and channel conductivity

If charges are trapped (de-trapped), or fixed space charges are distributed in the transistor channel on a time-scale comparable to the typical duration of the *I*–*V* measurement, it can be observed as a hysteresis during the forward and backward sweeps in transfer characteristics. We typically swept the voltages at a rate of 1 V/s, meaning a total measurement time of  $\sim$ 1 min.

In the case of pure TIPS-PEN transistors, non-ideal subthreshold behavior was observed in the form of 'shoulderlike'  $I_{SD}$ , with an obvious hysteresis during gate sweeps (Fig. 1a). The (counter-clockwise) hysteresis was independent of the sweep direction, i.e. it was the same when sweeping the gate biases ( $V_G$ ) in the opposite direction (from  $-10 \text{ V} \rightarrow +10 \text{ V} \rightarrow -10 \text{ V}$ , graphs not shown). This hysteresis occurs in the depletion regime, i.e. when the bulk of the semiconductor is (partly) depleted of unintentional charges. We attribute it to charging effects at the top surface of the semiconductor channel (the so-called 'backchannel effect'),

**Fig. 6.** Time-dependent surface potential images and corresponding 2D topographies recorded by SKPM, for pure TIPS-PEN (a) and blend (67 wt.% TIPS-PEN) transistors (b). The potential images in the middle row (t = 0) were measured by grounding all electrodes immediately after a gate bias of -10 V was applied for 10 min. The potential images at the bottom row were measured at t = 68 and 612 min after three electrodes were grounded for the pure and blend device, respectively.

as previously reported by Lee et al. [29]. The transfer characteristics of our blend transistors (with different TIPS-PEN/PS ratios) are essentially hysteresis-free, independent of the direction or range of the gate sweeps. Apparently, the 'backchannel effect' is absent in these blend devices. This points to an additional advantage of the insulating polymer binder. It passivates the charge transport layer.

Trapped channel charges can result in shifts of transistor threshold voltages. Furthermore, deep and shallow trapping can also influence the charge transport negatively. We found that in our blend devices that (1) the existence of insulating polymer causes long-term trapping of holes, and (2) the existence of insulating polymer increases the field-effect mobility and has only a marginal influence on the threshold voltage. We attribute this seeming contradiction to the fact that charge-trapping takes place almost exclusively at the contact edges and to a far lesser extent in the channel region of our blend transistors. Less than 1.6% [44] of the initially accumulated mobile charges induced by the gate bias can be trapped at only a few locations inside the channel (Fig. 6b). This explains why we do not observe threshold voltage shifts in our blend transistors. Whether and how much the trapped charges will mitigate charge transport in the channel cannot be determined or quantified. If any, it is expected to result in a decrease in channel conductivity, but in fact we observe the opposite. The net positive effect of polymer blending indicates that a complex interplay between different mechanisms is taking place here.

#### 4. Conclusions

To conclude, we have presented a systematic study of the influence of material composition and ink-jet processing conditions on the charge transport in bottom-gate field-effect transistors based on single droplets of TIPS-PEN/PS blends. Under optimal conditions the field-effect mobility of the blends is significantly higher than that of the pure TIPS-PEN. In addition, blending results in much better sub-threshold characteristics. These results represent an important step towards the application of ink-jet printing for controlled deposition of high-performance transistors in large-area organic electronics. Using channel scaling measurements and SKPM measurements, we show that the sharp turn-on in current in the blends is the result of a contact resistance that originates from a thin insulating PS layer between the injecting contacts and the semiconductor channel. This insight suggests that reducing the contact resistance is the best way forward to improve the transistor characteristics even further.

#### Acknowledgements

We acknowledge Peter Graat (Philips Research) for helpful discussions. The research leading to these results has received funding from the European Community's Seventh Framework Programme (FP7/2007–2013) under grant agreement No. 212311 of the ONE-P project and No. 216546 of the FLAME project.

#### References

- [1] G. Yu, J. Gao, J.C. Hummelen, F. Wudl, A.J. Heeger, Science 270 (1995) 1789–1791.

- [2] G. Li, V. Shrotriya, J. Huang, Y. Yao, T. Moriarty, K. Emery, Y. Yang, Nat. Mater. 4 (2005) 864–868.

- [3] S. Goffri, C. Muller, N. Stingelin-Stutzmann, D.W. Breiby, C.P. Radano, J.W. Andreasen, R. Thompson, R.A.J. Janssen, M.M. Nielsen, P. Smith, H. Sirringhaus, Nat. Mater. 5 (2006) 950–956.

- [4] B.A. Brown, J. Veres, R.M. Anemian, R.T. Williams, S.D. Ogier, S.W. Leeming, WO Patent 2005055248, 2005.

- [5] J. Smith, R. Hamilton, I. McCulloch, N. Stingelin-Stutzmann, M. Heeney, D. Bradley, T. Anthopoulos, J. Mater. Chem. 20 (2010) 2562– 2574.

- [6] B.K.C. Kjellander, W. Smaal, J.E. Anthony, G.H. Gelinck, Adv. Mater. 22 (2010) 4612–4616.

- [7] R. Hamilton, J. Smith, S. Ogier, M. Heeney, J.E. Anthony, I. McCulloch, J. Veres, D.D.C. Bradley, T.D. Anthopoulos, Adv. Mater. 21 (2009) 1166–1171.

- [8] J. Kang, N. Shin, D.Y. Jang, V.M. Prabhu, D.Y. Yoon, J. Am. Chem. Soc. 130 (2008) 12273–12275.

- [9] T. Ohe, M. Kuribayashi, R. Yasuda, A. Tsuboi, K. Nomoto, K. Satori, M. Itabashi, J. Kasahara, Appl. Phys. Lett. 93 (2008) 053303-3.

- [10] M. Madec, D. Crouch, G. Llorente, T. Whittle, M. Geoghegan, S. Yeates, J. Mater. Chem. 18 (2008) 3230-3236.

- [11] J. Kwon, S. Shin, K. Kim, M.J. Cho, K.N. Kim, D.H. Choi, B. Ju, Appl. Phys. Lett. 94 (2009) 013506-3.

- [12] J. Smith, R. Hamilton, Y. Qi, A. Kahn, D.D.C. Bradley, M. Heeney, I. McCulloch, T.D. Anthopoulos, Adv. Funct. Mater. 20 (2010) 2330– 2337.

- [13] S.D. Ogier, J. Veres, M. Zeidan, WO Patent 2007082584, 2007.

- [14] J. Smith, M. Heeney, I. McCulloch, J.N. Malik, N. Stingelin, D.D. Bradley, T.D. Anthopoulos, Org. Electron. 12 (2011) 143-147.

- [15] B. DeGans, P. Duineveld, U. Schubert, Adv. Mater. 16 (2004) 203– 213.

- [16] M. Madec, P. Smith, A. Malandraki, N. Wang, J. Korvink, S. Yeates, J. Mater. Chem. 20 (2010) 9155–9160.

- [17] J.A. Lim, W.H. Lee, H.S. Lee, J.H. Lee, Y.D. Park, K. Cho, Adv. Funct. Mater. 18 (2008) 229–234.

- [18] J.A. Lim, J. Kim, L. Qiu, W.H. Lee, H.S. Lee, D. Kwak, K. Cho, Adv. Funct. Mater. 20 (2010) 3292–3297.

- [19] J.E. Anthony, J.S. Brooks, D.L. Eaton, S.R. Parkin, J. Am. Chem. Soc. 123 (2001) 9482–9483.

- [20] M.M. Payne, S.R. Parkin, J.E. Anthony, C.C. Kuo, T.N. Jackson, J. Am. Chem. Soc. 127 (2005) 4986–4987.

- [21] D. Braga, G. Horowitz, Adv. Mater. 21 (2009) 1473-1486.

- [22] Y. Luo, F. Gustavo, J. Henry, F. Mathevet, F. Lefloch, M. Sanquer, P. Rannou, B. Grévin, Adv. Mater. 19 (2007) 2267–2273.

- [23] D. Charrier, M. Kemerink, B. Smalbrugge, T. de Vries, R. Janssen, ACS Nano 2 (2008) 622–626.

- [24] G. Koley, M.G. Spencer, H.R. Bhangale, Appl. Phys. Lett. 79 (2001) 545.

- [25] L.C. Teague, B.H. Hamadani, O.D. Jurchescu, S. Subramanian, J.E. Anthony, T.N. Jackson, C.A. Richter, D.J. Gundlach, J.G. Kushmerick, Adv. Mater. 20 (2008) 4513–4516.

- [26] L.C. Teague, O.D. Jurchescu, C.A. Richter, S. Subramanian, J.E. Anthony, T.N. Jackson, D.J. Gundlach, J.G. Kushmerick, Appl. Phys. Lett. 96 (2010) 203305-3.

- [27] A. Liscio, V. Palermo, K. Mullen, P. Samori, J. Phys. Chem. C 112 (2008) 17368–17377.

- [28] J. Brondijk, X. Li, H. Akkerman, P. Blom, B. de Boer, Appl. Phys. A Mater. Sci. Process. 95 (2009) 1–5.

- [29] S.H. Lee, M.H. Choi, S.H. Han, D.J. Choo, J. Jang, S.K. Kwon, Org. Electron. 9 (2008) 721–726.

- [30] G. Horowitz, P. Delannoy, J. Appl. Phys. 70 (1991) 469.

- [31] D. Yoon, Y. Chung, N. Shin, Y. Jo, J. Kang, V. Prabhu, D. Delongchamp, J. Kline, L. Richter, D. Gundlach, J. Anthony, MRS Fall Meeting, 2010, Boston, USA.

- [32] S.H. Kim, D. Choi, D.S. Chung, C. Yang, J. Jang, C.E. Park, S.K. Park, Appl. Phys. Lett. 93 (2008) 113306-3.

- [33] K. Myny, S. De Vusser, S. Steudel, D. Janssen, R. Muller, S. De Jonge, S. Verlaak, J. Genoe, P. Heremans, Appl. Phys. Lett. 88 (2006) 222103-3.

- [34] Z. Liu, J.H. Oh, M.E. Roberts, P. Wei, B.C. Paul, M. Okajima, Y. Nishi, Z. Bao, Appl. Phys. Lett. 94 (2009) 203301.

- [35] W. Choi, B. Park, J. Lee, T. Liu, IEEE Electron Device Lett. 28 (2007) 743-745.

- [36] K. Bhuwalka, J. Schulze, T. Eisele, Jpn. J. Appl. Phys. 43 (2004) 4073– 4078.

- [37] Q. Zhang, W. Zhao, A. Seabaugh, IEEE Electron Device Lett. 27 (2006) 297–300.

- [38] Y. Khatami, K. Banerjee, IEEE Trans. Electron Devices 56 (2009) 2752-2761.

- [39] K.P. Puntambekar, P.V. Pesavento, C.D. Frisbie, Appl. Phys. Lett. 83 (2003) 5539–5541.

- [40] L. Bürgi, T. Richards, M. Chiesa, R.H. Friend, H. Sirringhaus, Synth. Met. 146 (2004) 297–309.

- [41] M. Jaquith, J. Anthony, J. Marohn, J. Mater. Chem. 19 (2009) 6116-6123.

- [42] K. Baeg, Y. Noh, J. Ghim, S. Kang, H. Lee, D. Kim, Adv. Mater. 18 (2006) 3179-3183.

- [43] M. Debucquoy, M. Rockelé, J. Genoe, G. Gelinck, P. Heremans, Org. Electron. 10 (2009) 1252–1258.

- [44] The ratio (Y) of trapped holes to the gate-induced charges by accumulation at this location is estimated by using the following equation (Ref. [41]):  $Y = \Delta \varphi / |(V_G V_{th})|$ , where  $\Delta \varphi$  is the surface potential difference within the transistor channel region, as determined from SKPM (Fig. 6b (t = 0)), a maximum of +0.156 V, under the charging gate bias of  $V_G = -10$  V. Y is calculated to be a maximum of ~1.6% for the blend device.