## University of Groningen

## All-polymer ferroelectric transistors

Gelinck, GH; Marsman, AW; Touwslager, FJ; Setayesh, S; de Leeuw, DM; Naber, RCG; Blom, PWM

Published in: **Applied Physics Letters**

DOI:

10.1063/1.2035324

IMPORTANT NOTE: You are advised to consult the publisher's version (publisher's PDF) if you wish to cite from it. Please check the document version below.

Document Version Publisher's PDF, also known as Version of record

Publication date:

Link to publication in University of Groningen/UMCG research database

Citation for published version (APA):

Gelinck, G. H., Marsman, A. W., Touwslager, F. J., Setayesh, S., de Leeuw, D. M., Naber, R. C. G., & Blom, P. W. M. (2005). All-polymer ferroelectric transistors. Applied Physics Letters, 87(9), art. - 092903. [092903]. DOI: 10.1063/1.2035324

Copyright

Other than for strictly personal use, it is not permitted to download or to forward/distribute the text or part of it without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license (like Creative Commons).

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from the University of Groningen/UMCG research database (Pure): http://www.rug.nl/research/portal. For technical reasons the number of authors shown on this cover page is limited to 10 maximum.

Download date: 10-02-2018

## **All-polymer ferroelectric transistors**

G. H. Gelinck, A. W. Marsman, F. J. Touwslager, S. Setayesh, and D. M. de Leeuw<sup>a)</sup> *Philips Research Laboratories, Prof. Holstlaan 4, 5656 AA Eindhoven, The Netherlands*

R. C. G. Naber and P. W. M. Blom

Materials Science Center, University of Groningen, Nijenborgh 4, 9747 AG Groningen, The Netherlands

(Received 29 December 2004; accepted 7 July 2005; published online 23 August 2005)

We demonstrate thin-film ferroelectric transistors, made entirely from organic materials that are processed from solution. The devices consist of thin ferroelectric poly(vinylidene fluoride/trifluoroethylene) films sandwiched between electrodes made of conducting poly(3,4-ethylenedioxythiophene) stabilized with polystyrene-4-sulphonic acid. On top of this stack, an organic semiconductor is applied. The ferroelectric transistors, constructed using unipolar p- or n-type semiconductor channels, have remnant current modulations of  $\sim 10^3$  with a retention time of hours. They can be switched in 0.1–1 ms at operating voltages less than 10 V. © 2005 American Institute of Physics. [DOI: 10.1063/1.2035324]

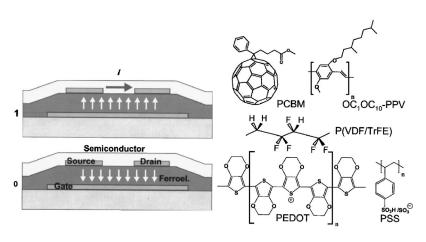

Thin film transistors based on solution-processed organic semiconductors are currently proposed for use in simple circuitry such as flexible displays <sup>1,2</sup> and identification tags.<sup>3</sup> The latter application requires nonvolatile data storage, preferably with memory elements that can be programmed, erased, and read electrically. Ferroelectric field-effect transistors (FeFETs) are attractive for this purpose due to fast nondestructive data readout and low-power consumption.<sup>4</sup> The simplest layout of a FeFET comprises a metal-ferroelectricsemiconductor layer stack (Fig. 1), in which the ferroelectric layer serves as the gate dielectric. The ferroelectric layer, because of its remnant polarization, can adopt either of two stable polarization states, which persist when no biases are applied. Switching from one polarization state to the other can occur by applying a sufficiently large gate bias. Depending on the orientation of the polarization, positive or negative charges are induced in the semiconductor at the semiconductor/ferroelectric interface, i.e., in the semiconductor channel. The induced surface charge density shifts the onset of channel accumulation towards either more negative or positive gate biases. Hence, a gate bias window, defined by the shifted onset voltages, exists wherein the drain current may have either of two levels depending on the actual polarization state of the ferroelectric gate dielectric. The corresponding drain current levels can be used to define Boolean "0" and "1" states of a nonvolatile memory with nondestructive readout. This is illustrated schematically in Fig. 1.

Several groups have demonstrated memory effects in organic-based field-effect transistors using ferroelectrics, ferroelectric-like materials and electrets as gate dielectric. Ferroelectric showed high-performance memory transistors with on-off ratio's as high as 10<sup>4</sup> using a random copolymer of vinylidenedifluoride and trifluoroethylene, P(VDF/TrFE), as ferroelectric gate dielectric, 11 in combination with a poly(*p*-phenylenevinylene) (PPV) semiconductor. The high on-off ratio was attributed to the high remnant surface charge density, of 18 mC/m<sup>2</sup> induced in the semiconductor channel by poling the ferroelectric. In that work, as well as the other studies, metallic electrodes were used (and in some cases also the gate dielectric was inorganic). For cost reasons

it is desirable to deposit all layers from solution by for instance spin coating or inkjet printing. Here, we demonstrate a 150 mm wafer scale technology to make all-polymer ferroelectric capacitors and transistors. The maximum processing temperature of 140  $^{\circ}\mathrm{C}$  ensures compatibility with flexible plastic substrates.

Devices are prepared on 150 mm size silicon support wafers with a 1500 nm thick layer of SiO2. First, a conducting layer of poly(ethylenedioxythiophene)-polystyrene-4sulphonic acid (Baytron P, Bayer Corp.), PEDOT-PSS, was spincoated and patterned to form the gate electrode according to a literature procedure. 12 Then, a film of P(VDF/TrFE) with 80 mol % VDF (Solvay and Cie, Belgium) was spincoated from a 2-butanone solution with a thickness of either 150 or 550 nm. The second PEDOT-PSS layer was applied and patterned to give source and drain electrodes. After processing, the PEDOT-PSS sheet resistances are  $1-2 \text{ k}\Omega$ /square. The wafers were heated to 140 °C for 1-2 h to increase P(VDF/TrFE) film crystallinity<sup>11</sup> after which the semiconductors, consisting of either poly(2methoxy-5-(3',7'-dimethyloctyloxy)-phenylenevinylene) (OC<sub>1</sub>OC<sub>10</sub>–PPV) or [6,6]–phenyl-C<sub>61</sub>-butyricacidmethylester (PCBM), was applied from chlorobenzene solution.<sup>13</sup>

The ferroelectric properties of P(VDF/TrFE) sandwiched between PEDOT-PSS electrodes, are characterized by displacement vs electric field (D-E) hysteresis loops. The measurements were recorded in ambient atmosphere using a Sawyer–Tower setup and sinusoidal field scanning at 1 Hz. The saturated loops are symmetric and square with remnant polarizations of |84| mC/m<sup>2</sup>. The coercive voltages  $(V_c)$ , i.e., where D=0, for 150 nm and 550 nm thick P(VDF/TrFE) films are found at |8| and |29| V, respectively. The coercive field  $(E_c)$  of  $\sim$ 53 MV/m is consistent with literature data and indicates that abrupt well-defined interfaces are formed between the solution-deposited P(VDF/TrFE) and PEDOT-PSS layers.

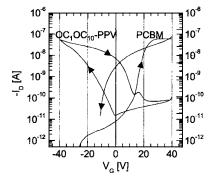

Transistor characteristics were measured in  $N_2$  and dark at room temperature using a HP4156B semiconductor parameter analyzer at a scan speed of 1 V/s. The transfer  $(I_D-V_G)$  characteristics of FeFETs with a 550 nm thick P(VDF/TrFE) layer, recorded at a drain bias of -5 V, are shown in Fig. 2. The wave made unipolar p-type and n-type FeFETs using  $OC_1OC_{10}$ -PPV or PCBM as a semiconductor,

a) Author to whom correspondence should be addressed; electronic mail: dago.de.leeuw@philips.com

FIG. 1. Schematic representation of the all-polymer ferroelectric transistor and the chemical structures of the materials used. The arrows indicate the two remnant states of polarization in the ferroelectric layer. Readout of the polarization state occurs nondestructively by detection of the current level, *I*, between source and drain electrodes

respectively. Both FeFETs show a drain current hysteresis that can be explained by the ferroelectric gate dielectric polarization. Polarization reversal occurs at gate biases comparable to the values of the coercive voltage.

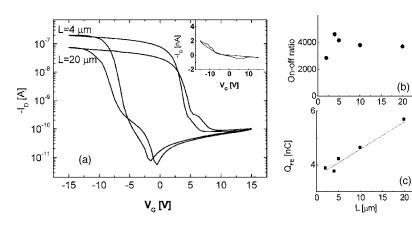

Figure 3(a) shows the transfer characteristics of a  $OC_1OC_{10}$ -PPV FeFET with different channel lengths, recorded at a drain bias of -2 V. The device has a 150 nm thick P(VDF/TrFE) layer. The driving voltages are significantly reduced compared to the devices with the thicker 550 nm P(VDF/TrFE) layer; polarization reversal occurs already below 10 V. Switching voltages were found to be somewhat lower for small-channel devices. For transistors with channel lengths ranging from 20 to 2  $\mu$ m, the on-off ratio was consistently higher than  $10^3$ , with a maximum of  $5\times10^3$  [Fig. 3(b)]. These values are superior to the remnant current modulations of 10-100 reported by other groups,  $^{5-7}$  and close to the highest value of  $10^4$  reported.

When the polarization switches from one state to another, charge is displaced across the ferroelectric insulator. The accompanying switching currents are observed as sharp features in the drain current [Figs. 2 and 3(a)] as well as gate current [see inset Fig. 3(a)]. Their presence confirms that the memory effect is driven by ferroelectric polarization, and that it is not due to injection of charges or ion migration. Furthermore, so-called inner loops,  $I_D - V_G$  scans to  $V_G$  smaller than the switching values (not shown), are symmetrically positioned on the  $V_G$  axis within the outer loops. This demonstrates that the hysteresis results from switching between two approximately equal opposite polarization states that differ from the net zero polarization present in the pris-

FIG. 2. Transfer  $(I_D - V_G)$  curves of all-polymer ferroelectric transistors with a 550 nm thick P(VDF/TrFE) gate dielectric layer and either  $OC_1C_{10}$ -PPV or PCBM semiconductor, respectively. The arrows indicate the directions of the hysteresis between the forward and backward scans recorded at drain biases of -5 V. The transistors have a channel length and width of 5 and 1000  $\mu$ m, respectively.

tine devices; when switching the device the semiconductor surface charge density within the channel changes from  $-P_R$  to  $+P_R$ , or vice versa.

Figure 3(c) shows the switching charge  $Q_{\rm FE}$  for different channel lengths, as obtained by integrating the difference in gate current in forward (switching) and backward  $I_D$ - $V_G$ sweep (non switching) direction and multiplying this value with the scan speed (1 V/s). A linear fit to the data yields an ordinate intercept ( $L=0 \mu m$ ) of 3.6±0.1 nC and a slope of  $0.011\pm0.001$  nC/ $\mu$ m. The intercept value is determined by the induced charge between overlapping source-drain and gate electrodes, which is identical for all transistors, and parasitic charging effects outside the active channel. It is therefore strongly dependent on the transistor geometry used. The slope of the curve can be used to estimate the semiconductor surface charge density  $(P_R)$  within the channel. From the slope and channel width of 1000  $\mu$ m, a switching charge per unit channel area of 11 mC/m<sup>2</sup> is calculated. If we assume that  $Q_{\rm FE}$  equals  $2P_R$ , as suggested by the observation that the inner loops are symmetrically centered within the outer loops, the semiconductor surface charge density induced by ferroelectric polarization is determined to be ~6 mC/m<sup>2</sup>. Measurements on other transistor series (with different channel widths and/or source-drain electrode configuration) yielded values within 25%. This value is smaller than the remnant polarization of 84 mC/m<sup>2</sup> found for our capacitors and the value of 18 mC/m<sup>2</sup> reported in the P(VDF-TrFE) transistors that have Au electrodes. 19 The latter value was estimated using the method of Miller and McWhorter. 17

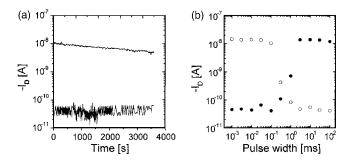

Data retention characteristics were examined by measuring the remnant drain currents ( $V_G=0$  V) as a function of time after a 100 ms set pulse of +15 or -15 V [Fig. 4(a)]. The off state current remains more or less constant with time. Note that loss of ferroelectric polarization would have resulted in an increasing off-state drain current. The on-state current decreases steadily with time. After 1 h the ratio of the remnant currents has deteriorated to ~30\% of the initial value. More information on the on state degradation mechanism was obtained by applying programming pulses on the "degraded" devices. Applying negative gate pulses to the devices that had been in the on state for 1 h did not result in an increase in on state remnant current. However, when these devices were first programmed to the off state and then switched back to the on state, recovery of the original on state current was observed. We found that recovery in the off state is completed within 1 h. Similar aging behavior was

FIG. 3. Characteristics of  ${\rm OC_{1}OC_{10}}$ –PPV ferroelectric transistors with a 150 nm thick P(VDF/TrFE) gate dielectric layer. (a)  $I_D$ – $V_G$  curve of transistors with channel length 4 and 20  $\mu$ m, recorded with  $V_D$ =–2 V. Inset:  $I_G$ – $V_G$  curve of the 20  $\mu$ m transistor; (b) ratio of remnant on- and off-currents, measured at  $V_G$ =0 V and  $V_D$ =–2 V for different channel lengths; (c) switching charge,  $Q_{\rm FE}$ , for different channel lengths. The channel width was 1000  $\mu$ m and the finger width of source and drain electrodes was 5  $\mu$ m, so that the gate-to-source/drain overlap in all devices was identical.

observed in *n*-type FeFETs. Based on these observations, we attribute the degradation to ferroelectric domain pinning by ionic contaminations. <sup>18</sup> Because this degradation was absent in devices that have gold electrodes, <sup>19</sup> it is likely that the ionic contaminations stem from the PEDOT-PSS layers.

Further insight in device operation is gained with transient switching investigations of  $OC_1OC_{10}$ –PPV FeFETs with a 150 nm P(VDF/TrFE) layer [Fig. 4(b)]. Duration, magnitude, and polarity of the voltage pulse were varied. If we define switching time as the crossover point of the two curves, the switching time decreases from  $\sim 3$  ms for pulses of  $\pm 10$  V to 0.1 ms for pulses of  $\pm 25$  V. Hence, especially for high fields the switching time is considerably larger than those of PEDOT-based ferroelectric capacitors of  $40~\mu s$ , suggesting that in the FeFETs the switching speed is dominated by the RC time constant of the semiconducting channel,  $^{21}$  i.e., the product of the source–drain channel resistance in depletion and the gate capacitance.

Concluding, we demonstrated a potentially low-cost technology to make all-polymer ferroelectric transistors with promising switching characteristics and retention properties. The technology is amenable to downscaling of the dimensions of the transistor, both minimum feature size and layer thickness of the ferroelectric layer, as demonstrated by transistors with channel lengths of 2  $\mu$ m that switch at voltages well below 10 V.

FIG. 4. Switching characteristics and retention times of  $OC_1OC_{10}$ -PPV ferroelectric transistors with a 150 nm thick P(VDF/TrFE) gate dielectric layer. (a) Time dependence of drain current ( $I_D$ ) in the on-and off-state; (b) drain current ( $I_D$ ) after application of gate pulse of + or -15 V with different pulse widths. In both (a) and (b), a 100 ms set pulse of + or -15 V was used to define the initial polarization state.  $V_D$  was kept at -2 V throughout the measurements.

The authors acknowledge Menno Prins and Eduard Meijer for useful discussions, and J.C. Hummelen (University of Groningen, The Netherlands) for the supply of PCBM.

<sup>1</sup>H. E. A. Huitema, G. H. Gelinck, J. B. P. H. van der Putten, K. E. Kuijk, C. M. Hart, E. Cantatore, P. T. Herwig, A. J. J. M. van Breemen, and D. M. de Leeuw, Nature (London) 414, 599 (2001).

<sup>2</sup>J. A. Rogers, Z. Bao, K. Baldwin, A. Dodabalapur, B. Crone, V. R. Raju, V. Kuck, H. Katz, K. Amundson, J. Ewing, and P. Drzaic, Proc. Natl. Acad. Sci. USA 98, 4835 (2001).

<sup>3</sup>D. M. de Leeuw, G. H. Gelinck, T. C. T. Geuns, E. van Veenendaal, E. Cantatore, and B. H. Huisman, 2002 Int. Electron Device Meet. (IEDM) Tech. Dig. 293 (2002).

<sup>4</sup>J. F. Scott, Ferroelectric Memories in Advanced Microelectronics (Springer, Berlin, 2000).

<sup>5</sup>G. Velu, C. Legrand, O. Tharaud, A. Chapoton, D. Remiens, and G. Horowitz, Appl. Phys. Lett. **79**, 659 (2001).

<sup>6</sup>T. Kodzasa, M. Yoshida, S. Uemura, and T. Kamata, Synth. Met. **137**, 943 (2003).

<sup>7</sup>R. Schroeder, L. A. Majewski, and M. Grell, Adv. Mater. (Weinheim, Ger.) **16**, 633 (2004).

<sup>8</sup>K. N. Narayanan Unni, R. de Bettignies, S. Dabos-Seignon, and J.-M. Nunzi, Appl. Phys. Lett. 85, 1823 (2004).

<sup>9</sup>Y. Matsuo, T. Ijichi, H. Yamada, J. Hatori, and S. Ikehata, Cent. Eur. J. Phys. **2**, 117 (2004).

<sup>10</sup>Th. B. Singh, N. Marjanoviæ, G. J. Matt, N. S. Sariciftci, R. Schwödiauer, and S. Bauer, Appl. Phys. Lett. 85, 5409 (2004).

<sup>11</sup>Ferroelectric Polymers; Chemistry, Physics and Applications, edited H. S. Nalwa (Marcel Dekker, New York, 1995).

<sup>12</sup>F. J. Touwslager, N. P. Willard, and D. M. de Leeuw, Appl. Phys. Lett. **81**, 4556 (2002)

<sup>13</sup>E. J. Meijer, D. M. De Leeuw, S. Setayesh, E. Van Veenendaal, B.-H. Huisman, P. W. M. Blom, J. C. Hummelen, U. Scherf, and T. M. Klapwijk, Nat. Mater. 2, 678 (2003).

<sup>14</sup>H.-S. Xu, Z.-Y. Cheng, V. Bharti, S. Wang, and Q. M. Zhang, J. Appl. Polym. Sci. 75, 945 (2000).

<sup>15</sup>The off-currents are independent of channel length and are due to leakage currents (<0.5 nA) outside the active device through the nonpatterned semiconductor layer.

<sup>16</sup>H. E. Katz, X. M. Hong, A. Dodabalapur, and R. Sarpeshkar, J. Appl. Phys. **91**, 1572 (2001).

<sup>17</sup>S. L. Miller and P. J. McWhorter, J. Appl. Phys. **72**, 5999 (1992).

<sup>18</sup>J. C. Burfoot and G. W. Taylor, in *Polar Dielectrics and their Applications* (MacMillan, New York, 1979).

<sup>19</sup>R. C. G. Naber, C. Tanase, P. W. M. Blom, G. H. Gelinck, A. W. Marsman, F. J. Touwslager, S. Setayesh, and D. M. de Leeuw, Nat. Mater. 4, 243 (2004).

<sup>20</sup>R. C. G. Naber, P. W. M. Blom, A. W. Marsman, and D. M. de Leeuw, Appl. Phys. Lett. **85**, 2032 (2004).

<sup>21</sup>M. W. J. Prins, K.-O. Grosse-Holz, G. Muller, J. F. M. Cillessen, J. B. Giesbers, R. P. Weening, and R. M. Wolf, Appl. Phys. Lett. **68**, 3650 (1996)