# University of Groningen

# Technology for nanoelectronic devices based on ultra-high vacuum scanning tunneling microscopy on the Si(100) surface

Palasantzas, Georgios; Ilge, B; Rogge, S; Geerlings, LJ

Published in: Microelectronic Engineering

DOI: 10.1016/S0167-9317(99)00035-0

IMPORTANT NOTE: You are advised to consult the publisher's version (publisher's PDF) if you wish to cite from it. Please check the document version below.

Document Version Publisher's PDF, also known as Version of record

Publication date: 1999

Link to publication in University of Groningen/UMCG research database

*Citation for published version (APA):* Palasantzas, G., Ilge, B., Rogge, S., & Geerlings, L. J. (1999). Technology for nanoelectronic devices based on ultra-high vacuum scanning tunneling microscopy on the Si(100) surface. Microelectronic Engineering, 46(1-4), 133-136. DOI: 10.1016/S0167-9317(99)00035-0

#### Copyright

Other than for strictly personal use, it is not permitted to download or to forward/distribute the text or part of it without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license (like Creative Commons).

Take-down policy If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from the University of Groningen/UMCG research database (Pure): http://www.rug.nl/research/portal. For technical reasons the number of authors shown on this cover page is limited to 10 maximum.

MICROELECTRONIC ENGINEERING

# Microelectronic Engineering 46 (1999) 133-136

Technology for nanoelectronic devices based on ultra-high vacuum scanning tunneling microscopy on the Si(100) surface

G. Palasantzas\*, B. Ilge, S. Rogge, and L. J. Geerligs

Delft University of Technology, Delft Institute of Microelectronics and Submicron Technology (DIMES) and Department of Applied Physics, NEXT-Lab, Lorentzweg 1, 2628 CJ Delft, The Netherlands

We describe two process steps in an STM-based fabrication technology for nanoelectronic devices. First, we have fabricated Co/Si metal lines on Si(100) surfaces by UHV-STM based nanolithography on a monohydride passivation layer. The STM tip was used to define depassivated lines (<10 nm in width) by electron-stimulated H desorption followed by Co deposition at submonolayer coverage. The resulting Co/Si wires show a granular structure with rough boundaries, but after anneal at 410 °C this changes into a compact structure possibly due to strong silicidation. Second, fabrication and analysis of tungsten contact metallization that will allow electrical transport studies along these metallic nanostructures has been performed.

# **1. INTRODUCTION**

Scanning tunneling and atomic force microscopy (STM and AFM) have been proven to be unique tools for the fabrication of nanoscale structures [1,2]. For example, under normal scanning conditions the STM does not perturb the H-Si(100) surface, while by increasing the voltage between the STM tip and the sample H can desorb leading effectively to the possibility to pattern areas of any desired shape and size [2]. Metallization proceeds by means of Chemical or Physical Vapour Deposition (CVD, PVD) techniques [2-4] of metal adatoms which nucleate selectively on depassivated areas due to the increased density of reaction sites.

Although metallization techniques have been demonstrated recently for Fe and Al by CVD and PVD, respectively [2-4], Co merits special attention since it forms silicides with widespread applications in microelectronics (e.g., transistor gates, contacts, etc.), because they have low electrical resistivity, small lattice mismatch with Si at room temperature (RT) [5], and are metallic in nature [6]. On the other hand, Al/Si suffer from high temperature processing ( $\geq$ 400 °C) due to dissolution of Al into Si [7] leading

effectively to degradation of metallic structures, while  $FeSi_2$  is usually semiconducting (depending on the phase) [8].

Furthermore, for nanometer-scale devices, it is necessary to use a high-resolution conventional patterning technology to link the atomic scale to the measurement equipment. The first reports on such technology were given in ref. [9,10]. Here we will present details of electronic properties of such contact metallization.

# 2. EXPERIMENTAL PROCEDURE

We have separated the experiments in two series; one directed at patterning of nanostructures, on conventionally prepared substrates, the other directed at the contact metallization. All experiments presented here were performed on p-doped Si(100) samples of resistivity approx. 25  $\Omega$ cm.

For the nanostructure patterning samples were cleaned by resistive heating to 1200 °C and dosed with atomic H from high purity  $H_2$  as described in ref. [11]. Co was e-beam evaporated at a rate ~0.0017 nm/sec. The samples were imaged and

<sup>\*</sup>Present address: Netherlands Institute for Metals Research (NIMR), Department of Applied Physics & Materials Science Center, Groningen University, Nijenborgh 4, 9747 AG Groningen, The Netherlands.

patterned in-situ with mechanically cut PtIr tips.

For the contact metallization, the liftoff technique to create tungsten patterns of 6 nm thickness with 30 nm resolution is described elsewhere [10]. Liftoff takes place in hydrofluoric acid (40% in water), which leaves the sample surface mostly hydrogen passivated. The sample is kept in dry nitrogen ambient as much as possible, and is immediately loaded into the UHV. A sequence of lengthy 400 °C degassing, hydrogen radical cleaning, and anneal at approx. 720 °C is used for the in-situ preparation. The last anneal takes place in a chamber with base 5.10 mbar; pressure avoiding carbon contamination of the surface is crucial for this step. These samples are imaged with etched and sputtered W tips (radius of curvature 10 to 20 nm). The results presented here are for 24  $\Omega$ cm p-type wafers.

# 3. FABRICATION TECHNOLOGY OF Co/Si NANOWIRES

Fig. 1 illustrates the ability of a mechanically cut PtIr STM tip to form high-resolution patterns on a H-Si(100) surface by electron stimulated H desorption. Depassivated lines were written with varying current, sample bias  $V_b$ =5.5 V, and a writing speed of 200 nm/sec. In this case ( $V_b$ <7 V) H desorbs according to a vibrational excitation mechanism [2]. The lines appear higher than the rest of the H-Si(100) surface due to the increased density of states (H-free Si dangling bonds) for tunneling. It is clear that at these moderately high voltages it is

Figure 1. Depassivated lines on H-Si(100) surfaces created with STM at writing currents 3 and 4 nA (from top to bottom), and substrate bias voltage 5.5 V. Imaging at -2 V and 0.1 nA. Scan size 30x20 nm.

possible with the mechanically cut tips to define depassivated lines of 2-3 dimer rows wide.

Submonolayer deposition of Co onto bare and passivated Si(100)2x1 surfaces at RT as well as elevated temperature, and the effect of subsequent annealing, is described in refs. [11 - 13]. On the bare surface, reaction occurs, in contrast to passivated surfaces, on which Co nucleates in sparse nonepitaxial islands.

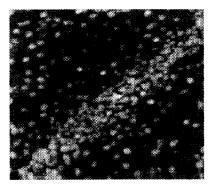

Fig. 2 shows part of a depassivated line on a H-Si(100) sample after deposition of 0.13 ML of Co at RT. A dense concentration of Co in the depassivated area occurs due to reaction of Co with Si towards silicide formation even at RT [5], while on the monohydride areas it forms distinct islands [11]. The deposited Co atoms nucleate randomly even close to the wire without showing a significant depletion zone around the wire boundary. The wire width is approximately 8-9 nm which is comparable to the original depassivated line width.

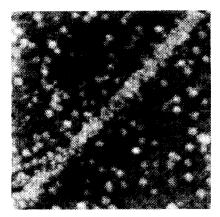

It is possible to improve the structure of the metal patterns by further annealing treatments up to 470 °C (where H desorption commences [14]). Previous studies have shown CoSi and CoSi<sub>2</sub> formation to occur in the temperature range 375-500 °C [5,15]. Such a possibility is presented in Fig. 3 where Co was deposited at RT on a H-Si(100) surface with depassivated lines of about 5 nm wide, and further annealed at 410 °C for 20 sec. A more distinct and compact structure than that at RT is formed indicating strong silicidation in the wire area. The monohydride side remains intact even closely at the wire boundary (appearing even sharper than at

Figure 2. Co/Si wire formed after Co deposition at RT. Scan size 33x40 nm, Imaging at -1.8 V and 0.48 nA.

Figure 3. Co wire (5 nm wide) after Co deposition at RT and anneal at 410 °C for 20 sec. Scan size 45x45 nm. Imaging at -1.5 V and 0.28 nA.

RT) after the annealing process. Finally, we should point out that the presence of Co islands around the wire is not a potential problem for electronic transport experiments. Electron hopping from the wire to the nearest isolated islands is effectively suppressed because it leads to large charging energy [1, 16].

# 4. ELECTRICAL CONTACT TECHNOLOGY

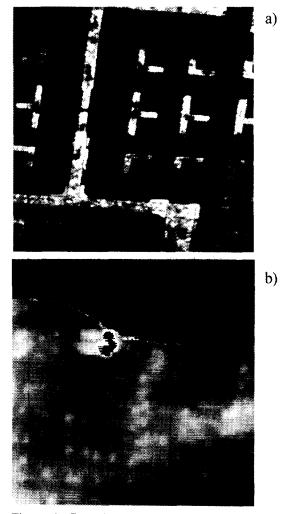

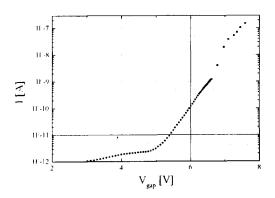

An STM image of a contact structure resulting from the processing described in section 2 is displayed in Fig. 4a. Fig. 5 shows the current versus voltage of the gap in this pattern, i.e., the conductance through the tungsten silicide-silicon barrier and the silicon gap at a temperature of 4 K. The leakage current is below the noise level (about 1 pA) up to 3 V, and below 2 pA up to 5 V. Above 5.5 V the I(V) curve can be well fitted to Fowler-Nordheim emission. Using an electron microscope measurement of the gap size, 120 nm, the fit yields a barrier height of 0.5 eV. We expect the metallization is partly silicidized after the preparation, and the fitted barrier corresponds quite well to common silicide-silicon Schottky barriers [5]. Note that the gap is small enough to neglect curvature of the silicon bands due to space charge: the gap can be approximated by a square barrier for the conduction electrons, which is rounded at the edges due to the image charge potential.

Figure 4. Central contact and marker pattern after cleaning as described in text. a) 4.5 micron view; b) detail of the area inside the gap, showing numerous terraces of the 2x1 reconstructed Si surface (25nm scan).

The silicon surface inside the gap is 2x1reconstructed. Fig. 4b shows a detail of this surface. In general, the silicon has many terraces close to the W metallization. This becomes progressively worse as the final anneal temperature is increased above 720 °C. Nevertheless, after hydrogen passivation we have written patterns on this substrate, crossing the terraces and apparently running into the metallization. However, due to tip convolution there is a 'shadow' region around the metal which can not be imaged, so it is not verified that these patterns

Figure 5. Current-voltage measurements through a structure closely similar to Fig. 4, with 120 nm gap. Temperature approximately 4 K.

actually connect to the metallization. Experiments are in progress for the resolution of this problem by employing thinner contacts and/or polishing techniques combined with alternative cleaning processes.

# 5. CONCLUSIONS

In comparison with former metallization studies, the Co/Si wires (especially the annealed ones) appear more compact than those by formed by CVD of  $Fe(CO)_5$  [3] and PVD of Al [4] and with better defined boundaries. Thus, Co can be a potentially suitable candidate for future nanofabrication of metallic nanostructures due its strong reaction with the Si. Experiments are in progress to create metal nanostructures connected to macroscopic contacts.

### ACKNOWLEDGEMENTS

This work is supported by the Stichting voor Fundamenteel Onderzoek der Materie (FOM) which is financially supported by the "Nederlandse Organisatie voor Wetenschappelijk Onderzoek (NWO)", and also by the ESPRIT research program 22953 (CHARGE).

#### REFERENCES

- 1. E.S. Snow, P.M. Campbell, and F.K. Perkins, Naval Research Reviews Vol. XLIX, 15 (1997).

- J.W. Lyding, Naval Research Reviews Vol. XLIX, 25 (1997) (and references therein); J.W. Lyding et al., Appl. Phys. Lett. 64, 2010 (1994); T.-C. Shen et al., Science 268, 1590 (1995); E. T. Foley et al., Phys. Rev. Lett. 80, 1336 (1998); R. S. Becker et al., Phys. Rev. Lett. 65, 1917 (1990); J. J. Boland, Surf. Sci. 244, 1 (1991).

- 3. D.P. Adams, T.M. Mayer, and B.S. Swartzentruber, Appl. Phys. Lett. **63**, 3571 (1996).

- T.-C. Shen, G.C. Abeln, and J.R. Tucker, Phys. Rev. Lett. 78, 1271 (1997).

- R. T. Tung, Mat. Chem. Phys. 32, 107 (1992);

S. P. Murarka, *Silicides for VLSI Applications* (Academic, New York, 1983).

- L. F. Matheiss and D. R. Hamman, Phys. Rev. B 37, 10623 (1988).

- J. W. Mayer and S. S. Lau, "Electronic Materials Science: For Integrated Circuits in Si and Ga As" (Macmillan Publishing Company, New York, 1990).

- 8. J. Derrien et al., Appl. Surf. Sci. 73, 90 (1993).

- 9. A. Dunn et al., Appl. Phys. Lett. **71**, 2937 (1997).

- M.R. Zuiddam et al., Microelectronic Engineering 41, 567 (1998); L.J. Geerligs et al., J. Surf. Analysis 4, 204 (1998).

- G. Palasantzas, B. Ilge, J. de Nijs, and L. J. Geerligs, Surf. Sci. 412-413, 509 (1998).

- 12. V. Scheuch, B. Voigtlander, and H. P. Bonzel, Surf. Sci. **372**, 71 (1996).

- M. Copel and R. M. Tromp, Appl. Phys. Lett. 65, 3102 (1994).

- 14. K. Sinniah et al., J. Chem. Phys. **92**, 5700 (1990).

- S. Mantl and H. L. Bay, Appl. Phys. Lett. 61, 267 (1992); C. W. T. Bulle-Lieuwma et al., J. Appl. Phys. 71, 2211 (1992); G. Rangelov, P. Augustin, J. Stober, and T. Fauster, Phys. Rev. B 49, 7535 (1994).

- 16. As is explained in ref. 1, envelope calculations indicate that for island sizes  $\leq 10$  nm the island charging energy  $\sim e^2/C$  can overcome the thermal energy K<sub>B</sub>T at RT (T $\approx 300$  K).