# GaN-on-Si Quasi-Vertical Power MOSFETs

Chao Liu, Riyaz Abdul Khadar, and Elison Matioli, Member, IEEE

Abstract— We demonstrate the first GaN vertical transistor on silicon, based on a 6.7-μm-thick n-p-n heterostructure grown on 6-inch silicon substrate by metal organic chemical vapor deposition (MOCVD). The devices consist of trench-gate quasi-vertical metal—oxide—semiconductor field-effect transistors (MOSFETs) with a 4 μm-thick drift layer, exhibiting enhancement-mode (E-mode) operation with a threshold voltage of 6.3 V and an on/off ratio of over  $10^8$ . A high off-state breakdown voltage of 645 V along with a specific on-resistance of 6.8 mΩ·cm² were achieved thanks to the high-quality 4 μm-thick GaN drift layer presenting a relatively low defect density and very high electron mobility (720 cm²/V·s). This excellent performance represents a major step towards the realization of high-performance GaN vertical power transistors on low-cost silicon substrates.

**Index Terms** – Gallium nitride, vertical transistors, GaN-on-Si, power, semiconductor, devices, MOSFETs.

#### I. INTRODUCTION

ide-bandgap III-nitride semiconductors have a great potential for the next generation of efficient and compact power systems. To date, the majority of the research has been directed towards lateral high electron mobility transistors (HEMTs) based on an AlGaN/GaN heterostructure [1]-[3]. This is due to the advantages offered by the high-density and high-mobility two-dimensional electron gas (2DEG) induced at the hetero-interface, which allow high-voltage devices with large switching speeds and reduced on-resistances. However, for high-voltage and high-current applications (over 1.2 kV/100 A), the lateral topology presents limitations in scalability to reach large chip areas with high breakdown at the desired high operating current level [4]. With a vertical topology, the implementation of high voltage chips is possible by increasing the thickness of the drift region, without sacrificing the device size. In contrast to lateral devices, vertical GaN MOSFETs are less sensitive to surface traps states, which can reduce the degradation in dynamic on-resistance and mitigate current collapse issues. In addition, vertical MOSFETs can display normally-off operation, which is an important feature for power switching applications [5]-[7]. Rapid progress has been reported for high-performance vertical GaN transistors grown on n-type GaN substrates [8]-[20], mainly attributed to the capability of growing thick drift layers and the

This work was supported the European Research Council (ERC) under the ERC Grant Agreement 679425. The authors are with the Power and Wide-band-gap Electronics Research Laboratory (POWERlab), École Polytechnique Fédérale de Lausanne (EPFL), CH-1015 Lausanne, Switzerland (e-mail: chao.liu@epfl.ch; elison.matioli@epfl.ch).

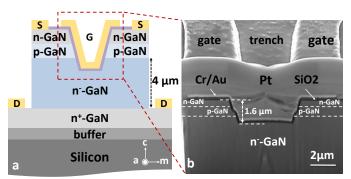

Fig. 1. Cross-sectional (a) schematic, and (b) SEM image of the fabricated quasi-vertical trench gate MOSFETs on Si substrate.

flexibility to form electrodes on the top and bottom of the devices. However, the high cost and availability of only small-size bulk GaN substrates limit their use for mass production. The GaN-on-Si platform offers a cost-effective alternative for vertical GaN MOSFETs, due to its low cost, large-scale availability, and a mature fabrication technology, including for substrate removal.

In recent years, GaN-on-Si technology has been developed extensively for several different areas, such as high-brightness light emitting diodes [21], high-power lateral HEMTs [2], [3], [22] and high-power vertical diodes [23]-[28]. However, there have been no reports up-to-date on GaN-on-Si vertical transistors, due to the challenge in obtaining high-quality n-p-n GaN heterostructures on silicon substrates. On one hand, the doping profile needs to be carefully engineered for abrupt heterojunctions; and on the other hand, a thick and continuous GaN drift layer with high electron mobility and low defect density is highly desired for low on-resistance and large breakdown voltage. This is especially challenging on silicon substrates considering the large mismatch between GaN and Si, both in lattice constant and thermal expansion coefficient.

In this work, we demonstrate the first GaN-on-Si vertical transistors fabricated on a 6.7  $\mu m$ -thick n-p-n heterostructure grown on 6-inch silicon substrates. This structure contained a 4  $\mu m$ -thick GaN drift layer, with a dopant concentration of 2  $\times$   $10^{16}$  cm $^{-3}$ . With an optimized buffer and doping profile, the lateral electron mobility in the drift layer was as high as 720 cm $^2/V \cdot s$ . To the best of our knowledge, this is the highest electron mobility in vertical GaN on Si. The fabricated vertical trench MOSFETs exhibited E-mode operation with a threshold voltage (V<sub>th</sub>) of 6.3 V and an on/off ratio of over  $10^8$ . A specific on-resistance of 6.8 m $\Omega \cdot cm^2$  and a high off-state breakdown voltage of 645 V were achieved. This excellent performance shows the great potential of GaN-on-Si to serve as a platform for future power electronic applications.

© 2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

#### II. DEVICE STRUCTURE AND FABRICATION

Fig. 1 (a) depicts a cross-sectional schematic of the fabricated quasi-vertical trench gate MOSFETs, in which the gate trench is aligned along the a-axis. The n-p-n heterostructure used in this work was grown on 6-inch Si (111) substrates by metal organic chemical vapor deposition (MOCVD). From bottom to top, the n-p-n structure consisted of a 1.1 μm-thick buffer layer, a 1 μm-thick n-type GaN layer (Si: ~  $1 \times 10^{19}$  cm<sup>-3</sup>), a 4 µm-thick n-type GaN layer (Si: ~  $2 \times 10^{16}$ cm<sup>-3</sup>), a 350 nm-thick p-type GaN layer (Mg:  $\sim 4 \times 10^{19}$  cm<sup>-3</sup>), a 200 nm-thick n-type GaN layer (Si:  $\sim 5 \times 10^{18}$  cm<sup>-3</sup>), and a 20 nm-thick n-type GaN layer (Si:  $\sim 1 \times 10^{19}$  cm<sup>-3</sup>). The x-ray diffraction (XRD) omega-rocking curves showed a small full width at half-maximum (FWHM) value of 235 arcsec and 307 arcsec near the GaN (002) and (102) reflections, respectively. For the growth of thick, continuous GaN on Si with low threading dislocation density, high quality buffer layers are important, especially the AlN nucleation layer. AlN buffer on Si with high crystalline quality (FWHM<sub>(002)</sub> < 1000 arcsec) and smooth surface was obtained by optimizing the AlN growth technology. With the high-quality AlN buffer layers, thick GaN on Si was grown without relaxation of the compressive stress during growth, which is important for compensating the tensile stress during cooling down. The value for wafer bowing after growth was  $X\sim-57$  µm,  $Y\sim-45$  µm. The lateral mobility of the n-type GaN drift layer was 720 cm<sup>2</sup>/V·s for a Si dopant concentration of  $2 \times 10^{16}$  cm<sup>-3</sup>, measured with a Hall system on n-GaN/i-GaN/buffer/Si.

The device fabrication started with a plasma-based dry etching process of GaN using Cl<sub>2</sub>/BCl<sub>3</sub>/Ar with SiO<sub>2</sub> hard mask to form the trench structures with a depth of 1.6 µm for the vertical gate. The sample was then treated with a 5% Tetra Methyl Ammonium Hydroxide (TMAH) solution at 85°C for 60 minutes. The TMAH wet etch was found effective in removing the damages from dry-etched GaN sidewalls [29], [30]. To activate the buried p-type GaN, a rapid thermal annealing (RTA) was performed at 850°C for 20 min in a N2 ambient. Subsequently, a 100 nm-thick SiO<sub>2</sub> gate dielectric for the vertical MOSFETs was deposited on the top surface and trenches by atomic layer deposition (ALD). After opening contact holes by reactive ion etching (RIE), a double-layer metal stack of Cr/Au was evaporated to form both the source and gate electrodes for the vertical MOSFETs. Finally, a 5 µm-deep etching was performed using a BCl<sub>3</sub>/Cl<sub>2</sub>-based inductively coupled plasma (ICP) etch, followed by the evaporation of Cr/Au drain electrodes.

Fig. 1 (b) shows the cross-sectional image of the quasi-vertical MOSFETs taken by focused ion beam-scanning electron microscope (FIB-SEM), in which a 3  $\mu$ m-thick Pt was deposited at the gate region for surface protection. The depth in the etched trench was 1.6  $\mu$ m, reaching the drift layer, and the trench sidewalls were inclined by 13.2° from the c-axis. The trench width was 4.0  $\mu$ m and 5.5  $\mu$ m at the bottom and the top, respectively. The angle of the trench sidewall can be improved with optimized dry etching conditions and further smoothened with longer TMAH treatment [29]-[31]. The small kink observed at the middle of the sidewall might be due to erosion

of the SiO<sub>2</sub> hard mask edge during dry etching [30].

#### III. RESULTS AND DISCUSSION

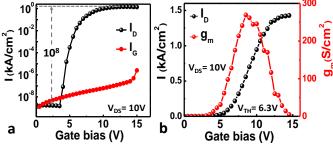

The transfer characteristics of the vertical trench MOSFETs in Fig. 2 (a) show a current on/off ratio of over  $10^8$  and a sub-threshold slope of 250 mV/dec. The low off-state leakage current level, below  $10^{-8}~kA/cm^2$ , reveals the effective current blocking by the n-p-n heterostructure in off state. The slight increase in gate leakage from  $1.2\times10^{-9}~kA/cm^2$  at  $V_{GS}=0~V$  to  $2.5\times10^{-6}~kA/cm^2$  at  $V_{GS}=15~V$  can be further reduced by optimizing the trench fabrication and the gate dielectric.

Fig. 2. (a) Semi-log, and (b) linear-scale transfer characteristics of the vertical trench gate MOSFETs on silicon substrate.

Fig. 2 (b) shows normally-off operation with a threshold voltage of 6.3 V (obtained by linear extrapolation) and peak transconductance of 269 S/cm<sup>2</sup>. The high  $V_{th}$  is preferable for high-power applications to guarantee a safe operation and better noise immunity. The channel mobility ( $\mu_{ch}$ ) extracted using the equation from Ref. [8] in the liner region was 17.8 cm<sup>2</sup>/(V·s), which is comparable to the value in Ref. [11] but lower than those from Refs. [8] and [9] (this value is underestimated due to additional series resistance induced by the thick drift layer (4  $\mu$ m) [32]). The lower  $\mu_{ch}$  is likely due to the typically larger defect density of GaN on silicon compared to that on bulk GaN substrates. In addition,  $\mu_{ch}$  can be enhanced by improving the sidewall smoothness with an optimized TMAH treatment process [29], [30].

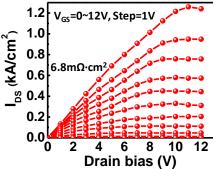

Fig. 3. Output I-V characteristics of the fabricated vertical trench gate MOSFETs on silicon substrate.

The output characteristic ( $I_D$ - $V_{DS}$ ) normalized by the trench area (Ref. [33]) is shown in Fig. 3. Good saturation behavior and an on-state current of  $\sim 1.3~kA/cm^2$  were observed at  $V_{GS}$  = 12 V and  $V_{DS}$  = 11 V. The specific on-resistance ( $R_{ON,SP}$ ) estimated from the linear region was 6.8 m $\Omega$ ·cm $^2$ . The calculated resistivity of each individual layer was  $1.28\times10^{-6}$  m $\Omega$ ·cm $^2$ ,  $3.78\times10^{-6}$  m $\Omega$ ·cm $^2$ ,  $1.77\times10^{-3}$  m $\Omega$ ·cm $^2$  for the source, drain, and drift layers, respectively (the contribution from

© 2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

contact resistances in vertical devices can be neglected [34]). These values are much smaller than the measured  $R_{ON,SP}$ , suggesting that the p-GaN channel layer and the spreading resistance in the drift region [35] are the main factor for the on-resistance. The larger channel resistivity is mainly due to our poorer channel mobility of 17.8 cm<sup>2</sup>/(V·s), compared to 131 cm<sup>2</sup>/(V·s) in Ref. [9].

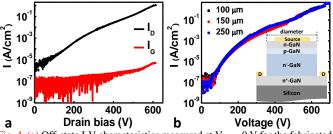

Fig. 4. (a) Off-state I-V characteristics measured at  $V_{GS} = 0$  V for the fabricated trench gate MOSFETs on silicon substrate, and (b) two terminal I-V characteristics of the as-grown n-p-n structure. The inset shows the schematic view of the measured n-p-n structure.

Fig. 4 (a) shows the off-state I-V characteristics measured at  $V_{\rm GS} = 0$  V for the fabricated trench gate MOSFET with floating substrate. The vertical MOSFETs exhibited a large hard breakdown voltage ( $V_{\rm Boff}$ ) of 645 V, while the gate current remained at a low value below  $10^{-5}$  A/cm², indicating that the breakdown occurred mainly between the source and drain terminals. The observed breakdown was destructive and mainly happened at the mesa edges. By introducing field-plates and edge-termination technologies to these devices, the electric field at the junction edge could be reduced, which would further enhance their breakdown voltage. However, the performance observed even without edge termination is quite remarkable which reveals the enormous potential for GaN on Si vertical transistors.

The measured  $V_{\rm Boff}$  was consistent with the vertical breakdown voltage measured from two-terminal circular n-p-n test structures of 679 V (Fig. 4 (b)). The similar leakage current density observed from these test structures with different mesa diameters (100 µm, 150 µm, and 250 µm), shown in Fig. 4 (b), indicates that the device leakage current mainly flows through the heterostructure, instead of the etched sidewalls [30]. The relation between leakage current density (I) and the average electric field (E) in the drift layer reveals the off-state leakage mechanism [36]. The nearly linear dependence of  $\ln(I) \propto E$  (extracted from Fig. 4 (a)) for the vertical MOSFETs indicates that the dominant leakage mechanisms in our devices is variable-range hopping [37].

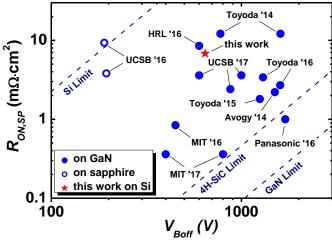

Fig. 5 shows the performance of our vertical trench gate MOSFETs on silicon substrates benchmarked against state-of-the-art E-mode vertical transistors on sapphire and GaN substrates [7], [12]-[20]. The  $V_{\rm Boff}$  of 645 V and  $R_{\rm ON,SP}$  of 6.8 mΩ·cm² resulted in a very good Baliga figure-of-merit (FOM) of 61 MW/cm², which is superior than devices fabricated on sapphire substrates. The FOM of these GaN-on-Si vertical MOSFETs can be significantly improved: 1. By utilizing TMAH treatment in the trenches with higher TMAH concentrations and longer durations to reduce  $R_{\rm ON,SP}$ ; 2. By designing field plates and edge terminations to enhance the  $V_{\rm Boff}$ ; 3. By substrate removal, as a fully vertical transistor

would significantly reduce current crowding in the bottom n-GaN layer towards the drain contact, thus reducing R<sub>ON,SP</sub>;

Fig. 5.  $R_{ON,SP}$  versus  $V_{Boff}$  benchmarks of the vertical trench gate MOSFETs on silicon substrates with state-of-the-art E-mode vertical transistors on sapphire and GaN substrates.

## IV. CONCLUSION

In summary, we have successfully demonstrated the first GaN vertical trench gate MOSFETs on 6-inch silicon substrates with a blocking voltage of 645 V. Normally-off operation was achieved with a threshold voltage of 6.3 V and an on/off ratio of over  $10^8$ . A specific on-resistance of 6.8 m $\Omega$ ·cm<sup>2</sup> was obtained. These results are very promising for the future adoption of GaN-on-Si for cost-effective high-voltage and high-power electronic applications.

### REFERENCES

- [1] B. Lu and T. Palacios, "High breakdown (>1500 V) AlGaN/GaN HEMTs by substrate-transfer technology," IEEE Electron Device Lett., vol. 31, no. 9, pp. 951–953, Sep. 2010, doi: 10.1109/LED.2010.2052587.

- [2] J. Ma and E. Matioli, "High Performance Tri-Gate GaN Power MOSHEMTs on Silicon Substrate," IEEE Electron Device Lett., vol. 38, no. 3, pp. 367–370, Mar. 2017. doi: 10.1109/LED.2017.2661755.

- [3] J. Ma and E. Matioli, "Slanted Tri-gates for High-Voltage GaN Power Devices.," IEEE Electron Device Lett., vol. 38, no. 9, pp. 1305–1308, Jul. 2017. doi: 10.1109/LED.2017.2731799.

- [4] H. Jiang, C. Liu, Y. Chen, X. Lu, C. W. Tang, and K. M. Lau, "Investigation of In Situ SiN as Gate Dielectric and Surface Passivation for GaN MISHEMTs.," IEEE Trans. Electron Devices., vol. 64, no. 3, pp. 832–839, Jan. 2017. doi: 10.1109/TED.2016.2638855.

- [5] S. Chowdhury, "Vertical Gallium Nitride Technology," in Power GaN Devices, Springer International Publishing, 2017, pp. 101–121.

- [6] S. Chowdhury, B. L. Swenson, M. H. Wong, and U. K. Mishra, "Current status and scope of gallium nitride-based vertical transistors for high power electronics application," Semicond. Sci. Technol., vol. 28, no. 7, p. 074014, Jul. 2013, doi: 10.1088/0268–1242/28/7/074014.

- [7] C. Gupta, S. H. Chan, Y. Enatsu, A. Agarwal, S. Keller and U. K. Mishra, "OG-FET: An in-situ Oxide, GaN interlayer based vertical trench MOSFET", IEEE Electron Device Lett., vol. 37, no. 12, pp.1601–1604, Dec. 2016. doi: 10.1109/LED.2016.2616508.

- [8] H. Otake, S. Egami, H. Ohta, Y. Nanishi, and H. Takasu, "GaN-based trench gate metal oxide semiconductor field effect transistors with over 100 cm<sup>2</sup>/(Vs) channel mobility," Jpn. J. Appl. Phys., vol. 46, no. 25, pp. L599–L601, Jul. 2007.doi: 10.1143/JJAP.46.L599.

- [9] H. Otake, K. Chikamatsu, A. Yamaguchi, T. Fujishima, and H. Ohta, "Vertical GaN-based trench gate metal oxide semiconductor field-effect transistors on GaN bulk substrates," Appl. Phys. Exp., vol. 1, no. 1, p. 011105, Jan. 2008, doi: 10.1143/APEX.1.011105.

© 2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

- [10] D. Ji, M. A. Laurent, A. Agarwal, W. Li, S. Mandal, S. Keller, and S. Chowdhury, "Normally OFF Trench CAVET With Active Mg-Doped GaN as Current Blocking Layer." IEEE Trans. Electron Devices, vol. 64, no. 3, pp 805–808, Mar. 2017, doi: 10.1109/TED.2016.2632150.

- [11] C. Gupta, S. H. Chan, C. Lund, A. Agarwal, O. Koksaldi, J. Liu, Y. Enatsu, S. Keller, and U. K. Mishra, "Comparing electrical performance of GaN trench-gate MOSFETs with a-plane (1120) and m-plane (1100) sidewall channels," Appl. Phys. Exp., vol. 9, no. 12, pp. 121001-1–121001-3, Nov. 2016, doi: 10.7567/APEX.9.121001.

- [12] C. Gupta, A. Agarwal, S. H. Chan, O. S. Koksaldi, S. Keller and U.K. Mishra, "1 kV field plated in-situ Oxide, GaN interlayer based vertical trench MOSFET (OG-FET)", in Proc. 75th Annu. Device Res. Conf. (DRC), Jun 2017, pp. 1–2, doi: 10.1109/DRC.2017.7999410.

- [13] C. Gupta, C. Lund, S. H. Chan, A. Agarwal, J. Liu, Y. Enatsu, S. Keller and U.K. Mishra, "In-situ Oxide, GaN interlayer based vertical trench MOSFET (OG-FET) on bulk GaN substrates", IEEE Electron Device Lett., vol. 38, no. 3, pp. 353–356, Mar. 2017. doi: 10.1109/LED.2017.2649599.

- [14] M. Sun, Y. Zhang, X. Gao and T. Palacios, "High performance GaN vertical fin power transistors on bulk GaN substrate", IEEE Electron Device Lett., vol. 38, no. 4, pp. 509–512, Apr. 2017, doi: 10.1109/LED.2017.2670925.

- [15] T. Oka, Y. Ueno, T. Ina, and K. Hasegawa, "Vertical GaN-based trench metal oxide semiconductor field effect transistors on a free-standing GaN substrate with blocking voltage of 1.6 kV," Appl. Phys. Exp., vol. 7, no. 2, p. 021002, 2014, doi: 10.7567/APEX.7.021002.

- [16] T. Oka, T. Ina, Y. Ueno and J. Nishii, "1.8 m $\Omega$ ·cm² vertical GaN-based trench metal—oxide—semiconductor field-effect transistors on a freestanding GaN substrate for 1.2-kV-class operation," Appl. Phys. Exp., vol. 8, no. 5, pp. 054101-1–054101-3, May. 2015, doi:10.7567/APEX.8.054101.

- [17] T. Oka, T. Ina, Y. Ueno, and J. Nishii, "Over 10 a operation with switching characteristics of 1.2 kV-class vertical GaN trench MOSFETs on a bulk GaN substrate," in Proc. 28th Int. Symp. Power Semiconductor Devices ICs (ISPSD), Jun. 2016, pp. 459–462, doi: 10.1109/ISPSD.2016.7520877.

- [18] R. Li, Y. Cao, M. Chen and R. Chu, "600V/1.7Ω Normally-Off GaN Vertical Trench Metal-Oxide-Semiconductor Field-Effect Transistor", IEEE Electron Device Lett., vol. 37, no. 11, pp.1466–1469, Nov. 2016, doi: 10.1109/LED.2016.2614515.

- [19] H. Nie, Q. Diduck, B. Alvarez, A. P. Edwards, B. M. Kayes, M. Zhang, G. Ye, T. Prunty, D. Bour and I. C. Kizilyalli, "1.5-kV and 2.2-mΩ.cm² vertical GaN transistors on bulk-GaN substrates," IEEE Electron Device Lett., vol. 35, no. 9, pp. 939–941, Sep. 2014, doi: 10.1109/LED.2014.2339197.

- [20] D. Shibata, R. Kajitani, M. Ogawa, K. Tanaka, S. Tamura, T. Hatsuda, M. Ishida, and T. Ueda, "1.7 kV/1.0 mΩ·cm² normally-off vertical GaN transistor on GaN substrate with regrown p-GaN/AlGaN/GaN semipolar gate structure," in IEDM Tech. Dig., 2016, pp. 10.1.1–10.1.4, doi: 10.1109/IEDM.2016.7838385.

- [21] J. Ma, X. Zhu, K. M. Wong, X. Zou, and K. M. Lau, "Improved GaN based LED grown on silicon (111) substrates using stress/dislocationengineered interlayer," J. Cryst. Growth, vol. 370, pp. 265–268, May 2013, doi: 10.1016/j.jcrysgro.2012.10.028.

- [22] J. Ren, C. Liu, C. W. Tang, K. M. Lau, and J. K. O. Sin, "A Novel Si–GaN Monolithic Integration Technology for a High-Voltage Cascoded Diode," IEEE Electron Device Lett., vol. 38, no. 4, pp. 501–504, Feb. 2017, doi: 10.1109/LED.2017.2665698.

- [23] X. Zhang, X. Zou, X. Lu, C. W. Tang, and K. M. Lau, "Fully- and Quasi-Vertical GaN-on-Si p-i-n Diodes: High Performance and Comprehensive Comparison," IEEE Trans. Electron Devices, vol. 64, no. 3, pp. 809–815, Mar. 2017, doi: 10.1109/TED.2017.2647990.

- [24] X. Zou, X. Zhang, X. Lu, C. W. Tang, and K. M. Lau, "Fully Vertical GaN p-i-n Diodes Using GaN-on-Si Epilayers," IEEE Electron Device Lett., vol. 37, no. 5, pp. 636–639, May 2016, doi: 10.1109/LED.2016.2548488.

- [25] X. Zou, X. Zhang, X. Lu, C. W. Tang, and K. M. Lau, "Breakdown Ruggedness of Quasi-Vertical GaN-Based p-i-n Diodes on Si Substrates," IEEE Electron Device Lett., vol. 37, no. 9, pp. 1158–1161, Sep. 2016, doi: 10.1109/LED.2016.2594821.

- [26] S. Mase, Y. Urayama, T. Hamada, J. J. Freedsman, and T. Egawa, "Novel fully vertical GaN p-n diode on Si substrate grown by metalorganic chemical vapor deposition," Appl. Phys. Exp., vol. 9, no. 11, p. 111005, Nov. 2016, doi: 10.7567/APEX.9.111005.

- [27] Y. Zhang, M. Sun, D. Piedra, M. Azize, X. Zhang, T. Fujishima, and T. Palacios, "GaN-on-Si Vertical Schottky and p-n Diodes," IEEE Electron Device Lett., vol. 35, no. 6, pp. 618–620, Jun. 2014, doi: 10.1109/LED.2014.2314637.

- [28] Y. Zhang, D. Piedra, M. Sun, J. Hennig, A. Dadgar, L. Yu, and T. Palacios, "High-Performance 500 V Quasi- and Fully- Vertical GaN-on-Si pn Diodes," IEEE Electron Device Lett., vol. 38, no. 2, pp. 248–251, Feb. 2017, doi: 10.1109/LED.2016.2646669.

- [29] M. Kodama, M. Sugimoto, E. Hayashi, N. Soejima, O. Ishiguro, M. Kanechika, K. Itoh, H. Ueda, T. Uesugi, and T. Kachi, "GaN-Based Trench Gate Metal Oxide Semiconductor Field-Effect Transistor Fabricated with Novel Wet Etching," Appl. Phys. Exp., vol. 1, no. 2, pp. 021104-1 021104-3, Feb. 2008, doi: 10.1143/APEX.1.021104.

- [30] Y. Zhang, M. Sun, H. Wong, Y. Lin, P. Srivastava, C. Hatem, M. Azize, D. Piedra, L. Yu, T. Sumitomo, N. Braga, R. Mickevicius, and T. Palacios, "Origin and Control of OFF-State Leakage Current in GaN-on-Si Vertical Diodes." IEEE Trans. Electron Devices, vol. 62, no. 7, pp 2155–2161, Jul. 2015, doi: 10.1109/TED.2015.2426711.

- [31] Y. Zhang, M. Sun, Z. Liu, D. Piedra, J. Hu, X. Gao, and T. Palacios, "Trench formation and corner rounding in vertical GaN power devices." Appl. Phys. Lett., vol. 110, no. 19, pp. 193506-1–193506-4, May. 2017, doi: 10.1063/1.4983558.

- [32] Y. EL-Mansy, "MOS Device and Technology Constraints in VLSI." IEEE Trans. Electron Devices, vol. ED-29, no. 4, pp 567–573, Apr. 1982, doi: 10.1109/T-ED.1982.20744.

- [33] W. Li, K. Nomoto, K. Lee, S. Islam, Z. Hu, M. Zhu, X. Gao, M. Pilla, D. Jena, and H. G. Xing, "600 V GaN vertical V-trench MOSFET with MBE regrown channel," in Proc. 75th Annu. Device Res. Conf. (DRC), Jun 2017, pp. 1–2, doi: 10.1109/DRC.2017.7999414.

- [34] Y. Cao, R. Chu, R. Li, M. Chen, R. Chang, and B. Hughes, "High-voltage vertical GaN Schottky diode enabled by low-carbon metal-organic chemical vapor deposition growth," Appl. Phys. Lett., vol. 108, no. 6, pp. 062103-1–062103-4, Feb. 2016, doi: 10.1063/1.4941814.

- [35] Y. Zhang, M. Sun, D. Piedra, J. Hennig, A. Dadgar, and T. Palacios, "Reduction of on-resistance and current crowding in quasi-vertical GaN power diodes," Appl. Phys. Lett., vol. 111, no. 16, pp. 163506-1– 163506-4, Oct. 2017, doi: 10.1063/1.4989599.

- [36] Y. Zhang, H. Y. Wong, M. Sun, S. Joglekar, L. Yu, N. A. Braga, R. V. Mickevicius, and T. Palacios, "Design space and origin of off-state leakage in GaN vertical power diodes," in Proc. IEEE Int. Electron Devices Meeting (IEDM), Dec. 2015, pp. 35.1.1–35.1.4, doi: 10.1109/IEDM.2015.7409830.

- [37] D. Han, C. Oh, H. Kim, J. Shim, K. Kim, and D. Shin, "Conduction Mechanisms of Leakage Currents in InGaN/GaN-Based Light-Emitting Diodes", IEEE Trans. Electron Devices, vol. 62, no. 2, pp. 587–592, Feb. 2015, doi: 10.1109/TED.2014.2381218.