# Machine Learning Support for Logic Diagnosis

Von der Fakultät Informatik, Elektrotechnik und Informationstechnik der Universität Stuttgart zur Erlangung der Würde eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigte Abhandlung

Vorgelegt von

# Laura Isabel Rodríguez Gómez

aus Madrid, Spanien

Hauptberichter: Prof. Dr. Hans-Joachim Wunderlich

Mitberichter: Prof. Dr. Sybille Hellebrand

Tag der mündlichen Prüfung: 13. Juli 2017

Institut für Technische Informatik der Universität Stuttgart

To my grandpa Jesús

# **CONTENTS**

| A  | cknov  | wledgn   | nents                                         | xiii |

|----|--------|----------|-----------------------------------------------|------|

| Al | bstrac | ct       |                                               | xv   |

| Zι | ısamı  | menfa    | ssung                                         | xvii |

| 1  | Intr   | oducti   | on                                            | 1    |

| 2  | Def    | ects, fa | ults and errors                               | 9    |

|    | 2.1    | Defec    | t mechanisms                                  | 10   |

|    |        | 2.1.1    | Manufacturing                                 | 11   |

|    |        | 2.1.2    | Lifetime                                      | 14   |

|    | 2.2    | Fault    | models                                        | 17   |

|    |        | 2.2.1    | Stuck-at faults                               | 17   |

|    |        | 2.2.2    | Delay faults                                  | 17   |

|    |        | 2.2.3    | Bridges                                       | 18   |

|    |        | 2.2.4    | Transistor faults                             | 20   |

|    |        | 2.2.5    | Non-determinism in fault models               | 20   |

|    | 2.3    | Reliab   | oility and yield                              | 21   |

|    |        | 2.3.1    | Yield ramping                                 | 21   |

|    |        | 2.3.2    | Lifetime tests                                | 25   |

| 3  | Test   | t, diagr | nosis and fault classification                | 27   |

|    | 3.1    | Test a   | lgorithms                                     | 28   |

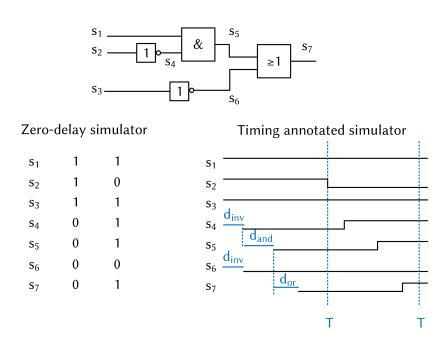

|    |        | 3.1.1    | Logic simulation                              | 28   |

|    |        | 3.1.2    | Test generation                               | 34   |

|    |        | 3.1.3    | Logic diagnosis                               | 37   |

|    | 3.2    | Manu     | facturing test                                | 41   |

|    |        | 3.2.1    | Test flow                                     | 42   |

|    |        | 3.2.2    | Test infrastructure                           | 43   |

|    |        | 3.2.3    | Test and diagnosis                            | 46   |

|    | 3.3    | Onlin    | e test and diagnosis                          | 48   |

|    |        | 331      | Concurrent and non-concurrent structural test | 18   |

### Contents

|   |      | 3.3.2   | Software-based self-test                                | 53  |

|---|------|---------|---------------------------------------------------------|-----|

|   |      | 3.3.3   | Automotive in-system test                               | 55  |

|   | 3.4  | Test d  | ata                                                     | 62  |

|   | 3.5  | Fault o | classification and physical failure analysis            | 63  |

| 4 | Circ | cuit un | certainty and machine learning                          | 67  |

|   | 4.1  | Machi   | ine learning and indeterminism                          | 68  |

|   | 4.2  | Source  | es of circuit uncertainty                               | 69  |

|   |      | 4.2.1   | Noise and environmental conditions                      | 69  |

|   |      | 4.2.2   | Variations                                              | 71  |

|   |      | 4.2.3   | Inaccurate modeling                                     | 75  |

|   | 4.3  | Machi   | ine learning                                            | 77  |

|   |      | 4.3.1   | Graphical models                                        | 78  |

|   |      | 4.3.2   | Supervised learning                                     | 79  |

|   |      | 4.3.3   | Unsupervised learning                                   | 81  |

|   | 4.4  | Root o  | cause identification and yield learning                 | 82  |

| 5 | Bay  | esian r | networks for identifying critical defects               | 85  |

|   | 5.1  | Adapt   | ive test and diagnosis                                  | 88  |

|   | 5.2  | Imme    | diate critical fault discrimination                     | 89  |

|   | 5.3  | Bayes   | ian networks                                            | 90  |

|   |      | 5.3.1   | Probabilities in Bayesian networks                      | 91  |

|   |      | 5.3.2   | Bayesian network structure                              | 92  |

|   |      | 5.3.3   | Inference in Bayesian networks                          | 93  |

|   | 5.4  | Critica | al fault discrimination with Bayesian networks          | 96  |

|   | 5.5  | Exper   | imental validation                                      | 99  |

|   |      | 5.5.1   | Injected faults                                         | 99  |

|   |      | 5.5.2   | Intermittent fault classification                       | 100 |

|   |      | 5.5.3   | Transient fault classification                          | 102 |

|   |      | 5.5.4   | Intermittent fault with background noise classification | 104 |

| 6 | Neu  | ral net | tworks for defect classification                        | 107 |

|   | 6.1  | Faults  | to be distinguished                                     | 110 |

|   | 6.2  | Featur  | res                                                     | 112 |

|   |      | 6.2.1   | Failing pattern information                             | 112 |

|   |      | 6.2.2   | Passing pattern information                             | 118 |

### Contents

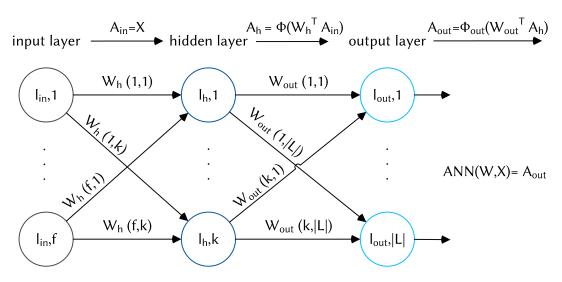

|    | 6.3    | Artific | cial neural networks for fault classification                   | 120 |

|----|--------|---------|-----------------------------------------------------------------|-----|

|    |        | 6.3.1   | Artificial neural networks: structure                           | 120 |

|    |        | 6.3.2   | Artificial neural networks: learning                            | 123 |

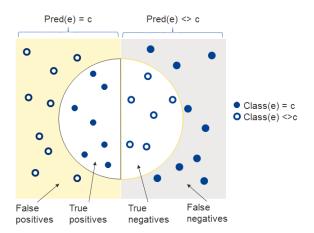

|    |        | 6.3.3   | Metrics for neural network based classifiers                    | 124 |

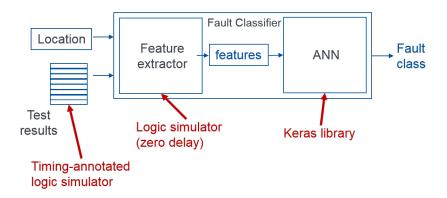

|    |        | 6.3.4   | Artificial neural networks for fault classification             | 127 |

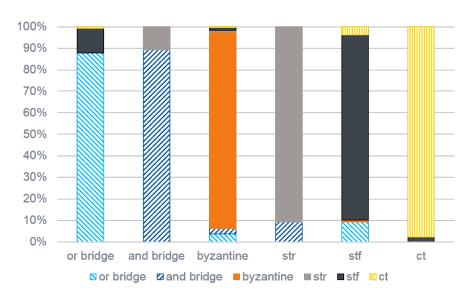

|    | 6.4    | Exper   | imental validation                                              | 127 |

|    |        | 6.4.1   | Fault classification after test                                 | 129 |

|    |        | 6.4.2   | Fault classification based exclusively on failing information . | 133 |

|    |        | 6.4.3   | Fault identification without product knowledge                  | 136 |

|    |        | 6.4.4   | Identification of intermittent faults                           | 140 |

| 7  | Con    | clusio  | ns and future work                                              | 147 |

|    | 7.1    | Future  | ework                                                           | 148 |

| Bi | bliog  | raphy   |                                                                 | 151 |

| In | dex    |         |                                                                 | 171 |

| Pυ | ıblica | tions o | of the Author                                                   | 173 |

# **LIST OF FIGURES**

| Cha | pter 1                                                     |

|-----|------------------------------------------------------------|

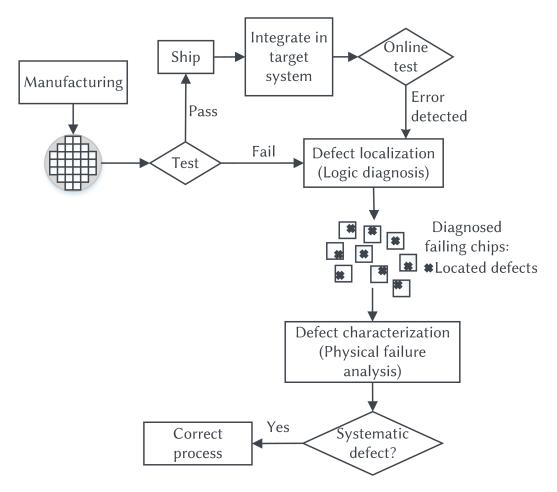

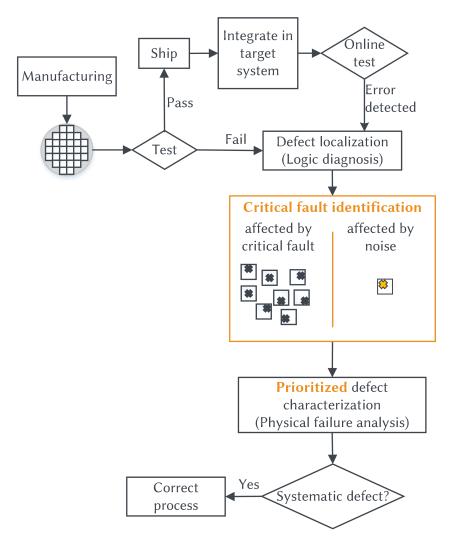

| 1.1 | Test and diagnosis flow after manufacturing                |

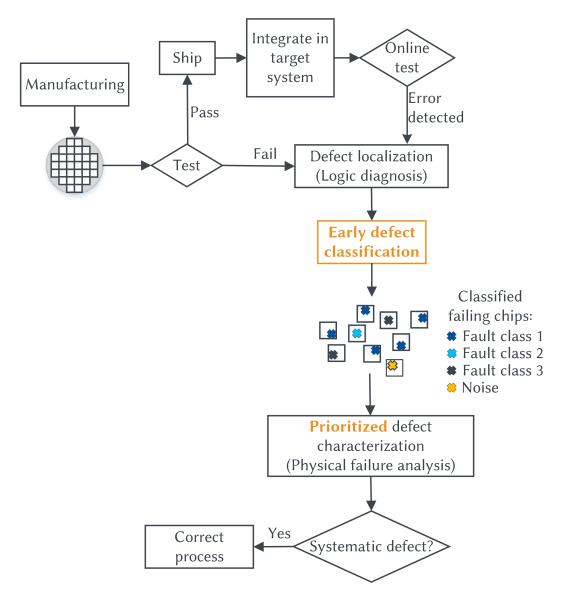

| 1.2 | Test and diagnosis flow after manufacturing: proposed flow |

| Cha | pter 2                                                     |

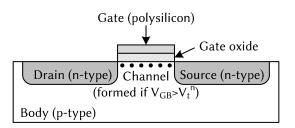

| 2.1 | nMOS transistor                                            |

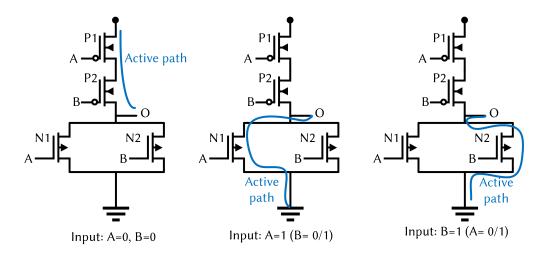

| 2.2 | CMOS NOR cell: transistor structure                        |

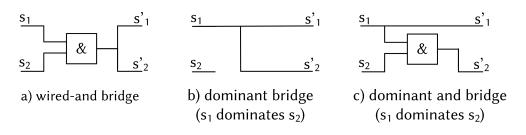

| 2.3 | Bridge fault models                                        |

| Cha | apter 3                                                    |

| 3.1 | Pessimism in three-valued simulation                       |

| 3.2 | Zero-delay vs timing annotated simulator                   |

| 3.3 | Metrics for logic diagnosis                                |

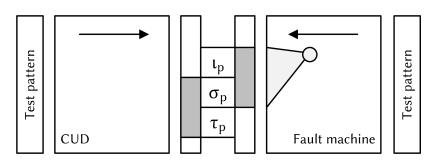

| 3.4 | Rollback test flow                                         |

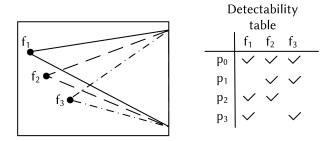

| 3.5 | Circuit and detectability table                            |

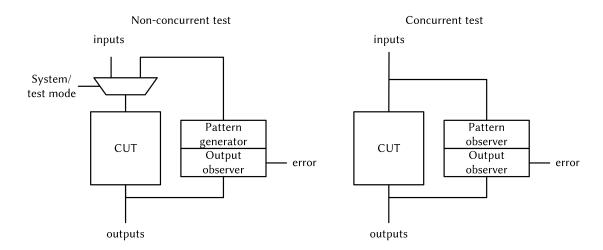

| 3.6 | Concurrent vs non-concurrent test                          |

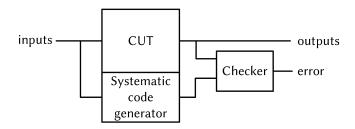

| 3.7 | Intrusive concurrent testers                               |

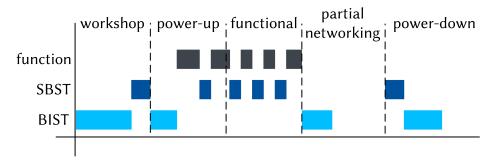

| 3.8 | In-system structural test integration                      |

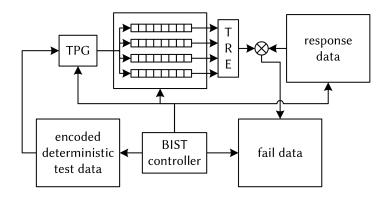

| 3.9 | BIST diagnostic architecture                               |

| Cha | pter 4                                                     |

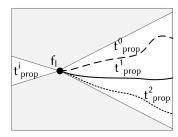

| 4.1 | Indeterminism in timing faults                             |

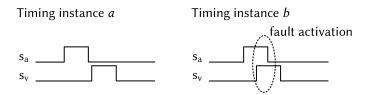

| 4.2 | Indeterminism in static faults                             |

| Cha | pter 5                                                     |

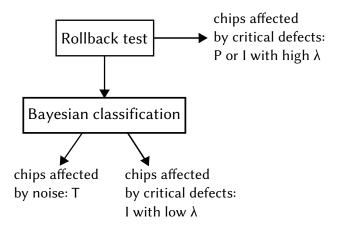

| 5.1 | Diagnosis flow with critical fault identification          |

| 5.2 | Adaptive flow for critical fault identification            |

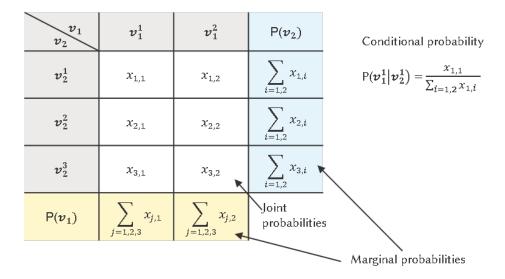

| 5.3 | Joint and marginal probabilities                           |

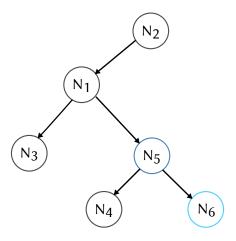

| 5.4 | Bayesian network structure                                 |

# Figures

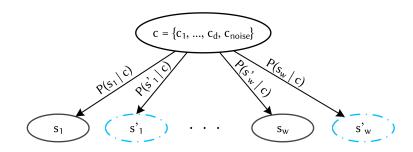

| 5.5  | Bayesian network for critical fault classification                                     | 97  |

|------|----------------------------------------------------------------------------------------|-----|

| 5.6  | Topological neighborhood N(2) of victim line $f$                                       | 100 |

|      |                                                                                        |     |

| Cha  | pter 6                                                                                 |     |

| 6.1  | Observed test response for different fault classes                                     | 108 |

| 6.2  | Complete diagnosis flow with early fault class identification                          | 109 |

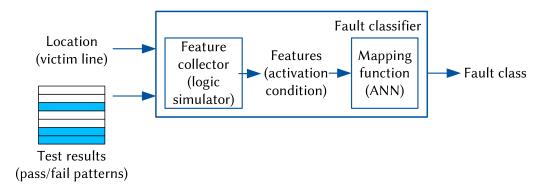

| 6.3  | Structure of the fault classifier                                                      | 110 |

| 6.4  | Driving gate inputs                                                                    | 114 |

| 6.5  | Multilayer feedforward ANN                                                             | 122 |

| 6.6  | Classification outcome: prediction vs actual category                                  | 125 |

| 6.7  | Experimental setup                                                                     | 128 |

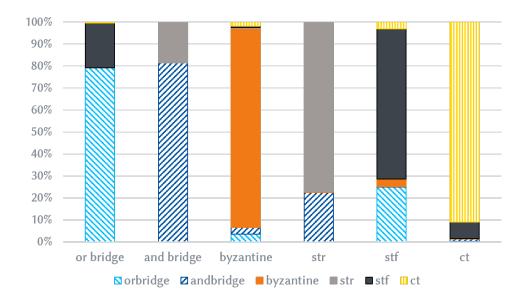

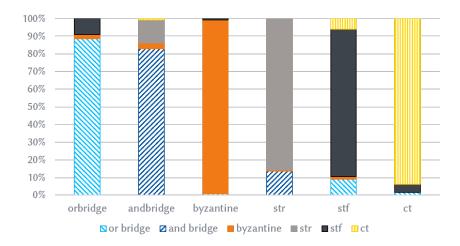

| 6.8  | Classification distribution per fault class                                            | 132 |

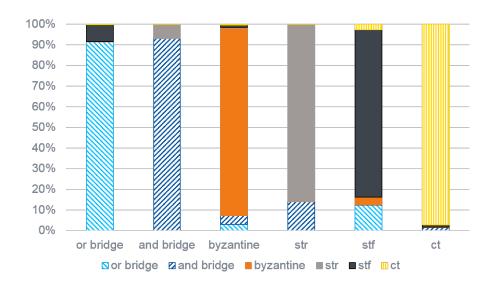

| 6.9  | Classification distribution for classification based on failing information.           | 136 |

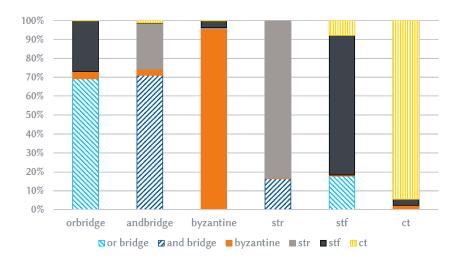

| 6.10 | Classification distribution per fault class (without product knowledge) .              | 138 |

| 6.11 | Distribution for classification based on failing information and without               |     |

|      | product knowledge                                                                      | 140 |

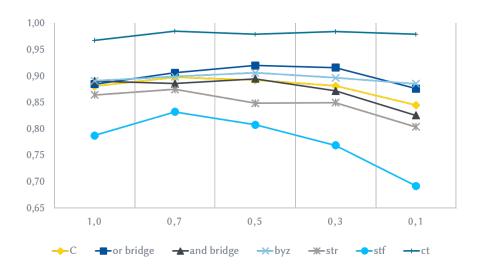

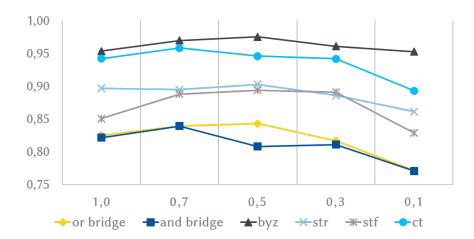

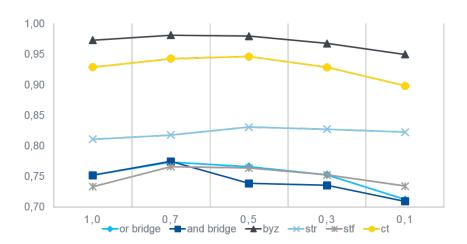

| 6.12 | Recall evolution for decreasing activation rates of intermittent faults in test        | 142 |

| 6.13 | Precision evolution for decreasing activation rates of intermittent faults             |     |

|      | in test                                                                                | 142 |

| 6.14 | Classification distribution for intermittent faults after test                         | 143 |

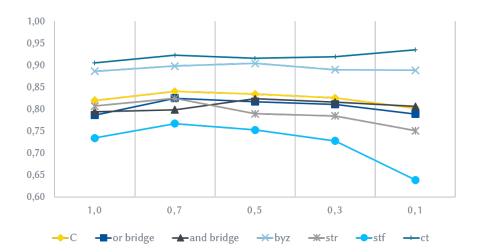

| 6.15 | Recall evolution for decreasing activation rates of intermittent faults in test        | 144 |

| 6.16 | Precision evolution for decreasing activation rates of intermittent faults             |     |

|      | after online error detection                                                           | 144 |

| 6.17 | Classification pattern for $p35k$ intermittents with $\lambda_{act} = 0.5 \dots \dots$ | 145 |

# **LIST OF TABLES**

| Cha  | pter 5                                                                                                                      |     |

|------|-----------------------------------------------------------------------------------------------------------------------------|-----|

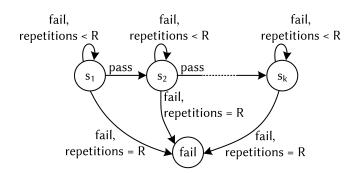

| 5.1  | Codes for test sessions depending on the outcome of rollback test for                                                       |     |

|      | $R_{max} = 2. \dots $ | 89  |

| 5.2  | Classification results for intermittents with $R_{max} = 2$ and $T_{max} = 10$                                              | 101 |

| 5.3  | Bayesian classification for intermittents                                                                                   | 102 |

| 5.4  | Classification results for transients with $R_{max} = 2$ and $T_{max} = 21$                                                 | 103 |

| 5.5  | Bayesian classification for transients                                                                                      | 103 |

| 5.6  | Classification results for intermittents in presence of background noise                                                    |     |

|      | with $R_{max} = 2$ and $T_{max} = 10$                                                                                       | 104 |

| 5.7  | Bayesian classification for intermittents in presence of background noise.                                                  | 105 |

|      |                                                                                                                             |     |

| Cha  | pter 6                                                                                                                      |     |

| 6.1  | Activation conditions for all fault classes                                                                                 | 113 |

| 6.2  | Accuracy results for classification after test, with product knowledge                                                      | 129 |

| 6.3  | Classification recall results after test, with product knowledge                                                            | 130 |

| 6.4  | Precision results for classification after test, with product knowledge                                                     | 131 |

| 6.5  | Classification accuracy results after online error detection, with product                                                  |     |

|      | knowledge                                                                                                                   | 134 |

| 6.6  | Classification recall results after online error detection, with product                                                    |     |

|      | knowledge                                                                                                                   | 134 |

| 6.7  | Precision results for classification with failing information                                                               | 135 |

| 6.8  | Classification recall results after test, without product knowledge                                                         | 137 |

| 6.9  | Precision results for classification after test, with no product knowledge                                                  | 138 |

| 6.10 | Recall results after online error detection, without product knowledge .                                                    | 139 |

| 6.11 | Precision results for classification with failing information                                                               | 139 |

# **ACKNOWLEDGMENTS**

This work would have never been possible without the contribution of many people, and I am happy to have the chance to express my gratitude.

I would like to thank Prof. Hans-Joachim Wunderlich for the opportunity to work at his department, where I found the space to grow and to learn how to approach scientific work, and also for the interesting discussions that greatly contributed to this thesis. I want to thank Prof. Sybille Hellebrand for her always constructive feedback and questions. Special thanks go to Marcus Eggenberger for his help with the German summary of this work.

A big thanks is due to my colleagues at the Institut für Technische Informatik for many insightful discussions. I am particularly grateful to those with whom I had the pleasure of sharing my teaching responsabilities: Rafał Baranowski, Chang Liu, Alejandro Cook, Dominik Ull, Eric Schneider, Claus Braun, Alexander Schöll and Ahmed Atteya. I am also thankful to Mirjam Breitling, Helmut Häfner and Lothar Hellmeier for their administrative and technical assistance.

I am greatly indebted to Willi Kessler, Gert Schley, Marcus Eggenberger, Manuel Strobel, Adrià Sales, Anto Levatino, Edu Ferrera and Max Schwilk, for sharing their experiences as PhD students in various universities and disciplines and providing me with continuous support.

Finally, my biggest debts of gratitude. To Pablo, for his patience and for his encouragement throughout the rockiest parts of the way. And to my parents and sisters, whose love and support in all of my adventures and undertakings are invaluable.

Stuttgart, July 2017

Laura Rodríguez Gómez

# **ABSTRACT**

Tiny feature sizes in deep submicron technologies pose both a yield and reliability threat. Imperfections in the manufacturing process may introduce systematic defects, especially as the first devices are produced when the process is not yet mature. The identification and correction of systematic process problems calls for efficient test and diagnosis techniques. Due to the increasing amount of variations introduced in the process parameters, however, these techniques must also tolerate a certain degree of indeterminism.

Chips that pass manufacturing test are then shipped to the customer and integrated in their target system. During the lifetime of a circuit wearout mechanisms can cause some of the structures to degrade. As a result, defects may appear in originally healthy chips. To avoid catastrophic consequences, many systems include in-the-field test techniques, which allow the detection of such problems. After detection, the defective parts must be diagnosed to identify any possible systematic degradation patterns, which point to weak structures. In addition to the indeterminism introduced by variations, the exact environmental conditions are unknown when in the field. Thus, test and diagnosis in the field must also handle uncertainty.

Whether after manufacturing or after online test, defective parts undergo logic diagnosis to locate the fault, and then physical failure analysis (PFA) to characterize the fault. However, PFA is a costly procedure because it requires physical inspection of the chip area. It benefits from logic diagnosis, which performs fault localization and narrows down the suspect area. PFA also benefits from a fast identification of the problem that would allow a prioritization of costly physical analysis procedures. Such a characterization is especially interesting in the case of faults which disappear when analyzed in the lab, either because they were only affected by noise or because the underlying fault is partially reversible. This thesis presents a fast characterization method which can be integrated in the diagnosis flow. It takes advantage of machine learning techniques, which can handle inaccurate or ambiguous information. The method incurs minimal overhead, and characterizes faults detected in manufacturing test as well as online.

# **ZUSAMMENFASSUNG**

Die fortschreitende Skalierung von Prozesstechnologien gefährdet sowohl die Produktionsausbeute als auch die Zuverlässigkeit. Gerade bei neuen Fertigungsprozessen können Herstellungsfehler zu systematischen Defekten in Schaltungen führen. Um solche Defekte zu finden und den Fertigungsprozess zu überarbeiten, werden effiziente Test- und Diagnoseverfahren benötigt. Eine zunehmende Variabilität in den Prozessparametern führt zu Indeterminismen in den Fertigungsergebnissen, und die eingesetzten Test- und Diagnoseverfahren müssen diese tolerieren können.

Chips, die den Fertigungstest bestehen, werden an Kunden ausgeliefert und ins Zielsystem eingebaut. Über die Lebensdauer des Chips hinweg kommen allerdings Alterungserscheinungen zum Tragen, die zum Verschleiß einzelner Strukturen und damit wiederum zu Defekten führen können. Daher werden in der Praxis häufig sogenannte Onlinetests während des Betriebs eingesetzt, um solche Probleme frühzeitig zu erkennen und größere Schäden zu verhindern.

Nachdem ein Problem erkannt wurde, müssen die fehlerhaften Chips untersucht werden, um die Strukturen zu identifizieren, die für Alterung anfällig sind. Hierbei muss die Diagnose einen weiteren Indeterminismusfaktor berücksichtigen, da die genauen Umgebungsbedingungen, die den Fehler aktiviert haben, zum Diagnosezeitpunkt zumeist nicht bekannt sind.

Um systematische Defekte zukünftig zu vermeiden und den Fertigungsprozess zu überarbeiten, muss nach der Diagnose noch eine physikalische Analyse (PA) durchgeführt werden. Da diese Analyse sehr aufwändig ist, wird die Fehlerregion zunächst durch eine Logikdiagnose eingeschränkt. Die Logikdiagnose kann allerdings nicht zwischen systematischen und unsystematischen Defekten unterscheiden, so dass keine priorisierte physikalische Analyse für Chips mit systematischen Defekten vorgenommen werden kann.

Diese Doktorarbeit stellt ein Verfahren vor, das eine schnelle Fehlerklassifikation und damit eine priorisierte physikalische Analyse ermöglicht. Das Verfahren basiert auf maschinellem Lernen, und kann mit Indeterminismus umgehen. Sowohl Herstellungsals auch Alterungsdefekte werden sehr schnell charakterisiert. Dabei sind die Kosten des Verfahrens sehr gering und es kann problemlos in bestehende Diagnoseprozesse integriert werden.

# CHAPTER

# Introduction

Short time-to-market requires the semiconductor industry to produce high quality electronic devices as efficiently as possible. The time constraint requires efficient test and diagnosis procedures, as well as fast systematic problem identification to speed up yield learning. Manufacturing and test are complex processes which deal with increasing degrees of uncertainty as technology evolves and moves in the deep submicron regime. Uncertainty affects also the diagnostic process, which can only confirm the nature of the problem after costly physical analysis of the defective parts. An electronic device is printed on a silicon wafer by doping different regions of the semiconductor with different donors and forming transistors, which are in turn con-

semiconductor with different donors and forming transistors, which are, in turn, connected with polysilicon or metal wires to form cells. Cells are finally connected by metal wires and conform the complete structure of the circuit. The production process is, however, error prone. It tends to introduce excess or voids in the material, causing circuits to deviate from their functional or performance specification. For instance, an accidental connection between two metal wires or a void in an interconnect cause the circuit to implement a different function. A crack in an interconnect, on the other hand, increases the resistance in the wire and may potentially introduce an additional delay. These distortions in the physical structure of the chip are referred to as point defects.

Due to limitations in the manufacturing tools, chips fabricated in recent technologies are affected by variations. Variations cause different devices that implement the same

design to exhibit diverging timing behaviors. Thus, each instance of a design may have a different maximum frequency and minimum supply voltage that ensure its correct operation. If exercised in conditions over its performance capacity, the device will produce incorrect output values.

To screen out defective chips, all devices must undergo manufacturing test. Tests are performed on all produced chips to ensure high product quality. The objective of test is to exercise the structure of the circuit thoroughly in a short time, uncovering a large number of point defects effectively. Test checks the observed responses against the expected ones and splits the chips in two groups: pass and fail.

The pass/fail categories do not correspond exactly to healthy/faulty chips. Devices which passed all tests are deemed healthy and can be shipped to the customer, the faulty ones must be further analyzed, and not just discarded. A careful analysis must be performed to distinguish those circuits affected by point defects from those only affected by variations, and which could work in different environmental conditions. This is so for two reasons: it allows early correction of systematic problems and avoids unnecessary yield loss. Moreover, the tiny structures in deep submicron technologies are sensitive to noise. In addition to distinguishing errors caused by point defects from those caused by performance limitations, a mechanism is needed to identify incorrect behavior caused by transient noise. Correctly identifying all cases allows to ship high-quality devices while avoiding discarding healthy chips.

While a process is not mature, it renders low yield values, that is, a high rate of the produced chips is defective. Identifying the systematic problems and its root cause allows correcting the process and enhances yield ramp-up. An early systematic problem detection is hence crucial to ensure the efficiency of the manufacturing process.

Detecting systematic problems requires identifying the location, nature and size of the point defect. The goal is to correct the process as soon as possible to fabricate larger numbers of fault-free devices. The diagnosis procedure is responsible for the problem identification task. Diagnosis is applied only to failing chips, and often includes logic diagnosis, a second diagnostic pass and physical failure analysis. Logic diagnosis locates the faulty line in the device. The algorithms typically take the results of test as a starting point. However, test detects the problem, but its goal does not include diagnostic resolution. Diagnosis benefits from larger amounts of information than those provided by test. For this reason, a second diagnostic test pass is often performed to extract more information about the possible underlying cause. The diagnostic pass

may include adaptively generating new test patterns which guide the diagnosis more precisely. This process can be performed for every faulty device. Because additional information may help discard or confirm candidate locations, its application is costly but extremely useful to narrow down the defect location.

After diagnosis, failure analysis physically analyzes the chip to confirm the location and identify the nature of the problem. With nowadays size and complexity, the analysis would need to cover a large surface. Also, since the process may be partially destructive, targeting the correct location in the first attempt is a requirement. The analysis of the location reveals the underlying physical distortion. A large number of defective chips affected by the same distortion indicates a systematic problem. Early correction of systematic problems can succeed if systematic problems are detected and correctly identified in a timely manner. By using as an input the outcome of logic diagnosis, the area to be studied can be reduced to a few locations, which eases and speeds up physical analysis. The nature of the problem, however, must be identified by physical failure analysis.

Although effective, the root cause identification procedure presents some problems. The first is its time consuming nature. Chips are analyzed in no particular order. As the chip is detected to malfunction, it undergoes diagnosis and is then queued for physical failure analysis. This is a suboptimal strategy: not only are the checks for different defect types heterogeneous, but also an earlier exam of devices affected by systematic problems would confirm the root cause sooner and hence speed up yield ramp-up. The second is the nature of some of the problems present in devices. High-frequency power droop or crosstalk effects are not as easily visible as additional metal connecting two independent wires. They are only active in specific conditions and may sometimes indicate a problem in the design or in operating conditions rather than in manufacturing. Even worse, if the chip was only affected by noise, it does not present any weak or defective structures, and so physical analysis will not be able to draw any conclusion.

The need for defect detection and diagnosis is not exclusive of manufacturing test. Fault-free devices at the time of shipping may still fail in their intended environment. This can be caused by noise in the environment that affects the nanometer structures, or due to degradation. Wearout mechanisms can cause the transistors and interconnects in a digital device to degrade until permanent malfunction. Defects can hence also appear online after a certain time. For this reason, and very particularly in safety critical applications, online tests are introduced.

### 4 Chapter 1 • Introduction

Like for manufacturing test, structural tests are highly effective to uncover defects. However, to be applicable online, they need to be carefully integrated in the system in order not to disrupt its function and performance properties. If the integration is successful, online test has the advantage that some faults are only detectable in this scenario, as their activation conditions may only be fulfilled in very specific environments or configurations.

Devices detected to be faulty during operational mode are returned to the manufacturer, who must analyze them to detect any possible generalized degradation profiles. Diagnosis and physical failure analysis are again performed. However, the amount of information gathered and stored in a safety critical system is typically limited due to cost or scheduling constraints. The available test data after online test is hence more limited than after manufacturing test. A second diagnostic pass could solve the problem and provide more results. Still, on top of being costly, some of the problems that may appear online disappear again if the stress conditions are removed. Very often the automotive and aerospace industry face the so-called no-trouble-found problem: field returns of safety-critical systems produced erroneous outputs which were detected by online test but which, upon further analysis in the laboratory, no longer behave erroneously and hence provide no information. The reason for this may be either random noise which caused the problem, partially reversible changes in the circuit caused by degradation, or temporary extreme environmental conditions unknown at the time of diagnosis. The lack of diagnosability leaves physical analysis with very limited information as a starting point, hence slowing the process down.

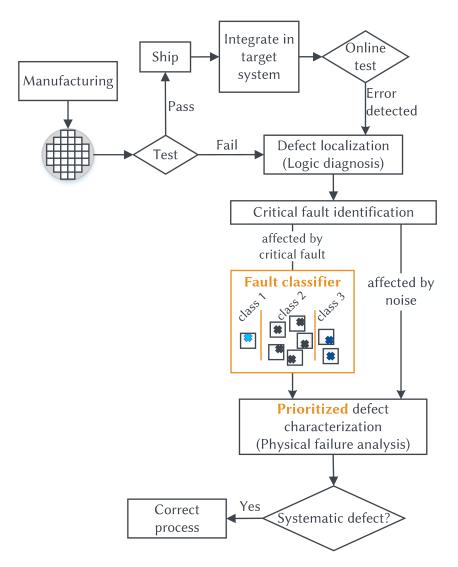

Figure 1.1 depicts the complete flow. Chips from manufacturing are passed on to test, which divides them into passing and faulty. The first are integrated in the target system and undergo online test, while the latter are diagnosed and analyzed. Field returns detected to be faulty during operation are also returned for diagnosis and analysis. In case of a systematic problem, the process or design are corrected.

Field return analysis faces the same problems as manufacturing defect analysis, and most of them aggravated. The lack of information complicates the analysis, the exact timing behavior is unpredictable, and also the characteristics of the problem (whether noise or defect, the location, size and nature in case of the latter) are unknown. Because environmental conditions play a role in the activation of some defects, this additional degree of uncertainty poses an added challenge to the already complicated defect analysis.

▲ Figure 1.1 — Test and diagnosis flow

To increase yield and reliability, systematic defects and structures systematically affected by wearout mechanisms must be identified as soon as possible. To succeed, the identification approach must be robust with respect to uncertainty, given the number of factors that cause the device to deviate from its intended characteristics. Time and cost optimization are also mandatory requirements. Hence, prioritization of physical analysis according to the underlying fault type would be beneficial. The prioritization scheme must be integrated in the test and diagnosis flow. A low cost scheme is required, since test and diagnosis already represent a big part of the costs of producing electronics.

This thesis presents a low overhead modification in the traditional flow that helps prioritize the application of costly diagnostic procedures, and guides physical analysis even in the case of reversible faults. Figure 1.2 depicts the resulting flow. The block

highlighted in orange is the proposed modification, which distinguishes noise from critical defects and classifies the latter.

▲ Figure 1.2 — Test and diagnosis flow after manufacturing: proposed flow

The approach makes use of *machine learning* because of its robustness even in the presence of uncertainty, such as caused in this problem by variations and the physical characteristics of defects. Its overhead in the complete flow is negligible, and it performs a fast classification to prioritize costly analysis resources, hence speeding up the identification of systematic problems, introduced during manufacturing or as a result of wearout.

This work is organized as follows: chapter 2 includes a description of defects and their corresponding fault models, as well as their relation with yield and reliability. Chapter 3 presents the algorithms for manufacturing and online test, diagnosis and preliminary fault characterization state-of-the-art. Chapter 4 presents the challenges introduced by variations and at the same time the potential of machine learning algorithms to be deployed in this context. The following chapters contain the contribution to the field. Chapter 5 presents a Bayesian network-based approach to distinguish transient noise from intermittent or permanent critical faults. Chapter 6 introduces a method for fault classification that can further guide physical analysis without requiring costly second diagnostic passes. Finally, chapter 7 presents the conclusions and directions for further research.

# **DEFECTS, FAULTS AND ERRORS**

Malfunctioning of a circuit has a wide range of sources. During the manufacturing process, imperfections in the fabrication introduce physical distortions in the structure. Depending on the size and nature of the distortion, it may cause the circuit to deviate from its intended functional specification, potentially introducing risks for the system. Also, as the circuit degrades, wearout mechanisms may cause defects to appear during the lifetime of the device. Finally, devices fabricated in nanometer technologies are very sensitive to environmental conditions. Some devices only malfunction under certain external conditions.

Defects introduced in manufacturing impact yield levels negatively. A test escape or the appearance of lifetime defect mechanisms can compromise the reliability of the system. Both for test and reliability assessment, fault models are used which abstract the defect behavior. Targeting defects adds complexity to the approaches and would make them, for the best part, unfeasible for nowadays circuits.

This chapter presents the most common defect mechanisms that may appear both in manufacturing and during the lifetime of the circuit. It then introduces the fault models with which the defects are represented at higher abstraction levels, and finally concludes with an introduction to the reliability threat defects introduce and their relation with yield.

### 2.1 Defect mechanisms

In complementary metal oxide semiconductor (CMOS) technology, the basic units, also referred to as gates or cells, are formed by transistors. The physical properties of transistors determine the functional and performance properties of the chip. Moreover, they are responsible for the sensitivity to noise of chips, and explain some of the fault models considered in this work. For this reason, this section explains the basic structure and function of a transistor, its implications on the design with CMOS technology, and the defects that can affect transistors and interconnects.

A transistor [Westell] is a four terminal device which conducts depending on the voltage differences of its terminals. To form a transistor, some regions of the silicon are doped with an electrons (n) or holes (p) donor. Figure 2.1 sketches an nMOS transistor: a transistor which conducts based on electron mobility. The four terminals are marked on the figure: gate, bulk (body), source and drain. The body of the transistor is p-doped silicon, while the source and drain are of type n. The gate is usually polysilicon, and is separated of the body by a thin oxide layer. When the voltage between the *gate* and bulk terminals  $V_{GB}$  is greater than the threshold voltage  $V_t^n$ , a channel is formed along which the transistor can conduct a current between the source and drain terminals.

▲ Figure 2.1 — nMOS transistor

The pMOS transistor is its complementary structure: it sits on an n-doped silicon, and its source and drain are p-doped. Its body is usually connected to power, and for a given threshold voltage  $V_t^p$ , it conducts when  $V_{GB} < V_t^p$ .

Both types of transistors are combined to form CMOS cells [Weste11]. A CMOS cell is formed by complementary p (or pull-up) and n (or pull-down) networks. The disposition of the transistors is such that for any input values, only one of the networks will be active. This ensures that the output terminal of the cell is connected either to power or to ground. Figure 2.2 depicts the CMOS cell which implements a logic NOR function. The

figure shows the active path for each input pattern (indicated below the corresponding illustration). Note that the expected logic output value can be interpreted as 0 or 1 because the networks are complementary and prevent an intermediate value of being placed at the output.

▲ Figure 2.2 — CMOS NOR cell: transistor structure

To implement complex logic functions, cells are connected by wires. The wires are organized in layers of metal, and with aggressive scaling and increasing transistor density, the amount of interconnect infrastructure, including wires and vias, has also increased [Weste11].

This section describes the defects that can be introduced in cells and interconnects, not only during manufacturing, but also during the lifetime of a digital circuit.

### **Manufacturing** 2.1.1

Imperfections in the manufacturing process complicate the fabrication of nanometer technology devices. In particular, spot defects such as excesses or voids in the material, and parametric variations, such as transistor channel length or doping, cause the fabricated circuit to deviate from the layout specification. This deviation of the physical structure with respect to the intended layout may modify the properties of the system. Depending on the nature, size and shape of the deviation, it may eventually lead to erroneous behavior.

### **Shorts**

One of the most common defects introduced during the fabrication of chips are interconnect bridging defects [Segur04]. A bridge or shorting defect is the unwanted connection of two or more neighboring lines in the integrated circuit (IC). Such a problem can be caused by metal slivers between two lines or by larger blobs of material that short two or more lines. The electrical properties of the metal connecting both lines, as well as the properties of the surrounding circuit, translate into an effect on the circuit behavior.

A bridge will cause the circuit to malfunction if its resistance  $R_{bridge}$  value is below a certain critical value  $R_{critical}$ . In such case, the value of the connected lines depends on the strengths of the pull-up and pull-down networks. A bridge is activated if the pull-up network is active for the driving gate of one of the lines while the other line is pulled down. The resulting voltage of the bridge depends on the properties and strengths of the conducting elements: if the pull-up network is stronger, then a logic 1 will be interpreted, and 0 otherwise. The relative strengths of the driving gates are also patten-dependent. In [Segur04], the authors summarize in a table the  $R_{critical}$  values of a defect bridge between a three-input NAND gate and a two-input NAND gate. The value varies depending on the logic state, i.e., on the input values of both gates.

Bridges can introduce non deterministic behavior in the circuit if the two affected lines are dependent. Two lines are dependent if one of them is function of the other, for instance the input and the output of a gate. A feedback bridge is a short between two dependent lines which introduces an undesired loop in the combinational part of the design. Depending on the structure of the circuit and the applied pattern, an oscillating behavior may be introduced [Chess98a].

### **Opens**

An *open* [Wunde10] is a void or crack in the material which alters its physical properties. In interconnects, the resistance introduced by the void determines the impact on the system behavior. If the open defect causes the line to be interrupted, leaving one of the ends floating, it is called a full open. On the other hand, if the current can still flow although the region has a higher resistance value than designed, it is a resistive open. Resistive opens impact the timing behavior and introduce and additional delay. If a full open appears, the line is interrupted, and the value of the *floating* end depends on the capacitance between the line and the adjacent neighbors, and the voltage values of the

latter. The trapped charged in the floating line is  $Q_0$ . The total parasitic capacitance to power is denoted as  $C_{UP}$ , and those tied to ground,  $C_{DOWN}$ . The voltage of the floating line  $V_{FL}$  can then be calculated as [Wunde10]:

$$V_{FL} = \frac{C_{UP}}{C_{UP} + C_{DOWN}} V_{DD} + \frac{Q_0}{C_{UP} + C_{DOWN}}$$

so  $V_{FL}$  is mainly determined by the trapped charge and the ratio of the parasitic capacitance tied to power.

Finally, an intragate open causes two terminals inside a cell to be disconnected [Wadsa78]. It is also caused by a crack or void in the material, and it restricts the conductivity capacity of the affected path. In the worst case, there is a full open which causes the path not to conduct. This again breaks the CMOS principle that always one path conducts, either to power or to ground. As a result, for those patterns that should activate the affected path the output is left in high impedance. It has been observed [Wadsa78] that the output keeps the previous value, introducing sequential behavior in purely combinational parts of the circuit.

### Parametric failures

In nanometer technologies, parameter variation has become a major issue. With aggressive scaling, the factor by which the manufactured devices differ from the designed ones has increased. This leads to a different kind of problem: in contrast to the previously introduced spot defects, parametric variations induce often a timing problem under certain given conditions. The relevant parameters may be divided into intrinsic and extrinsic [Segur04]. The intrinsic parameters include channel width and length, random doping fluctuations, different ratios between the nMOS and pMOS devices, and effective gate oxide thickness variations. Extrinsic parameters include temperature and supply voltage. These parametric variations affect the conducting behavior of transistors, and hence the timing of the logic cells. For instance, the power fed to a transistor gate controls the formation of the channel [Westell]. Temperature, on the other hand, impacts carrier mobility [Wolpe12]. Intrinsic parameters, especially channel length, also impact the threshold voltage. A shift the threshold affects the formation of the channel, which impacts the timing behaviour [Segur04]. The challenge in parametric failures, however, is that one parameter variation on its own need not be fatal. It is

rather a combination of them that leads to failure, making the prediction, test and diagnosis of such problems extremely hard.

### 2.1.2 Lifetime

The environmental conditions in which a device works, sensitivity to noise and aging may cause a chip to malfunction, even if it passed all manufacturing tests. The term *noise* refers to a temporal malfunction caused by external conditions. An example is the radiation in aerospace industry [Dodd03], where heavy ions hit the microelectronic designs, causing memory and logic elements for a cycle or small number of cycles.

Problems during lifetime may also appear in the power supply [Chen98]. For instance, erroneous behavior may be caused by several transistors fed by the same power line and switching at the same time, causing spikes. Variations in the power supply may cause timing deviations, which in turn may cause an observable error [Segur04]. Also, if many neighbors switch in the same direction, some may suffer of power starvation and propagate an incorrect value to the outputs. This phenomenon is referred to as high-frequency power droop [Polia06].

A problem of different nature may arise if two interconnects are too close and run parallel for a long distance. In this case, the activity of one line may affect a neighboring line, i.e., interferences may happen. In particular, coupling capacitance or *crosstalk* causes a delay [Chen02] in the victim line transition if the aggressor(s) switch in the opposite direction. The induced delay can be expressed as a function of the distance (in time) between the transition in the aggressor and the transition in the victim. The largest delay is introduced when both transitions are aligned [Kahng00].

Another source of lifetime problems is wearout, also referred to as aging. Due to workload, temperature and voltage conditions along the life of the chip, the structures in it degrade. Wearout mechanisms cause defects to appear during the lifetime of the device. With scaling of CMOS technology, the sensitivity to wearout effects has become more severe [Segur04]. The most important wearout mechanisms include electromigration, hot carrier injection, bias temperature instability and dielectric breakdown.

### Electromigration

Electromigration [Lieni05] is an aging mechanism which affects the interconnect infrastructure: wires, vias and contacts. It is caused by high current densities, which often

appear in integrated circuits. Unidirectional high current densities cause the metal atoms to gradually move. Eventually, this shift of the material can cause voids in the metal, or hillocks that can potentially cause a short. The mean time to failure (MTTF) of a wire can be estimated from Black's Equation [Maric13]:

$$MTTF = \frac{A}{J^n} exp\left(\frac{E_a}{kT}\right)$$

where A is a constant that depends on the cross-section of the wire, k is the Boltzmann constant,  $E_a$  is the activation energy of the material, J is the current density, n is a scaling factor and *T* is the temperature. Electromigration requires particular attention to be paid when designing the vias, since they are more prone to suffering this effect [Westell]. With the introduction of copper, wires became more resistant to electromigration. Tin has also been identified as a good solution to mitigate the problem, but electromigration is still a problem in CMOS circuits [Maric13].

### Negative bias temperature instability

Negative bias temperature instability (NBTI) [Westell] affects pMOS transistors which have a negative bias and work in high temperature. The stress conditions over a long period of time cause some of the charges to be trapped, deriving in a shift of the transistor parameters, such as the threshold voltage. The total degradation induced by NBTI was found to have two components: a permanent and a recoverable one [Maric11]. The permanent component is caused by defects near the silicon/oxide interface, and increases with the time the device is under stress conditions (i.e., negative bias). The recoverable component, on the other hand, disappears in the *relaxation time*, that is, when the stress conditions are removed. The permanent component accumulates over time and is never reduced, which leads to eventual non-recoverable degradation after some time. Although NBTI mainly affects pMOS transistors, an analogous effect is observed in some technologies for nMOS devices under positive bias [Maric13].

Due to the recoverable component, NBTI is partially reversible when the permanent component is not yet significant [Maric13]. For this reason, upon later analysis the faulty behavior of the device cannot always be reproduced. This is known as the no-troublefound (NTF) problem, a well known issue in automotive or avionic industries [LiVol11].

### Hot carrier injection

A hot carrier is a particle (electron or hole) with high energy that allows it to overcome the interface state and deviate from its intended trajectory [Maric13]. In CMOS technology, hot carrier injection (HCI) injects these high energy particles in the gate oxide region near the drain. The effects of HCI translate into a shift of the threshold voltage in the affected transistor. This increase in the threshold voltage is often modeled as a function of time in which the device is under stress conditions. Temperature and the length of the channel also have an impact on the wearout effects: some of the possible causes of HCI include higher than specified voltage supplies, short effective channels or accidental peaks in the power rail that increase the power supply [Segur04]. Although HCI primarily affects nMOS transistors, it can also affect pMOS devices and enhance other wearout effects such as NBTI [Maric13].

### Dielectric breakdown

Gate oxide or dielectric breakdown [Weste11] occurs when a large electric field is applied to the dielectric material, causing it to lose its insulating properties. If the electric field is very large, a so-called hard breakdown occurs. A hard breakdown causes severe local damage and may short the transistor, bonding the silicon substrate to the polysilicon of the gate in extreme cases [Segur04]. In CMOS technologies, this situation arises only with high voltage supply values [Maric13]. For weaker electric fields and thin oxides the degradation is partial, and is referred to as soft breakdown. In soft breakdown, the gate current or voltage may increase slightly. However, the clearest indication of breakdown is an increase in the gate current noise. For ultra-thin oxides, soft breakdown appears first. Then, if the chip endures the stress condition for a long time, soft breakdown is followed by progressive breakdown, which induces an increase of the gate current. Although soft breakdown does not always imply a final hard breakdown, it favors it as it weakens the oxide structure.

The time to the appearance of dielectric breakdown is a function of voltage, temperature and oxide thickness. The degradation of the dielectric material is not reversible.

### 2.2 Fault models

Test pattern generation, test pattern quality assessment and diagnosis, among other tasks, deploy an abstraction of the defects in the physical structure of the circuit. The behavior of defects is represented with fault models, which abstract the effect of the physical distortion at a higher level. Logic level is a higher abstraction level that represents the voltages of the lines as binary variables. In other words: it interprets low voltage values as a logic 0 and high voltage values (close to  $V_{DD}$ ) as a logic 1. With this transformation, faults can be represented using the conditional line flip (CLF) fault model [Wunde10]. A CLF has the form  $s_v \oplus |cond|$ , where the variable  $s_v$  identifies the victim signal to be flipped and cond are the activation conditions, expressed as a Boolean formula. The CLF calculus allows the description of all fault models.

### Stuck-at faults 2.2.1

The stuck-at model [Bushn13] has been widely used in many applications. It assigns a fixed value to a victim line  $s_v$  of 0 ( $s_v$ @0) or 1 ( $s_v$ @1). For a long time the stuck-at has been the state-of-the-art representation for test pattern generation or diagnosis. In CLF, a stuck-at-1 fault can be represented as  $s_v \oplus [\neg s_v]$ . The condition that triggers a flip in the line is simply that the value of the victim is 0. As a result, the line is permanently fixed to 1. Analogously, a stuck-at-0 can be represented as  $s_v \oplus \lceil s_v \rceil$ . The stuck-at model can represent a short to power or ground. However, it is not flexible enough to represent defects with sophisticated activation conditions.

### **Delay faults** 2.2.2

As mentioned in 2.1, defects can cause a circuit to deviate from its intended timing specification. In a fault free circuit each gate has an expected delay, derived from nominal delay and variations (cf. section 4.2.2). The timing specification of the complete circuit can be derived from the delay of its components. A delay fault is a model that assumes a mismatch between the expected delay and the actual delay of a component due to a defect. There exist different delay faults, the most important of which are path delay fault, transition fault and small delay fault [Wang06].

A transition fault [Bushn13] assumes that the time for the rising or falling transition deviates from the expected transition time. Each gate may thus have a slow-to-rise (str) and slow-to-fall (stf) fault. In the transition fault model, the delay is bigger than the slack of the shortest path, i.e., all outputs to which the fault can be structurally propagated are affected. The activation condition for this kind of fault is hence a transition at the inputs of the gate that generates a transition at the output. Another model is the *path delay fault* model [Wang06]. A path is a set of gates and signals which connect a primary input or a flip-flop to a primary output or a flip-flop. Unlike the transition fault model, the path delay fault model considers the cumulative delay along a complete path instead of that of an individual gate. The number of paths in a circuit may be exponentially large, which makes the path delay model less practical than the transition model [Wunde10]. Finally, *small delay faults* [Tehra11] introduce small additional delays in the circuit. They reflect the behavior induced by small sized defects, and pose a challenge for test, since they can only be detected with a long path that crosses the fault site.

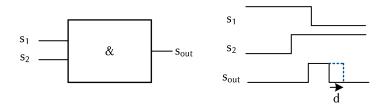

Crosstalk-induced delay can also be modeled in CLF calculus [Wunde10]. The aggressor line is denoted as  $s_a$ , and its value in the previous time unit as  $s_a^{-1}$ . The same applies for the victim line  $s_v$  and its evaluation in the previous time unit  $s_v^{-1}$ . The transition in the victim signal is delayed if the condition that both lines flip in opposite direction is fulfilled:  $s_v \oplus \left[ (s_v \oplus s_v^{-1}) \wedge (s_a \oplus s_a^{-1}) \wedge (s_a \oplus s_v) \right]$ . Note that for simplicity the time is considered discrete in the above formula. However, the time points can be easily substituted by a time point in the continuous time for a more exact representation of the actual defect.

## 2.2.3 Bridges

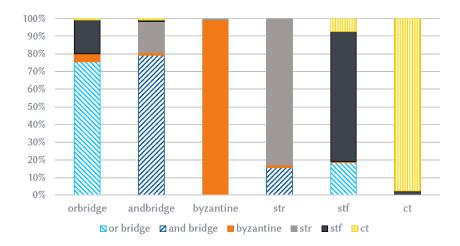

Different bridge models exist to reflect the effects of bridge defects [Wang06]. The common activation condition to all of them is that the two affected lines have different logic values. However, the resulting value of the line differs depending on the assumptions made by the fault model.

The affecting line is referred to as aggressor, while the affected one receives the name of victim. In some fault models, both lines may be at the same time aggressor and victim. So-called wired bridges [Wunde10], for instance, consider that the two lines are affected and get the same value. These models assume a zero-resistance bridge, and the resulting logic value of the signals is calculated by combining the two fault-free values with a logic operation. Wired bridges come in two flavors: the AND-wired bridges, which model n-networks stronger than their p counterparts, and OR-bridges,

which assume the opposite. This model was developed for technologies in which one net clearly dominates over the other.

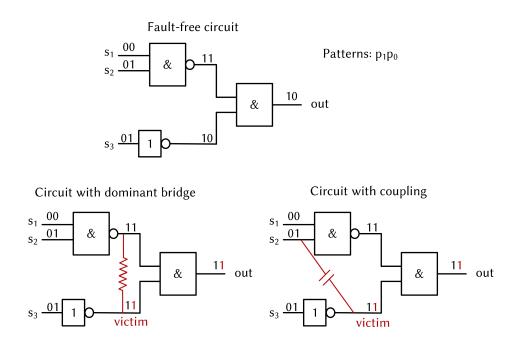

More realistic for CMOS technologies, the dominant bridge models [Wang06] were developed. They assume one of the driving cells dominates over the other: the victim line takes the value of the aggressor always. To reflect the behavior of resistive bridges, the dominant AND- and OR-bridges were developed: the victim takes the value of the aggressor only for a certain value. In a dominant AND-bridge, for instance, the victim line will be driven to 0 if the aggressor is 0. However, if the aggressor is 1, the victim maintains its fault-free value [Wang06]. Figure 2.3 shows the difference between the wired and the dominant fault models (in the AND variant).

▲ Figure 2.3 — Bridge fault models. Adapted from [Wang06]

The byzantine bridge model [Cheun07] causes either of the two lines, or both, to flip upon fulfilling the activation condition that their values are different. This model accounts for the fact that in a bridge, intermediate voltage levels may be generated which are, in turn, interpreted differently by the gates fed by the affected lines. The more realistic fault models take into account the driving strengths of the involved wires. More sophisticated models, such as the voting model [Acken91], were proposed. Also, depending on the resistance of the connection, the bridge may even present a timing component, introducing a delay when the activation condition is met [Li03].

The CLF calculus is also able to represent all of these fault models. A dominant-and bridge, for instance, would be written as  $s_v \oplus [\neg s_a \land (s_v \oplus s_a)]$ . In other words: the fault is activated if the aggressor and victim have opposite values and the fault-free value of the aggressor is a 0.

## 2.2.4 Transistor faults

Transistor defects are also represented at higher abstraction levels. The most relevant fault models are the stuck-on and stuck-off [Wang06]. The stuck-on model assumes the affected transistor is always conducting. Hence, for some patterns a path will be created from the power supply to ground. In a CMOS inverter, for instance, if the nMOS transistor is stuck-on and a logic 0 is applied at the input, the voltage at the output is an intermediate value. It can be interpreted as a 0 or a 1 by the subsequent gates.

A stuck-off, on the other hand, assumes a permanent disconnection between the drain and source terminals of a transistor. A stuck-off transistor introduces a memory effect in the cell. The value of the output signal is calculated as the logic function implemented by the cell for all patterns except for those which exercise the affected path between a power line and the output. In the example of the inverter, if the nMOS is affected by a stuck-open, it never conducts. Hence, for the patterns that exercise that path (input = 1) the cell retains the previous output value. For the rest of the patterns (in this case only input = 0), the power-up net is active and the cell produces the correct value.

# 2.2.5 Non-determinism in fault models

While the activation conditions of faults are known, modeling still poses a challenge. Due to variations, the exact physical structure of the circuit is unknown. On top of that, the size and nature of the defect cannot be predicted, either. With unpredictable exact timing behavior due to variations, shrinking feature sizes and more complex fault activation conditions appearing, the degree of uncertainty increases. It is not realistic to expect deterministic behavior at logic level. Physical parameters and the nature of the problem influence the activation rate, causing the activation to look random for those patterns in which the logic activation conditions are met. As an example, the NBTI effects may appear random at logic level since they depend on the temperature, which is not taken into account in logic simulation. Thus, an additional classification [Const03] of the faults into permanent, intermittent or transient is introduced. The category depends on their activation rate and location:

- *Permanent* faults are those which are activated in the same location(s) and have a deterministic behavior.

- *Intermittent* faults are those activated in the same location(s), but whose activation appears random. They are characterized by an activation rate, which determines

for which patterns, among those which satisfy the logic condition, the fault is activated.

• transient faults represent random noise. They affect random locations and have a low activation rate.

In new technologies, both intermittent and transient faults are gaining importance.

Permanent, intermittent and transient faults can also be represented using the CLF model by introducing additional conditions. A permanent fault is activated always, and needs no further specification. However, intermittents and transients are activated with a certain rate. Let  $s_v \oplus cond$  be the CLF expression for a fault. If the fault is actually intermittent, its activation is not static but depends on a rate  $\lambda_a$ . To account for the indeterminism introduced by the lack of accuracy of the models and the lack of knowledge of the exact physical parameters, it is enough to generate a random number r within a range  $[r_{min}, r_{max}]$ . Then, the condition  $r < \lambda(r_{max} - r_{min})$  is added to the activation. As a result, the CLF model for the intermittent fault is  $s_v \oplus |cond \land (r < r)|$  $\lambda(r_{max} - r_{min})$ . Analogously for a transient fault with activation rate  $\mu_a$ .

#### 2.3 Reliability and yield

The goal of manufacturing is to efficiently mass-produce high quality circuits [May06]. Many aspects of manufacturing impact that goal, including costs, yield and reliability. Yield is an important indicator of the maturity of the production process. It measures the proportion of fault-free devices among all produced ones. The cost per device and yield are inversely related: for a given global manufacturing cost, the higher the yield, the lower the cost per circuit and viceversa.

Reliability measures the probability that a chip will continue to function correctly over time. Both yield and reliability are threatened by continuous scaling: in nanometer technologies the manufacturing process must come up with solutions to print structures smaller than the used wavelength, and chips become increasingly sensitive to wearout mechanisms and noise [McPhe06].

#### **Yield ramping** 2.3.1

When the production of a new design is started, yield levels are generally low. Yield losses come mainly in three different flavors: parametric, systematic and random

[Madge05]. Each yield loss class is caused by different factors and has varying impact on the final total yield. The corresponding corrective actions to tackle the problem are also heterogeneous.

Parametric yield losses are those circuits which are functional, but do not comply with the non-functional specification. For instance, due to process variations, the timing of the circuit and hence its maximum operating frequency are not fixed. Instead, the longest path delay follows a distribution [Kim03]. Depending on the target frequency, the slowest circuits may easily fall out of the non-functional specification. For example, they may deviate from the intended frequency requirements, and require a longer clock cycle to correctly perform the function.

Systematic yield loss is caused by errors in the production flow. A process which is not yet mature may systematically introduce voids or cracks in the interconnects, or dope the silicon incorrectly, or have misaligned masks. The undesired effect will be injected in a high number of devices, drastically reducing yield.

Finally, random yield losses are defects introduced arbitrarily, and can be caused by spurious contamination during production [Wali09].

The process of increasing the yield levels to a significantly higher value, proper of a mature process, is referred to as *yield ramping* or *learning*. Yield learning requires first the identification of the problem, and then the correct countermeasure for each yield loss type.

## Parametric yield losses

Parametric yield losses can be avoided with techniques such as binning. Binning separates the ICs in different categories instead of merely labeling them as passed or fail. It is a well-established industrial practice, and industry reported selling microprocessors in up to six different speed grades already at the beginning of the 2000s [Belet02]. The categories are based on the performance of the device with respect to different non-functional aspects, for instance speed [Kim03] or voltage [Shen12]. With shrinking technologies, however, the variation has increased and a careful selection of test patterns, infrastructure and configuration must be made to keep the technique affordable.

The simplest versions of binning applied functional tests to the devices under different configurations to pick out the maximum frequency or minimum voltage they need [Bushn13]. However, testing all possible configurations of parameters is not

feasible, and different approaches have been proposed to minimize test time while being able to predict circuit performance. The authors in [Zeng04] demonstrate the correlation between structural delay tests and functional testing frequencies. In [Belet02], experiments are performed on a microprocessor to compare the correlation of structural and functional tests. They conclude that path-based test correlates better than transition based test, with the limitation that the test generator must be improved to infer a high path-coverage test sequence which meets the test cost requirements in terms of time and memory. In [Paul07], some long paths are chosen at design time. They can be configured as ring-oscillators, and the authors measure the timing in a small subset of voltage and frequency configurations. The differences in the timing measure the sensitivity of the circuit, and this sensitivity is used to extrapolate for other configurations, which allows to predict the maximum frequency at different operating points for the design.

Binning may also be performed based on the supply voltage. In [Shen12], the authors infer an optimal number of bins given a low bound for yield and the corresponding binning algorithm. They take the test measurements of a population, and represent the voltage intervals as horizontal lines on a graph. Then, the optimal number of bins is inferred. The algorithm requires that each fault-free chip falls in at least one bin, hence, the problem is a cover of vertical lines which crosses all voltage intervals of the population. The authors in [Licht13] take advantage of the relation between performance and leakage to propose their binning approach. In particular, and given that systems have a power budget, they propose to reduce the supply voltage to the fastest circuits. That way, leakage is reduced but the chips' performance is not affected. This reduces yield losses since it rescues the fastest chips, which would be discarded by a leakage screen.

## Systematic yield losses

To reduce systematic yield losses, the root cause must be identified to correct the imperfection in the process as soon as possible. Often, process monitors are introduced in the wafers in order to control the development of manufacturing. Process monitors are special test structures manufactured in the same technology as the chips, and probed by the test equipment to check the existence of systematic defects. The original snake and comb test structures introduced were able to detect a short or an open. However, they could not provide information about the size of the introduced defects. More

recent structures haven been proposed. An example is the NEST structure presented in [Hess01], which is formed by a set of serpentine-shaped nested wires. Each wire is connected to two pads, and electrical measurements on them allow the detection of systematic problems. For instance, the resistance between two pads may give an indication of opens or shorts. Moreover, depending on the measurements, it is possible to infer which lines are affected and hence the defect size distributions. The NEST structure requires only one mask and can be implemented in one layer. However, other structures can be introduced to monitor the introduction of defects between different layers. The authors of [Khare94] propose to use the double bridge test structure to extract defect densities and sizes between two layers, while in [Hamam04] the structure includes open and short monitors, which allow not only the detection but also the location of the defect through the electrical measurements.

Despite careful design based on knowledge about previous processes, test structures cannot always reflect the diversity of production IC structures [Blant12]. For this reason, defective ICs are also deployed as a source of systematic yield loss information. In order to increase yield levels, two approaches are possible [Bushn13]. The first is known as diagnosis and repair, and it consists of performing a thorough diagnosis for the defective parts, which are then repaired. Although yield values increase, so does manufacturing cost. The economic costs make diagnosis and repair less attractive to correct systematic problems. Process diagnosis and correction, on the other hand, tries to find the source of the problem and correct it. Once the systematic problem is corrected, the defect density decreases, causing yield to increase.

In order for the process diagnosis and correction approach to succeed in rapidly ramping yield, the identification of the root cause of the problem must also be a fast process. Ideally, it should not impose a high overhead on the already costly test flow. Otherwise, handling many chips affected by defects will get prohibitively expensive. A fast and cheap failure analysis diagnostics approach combined with process imperfection correction becomes the crucial step for yield learning [Madge05].

The general definition of yield is the ratio of fault-free dies per wafer. However, some authors go one step further and point out that the fault-free devices discarded by mistake also constitute yield loss [Madge05]. This could apply to parametric yield losses, which have been tackled with binning techniques. However, it also applies to those circuits affected by spurious noise during test. If the noise affects a component in the device and propagates an incorrect value to the outputs, then the chip will be labeled

as faulty and discarded. Also, chips for which the outputs were sampled incorrectly due to the resolution of the test equipment may be identified as faulty. These categories will not only pose a problem for the analysis, since no defect will be found, but will also contribute to the number of unnecessary yield losses. Hence, careful analysis needs to be conducted to avoid this situation. However, due to sensitivity to noise and sophisticated defect mechanisms, in nanometer technologies the distinction between noise and systematic problems is not yet resolved.

#### 2.3.2 Lifetime tests

After manufacturing and passing test, a device can be shipped to the customer. However, test escapes as well as aging mechanisms can lead to system failure. In order to ensure the reliability throughout the complete life cycle of the device, two kinds of strategies are deployed, namely, circuit failure prediction and online tests.

Circuit failure prediction attempts to anticipate the time in which degradation will have affected the system and will lead to failure. The main advantages of this technique are the early failure detection, before the system actually degrades and ends up in an unsafe state, and that it is generally an inexpensive approach [Agarw07]. However, the success of the prediction is determining, and a careful selection of features must be performed for prediction. Prediction methods are based on online collecting information about the workload or timing properties of the system combined with a prediction model, generally implemented in software and which can run online, hence preventing the system of degrading with catastrophic consequences.

In [Baran15], the authors propose to monitor the workload of some representative cells in the circuit. The selection of the set of cells is crucial, as they need to characterize the whole circuit. The choice is based on feature selection with a wrapper method [Hall99], which extracts relevant features well correlated with the corresponding expected output even if they are uncorrelated among them. The resulting set is then monitored online, and a software evaluator which contains a model of the expected aging pattern checks for the consistency of the signals.

The authors from [Agarw07] propose the design of special monitors which are provided with a guardband. When the guardband is violated, it means that one of more paths have aged enough to delay the signal arrival into the guardband. However, the functional flip-flops of the circuit still capture the correct value. Consequently, the degradation of the system is detected in advance while the system itself is fully functional and within performance specification. The monitors are combined with a self-adjusting model based on the degradation registered after small periods of time.

Other methods try to identify degradation by monitoring the timing performance of the circuit. In [Agarw08], the authors propose a method to calculate a maximum bound for degradation. Based on the results of this prediction, they choose the optimal placement for the set of monitors at the end of long critical paths. The costs are reduced with the approach presented in [Liu15b], in which the authors consider path segments instead of whole paths, hence increasing the path coverage. To avoid the clocking problems of placing the monitors in arbitrary nets, the monitors are controlled by the inverted clock.

Unlike failure prediction, online error detection can only discover errors once they have already happened. The disadvantage is, of course, that some errors can lead to system failures. However, with good fault coverage and latency values, it only needs a fault tolerant design to allow for graceful degradation while detecting any problem. To this end, many architectures have been proposed which involve an observer, who predicts the fault-free outputs of the module and detects any mismatches [Kocht10] [Sharm88] [Drine03]. Some test approaches are developed so that no additional hardware is needed [Psara10], while other techniques [Wunde98] can be integrated as part of a system-level online strategy [Reima14], [Abele14].

Online error detection techniques are crucial not only because they identify fault occurrences, but also because this instant detection allows the system to collect data about the patterns which activated the fault and also about the obtained response. This information is relevant for later analysis, particularly for faults which are partially reversible or only activated under specific environmental conditions. Without online error detection and information registration, the analysis of such faults is extremely complex.

# TEST, DIAGNOSIS AND FAULT CLASSIFICATION

Test is the procedure in which input stimuli are applied to a unit, and its responses checked against the expected ones. In case of a mismatch, the circuit is deemed faulty. The goal of test is to detect faulty devices as early as possible. Hence, the first step of test is the generation of input patterns which uncover the defects in the device effectively. In order to test a device, the target fault model is first established. Then, a test set is generated which attempts to activate and propagate to the outputs as many of the considered faults as possible. Finally, the test patterns are applied to the device. If the obtained response deviates from the expected output pattern, the chip is identified as faulty and discarded.

To ensure high product quality and reliability, tests are performed throughout the complete lifetime of a circuit. Manufacturing test sorts out the failing devices, which undergo the fault location phase, and finally physical failure analysis (PFA). Although the last step is particularly costly, it is key to yield ramp up: PFA identifies systematic defects so that they can be corrected as soon as possible. PFA cost is partially reduced by applying logic diagnosis. Narrowing down the suspected defect area reduces the time required for PFA.

After a chip is shipped to the customer and integrated in its target system, in-the-field

test are performed to detect any possible degradation effects. Should any problem be detected, the chip must go through the diagnosis and PFA procedure to identify weak structures systematically affected by degradation. Due to the lack of insight into the defect mechanism, physical analysis is performed without the possibility of prioritizing it and hence saving time and resources.