# Adaptable Architectures for Acceleration of Protocol Processing using FPGAs

Akagic Amila

A dissertation submitted in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

School of Science for Open and Environmental Systems

Graduate School of Science and Technology

Keio University

September 2013

# **Abstract**

The emergence of multi-Gigabit Ethernet and ever-increasing volume of network traffic on the Internet has begun outpacing server capacity to manage incoming data. In recent years, the network traffic exhibits constant increase, due to the confluence of many market trends. Today, data centers are considering employment of new technologies, such as 40- and 100-Gb Ethernet, however their adoption rate is still rather small. The major concern is that the potential for such high bandwidths would not be exploited, due to the communication overhead that consumes high levels of processor's processing power. One major source of processing overhead is the TCP/IP stack. This problem has been addressed in various methods. One method is to dedicate one or more cores for TCP/IP processing exclusively. However, with the new paradigm shift to multicore processors, it is hard to guarantee the high throughput for inherently sequential processes, such as cyclic redundancy checks. Other methods include protocol processing offloading onto a specialized hardware and using special large packets known as jumbo frames. This has been specially beneficial in storage applications that transfer large blocks of data.

The future networks also seem to take a new direction toward so called *programmable networks*, which will allow greater agility, programmability and flexibility. In this dissertation, we take another step in this direction by utilizing programmable hardware to achieve the same goals. At first, we target one of the challenging aspects of iSCSI processing, which is processing of digests or Cyclic Redundancy Checks (CRC). CRCs are often characterized as computationally intensive, and thus often substituted with less efficient error detection schemes. We propose a *non-adaptable* and *fully-adaptable CRC accelerators* based on a table-based algorithm, which has been rarely used in hardware implementations. The *non-adaptable* CRC accelerator is suitable for acceleration of a specific application, and has no ability to adapt to a new standard or an application. The *fully-adaptable CRC accelerator* has ability to process arbitrary number of input data and generates CRC for any known CRC standard during run-time. We modify table generation algorithm in order to decrease its space complexity.

We also address the problem of efficiently implementing IP-based iSCSI Offload Engine which operates on the top of the TCP/IP protocol stack. Based on the analysis of iSCSI traffic, CPU utilization and throughput of software-based Open-iSCSI, we propose a new architecture which offloads data transfer and related non-data functions to an FPGA based adapter. The resulting architecture relieves the host CPU from computational burden imposed by software

Abstract

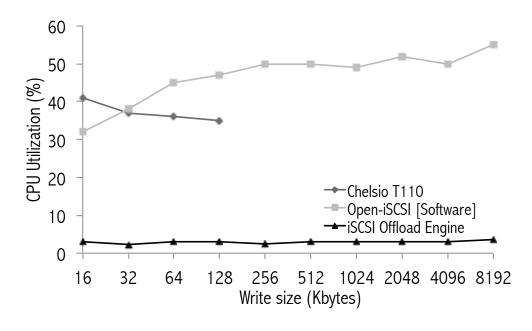

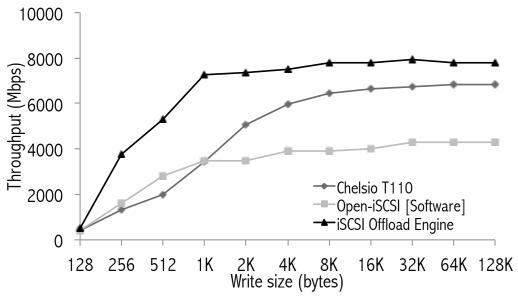

implementations. The iSCSI Offload Engine allows very low utilization on the host CPU of approximately 3%.

Our work is a step toward the goal of using hardware accelerators to enable higher levels of agility, programmability and flexibility in future networks.

# **Acknowledgments**

There are a number of people without whom my doctoral study might not have been accomplished, and to whom I am greatly indebted.

Most of all, I would like to express my deepest gratitude to my supervisor, Professor Hideharu Amano. His constant, patient and generous guidance, suggestions and hopeful encouragements have been my endless source to pursue my work for three years I've spend in his laboratory. He has always given me encouraging words whenever I had a difficulty in my research life, and reviewed every paper that I have written with constructive comments. I am also grateful to all the members of "hlab" and ASAP group. Especially, Kazuei Hironaka, Keimei Miyajima, Takayuki Akamine and other h\_superusers with technical support and significant knowledge.

For this dissertation, I would also like to thank my committee members: Naoaki Yamanaka, Iwao Sasase, and Fumio Teraoka for their time, interest, and helpful comments.

I wish to express my reverence and heartfelt gratitude to Prof. Walid Najjar from University of California, Riverside, for introducing me to this topic, which afterwards became my main focus of research. He has shared his great experience to enlarge my knowledge on computer architecture fields, and also provided me with the crucial evaluation environment for this study.

I'm grateful to Professor Novica Nosovic and Professor Adnan Salihbegovic, my former professors who had addressed evocative words on every milestone in my university life at University of Sarajevo and here at Keio. I would also like to express my reverence to many other colleagues and staff members from Faculty of Electrical Engineering, University of Sarajevo for being supportive during my studies.

My deepest reverence and unfathomable sense of gratitude goes to Zejnil Velic, Zikret Dzananovic, Redzep Husejnagic, Omer Mustafic and many other professors, who lost their lives in the Srebrenica Genocide. In the time of madness, you encouraged curiosity and a passion for learning, that has changed my life forever. I will never forget Zejnil Velic's colorful drawings from Biology class, who helped us memorize every lesson with ease. He thought me one of the most important concept in life: "If you can't explain it simply, you don't understand it well enough".

I gratefully acknowledge the funding sources that made my Ph.D. studies possible. First and foremost, I wish to express my sincere gratitude to Ministry of Education, Culture, Sports, Science, and Technology of Japan for awarding me Monbukagakusho Scholarship. This extraordinary opportunity enriched my life beyond all my expectations. I experienced a sense of

Acknowledgments

personal achievement that felt very different from professional achievements. I appreciate the opportunity to experience the wonders of Japanese cultures and to understand its history a little bit better. Second, I was funded by the Global COE (Center of Excellence) for the first 2 years and I was honored to be GCOE Research Assistant. My gratitude extends to GCOE's project leaders, Professor Naoaki Yamanaka and Professor Masayasu Yamaguchi, for their exceptional leadership and support during my studies. Third, my work was supported with grants from Keio Leading-edge Laboratory of Science and Technology. I'm thankful to all administrative staff from all three sources for their professionalism and helpfulness.

My time in Japan was made enjoyable in large part due to many friends and groups that became a part of my life. I'm especially grateful to KIND, MIFA and Keio Welcome Net groups for their efforts to introduce Japanese culture to foreign students. My unbounded thanks to all my friends, especially Alma Halilovic Okajima and Taro Okajima, who helped and supported my life in Japan countless times.

Lastly, I would like to thank my family for all their love and encouragement. For my parents Djulzida and Mirsad, who raised me with a love of science and supported me in all my pursuits, and my brother Adnan for his constant support. I'm especially grateful to my grandparents Behija Temim and Munib Talovic, whose values are deeply embedded in my character, and who have been my silent advisers and supporters whenever I felt lost.

And most of all for my loving, supportive, encouraging, patient and the best husband Emir Buza whose faithful support during all stages of my Ph.D. is so appreciated. Thank you.

Amila Akagic Yokohama, Japan September 2013

# **Contents**

| A  | Abstract        |         |                                                      |    |  |

|----|-----------------|---------|------------------------------------------------------|----|--|

| Ad | Acknowledgments |         |                                                      |    |  |

| 1  | Intr            | oducti  | on                                                   | 1  |  |

|    | 1.1             | Back    | ground                                               | 1  |  |

|    | 1.2             | Objec   | ctive                                                | 3  |  |

|    | 1.3             | Contr   | ribution                                             | 4  |  |

|    | 1.4             | Disse   | ertation Organization                                | 5  |  |

| 2  | Сус             | lic Red | lundancy Checks and iSCSI initiator                  | 8  |  |

|    | 2.1             | Error   | Control Coding                                       | 9  |  |

|    |                 | 2.1.1   | Types of Errors                                      | 10 |  |

|    |                 | 2.1.2   | Types of Error protecting codes                      | 11 |  |

|    |                 | 2.1.3   | Principles of Block Coding                           | 11 |  |

|    |                 | 2.1.4   | Error Detection Schemes                              | 15 |  |

|    | 2.2             | Cyclic  | Redundancy Checks (CRC)                              | 16 |  |

|    |                 | 2.2.1   | Algorithms for CRC Computation                       | 16 |  |

|    |                 | 2.2.2   | CRC Standard                                         | 22 |  |

|    |                 | 2.2.3   | Related Work                                         | 23 |  |

|    | 2.3             | Intern  | et Small Computer System Interface (iSCSI) initiator | 25 |  |

|    |                 | 2.3.1   | The iSCSI Protocol                                   | 25 |  |

|    |                 | 2.3.2   | Processing of iSCSI Read and Write commands          | 25 |  |

|    |                 | 2.3.3   | Implementation Approaches                            | 28 |  |

|    |                 | 2.3.4   | Performance Analysis of Open-iSCSI                   | 29 |  |

|    |                 | 2.3.5   | Related Work                                         | 30 |  |

| 3  | Higl            | n Perfo | rmance Reconfigurable Computing                      | 31 |  |

|    | 3.1             | Accele  | erator Based Computing with FPGAs                    | 33 |  |

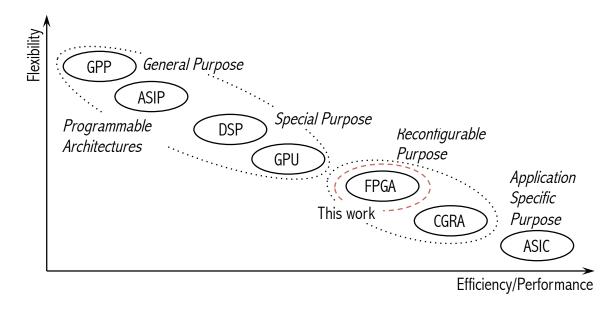

|    | 3.2             | Class   | es of data processing architectures                  | 34 |  |

|    |                 | 321     | Programmable Architectures                           | 35 |  |

Contents

|   |      | 3.2.2   | Reconfigurable Architectures                               | 37 |

|---|------|---------|------------------------------------------------------------|----|

|   |      | 3.2.3   | Application-Specific Architectures                         | 40 |

|   | 3.3  | Overvi  | iew of Field Programmable Gate Arrays                      | 41 |

|   |      | 3.3.1   | FPGA Programming Technologies                              | 41 |

|   |      | 3.3.2   | FPGA Architecture                                          | 43 |

|   |      | 3.3.3   | Configurable Logic Block                                   | 44 |

|   | 3.4  | Hardw   | rare Design Flow                                           | 47 |

| 4 | High | n-Speed | d Fully-Adaptable CRC Accelerators                         | 49 |

|   | 4.1  | Desigr  | n of a CRC Accelerator                                     | 50 |

|   |      | 4.1.1   | CRC Generation Module                                      | 52 |

|   |      | 4.1.2   | Tables Generation Module                                   | 53 |

|   |      | 4.1.3   | Effects of architecture's scalability                      | 57 |

|   |      | 4.1.4   | The IP* Core Interface                                     | 59 |

|   | 4.2  | FPGA    | Implementation                                             | 59 |

|   | 4.3  | Evalua  | ation                                                      | 60 |

|   |      | 4.3.1   | Non-adaptable CRC accelerator core                         | 60 |

|   |      | 4.3.2   | Fully-adaptable CRC accelerator                            | 61 |

|   |      | 4.3.3   | Comparison to Related Work                                 | 64 |

|   | 4.4  | Summ    | ary                                                        | 65 |

| 5 | Des  | ign and | implementation of IP-based iSCSI Offload Engine on an FPGA | 67 |

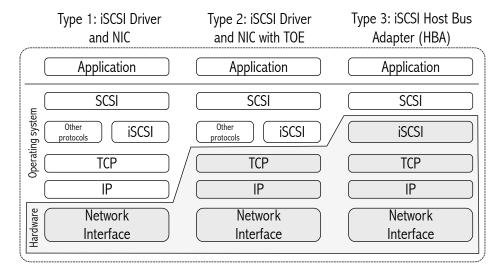

|   | 5.1  | Desigr  | n and implementation of iSCSI Offload Engine               | 69 |

|   |      | 5.1.1   | The Reception Module (Rx)                                  | 73 |

|   |      | 5.1.2   | The Transmission Module (Tx)                               | 75 |

|   |      | 5.1.3   | The CRC Generation Unit                                    | 76 |

|   |      | 5.1.4   | The Control Module                                         | 77 |

|   |      | 5.1.5   | Modification of the Open-iSCSI Initiator                   | 79 |

|   | 5.2  | Impler  | mentation Results and Analysis                             | 82 |

|   |      | 5.2.1   | iSCSI Offload Engine Board                                 | 82 |

|   |      | 5.2.2   | Elapsed time of main operations                            | 82 |

|   |      | 5.2.3   | CPU Utilization and Throughput                             | 83 |

|   |      | 5.2.4   | Reconfiguration time                                       | 85 |

|   |      | 5.2.5   | Resource Utilization                                       | 85 |

|   |      | 5.2.6   | Comparison to Related Work                                 | 86 |

|   | 5.3  | Summ    | ary                                                        | 86 |

| 6 | Con  | clusior | ns                                                         | 88 |

|   |      |         |                                                            |    |

| Contents     | vii |

|--------------|-----|

| Bibliography | 93  |

| Publications | 99  |

# **List of Tables**

| 2.1 | A linear block code with k=4 and n = 7                                                     | 12 |

|-----|--------------------------------------------------------------------------------------------|----|

| 2.2 | A list of parameters defined by a CRC standard                                             | 23 |

| 2.3 | A list of CRC standards with associated applications and protocols                         | 24 |

| 3.1 | Acceleration benefits on Virtex FPGAs                                                      | 34 |

| 3.2 | A comparison between fine- and coarse-grained architectures                                | 39 |

| 3.3 | A comparison summary of selected architecture domains                                      | 39 |

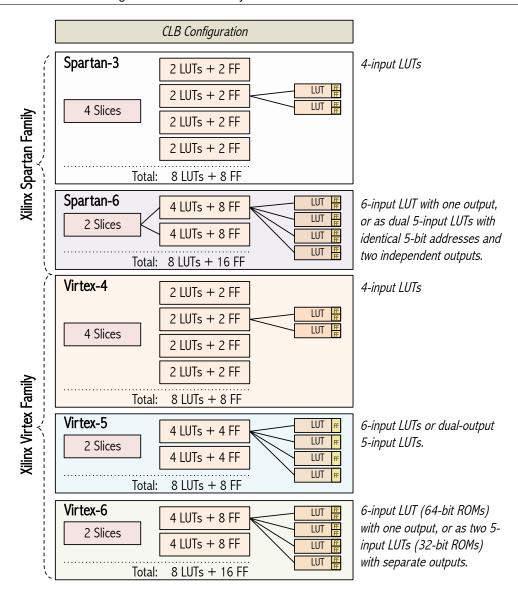

| 3.4 | Resource comparison between five Xilinx generations of FPGAs                               | 46 |

| 4.1 | Resource utilization of R Modules in $(T_{R_i} + 1)$ -stage pipelined architecture         | 60 |

| 4.2 | Resource utilization of <i>non-adaptable</i> Slicing–by– $N_{32}$ and Slicing–by– $N_{64}$ | 61 |

| 4.3 | Resource utilization of fully-adaptable CRC accelerator                                    | 63 |

| 4.4 | Number of clock cycles and time required for re-generation of tables                       | 63 |

| 4.5 | A summary of different CRC designs from Related Work and our implementations.              | 65 |

| 5.1 | A minimum set of opcodes defined on an initiator and a target                              | 72 |

| 5.2 | Elapsed time of main operations for a 1500-byte data packet                                | 83 |

| 5.3 | Resource utilization of iSCSI Engine on Virtex-6 XC6VLX240T FPGA                           | 86 |

# **List of Figures**

| 1.1 | Dissertation organization                                                        | 6  |

|-----|----------------------------------------------------------------------------------|----|

| 1.2 | Positions and contributions of this dissertation                                 | 7  |

| 2.1 | Effects of noise on transmission lines                                           | 10 |

| 2.2 | A representation of n-bit codeword.                                              | 11 |

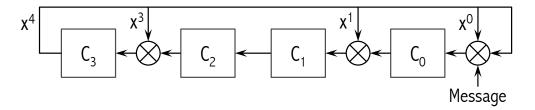

| 2.3 | LSFR for polynomial $P(x) = x^4 + x^3 + x + 1$                                   | 16 |

| 2.4 | LSFR2 for polynomial $P(x) = x^4 + x^3 + x + 1$                                  | 17 |

| 2.5 | Layers of iSCSI packet                                                           | 26 |

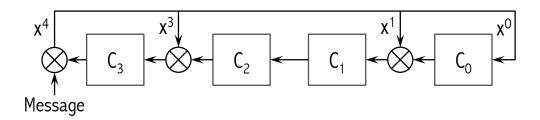

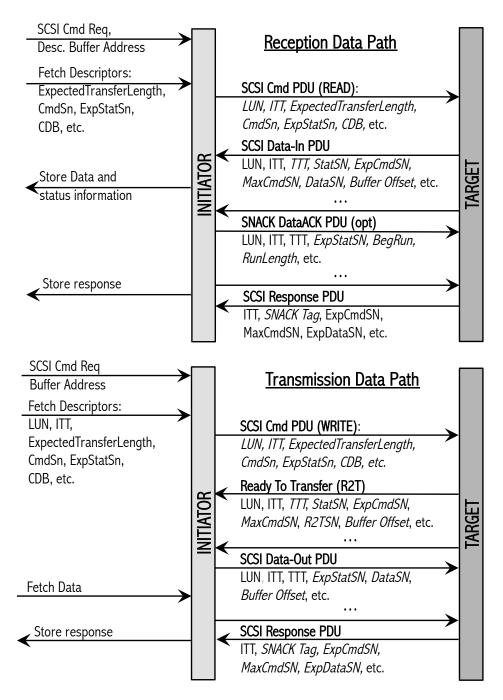

| 2.6 | Flow diagram for processing of a) Data-In PDU and b) Data-Out PDU                | 27 |

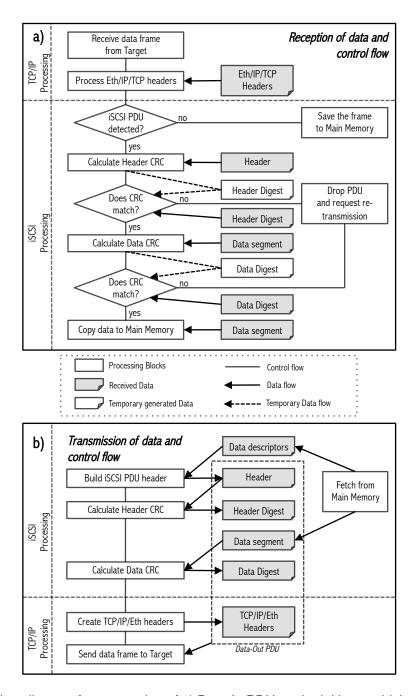

| 2.7 | Three major implementation choices for iSCSI                                     | 28 |

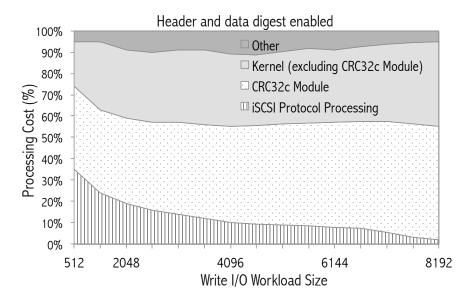

| 2.8 | The performance profile of processing Data-In PDUs                               | 29 |

| 3.1 | Architecture domains as a function of efficiency/performance and flexibility     | 35 |

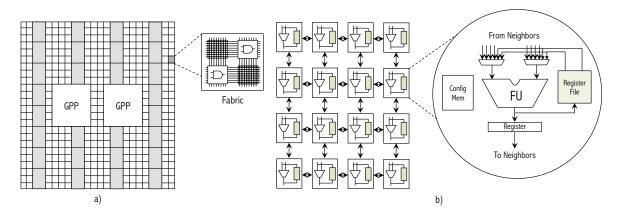

| 3.2 | An example of a) fine-grained and b) coarse-grained reconfigurable architecture  | 38 |

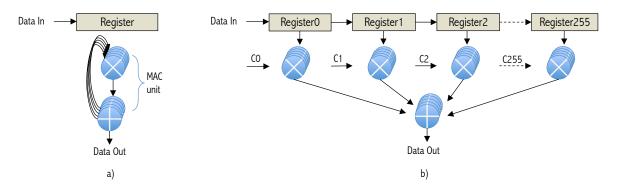

| 3.3 | An implementation of 256-tap FIR filter in a) GPPs/ASIPs and b) FPGAs            | 40 |

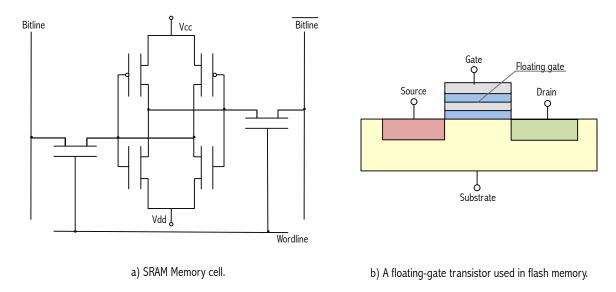

| 3.4 | Two basic elements used in FPGA implementation technologies                      | 42 |

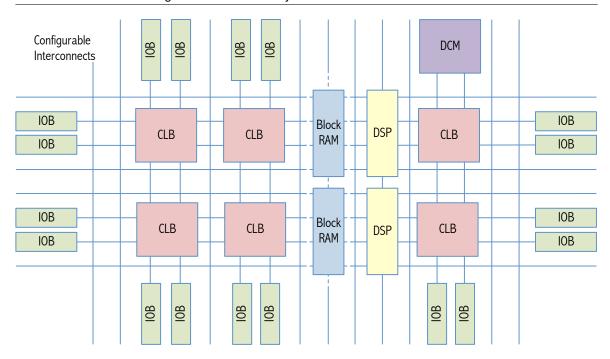

| 3.5 | FPGA Block Structure                                                             | 43 |

| 3.6 | Advancement in configuration of a CLB in latest Xilinx FPGAs                     | 45 |

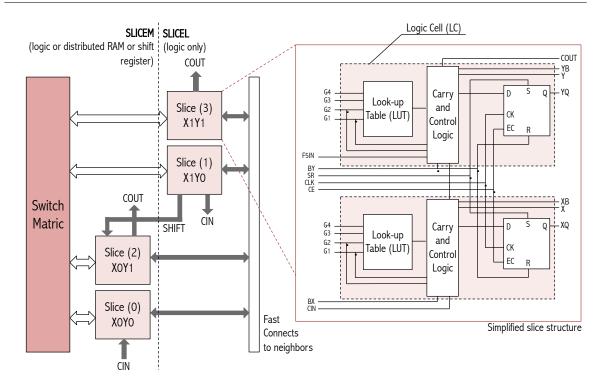

| 3.7 | An example of basic Xilinx Spartan-3 Configurable Logic Block                    | 46 |

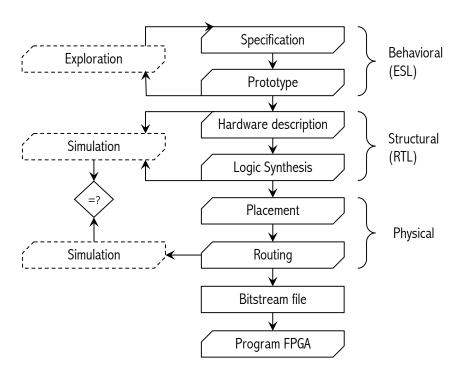

| 3.8 | Design flow of system hardware development                                       | 47 |

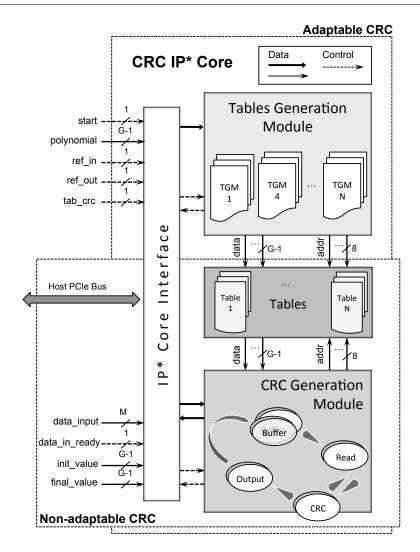

| 4.1 | Design overview of the non-adaptable and fully-adaptable CRC accelerators        | 51 |

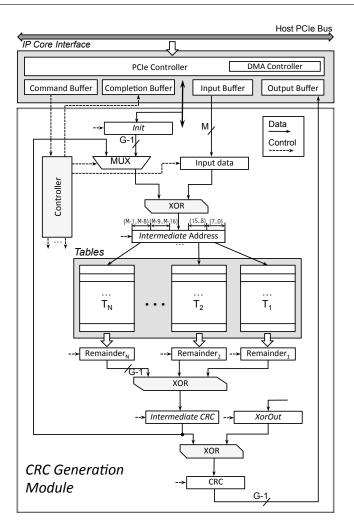

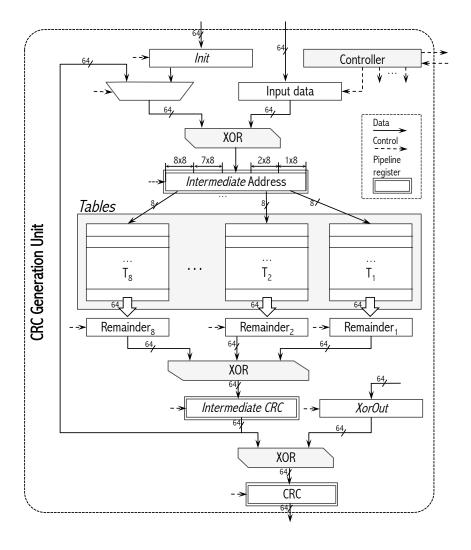

| 4.2 | The generic architecture of CRC Generator Module (CGM)                           | 52 |

| 4.3 | Pseudocode for generating contents of tables                                     | 54 |

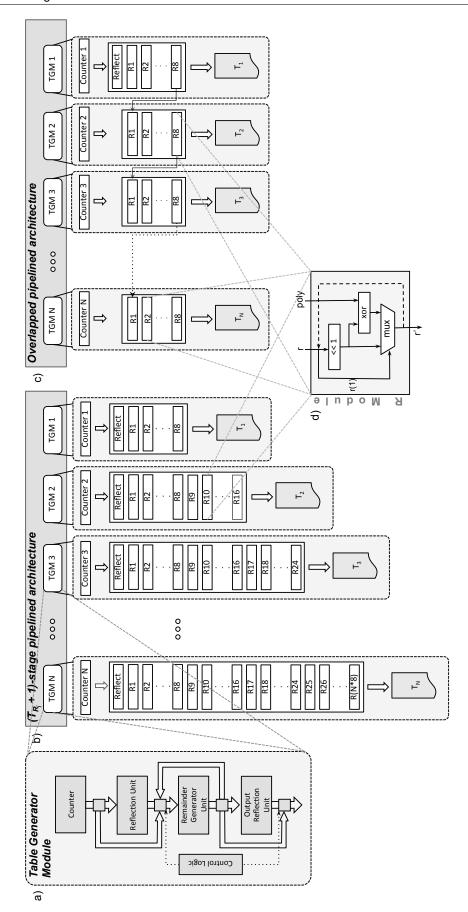

| 4.4 | A schematic of various architectures of Table Generation Module                  | 55 |

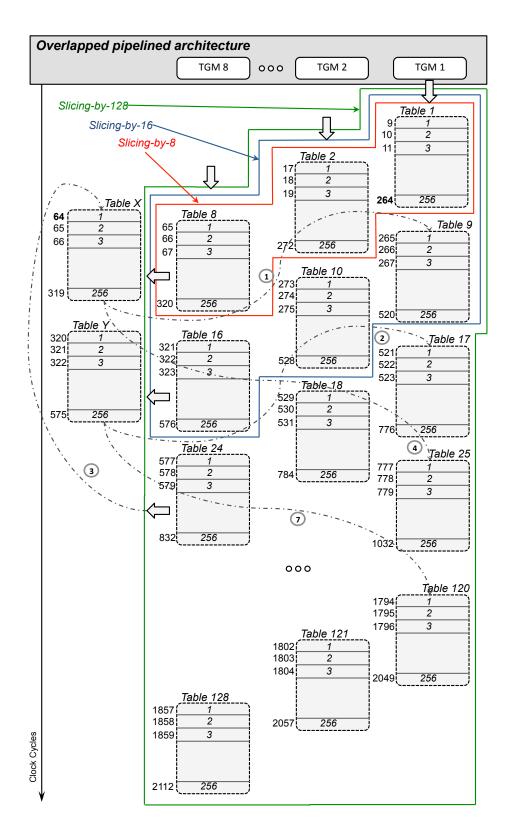

| 4.5 | Overlapped implementation of eight TGMs                                          | 58 |

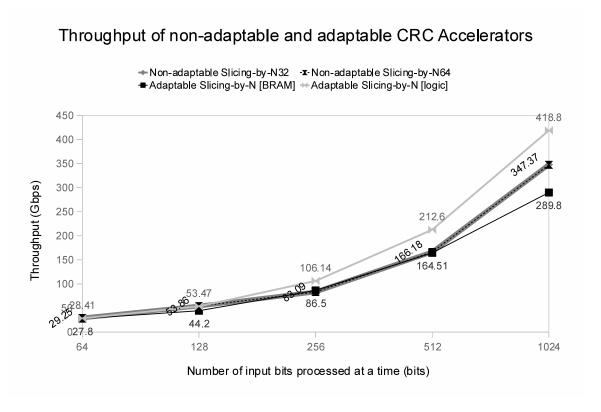

| 4.6 | Throughputs of non-adaptable and fully-adaptable CRC accelerators                | 62 |

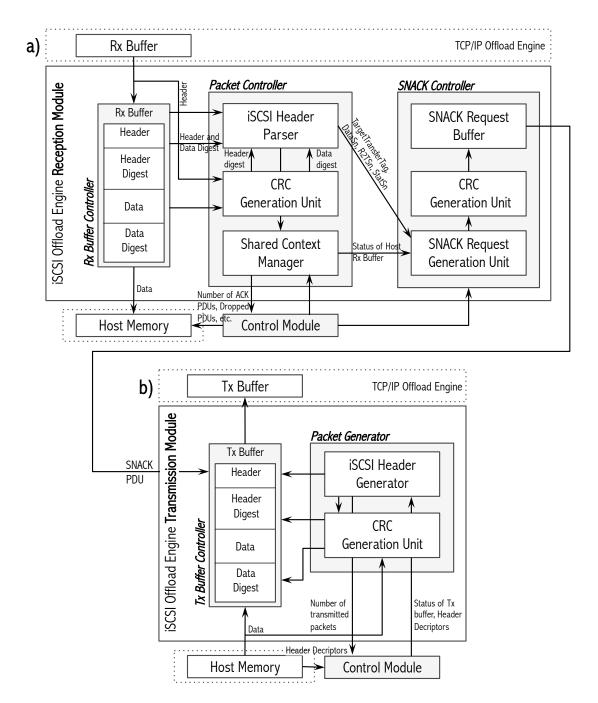

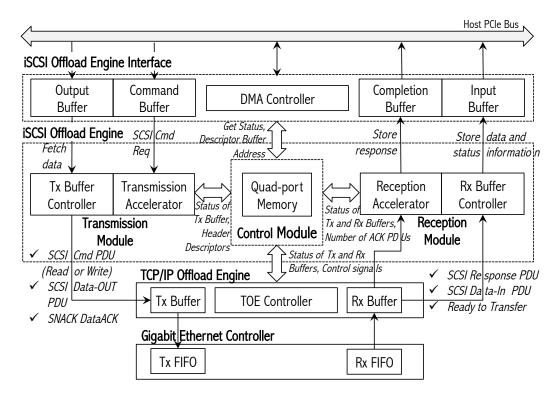

| 5.1 | Design overview of the proposed iSCSI Offload Engine.                            | 70 |

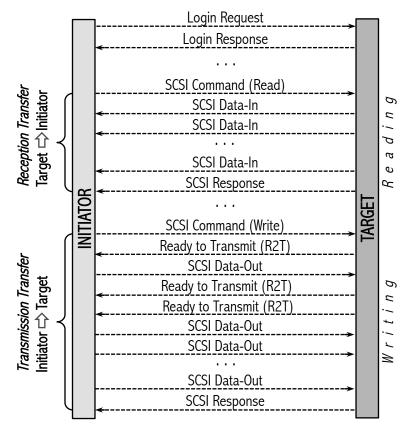

| 5.2 | An overview of two transfer directions during reading and writing processes      | 71 |

| 5.3 | The structure of Reception and Transmission Modules in the iSCSI Offload Engine. | 74 |

| List of Figures | х |

|-----------------|---|

|                 |   |

| 5.4 | The architecture of CRC Generation Unit                                      | 76 |

|-----|------------------------------------------------------------------------------|----|

| 5.5 | An exemplary exchange of information between the initiator and target        | 78 |

| 5.6 | The flow of information between modules in the iSCSI Offload Engine          | 79 |

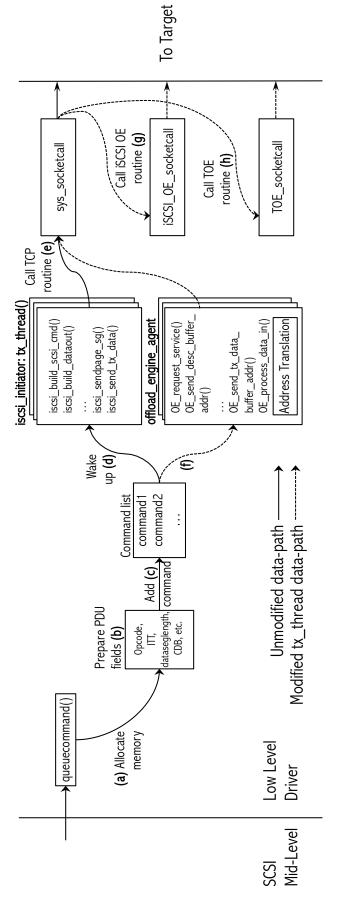

| 5.7 | Unmodified and modified data-paths for creating a SCSI Command by tx_thread. | 81 |

| 5.8 | Comparison of throughput and CPU utilization for 1500 bytes MTU              | 84 |

# **Chapter 1**

# Introduction

#### 1.1 Background

The emergence of multi-Gigabit Ethernet and ever-increasing volume of network traffic on the Internet has begun outpacing server capacity to manage incoming data. In recent years, the network traffic exhibits constant increase, due to the confluence of many market trends. Consequently, there is a very high demand for faster transfer, processing, compilation, and storage of data. In the recent 2012 study [1], Cisco predicts that annual global IP traffic will reach 1.3 zettabytes by 2016. The level of traffic growth is driven by a number of factors, including (a) an increasing number of devices: 2.5 connections for each person on earth and an estimate of 50 billion devices by 2020 [2], (b) more Internet users: about 45% of the world's projected population, (c) faster broadband speeds: expected to increase nearly a fourfold, (d) more video content: 1.2M video minutes in every second and (e) Wi-Fi growth, which will account for the half of the world's Internet traffic by 2016. These factors are having a cumulative effect of putting new demands on IT.

The Internet is evolving from the *Internet of Things (IoT)* [3], with 10 billions of devices connected to the Internet every day, to the *Internet of Everything (IoE)*, also referred to as *networks of networks* [4], with more than 50 billion of connected *things*. The principal difference between these concepts is that IoT focuses on the *volume* of connected things, whereas IoE focuses on the actual *connections*. In the future, billions of new devices and smart sensors will interact with one another without any human interaction. Hence, they will generate an enormous amount of data at an unprecedented scale and resolution. It is obvious that the number of users is everincreasing factor that has an effect on a network. This effect is defined by *Metcalfe's law*. Those organizations who put the highest effort to harness capacities offered by the new *networks of networks* will have the competitive edge.

Thus, there will be many unprecedented opportunities as well as challenges to face in the

<sup>&</sup>lt;sup>1</sup>The Metcalfe's law states that the value of a network increases proportionally to the square of the number of users.

1.1. Background 2

next decade. One of the goals of both IoT and IoE is to bring applications available anytime and anywhere, which will allow users to move with greater agility and speed. In order to support this idea, data centers have become the connecting technology between users and online applications. The entire infrastructure of data centers is undergoing a major transformation. The major initiators of this change are migration of applications to private and public clouds, networks getting faster and adoption of virtualization. In terms of network connections, data centers today tend to employ 10-gigabit Ethernet (10GbE). However, they are heavily virtualized or handling large-scale streaming audio/video applications [5], thus it became apparent that 10GbE isn't fast enough. Even though there are numerous network adapter cards that operate at 40- or 100-gigabit Ethernet, their adoption rate is still rather small. The reasons for this are many, but two major reasons are the price of the equipment and new wiring connectors.

Another aspect to consider is the processing power or CPU utilization of data center servers. The potential for high bandwidth has little value if communication overheads consume all the CPU processing power. In such a case, very little processing power is left for processing other applications. Thus, CPU utilization is as important as bandwidth. It has been shown that a GbE link in a *single-CPU server* can consume close to a half of server's processing cycles [6,7]. Thus, the CPU's processing power would become a bottleneck if architecture of the network interface card (NIC) would not change. A consequence would be severely limited throughput. One of the solutions for this problem is to dedicate one or more cores for TCP/IP processing [8]. However, with maximum operating speed of little above 3 GHz it is hard to guarantee high throughput<sup>2</sup>. Other methods to minimize CPU utilization include *offloading* protocol processing onto specialized hardware [10–14] and using special large packets known as jumbo frames. This has been especially beneficial in storage applications that transfers large blocks of data.

The future networks also seem to take another direction, as has been recently presented by the CEO of Cisco, John Chambers. He predicts that networks will become *programmable* and not just in the data centers, but throughout the network. This will allow greater agility, programmability and flexibility. One step in this direction is so called *Software Defined Networking*, which separates data and control planes with well-defined protocol [15]. In this concept, the control functionalities are taken out of the equipment and moved to a centralized or distributed system, while data plane is retained in the equipment. Cisco already started developing a prototype solution which they call Cisco Open Network Environment (Cisco ONE) [16].

In this dissertation, we take another step in this direction by utilizing *programmable hardware* to achieve greater agility, programmability and flexibility. We utilize the Field Programmable Gate Array (FPGA) which has been commonly used to speed up computationally intensive applications.

<sup>&</sup>lt;sup>2</sup>A general rule of thumb is that it takes 1 MHz of CPU processing power to handle 1 Mb of network bandwidth [9]. Thus, a processor operating on 10 GHz would be required in order to process 10 Gbps.

1.2. Objective

#### 1.2 Objective

The objective of this dissertation is to study high performance reconfigurable architectures for protocol processing. The study is based on the viewpoint that future computer systems will integrate small FPGAs with general purpose processors, whose role will be to accelerate computationally intensive kernels.

At first, we address the problem of efficient implementation of Cyclic Redundancy Check, which has been identified as one of major bottlenecks in iSCSI protocol implementation. Traditionally, CRCs have been used in numerous applications for various types of network data transmissions, data compression (e.g. gzip and bzip2) and data encryption. Howerver, they are often characterized as computationally intensive, and thus often substituted with less efficient error detection schemes. CRC plays an important role in the implementation of iSCSI (Internet Small Computer System Interface) protocol in Storage Area Networks (SANs) for detecting errors which occur between protocol transitions. When CRC is disabled, the network must rely on other mechanisms to detect corrupted data, such as TCP and Ethernet error detection mechanisms. Unfortunately, these mechanisms cannot detected data corruption between upper layer protocol transitions. This can lead to various problems such as failed integrity check of a database. Therefore, our goals are to (1) reduce the computational burden, (2) make architecture generic enough to support a variety of applications, (3) make architecture scalable so it can process arbitrary number of data input (4) achieve significant improvements in throughput and (5) make it area efficient.

The goal of traditional methods for designing CRC accelerators is acceleration of a specific application. In such accelerators, the resulting CRC value is determined by a CRC standard deployed by the application, which is usually fixed at the design time. We call these accelerators non-adaptable. If accelerator does not have ability to adapt to a new standard or an application, its usability is very limited. Thus, we propose adaptable CRC accelerator, which has ability to generate CRC for a variety of CRC standards and thus support a wide range of applications. Such accelerator eliminates the need for many non-adaptable CRC implementations. It also has ability to process arbitrary number of input data and generates CRC for all currently defined CRC standards during run-time.

Cyclic Redundancy Check plays an important role in IP-based storage systems or precisely iSCSI initiator [17]. IP-based storage systems often require bandwidth intensive access to storage devices, thus they exhibit high CPU utilization and low throughput when executed in a principally software implementation. This is especially evident for multi-Gbps networks where the impact of computational overhead is so pronounced that the current state of the art processors cannot take advantage of the capacity of the network. The major concern is the processing of iSCSI digests or CRC [18], thus it is common practice to disable data digests [19]. Commercial hardware iSCSI solutions have been implemented by using TCP/IP Offload Engines (TOE) or

1.3. Contribution 4

iSCSI host bus adapters (HBA). There has been only one attempt to offload iSCSI protocol to an FPGA [14]. However, the maximum reported throughput is less than 100 Mbps, which is not adequate for new multi-Gbps networks. There are three primary reasons why we believe offloading the iSCSI protocol is challenging. First, the scope of iSCSI code is too large and requires a lot of programming effort and time. Second, some functions such as authentication, authorization and security are challenging to implement in hardware. Third, it is thought that operating frequency of FPGAs is not enough to accomplish required throughput for high-speed networks. The performance of software initiators is limited by the processing power of a general purpose processor, especially for the multi-Gbps networks [20]. The biggest concern is high level of CPU utilization that it causes. This has led to extensive research of offloading protocol processing to hardware.

In the second part of this work, we address the problem of efficiently implementing IP-based iSCSI Offload Engine which operates on the top of the TCP/IP protocol stack. Even though processing iSCSI digests have been identified as the most computationally intensive part of iSCSI protocol processing, it is not enough to offload only iSCSI digests. In such a case, the communication overhead between software and hardware parts might undermine all the performance gain. On the other hand, it is challenging to offload all iSCSI processes onto an FPGA. The target applications are mission-critical applications which require high data integrity, such as those of financial and banking transactions where database integrity failures might lead to lost funds, inaccurate stock exchange or credit card transactions. In these systems it is required to enable header and data digests, which adversely affects overall performance.

To address these issues, we propose to combine two types of computing engines, general purpose processors and FPGAs, in order to satisfy the current and future performance demands. The advantage of FPGAs is that they allow speedup of slow sequential algorithms by efficient hardware implementations. Thus, an algorithms can be partitioned into smaller units and executed in parallel on an FPGA. This means that in every clock cycle it is possible to execute all the units with no delay. FPGAs can also be re-programmed to obtain different hardware capabilities at various times and this characteristic is knows as *reconfigurability*. Another advantage is so called *dynamic reconfigurability*, which allows FPGAs to modify operation during run-time. One drawback of FPGAs is their low clock speed when compared with ASICs or CPUs, which is usually an order slower. Thus, not every algorithm is suitable for execution on FPGAs. Some algorithms might present a set of challenges due to the complexity and the volume of the code.

#### 1.3 Contribution

In this dissertation, we address the problem of efficiently implementing 1) Cyclic Redundancy Checks accelerators and 2) IP-based iSCSI Offload Engine which operate on the top of the TCP/IP protocol stack. One major concern for CRC implementations is high level of CPU utilization and low throughput when executed in a principally software implementation. This has

5

led to substituting CRC with less efficient error detection schemes. We describe the design and implementation of non-adaptable and fully-adaptable CRC accelerators based on a table-based algorithm which is suited for the flexible implementation. Although the table-based algorithm has been used in software, it has been rarely implemented in hardware as its performance is believed to be lower than traditional implementation. We prove that this approach can be successfully implemented on an FPGA and achieve significant performance improvements over related work.

Our contributions are as follows:

- 1) We design non-adaptable CRC accelerators with sufficient performance and reasonable resource utilization using a table-based algorithm. Based on this design, a *fully-adaptable* CRC accelerator is proposed by integrating algorithm for generating CRCs and algorithm for generating contents of tables. Resulting architecture generates CRC for any known CRC standard during run-time. It achieves throughput of up to 418.8 Gbps, when the number of input bits M is 1024. Additionally, we modify table generation algorithm in order to decrease its space complexity from O(nm) to O(n), where n is a number of tables, and m is a number of bits in a slice<sup>3</sup>. Design of our architectures guarantees scalability/expandability by processing arbitrary number of input bits M at minimal area cost. In order to show efficiency of our architecture in terms of area utilization and throughput, we design five implementations, where  $M \in 64$ , 128, 256, 512, 1024.

- 2) We analyze iSCSI traffic and identify the most commonly used functions. We measure and analyze CPU utilization and throughput of Open-iSCSI [21], which is an open source software based iSCSI initiator. Based on this analysis, we offload data transfer and related non-data functions to an FPGA based adapter. Data transfer functions are the most computationally intensive and the most executed functions in a common case scenario. Other functions which do not affect performance are implemented in software on a general purpose processor. The resulting architecture relieves the host CPU from computational burden imposed by the software implementation. It is proved that the new architecture overcomes the performance limitations imposed by a single processor which operates on 15 times higher frequency than our FPGA implementation. The iSCSI Offload Engine allows very low utilization on the host CPU of approximately 3%. Our architecture guarantees flexibility, since many functions are implemented on a general purpose processor. Any new feature, such as security functions, specification updates, CRC standards, etc., can be easily implemented.

## 1.4 Dissertation Organization

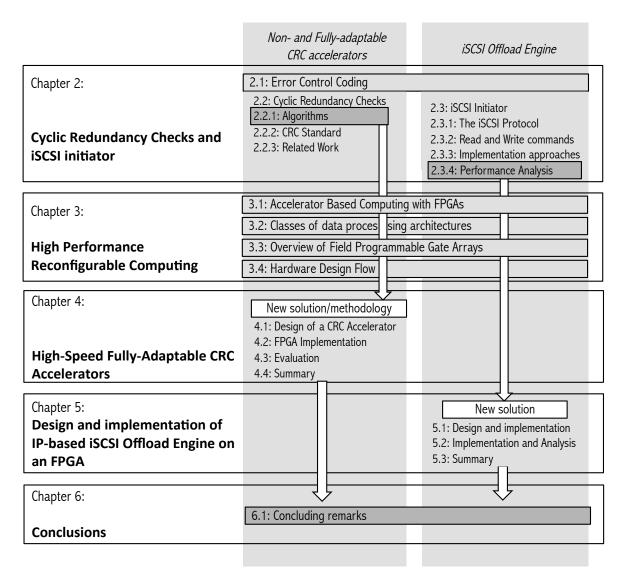

The dissertation organization is provided in Fig. 1.1 and here we provide short description of every chapter. In Chapter 2 we introduce two problems that we addressed in this dissertation. We survey theory behind error conrol coding, commonly used CRC algorithms and overview

<sup>&</sup>lt;sup>3</sup>A slice is formed when a binary number is sliced into two or more constituent. Here, the slice is referred to Slicing-by-N algorithm, and not to FPGA slice.

Figure 1.1: Dissertation organization

Internet Small Computer System Interface protocol. We highlight problems related to these two topics. We present results of performance analysis of software-based Open-iSCSI Initiator and highlight its bottlenecks. Chapter 3 explains current state of high performance reconfigurable technologies and gives short introduction to Field Programmable Gate Array (FPGA), which we use to solve problems related with conventional approaches. Chapter 4 proposes a new methodology for designing non-adaptable and fully-adaptable CRC accelerators. Chapter 5 proposes an iSCSI Offload Engine based on a FPGA adapter. The new architecture relieves the host CPU from computational burden imposed by the software implementation. We compare our results with similar technologies. Chapter 6 summarizes and concludes this dissertation.

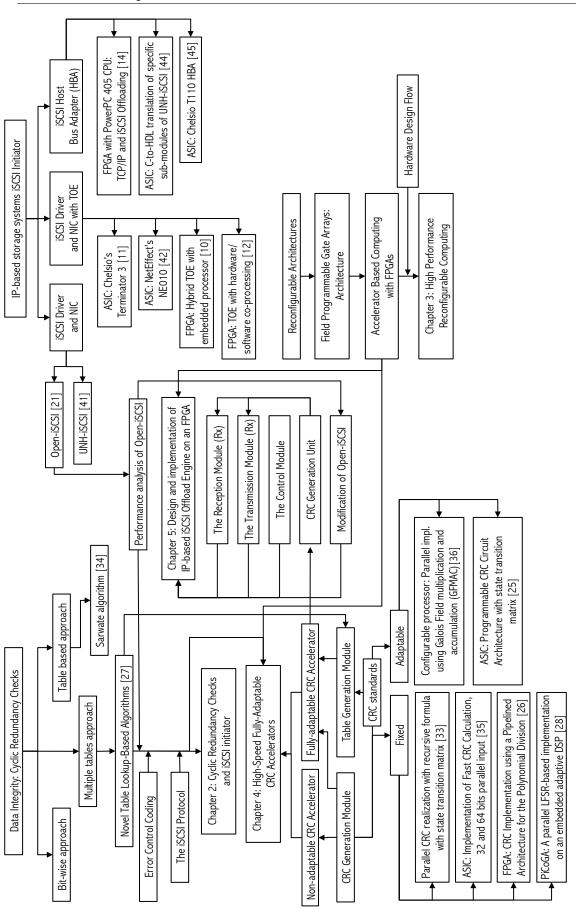

In Fig. 1.2 we present positions of related work and contributions of this dissertations.

#### 1.4. Dissertation Organization

Figure 1.2: Positions and contributions of this dissertation.

# Chapter 2

# Cyclic Redundancy Checks and iSCSI initiator

Cyclic Redundancy Check (CRC) is a well known error detection scheme used to detect corruption of digital content in digital networks and storage devices. Numerous applications use different CRC standards and algorithms for various types of network data transmissions, data compression (e.g. gzip and bzip2) and data encryption. The simplest CRC algorithm imitates the standard hand calculations, which are repeated shifts and conditional subtracts. In this case, input bits are processed one at a time. One way to speed up this process is to merge a number of shift and conditional subtract operations together within a single clock cycle, which is commonly referred to as parallel CRC generation [22].

Traditionally, CRCs are implemented using *hardware* or *software* methods. Early hardware designs are based on the serial Linear Feedback Shift Register (LFSR), which performs the computations by handling one bit at the time [23, 24]. However, some parallel implementations are proposed in [25, 26]. In [25], *Toal et al.* proposed ASIC based architecture for parallel CRC generation, based on a method of merging shift and conditional subtract operations together within a single clock cycle [22]. While in [26], *Monteiro et al.* proposed pipelined architecture for polynomial division by using FPGAs. The basic idea is to perform a number of successive multiplications and divisions in a shift-register structure.

Software implementations can handle word-size data, thus they became more convenient and, until recently, very fast. They are based on algorithms with pre-computed remainders stored in table(s), which are referred to as *table-based* approaches. The most recent algorithms, Slicing-by-4 and Slicing-by-8, are based on *multiple tables approach*. Their main advantage is the ability to process arbitrary number of data at a time. However, with the new paradigm shift to multicore processors, it is challenging to exploit available parallelism due to a sequential nature of cyclic redundancy checks algorithms. Hence, when CRCs are implemented in principally software implementations, they provide modest throughput of up to 3.6 Gbps [27], which is not suitable for multi-Gbps networks. One additional problem is that they consume significant portion of CPU processing power, thus very little to no resources are left for execution of other applications. Hence, the major concern is that the potential of new multi-Gbps networks will

not be exploited, due to the communication overhead that consumes high levels of processor's processing power. One obvious advantage of software implementations is that they are very flexible, since very little effort is required to adapt algorithm to different CRC standards.

Even though many CRC implementations exist, there are two concerns that need to be addressed. The first one is the potential to processes data at current high-speed line rates, such as 10, 40 or more Gbps. Based on our review of current implementations, it is evident that almost all implementations provide less than 10 Gbps throughput. Only one ASIC-based implementation [28] provides around 25 Gbps of throughput. As we mentioned earlier, the most recent software implementation provides only up to 3.6 Gbps [27]. The second concern is ability to adapt to different CRC standards. This may become concern when specification of an application or a protocol changes, or when only one CRC accelerator is available. If the accelerator is fixed to only one CRC standard, it cannot be used with other applications or protocols. This is especially evident in ASIC implementations which tend to have fixed structure.

In this chapter we first review basic theory behind Error Control Coding, with the special focus on Cyclic Redundancy Checks. Then, we review existing algorithms for CRC generation and we highlight their bottlenecks. Then, we address one practical problem where CRCs have been identified as the major bottleneck of processing, especially when executed in principally software implementations. That is *Internet Small Computer System Interface (iSCSI) initiator*, which is one of the mostly used components in IP-based storage systems.

## 2.1 Error Control Coding

Error control coding is a method which provides the means to detect or correct transmission errors by introducing redundancies into the data to be transmitted. Error control coding usually refers to error detection and correction. Error detection is the ability to detect errors caused by noise or other impairments during transmission from the transmitter to the receiver [29]. Error correction has an additional feature that enables identification and correction of the errors. Error detection always precedes error correction. In this dissertation, we focus only on detection, because most network applications do not use error correcting codes. The reason is that they are expensive in terms of computational power. Also, they can correct only a few bits of errors, thus they are not effective for more common burst errors. Instead of error correction, network applications rather ask sender to re-transmit the correct bits. It is important to note that today's fiber optic network have very small error rates. If a packet is lost it is often due to the lack of buffering in routers. In a case where a small number of bit errors occur, the error correcting codes do not help. In the case of magnetic disks, they have to use error correcting codes because they cannot depend on re-transmission for error correction.

All error detection codes transmit more bits than it was in the original data. These bits are derived by some deterministic algorithm, that will produce the same output if applied on the

original data. In the case of error detection, a receiver can apply the same method as sender and check if the output is the same as received bits. These additional bits are referred as redundancy, check bits or parity bits. The method to generate these bits is called error detection scheme. The effectiveness of an error detection scheme is measured by the error scenario that results in the most undetected errors [30]. Its purpose is to reduce the rate of undetected errors to a level acceptable to users.

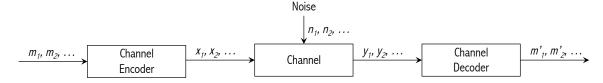

#### 2.1.1 Types of Errors

Errors on transmission lines can occur due to *inter-symbol interference* and *noise* (Fig. 2.1). The inter-symbol interference refers to a case when the energy from a previous bit causes a bit to be wrongly interpreted. The noise, on the other hand, causes a change of a 0 level into a 1 level. The *raw error rate* is the fraction of incorrect senseword symbols (output symbols from channel demodulator), which is expressed as:

$$\lim_{n \to \infty} \frac{1}{n} \sum_{i=1}^{n} P(x_i \neq y_i), \tag{2.1}$$

where  $x_i$  represents input bits into a channel, and  $y_i$  output bits from the channel (Fig. 2.1).

There are three types of errors that occur on transmission lines: *random*, *burst* and *catastrophic* errors. The *random errors* are independent noise symbols. They are caused by thermal noise that is always present on transmission lines. Each noise event affects isolated symbols. The *burst errors* occur when noise event causes a contiguous sequence of unreliable symbols. They also occur due to incorrect synchronization at the physical layers (e.g. when a connector is being plugged in). The *catastrophic errors* occur when a channel becomes unusable for a period of time comparable to or longer than a data packet (e.g. ethernet collisions). In this case, re-transmission is needed because packets are very corrupted.

**Definition 1** A burst error of length l is an n-tuple whose nonzero symbols are confined to a span of l symbols and no fewer.

The intermediate bits may or may not be corrupted. The burst error detecting ability of every (n, k) block code is less or equal to n - k. An ideal error detection code should be able to detect large localized burst errors and also be able to detect as many random bit errors as possible.

Figure 2.1: Effects of noise on transmission lines.

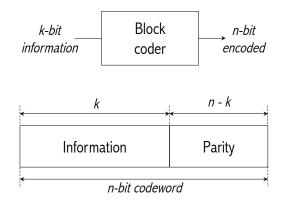

Figure 2.2: A representation of n-bit codeword.

#### 2.1.2 Types of Error protecting codes

There are two types of error protecting codes: *block* and *convolutional* codes. In the block coding, a data is blocked into k-vectors of information digits, then encoded into n-digit codewords  $(n \ge k)$  by adding p = n - k redundant check digits [31,32]. The encoding of each data block is independent of past and future blocks. Since cyclick redundancy checks are a type of block codes, we focus only on block codes and provide more information in section 2.1.3.

The convolutional code is time-invariant encoding scheme, where each n-bit codeword depends on the current information digits on the past m information blocks [31, 32]. This means that the information bits are spread along the sequence. The information is mapped to code bits, instead of blocks.

#### 2.1.3 Principles of Block Coding

In the block coding, a binary information sequence is segmented into message blocks of fixed length, where each block u consists of k bits. Thus, in the case of binary information from the field of  $GF(2)^1$ , there are a total of  $2^k$  distinct messages.

In more general terms, elements from a bigger field GF(q) might be considered, thus there are a total of  $q^k$  distinct messages. A message of n symbols associated with an input block is called a *codeword*. An alternative approach to repeatedly calculating code every time it is needed is to have a *lookup* table with k inputs and n outputs. This approach is feasible when k is small, however this might be infeasible when k gets large.

A *block code* is a code in which k bits (also referred as symbols) are input and n bits are output (Fig. 2.2). This code is designated as an (n, k) code. A binary block code is linear if and

<sup>&</sup>lt;sup>1</sup> A field with a finite number of elements is called a *finite field* or *Galois field* (GF). In the case of GF(2), the field has only two elements {0,1}, and it is called *binary field*.

| Messages | Codewords |

|----------|-----------|

**Table 2.1**: A linear block code with k=4 and n=7.

| Messages  | Codewords       |

|-----------|-----------------|

| (0 0 0 0) | (0 0 0 0 0 0 0) |

| (1 0 0 0) | (1 1 0 1 0 0 0) |

| (0 1 0 0) | (0 1 1 0 1 0 0) |

| (1 1 0 0) | (1 0 1 1 1 0 0) |

| (0 0 1 0) | (1 1 1 0 0 1 0) |

| (1 0 1 0) | (0 0 1 1 0 1 0) |

| (0 1 1 0) | (1 0 0 0 1 1 0) |

| (1 1 1 0) | (0 1 0 1 1 1 0) |

| (0 0 0 1) | (1 0 1 0 0 0 1) |

| (1 0 0 1) | (0 1 1 1 0 0 1) |

| (0 1 0 1) | (1 1 0 0 1 0 1) |

| (1 1 0 1) | (0 0 0 1 1 0 1) |

| (0 0 1 1) | (0 1 0 0 0 1 1) |

| (1 0 1 1) | (1 0 0 1 0 1 1) |

| (0 1 1 1) | (1 0 1 0 1 1 1) |

| (1 1 1 1) | (1 1 1 1 1 1 1) |

only if the modulo-2 sum of two code words is also a code word. An example of linear block code (7, 4) is given in Table 2.1.

**Definition 2** A block code C of length n with  $2^k$  code words is called a **linear** (n, k) code if and only if its  $2^k$  code words form a k-dimensional subspace of the vector space of all n-tuples over the field GF(2).

Since an (n, k) linear code C is a k-dimensional subspace of the vector space  $V_n$  of all the binary n-tuples, it is possible to find k linearly independent code words  $g_0, g_1, ..., g_{k-1}$  in C such that every *codeword* v is a linear combination of these k *codewords*:

$$v = u_0 g_0 + u_1 g_1 + \dots + u_{k-1} g_{k-1}, (2.2)$$

where  $u_i = 0$  or 1 for  $0 \le i \le k$ . These linearly independent *codewords* can be arranged in rows of a  $k \times n$  matrix as shown in equation 2.3.

$$G = \begin{bmatrix} g_0 \\ g_1 \\ \vdots \\ g_{k-1} \end{bmatrix} = \begin{bmatrix} g_{00} & g_{01} & g_{02} & \cdots & g_{0,n-1} \\ g_{10} & g_{11} & g_{12} & \cdots & g_{1,n-1} \\ \vdots & \vdots & \ddots & \ddots & \ddots \\ \vdots & \vdots & \ddots & \ddots & \ddots \\ g_{k-1,0} & g_{k-1,1} & g_{k-1,2} & \cdots & g_{k-1,n-1} \end{bmatrix},$$

$$(2.3)$$

where  $g_i = (g_{i0}, g_{i1}, ..., g_{i,n-1})$  for  $0 \le i \le k$ . If  $u = (u_0, u_1, ..., u_{k-1})$  is the message to be encoded, the corresponding *codeword* is given as follows:

$$v = u \times G = (u_0, u_1, ..., u_{k-1}) \begin{bmatrix} g_0 \\ g_1 \\ \vdots \\ \vdots \\ g_{k-1} \end{bmatrix} = u_0 g_0 + u_1 g_1 + ... + u_{k-1} g_{k-1}.$$

(2.4)

The matrix G is called a *generator matrix* for C. Its rows generate the (n,k) linear code C. Thus, the coding operation can be represented as matrix multiplication. The linear code (n,k) is completely specified by the k rows of a generator matrix G, therefore the encoder can store the k rows of G and form a linear combination based on the input message. All-zero sequence must be a codeword. Therefore, the minimum distance of the code C is the codeword of smallest weight.

The generator matrix for the (7, 4) code from Table 2.1 can be formed as follows:

$$G = \begin{bmatrix} g_0 \\ g_1 \\ g_2 \\ g_3 \end{bmatrix} = \begin{bmatrix} 1 & 1 & 0 & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 & 0 \\ 1 & 1 & 1 & 0 & 0 & 1 & 0 \\ 1 & 0 & 1 & 0 & 0 & 0 & 1 \end{bmatrix}. \tag{2.5}$$

Thus, the codeword for a message  $u = (1\ 1\ 0\ 1)$  is calculated as:

$$v = 1 \times g_0 + 1 \times g_1 + 0 \times g_2 + 1 \times g_3$$

$$= (1 \quad 1 \quad 0 \quad 1 \quad 0 \quad 0 \quad 0)$$

$$+ (0 \quad 1 \quad 1 \quad 0 \quad 1 \quad 0 \quad 0)$$

$$+ (1 \quad 0 \quad 1 \quad 0 \quad 0 \quad 0 \quad 1)$$

$$= (0 \quad 0 \quad 0 \quad 1 \quad 1 \quad 0 \quad 1).$$

Associated with every linear block code generator G is a matrix H called the *parity check matrix* whose rows span the nullspace of G. If v is a codeword, then it is orthogonal to each row of H, which is expressed by the following equation:

$$v \times H_T = 0. ag{2.6}$$

From this equation, follows the following:

$$G \times H_T = 0. (2.7)$$

It is called *dual code* and it has H as its generator matrix. This code is denoted as  $C^{\perp}$ . If G is the generator for an (n,k) code, then H is the generator for an (n,n-k) code. From the example given above, the parity check matrix can be calculated as:

$$H = \begin{bmatrix} 0 & 0 & 1 & 0 & 1 & 1 & 1 \\ 1 & 0 & 0 & 1 & 0 & 1 & 1 \\ 0 & 0 & 0 & 1 & 1 & 0 & 1 \end{bmatrix}.$$

This is called the generator of an (7,3) code. And, from here it is possible to calculate the coderwords for dual code:

It may be verified that every codeword in C is orthogonal to every codeword in  $C^{\perp}$ .

When original data needs to be explicitly evident in the corewords, that coding is called  $systematic\ encoding$ . Then, G is denoted as:

$$G = [P|I_k], (2.8)$$

where  $I_k$  is  $k \times k$  identity matrix and P is  $k \times n - k$  matrix. A linear systematic (n, k) code is completely specified by a  $k \times n$  matrix G in the following form:

$$G = \begin{bmatrix} g_0 \\ g_1 \\ g_2 \\ \vdots \\ g_{k-1} \end{bmatrix} = \begin{bmatrix} p_{00} & p_{01} & \dots & p_{0,n-k-1} & | & 1 & 0 & 0 & \dots & 0 \\ p_{10} & p_{11} & \dots & p_{1,n-k-1} & | & 0 & 1 & 0 & \dots & 0 \\ p_{20} & p_{21} & \dots & p_{2,n-k-1} & | & 0 & 0 & 1 & \dots & 0 \\ & & & & & | & & \dots & & \\ & & & & | & & \dots & & \\ p_{k-1,0} & p_{k-1,1} & \dots & p_{k-1,n-k-1} & | & 0 & 0 & 0 & \dots & 1 \end{bmatrix}.$$

(2.9)

Similarly, H parity matrix of an (n, k) linear code can take the following form:

$$H = [I_{n-k}|P^T] = \begin{bmatrix} 1 & 0 & 0 & \dots & 0 & | & p_{00} & p_{01} & \dots & p_{k-1,0} \\ 0 & 1 & 0 & \dots & 0 & | & p_{10} & p_{11} & \dots & p_{k-1,1} \\ 0 & 0 & 1 & \dots & 0 & | & p_0 & p_{21} & \dots & p_{k-1,2} \\ & & \dots & & | & & & & \\ & & \dots & & | & & & \\ & & \dots & & | & & & \\ 0 & 0 & 0 & \dots & 1 & | & p_{0,n-k-1} & p_{1,n-k-1} & \dots & p_{k-1,n-k-1} \end{bmatrix}.$$

(2.10)

#### 2.1.4 Error Detection Schemes

There are several schemes for error detection. We will review some of them, with emphasize on CRC (section 2.2).

- Repetition schemes: The data is broken up into blocks of bits and each block is sent predetermined number of times. This scheme is not efficient since all repeated blocks of data might be corrupted, thus the receiver might think that the data is correct.

- 2. Parity schemes: The data is broken up into blocks of bits and the number of 1 bits is counted. The extra bit is added during the transmission. This bit is called *parity bit*. There are two type of parity scheme: even and odd parity scheme. In the *Even scheme*, if the number of "1" bits is even (including parity bit), then the parity bit is set to "0", else to "1". In the *Odd scheme*, if the number of "1" bits is odd (including parity bit), then the parity bit is set to "1", else to "0". The problem arises when there are even number of error bits. In this case, the parity scheme can not detect errors. This scheme also can not identify the error bit's position.

- 3. Checksum: The data is broken up into blocks of bits whose binary values are added to form a checksum. The checksum is appended to the end of the transmitted message. On the other end of the communication channel, this process is repeated and the result is compared with the existing checksum. A non-match indicates an error, while a match only indicates that the algorithm did not detect any errors. The checksum can not detect all types of errors, some of which are the following: reordering of the bytes, inserting or deleting zero-valued bytes and multiple errors that cancel each other out.

- 4. Cyclic redundancy checks: This error detecting scheme is almost universally used in networks. This is because CRCs have good burst error detection properties and good random bit error detection properties. It has high probability of detection for most larger random bit errors. Its advantage over other detecting scheme is that it can detect almost all errors with relatively low number of bits of redundancy. It is detailed in section 2.2.

**Figure 2.3**: LSFR for polynomial  $P(x) = x^4 + x^3 + x + 1$ .

### 2.2 Cyclic Redundancy Checks (CRC)

CRC is calculated by performing long division operation between input message and a generator polynomial. At first, a message M is multiplied by  $x^w$  (x is a dummy variable, while w is the length of a generator polynomial), which is equivalent to shifting to left by a polynomial length. This value is then divided by a generator polynomial G(x), and the remainder is called CRC as shown in equation 2.11. The CRC is affixed to the original message M and transmitted to a receiver.

$$CRC(M) = M(x) \times x^{w} \mod G(x)$$

(2.11)

An input data or a message M is treated as a polynomial, where bit values are coefficients of a dummy variable x. The coefficients are all either 0 or 1, while the power of x corresponds to the bit position. For example, the message "01010100" is represented as  $0 \times x^7 + 1 \times x^6 + 0 \times x^5 + 1 \times x^4 + 0 \times x^3 + 1 \times x^2 + 0 \times x^1 + 0 \times x^0$ . If the length of M is defined as I, then I0 can be represented as:

$$M(x) = m_{l-1}x^{l-1} + m_{l-2}x^{l-2} + \dots + m_0$$

(2.12)

where  $m_{l-1}$  is the most significant bit of a message M and  $m_0$  is the least significant bit. A generator polynomial of length w is represented in the same manner:

$$G(x) = g_w x^w + g_{w-1} x^{w-1} + g_{w-2} x^{w-2} + \dots + g_0$$

(2.13)

Due to interference during transmission, data might be corrupted during transport. Errors will be detected on a receiver's side by performing similar process as a sender. At first, a receiver will remove received CRC, then it will perform long division operation with the same generator polynomial specified by a protocol used. Then it will compare received CRC value and its own. Any discrepancy between these two values indicates the presence of transmission errors in the received pair. In this case, a receiver will discard the message and request re-transmission of the data.

#### 2.2.1 Algorithms for CRC Computation

In this section we overview widely used approaches for generating CRC with emphasize on newly proposed ones [27]. We highlight major overheads of these approaches.

#### 2.2.1.1 Bitwise approach

In this approach, CRC is calculated with N shifts and XOR operations for N-bit input message, which makes this algorithm computationally intensive. Early hardware implementations were based on this algorithm, and implemented using linear feedback shift registers (LFSR) [24] (illustrated in Fig. 2.3). Input message is fed *serially* into a circuit, hence if implemented on an FPGA throughput would be limited by operating frequency of an FPGA (e.g. 200 MHz limits throughput to 200 Mbps, thus will not be suitable for high-speed links). Some level of parallelism must be introduced to gain higher throughput.

Traditional implementation with LFSR can be modified to combine the message with the most significant register bit to form the feedback, as is illustrated in Fig. 2.4. This optimization has been referred to as LFSR2. The advantage is that no zeros are needed to be shifted at the end, thus the CRC can be generated in w clock cycles earlier (w is the length of a polynomial).

#### 2.2.1.2 Parallel CRC Computation

In [33], Campobello et al. proposed parallel implementation of the CRC based on the circuit in Fig. 2.4. The initial assumption is that the degree of the polynomial (w) and the length of the message are both multiples of the number of bits processed in parallel (M). From linear systems theory, time-invariant linear system can be expressed as follows:

$$X(i+1) = FX(i) + GU(i)$$

$Y(i) = HX(i) + JU(i),$  (2.14)

where X is the state of the system, U input, Y output, and i ranges from 2 to M. F, G, H, J are used to denote matrices, and X, Y, and U column vectors. Thus, X(i) can be derived from previous equation as:

$$X(i) = F^{i}X(0) + [F^{i-1}G \cdots FG G][U(0) \cdots U(i-1)]^{T}.$$

(2.15)

Matrix F and G are chosen according to the equations of serial LFRS, while H and J are the identity and zero matrices, respectively. Thus, X and H are:

$$X = [x_{w-1} \cdots x_1 x_0]^T$$

$$H = I_w.$$

**Figure 2.4**: LSFR2 for polynomial  $P(x) = x^4 + x^3 + x + 1$ .

If the identity matrix is of size  $w \times w$ , then

$$J = [00 \cdots 0]^{T},$$

$$U = d,$$

$$G = [00 \cdots 1]^{T},$$

$$F = \begin{bmatrix} G_{w-1} & 1 & 0 & \dots & 0 \\ G_{w-2} & 0 & 1 & \dots & 0 \\ \dots & \dots & \dots & \dots & \dots \\ G_{1} & 0 & 0 & \dots & 1 \\ G_{0} & 0 & 0 & \dots & 0 \end{bmatrix}.$$

When i = M, then X(M) can be derived as:

$$X(M) = F^{M} \otimes X(0) \oplus [0 \cdots 0|d(0) \cdots d(M-1)]^{T}.$$

(2.16)

From here it is possible to obtain a recursive formula:

$$X' = F^M \otimes X \oplus D, \tag{2.17}$$

where X' and X represent the next and the present state of the system, while  $D = [d_{w-1} \cdots d_1 d_0]^T$  assumes the following values:  $[0 \cdots 0|b_0 \cdots b_{M-1}]^T$ ,  $[0 \cdots 0|b_M \cdots b_{M-1}]^T$ , where  $b_i$  are bits of original input data followed by a sequence of w zeros.

For every generator polynomial, new  $F^w$  matrix must be derived, and from there it is possible to derive matrix  $F^M$ .  $F^w$  matrix is constructed recursively from the following formula:

$$F^{i} = \begin{bmatrix} F^{i-1} \otimes \begin{bmatrix} p_{m-1} \\ \dots \\ p_1 \\ p_0 \end{bmatrix} & | \text{ the first } m-1 \text{ columns of } F^{i-1} \end{bmatrix}. \tag{2.18}$$

$F^M$  is defined as:

$$F^{M} = \left[ F^{M-1} \otimes P' ... F \otimes P' P' | \frac{I_{m-w}}{0} \right]. \tag{2.19}$$

While,  $F^w$  is:

$$F^{w} = \left[ F^{w-1} \otimes P' | ... | F \otimes P' | P' \right]. \tag{2.20}$$

Here, we show four examples of  $F^w$  matrices based on four polynomials. In order to improve the readability, matrices  $F^w$  are reported as a column vector in which each element is the hexadecimal representation of the binary sequence obtained from the corresponding row of  $F^w$ , where the first bit is the most significant. G denotes generator polynomial.

```

\begin{aligned} \textbf{CRC-12: G} &= \{1, 1, 1, 1, 0, 0, 0, 0, 0, 0, 1, 1\} \\ F_{CRC-12}^{12} &= [CFF\ 280\ 140\ 0A0\ 050\ 028\ 814\ 40A\ 205\ DFD\ A01\ 9FF]^T \\ \textbf{CRC-16: G} &= \{1, 0, 1, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 1, 1\} \\ F_{CRC-16}^{16} &= [2DFFF\ 3000\ 1800\ 0C00\ 0600\ 0300\ 0180 \\ &\qquad \qquad 00C0\ 0060\ 0030\ 0018\ 000C\ 8006\ 4003\ 7FFE\ BFFF]^T. \end{aligned}

```

**CRC-CCITT**: G = {1, 0, 0, 0, 0, 1, 0, 0, 0, 0, 0, 1, 0, 0, 0, 1}

$$F_{CRC-CCITT}^{16}$$

= [0C88 0644 0322 8191 CC40 6620 B310 D988 ECC4

7662 3B31 9110 C888 6444 3222 1911]<sup>T</sup>.

CRC-32: G = {1, 1, 1, 0, 1, 1, 0, 1, 1, 0, 1, 1, 1, 0, 0, 0, 1, 0, 0, 0, 0, 0, 1, 1, 0, 0, 1, 0, 0, 0, 0, 0, 1}  $F_{CRC-32}^{32} = [FB808B20\ 7DC04590\ BEE022C8\ 5F701164\ 2FB808B2\ 97DC0459}$   $B06E890C\ 58374486\ AC1BA243\ AD8D5A01\ AD462620\ 56A31310\ 2B518988$   $95A8C4C4\ CAD46262\ 656A3131\ 493593B8\ 249AC9DC\ 924D64EE\ C926B277$   $9F13D21B\ B409622D\ 21843A36\ 90C21D1B\ 33E185AD\ 627049F6\ 313824FB$   $E31C995D\ 8A0EC78E\ C50763C7\ 19033AC3\ F7011641]^T.$

#### 2.2.1.3 Table based approach

The main idea behind this approach is to pre-compute remainders for a specific input and store them into a table. Widely used algorithm with this approach is known as Sarwate algorithm [34]. This algorithm has been designed when computer architectures supported XOR operation with only *eight* bits, but it is still used today in low-performance implementations. In general, to process a message M of length l, Sarwate algorithm requires a table of  $2^l \times (w-1)$  pre-computed remainders (w is the length of a generator polynomial). Today's processors support operations with 32 and 64 bit values, thus if this algorithm is to be extended it would require lookup tables of  $2^{32} \times (w-1)$  and  $2^{64} \times (w-1)$  for processing 32 or 64 bit input data, respectively.

| Number of bits            | Size of a table       |  |

|---------------------------|-----------------------|--|

| processed in parallel (l) |                       |  |

| 8                         | $2^8\times (w-1)$     |  |

| 16                        | $2^{16}\times (w-1)$  |  |

| 32                        | $2^{32}\times (w-1)$  |  |

| 64                        | $2^{64} \times (w-1)$ |  |

The problem arises when one wants to extend the number of bits processed in parallel l, as is shown in the table bellow. The size of the table grows very quickly, and it would be impossible to implement this algorithm efficiently in software or hardware. These tables cannot fit into a

cache so their contents have to be constantly fetched from the main memory, causing significant performance drop.

#### 2.2.1.4 Multiple tables approach

Looking to overcome limitations of processing only 8 bits of data at a time, two new algorithms have been proposed and evaluated in [27]: *Slicing-by-4* and *Slicing-by-8*. The main advantage is that they can read and process *arbitrarily large amounts* of data at a time. The algorithms are based on two principles associated with modulo-2 arithmetic: 1) *bit-slicing* and 2) *bit replacement*. The bit-slicing principle suggests that if a binary number is sliced into two or more constituent terms, then the CRC value can be calculated as a function of the CRC values of its constituent terms. The bit replacement principle suggests that the amounts of bits from bitstreams can be replaced by potentially much smaller in length binary numbers producing the same CRC values.

The Slicing-by-4 and Slicing-by-8 are based on the algorithmic framework which distinguishes the first and all subsequent steps. The reason why these steps are different is because the length on input stream may not be a multiple of the amount of bits that are read at a time q. Thus, different set of tables may be needed than in all other subsequent steps. At first, we provide details of the *first step* and then every subsequent step k.

**First step** differs from all subsequent steps. Let  $B = [b_1b_2...b_l]$  be the input bitstream,  $P = [b_1b_2...b_p]$  the initial p most significant bits of B, and  $b_1$  the most significant bit of P and B. The length l of B is l > p, and the length g of generator polynomial G(x) is g < l. Then, the l-g+1 most significant bits of B are the information bits that are being encoded, and the g-1 bits of B are equal to zero.

In order to be able to read potentially large amounts of data without the need to access a lookup table of  $2^p$  entries, P is sliced into m slices, which are symbolized as  $P_1, P_2, ..., P_m$  with lengths  $p_1, p_2, ..., p_m$ . Thus, the binary number P and its length p are expressed as  $P = [P_1 : P_2 : ... : P_m]$  and  $p = \sum_i p_i$  for every  $i \in [1, m]$ .

Each slice is associated with separate table. Thus, there are m different tables  $T_1, T_2, ..., T_m$  of sizes equal to  $2^{p_1}, 2^{p_2}, ..., 2^{p_m}$ , respectively. Each table  $T_i$  contains the remainders from the long division of all possible values of slice  $P_i$  shifted by an offset  $o_i$ . The divisor used is the generator polynomial. The offset  $o_i$  is given by

$$o_i = \sum_{j=i+1}^m p_j. (2.21)$$

The remainders during the first step are calculated with

$$R_i^{(1)} = P_i \cdot 2^{o_i} \mod G$$

, where  $i \in \{1, 2, ..., m\}$ . (2.22)

Then, the  $R^{(1)}$  is defined as the result of XOR operation  $(\oplus)$  between all  $R_i^{(1)}$  values returned from tables:

$$R^{(1)} = \bigoplus_{i=1}^{m} R_i^{(1)}.$$

(2.23)

If  $Q^{(1)}$  represents the next q bits of the bitstream, which are positioned after the initial p bits, then  $Q^{(1)}$  is defined by

$$Q^{(1)} = [b_{p+1}b_{p+2}...b_{p+q}]. (2.24)$$

From here, it is possible to define the binary number  $S^{(1)}$ :

$$S^{(1)} = [R^{(1)}: Q^{(1)}] = R^{(1)} \cdot 2^q \oplus Q^{(1)}.$$

(2.25)

The *First step* ends with derivation of the binary number  $S^{(1)}$ . In each subsequent step k, the algorithms operate on a binary number  $S^{(k-1)}$  produced during the previous step k-1.

**Step** k: The binary number  $S^{(k-1)}$  of length s is sliced into n slices, which are symbolized as  $S_1^{(k-1)}, S_2^{(k-1)}, ..., S_n^{(k-1)}$  with corresponding slice lengths  $s_1, s_2, ..., s_n$ . Hence,  $S^{(k-1)} = [S_1^{(k-1)}: S_2^{(k-1)}: ...: S_n^{(k-1)}]$ , while  $s = \sum_i s_i$  for  $i \in [1, n]$ . Each slice is used to perform a table lookup. The number of tables equals number of slices and every step k > 1 uses the same set of tables. For n slices, there are n tables symbolized as  $T_1', T_2', ..., T_n'$  with sizes equal to  $2^{s_1}, 2^{s_2}, ..., 2^{s_n}$  entries, respectively. Each table  $T_i'$  contains the remainders from the long division of  $S_i^{k-1}$  shifted by an offset  $f_i$ . Similar to equation 2.21, the offset  $f_i$  is defined as:

$$f_i = \sum_{i=i+1}^n s_j. {(2.26)}$$

The remainders during this step are calculated by

$$R_i^{(k)} = S_i^{k-1} \cdot 2^{f_i} \mod G$$

, where  $i \in \{1, 2, ..., m\}$ . (2.27)

Then, the  $R^{(k)}$  is defined as the result of XOR operation  $(\oplus)$  between all  $R_i^{(k)}$  values returned from tables:

$$R^{(k)} = \bigoplus_{i=1}^{n} R_i^{(1)}.$$

(2.28)

Subsequently, the binary number  $S^{(k)}$  is calculated from  $R^{(k)}$ , and the next q bits of the bitstream are formed:

$$S^{(k)} = [R^{(k)} : Q^{(k)}] = R^{(k)} \cdot 2^q \oplus Q^{(k)}. \tag{2.29}$$

The step k ends with derivation of the binary number  $S^k$ . In subsequent iteration, the same procedure of bit slicing and parallel table lookups is repeated until all the bits in the bitstream are processed. The total number of steps N that are required for the calculation of a CRC value for bitstream B of length l is equal to

$$N = \left| \frac{l}{q} \right| + 1,\tag{2.30}$$

where q is the number of bits read at a time. It is assumed that the number of bits initially read p is not the same as q.

The difference between two algorithms and comparison with Sarwate algorithm is given below. The Slicing-by-4 algorithm reads and processes 32 bits at a time, and it doubles the performance of existing implementations of Sarware algorithm. The algorithm deploys four tables with pre-computed remainders, which are accessed in parallel by using four 8 bit slices. A slice is formed by slicing input binary number into four constituent terms. Each table requires 1 KB of data in the cache ( $256 \times 32$  bits values for 33 bit generator polynomial), thus Slicing-by-4 requires 4 KB of data in memory. This amount of data can easily fit in today's cache, resulting in faster execution, but it is still limited by the speed of a processor.

Similarly, the *Slicing-by-8* triples the performance of the Sarware algorithm. It reads and processes 64 bits at a time, and it deploys *eight* look-up tables accessed by *eight* 8 bit slices. The algorithm requires 8 KB of data in the cache.

#### 2.2.2 CRC Standard

The content of a pre-computed table depends on specific parameters of a CRC standard, as well as on the position of a byte in the input stream that is being processed. A CRC standard is defined by 8 parameters, as shown on the example of CRC32c standard in Table 2.2.

Width defines width of the algorithm. Poly defines hexadecimal value of a generator polynomial, with top bit omitted, since its value is always 1. Init defines initial value of a CRC register used only in the first iteration of a CRC algorithm. Input message is reflected before performing long division operation if parameter RefIn is true, e.g. 8 bit value will be processed with bit 7 being treated as the least significant bit (LSB) and bit 0 as most significant bit (MSB). If RefIn is false, input bits will not be reflected. Similarly, if RefOut parameter is defined as true, the remainder is reflected before writing it into the table. XorOut parameter is defined as a hexadecimal value and it is used in a final stage before the value is returned as the official checksum. Check parameter is defined as hexadecimal value that represents CRC value of the ASCII string "123456789". It is used as a weak validator of implementations of the algorithm. The parameters Name and Check are not of any use for our implementation, thus we omit them.

**Table 2.2**: A list of parameters defined by a CRC standard shown on the example of CRC32c standard.

| Parameter | Value    |  |

|-----------|----------|--|

| Name      | CRC-32C  |  |

| Width     | 32       |  |

| Poly      | 1EDC6F41 |  |

| Init      | FFFFFFF  |  |

| Refln     | True     |  |

| RefOut    | True     |  |

| XorOut    | FFFFFFF  |  |

| Check     | E3069283 |  |

In the server-type workload, CRC standard can be changed often. This is related to a number and a type of applications and protocols usually executed/employed on the server. Some applications/protocols share a common CRC standard, in which case it is not required to change functionality. However, many applications/protocols employ different CRC standards. Some examples are listed in Table 2.3.

CRC standard is sometimes changed in the specification of an application or a protocol, due to the policy change or the need for more effectiveness. In some cases, it is important to have ability to adapt fast. When CRC is implemented in software, then adaptation is very fast (the code is modified, compiled and ran). However, in the case of ASIC solutions, the entire chip or often the accelerator card has to be replaced, which affects operational cost of the system.

#### 2.2.3 Related Work

Implementations of CRC accelerators with fixed CRC Standards are presented in [26,28,33,35]. In [33] authors identified a recursive formula in serial implementation from which they derived parallel implementation, achieving maximum of 4.38 Gbps while processing 32 bits at a time, occupying only 162 LUTs. In [35] authors design a circuit with two parallel calculation units, capable of processing 32 and 64 bits of input in two different implementations. They operate on 180 MHz in 0.35 micron technology, with maximum throughput of 5.76 Gpbs for 32 and 64 bits processed every clock cycle. In [26] CRC is implemented in a pipeline structure, with a number of successive multiplications and divisions. The maximum reported throughput for processing 32 bits at a time with 16 bits generator polynomial is 4.585 Gbps with clock of 153.84 MHz, and 2.838 Gbps for processing 32 bits with 32 bits polynomial, with clock of 95.23 MHz on Altera FLEX 10KE

**Table 2.3**: A list of CRC standards with associated applications and protocols.

CRC Standard Applications and Protocols

CRC-16-CCITT Bluetooth, HDLC FCS, SD

CRC-16-IBM USB

CRC-24 OpenPGP

CRC-32 Serial ATA, Gnuradio, HDLC,

Ethernet, MPEG-2, Gzip, Bzip2

CRC-32C iSCSI, Btrfs, ext4, SCTP

CRC-40 GSM control channel

CRC-64-ISO HDLC

CRC-64-ECMA-182 XZ Utils

device. In [28], the implementation of parallel LFSR-based applications on an adaptive DSP featuring a Pipelined Configurable Gate Array (PiCoGA) has been presented, with Ethernet's 32 bits CRC as a test-case. PiCoGA is integrated in the embedded digital signal processor based on run-time reconfigurable technology (named DREAM), featuring a working frequency of 200 MHz. On the target architecture, CRC circuit achieves up to 25 Gbps throughput with a parallel LFSR processing 128 bits at time.

There is relatively little work in the area of fully-adaptable CRCs on FPGAs. We found only two other hardware implementations [25, 36] that can support very limited number of generator polynomials. The re-generation in [36] is achieved with Galois Field Multiplication and Accumulation (GFMAC) with *soft-coded* and *hard-coded* generator polynomials. Soft-coded implementation is much slower than fixed hard-coded counterpart. The maximum throughput of soft-coded design with 32 bit CRC is 1.3 Gbps for a 128 bit message. Unfortunately, the reconfiguration time is not provided. The implementation [25] can process variable number of 32 bit generator polynomials, and can be modified to support 64 bit, but cannot support both at the same time in one circuit. The maximum throughput for processing 32 bits with a 32 bit generator polynomial is 4.92 Gbps. It is generic in its design, thus it can be scaled to 64, 128 or 256 bits, with maximal theoretical throughput of 40 Gbps at 256 bits. The reconfiguration time is not very specific under  $1\mu$ s.

The mostly used software solution [27] achieves maximum of 3.6 Gbps for processing 64 bits at a time on Intel Pentium 1.7 GHz. In [37] we measured performance of the same algorithm on the state-of-the-art Xeon 3 GHz processor with 4MB of L2 cache, and the throughput was 9.58 Gbps while processing 512 bits at a time, in idealized conditions without cache misses. There is no research about CRC circuits which support 64 bit generator polynomials.

#### 2.3 Internet Small Computer System Interface (iSCSI) initiator

In this section, we overview *Internet Small Computer System Interface (iSCSI)* initiator, which is one of mostly used components in IP-based storage systems. The target applications are mission-critical applications which require high data integrity, such as those of financial and banking transactions where database integrity failures might lead to lost funds, inaccurate stock exchange or credit card transactions. In these systems it is required to enable header and data digests (CRC), which adversely affects overall performance. IP-based storage systems often require bandwidth intensive access to storage devices, thus *they exhibit high CPU utilization* and low throughput when executed in a principally software implementation. Even though, CRC has been identified as one of the major bottlenecks in iSCSI implementations, it is not enough to offload only CRC to an accelerator card. In this case, the overhead of communication between software and hardware parts might undermine all the effort.

Hereafter, we overview the iSCSI Protocol, the common approaches of implementation, and we provide performance analysis of commonly used software-based Open-iSCSI. We highlight bottlenecks of this implementation. At the end of this section, we provide related work. In Chapter 5, we propose to offload frequently executed operations to an FPGA-based accelerator card to address the problems of high CPU utilization and low throughput.

#### 2.3.1 The iSCSI Protocol

The iSCSI protocol is a transport for SCSI packets over TCP/IP infrastructure. The information exchange is based on a client/server model where the client is called *initiator*, and server *target*. The initiator and target divide their communications into messages, which are called Protocol Data Units (PDUs). Typically, an initiator issues commands to a SCSI target to request transfer of data to/from I/O devices. The group of TCP connections that link an initiator with a target form a session. A session has two phases: Login and Full Feature Phase. In the Login Phase, an initiator and a target negotiate protocol and security parameters, and authenticate each other for the rest of the session. The session then transitions to the Full Feature Phase. In this phase, an initiator may send SCSI commands and data to various SCSI devices on the target. The majority of protocol processing load happens in the second phase.

#### 2.3.2 Processing of iSCSI Read and Write commands

The principal layers of the storage networking model based on iSCSI are shown in Fig. 2.5. The data segment represents the SCSI command set for communication with SCSI devices. iSCSI layer is responsible for transmitting and receiving SCSI commands over TCP/IP infrastructure. The TCP layer is used as end-to-end protocol to establish a reliable session, and for delivering in-order TCP segments to the iSCSI layer. The IP layer is used to route the datagrams between

network devices, and the Ethernet layer is used as MAC protocol handler to transfer Ethernet frames across the physical link.