Jürgen Becker Marco Platzner Serge Vernalde (Eds.)

# **LNCS 3203**

# Field-Programmable Logic and Applications

14th International Conference, FPL 2004 Antwerp, Belgium, August/September 2004 Proceedings

#### Lecture Notes in Computer Science 3203

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen University of Dortmund, Germany Madhu Sudan Massachusetts Institute of Technology, MA, USA Demetri Terzopoulos New York University, NY, USA Doug Tygar University of California, Berkeley, CA, USA Moshe Y. Vardi Rice University, Houston, TX, USA Gerhard Weikum Max-Planck Institute of Computer Science, Saarbruecken, Germany Jürgen Becker Marco Platzner Serge Vernalde (Eds.)

# Field-Programmable Logic and Applications

14th International Conference, FPL 2004 Antwerp, Belgium, August 30–September 1, 2004 Proceedings

Volume Editors

Jürgen Becker Universität Karlsruhe (TH) Institut für Technik der Informationsverabeitung (ITIV) Engesserstr. 5, 76128 Karlsruhe, Germany E-mail: becker@itiv.uni-karlsruhe.de

Marco Platzner Swiss Federal Institute of Technology (ETH) Zurich Computer Engineering and Networks Lab Gloriastr. 35, 8092 Zurich Switzerland E-mail: marco.platzner@computer.org

Serge Vernalde IMEC vzw Kapeldreef 75, 3001 Leuven, Belgium E-mail: serge.vernalde@imec.be

Library of Congress Control Number: 2004111058

CR Subject Classification (1998): B.6-7, C.2, J.6

ISSN 0302-9743 ISBN 3-540-22989-2 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springeronline.com

© Springer-Verlag Berlin Heidelberg 2004 Printed in Germany

Typesetting: Camera-ready by author, data conversion by PTP-Berlin, Protago-TeX-Production GmbH Printed on acid-free paper SPIN: 11311713 06/3142 5 4 3 2 1 0

### Preface

This book contains the papers presented at the 14th International Conference on Field Programmable Logic and Applications (FPL) held during August 30th– September 1st 2004. The conference was hosted by the Interuniversity Micro-Electronics Center (IMEC) in Leuven, Belgium.

The FPL series of conferences was founded in 1991 at Oxford University (UK), and has been held annually since: in Oxford (3 times), Vienna, Prague, Darmstadt, London, Tallinn, Glasgow, Villach, Belfast, Montpellier and Lisbon. It is the largest and oldest conference in reconfigurable computing and brings together academic researchers, industry experts, users and newcomers in an informal, welcoming atmosphere that encourages productive exchange of ideas and knowledge between the delegates.

The fast and exciting advances in field programmable logic are increasing steadily with more and more application potential and need. New ground has been broken in architectures, design techniques, (partial) run-time reconfiguration and applications of field programmable devices in several different areas. Many of these recent innovations are reported in this volume.

The size of the FPL conferences has grown significantly over the years. FPL in 2003 saw 216 papers submitted. The interest and support for FPL in the programmable logic community continued this year with 285 scientific papers submitted, demonstrating a 32% increase when compared to the year before. The technical program was assembled from 78 selected regular papers, 45 additional short papers and 29 posters, resulting in this volume of proceedings. The program also included three invited plenary keynote presentations from Xilinx, Gilder Technology Report and Altera, and three embedded tutorials from Xilinx, the Universität Karlsruhe (TH) and the University of Oslo.

Due to the inclusive tradition of the conference, FPL continues to attract submissions from all over the world. The accepted contributions were submitted by researchers from 24 different countries:

| USA     | 37 | Canada   | 6 | Netherlands | 3 | Mexico      | 2 |

|---------|----|----------|---|-------------|---|-------------|---|

| Spain   | 21 | Portugal | 6 | Austria     | 2 | Switzerland | 2 |

| Germany | 20 | Brazil   | 5 | Belgium     | 2 | Australia   | 1 |

| UK      | 11 | Finland  | 3 | Czechia     | 2 | China       | 1 |

| Japan   | 9  | Ireland  | 3 | Greece      | 2 | Estonia     | 1 |

| France  | 7  | Poland   | 3 | Italy       | 2 | Lebanon     | 1 |

We would like to thank all the authors for submitting their first versions of the papers and the final versions of the accepted papers. We also gratefully acknowledge the tremendous reviewing work done by the Program Committee members and many additional reviewers who contributed their time and expertise towards the compilation of this volume. We would also like to thank the members of the Organizing Committee for their competent guidance and work in the last month. Especially, we acknowledge the assistance of Michael Hübner and Oliver Sander from Universität Karlsruhe (TH) and Rolf Enzler from ETH Zurich in compiling the final program. The members of our Program and Organizing Committees as well as all other reviewers are listed on the following pages.

We would like to thank Altera, Synplicity and Xilinx for their sponsorships. We are indebted to Richard van de Stadt, the author of CyberChair. This extraordinary free software made our task of managing the submission and reviewing process much easier.

We are grateful to Springer-Verlag, particularly Alfred Hofmann, for his work in publishing this book.

June 2004

Jürgen Becker Marco Platzner Serge Vernalde

# Organization

# Organizing Committee

| General Chair             | Serge Vernalde,<br>IMEC vzw, Belgium                         |

|---------------------------|--------------------------------------------------------------|

| Program Chair             | Jürgen Becker,<br>Universität Karlsruhe, Germany             |

| Ph.DForum Chair           | Jürgen Teich,<br>University of Erlangen-Nuremberg, Germany   |

| Publicity Chair           | Reiner Hartenstein,<br>University of Kaiserslautern, Germany |

| Proceedings Chair         | Marco Platzner,<br>ETH Zurich, Switzerland                   |

| Exhibition/Sponsors Chair | Erik Watzeels,<br>IMEC vzw, Belgium                          |

| Finance Chair             | Diederik Verkest,<br>IMEC vzw, Belgium                       |

| Local Arrangements Chair  | Annemie Stas,<br>IMEC vzw, Belgium                           |

### Program Committee

| Nazeeh Aranki<br>Jeff Arnold<br>Peter Athanas<br>Jürgen Becker<br>Neil Bergmann<br>Dinesh Bhatia<br>Eduardo Boemo<br>Gordon Brebner<br>Andrew Brown<br>Klaus Buchenrieder<br>João Cardoso<br>Steve Casselman<br>Peter Cheung<br>George Constantinides<br>Carl Ebeling<br>Hossam ElGindy<br>Manfred Glesner<br>Fernando Gonçalves<br>Steven Guccione<br>Reiner Hartenstein<br>Scott Hauck<br>Tom Kean<br>Andreas Koch<br>Dominique Lavenier<br>Philip Leong<br>Wayne Luk<br>Patrick Lysaght<br>Oskar Mencer<br>Toshiyaki Miyazaki<br>Fernando Moraes<br>Klaus Müller-Glaser<br>Brent Nelson<br>Horácio Neto | Jet Propulsion Laboratory, USA<br>Stretch, Inc., USA<br>Virginia Tech, USA<br>Universität Karlsruhe, Germany<br>Queensland University of Technology, Australia<br>University of Texas, USA<br>Universidad Autonoma de Madrid, Spain<br>Xilinx, Inc., USA<br>University of Southampton, UK<br>Infineon Technologies AG, Germany<br>University of the Algarve, Portugal<br>Virtual Computer Corporation, USA<br>Imperial College London, UK<br>Imperial College London, UK<br>University of New South Wales, Australia<br>Darmstadt University of Technology, Germany<br>Technical University of Technology, Germany<br>Technical University of Lisbon, Portugal<br>Quicksilver Technology, USA<br>University of Kaiserslautern, Germany<br>University of Braunschweig, Germany<br>University of Braunschweig, Germany<br>University of Braunschweig, Germany<br>University of Montpellier II, France<br>Chinese University of Hong Kong, China<br>Imperial College London, UK<br>Xilinx, Inc., USA<br>Imperial College London, UK<br>NTT Network Innovation Labs, Japan<br>PUCRS, Brazil<br>Universität Karlsruhe, Germany<br>Brigham Young University, USA<br>Technical University of Lisbon, Portugal |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | · - ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | · -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Sebastien Pillement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ENSSAT, France                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Marco Platzner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ETH Zurich, Switzerland                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Viktor Prasanna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | University of Southern California, USA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Franz Rammig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Universität Paderborn, Germany                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Ricardo Reis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Universidade Federal do Rio Grande do Sul, Brazil                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Jonathan Rose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | University of Toronto, Canada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Zoran Salcic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | University of Auckland, New Zealand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Sergej Sawitzki                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Philips Research, The Netherlands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Hartmut Schmeck                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | University of Karlsruhe, Germany                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Subarna Sinha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Synopsys, Inc., USA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Gerard Smit          | University of Twente, The Netherlands           |

|----------------------|-------------------------------------------------|

| Jose T. de Sousa     | Technical University of Lisbon, Portugal        |

| Rainer Spallek       | Dresden University of Technology, Germany       |

| Adrian Stoica        | Jet Propulsion Laboratory, USA                  |

| Jürgen Teich         | University of Erlangen-Nuremberg, Germany       |

| Lothar Thiele        | ETH Zurich, Switzerland                         |

| Lionel Torres        | University of Montpellier II, France            |

| Nick Tredennick      | Gilder Technology Report, USA                   |

| Stephen Trimberger   | Xilinx, Inc., USA                               |

| Milan Vasilko        | Bournemouth University, UK                      |

| Stamatis Vassiliadis | Delft University of Technology, The Netherlands |

| Ranga Vemuri         | University of Cincinnati, USA                   |

| Serge Vernalde       | IMEC vzw, Belgium                               |

| Martin Vorbach       | PACT Informationstechnologie, Germany           |

| Serge Vernalde       | IMEC vzw, Belgium                               |

#### Steering Committee

Jose T. de Sousa Manfred Glesner John Gray Herbert Grünbacher Reiner Hartenstein Andres Keevallik Wayne Luk Patrick Lysaght Michel Renovell Roger Woods

| Technical University of Lisbon, Portugal    |

|---------------------------------------------|

| Darmstadt University of Technology, Germany |

| Independent Consultant, UK                  |

| Carinthia Technical Institute, Austria      |

| University of Kaiserslautern, Germany       |

| Tallinn Technical University, Estonia       |

| Imperial College London, UK                 |

| Xilinx, Inc., USA                           |

| University of Montpellier II, France        |

| Queen's University Belfast, UK              |

|                                             |

#### Additional Reviewers

Waleed Abdulla Ali Ahmadinia Kupriyanov Alexey Iosif Antochi Chris Assad Liping Bai Zachary Baker Marcelo Barcelos Michael Beauchamp Marcus Bednara Stevan Berber Jean-Luc Beuchat Eduardo Augusto Bezerra Carsten Bieser Abbas Bigdeli Morteza Biglari-Abhari Christophe Bobda Peter Boll Matthias Bonn Christos-Savvas Bouganis Ney Calazans Humberto Calderon Nicola Campregher Joao Paulo Carvalho Ewerson Luiz de Souza Carvalho Bryan Catanzaro Mark L. Chang Francois Charot C.C. Cheung Charles Chiang **Daniel** Chillet Seonil Choi Tim Courtney G. Figueiredo Coutinho S Craven Dan Crisu Miro Cupak Raphael David Joze Dedic A. Derbyshire Steven Derrien Dirk Desmet Florent de Dinechin Matthias Dyer Ilos Eix **Rolf Enzler** C.T. Ewe Erwan Fabiani Suhaib Fahmy George Ferizis A. Fidjeland Matjaz Finc **Robert Fischer** A. Abdul Gaffar Carlo Galuzzi Georgi N. Gaydadjiev Gokul Govindu Michael Guntsch Said Hamdioui Manish Handa Frank Hannig Michael Haselman Christian Haubelt Michael Hübner Fabiano Hessel Samih Hijwel Clint Hilton Th. Hinze Christian Hochberger

Mark Holland Thomas Hollstein Zhedong Hua Rengiu Huang Finn Hughes Jung Hyun Choi Leandro Soares Indrusiak Hidevuki Ito Xin Jia Eric Johnson Ralf König Thorsten Köster Heiko Kalte F. Gusmão de Lima Kastensmidt Jamil Kawa Ronan Kervell Jawad Khan Mohammed Ghiath Khatib Kichul Kim Dirk Koch Franci Kopac Georgi Kuzmanov Julien Lamoureux Pepijn de Langen Dong-U Lee Gareth Lee Seokjin Lee Yujie Lee Stan Liao Yang Liu Marcelo Lubaszewski Ralf Ludewig A. Mahar Mateusz Majer Usama Malik André Malz Freddy Mang César Augusto Missio Marcon Theodore Marescaux John McAllister Wim J. C. Melis Aline Vieira de Mello Jean-Yves Mignolet Will Moffat Sumit Mohanty

Leandro Heleno Möller Anca Molnos Edson Ifarraguirre Moreno Carlos Morra Gareth Morris Elena Moscu Panainte Erdem Motuk Tudor Murgan Takahiro Murooka Kouichi Nagami Yoshiki Nakane Vincent Nollet Juan Jesus Ocampo-Hidalgo Yuichi Okuyama Luciano Copello Ost Jingzhao Ou K. Paar José Carlos Sant'Anna Palma Joseph Palmer Alex Panato Sujan Pandey Mihail Petrov Jean-Marc Philippe Shawn Phillips Thilo Pionteck Christian Plessl Kara Poon Adam Postula Bernard Pottier Brad Quinton Frédéric Raimbault M. Rans Rainer Rawer Darren Reilly T. Rissa Pasko Robert Partha Roop Andrew Roval Stéphane Rubini Luc Rynders Oliver Sander Gilles Sassatelli Bernd Scheuermann Clemens Schlachta Joerg Schneider

**Bonald Scrofano** Pete Sedcole **Olivier Sentievs** Balasubramanian Sethuraman A. Shahbahrami Akshav Sharma Nalin Sidahao Rectinder Sidhu Ivan Saraiva Silva Mihai Sima Alastair Smith Keith So O. Soffke Raphael Some Galileu Batista de Sousa N. Steiner Piotr Stepien S. Stone Thilo Streichert Qing Su Peter Sutton Alex Thomas D. Thomas Andrej Trost **Richard Turner** Michael Ullmann G. Vanmeerbeeck Matjaz Verderber Francois Verdier Carlos Y Villalpando Patrick Vollmer Herbert Walder Jian Wang Xin Wang John Williams Laurent Wojcieszak Christophe Wolinski Stephan Wong James Wu Yunfei Wu Andy Yan Jenny Yi-Chun Kua Jae Young Hur Frank Zee Cong Zhang

Ling Zhuo Daniel Ziener Heiko Zimmer Peter Zipf

# Table of Contents

# Plenary Keynotes

| FPGAs and the Era of Field Programmability                                                                                                                                                                        | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Reconfigurable Systems Emerge<br>N. Tredennick, B. Shimamoto                                                                                                                                                      | 2  |

| System-Level Design Tools Can Provide Low Cost Solutions<br>in FPGAs: TRUE or FALSE?                                                                                                                              | 12 |

| Organic and Biology Computing                                                                                                                                                                                     |    |

| Hardware Accelerated Novel Protein Identification<br>A. Alex, J. Rose, R. Isserlin-Weinberger, C. Hogue                                                                                                           | 13 |

| Large Scale Protein Sequence Alignment<br>Using FPGA Reprogrammable Logic Devices<br>S. Dydel, P. Bała                                                                                                            | 23 |

| Security and Cryptography 1                                                                                                                                                                                       |    |

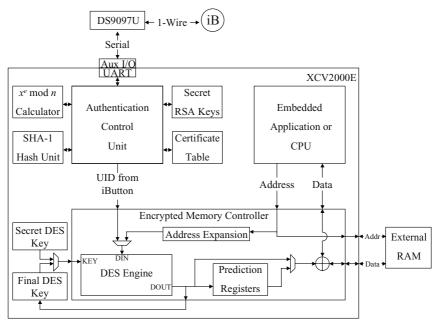

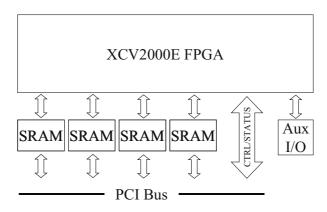

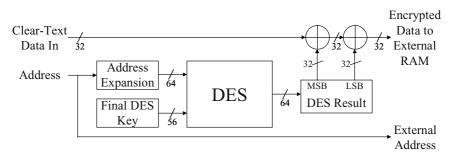

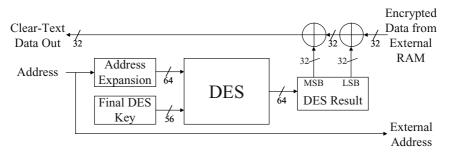

| A Key Management Architecture<br>for Securing Off-Chip Data Transfers<br>J. Graf, P. Athanas                                                                                                                      | 33 |

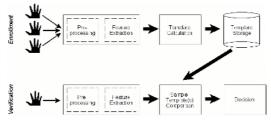

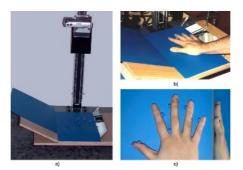

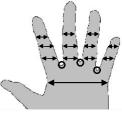

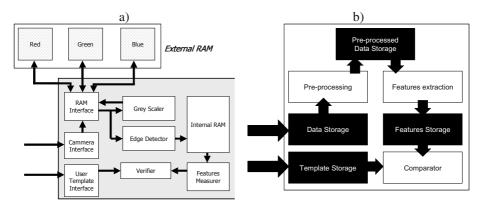

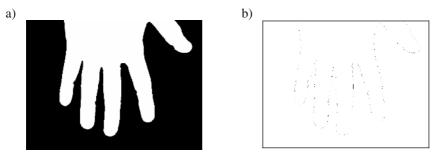

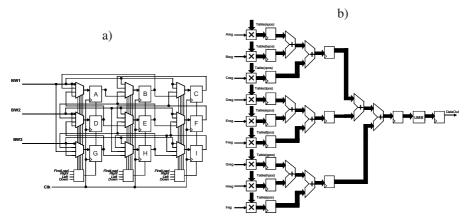

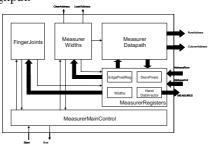

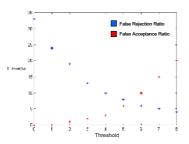

| <ul> <li>FPGA Implementation of Biometric Authentication System</li> <li>Based on Hand Geometry</li> <li>C. López-Ongil, R. Sanchez-Reillo, J. Liu-Jimenez, F. Casado,</li> <li>L. Sánchez, L. Entrena</li> </ul> | 43 |

| Platform Based Design                                                                                                                                                                                             |    |

| SoftSONIC: A Customisable Modular Platform for Video Applications | 54 |

|-------------------------------------------------------------------|----|

| T. Rissa, P.Y.K. Cheung, W. Luk                                   |    |

| Deploying Hardware Platforms for SoC Validation:                  |    |

| An Industrial Case Study                                          | 64 |

| A. Bigot, F. Charpentier, H. Krupnova, I. Sans                    |    |

## Algorithms and Architectures

| Algorithms and Architectures for Use in FPGA Implementations                                                          |    |

|-----------------------------------------------------------------------------------------------------------------------|----|

| of Identity Based Encryption Schemes                                                                                  | 74 |

| T. Kerins, E. Popovici, W. Marnane                                                                                    |    |

| Power Analysis Attacks Against FPGA Implementations of the DES<br>FX. Standaert, S.B. Örs, JJ. Quisquater, B. Preneel | 84 |

### Acceleration Application 1

| Monte Carlo Radiative Heat Transfer Simulation<br>on a Reconfigurable Computer<br><i>M. Gokhale, J. Frigo, C. Ahrens, J.L. Tripp, R. Minnich</i>                                                                                                                                 | 95  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Stochastic Simulation for Biochemical Reactions on FPGA<br>M. Yoshimi, Y. Osana, T. Fukushima, H. Amano                                                                                                                                                                          | 105 |

| Architecture 1                                                                                                                                                                                                                                                                   |     |

| Dynamic Adaptive Runtime Routing Techniques<br>in Multigrain Reconfigurable Hardware Architectures<br>A. Thomas, J. Becker                                                                                                                                                       | 115 |

| Interconnecting Heterogeneous Nodes<br>in an Adaptive Computing Machine<br><i>F. Furtek, E. Hogenauer, J. Scheuermann</i>                                                                                                                                                        | 125 |

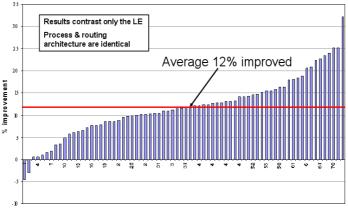

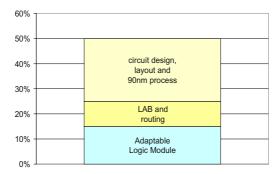

| <ul> <li>Improving FPGA Performance and Area</li> <li>Using an Adaptive Logic Module</li> <li>M. Hutton, J. Schleicher, D. Lewis, B. Pedersen, R. Yuan,</li> <li>S. Kaptanoglu, G. Baeckler, B. Ratchev, K. Padalia,</li> <li>M. Bourgeault, A. Lee, H. Kim, R. Saini</li> </ul> | 135 |

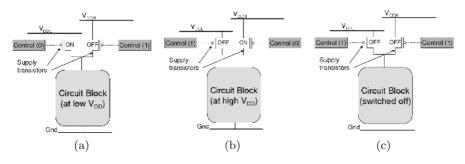

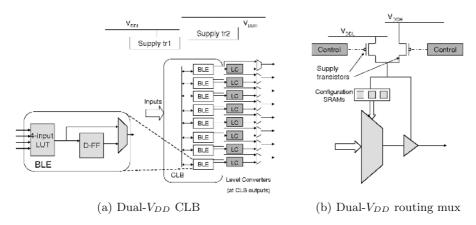

| A Dual-V <sub>DD</sub> Low Power FPGA Architecture<br>A. Gayasen, K. Lee, N. Vijaykrishnan, M. Kandemir, M.J. Irwin,<br>T. Tuan                                                                                                                                                  | 145 |

#### Physical Design 1

| Simultaneous Timing Driven Clustering and Placement for FPGAs | 158 |

|---------------------------------------------------------------|-----|

| G. Chen, J. Cong                                              |     |

| Run-Time-Conscious Automatic Timing-Driven                    |     |

| FPGA Layout Synthesis                                         | 168 |

| J. Anderson, S. Nag, K. Chaudhary, S. Kalman, C. Madabhushi,  |     |

| P. Cheng                                                      |     |

| Compact Buffered Routing Architecture<br>A. Lodi, R. Giansante, C. Chiesa, L. Ciccarelli, F. Campi,<br>M. Toma                                                                                    | 179 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| On Optimal Irregular Switch Box Designs<br>H. Fan, YL. Wu, CC. Cheung, J. Liu                                                                                                                     | 189 |

| Arithmetic 1                                                                                                                                                                                      |     |

| Dual Fixed-Point:<br>An Efficient Alternative to Floating-Point Computation<br><i>C.T. Ewe, P.Y.K. Cheung, G.A. Constantinides</i>                                                                | 200 |

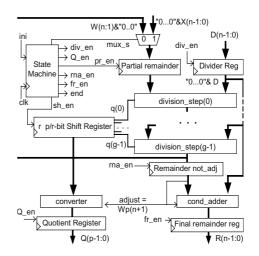

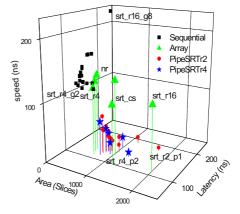

| Comparative Study of SRT-Dividers in FPGA<br>G. Sutter, G. Bioul, JP. Deschamps                                                                                                                   | 209 |

| Second Order Function Approximation<br>Using a Single Multiplication on FPGAs<br>J. Detrey, F. de Dinechin                                                                                        | 221 |

| Efficient Modular Division Implementation<br>(ECC over GF(p) Affine Coordinates Application)<br>G. Meurice de Dormale, P. Bulens, JJ. Quisquater                                                  | 231 |

| Multitasking                                                                                                                                                                                      |     |

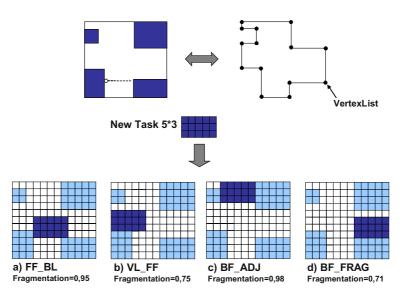

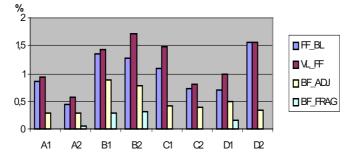

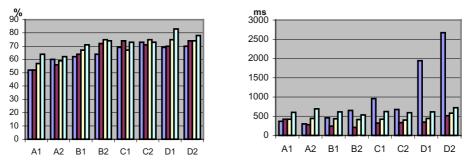

| A Low Fragmentation Heuristic for Task Placement<br>in 2D RTR HW Management<br>J. Tabero, J. Septién, H. Mecha, D. Mozos                                                                          | 241 |

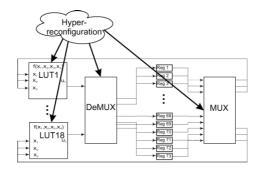

| The Partition into Hypercontexts Problem<br>for Hyperreconfigurable Architectures                                                                                                                 | 251 |

| Circuit Technology                                                                                                                                                                                |     |

| A High-Density Optically Reconfigurable Gate Array<br>Using Dynamic Method<br>M. Watanabe, F. Kobayashi                                                                                           | 261 |

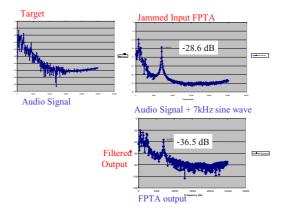

| <ul><li>Evolvable Hardware for Signal Separation and Noise Cancellation</li><li>Using Analog Reconfigurable Device</li><li>D. Keymeulen, R. Zebulum, A. Stoica, V. Duong, M.I. Ferguson</li></ul> | 270 |

# Memory 1

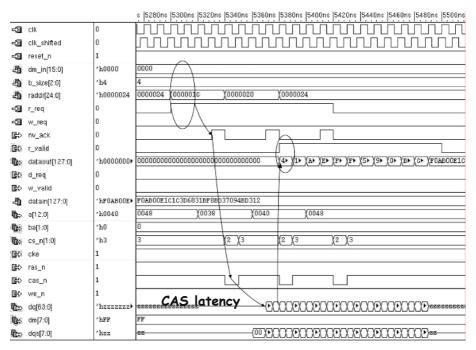

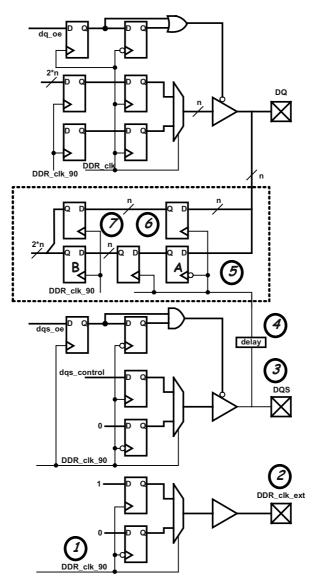

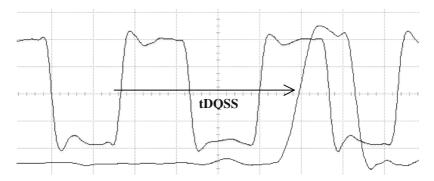

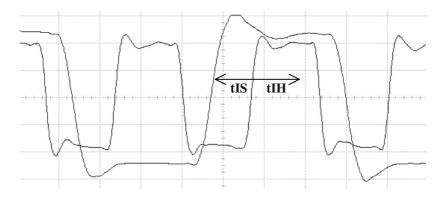

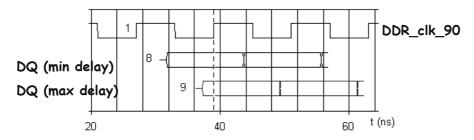

| Implementing High-Speed Double-Data Rate (DDR)         SDRAM Controllers on FPGA         E. Picatoste-Olloqui, F. Cardells-Tormo, J. Sempere-Agullo,         A. Herms-Berenguer | 279 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Logic Modules with Shared SRAM Tables<br>for Field-Programmable Gate Arrays<br><i>F. Kocan, J. Meyer</i>                                                                        | 289 |

| Network Processing                                                                                                                                                              |     |

| A Modular System for FPGA-Based TCP Flow Processing<br>in High-Speed Networks<br>D.V. Schuehler, J.W. Lockwood                                                                  | 301 |

| Automatic Synthesis of Efficient Intrusion Detection Systems<br>on FPGAs                                                                                                        | 311 |

| Testing                                                                                                                                                                         |     |

| BIST Based Interconnect Fault Location for FPGAs<br>N. Campregher, P.Y.K. Cheung, M. Vasilko                                                                                    | 322 |

| FPGAs BIST Evaluation                                                                                                                                                           | 333 |

| Applications                                                                                                                                                                    |     |

| Solving SAT with a Context-Switching Virtual Clause Pipeline<br>and an FPGA Embedded Processor<br><i>C.J. Tavares, C. Bungardean, G.M. Matos, J.T. de Sousa</i>                 | 344 |

| Evaluating Fault Emulation on FPGA<br>P. Ellervee, J. Raik, V. Tihhomirov, K. Tammemäe                                                                                          | 354 |

| Arithmetic 2                                                                                                                                                                    |     |

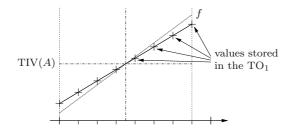

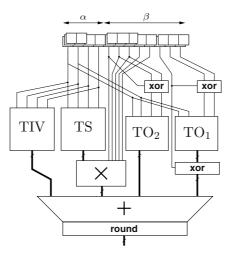

| Automating Optimized Table-with-Polynomial Function Evaluation<br>for FPGAs<br>DU. Lee, O. Mencer, D.J. Pearce, W. Luk                                                          | 364 |

| Multiple Restricted Multiplication<br>N. Sidahao, G.A. Constantinides, P.Y.K. Cheung                                                                                            | 374 |

#### Signal Processing 1

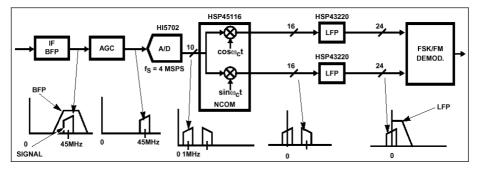

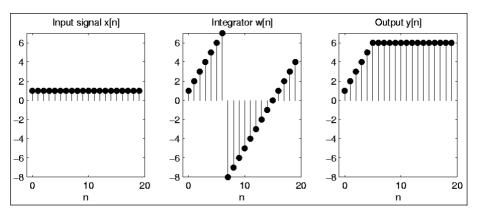

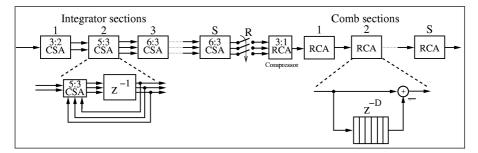

| Area*Time Optimized Hogenauer Channelizer Design<br>Using FPL Devices<br>U. Meyer-Bäse, S. Rao, J. Ramírez, A. García                                          | 384 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A Steerable Complex Wavelet Construction and Its Implementation<br>on FPGA                                                                                     | 394 |

| Computational Models and Compiler                                                                                                                              |     |

| Programmable Logic Has More Computational Power<br>than Fixed Logic<br><i>G. Brebner</i>                                                                       | 404 |

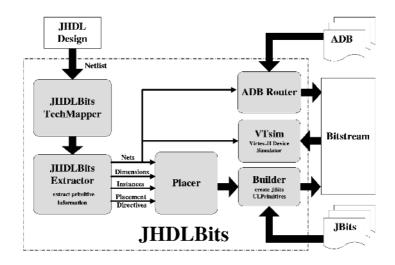

| JHDLBits: The Merging of Two Worlds A. Poetter, J. Hunter, C. Patterson, P. Athanas, B. Nelson, N. Steiner                                                     | 414 |

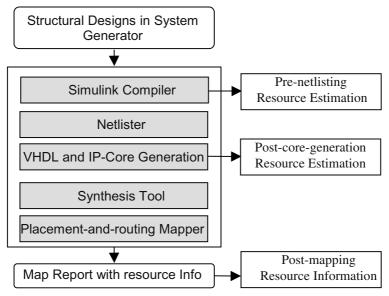

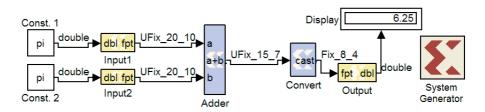

| A System Level Resource Estimation Tool for FPGAs<br>C. Shi, J. Hwang, S. McMillan, A. Root, V. Singh                                                          | 424 |

| The PowerPC Backend Molen Compiler<br>E. Moscu Panainte, K. Bertels, S. Vassiliadis                                                                            | 434 |

| Dynamic Reconfiguration 1                                                                                                                                      |     |

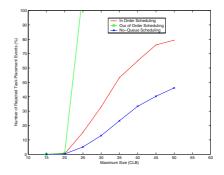

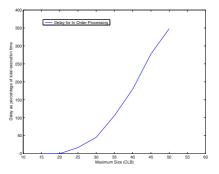

| An Integrated Online Scheduling and Placement Methodology<br>M. Handa, R. Vemuri                                                                               | 444 |

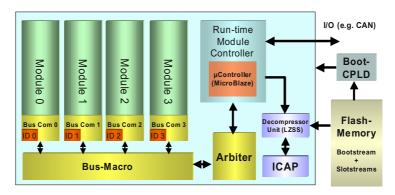

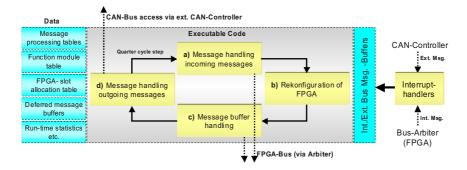

| On-Demand FPGA Run-Time System for Dynamical Reconfiguration<br>with Adaptive Priorities<br>M. Ullmann, M. Hübner, B. Grimm, J. Becker                         | 454 |

| Techniques for Virtual Hardware on a Dynamically Reconfigurable<br>Processor – An Approach to Tough Cases –<br>H. Amano, T. Inuo, H. Kami, T. Fujii, M. Suzuki | 464 |

| Throughput and Reconfiguration Time Trade-Offs:<br>From Static to Dynamic Reconfiguration in Dedicated Image Filters<br>M.R. Boschetti, S. Bampi, I.S. Silva   | 474 |

| Network and Optimization Algorithms                                                                                                                            |     |

| Over 10Gbps String Matching Mechanism<br>for Multi-stream Packet Scanning Systems                                                                              | 484 |

Y. Sugawara, M. Inaba, K. Hiraki

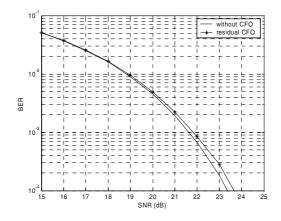

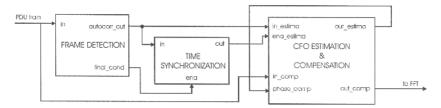

| Hardware Design of a FPGA-Based Synchronizer for Hiperlan/2<br>M.J. Canet, F. Vicedo, V. Almenar, J. Valls, E.R. de Lima                                                                                         | 494 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

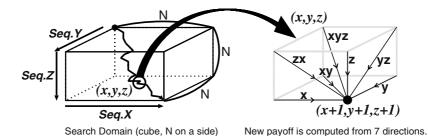

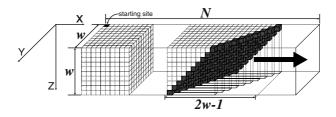

| Three-Dimensional Dynamic Programming for Homology Search<br>Y. Yamaguchi, T. Maruyama, A. Konagaya                                                                                                              | 505 |

| An Instance-Specific Hardware Algorithm<br>for Finding a Maximum Clique<br>S. Wakabayashi, K. Kikuchi                                                                                                            | 516 |

| System-on-Chip 1                                                                                                                                                                                                 |     |

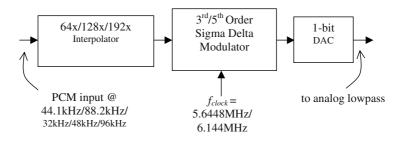

| <ul> <li>IP Generation for an FPGA-Based</li> <li>Audio DAC Sigma-Delta Converter</li> <li><i>R. Ludewig, O. Soffke, P. Zipf, M. Glesner, K.P. Pun,</i></li> <li><i>K.H. Tsoi, K.H. Lee, P. Leong</i></li> </ul> | 526 |

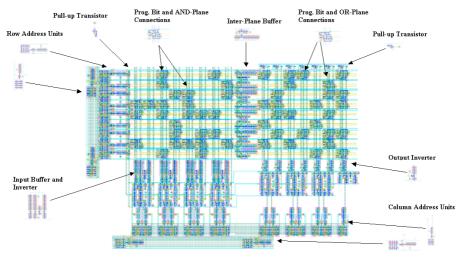

| Automatic Creation of Reconfigurable PALs/PLAs for SoC<br>M. Holland, S. Hauck                                                                                                                                   | 536 |

| High Speed Design                                                                                                                                                                                                |     |

| A Key Agile 17.4 Gbit/sec Camellia Implementation<br>D. Denning, J. Irvine, M. Devlin                                                                                                                            | 546 |

| High Performance True Random Number Generator<br>in Altera Stratix FPLDs<br>V. Fischer, M. Drutarovský, M. Šimka, N. Bochard                                                                                     | 555 |

| Security and Cryptography 2                                                                                                                                                                                      |     |

| A Universal and Efficient AES Co-processor                         |      |

|--------------------------------------------------------------------|------|

| for Field Programmable Logic Arrays                                | 565  |

| N. Pramstaller, J. Wolkerstorfer                                   |      |

| Employing Anal /Dalay The deaffer in an AEC EDCA Invalance testion | F 77 |

Exploring Area/Delay Tradeoffs in an AES FPGA Implementation ..... 575 J. Zambreno, D. Nguyen, A. Choudhary

# Architectures 2

| Reconfigurable Instruction Set Extension for Enabling ECC |     |

|-----------------------------------------------------------|-----|

| on an 8-Bit Processor                                     | 586 |

| S. Kumar, C. Paar                                         |     |

#### Memory 2

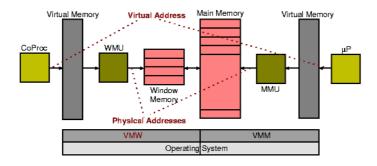

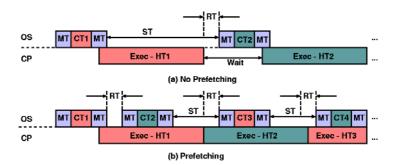

| Dynamic Prefetching in the Virtual Memory Window          |     |

|-----------------------------------------------------------|-----|

| of Portable Reconfigurable Coprocessors                   | 596 |

| M. Vuletić, L. Pozzi, P. Ienne                            |     |

| Storage Allocation for Diverse FPGA Memory Specifications | 606 |

| D. Dagher, I. Ouaiss                                      |     |

#### Image Processing 1

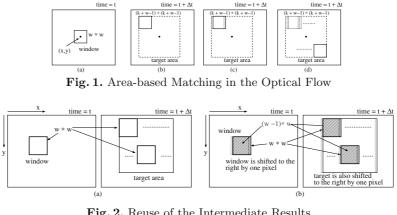

| Real Time Optical Flow Processing System       | . 617 |

|------------------------------------------------|-------|

| J. Díaz, E. Ros, S. Mota, R. Carrillo, R. Agis |       |

#### Network-on-Chip

| Network-on-Chip for Reconfigurable Systems:                     |     |

|-----------------------------------------------------------------|-----|

| From High-Level Design Down to Implementation                   | 637 |

| T.A. Bartic, D. Desmet, JY. Mignolet, T. Marescaux, D. Verkest, |     |

| S. Vernalde, R. Lauwereins, J. Miller, F. Robert                |     |

| A Reconfigurable Recurrent Bitonic Sorting Network              |     |

| for Concurrently Accessible Data                                | 648 |

| C. Layer, HJ. Pfleiderer                                        |     |

#### Power Aware Design 1

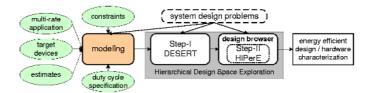

| A Framework for Energy Efficient Design of Multi-rate Applications |     |

|--------------------------------------------------------------------|-----|

| Using Hybrid Reconfigurable Systems                                | 658 |

| S. Mohanty, V.K. Prasanna                                          |     |

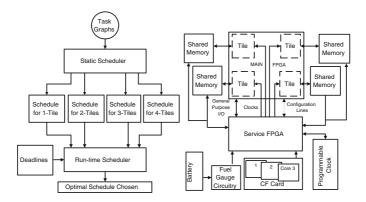

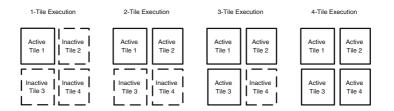

| An Efficient Battery-Aware Task Scheduling Methodology             |     |

| for Portable RC Platforms                                          | 669 |

| J. Khan. R. Vemuri                                                 |     |

# **IP-Based Design**

| HW/SW Co-design by Automatic Embedding of Complex IP Cores<br>H. Lange, A. Koch                                                | 679 |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| Increasing Pipelined IP Core Utilization in Process Networks<br>Using Exploration<br>C. Zissulescu, B. Kienhuis, E. Deprettere | 690 |

| Distribution of Bitstream-Level IP Cores<br>for Functional Evaluation Using FPGAs<br><i>R. Siripokarpirom</i>                  | 700 |

| SOC and RTOS: | Managing IPs a | nd Tasks | Communications | <br>710 |

|---------------|----------------|----------|----------------|---------|

| A. Segard, F. | Verdier        |          |                |         |

# Power Aware Design 2

| The Impact of Pipelining on Energy per Operation<br>in Field-Programmable Gate Arrays                              | 719 |

|--------------------------------------------------------------------------------------------------------------------|-----|

| A Methodology for Energy Efficient FPGA Designs<br>Using Malleable Algorithms<br>J. Ou, V.K. Prasanna              | 729 |

| Power-Driven Design Partitioning<br>R. Mukherjee, S.O. Memik                                                       | 740 |

| Power Consumption Reduction Through Dynamic Reconfiguration<br>M.G. Lorenz, L. Mengibar, M.G. Valderas, L. Entrena | 751 |

### **Coprocessing Architectures**

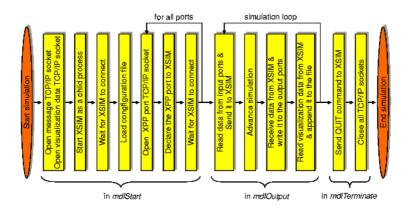

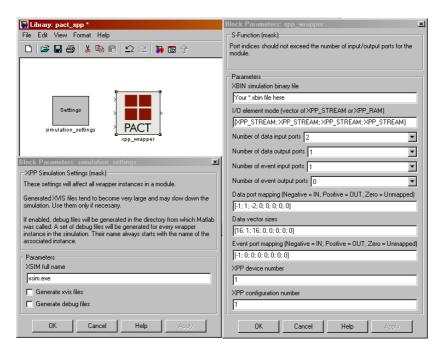

| The XPP Architecture and Its Co-simulation<br>Within the Simulink Environment<br>M. Petrov, T. Murgan, F. May, M. Vorbach, P. Zipf, M. Glesner                                                                        | 761 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

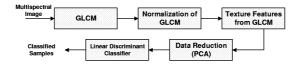

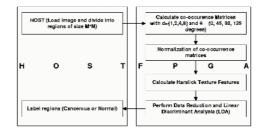

| An FPGA Based Coprocessor for the Classification<br>of Tissue Patterns in Prostatic Cancer                                                                                                                            | 771 |

| Increasing ILP of RISC Microprocessors<br>Through Control-Flow Based Reconfiguration<br>S. Köhler, J. Braunes, T. Preußer, M. Zabel, R.G. Spallek                                                                     | 781 |

| Using of FPGA Coprocessor for Improving the Execution Speed<br>of the Pattern Recognition Algorithm for ATLAS –<br>High Energy Physics Experiment<br><i>C. Hinkelbein, A. Khomich, A. Kugel, R. Männer, M. Müller</i> | 791 |

| Embedded Tutorials                                                                                                                                                                                                    |     |

| Partial and Dynamically Reconfiguration of Xilinx Virtex-II FPGAs<br>B. Blodget, C. Bobda, M. Huebner, A. Niyonkuru                                                                                                   | 801 |

| SystemC for the Design and Modeling of Programmable Systems<br>A. Donlin, A. Braun, A. Rose                                                                                                                           | 811 |

| An Evolvable Hardware Tutorial | 821 |

|--------------------------------|-----|

| J. Torresen                    |     |

#### **Dynamic Reconfiguration 2**

| A Runtime Environment<br>for Reconfigurable Hardware Operating Systems<br><i>H. Walder, M. Platzner</i>                                                                                                 | 831 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A Dynamically Reconfigurable<br>Asynchronous FPGA Architecture<br>X. Jia, J. Rajagopalan, R. Vemuri                                                                                                     | 836 |

| Hardware Support for Dynamic Reconfiguration in Reconfigurable<br>SoC Architectures<br>B. Griese, E. Vonnahme, M. Porrmann, U. Rückert                                                                  | 842 |

| Physical Design 2                                                                                                                                                                                       |     |

| Optimal Routing-Conscious Dynamic Placement<br>for Reconfigurable Devices                                                                                                                               | 847 |

| Optimizing the Performance of the Simulated Annealing<br>Based Placement Algorithms for Island-Style FPGAs<br>A. Danilin, S. Sawitzki                                                                   | 852 |

| Automating the Layout of Reconfigurable Subsystems<br>via Template Reduction<br>S. Phillips, A. Sharma, S. Hauck                                                                                        | 857 |

| Acceleration Application 2                                                                                                                                                                              |     |

| FPGA Acceleration of Rigid Molecule Interactions<br>T. Van Court, Y. Gu, M. Herbordt                                                                                                                    | 862 |

| <ul> <li>Mapping DSP Applications to a High-Performance Reconfigurable</li> <li>Coarse-Grain Data-Path</li> <li>M.D. Galanis, G. Theodoridis, S. Tragoudas, D. Soudris,</li> <li>C.E. Goutis</li> </ul> | 868 |

#### System Level Design

| System-Level Modeling of Dynamically Reconfigurable Co-processors | 881 |

|-------------------------------------------------------------------|-----|

| Y. Qu, K. Tiensyrjä, K. Masselos                                  |     |

|                                                                   |     |

| A Development Support System for Applications That Use            |     |

| Dynamically Reconfigurable Hardware                               | 886 |

| J. Canas Ferreira, J. Silva Matos                                 |     |

## **Physical Interconnect**

| Interconnect-Aware Mapping of Applications<br>to Coarse-Grain Reconfigurable Architectures<br>N. Bansal, S. Gupta, N. Dutt, A. Nicolau, R. Gupta | 891 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Analysis of a Hybrid Interconnect Architecture<br>for Dynamically Reconfigurable FPGAs<br><i>R. Huang, M. Handa, R. Vemuri</i>                   | 900 |

| Computational Models                                                                                                                             |     |

| Mapping Basic Recursive Structures<br>to Runtime Reconfigurable Hardware<br><i>H. ElGindy, G. Ferizis</i>                                        | 906 |

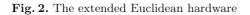

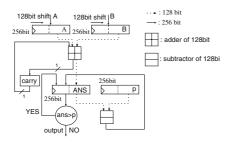

| Implementation of the Extended Euclidean Algorithmfor the Tate Pairing on FPGAT. Ito, Y. Shibata, K. Oguri                                       | 911 |

| Acceleration Applications 3                                                                                                                      |     |

| Java Technology in an FPGA<br>M. Schoeberl                                                                                                       | 917 |

| Hardware/Software Implementation of FPGA-Targeted<br>Matrix-Oriented SAT Solvers<br>V. Sklyarov, I. Skliarova, B. Pimentel, J. Arrais            | 922 |

| The Chess Monster Hydra<br>C. Donninger, U. Lorenz                                                                                               | 927 |

| Arithmetic 3                                                                                                                                     |     |

| FPGA-Efficient Hybrid LUT/CORDIC Architecture<br>I. Janiszewski, H. Meuth, B. Hoppe                                                              | 933 |

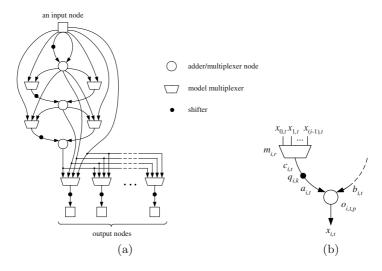

| A Multiplexer-Based Concept for Reconfigurable Multiplier Arrays<br>O.A. Pfänder, R. Hacker, HJ. Pfleiderer                                      | 938 |

| Design and Implementation of a CFAR Processor<br>for Target Detection<br><i>C. Torres-Huitzil, R. Cumplido-Parra, S. López-Estrada</i>           | 943 |

| Signal Processing 2                                                                                                                              |     |

|                                                                                                                                                  |     |

| A Parallel FFT Architecture for FPGAs | 948 |

|---------------------------------------|-----|

| J. Palmer, B. Nelson                  |     |

| FPGA Custom DSP for ECG Signal Analysis and Compression<br>M.M. Peiró, F. Ballester, G. Paya, J. Belenguer, R. Colom,<br>R. Gadea                          | 954 |