## DESIGN OF LOW POWER CARRY SKIP ADDER USING DTCMOS

T.R.Dinesh Kumar<sup>1</sup>, K.Mohana Sundaram<sup>2</sup>, M.Anto Bennet<sup>1</sup>, Aruna.R<sup>3\*</sup>, Meena.B<sup>3</sup>, M.Mohanapriya<sup>3</sup>

<sup>1</sup>Faculty of Electronics and Communication Engineering, Vel Tech, Chennai, Tamilnadu, India

<sup>2</sup>Faculty of Electrical and Electronics Engineering, Vel Tech Multitech Dr. Rangarajan Dr.

Sakunthala Engineering College,,Chennai,Tamilnadu,India

<sup>3</sup>UG Student of Electronics and Communication Engineering, Vel Tech, Chennai, Tamilnadu, India

\* Email: arunaraja95@gmail.com

Submitted: May 27, 2017 Accepted: June 15, 2017 Published: Sep 1, 2017

Abstract- In the domain of VLSI design, the adders are always meant to be the most fundamental requirements for processors of high performance and other multicore devices. It is found that power dissipation is a major problem in the electronic devices. Power management integrated circuit (PMIC) is emphasized as battery-powered portable electronics such as smart phone are commonly used. In this paper we are designing a carry skip adder which consumes less power than the other conventional adders using dynamic threshold complementary metal oxide semiconductor (DTCMOS). The circuit is designed using tanner EDA simulator of 32nm technology. Also the circuit is compared with the CMOS technology methods.

Index terms: Carry skip adder, low power consumption, high performance, speed and delay parameters

## I. INTRODUCTION

The adders are most widely used digital circuits which performs addition of numbers. Especially processors and computers make use of adders in arithmetic logic units[1,2]. The other operations which they perform in the processors are calculating table indices, addresses, and increment and decrement operators.for eg.,Ripple carry adder(RCA),carry look ahead adder(CLA),carry skip adder(CSKA),carry save adder(CSA)for multiple bit addition. The most basic circuits for adders are full adder, half adder and binary adder[3,4].

### 1.1 Analysis of adder circuits:

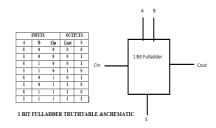

Full adder is a logic circuit which adds two input bits plus a carry-in bit and produces the outputs as a carry-out bit and a sum bit. Fig.1.The s0 of a full adder is obtained by XOR of two input bits A, B and the Cin bit. The following are the schematic and truth table.

Figure.1 full adder truth table & schematic

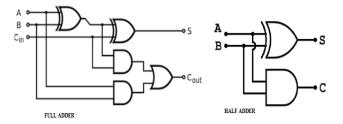

Fig.2.The two half adder circuits cascaded together forms a full adder circuit. Its schematic view is:

Figure.2 full adder circuit using gates

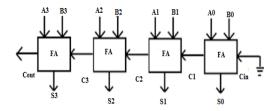

To add an N-bit number, multiple full adders are implemented in which they are cascaded in parallel. Hence we go for such multiple bit adders to reduce time consumption.RCA is a logic circuit in which each full adder's carry out is given as the carry in for the next succeeding significant full adder. It is named so, as each carry bit gets rippled to the next stage. Now there exists a term propagation delay for such operation. It is the time elapsed between the application of the input and occurrence of its corresponding output[5,6].

Consider an example as NOT gate in which the output will be "1" when an input of "0" is given. The time taken for NOT gate's output "0" after an input "1" is given to the NOT gate's input is the propagation delay found here. Similarly we can say that the carry propagation delay is the time elapsed between the application of carry-in and the occurrence of the carry-out.

Fig.3: Ripple carry adder

Fig.3. In the circuit, the sum-out (S0) and carry-out (Cout) of first full adder is only valid after the propagation delay of first full adder. Similarly, S3 of fourth full adder is valid only after the combined propagation delays of first full adder to fourth full adder. Finally, we can conclude that the final output of RCA is valid only after the joint propagation delays of all the full adders present in it[7,8].

### II. Existing Methodology:

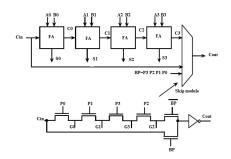

A carry skip adder is a multiple bit adder which consists of a RCA with speed up carry chain known as skip chain. The chain is the distribution of ripple carry blocks constituting skip carry blocks finally gives a skip adder. The CSKA gives us a compromise between the RCA and CLA.

Fig.4.The 8-block CSA circuit and its corresponding implementation in cadence tool are shown below:

#### T.R.Dinesh Kumar, K.Mohana Sundaram, M.Anto Bennet, Aruna.R, Meena.B, M.Mohanapriya

Design of low power carry skip adder using dtcmos

Figure.4 8-block CSA in cadence tool.

#### **Features:**

- ▶ It speeds up the computations during comparison with RCA reducing path delay.

- When both the inputs of CSKA are not equal, it skips that stage particularly since the carry propagator is a XOR operation that is always high in this condition.

Fig.5. Hence in CSKA, the linearity of carry chain delays with the size of inputs is progressed allowing carries to skip instead of rippling through them.

| ALL AND A DECK AND A DECK |   |   |   |    |   |                       |   |

|---------------------------|---|---|---|----|---|-----------------------|---|

| Sector Sector Sector      | _ | _ | _ |    | _ | _                     | _ |

|                           |   |   | _ | -  |   |                       | - |

| = :19 E=                  |   |   |   |    |   |                       |   |

|                           |   |   |   |    |   |                       |   |

| - 15 K                    |   |   |   |    |   |                       |   |

| T 1841                    |   |   | - |    |   |                       |   |

|                           | - |   |   | -  |   |                       |   |

|                           |   |   |   | -  |   |                       |   |

| = 18 t                    |   |   |   |    |   |                       |   |

| 5 18E                     |   |   |   |    | - |                       | _ |

| 1 181-                    |   |   |   |    | - |                       |   |

|                           |   |   |   |    |   | -                     |   |

|                           |   | _ |   | _  |   | and the second second |   |

| 1 1 K 10 K 100            |   |   |   | -  |   |                       |   |

| : 2011日                   |   |   |   | -  | - |                       |   |

| 1 (188) ····              |   |   |   |    |   |                       |   |

|                           |   | - | - |    | _ |                       | _ |

| E.G                       |   |   |   | -  |   | -                     |   |

| 5-6-1                     |   |   |   |    |   |                       |   |

|                           |   |   |   | -  | - | -                     | - |

| -                         |   | - |   | 22 |   | -                     | _ |

Figure.5 simulation of 8-block

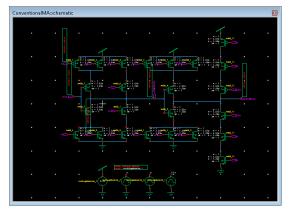

Fig.8. The CSKA circuit using CMOS technology is designed as shown below:

Figure.8 conventional CSKA

Hence we could say that there was a reduction in power consumption and delay factors as shown in below table. Though the number of transistors used is increased but the delay has been reduced accordingly.

| FACTO      | RC   | 2BLOC | 4BLOC | 8BLOC |

|------------|------|-------|-------|-------|

| RS         | Α    | K     | K     | K     |

|            |      | CSKA  | CSKA  | CSKA  |

| Power(µ    | 0.53 | 0.614 | 0.68  | 0.73  |

| <b>W</b> ) |      |       |       |       |

| Delay(ns)  | 47.1 | 46.79 | 44.47 | 41.53 |

|            | 8    |       |       |       |

| Transisto  | 160  | 186   | 214   | 258   |

| rs         |      |       |       |       |

Table.1 parameter analysis

Table.2.Average power consumption by the circuit

| TECHNIQUES | AVERAGE |

|------------|---------|

|            | POWER   |

| CMOS       | 3.04µW  |

| DTCMOS     | 2.87µW  |

## III. Proposed Technique:

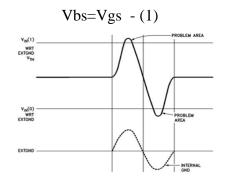

The DTCMOS technique is a concept in which the input voltage is greater than zero for NMOS and negative for PMOS. Hence accordingly the threshold voltage gets reduced. This

Design of low power carry skip adder using dtcmos

technique uses the body terminal too along with the other three terminals as input signal. That is, the gate and the body terminal are shorted. Hence we can say,

Figure.9 applied input signals

Fig.9. Also the relation of threshold voltage Vt and input signal is given by,

$VT0 = 2\phi B + VFB + 2q\epsilon sNa (2\phi B) Cox - (2)$

VFB - flat band voltage

$\phi B$  - inversion layer voltage

Na - channel doping,

εs - Si permittivity,

q - Electron charge.

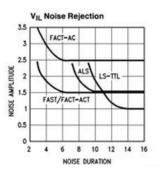

## **3.1.Dynamic thresholds are characterized as:**

The dynamic threshold characteristics of a circuit are specified by VIHD and VILD. Those are defined as:

VIHD-The minimum HIGH input level where the normal switching characteristics are observed during output transients.

VILD - The maximum LOW input level where the normal switching characteristics are observed during output transients.

Figure.10 noise factor

## IV. Simulation Results:

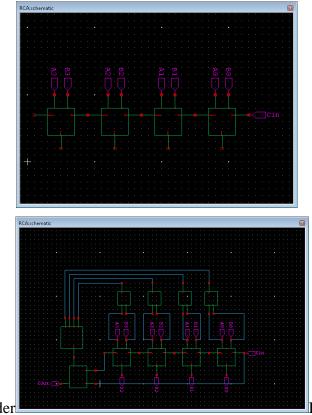

The implementation of CSKA circuit was done successfully and their respective results were obtained in the motive to reduce the power consumption. Firstly, the full adder circuit is designed using which ripple carry adder are constructed. Later the complete CSKA circuit is obtained using tanner EDA simulator as shown in figure.11:

Fig.11: full adder design

Fig.12: ripple carry adder

Fig.13: carry skip adder

#### T.R.Dinesh Kumar, K.Mohana Sundaram, M.Anto Bennet, Aruna.R, Meena.B, M.Mohanapriya

Design of low power carry skip adder using dtcmos

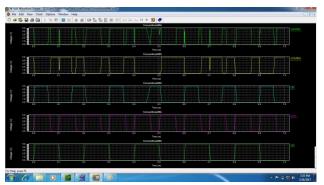

Fig.15.Output waveform for full adder

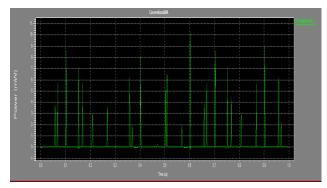

Fig.16.Average power consumed by the circuit

#### V. Conclusion:

Hence we can say that the circuit implemented using DTCMOS had much reduction of power consumption than the CMOS technology. Even the delay factor is reduced in this circuit as compared with the ripple carry adder.

#### REFERENCES

[1] Aizat Azmi, Ahmad Amsyar Azman, Sallehuddin Ibrahim, and Mohd Amri Md Yunus, "Techniques In Advancing The Capabilities Of Various Nitrate Detection Methods: A Review", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 2, June 2017, pp. 223-261.

[2] Tsugunosuke Sakai, Haruya Tamaki, Yosuke Ota, Ryohei Egusa, Shigenori Inagaki, Fusako Kusunoki, Masanori Sugimoto, Hiroshi Mizoguchi, "Eda-Based Estimation Of Visual Attention By Observation Of Eye Blink Frequency", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 2, June 2017, pp. 296-307.

[3] Ismail Ben Abdallah, Yassine Bouteraa, and Chokri Rekik, "Design And Development Of 3d Printed Myoelctric Robotic Exoskeleton For Hand Rehabilitation", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 2, June 2017, pp. 341-366.

[4] S. H. Teay, C. Batunlu and A. Albarbar, "Smart Sensing System For Enhanceing The Reliability Of Power Electronic Devices Used In Wind Turbines", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 2, June 2017, pp. 407- 424

[5] SCihan Gercek, Djilali Kourtiche, Mustapha Nadi, Isabelle Magne, Pierre Schmitt, Martine Souques and Patrice Roth, "An In Vitro Cost-Effective Test Bench For Active Cardiac Implants, Reproducing Human Exposure To Electric Fields 50/60 Hz", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 1, March 2017, pp. 1-17

[6] P. Visconti, P. Primiceri, R. de Fazio and A. Lay Ekuakille, "A Solar-Powered White Led-Based Uv-Vis Spectrophotometric System Managed By Pc For Air Pollution Detection In Faraway And Unfriendly Locations", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 1, March 2017, pp. 18-49

[7] Samarendra Nath Sur, Rabindranath Bera and Bansibadan Maji, "Feedback Equalizer For Vehicular Channel", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 1, March 2017, pp. 50- 68

[8] Yen-Hong A. Chen, Kai-Jan Lin and Yu-Chu M. Li, "Assessment To Effectiveness Of The New Early Streamer Emission Lightning Protection System", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 1, March 2017, pp. 108-123

[9] Iman Heidarpour Shahrezaei, Morteza Kazerooni and Mohsen Fallah, "A Total Quality Assessment Solution For Synthetic Aperture Radar Nlfm Waveform Generation And Evaluation In A Complex Random Media", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 1, March 2017, pp. 174- 198

[10] P. Visconti ,R.Ferri, M.Pucciarelli and E.Venere, "Development And Characterization Of A Solar-Based Energy Harvesting And Power Management System For A Wsn Node Applied To Optimized Goods Transport And Storage", International Journal on Smart Sensing and Intelligent Systems., VOL. 9, NO. 4, December 2016, pp. 1637-1667

[11] YoumeiSong, Jianbo Li, Chenglong Li, Fushu Wang, "Social Popularity Based Routing In Delay Tolerant Networks", International Journal on Smart Sensing and Intelligent Systems., VOL. 9, NO. 4, December 2016, pp. 1687-1709

[12] Seifeddine Ben Warrad and OlfaBoubaker, "Full Order Unknown Inputs Observer For Multiple Time-Delay Systems", International Journal on Smart Sensing and Intelligent Systems., VOL. 9, NO. 4, December 2016, pp. 1750-1775 [13] Rajesh, M., and J. M. Gnanasekar. "Path observation-based physical routing protocol for wireless ad hoc networks." International Journal of Wireless and Mobile Computing 11.3 (2016): 244-257.

[14]. Rajesh, M., and J. M. Gnanasekar. "Congestion control in heterogeneous wireless ad hoc network using FRCC." Australian Journal of Basic and Applied Sciences 9.7 (2015): 698-702.

[15]. Rajesh, M., and J. M. Gnanasekar. "GCCover Heterogeneous Wireless Ad hoc Networks." Journal of Chemical and Pharmaceutical Sciences (2015): 195-200.

[16]. Rajesh, M., and J. M. Gnanasekar. "CONGESTION CONTROL USING AODV PROTOCOL SCHEME FOR WIRELESS AD-HOC NETWORK." Advances in Computer Science and Engineering 16.1/2 (2016): 19.

[17]. Rajesh, M., and J. M. Gnanasekar. "An optimized congestion control and error management system for OCCEM." International Journal of Advanced Research in IT and Engineering 4.4 (2015): 1-10.

[18]. Rajesh, M., and J. M. Gnanasekar. "Constructing Well-Organized Wireless Sensor Networks with Low-Level Identification." World Engineering & Applied Sciences Journal 7.1 (2016).

[19] L. Jamal, M. Shamsujjoha, and H. M. Hasan Babu, "Design of optimal reversible carry lookahead adder with optimal garbage and quantum cost," International Journal of Engineering and Technology, vol. 2, pp. 44–50, 2012.

[20] S. N. Mahammad and K. Veezhinathan, "Constructing online testable circuits using reversible logic," IEEE Transactions on Instrumentation and Measurement, vol. 59, pp. 101–109, 2010.

[21] W. N. N. Hung, X. Song, G. Yang, J. Yang, and M. A. Perkowski, "Optimal synthesis of multiple output boolean functions using a set of quantum gates by symbolic reachability analysis," IEEE Trans. on CAD of Integrated Circuits and Systems, vol. 25, no. 9, pp. 1652–1663, 2006.

[22] F. Sharmin, M. M. A. Polash, M. Shamsujjoha, L. Jamal, and H. M. Hasan Babu, "Design of a compact reversible random access memory," in 4th IEEE International Conference on Computer Science and Information Technology, vol. 10, june 2011, pp. 103–107.

[23] Dr. AntoBennet, M, Sankar Babu G, Suresh R, Mohammed Sulaiman S, Sheriff M, Janakiraman G, Natarajan S, "Design & Testing of Tcam Faults Using  $T_H$  Algorithm", Middle-East Journal of Scientific Research 23(08): 1921-1929, August 2015.

[24] Dr. AntoBennet, M "Power Optimization Techniques for sequential elements using pulse triggered flipflops", International Journal of Computer & Modern Technology, Issue 01, Volume01, pp 29-40, June 2015.