# A Compact Analytical Design of Dual-Loop 18 GHz Frequency Synthesizer to Enhance Signal Reliability in Digital Millimeter Radio Link System

Mahmoud Moghavvemi,<sup>1,\*</sup> Hossein Ameri<sup>1</sup> and Aliyar Attaran<sup>1</sup>

<sup>1</sup> University of Malaya, Malaysia

**Abstract.** In this paper a high resolution dual-loop 17.7–19.7 GHz frequency synthesizer is presented which is compatible with ITU-R (F.595-6) standards. The investigations of phase noise and spur frequency contents are discussed in detail. The simulated and measured phase noise and spur frequency contents are similar to one another. Phase noise of -81 dBc/Hz in 17.7 GHz at 10 KHz offset frequency is measured by (HP8560) series Spectrum analyzer and it matches with predicted measurements.

**Keywords.** Dual-Band, Frequency Synthesizer, IRTU-R (F.595-6), Digital Millimeter Radio Link System.

**PACS<sup>®</sup>(2010).** 06.30.Ft, 06.20.fb, 84.40.-x, 07.57.Kp, 07.57.Hm.

#### 1 Introduction

A high frequency dual-loop frequency synthesizer is very complex to construct but it is a crucial functional block in telecommunication systems. It has the least trade-offs among all synthesizer structures. In a dual-loop frequency synthesis structure, one synthesizer loop operates in high frequency and consumes more power than other loops.

In wireless transmission systems, synthesizers are the heart of the system in which data transmission performances such as channel speed switching, signal purity and integrity are determined. Indirect synthesis such as dual-loop structure can offer these performance requirements unlike direct-digital synthesis (DDS) where the modulated signal is directly synthesized at the output frequency with adequate performance quality ([1–3]). The high resolution

**Corresponding author:** Mahmoud Moghavvemi, Center of Research in Applied Electronics CRAE, Department of Engineering, University of Malaya, 50603 Malaysia;

E-mail: mahmoud@um.edu.my.

Received: October 29, 2010.

property allows not only a fine channel frequency selection, but accurate constant-amplitude continuous-phase modulation at the output frequency ([4]).

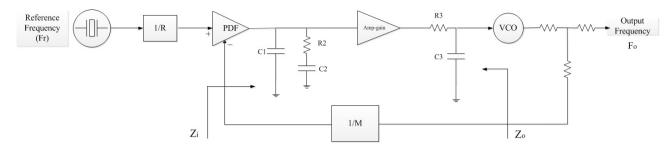

Figure 1 illustrates a general synthesizer block diagram. The relationship between input reference frequency and output frequency is shown by equation (1):

$$F_{\text{output}} = \frac{M}{R} F_r. \tag{1}$$

The relationship between the output phase noise and reference frequency phase noise is as below:

$$PN_{\text{output}} = PN_r + 20\log\frac{M}{R}.$$

(2)

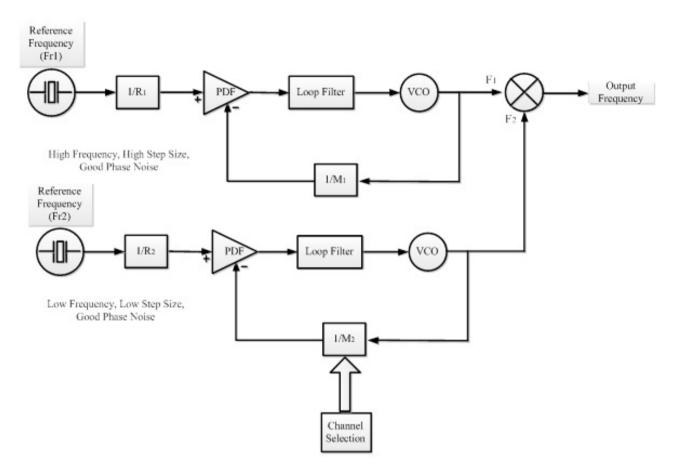

For achieving an acceptable phase noise with good resolution, a dual-loop synthesizer structure is introduced, in which one loop generates low frequency with low step size, and the other loop generates high frequency with large step size. By mixing the output frequency of these two loops, a high frequency with low step size can be achieved.

A general dual-loop synthesizer block diagram is shown in Figure 2.

The output frequency equation is given by equation (3):

$$F_{\text{out}} = \frac{M_1}{R_1} F_{r1} + \frac{M_2}{R_2} F_{r2}.$$

(3)

For dual-loop synthesizers working in Ku band, one single loop in L band and one single loop in X-band are designed to achieve 18 GHz output.

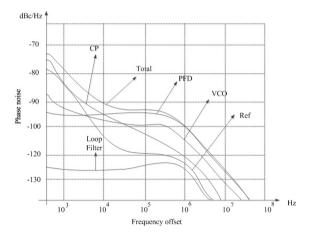

The modeled phase noise contributed from each functional synthesizer loop block is shown in Figure 3.

Table 1 shows an extensive performance comparison between various synthesizer structures based on their performance.

### 2 Phase Noise Modeling

Phase noise dictates the performance quality of the high-speed telecommunication transceivers. Phase noise in frequency-domain and jitter noise in time-domain are used to characterize digital micrometer wave link systems for high-speed radio application.

Figure 1. Basic single loop block diagram of a synthesizer.

In Figure 1, the third order loop filter, trans-impedance can be expressed as:

$$G(s) = \frac{Z_i(f) \times \frac{1}{i2\pi f C_3}}{Z_i(f) + R_3 + \frac{1}{i2\pi f C_3}},$$

(4)

$$G(s) = \frac{i2\pi f R_2 C_2 + 1}{i2\pi f \times (i2\pi f R_2 C_2 C_1 + C_1 + C_2)}.$$

(5)

Generally, every functional loop block in the synthesizer is a noise source (intrinsic). All the intrinsic noise sources in the synthesizer loop are uncorrelated. Hence the powerspectrum density (PSD) noise at the output is the superposition of all the noise contributions from each block multiplied by their noise transfer function ([5]).

Reference noise  $N_{\text{ref}}$  is the phase noise contribution of reference oscillator in (f) offset frequency, and it can be modeled as:

$$N_{\text{ref}}(f) = N_{\text{ref}}(\Delta f) \frac{(\Delta f)^2}{f^2} + N_{\text{ref-floor}}$$

(6)

where  $N_{\rm ref}(\Delta f)$  is the phase noise at  $\Delta f$  offset frequency in the  $-20\,{\rm dB/dec}$  spectrum region,  $N_{\rm ref-floor}$  is the noise floor of the reference oscillator.

The noise from the reference oscillator in the output will be

$$N_{\rm ref,inoutput} = N_{\rm ref} N^2 H^2$$

where  $H = 1 - \frac{1}{1 + \frac{H_0}{N}}$ . (7)

Phase detector noise  $N_{\rm PDF-ref}$  is generated in transistorlevel integrated-circuitry (IC) fabricated in factory, whose noise floor is proportional to  $10 \log(F_{\rm ref}/1 \text{ Hz})$ . The actual noise is flat with respect to the operating frequency, and by setting a proper loop bandwidth, the effective  $N_{\rm PFD}$  can be filtered out ([6]).

$$\log (N_{\text{PFD}}) = G_{\text{cl}}(f) \times \frac{N_{\text{PDF-ref}} + 10 \log(\frac{F_{\text{ref}}}{1 \text{ Hz}})}{20}$$

(8)

where  $G_{cl}(f)$  is the close-loop gain of the synthesizer loop ([8]).

Loop filter noise  $N_{\rm fil}$  can be modeled from noise current and the admittance of the loop filter,  $Y_{\rm fil}$ .

$$N_{\rm fil}(s) = 2 \cdot K \cdot T \cdot Re(Y_{\rm fil}(s)) \tag{9}$$

where K is Boltzmann's constant, T is the absolute temperature, and  $Y_{\rm fil}$  is  $1/Z_i + 1/Z_o$ , as shown in Figure 2, the complex admittance of the loop filter. Finally the loop filter contribution in output can be expressed as ([7,8])

$$N_{\text{fil,inoutput}} = N_{\text{fil}}(s) |G(s)|^2 \left| \frac{K_{\text{VCO}}}{s} \right|^2 \cdot (1 - H^2)$$

(10)

Charge-pump noise  $N_{\rm CP}$  exhibits flicker noise (1/f) and thermal noise, which is proportional to the duty cycle  $\alpha_{\rm CP}$ . For a large  $\alpha_{\rm CP}$ , the flicker noise corner will be high and the generated thermal noise will be small compared to flicker noise ([8]).

$$N_{\text{CP,inoutput}} = N_{\text{CP}} \cdot |G(s)|^2 \cdot \left| \frac{K_{\text{VCO}}}{s} \right|^2 \cdot (1 - H^2). \quad (11)$$

VCO noise N<sub>VCO</sub> can be modeled as

$$N_{\text{VCO}}(f) = N_{\text{VCO}}(\Delta f) \frac{(\Delta f)^2}{f^2} \left( 1 + \frac{f_{c,\text{VCO}}}{f} \right) + N_{\text{VCO,floor}}$$

(12)

where  $N_{\text{VCO}}(\Delta f)$  is the VCO phase noise at  $\Delta f$  offset frequency,  $f_{c,\text{VCO}}$  is the  $1/f^3$  noise corner of VCO and  $N_{\text{VCO,floor}}$  is the noise floor of VCO. The VCO noise contribution in the output frequency can be expressed as ([6])

$$N_{\text{VCO,inoutput}} = N_{\text{VCO}} \left| 1 - H \right|^2. \tag{13}$$

For uncorrelated noise sources, the respective noise spectra must be summed up to obtain total phase noise spectrum at the frequency synthesizer output.

$$N_{

m total,inoutput} = N_{

m ref,inoutput} + N_{

m PFD,inoutput} \ + N_{

m CP,inoutput} + N_{

m fil,inoutput} \ + N_{

m VCO,inoutput} + N_{

m divider,inoutput}.$$

The modeled phase noise contributed from each functional synthesizer loop block is shown in Figure 3.

Table 1 shows an extensive performance comparison between various synthesizer structures based on their performance.

Figure 2. Basic block diagram of dual-loop synthesizer.

#### 3 System Block Diagram

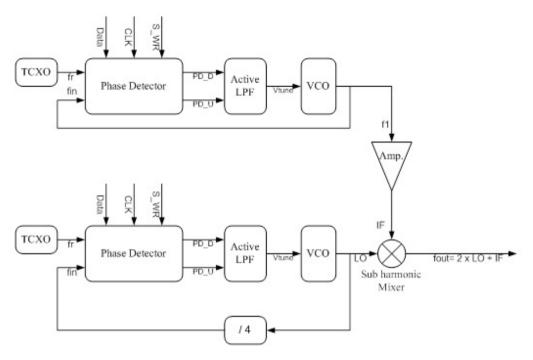

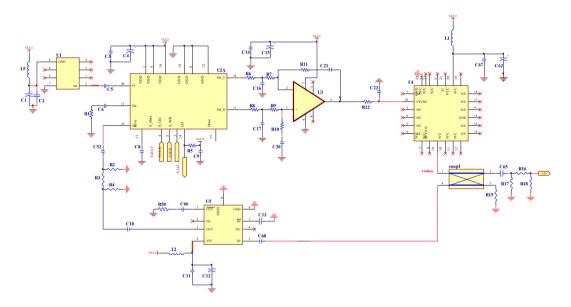

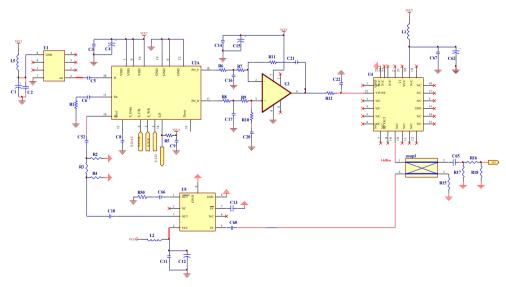

The block diagram of the 18 GHz synthesizer is shown in Figure 4. The structure is dual loop and thus there are two phase lock loops to generate the IF and LO signals. Both signals are combined in a sub harmonic mixer, generating the desired output frequency.

In the IF PLL, a TCXO10 is used as the reference of 10 MHz half sinewave signal. The used crystal's high phase noise performance (Table 3) and high slope in the lower edge of the signal are the main advantages of this chip which improves the phase detector efficiency.

For the phase detection part, a chip is selected that includes a phase/frequency detector and two internal digital frequency dividers M and R. The M and R values are determined by a programmable microcontroller and applied to the phase detector.

An MMIC is used as the VCO. This MMIC operates at 5 v, 10 mA DC bias. The output signal frequency of the VCO is in the 970–2150 MHz range and has a good phase noise as indicated in Table 2. The VCO's output signal is sampled and used as a feedback to PD.

In the fabricated synthesizer, the R and M values are programmed to be 5 and 518, respectively. The resulting

**Figure 3.** Modeled phase noise spectrum using the formulas.

output frequency signal  $f_{IF}$  in the locked loop state is equal to

$$f_{IF} = \frac{M}{R} f_r \Longrightarrow f_{IF} = 1036 \text{ MHz}.$$

(14)

The IF signals is passed through an amplifier to have an acceptable power level at the mixer input. The schematic of

Figure 4. The 18 GHz synthesizer block diagram.

Figure 5. The IF PLL circuit schematic.

| Refer-<br>ence | Frequency<br>range<br>(GHz) | Structure                      | Technology                 | Tuning (%) | Phase noise (dBc/Hz) | Supply voltage (V) | Spurs<br>content<br>(dBc) | Gain<br>power    |

|----------------|-----------------------------|--------------------------------|----------------------------|------------|----------------------|--------------------|---------------------------|------------------|

| [9]            | 24                          | 2 step up-<br>conversion mixer | 0.18um<br>CMOS             | 5          | _                    | 2.5                | _                         | 26.5 dBm         |

| [10]           | 13.9–<br>15.6               | Integer-N                      | 0.18um<br>CMOS             | 12.2       | -103.8 @<br>1 MHz    | 1.8                | _                         | 60 dBc           |

| [11]           | 2–18                        | MMIC                           | 0.2um<br>PHEMT             | 88         | −80 @<br>100 KHz     | _                  | < 55                      | _                |

| [12]           | 17                          | Integer-N,<br>QVCO             | 0.18um<br>CMOS             | 16.5       | −110 @<br>1 MHz      | 1                  | _                         | _                |

| [13]           | 6.3–9                       | Integer-N                      | 0.18um<br>CMOS             | 30         | -109 @<br>1 MHz      | 1.8                | -52                       | _                |

| [14]           | 10                          | Integer-N                      | 0.18um<br>CMOS             | _          | -102 @<br>1 MHz      | 1.8                | -48                       | _                |

| [15]           | 22–29                       | Direct-<br>conversion          | 0.18um<br>SiGe BiC-<br>MOS | 24         | -100.4 @<br>1 MHz    | 1.8                | <b>-47</b>                | 35/31 dB         |

| [16]           | 24.2                        | Integer-N                      | 0.18um<br>CMOS             | 6          | -106 @<br>100 KHz    | 1                  | _                         | _                |

| [17]           | 3.1–8                       | Integer-N, mixer               | 0.18um<br>CMOS             | 158        | -126 @<br>10 MHz     | 1.8                | _                         | 81.5–<br>85.2 dB |

| [18]           | 16–18.8                     | Integer-N                      | 0.13um<br>SiGe BiC-<br>MOS | 14.89      | −90 @<br>100 KHz     | 1.8                | -65                       | _                |

| this<br>work   | 17.7–<br>19.7               | Dual-loop                      | Discrete                   | 11.29      | -81 @<br>10 KHz      | 0–5.5              | -57                       | 51.83 dB         |

**Table 1.** Performance comparison between various synthesizer structures.

Figure 6. The LO PLL circuit schematic.

| Offset frequency | Phase noise (dBc/Hz) |  |  |  |

|------------------|----------------------|--|--|--|

| 1 KHz            | -70                  |  |  |  |

| 10 KHz           | -96                  |  |  |  |

| 100 KHz          | -118                 |  |  |  |

| 1 MHz            | -138                 |  |  |  |

Table 2. VCO phase noise versus offset frequency.

| Offset frequency | Phase noise (dBc/Hz) |

|------------------|----------------------|

| 1 KHz            | -55                  |

| 10 KHz           | -85                  |

| 100 KHz          | -110                 |

| 1 MHz            | -125                 |

Table 3. Xtal phase noise versus offset frequency.

the IF PLL is indicated in Figure 5. In the LO PLL, the reference frequency is generated by another TCXO, a product of RAKON Inc., to have a very low noise and high stability of 5 PPM. The phase noise versus offset is presented in Table 3 for this chip. The applied PD in the loop is the same chip as described in the previous section. An MMIC is selected for the VCO block. The MMIC has an operation frequency range of 7.8–8.7 GHz and is capable of changing the output frequency by a tune voltage of 1–11 v range. A 10 dB directional coupler is used to sample the output frequency, since the power level of the output is high enough (14 dBm). The sampled frequency is passed through a frequency divider, so  $f_{\rm in} = f_{\rm LO}/4$ .

The selected chip for the frequency divider block has a very low noise. Its operation frequency range is from DC to 12.5 GHz and its supply voltage and current are 5 v,  $100 \, \text{mA}$ , respectively. In the fabricated synthesizer, M and R are set to 4 and 83, to provide the LO output signal frequency  $f_{\text{LO}}$ :

$$\frac{f_{\rm LO}}{4} = \frac{M}{R} f_r \Longrightarrow f_{\rm LO} = 8300 \text{ MHz}. \tag{15}$$

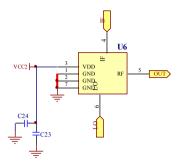

The schematic diagram of the LO PLL is shown in Figure 6. Finally, the IF and LO signals are applied to a sub harmonic mixer in order to generate the required frequency. The sub harmonic mixer MMIC has a LO internal amplifier and its conversion loss is equal to 10 dB. The frequency ranges of IF and LO signals of this chip are DC 3 GHz and 7–10.5 GHz respectively.

Considering the sub harmonic mixer characteristic, the output signal frequency will be equal to

$$f_{\text{out}} = 2 \times f_{\text{LO}} + f_{\text{in}} = 17706 \text{ MHz}.$$

(16)

Figure 7 illustrates the schematic of the sub harmonic mixer. The phase noise of the fabricated synthesizer is measured and presented in the next section.

Figure 7. Modeled mixer circuit schematic.

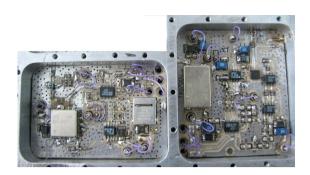

#### 4 Fabrication and Measurement Results

The synthesizer is fabricated and shown in Figure 8. The LO and IF PLL loop's VCOs have a phase noise around  $-90\,\mathrm{dBc/Hz}$  and  $-96\,\mathrm{dBc/Hz}$  at  $10\,\mathrm{KHz}$  offset, respectively, according to their datasheets. The phase noise of the LO signal decreases by  $10\log2$  factor, after multiplying by 2 in the sub harmonic mixer. Therefore, there are two signals at the sub harmonic mixer inputs: a signal with frequency of  $2\times f_{\rm LO}$  and  $-87\,\mathrm{dBc/Hz}$  phase noise, and an IF signal with  $-96\,\mathrm{dBc/Hz}$  phase noise. The output signal phase noise follows the  $2\times f_{\rm LO}$  signal phase noise considering the higher phase noise of the IF signal. So a phase noise of  $-84\,\mathrm{dBc/Hz}$  is predicted for output signal because of the sub harmonic mixer characteristic.

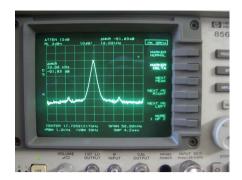

Measurement results of the fabricated synthesizer are shown in Figure 9. The frequency spectrum is observed by an HP8563A spectrum analyzer. The frequency span, RBW, and VBW are set to 50 KHz, 1 KHz, and 30 Hz, respectively. The difference between carrier and 10 KHz offset power level is equal to -51.83 dB, as indicated in Figure 9. Thus the phase noise of the output signal is obtained by the following relation ([10, 11]):

Measured phases noise =

$$-51.83-10 \log RBW$$

=  $-81.83 dBc/Hz$ . (17)

Phase noise at 1 KHz and 100 KHz offset are -60 and -100 dBc/Hz, respectively. Spur frequency contents are measured at -57 dBc. The predicted performance parameters such as gain, spur contents and phase noise are in comparable to the measured results. The comparison results indicate that the phase noise of the system is superior to its rivals.

#### 5 Conclusion

The modeling representations of all intrinsic phase noise spectrum sources of frequency synthesizer loop are discussed. The block-circuit analysis of a dual-loop synthesizer is presented. A carefully calculated frequency resolutions and design parameters in each loop are analyzed. This

Figure 8. The fabricated synthesizer.

method is proposed to dramatically reduce the phase noise effect in output oscillating frequency due to performance trade-offs in all the other synthesizer loop structures. In this paper, the methodology analysis of dual-loop frequency synthesizer and spur frequency contents and phase noise are analyzed. The performance comparison between the proposed method and previous works in this frequency is presented. The channel switching is fully programmable for 17.7–19.7 GHz frequency range. Test results indicate that the fabricated synthesizer has a phase noise of  $-81\,\mathrm{dBc/Hz}$ , much superior to the phase noise reported in the references.

## Acknowledgments

The first author was supported by the Center of Research in Applied Electronics CRAE. The second author was supported by the University of Malaya.

#### References

- [1] N. M. Filiol et al., An agile ISM band frequency synthesizer with built-in GMSK data modulation, *IEEE Journal of Solid-State Circuits* 33 (1998), no. 7, 998–1008.

- [2] T. A. D. Riley, M. A. Copeland and T. A. Kwasniewski, Delta-sigma modulation in fractional-N frequency synthesis, IEEE Journal of Solid-State Circuits 28 (1993), no. 28, 553–559.

- [3] A. Attaran, M. Moghavvemi and H. Ameri, Design a 14 to 20GHz stable source, *Microwave and RF* 49 (2010), 62–66.

- [4] M. H. Perrott, T. L. Tewksbury and C. G. Sodini, A 27 mW CMOS fractional-N synthesizer/modulator IC, *Solid-State Circuits Conference 1997*, Digest of Technical Papers, 43rd ISSCC, 1997 IEEE International, 1997.

- [5] S. A. Osmany, F. Herzel, J. C. Scheytt, K. Schmalz and W. Winkler, An integrated 19-GHz low-phase-noise frequency synthesizer in SiGeBiCMOS technology, *IEEE Compound Semiconductor Integrated Circuit Symposium*, Technology Digest, pp. 191–194, 2007.

- [6] F. Herzel, S. A. Osmany and J. C. Scheytt, Analytical Phase-Noise Modeling and Charge Pump Optimization for Fractional PLLs, *IEEE Transactions on Circuits and Systems I* Regular Papers (2010), PP(99), 1.

Figure 9. The measurement result.

- [7] A. Attaran, H. Ameri and M. Moghavvemi, Design an X-band frequency synthesizer, *Microwaves and RF* 49 (2010), 98-103.

- [8] L. Lascari, Accurate Phase Noise Prediction in PLL Synthesizers Part 2: Here is a method that uses more complete modeling for wireless applications, *Applied Microwave & Wireless* 12 (2000), no. 5, 90–94.

- [9] A. Natarajan, A. Komijani and A. Hajimiri, A fully integrated 24-GHz phased-array transmitter in CMOS, *IEEE Journal of Solid-State Circuits* 40 (2005), no. 11, 2502– 2514.

- [10] P. Yu-Hsun and L. Liang-Hung, A 16-GHz Triple-Modulus Phase-Switching Prescaler and Its Application to a 15-GHz Frequency Synthesizer in 0.18um CMOS, *IEEE Transactions on Microwave Theory and Techniques* 55 (2007), no. 1, 44–51.

- [11] J. Mondal et al., A highly integrated multifunction macro synthesizer chip (MMSC) for applications in 2–18 GHz synthesized sources, *IEEE Journal of Solid-State Circuits* 32 (1997), no. 8, 1405–1409.

- [12] A. W. L. Ng and H. C. Luong, A 1-V 17-GHz 5-mW CMOS Quadrature VCO Based on Transformer Coupling, *IEEE Journal of Solid-State Circuits* 42 (2007), no. 8, 1933–1941.

- [13] T. Geum-Young et al., A 6.3–9-GHz CMOS fast settling PLL for MB-OFDM UWB applications, *IEEE Journal of Solid-State Circuits* 40 (2005), no. 7, 1671–1679.

- [14] T. H. Lin and Y. J. Lai, An Agile VCO Frequency Calibration Technique for a 10-GHz CMOS PLL, *IEEE Journal of Solid-State Circuits* 42 (2007), no. 2, 340–349.

- [15] V. Jain et al., A Single-Chip Dual-Band 22–29-GHz/77–81-GHz BiCMOS Transceiver for Automotive Radars, *IEEE Journal of Solid-State Circuits* 44 (2009), no. 11, 3469–3485.

- [16] A. W. L. Ng et al., A 1-V 24-GHz 17.5-mW phase-locked loop in a 0.18um CMOS process, *IEEE Journal of Solid-State Circuits* 41 (2006), no. 6, 1236–1244.

- [17] Z. Hui et al., A 3.1 GHz to 8.0 GHz Single-Chip Transceiver for MB-OFDM UWB in 0.18 um CMOS Process, *IEEE Journal of Solid-State Circuits* 44 (2009), no. 2, 414–426.

- [18] B. A. Floyd, A 16–18.8-GHz Sub-Integer-N Frequency Synthesizer for 60-GHz Transceivers, *IEEE Journal of Solid-State Circuits* 43 (2008), no. 5, 1076–1086.