# REALIZATION of READOUT INTEGRATED CIRCUIT (ROIC) for an ARRAY of 288x4, N-on-P type HgCdTe LONG WAVE INFRARED DETECTORS

by

# Hüseyin KAYAHAN

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfillment of the requirements for the degree of

**Master of Science**

**Sabancı University**

**Summer, 2008**

# REALIZATION of READOUT INTEGRATED CIRCUIT (ROIC) for an ARRAY of 288x4, N-on-P type HgCdTe LONG WAVE INFRARED DETECTORS

| APPROVED BY:   |                                                      |  |

|----------------|------------------------------------------------------|--|

|                | Assoc. Prof. Dr. Yaşar GÜRBÜZ<br>(Thesis Supervisor) |  |

|                | Assist. Prof. Dr. Ayhan BOZKURT                      |  |

|                | Assoc. Prof. Dr. Meriç ÖZCAN                         |  |

|                | Assist. Prof. Dr. Cem ÖZTÜRK                         |  |

|                | Assoc. Prof. Dr. Erhan BUDAK                         |  |

|                |                                                      |  |

|                |                                                      |  |

| DATE OF ADDROV | AT.                                                  |  |

| DATE OF APPROV | AL:                                                  |  |

© Hüseyin KAYAHAN 2008

All Rights Reserved

REALIZATION of READOUT INTEGRATED CIRCUIT (ROIC) for an ARRAY of 288x4, N-on-P type HgCdTe LONG WAVE INFRARED DETECTORS

Hüseyin KAYAHAN

EE, MS Thesis, 2008

Thesis Supervisor: Assoc. Prof. Dr. Yaşar GÜRBÜZ

Keywords: Readout integrated circuit (ROIC), focal plane array (FPA), scanning FPA, time delay integration (TDI)

#### **Abstract**

Infrared (IR) imaging systems are used in a variety of applications from biomedical to astronomic and strategic imaging. Modern military missile guidance and surveillance systems also incorporate infrared imaging systems. The most critical component of an infrared imaging system is the focal plane array (FPA), a key assembly of detectors and readout electronics to carry out the function of infrared to electrical signal conversion. As in all sensor networks, extraordinary care must be given to both the detector design and readout integrated circuits, to obtain a high performance and durable system. In IRFPAs, detectors set the operation wavelength, readout circuit area and operation temperature. However many of the system performance parameters such as signal to noise ratio (SNR), linearity, input referred noise level, dynamic range, are set by the readout integrated circuit (ROIC).

First generation of IR imaging systems incorporated single detector, or a fewer number of detectors. Higher frame rate and resolution requirements brought up the scanning type of FPAs where a scene is scanned constantly to create a 2D electronic image by a single array of detectors. Scanning type FPAs, with higher frame rates, started to replace staring arrays, with the maturing of detector processing technology and allowing integration of thousands of

iv

functioning detectors (pixels) on a single substrate, with smaller pitches. However, scanning type arrays are attractive due to their lower cost.

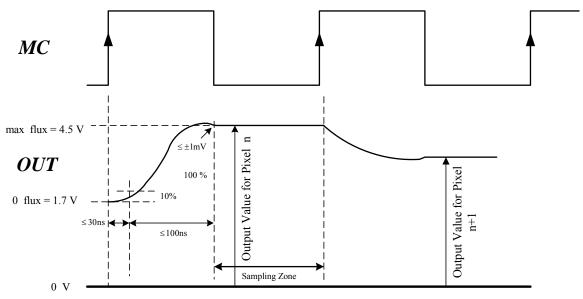

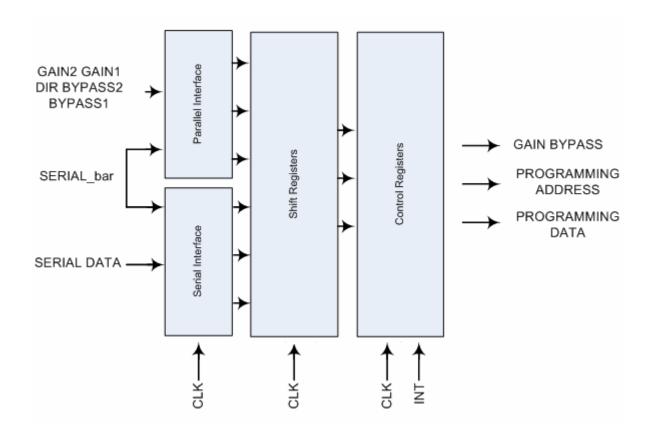

In this thesis, design of a CMOS readout integrated circuit for an array of 288x4, n-on-p type HgCdTe long wave infrared detectors is presented. ROIC input preamplifier is current mirroring integration type due to low input impedance requirement. In order to increase SNR, time delay integration (TDI) on 4 detectors is applied with a super sampling rate of 3. ROIC has additional features of bidirectional TDI scanning, dead pixel deselection, automatic gain adjustment in response to pixel deselection, in addition to programmable four gain settings (up to 2.58pC storage), and programmable integration time. ROIC has four outputs with a dynamic range of 2.8V (from 1.7V to 4.5V) and input referred noise of 2989 electrons for an area of 13mm<sup>2</sup>. Two clocks: master clock and integration clock are required in order to operate the ROIC. Integration clock sets the integration time and adjust frame rate. Master clock maintains synchronization and can be adjusted up to 5MHz. ROIC can be programmed through both serial and parallel interface with full functionality but pixel deselection being allowed only in serial interface mode.

288x4, P üzeri N türü HgCdTe UZUN DALGA BOYU KIZILÖTESİ DEDEKTÖR DİZİNİ için ENTEGRE OKUMA DEVRESİNİN GERÇEKLEŞTİRİLMESİ

Hüseyin KAYAHAN

EE, Master Tezi, 2008

Tez Danışmanı: Doç. Dr. Yaşar GÜRBÜZ

Anahtar kelimeler: Entegre okuma devresi (ROIC), odaksal düzlem dizileri (FPA), taramalı FPA, zaman geciktirmeli toplama (TDI)

Özet

Kızılötesi görüntüleme sistemleri biomedikal uygulamalardan, astronomik uygulamalara ve stratejik görüntüleme sistemlerine kadar geniş bir uygulama alanına sahiptir. Modern askeri füze güdüm sistemleri ve gözetleme sistemleri de kızılötesi görüntüleme sistemleri içermektedir. Kızılötesi sistemlerin en önemli bileşeni, kızılötesi ışımayı elektriksel işarete dönüştüren, dedektör ve dedektöre ait okuma devresinden oluşan odaksal düzlem dizileridir (FPA). Bütün sensor devrelerinde olduğuu gibi işlevsel, dayanıklı bir system tasarımı için, hem dedektör hem de okuma devresinin tasarımına özel dikkat gösterilmelidir. Bu sistemlerde, dedektörler çalışma dalga boyunu, okuma devresi alanını ve çalışma sıcaklığını belirlerken, okuma devreleri de gürültü işaret oranı (SNR), doğrusallık, girişe yansıtılmış gürültü seviyesi, dinamik aralık gibi performans parametrelerini belirlerler.

Birinci nesil kızılötesi görüntüleme sistemleri tek ya da sınırlı sayıda dedektör içermekteydi. Yüksek çerçeve hızı ve çözünürlük gereksinimleri iki boyutlu görüntü oluşturmak için bir dizi dedektörün kullanıldığı taramalı sistemleri ortaya çıkarmıştır. Dedektör işleme teknolojilerinin gelişmesi ile daha çok sayıda çalışır dedektör aynı substrata daha küçük pixel alanlarıyla üretilebilmiştir ve böylece taramalı diziler, daha yüksek çerçeve hızına sahip

vi

hareketsiz dizilerle değiştirilmeye başlanmıştır. Bununla birlikte taramalı diziler halen daha ucuz olmaları itibariyle cazip bir tercih olmayı sürdürmektedir.

Bu tezde p katman üzerine n tabakayla oluşturulmuş, yüksek dalgaboyunda çalışan, 288x4 HgCdTe kızılötesi dedektör dizisi için CMOS okuma devresi (ROIC) tasarımı gösterilmektedir. Tasarlanan okuma devresi dört eleman üzerinde üçlü örnekleme ile zaman geciktirmeli toplama (TDI), hatalı piksel ayırma ve bu ayırma işlemine göre otomatik kazanç ayarlama, dört ayarlanabilir giriş kazanç ayarı ve ayarlanabilir entegrasyon süresi özelliklerine sahiptir. Okuma devresinin dinamik aralığı 2.8 volttur (1.7-4.5V), toplam kırmık alanı 13mm² dir ve girişe yansıtılmış gürültü seviyesi 2989 elektrondur. Okuma devresinin çalışması ana saat işareti ve entegrasyon saat işareti gerekmektedir. Entegrasyon saati çerçeve hızını ve entegrasyon süresini belirler. Ana saat ise senkronizasyonu sağlar ve 5MHz'e kadar çıkabilir. Okuma devresi seri ya da parallel modda programlanabilir.

## Acknowledgements

I have started to work on this project in 2006 as an undergraduate student. I had neither a prior tape-out experience nor the vision to see how vast designing a circuit like this one was. Today, while ending my MSc study in Sabanci University, I feel technically confident, experienced and ready to face upcoming challenges. All these are possible today with the help of my professors, co-workers on this project and friends aside from the hard work and late nights across the stationary view of a workstation. I would like to thank to those people here.

First, I would like to thank to my advisor Yaşar Gürbüz, for his endless, patient guidance, his support throughout my MSc and his trust in my judgments. He was always closer than a professor to me. I am thankful to Ayhan Bozkurt for all the technical discussions and his patient help with all the problems I had with various design tools. I would also like to thank to Cem Öztürk, Meriç Özcan and Erhan Budak for their valuable comments and presences in my thesis defense

This thesis was sponsored financially by ASELSAN Inc. I thank the team that we worked with, under the supervision of Mrs. Hacer Selamoglu, Manager of the Electronics Design Group, at ASELSAN-MGEO, for their great support and valuable technical discussions through my thesis work.

Throughout my MSc study, I was supported by the scholarship supplied by TÜBİTAK and I would like to express my graditude for its contribution to my education and many young people like me as well.

I want to thank to Arzu Minareci Ergintav not only for her technical support on various design issues and for sharing the never ending tape-out nights, but also for her friendship. Also, thanks to my comrade designer Ömer Ceylan and Ahmet Kemal Bakkaloğlu for their contributions to this work.

Finally, I would like to thank to my family; my parents Ali and Ümmihan, my sister Sevil and my brother İsa, just for their love.

# **Table of Contents**

| CHAPTER 1 INTRODUCTION                                  | 1  |

|---------------------------------------------------------|----|

| 1.1 Introduction                                        | 1  |

| 1.2 Motivation                                          | 8  |

| 1.3 Organization of Thesis                              | 9  |

| CHAPTER 2 LINEAR ROIC BUILDING BLOCKS                   | 11 |

| 2.1 Introduction                                        | 11 |

| 2.2 Preamplifiers                                       |    |

| 2.2.1 Self Integration Preamplifier                     | 12 |

| 2.2.2 Source Follower per Detector Preamplifier         | 13 |

| 2.2.3 Direct Injection                                  | 14 |

| 2.2.4 Buffered Direct Injection                         |    |

| 2.2.5 Capacitive Feedback Transimpedance Amplifier      |    |

| 2.2.6 Resistor Gate Modulation                          | 18 |

| 2.2.7 Current Mirror Gate Modulation                    | 19 |

| 2.2.8 Current Mirroring Direct Injection                | 20 |

| 2.2.9 Current Mirroring Integration                     |    |

| 2.2.10 Comparison of ROIC Preamplifiers                 | 23 |

| 2.3 Time Delay Integration                              |    |

| 2.4 Additional ROIC Features                            |    |

| CHAPTER 3 288x4 ROIC IMPLEMENTATION                     |    |

| 3.1 ROIC Definition and Requirements                    |    |

| 3.2 ROIC Architecture                                   |    |

| 3.3 ROIC Implementation                                 |    |

| 3.3.1 Input Stages                                      |    |

| 3.3.1.1 Preamplifier Design                             |    |

| 3.3.1.2 Input Capacitors                                |    |

| 3.3.2 Implementation of TDI stages                      |    |

| 3.3.3 Offset Cancellation and Automatic Gain Adjustment |    |

| 3.3.4 Output Buffer Design                              |    |

| 3.3.5 Digital Circuit Design                            |    |

| 3.3.5.1 Main Control Circuit Design                     |    |

| 3.3.5.2 Interface Circuit Design                        |    |

| 3.3.4.3 Decoder and Level Shifter Design                |    |

| 3.4 Physical Design                                     | 57 |

| CHAPTER 4 RESULTS                                       |    |

| 4.1 Simulation Results of Minimum Input Current         |    |

| 4.1.1 Schematics Results                                |    |

| 4.1.2 Extracted Results                                 |    |

| 4.2 Simulation Results of Nominal Input Current         |    |

| 4.2.1 Schematics Results                                |    |

| 4.2.2 Extracted Results                                 |    |

| 4.3 Simulation Results of 25nA Input Current            |    |

| 4.3.1 Schematics Results                                |    |

| 4.3.2 Extracted Results                                 |    |

| 4.4 Simulation Results of 55nA Input Current            | 74 |

| 4.4.2 Extracted Results       76         4.5 Simulation Results with G0.50 setting       78         4.5.1 Schematics Results       78         4.5.2 Extracted Results       80         4.6 Comments on Simulation Results       82         4.7 NOISE ANALYSIS       82         4.8 MEASUREMENT RESULTS of 1x4 ROIC       84 | 4.4.1 Schematics Results                  | 74 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----|

| 4.5.1 Schematics Results       78         4.5.2 Extracted Results       80         4.6 Comments on Simulation Results       82         4.7 NOISE ANALYSIS       82         4.8 MEASUREMENT RESULTS of 1x4 ROIC       84                                                                                                     | 4.4.2 Extracted Results                   | 76 |

| 4.5.1 Schematics Results       78         4.5.2 Extracted Results       80         4.6 Comments on Simulation Results       82         4.7 NOISE ANALYSIS       82         4.8 MEASUREMENT RESULTS of 1x4 ROIC       84                                                                                                     | 4.5 Simulation Results with G0.50 setting | 78 |

| 4.6 Comments on Simulation Results824.7 NOISE ANALYSIS824.8 MEASUREMENT RESULTS of 1x4 ROIC84                                                                                                                                                                                                                               | 4.5.1 Schematics Results                  | 78 |

| 4.7 NOISE ANALYSIS                                                                                                                                                                                                                                                                                                          | 4.5.2 Extracted Results                   | 80 |

| 4.8 MEASUREMENT RESULTS of 1x4 ROIC                                                                                                                                                                                                                                                                                         | 4.6 Comments on Simulation Results        | 82 |

|                                                                                                                                                                                                                                                                                                                             | 4.7 NOISE ANALYSIS                        | 82 |

|                                                                                                                                                                                                                                                                                                                             | 4.8 MEASUREMENT RESULTS of 1x4 ROIC       | 84 |

| Chapter 5 CONCLUSIONS                                                                                                                                                                                                                                                                                                       | Chapter 5 CONCLUSIONS                     | 88 |

| REFERENCES 91                                                                                                                                                                                                                                                                                                               | REFERENCES                                | 91 |

# **List of Figures**

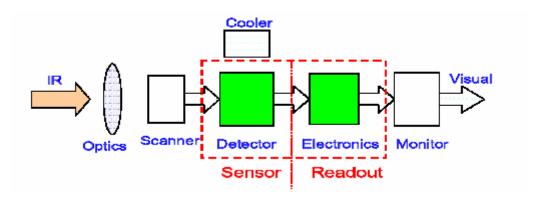

| Figure 1.1: General architecture of an infrared imaging system.                   | 1             |

|-----------------------------------------------------------------------------------|---------------|

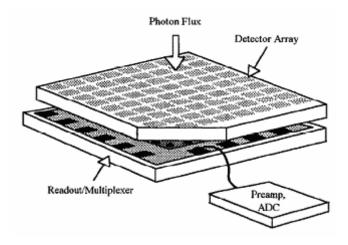

| Figure 1.2: Representation of FPA, detector array and multiplexer [2]             | 2             |

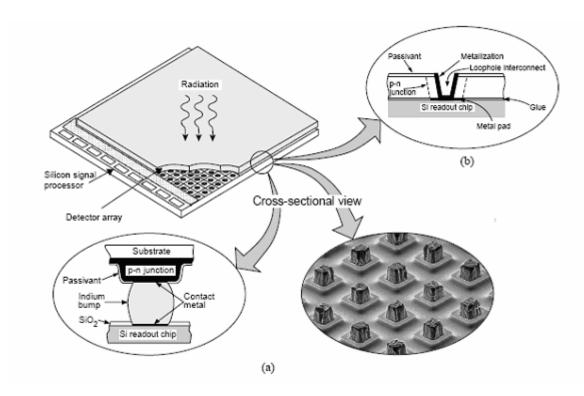

| Figure 1.3: Hybrid IRFPA with independently optimized detector and readout (a)    | indium bump   |

| technique, (b) loophole technique [2]                                             | 3             |

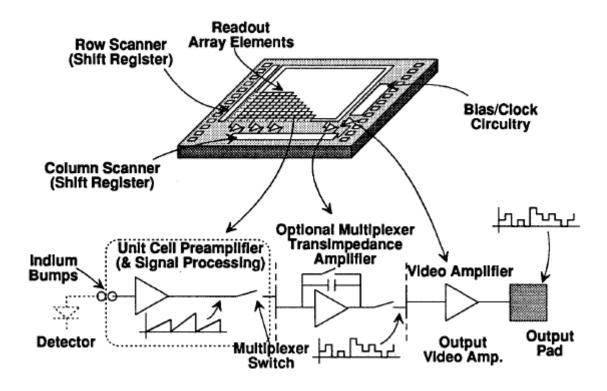

| Figure 1.4: Generic staring type ROIC. [7]                                        | 6             |

| Figure 2.1: Self integrator readout [7]                                           | 12            |

| Figure 2.2: Source follower per detector readout [7]                              | 13            |

| Figure 2.3: Direct injection preamplifier                                         | 15            |

| Figure 2.4: Buffered direct injection preamplifier                                | 16            |

| Figure 2.5: Capacitive feedback transimpedance preamplifier [7]                   | 17            |

| Figure 2.6: Resistor gate modulation preamplifier.                                | 18            |

| Figure 2.7: Current mirror gate modulation preamplifier                           | 19            |

| Figure 2.8: Current mirror direct injection preamplifier.                         | 20            |

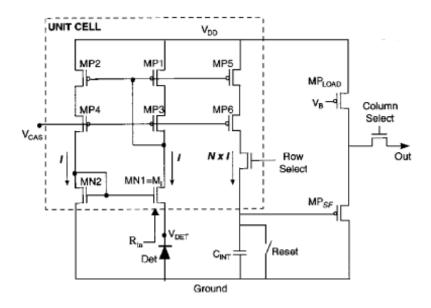

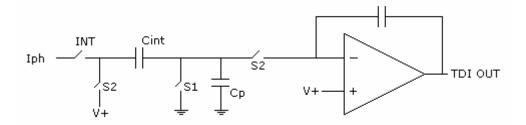

| Figure 2.9: Current mirroring integration preamplifier.                           | 22            |

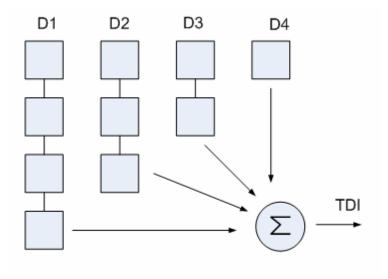

| Figure 2.10: Block diagram of TDI operation on four detectors                     | 27            |

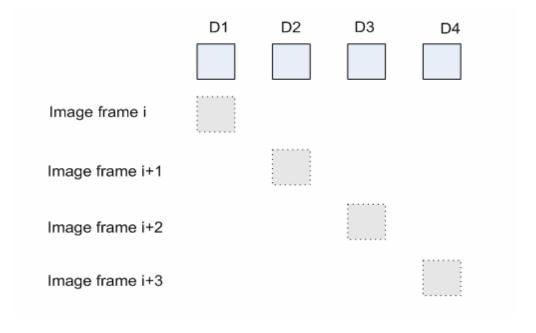

| Figure 2.11: TDI scanning on four detectors.                                      | 27            |

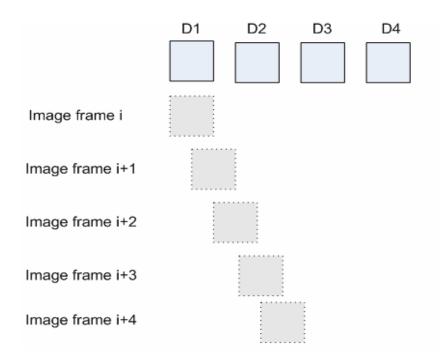

| Figure 2.12: TDI scanning on four detectors with super sampling rate of three     | 28            |

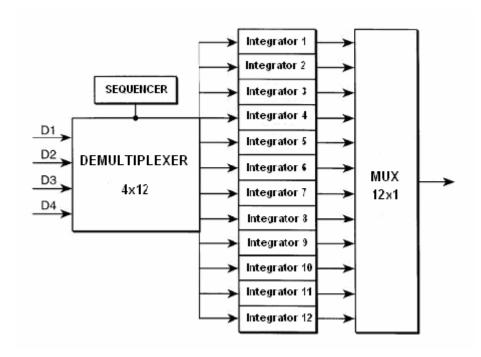

| Figure 2.13: TDI architecture with use of 12 integrators [16]                     | 29            |

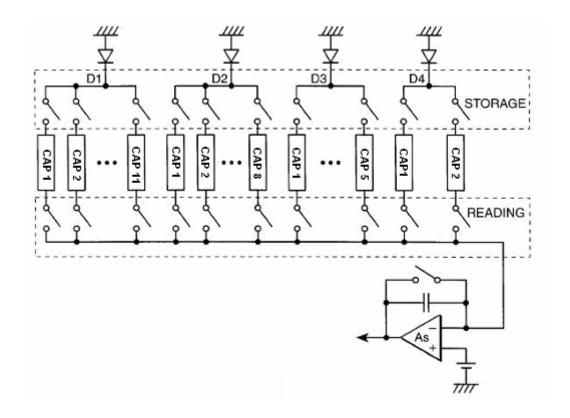

| Figure 2.14: TDI architecture with use of single integrator to a cost of more sto | rage elements |

| [16]                                                                              | 31            |

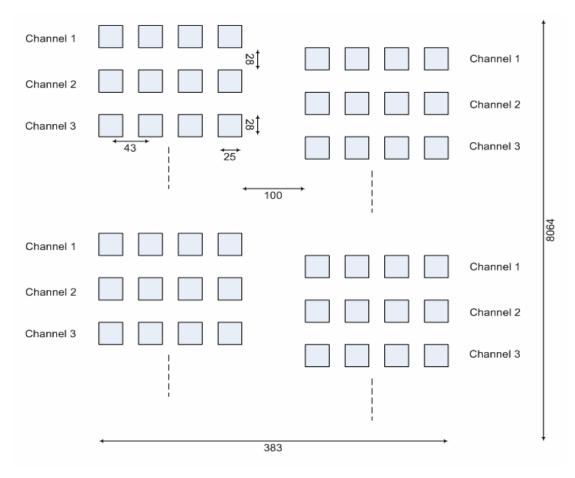

| Figure 3.1: Detector distribution and size over the FPA                           | 33            |

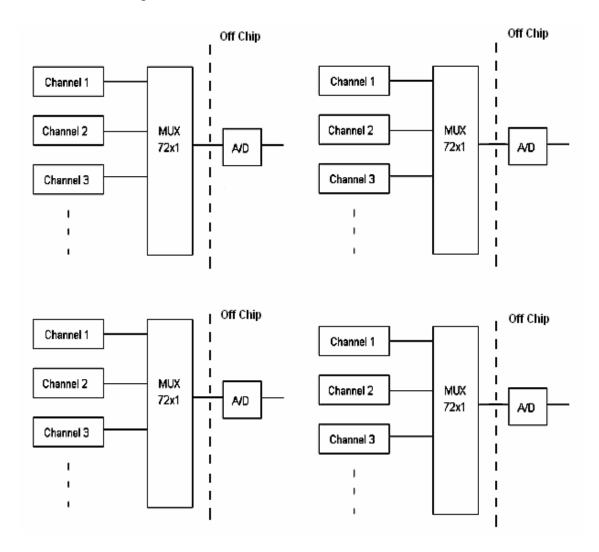

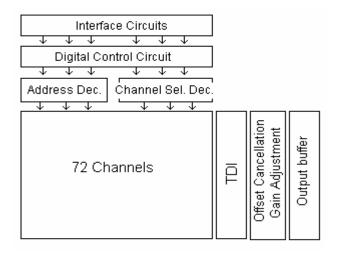

| Figure 3.2: Block diagram of 288x4 ROIC with off-chip ADC.                        | 34            |

| Figure 3.3: Block diagram of 72x4 ROIC                                            | 36            |

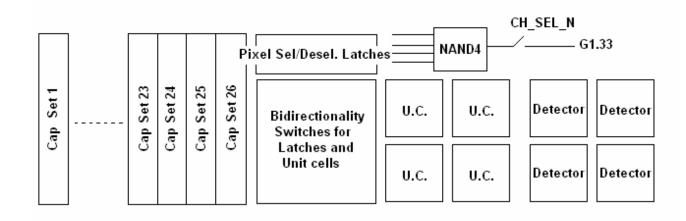

| Figure 3.4: Block diagram of a channel.                                           | 36            |

| Figure 3.5: Parasitics associated with lines to carry photocurrent.               | 37            |

| Figure 3.6: Schematic of CMI unit cell.                                           | 38            |

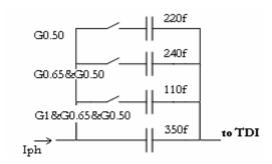

| Figure 3.7: Input Capacitors.                                                     | 40            |

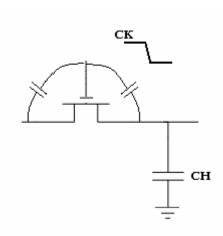

| Figure 3.8: Circuit used for realization of TDI.                                  | 41            |

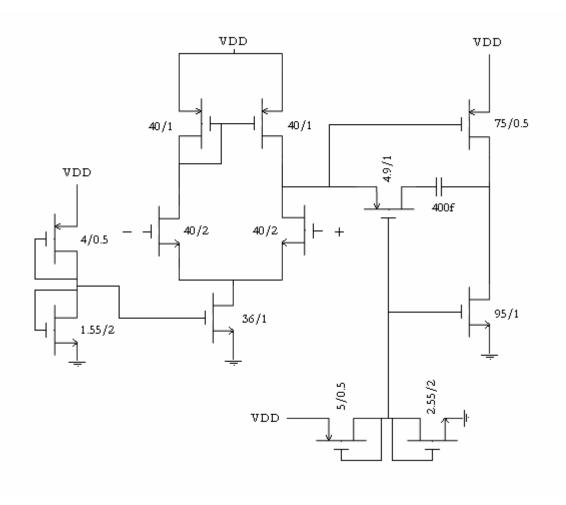

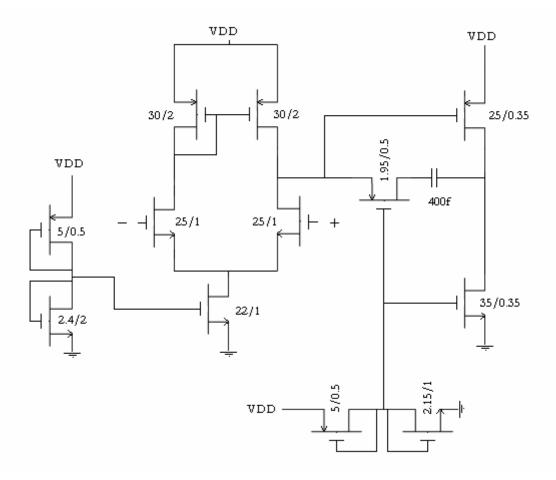

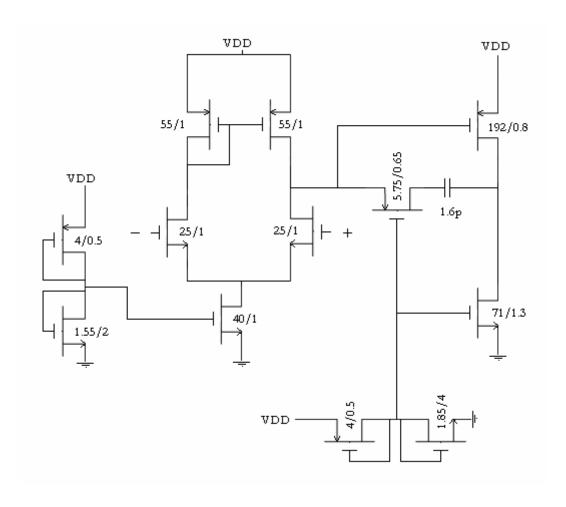

| Figure 3.9: Schematic of TDI amplifier                                            | 43            |

| Figure 3.10: Parasitic capacitances that cause clock feed through effect          | 44            |

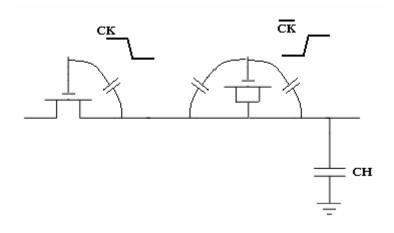

| Figure 3.11: Schematic of dummy switch method.                                    | 45            |

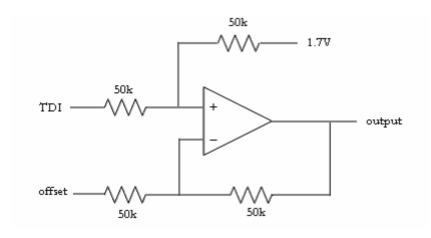

| Figure 3.12: Offset cancellation circuit.                                         | 46            |

| Figure 3.13: Schematic of amplifier used in offset cancellation circuit           | 47            |

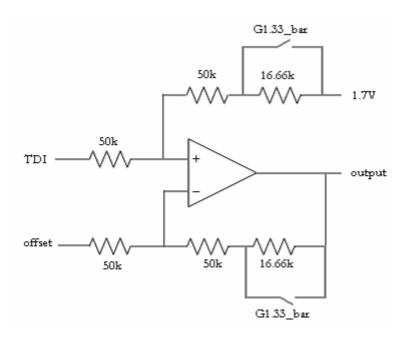

| Figure 3.14: Circuit that removes offset as well as performs automatic gain adjustment          | 48 |

|-------------------------------------------------------------------------------------------------|----|

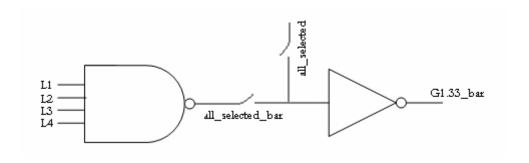

| Figure 3.15: Digital logic to set automatic gain adjustment control signal, G1.33_bar           | 48 |

| Figure 3.16: Output waveform.                                                                   | 49 |

| Figure 3.17: Schematics of amplifier used as buffer                                             | 50 |

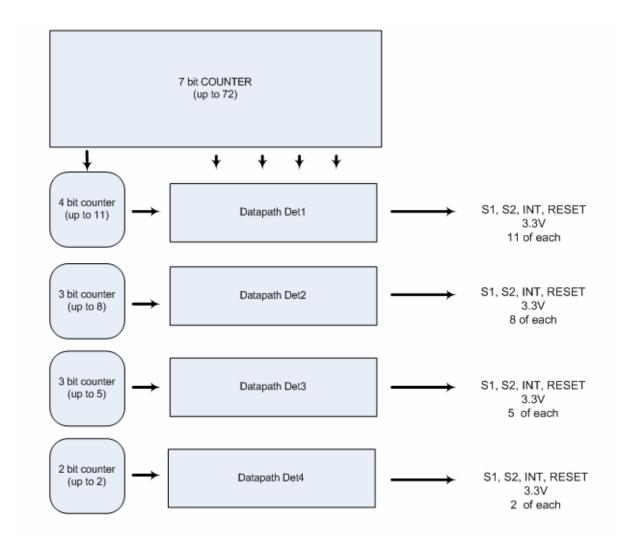

| Figure 3.18: Block diagram of main control block.                                               | 51 |

| Figure 3.19: Block diagram of interface circuits                                                | 54 |

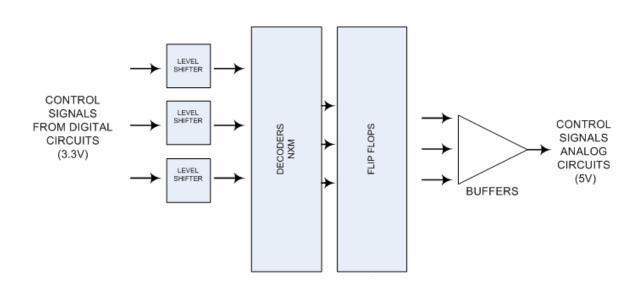

| Figure 3.20: Block diagram of final digital stage.                                              | 55 |

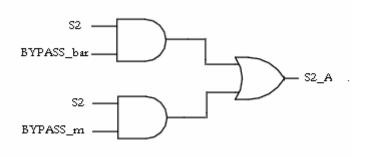

| Figure 3.21: Logic to realize bypass control through S2 switch                                  | 56 |

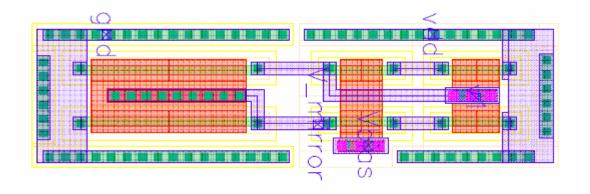

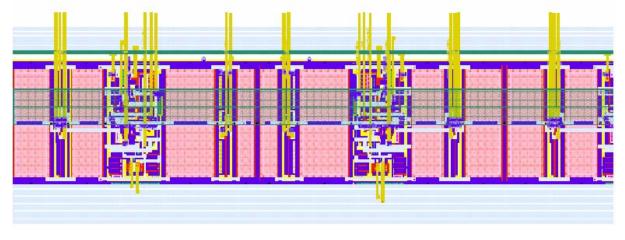

| Figure 3.22: Layout of CMDI unit cell                                                           | 57 |

| Figure 3.23: Layout of Input capacitor set                                                      | 57 |

| Figure 3.24: Part of layout of a channel                                                        | 57 |

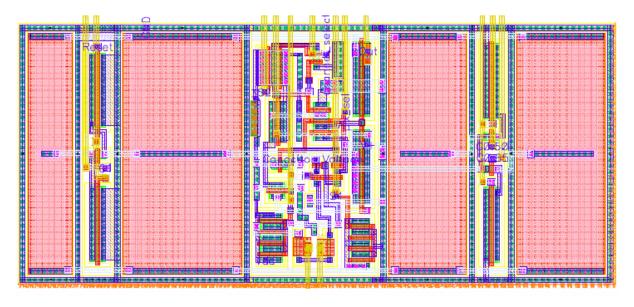

| Figure 3.25: Layout of current sources.                                                         | 58 |

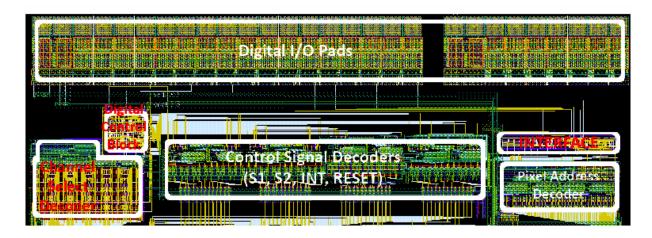

| Figure 3.26: Layout of the complete digital blocks with I/O pads                                | 58 |

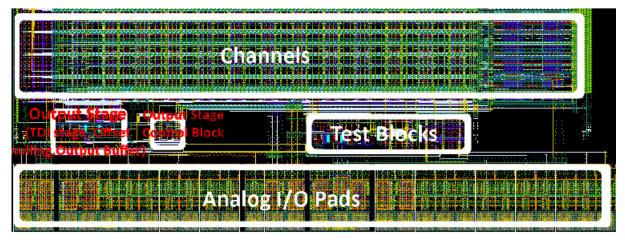

| Figure 3.27: Layout of the output stage with I/O pads                                           | 58 |

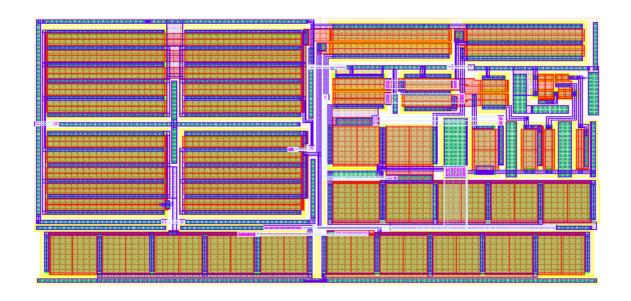

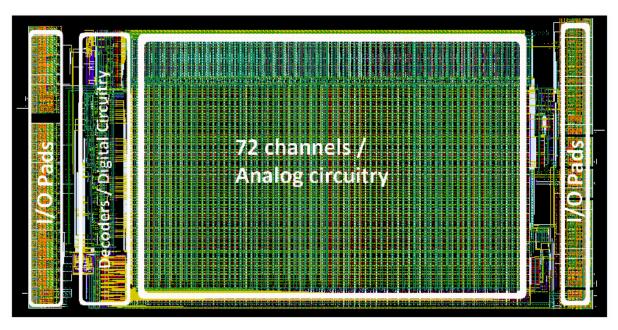

| Figure 3.28: Layout of the 72x4 ROIC, size 5.8mm x 3mm.                                         | 59 |

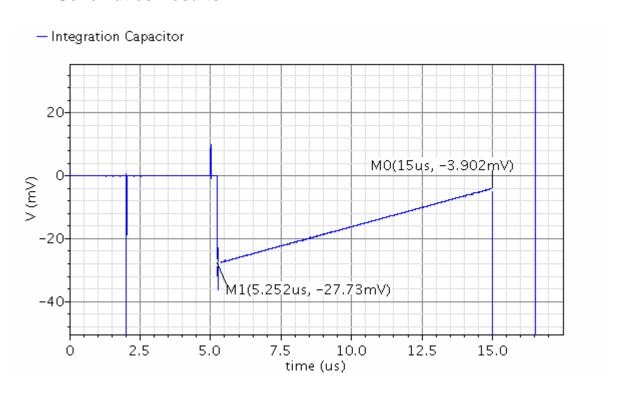

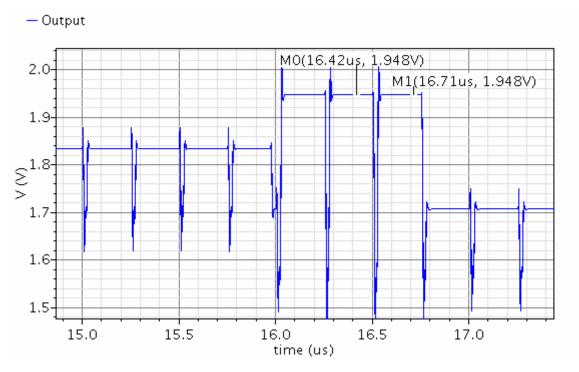

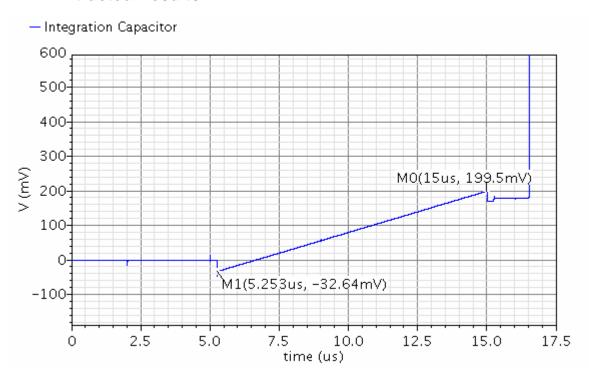

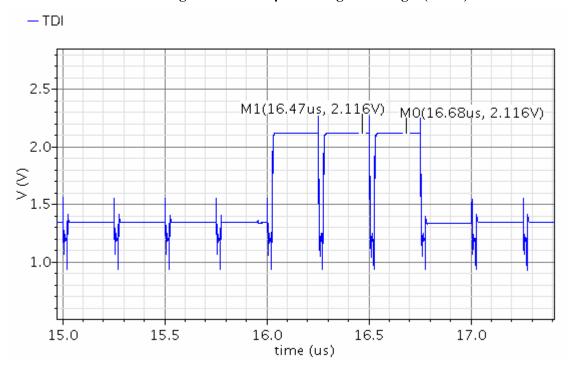

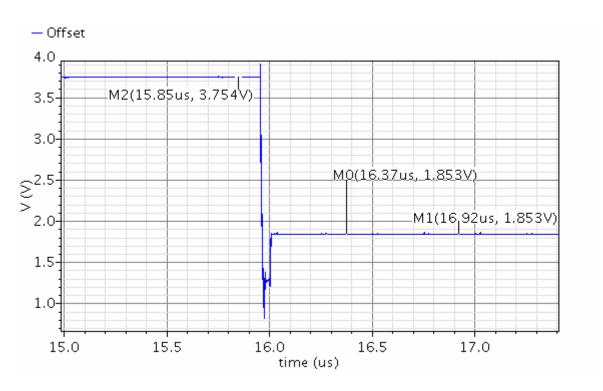

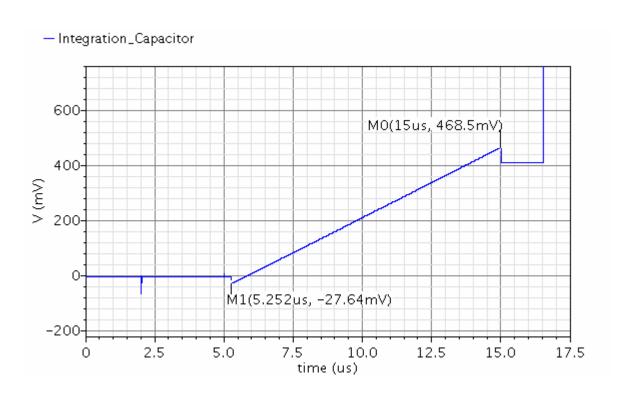

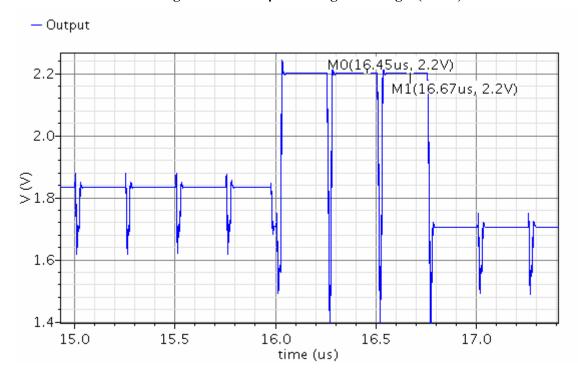

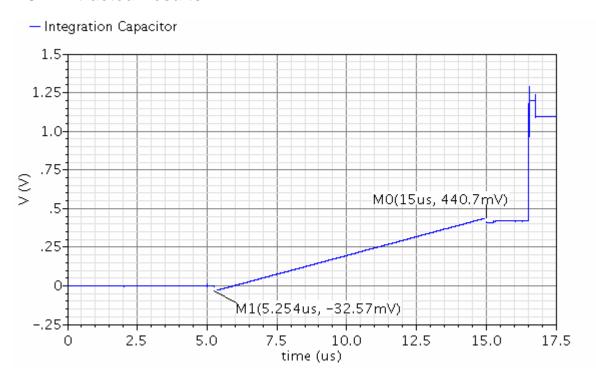

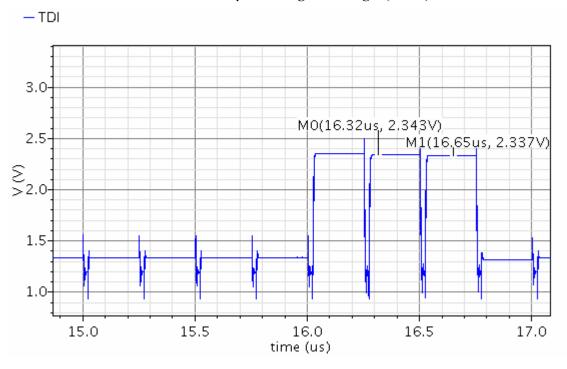

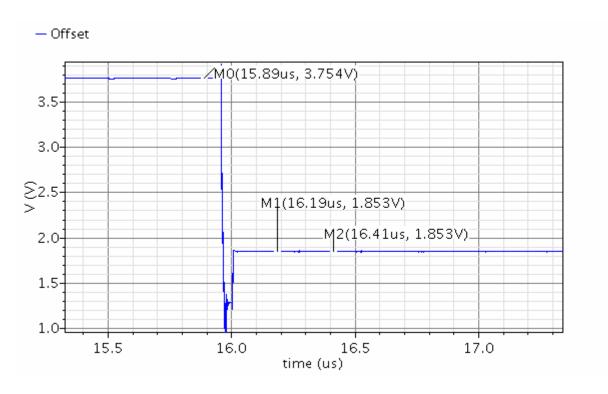

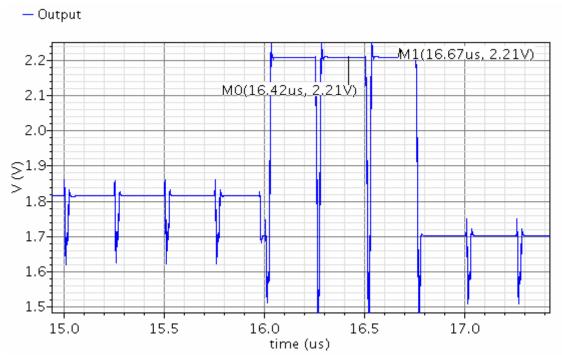

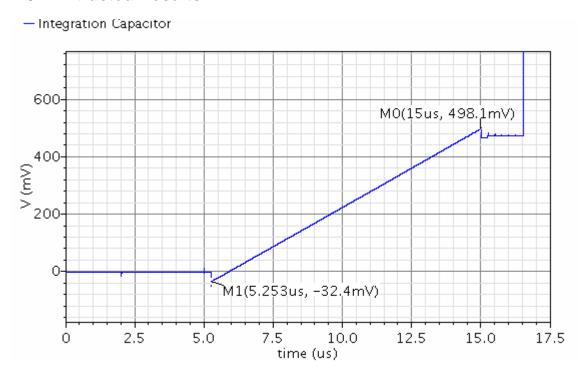

| Figure 4.1: Schematic level simulation result at the input, for input current of 1.2nA          | 60 |

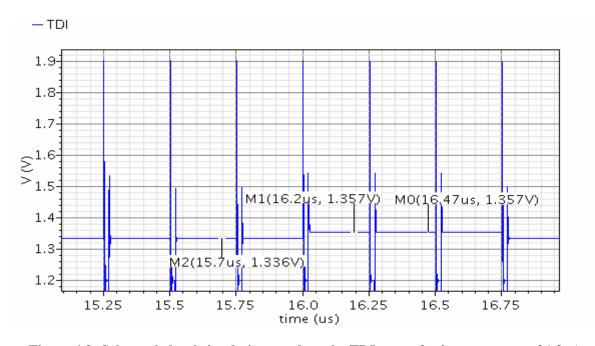

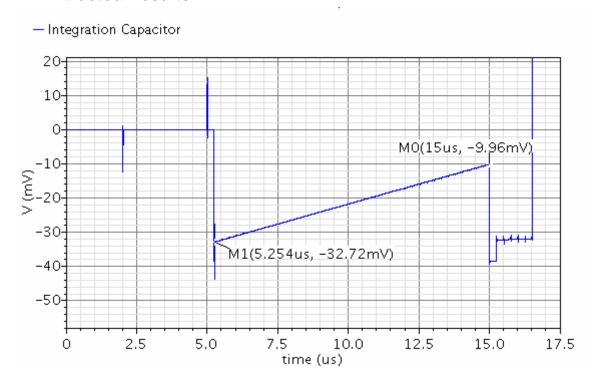

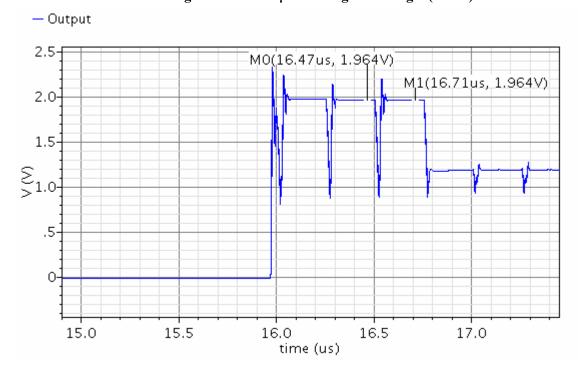

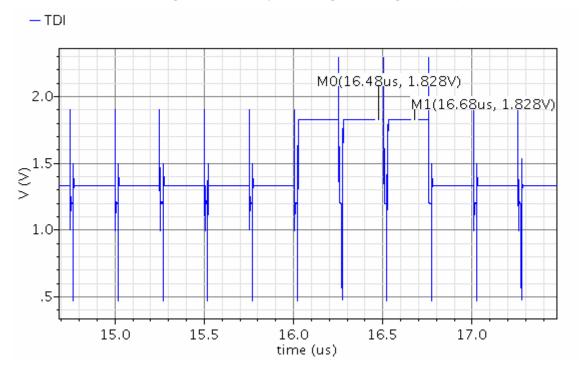

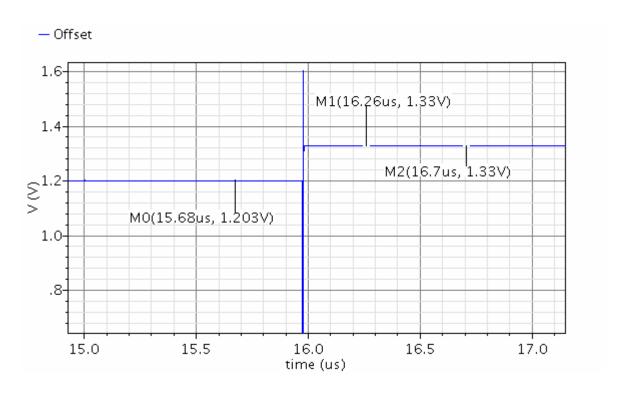

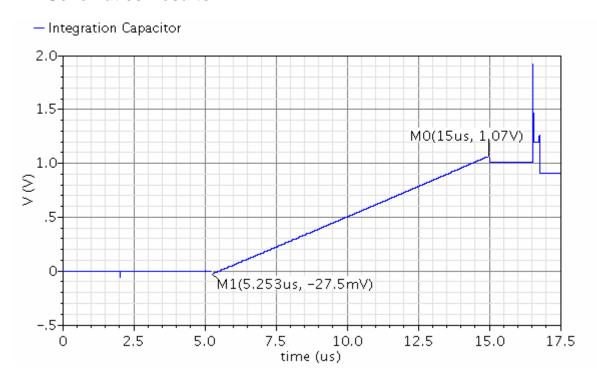

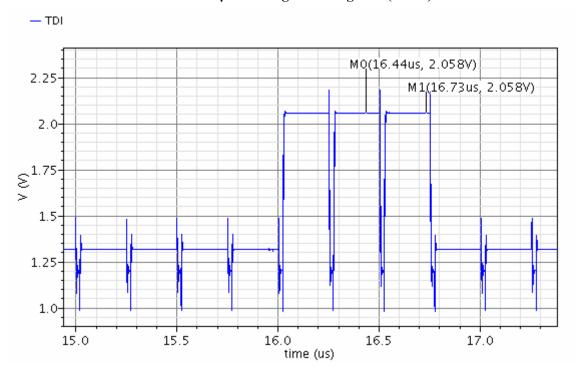

| Figure 4.2: Schematic level simulation result at the TDI stage, for input current of 1.2nA      | 61 |

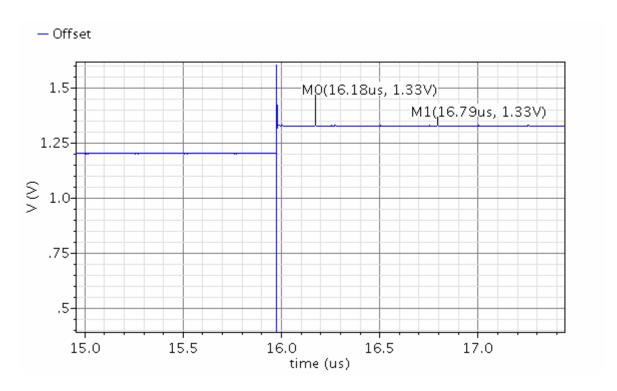

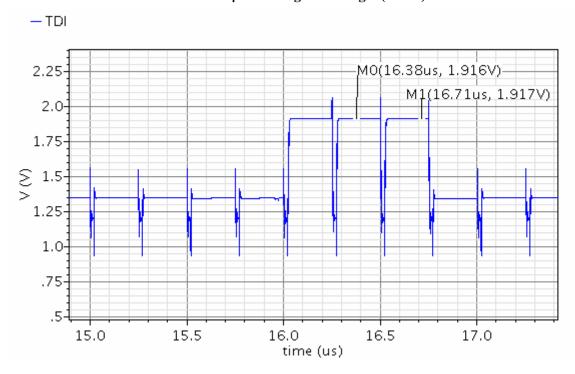

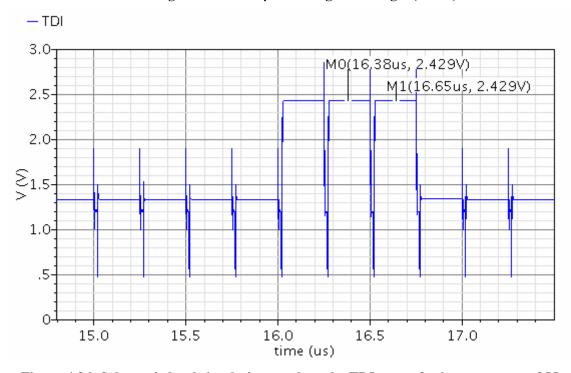

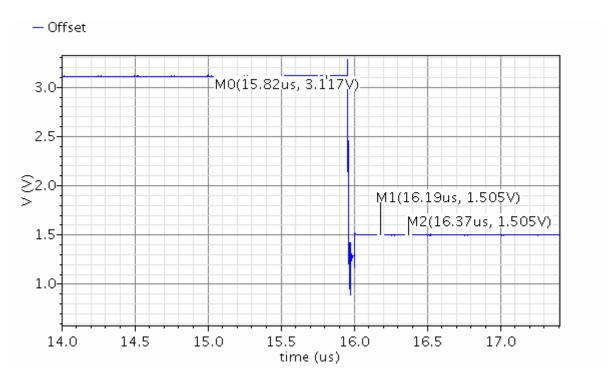

| Figure 4.3: Schematic level simulation result at the offset stage, for input current of 1.2nA   | 61 |

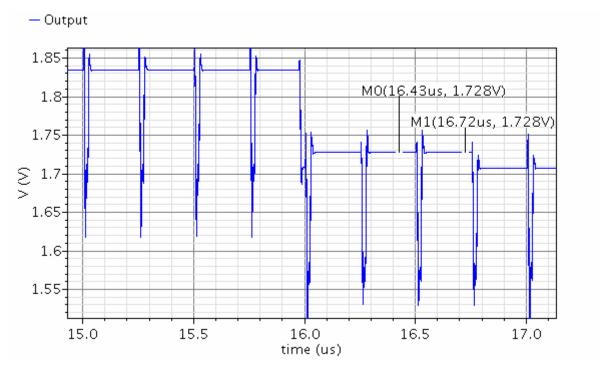

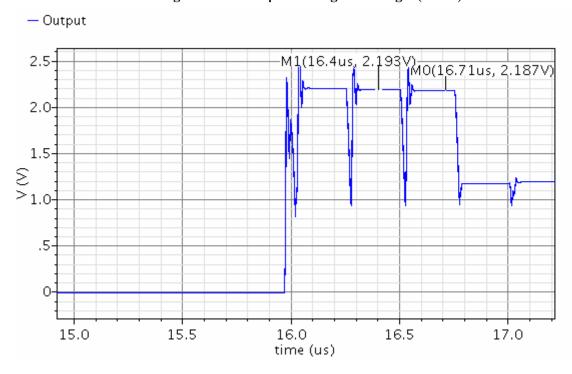

| Figure 4.4: Schematic level simulation result at the output , for input current of 1.2nA        | 62 |

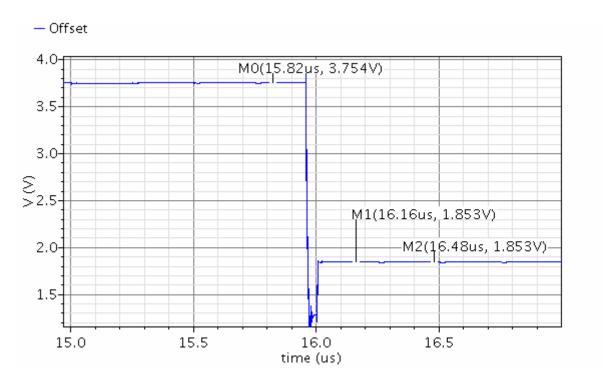

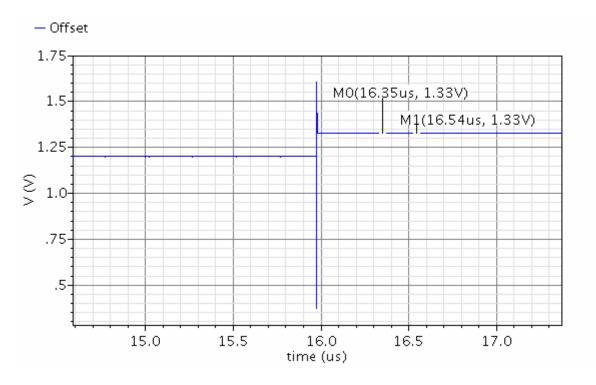

| Figure 4.5: Extracted level simulation result at the input, for input current of 1.2nA          | 62 |

| Figure 4.6: Extracted level simulation result at the TDI stage, for input current of 1.2nA      | 63 |

| Figure 4.7: Extracted level simulation result at the offset stage, for input current of 1.2nA   | 63 |

| Figure 4.8: Extracted level simulation result at the output stage, for input current of 1.2nA   | 64 |

| Figure 4.9: Schematic level simulation result at the input, for input current of 12.3nA         | 65 |

| Figure 4.10: Schematic level simulation result at the TDI stage, for input current of 12.3nA    | 65 |

| Figure 4.11: Schematic level simulation result at the offset stage, for input current of 12.3nA | 66 |

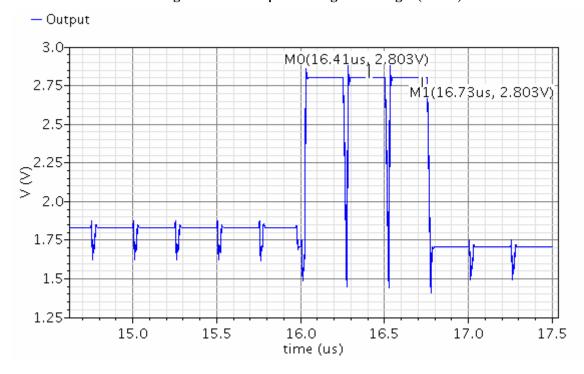

| Figure 4.12: Schematic level simulation result at the output, for input current of 12.3nA       | 66 |

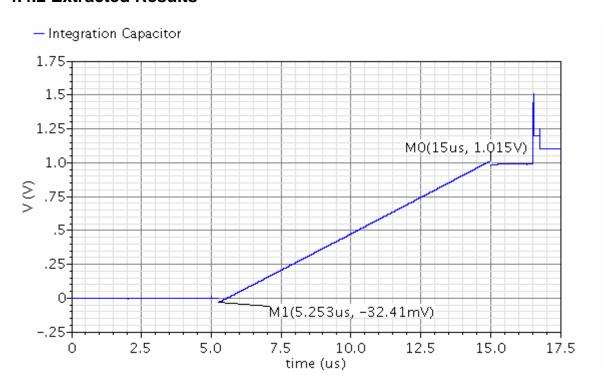

| Figure 4.13: Extracted level simulation result at the input, for input current of 12.3nA        | 67 |

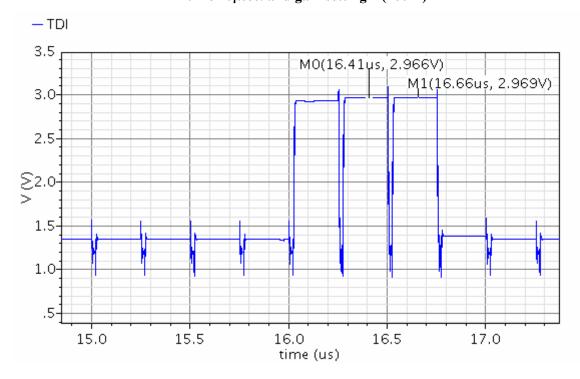

| Figure 4.14: Extracted level simulation result at the TDI stage, for input current of 12.3nA    | 67 |

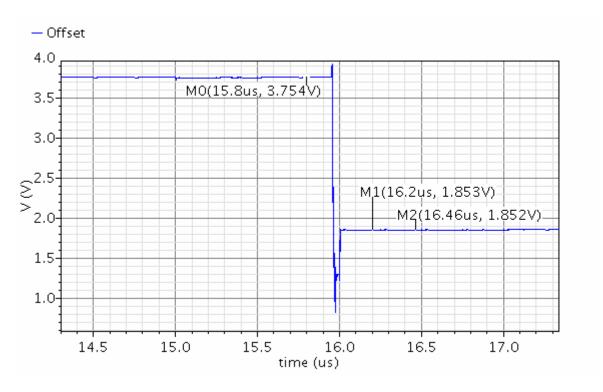

| Figure 4.15: Extracted level simulation result at the offset stage, for input current of 12.3nA | 68 |

| Figure 4.16: Extracted level simulation result at the output stage, for input current of 12.3nA | 68 |

| Figure 4.17: Schematic level simulation result at the input, for input current of 25nA          | 69 |

| Figure 4.18: Schematic level simulation result at the TDI stage, for input current of 25nA      | 69 |

| Figure 4.19: Schematic level simulation result at the offset stage, for input current of 25nA   | 70 |

| Figure 4.20 Schematic level simulation result at the output, for input current of 25nA          | 70 |

| Figure 4.21: Extracted level simulation result at the input, for input current of 25nA          | 71 |

| Figure 4.22: Extracted level simulation result at the TDI stage, for input current of 25nA      | 71 |

| Figure 4.23: Extracted level simulation result at the offset stage, for input current of 25nA | 72 |

|-----------------------------------------------------------------------------------------------|----|

| Figure 4.24: Extracted level simulation result at the output, for input current of 25nA       | 72 |

| Figure 4.25: Schematic level simulation result at the input, for input current of 55nA        | 73 |

| Figure 4.26: Schematic level simulation result at the TDI stage, for input current of 55nA    | 73 |

| Figure 4.27: Schematic level simulation result at the offset stage, for input current of 55nA | 74 |

| Figure 4.28: Schematic level simulation result at the output, for input current of 55nA       | 74 |

| Figure 4.29: Extracted level simulation result at the input, for input current of 55nA        | 75 |

| Figure 4.30: Extracted level simulation result at the TDI stage, for input current of 55nA    | 75 |

| Figure 4.31: Extracted level simulation result at the offset stage, for input current of 55nA | 76 |

| Figure 4.32: Extracted level simulation result at the output, for input current of 55nA       | 76 |

| Figure 4.33: Schematic level simulation result at the input, for input current of 55nA        | 77 |

| Figure 4.34: Schematic level simulation result at the TDI stage, for input current of 55nA    | 77 |

| Figure 4.35: Schematic level simulation result at the offset stage, for input current of 55nA | 78 |

| Figure 4.36: Schematic level simulation result at the output, for input current of 55nA       | 78 |

| Figure 4.37: Extracted level simulation result at the input, for input current of 55nA        | 79 |

| Figure 4.38: Extracted level simulation result at the TDI stage, for input current of 55nA    | 79 |

| Figure 4.39: Extracted level simulation result at the offset stage, for input current of 55nA | 80 |

| Figure 4.40: Extracted level simulation result at the output, for input current of 55nA       | 80 |

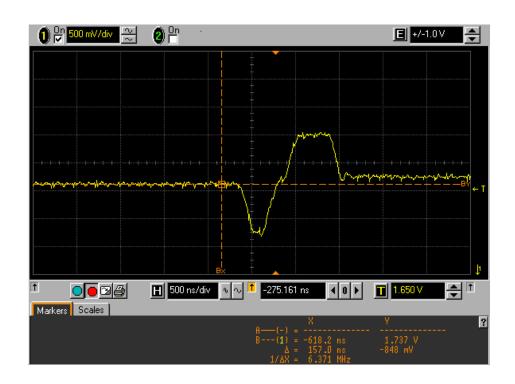

| Figure 4.41: Measurement of 1x4 ROIC with input current 1nA, integration time 32 us           | 83 |

| Figure 4.42: Measurement of 1x4 ROIC with input current 1nA, integration time 16 us           | 84 |

| Figure 4.43: Measurement of 1x4 ROIC with input current 1nA, integration time 8 us            | 84 |

| Figure 4.44: Measurement of 1x4 ROIC with input current 1nA, integration time 4 us            | 85 |

# **List of Tables**

| Table 1.1 Division of infrared radiation [5].                                           | 3                 |

|-----------------------------------------------------------------------------------------|-------------------|

| Table 1.2: Comparison of detectors [4]                                                  | 5                 |

| Table 1.3: Relationship between readout performance parameters and system               |                   |

| requirements [7]                                                                        | 7                 |

| Table 2.1: Comparison of DI, BDI and CMDI preamplifiers [11]                            | 21                |

| Table 2.2: A comparison of preamplifiers in terms of input impedance, detector bias sta | ability, size and |

| input referred noise                                                                    | 25                |

| Table 3.1: performance comparison of designed DI and CMDI unit cells                    | 39                |

| Table 3.2: Gain settings and ratios.                                                    | 40                |

| Table 3.3: Gain settings according to gain bits.                                        | 52                |

| Table 3.4: TDI and test mode settings according to programming bits                     | 52                |

| Table 4.1 Simulation results of 288x4 ROIC.                                             | 81                |

| Table 4.2 Output voltage increase (mV) for integration times 32us and 16us              | 85                |

| Table 4.3: Output voltage increase (mV) for integration times 8us and 4us               | 86                |

# **CHAPTER 1 INTRODUCTION**

#### 1.1 Introduction

Infrared (IR) imaging systems find a variety of applications in civil and military applications such as medical imaging, space and astronomy applications, surveillance, infrared search and track systems, missile guidance and forward looking infrared systems (FLIR). An infrared imaging system in general, is composed of optics, a scanner, a detector and readout electronics that may be enclosed in a cooler, to carry out IR generated signals, and further signal processing blocks as shown in Figure 1.1.

Figure 1.1: General architecture of an infrared imaging system

In applications where high resolution and sensitivity is demanded, large integrated set of detectors are required. Since 1970, research on highly integrated set of detectors and their multiplexers produced infrared focal plane arrays (IRFPA); an array of detectors and its readout electronics. Compared to the conventional discrete infrared detector configurations, IRFPAs has two major advantages: they provide an economical method for high density packaging of detectors and they allow signal processing to take place on the focal plane. Both of these advantages permit design tradeoffs of system parameters such as smaller optical apertures, reduced spectral bandwidths, and faster frame rates [1].

Readout electronics and detectors are in general built on different substrates and are flip chip bonded through indium bumps, in order to select optimum substrate for both, as shown in Figure 1.2 [2]. Usually an off package ADC, is involved before further signal processing. Majority of the detectors used in FPAs are mostly mercury cadmium telluride alloys (HgCdTe or MCT) and readout integrated circuits are charge coupled devices or CMOS circuits, with trend moving towards CMOS ROICs.

Figure 1.2: Representation of FPA, detector array and multiplexer [2]

Focal Plane Arrays (FPA) can be classified according to their substrate and readout circuits being on the same substrates as monolithic and hybrid. Monolithic approach involves some of the signal processing on the detector substrate, however mature applications of this approach are limited to silicon based Schottky-barrier detectors [3]. Hybrid approach, as shown in Figure 1.3 involves that detectors and readout are fabricated on their optimum, different substrates and are than connected together by use of indium bumps with flip chip bonding method or loophole method (also called via-hole method). In both methods, Aside from optimum substrates selection, larger signal processing area can be obtained with the hybrid approach.

In the flip chip bonding method, a planar readout multiplexer is aligned with the detector array; a single contact from every detector to the readout is formed as in Figure 1.3.(a). Contacts can be formed in two ways; either indium bumps are formed on both detectors and readout chip or indium bumps are only formed on readout chip. Finally, connection is achieved by heating or by applying mechanical force. Loophole method differs from flip chip bonding by the detectors being processed after readout chip and detector substrate are connected by a glue as in Figure 1.3.(b). Following detector processing holes are created by ion milling, and indium bumps are inserted for connection with readout array.

Figure 1.3: Hybrid IRFPA with independently optimized detector and readout (a) indium bump technique, (b) loophole technique [4]

IR detectors mainly focus on the spectrum range in terms of wavelength as 3-5  $\mu$ m (mid wave infrared, MWIR) and 8-14  $\mu$ m (long wave infrared LWIR) due to the high atmospheric transmission and maximum emissivity of objects is achieved around 10  $\mu$ m [4]. Detectors are classified in two as their mode of detection, as thermal detectors and photon detectors. Further classification can be done according to the detection schemes; thermal detector types can be given as pyroelectric, bolometers and thermoelectric effect devices; intrinsic, extrinsic and quantum well, Schottky barrier devices, can be listed as photon detector types.

| Region (abbreviation)           | Wavelength range (µm) |  |

|---------------------------------|-----------------------|--|

| Near infrared (NIR)             | 0.78–1                |  |

| Short wavelength IR (SWIR)      | 1–3                   |  |

| Medium wavelength IR (MWIR)     | 3–6                   |  |

| Long wavelength IR (LWIR)       | 6–15                  |  |

| Very long wavelength IR (VLWIR) | 15–1000               |  |

**Table 1.1: Division of infrared radiation [5]**

Thermal detectors rely on the change of device temperature under IR illumination. Change in device temperature causes device's physical or electrical properties to change, forming the

detection mechanism. In theory, these devices are not wavelength selective; rather they depend on the power of the radiation. Thermal detectors operate at room temperature and easy to make and cheap however, they have average sensitivity and slow response times due to the time required for heating of the device [3].

Photon detectors are semiconductor devices that create an output signal in response to the change of electric energy distribution in case of a radiation contact with an electron at the device [3]. These devices operate wavelength selective, has very good sensitivity (high signal to noise ratio) and has very fast response times. However these advantages come with a cost of cryogenic cooling requirement, mostly down to 77K, in order to prevent thermal generation of charges in the device. Uncooled detectors are quite noisy, and the cooling requirement makes the use of photon detectors expensive.

A comparison of IR detector types, both thermal and photon, is represented in [3] and also shown in Table 1.2. For infrared detection, the most suitable and preferred photon detector material is HgCdTe, even its disadvantages of harsh processing issues as its toxiticity and high vapor pressure at melting point [4]. However certain advantages of HgCdTe detectors make their use inevitable as the primary material for photon detectors. First by properly selecting the amount of CdTe and HgTe, spectral response of detector can be set to a range of 1-25 µm. HgCdTe detectors, are direct bandgap materials and being relatively thin, can absorb high amount of energy. A thin substrate generates lower noise. Finally lattice matched substrates for epitaxial growth is available for HgCdTe detectors for total range of IR spectral range, posing a major advantage over other detector materials [3] [4].

| Detector |                                                |                                        | Advantages                                                                          | Disadvantages                                                                                 |

|----------|------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Thermal  | Thermal (thermopile, bolometers, pyroelectric) | ters, pyroelectric)                    | Light, rugged, reliable, and low cost<br>Room temperature operation                 | Low detectivity at high frequency<br>Slow response (ms order)                                 |

| Photon   | Intrinsic                                      | IV-VI (PbS, PbSc, PbSnTe)              | Easier to prepare<br>More stable materials                                          | Very high thermal expansion coefficient<br>Large permittivity                                 |

|          |                                                | II-VI (HgCdTe)                         | Easy bandgap tailoring<br>Well developed theory & exp.<br>Multicolour detectors     | Non-uniformity over large area<br>High cost in growth and processing<br>Surface instability   |

|          |                                                | III-V (InGaAs, InAs, InSb, InAsSb)     | Good material & dopants<br>Advanced technology<br>Possible monolithic integration   | Heteroepitaxy with large lattice mismatch<br>Long wavelength cutoff limited to 7 µm (at 77 K) |

|          | Extrinsic (Si:Ga, S                            | Extrinsic (Si:Ga, Si:As, Ge:Cu, Ge:Hg) | Very long wavelength operation<br>Relatively simple technology                      | High thermal generation<br>Extremely low temperature operation                                |

|          | Free carriers (PtSi, Pt <sub>2</sub> Si, IrSi) | , Pł <sub>2</sub> Si, IrSi)            | Low-cost, high yields<br>Large & close packed 2-D arrays                            | Low quantum efficiency<br>Low temperature operation                                           |

|          | Quantum wells                                  | Type I (GaAs/AlGaAs, InGaAs/AlGaAs)    | Matured material growth<br>Good uniformity over large area<br>Multicolour detectors | High thermal generation<br>Complicated design and growth                                      |

|          |                                                | Type II (InAs/InGaSb, InAs/InAsSb)     | Low Auger recombination rate<br>Easy wavelength control                             | Complicated design and growth<br>Sensitive to the interfaces                                  |

|          | Quantum dots                                   | InAs/GaAs, InGaAs/InGaP, Ge/Si         | Normal incidence of light<br>Low thermal generation                                 | Complicated design and growth                                                                 |

**Table 1.2: Comparison of detectors [4]**

Photovoltaic and photoconductive HgCdTe detectors are available and applied successfully to ROICs. Photovoltaic (PV) detectors are basically pn junction devices, producing current of an incident photon with energy higher than the band gap of the junction. In most ROICs in order to benefit from the large shunt impedance, and reduce power consumption, PV detectors are operated at almost zero bias. Photovoltaic detector process is a challenging, but due low power advantage, is a quite attractive one. Today, IRFPAs are dominated by photovoltaic detectors, most of which are HgCdTe alloys.

Photoconductive (PC) detectors are semiconductor devices with a detection mechanism of changing conductance under IR illumination. In case of an incident photon, either an electrohole pair is generated (intrinsic semiconductor) or majority carriers are activated (extrinsic semiconductors) [6]. PC detectors are operated through a constant bias thus; power consumption is a problem, compared to PV detectors, making PC detectors not favorable for large array applications.

Figure 1.4: Generic staring type ROIC. ROIC includes amplification and signal processing. [7]

ROICs are sensor interface blocks where photocurrent to immediate voltage conversion on an integration capacitor for a certain integration time is held. In Figure 1.4, a generic view of ROICs is represented. Detectors are connected to the ROIC by indium bumps with flip chip bonding method. For every single element in FPA there is a unit cell preamplifier. Unit cell

can be direct injection, buffered direct injection, current mirroring direct injection, or any other topology, selected according to the detector's shunt impedance, noise, linearity, and power consumption requirements of the readout circuit. A transimpedance amplifier may be required according to signal processing used. Finally, a video amplifier or output buffer is employed. Additionally, ROICs can have on chip analog to digital converters (ADC) and on chip clock generators.

Most important parameter of an ROIC is the signal to noise ratio. Most ROICs have input referred noise levels less than the detector itself. Largest possible dynamic range is desired in order to maximize the saturation level of the signal. Since photon detectors operate at cryogenic temperature, power consumption of the circuit should be minimized in order to reduce cooling requirements. A careful input preamplifier selection must be made according to the detector properties (shunt impedance, capacitance) as well as aimed radiation conditions of the detector array (flux level), since input preamplifier sets linearity and efficiency of ROIC along with dynamic range. These requirements are discussed in [7] as shown in Table 1.3.

| Major Boodout Boufour                   | Poloted Custom Bouserester                             |                                                                          |

|-----------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------|

| Major Readout Performance<br>Parameters | Related System Parameter<br>or Interface Impact        | Comments                                                                 |

| NEC (noise equivalent charge)           | Sensitivity                                            | Minimized to enhance SNR                                                 |

| Power dissipation                       | Cooldown time<br>Life<br>Weight                        | Limited cryogen/cooler life<br>Cryogen weight/cooler size                |

| Dynamic range                           | Maximum saturation signal                              | Loss of signal                                                           |

| Crosstalk                               | System MTF (resolution) Blooming of saturated elements | Element to element                                                       |

| Frequency response                      | System MTF (resolution)<br>Latent images               | Often related to crosstalk                                               |

| Input impedance                         | Signal linearity<br>Noise                              | Detector bias changes with<br>signal<br>Loss of optimum detector<br>bias |

| Linearity reliability                   | Calibration<br>Instrument life                         | Proper identification<br>Confidence of success                           |

| Gain                                    | Sensitivity                                            | Signal amplified above<br>system noise floor                             |

| Output video driver impedance           | Sensitivity<br>MTF                                     | EMI from environment<br>crosstalk between<br>multiplexed elements        |

Table 1.3: Relationship between readout performance parameters and system requirements [7]

Circuit architecture of ROICs also depends on the type of FPA. FPAs can be staring or scanning type. Scanning arrays are first generation FPAs incorporating a single column of

detectors. Four or seven columns of detectors are also developed with time delay integration functionality. The bottle neck of developing huge number of functioning devices led to the first generation FPAs to be linear, scanning type arrays. In scanning type arrays, only a single column of image is produced at a single frame. An optic scanner scans the scene continuously to create a full image output. ROICs for scanning type arrays operate at lower frame rates and lower spatial resolution; super sampling is incorporated for increasing the spatial resolution.

The second generation of FPAs is the staring arrays incorporating thousands of elements up to 2048x2048. Having higher number of elements, these FPAs have much higher field of view than scanning ones. These arrays operate at higher frame rates and have better spatial resolution. Also as in [8], trend is to operate FPA at higher temperature as 110K, for a better performance.

Finally it is important to mention the process technologies ROICs are built. First IRFPA readouts were made by CCD technology. Until that, only way to create a sensitive, high resolution system is through configuring a large set of detectors with each detector being connected to a single wire (and probably an individual preamplifier). Also these detectors and readout elements are all required to be packaged in a small dewar [1]. This would be a difficult task with dewar being quite large, as well as harsh cooling requirements, due to higher power consumption.

Although CCD technology enabled high integration, IRFPAs benefited from the mature CMOS technology. Advantages of CMOS IRFPAs are based on versatility and compactness. CMOS based readouts can cover operating ranges down to 10 Kelvin. High performance low noise amplifiers are available through CMOS technology. Finally, through low voltage operation compared to CCD technology, CMOS technology has proven very successful for designing readout integrated circuits.

#### 1.2 Motivation

As mentioned in the previous section, first generation of IR imaging systems incorporated single detector, or a limited number of detectors. High frame rate and resolution requirements brought up the scanning type of FPAs where a scene is scanned constantly to create a 2D image by a single array of detectors. Staring arrays allow high frame rates and better resolution. However staring arrays are expensive and it is hard to integrate large set of detectors. Hence scanning type arrays are attractive choices due to the above mentioned

advantages. It is easier to build scanning arrays due less number of elements being incorporated. Scanning arrays are also cheap with all advantages of integrated array technology.

In this thesis, design of a CMOS readout integrated circuit for a scanning array of 288x4 elements of n-on-p type HgCdTe detectors for long wave infrared spectrum is represented. Designed readout ROIC structure includes four elements time delay integration (TDI) functioning with a super sampling rate of 3, bidirectional TDI scanning, dead pixel deselection, automatic gain adjustment in response to pixel deselection, besides programmable four gain settings (up to 2.58pC storage), and programmable integration time. ROIC has four outputs with a dynamic range of 2.8V (from 1.7V to 4.5V) and input referred noise of 2989 electrons for an area of 13mm<sup>2</sup>. Organization of the thesis is given in the next section.

# 1.3 Organization of Thesis

In Chapter 2, scanning type ROIC building blocks are discussed. First, most of the preamplifiers already discussed in the literature, are explained and compared in terms of their injection efficiency, linearity, input referred noise level and power consumption. Specific applications of each preamplifier are discussed. Next a noise reduction technique, widely known and applied to scanning type of ROICs, time delay integration (TDI) is announced. Application of TDI with super sampling rate of three on four detectors is shown. Possible implementation methods are also addressed and compared in terms of trade offs between area and power consumption. In the last section of the chapter additional ROIC features such as pixel deselecting in case of a malfunctioning detector, automatic gain adjustments and test mode operations are explained.

In Chapter 3, implementation of individual blocks discussed in Chapter 2 is explained. First requirements for the specific ROIC 288x4 HgCdTe array are given as well as the detector properties. Next, input preamplifier selection as current mirroring integration is introduced. Implementation of preamplifier together with input capacitor selection and variable gain application is discussed. In the next section, implementation of the TDI according to the chosen topology is shown. Implementation of TDI amplifier is represented as well. Due to TDI implementation some offset is added to the output. Following section illustrates implementation of an offset cancellation block, which also reduces charge injection and clock

feedthrough effects. Output buffer is also defined. Finally control block design to operate the ROIC, as well as required user interface is explained.

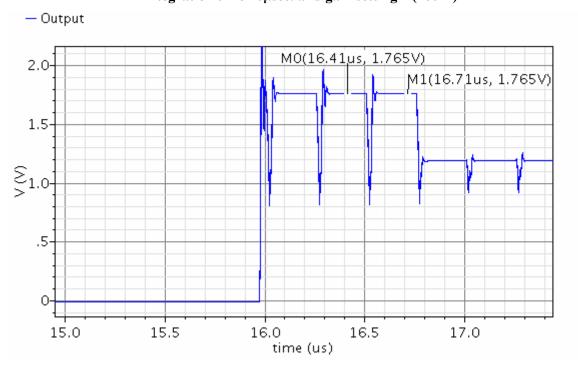

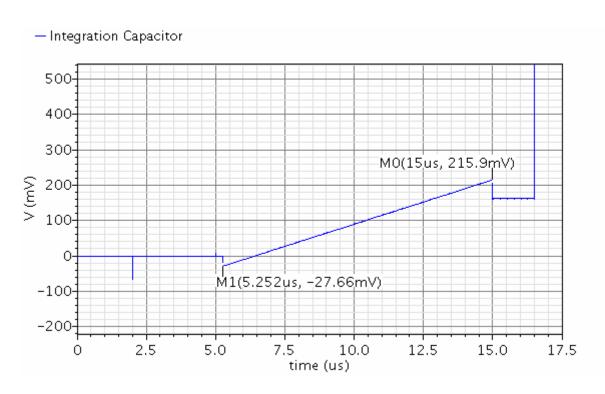

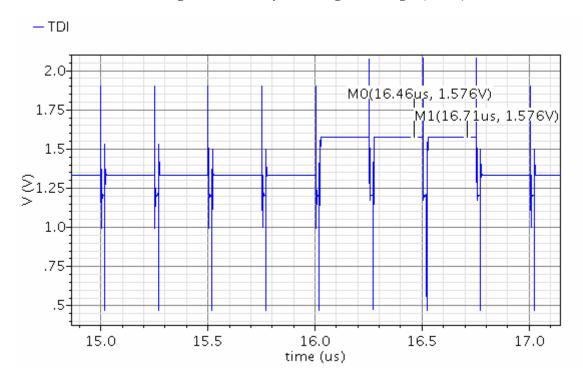

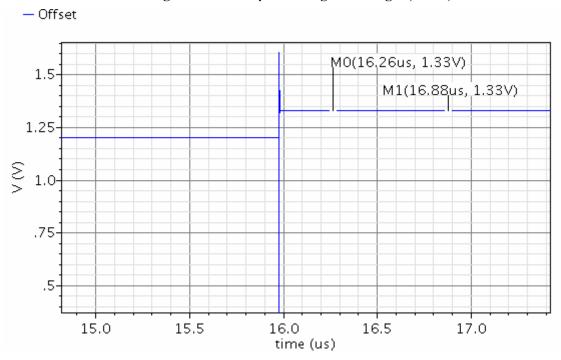

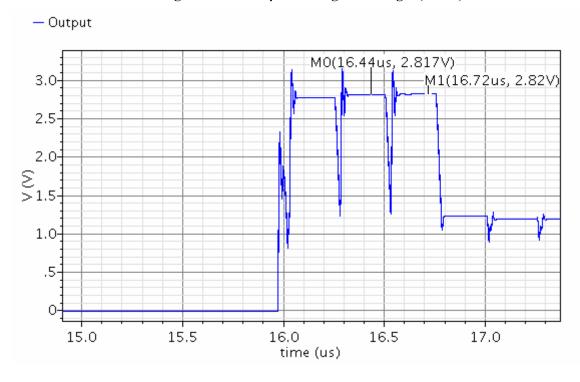

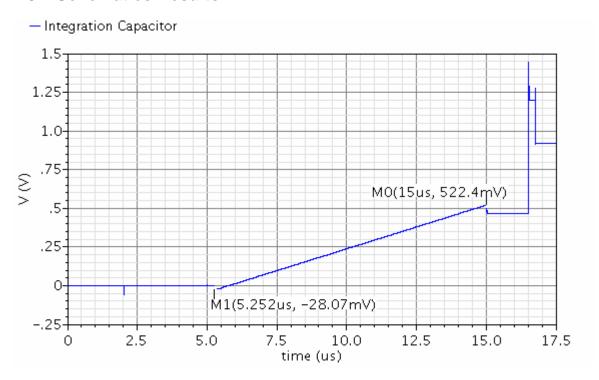

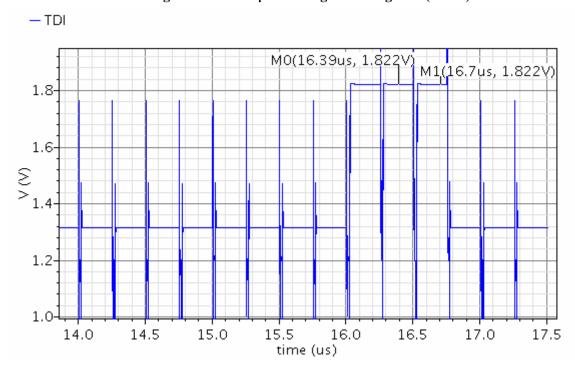

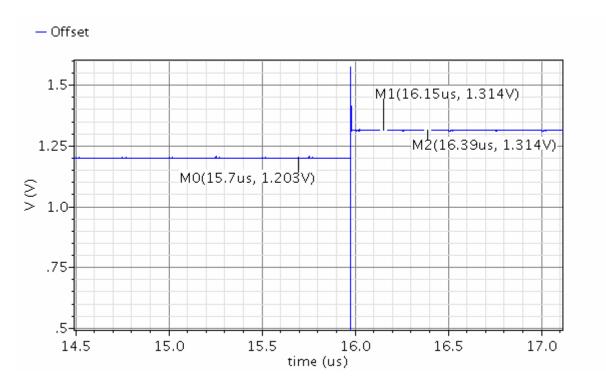

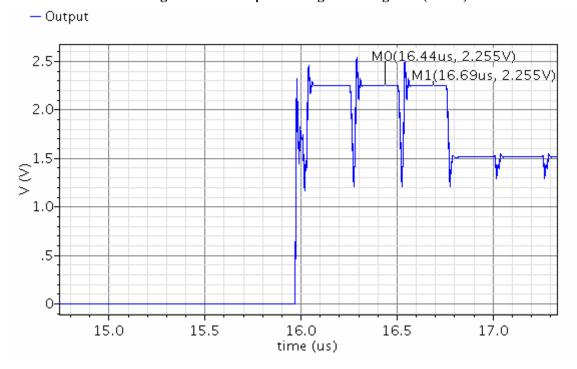

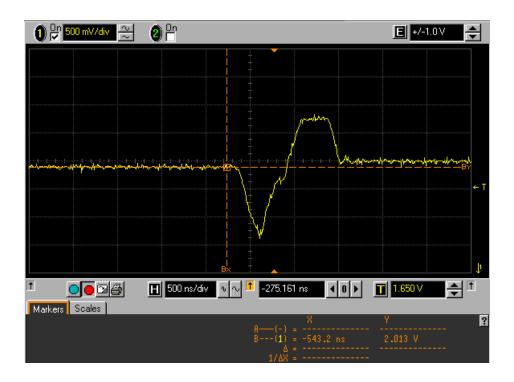

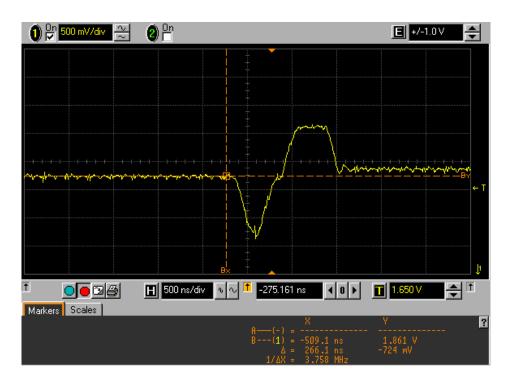

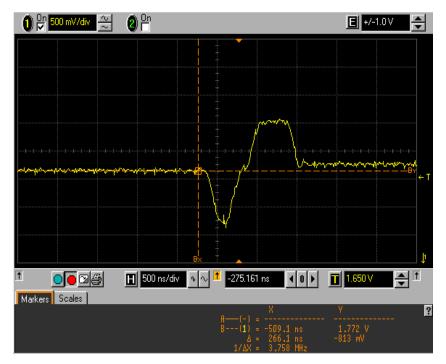

Chapter four includes simulation and experimental results. First, measurement results from a 1x4 ROIC is given. Then simulation results of 288x4 ROIC are represented by a 72x4 sub block. Results are shown for minimum, nominal and maximum input current levels for voltage levels at the integration capacitors, at the TDI amplifier output, at the output of offset cancellation stage and at the output buffer.

Finally, in chapter five, conclusions of this study are provided, problems are addressed and future study is discussed.

# CHAPTER 2 LINEAR ROIC BUILDING BLOCKS

#### 2.1 Introduction

All ROICs, scanning or staring type, involves use of a preamplifier, also named the unit cell as the immediate interface circuit. As in all sensor readouts, most of the performance parameters are strictly dependent on this input preamplifier, especially; input referred noise, injection efficiency, dynamic range and linearity are key performance parameters of ROIC are set through unit cell.

Second, all linear ROICs employ signal processing such as correlated double sampling or time delay integration. Correlated double sampling (CDS), is used in sample and hold circuits in order to store an amplifier noise, and subtract it from another set of results. Time delay integration (TDI) is another method used to increase signal to noise ratio (SNR) through creating an output by adding multiple measurements from a set o detectors.

Most linear ROICs apply super sampling with TDI, to effectively increase spatial resolution of the image, without increasing the number of elements on the FPA. Super sampling is realized by setting certain scanning steps for a single detector on a row. For example an image is passed through a detector with three steps, results with three data from a single detector, hence a super sampling rate of three.

ROICs employ additional functionalities such as dead pixel deselection, automatic gain adjustment or bypass (test) mode. These functionalities are correlated. By test mode malfunctioning detectors are determined. ROIC is then programmed according to data obtained. During read phase, in case of one or more defected detectors, gain is adjusted so that the effect is not observed at the output.

In this section above mentioned building blocks and signal processing methods are discussed in detail with possible circuit or implementation types. Focus is given to set the key parameters, advantages and disadvantages of each circuit or method and application types each circuit or method is applicable.

# 2.2 Preamplifiers

Initial conversion from photocurrent to voltage takes place at the preamplifier (unit cell) and. further processing of signal is held in voltage domain. In order this conversion to be accurate, stringent requirements are met by different types of preamplifiers.

First, preamplifiers should have low noise, but in return should not loose the advantage of having low input impedance (hence high injection efficiency) or linearity, which is not the case most of the types. Also these cells must be operable at very low current levels, such as 1nA, in cryogenic temperatures most of the time, due to the cooling requirement of the FPAs. Moreover, since they are the most repeated building block (every detector has one dedicated unit cell) preamplifiers should consume minimal power. Finally, most ROIC incorporates unit cells just under the detector itself; in this case, preamplifiers must fit in area determined by the size of the detector.

There are various different types of preamplifiers in the literature. Most common ones are discussed in this section. In the end, advantages and disadvantages of each topology is given.

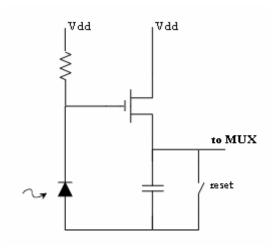

# 2.2.1 Self Integration Preamplifier

Among all ROIC preamplifiers self integration (SI) is the unit cell with the least number of components and has an advantage of being implemented in the minimum area. However SI unit cell is subject to limited dynamic range and causes nonlinearity as the detector bias is varied with the stored charge on the integration capacitor.

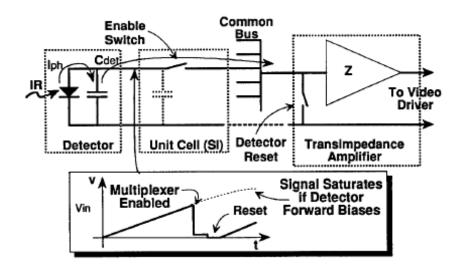

The operation of SI unit cell is simple, for a certain IR radiation, photocurrent is accumulated on the stray capacitance as well as parasitics from the line to the multiplexer bus. Additional capacitance to widen the dynamic range is also applicable [7]. For a given frame time integration is done over the stray capacitances and then the multiplexer connects the detector to the transimpedance amplifier where conversion from charge to voltage domain takes place. Depending on the transimpedence amplifier used a reset bus may be required to reset the detector (integrated) voltage to its initial value. The operation type discussed is represented in the following Figure 2.1.

Figure 2.1: Self integrator readout [7]

As seen from the integrated voltage curve, there are two important issues to mention in terms of linearity and dynamic range of SI type preamplifiers. First the voltage over the PV diode is evaluated as:

$$Vout = Z \int I_{ph} x dt + ZQr, \qquad (2.1)$$

with Z, being the charge to voltage gain of the preamplifier, I<sub>ph</sub> is the photocurrent and Qr being the initial charge remained following the reset operation of the PV detector [7]. As the voltage increases the dark current associated with the detector will change resulting nonlinearity for different radiation levels. Further increase of the integrated voltage will forward bias the PV detector limiting the voltage level to the PV detectors on voltage. Hence, the dynamic range of SI is limited to the flat back bias signal excursion of the detector [7].

Finally, in terms of noise contribution, SI unit cell suffers from kTC noise as all switched capacitor circuits as well as detector thermal noise and photon noise. The column multiplexer is also a major contributor to the noise generated although it is outside the unit cell [7]. However, SI is along with direct injection unit cell, is the lowest noise contributing preamplifier. Aside this advantage, its limited dynamic range and nonlinearity limits its applications.

# 2.2.2 Source Follower per Detector Preamplifier

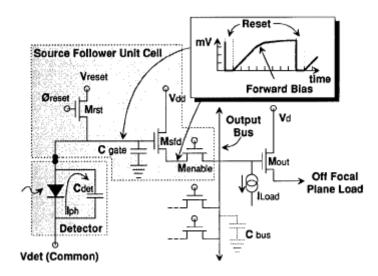

The source follower per detector (SFD) preamplifier is similar to the SI preamplifier, aside from having a source follower instead of the transimpedance amplifier. SFD unit cell is subject to limited dynamic range and causes nonlinearity with the detector bias varied with the stored charge on the integration capacitor. However, with the reset bus, the detector bias can be initialized better than the SI unit cell. The SFD is typically utilized in low background applications where long integration times accumulate sufficient charge for readout.

The unit cell is again simple with having only three transistors, one to reset the detector voltage and two as the source follower amplifier, as in Figure 2.2.

Figure 2.2: Source follower per detector readout [7]

As in the SI unit cell, the stray capacitance of the detector and the routing capacitances in addition to the gate capacitance of the source follower, form the integration capacitance. Since voltage conversion is handled by the source follower no additional bus amplifiers are required. Following the read operation, the detector is reinitialized by the reset switch and integration begins again.

The noise sources of the SFD are again kTC, MOSFET 1/f noise and MOSFET thermal noise. SFD having moderate noise has limited dynamic range and poor linearity at high background fluxes.

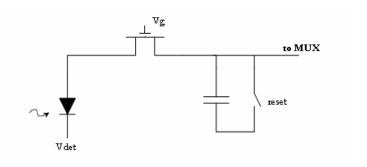

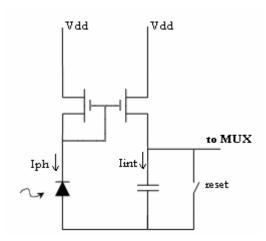

#### 2.2.3 Direct Injection

Following the SI unit cell, direct injection preamplifier (DI) is the smallest unit cell which can also achieve very good results for IR imaging with PV type detectors, especially for SWIR and MWIR with high irradiance applications. Formed of only a single transistor, DI has very low noise. Compared to SI and SFD preamplifiers, it results with quite better detector bias

stability. Also gain is not dependent on detector capacitance and parasitic capacitances. Using an integrated capacitor, ROICs with DI preamplifier can achieve variable gains. However, for low background applications the injection efficiency drops significantly, resulting in a poor SNR. Use of DI circuits for low impedance detectors, especially LWIR PV detectors, is also limited due to the decrease in the injection efficiency.

The working principle of DI is simple. As in the Figure 2.3, the source of a MOSFET, controlling the integration of the photocurrent to the integration capacitor, follows the reverse biased PV detector. The injected charge is accumulated at the integration capacitor where the immediate change to charge to voltage domain takes place. Then the stored charge can be read through the use of a multiplexer to the output. Following the read of the integrated voltage, a reset switch initializes the integration capacitor for the following frame.

Figure 2.3: Direct injection preamplifier

In DI preamplifier, the detector bias is obtained by a stable voltage source ( $V_{det}$ ) and the source of the MOSFET which is, ignoring the low overdrive voltage, the gate voltage plus the threshold voltage of the device. However this would not create a constant bias for all the PV detectors in the FPA since not all detectors are radiated by the same flux. Hence not driven by the same current source, the source voltages of the integration MOSFETs will differ over the FPA. This variation can be on the order of 10 - 50 mV and can result higher 1/f noise and dark current values, decreasing the SNR and linearity [7].

Another issue about the DI unit cell arises in terms of its injection efficiency. Injection efficiency is defined as the ratio of the integrated photon current  $I_{int}$  to the generated photocurrent  $I_{ph}$  is

$$Injection\_efficiency = \frac{I_{int}}{I_{ph}} = \frac{r_{det}g_m}{1 + r_{det}g_m}$$

(2.2)

Where  $r_{det}$  is the detector impedance and  $g_m$  is the transconductance of the MOSFET. For low flux applications  $g_m$  is strongly dependent to the photocurrent since the MOSFET will be in weak inversion (sub threshold region). MOSFET will then operate with the equation as stated in [9]

$$I_d = \frac{W}{L} \mu_{\rm n} C_{ox} \exp(V_g - \frac{mkT}{q})$$

(2.3)

Then, g<sub>m</sub> will be:

$$g_m = \frac{I_d q}{mkT} \tag{2.4}$$

G<sub>m</sub> is independent of the device geometry parameters and dependent to the photocurrent. This results with DI being a poor choice for the low flux or low detector impedance applications reducing the linearity of ROICs significantly due to poor injection efficiency.

The noise sources for DI are again kTC, MOSFET 1/f and thermal noises. However with MOSFET noise contribution in terms of current being as given in [7]

$$i_0 \approx \frac{e_n g_m}{1 + r_{\text{det}} g_m} = injection\_efficiency \frac{e_n}{r_{\text{det}}},$$

(2.5)

where  $i_0$  is the noise current integrated to the capacitor and  $e_n$  is the input referred rms noise voltage of the MOSFET device, MOSFET noise becomes insignificant.

In brief, DI is a small, low noise, compact preamplifier creating a relatively good detector bias stability compared to SI and SDF. However its applications lack to cover low flux applications and LWIR PV detector type ROICs where the detector impedances are small.

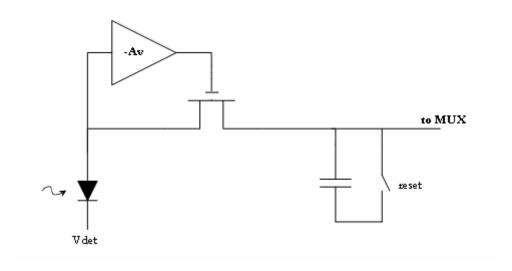

# 2.2.4 Buffered Direct Injection

Buffered direct injection (BDI) lowers the input impedance of the preamplifier by using a feed forward amplifier. It has all the advantages similar to DI, with lower input impedance. However its drawback is the use of amplifier which is hard to build in small pixel area, and consumes power which heats the ROIC which is a problem increasing noise and complicating the cooling process.

BDI is represented in Figure 2.4. Its operation is same as in DI. As in the figure the source of a MOSFET, controlling the integration of the photocurrent to the integration capacitor follows the reverse biased PV detector. Then the stored charge can be read through the use of a multiplexer to the output. Following the read of the integrated voltage, a reset switch initializes the integration capacitor for the following frame.

Figure 2.4: Buffered direct injection preamplifier

The feed forward amplifier provides an increase of  $g_m$  by a factor of  $1+A_v$ ; hence the input impedance of the unit cell is reduced by a factor of  $1+A_v$ .

In addition to the noise sources of kTC, MOSFET 1/f, thermal noises, input noise of the inverting amplifier will be an additional noise source, representing the linearity vs. noise tradeoff.

BDI is a unit cell with all the advantages of DI with lower input impedance. However the amplifier will cause additional noise and increase power consumption. Also it is important to mention that it is a difficult task to get high gain and low noise, low power amplifier in a small area.

## 2.2.5 Capacitive Feedback Transimpedance Amplifier

The Capacitor feedback transimpedance amplifier (CTIA) unit cell is a reset integrator and addresses a broad range of detector interfaces for many applications [10]. It is mostly employed in ROICs with correlated double sampling, with having 3 transistors and a feedback capacitor.

The CTIA preamplifier in figure functions as follows. The photocurrent increases the voltage at the negative input of the amplifier. This change in the input reduces the output voltage, which in return pulls the photocurrent to the feedback capacitor. Hence a decreasing ramp at the output is observed. Following the read operation the feedback capacitor is initialized through the reset switch.

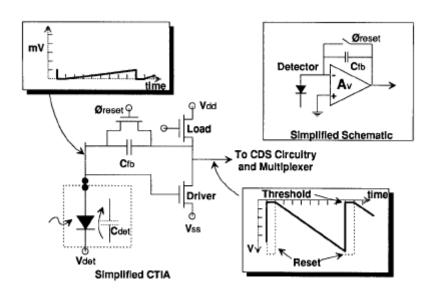

Figure 2.5: Capacitive feedback transimpedance preamplifier. Only a small change at the input is observed for a high change at the output [7]

CTIA as seen in the above graphs has little voltage variation at its input compared to the ramp at the output; hence it has good detector voltage bias stability. However its noise is affected by the amplifier input transistors, introducing its drawback.

## 2.2.6 Resistor Gate Modulation

Resistor gate modulation input cell is the only preamplifier that has nonlinear operation. Lacking the linearity, its advantage is that is appropriate for high flux background applications where with proper design of the resistor value, some level of background suppression can be achieved.

The RL circuit in figure operates as follows. Radiation caused photocurrent and dark current passes through the RL creates the voltage  $V_{in}$ . This voltage than induces a current that will pas through the MOSFET which operates in the sub threshold region. The integrated device current  $I_{int}$  will be an exponential according to the formula [7]:

$$I_{\text{int}} = I_d = \frac{W}{L} \mu_n C_{ox} \exp(V_{in} - \frac{mkT}{q}) \approx K \exp(V_{in}),$$

(2.6)

where K is dependent on resistor bias, geometry parameters and threshold voltage.

Figure 2.6: Resistor gate modulation preamplifier

With proper design of the resistor value, I<sub>int</sub> can be reduced close to zero for a determined value of background irradiance. Aside this advantage, RL preamplifier has fixed pattern noise due to variations of transistor geometry and threshold voltages over the FPA which limits its applications to high background irradiance applications. Also the resistance creates additional noise.

#### 2.2.7 Current Mirror Gate Modulation

Current mirror gate modulation (CM) preamplifier is similar to RL unit cell with the resistor being replaced by a diode connected MOSFET. It has better linearity compared to RL type unit cell, similar injection efficiency compared to DI unit cell. As in RL preamplifier, CM suffers from threshold voltage variations and geometry variations over the FPA.

The operation of CM unit cell in Figure 2.7 is as follows. The photo generated current creates a bias that is mirrored to the transistor whose drain is connected to the integration capacitor. After being connected to the output multiplexers a reset switch initializes the integration capacitor.

The CM preamplifier, although having better performance in terms of linearity, lacks the low input impedance since the input impedance will be strictly dependent on  $g_m$  as in the DI

preamplifier. Also it has the same noise issues of RL preamplifier as fixed pattern noise due to variations of transistor geometry and threshold voltages over the FPA.

Figure 2.7: Current mirror gate modulation preamplifier

# 2.2.8 Current Mirroring Direct Injection

Current mirroring direct injection (CMDI) achieves 100% injection efficiency even for very low input impedances with a little extra power consumption compared to BDI and creates a very stable detector bias compared to the DI preamplifiers. Its disadvantage is the moderate noise it introduces compared to above mentioned preamplifiers.

As in Figure 2.8, by the use of current mirrors, the photo current  $I_{ph}$  is mirrored to the transistors to the left. Since the drain currents of two NMOS devices are equal with same gate voltage the source of MN2 will be zero, creating a zero bias on the PV detector. A zero bias will also result a zero dark current, creating the measured integrated voltage to be only as a result of IR radiation. However, due to transistor threshold voltage mismatches, the PV diode can move slightly from zero bias to a 1 mV of reverse bias as stated in [11].

Figure 2.8: Current mirror direct injection preamplifier

The injection efficiency of CMDI preamplifier is also evaluated in detail as well as its comparison with widely used preamplifiers of DI and BDI in [11] and given as:

injection\_efficiency =

$$\frac{R_D}{R_D + R_{IN}} = \frac{g_{mn2}R_D}{g_{mn2}R_D + (1 - \gamma_{gm})}$$

, (2.7)

where  $\gamma_{gm}$  is given as:

$$\gamma_{gm} = \frac{g_{mp1}}{g_{mp2}} x \frac{g_{mn2}}{g_{mn1}}$$

(2.8)

And the reverse bias voltage over the detector is given as:

$$V_{DET} = \frac{K_P}{K_N} \Delta V_{TP} + \Delta V_{TN}, \qquad (2.9)$$

where  $K_P$  and  $K_N$  are geometry constants,  $\Delta V_{TP}$  and  $\Delta V_{TN}$  are threshold variations between two mirroring transistors of PMOS and PNMOS devices respectively [12].

The comparison with DI and BDI as in table shows that for a cost of little power consumption. However this work ignores that CMDI together with its benefits stated has higher noise level than DI.

|                                                      | DI                           | BDI                                             | CMDI                          |

|------------------------------------------------------|------------------------------|-------------------------------------------------|-------------------------------|

| $\Delta I_D$ (when $\Delta I_{ph} = 20 \text{ nA}$   | 1.17nA                       | 8.92nA                                          | 10.15nA                       |

| Injection efficiency<br>$(\Delta I_D/\Delta I_{ph})$ | 11.7%                        | 89.2%                                           | 101.5%                        |

| Unit cell power<br>consumption                       | $\sim V_{DD} \cdot I_{ph}$   | $\sim V_{DD} \cdot I_{ph}$<br>+ amplifier power | $\sim 2V_{DD}\cdot I_{pk}$    |

| Cell to cell detector<br>bias variation              | Within<br>~ 50mV<br>over FPA | Within<br>~ 2.5mV<br>over FPA                   | Within<br>~ 0.5mV<br>over FPA |

Table 2.1: Comparison of DI, BDI and CMDI preamplifiers [11]

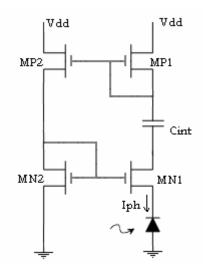

# 2.2.9 Current Mirroring Integration

Current Mirroring Integration (CMI) operates very similarly to CMDI but has the integration capacitor off-pixel, increasing the dynamic range and charge storage capacity. It has, as in CMDI, 100% injection efficiency and very stable detector bias over the FPA to a cost of higher power consumption, larger size and moderate noise.

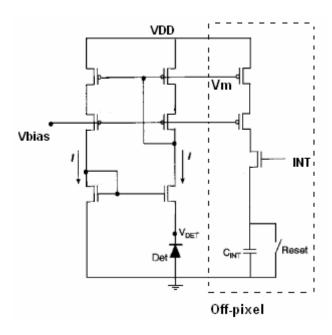

The operation of CMI unit cell as represented in Figure 2.9 is as follows. The photo generated current passes through MN1 and is mirrored to MN2 with high swing cascade current mirror through transistors MP1 and MP4. Similar to the CMDI preamplifier MN1 and MN2 being connected as current mirror, the PV detector bias is forced to be zero. By use of MP5 and MP6 the photocurrent is mirrored to the integration capacitor [12]. Following the read operation, a reset switch initializes the integration capacitor voltage.

Injection efficiency of the CMI unit cell is identical to that of CMDI, almost 100%. However for very low photocurrents (less than 1nA) the devices operating in the weak inversion may have significantly low transconductance values, decreasing the 100% injection efficiency. In terms of the detector bias stability, CMDI is identical to CMI. Its drawback is that CMI has significantly higher noise than DI or BDI type preamplifiers.

Figure 2.9: Current mirroring integration readout [12]

### 2.2.10 Comparison of ROIC Preamplifiers

Preamplifiers are the first circuit parts where photo generated charge to voltage conversion occur. In general, for user specified integration time charge is stored on a capacitor, multiplexed to the output and before a subsequent read operation a reset switch initializes the capacitor voltage. As discussed in the previous sections there are different types of input circuits varied with their properties as size, power consumption, input referred noise and dynamic range. The preamplifier choice is a designer decision according to the application specifications such as detector type, detector impedance and capacitance and application's radiation levels.

Among all preamplifiers, SI is the smallest unit cell, with minimum noise contribution. However using only detectors stray capacitance and detector getting in to forward bias region as the integrated voltage increases, results a limited dynamic range. A bus amplifier is required for charge to voltage conversion following the multiplexing of a detector to be read. SFD also uses the stray capacitance for same reasons as in SI, has a limited dynamic range. With three transistors, one for reset operation and two for source follower per detector, it is larger than SI unit cell, but ROICs with SFD does not require a bus amplifier due voltage conversion before multiplexing is handled by the source followers. Due the source follower, noise in SFD is higher than noise in SI preamplifiers.

Direct injection preamplifier is also a very compact input cell, which has higher dynamic range than SI and SFD due to the integrated capacitor. Compared to SI and SFD it has good detector voltage stability. DI preamplifier has also low noise due it has only one MOSFET device as the noise source. However, its only, but significant drawback is that for low IR irradiances DI unit cell shows poor injection efficiency due having high impedances. Hence DI unit cell is an inappropriate choice for low impedance detector arrays such as LWIR PV FPAs.

The injection efficiency problem is solved by using a feed forward inverting amplifier at the input as in BDI preamplifier. Injection efficiency is increased by a factor of the amplifier gain. However, input noise of the amplifier is another noise source. In addition, obtaining a high gain, low power amplifier at a small pixel area is a difficult task.

Capacitive transimpedance amplifier unit cell is widely used in many different ROICs as the preamplifier. It also uses an amplifier at the input as in the BDI which creates a wide output voltage change for a little change at the input. Hence for the integration period detector bias is quite stable. However as in BDI, the amplifier creates additional noise.

Resistive gate modulation circuit is used in high background applications due its nonlinear operation. Its size is also dependent on the resistor. Its drawback is that it creates a fixed pattern noise due to the device mismatches over the FPA.

Resistor is replaced by a mirroring MOSFET in current mirror gate modulation (CM) unit cell, making it operating linearly. It has only two transistors making it compact. However it also suffers from threshold voltage variations and geometry variations of MOSFETs creating noise.

Current mirroring direct injection unit cell is another preamplifier using current mirrors to stabilize the detector bias and reducing the input impedance. Very low input impedances can be achieved increasing the injection efficiency to 100%. Detector bias variations over the FPA can be as low as 2.5 mV which suppresses dark current variations. Its drawback is that integration capacitor is used in pixel, reducing the dynamic range in small pixel area. It also has high noise due to current mirrors.

Current mirroring injection (CMI) is similar to CMDI preamplifier, but it uses a high swing cascade current mirror structure to mirror the photo generated current to the off pixel

integration capacitor. Using off-pixel integration capacitor increases charge handling capacity. CMI injection efficiency and noise issues are same as in CMDI preamplifier.

| Preamplifier | Input<br>Impedance                     | Detector Bias<br>Stability                             | Size                                                       | Input Referred<br>Noise               |

|--------------|----------------------------------------|--------------------------------------------------------|------------------------------------------------------------|---------------------------------------|

| SI           | Self<br>integrator                     | Not stable, changes during integration                 | Small                                                      | Low, detector noise only              |

| SFD          |                                        | Not stable, changes during integration                 | Small, 3<br>transistors                                    | Moderate,  Depends on source follower |

| DI           | 1/g <sub>m</sub>                       | Not stable, changes<br>during integration<br>(10-50mV) | Small, only 1<br>transistor                                | Low, depends on single MOS            |

| BDI          | 1/g <sub>m</sub> x (1+A <sub>v</sub> ) | Stable, controlled<br>by op-amp feedback               | Large, due to in pixel amplifier and integration capacitor | Moderate,  Depends on amplifier noise |

| CTIA         | Self<br>integrator                     | Stable, controlled by op-amp feedback                  | Large, due to in pixel amplifier and integration capacitor | Moderate,  Depends on amplifier noise |

| RL           | Load resistor                          | Not stable, depends on photocurrent                    | Large due to in pixel resistor                             | Moderate, Depends on                  |

|      |                      |                                       | and capacitor                                                       | resistor                                   |

|------|----------------------|---------------------------------------|---------------------------------------------------------------------|--------------------------------------------|

| CM   | 1/g <sub>m</sub>     | Stable, controlled by current mirrors | Large due in pixel capacitor                                        | Moderate,<br>depends on<br>current mirrors |

| CMDI | 1-γ / g <sub>m</sub> | Stable (1-2.5mV)                      | Large due to in pixel integration capacitor and four transistors    | High due to current mirrors                |

| CMI  | 1-γ / g <sub>m</sub> | Stable (1-2.5mV)                      | Small,9<br>transistors but<br>off-pixel<br>integration<br>capacitor | High due to current mirrors                |

Table 2.2: A comparison of preamplifiers in terms of input impedance, detector bias stability, size and input referred noise, where  $A_{\nu}$  is the amplifier gain,  $\gamma$  is as given in equation 2.8 and  $g_m$  is the transconductance

# 2.3 Time Delay Integration

There are different signal processing techniques associated with ROICs such as time delay integration (TDI), sample and hold and correlated double sampling (CDS). ROICs, as well as these techniques, may have features such as variable gains, pixel selection-deselection in case of a malfunctioning pixel, automatic gain adjustments and etc. Thanks to the high integration capacity of CMOS technology, on chip digital quantization is also possible.

A sample and hold technique can be employed in a ROIC in order to obtain continuous integration. The integrated charge can be sampled to a storage capacitor and read while a new integration continues during the read from the hold capacitor.

Another technique, correlated double sampling (CDS) is widely used in sampled data circuits especially in switch capacitor circuits [13]. In switch capacitor circuits, CDS is used to store the noise of an amplifier in one phase and to subtract it from a new set of amplifier noise on a

subsequent phase creating a DC zero in the frequency domain, which eliminates flicker noise [14].

TDI is another signal processing techniques applied on ROICs to reduce noise, hence increase the SNR. SNR in infrared detectors is proportional to the square root of the integration time; TDI is used as a method to effectively increase the integration time without changing frame rate and resolution. By implementing TDI technique, diodes on the same row are used to detect the same image and the signal is integrated from these photo-diodes [3]. Hence, TDI realized on N detectors, results in an improvement of  $\sqrt{N}$  in SNR, effectively increasing integration time by N.

A mathematical formulation is presented in [4] as follows. Radiation is received by the first pixel and following a time delay  $\Delta t$ , same radiation is received by the subsequent pixel on the array. The output is the sum of charge stored by n pixels, n being the number TDI pixels used. Hence total voltage summed at the output is given as:

$$V_{total} = \sum_{i=1}^{n} v_i (t1 + (i-1) * \Delta t),$$

(2.10)

Where v<sub>i</sub> is the voltage corresponding to the charge accumulated by detector i.