# DESIGN AND REALIZATION OF A HIGH SPEED 64 X 64 – BIT MULTIPLIER FOR LOW POWER APPLICATIONS

by BERİL SEDA ÇİFTÇİ

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfillment of the requirements for the degree of Master of Science

> Sabancı University Spring 2003

# DESIGN AND REALIZATION OF A HIGH SPEED 64 X 64 – BIT MULTIPLIER FOR LOW POWER APPLICATIONS

APPROVED BY:

Assoc. Prof. Dr. Yaşar GÜRBÜZ

(Thesis Supervisor)

Assist. Prof. Dr. Ayhan BOZKURT

Assist. Prof. Dr. Erkay SAVAŞ

DATE OF APPROVAL:

© Beril Seda Çiftçi 2003 All Rights Reserved To my parents

#### ACKNOWLEDGEMENTS

I would like to thank my supervisor, Assoc. Prof. Yaşar Gürbüz, for his guidance, patience and encouragement throughout my research at Sabancı University. His contributions and helpful comments enabled me to study more efficiently. I also would like to thank my co-advisor, Assist. Prof. Ayhan Bozkurt, for his suggestions and help.

I am grateful to Tuğba Demirci for sharing her all design experience with me, answering my endless questions patiently and for her great friendship. Without her efforts, I could have never succeeded in the end.

It was a great pleasure to work with all colleagues at Microelectronics Group. I would like to thank Alper Emrah Üstünay, Aylin Ekşim, İhsan Çiçek, Mansoor Naseer and Mustafa Parlak for their valuable contributions, friendship and support.

I would like to present my thanks to four special friends, Fatma Tepiroğlu, Nihan Erol, Serdar Köroğlu and Verjin Karaoğlu, who have always been by my side whenever I need them, from the very first day we have known each other. I'm thankful for their unconditional love, trust and encouragement. I cannot imagine a life without them.

I also wish to acknowledge all the faculty members, graduate students and other individuals who have contributed to me during the period of my study at Sabancı University. Especially, I would like to thank Arif Volkan Vural, Ayça Çeşmelioğlu, Ekim Özaydın, Hacı Murat Özdemir, İpek Uzpeder, Özhan Öztürk, Sercan Uslu, Şenay Mihçin, Yeşim Müge Şahin and Zafer Gürel for their intimate friendship. Also, thanks to my late night workmates, Alper Gür, Ayşe Kıvılcım Coşkun, Didem Türker, Dilber Ece Gamsız, Erdinç Öztürk and Özkan Öztürk, who gave me the courage and support that I needed at the hardest aspects of my project.

Furthermore, I feel very lucky to have three precious friends in Sabancı University; I would like to thank Hakan Göl, Mustafa Kerem Darıcı and Nuri Mehmet Gökhan, for their invaluable friendship and for being my never-ending source of motivation.

Finally, I will forever be grateful to my parents for their unconditional endless love and for giving me the best of everything in the world. I would like to express my appreciation, especially to my mother, for all their sacrifices and efforts. Without their love and encouragement, all I could have achieved would be a complete failure.

# DESIGN AND REALIZATION OF A HIGH SPEED 64 X 64 – BIT MULTIPLIER FOR LOW POWER APPLICATIONS

### ABSTRACT

Wireless communication systems, including third generation cellular radio systems and wireless LANs, have become tremendously popular in recent years. These systems can be implemented using various platforms, like digital signal processors, ASICs and FPGAs. Most digital signal processing systems incorporate a multiplication unit to implement algorithms such as correlations, convolution, filtering and frequency analysis. These algorithms are used in applications such as finite impulse filters (FIR), infinite impulse filters (IIR), discrete cosine transforms (DCT) and fast Fourier transforms (FFT). Moreover, there has been a rapid increase in the popularity of portable and wireless electronic devices, like laptop computers, portable video players and cellular phones, which rely on embedded digital signal processors. Since the desire is to design digital systems for communication applications at best performance without power sacrifices, the need for high performance and low power multipliers is inevitable.

Since multiplication is one of the most critical operations in many computational systems, there have been many algorithm proposals in the literature to perform multiplication, each offering different advantages and having tradeoffs in terms of speed, circuit complexity, area and power consumption. This thesis focuses on an ASIC implementation of a multiplexer-based multiplication method, an efficient algorithm which is applicable to low power applications. Recently, it has been proved that the multiplexer-based multiplier outperforms the modified Booth multiplier both in speed and power dissipation by 13% to 26%, due to small internal capacitance. After analyzing the performance characteristics of conventional multiplier types, it is observed that the one designed using multiplexer-based multiplied numbers is small. In order to verify the superiorities of this algorithm, we performed an implementation, in which the bit size of the multiplicand and the multiplier is comparably large. Thus,

realization of a 64 x 64–bit multiplier block has been done in  $0.35\mu$  CMOS technology using Cadence Design Framework tools. The final multiplier structure operates at 12.8ns with an approximate dynamic power consumption of 1mW. Also, using the same algorithm, another block of 32-bit x 32-bit multiplier is designed and is sent for fabrication.

### ÖZET

Üçüncü nesil hücresel radyo sistemleri, kablosuz yerel bölge ağları gibi telsiz haberleşme sistemleri son yıllarda büyük önem kazanmıştır. Bu sistemler, sayısal işaret işlemciler, uygulamaya özgün tümdevreler (ASIC) ve alan-programlanabilir mantıksal kapı dizileri (FPGA) gibi ortamlar kullanılarak gerçekleştirilebilir. Temeli çarpma işlemine dayanan korelasyon, konvolüsyon, filtreleme ve frekans analizi gibi haberlesme algoritmalarının gerçeklenmesi amacıyla, sayısal işaret işlemcilerin çoğunda bir çarpma bloğu bulunur. Bu algoritmalar sonlu ve sonsuz dürtü yanıtlı süzgeçler, ayrık kosinüs dönüşümleri ve hızlı Fourier dönüşümleri gibi uygulamalarda yaygın olarak kullanılmaktadır. Bununla birlikte, tümleşik sayısal işaret işlemcilerle çalışan dizüstü bilgisayarlar, kablosuz video oynaticilari ve cep telefonları gibi tasınabilir elektronik tüketim mallarına olan rağbet hızla artmaktadır. Telekomünikasyon uygulamalarında hedef, güç tüketiminden ödün vermeden en yüksek performansta çalışan sayısal devre tasarımı gerçekleştirmek olduğundan, yüksek hızlı ve az güç tüketen çarpma devrelerine olan ihtiyaç kaçınılmazdır.

Çarpma, sayısal sistemlerin çoğunda yer alan en kritik işlemlerden biri olduğundan, tarihte çarpma işlemini gerçeklemeye yarayan ve farklı hız, alan, güç tüketimi ve devre karmaşıklığı özelliklerine sahip olan pek çok algoritma önerilmiştir. Bu tez, düşük güç tüketimli devreler için elverişli bir algoritma olan çoğullayıcı tabanlı çarpma yönteminin tümdevre (ASIC) uygulamasını içermektedir. Küçük iç kapasite özelliğinden dolayı, çoğullayıcı tabanlı çarpıcıların Booth çarpıcılarından hız ve güç tüketimi bağlamında %13 ila %26 oranında daha üstün olduğu teorik olarak kanıtlanmıştır. Klasik çarpma algoritmasıyla tasarlanmış devrelerin, özellikle küçük sayılarla işlem yaptığında, daha avantajlı olduğu görülmüştür. Bu algoritmanın üstünlüklerini doğrulamak ve diğer yapılarla kıyaslamak amacıyla, daha büyük sayılarla

çalışan bir uygulama ele alınmıştır. Bu amaçla, 64 x 64 - bitlik bir çarpma bloğunun tasarımı  $0.35\mu$  CMOS teknolojisinde Cadence tasarım programı kullanılarak gerçeklenmiştir. Elde edilen yapı 12.8ns'lik gecikme süresi ile çalışmakta olup statik güç tüketimi yaklaşık olarak 1mW olarak bulunmuştur. Ayrıca, üretim amacıyla yine aynı algoritma kullanılarak 32 x 32 – bitlik bir çarpma bloğu daha tasarlanmıştır.

## **TABLE OF CONTENTS**

| 1. | INTRC  | DUCTION                                             | 1  |

|----|--------|-----------------------------------------------------|----|

|    | 1.1.   | Design Considerations in Integrated Circuits        | 2  |

|    | 1.2.   | Why Low Power                                       | 2  |

|    | 1.3.   | Thesis Outline                                      | 3  |

| 2. | THEO   | RY OF MULTIPLICATION ALGORITHMS                     | 4  |

|    | 2.1.   | Multiplier Structure                                | 4  |

|    | 2.1.1. | Partial Product Generation                          | 5  |

|    | 2.1.2. | Partial Product Reduction                           | 6  |

|    | 2.1.2  | 2.1. Array Style Reduction                          | 7  |

|    | 2.1.2  | 2.2. Wallace Tree Partial Product Reduction         | 7  |

|    | 2.1.2  | 2.3. Partial Product Reduction using Booth Recoding | 10 |

|    | 2.2.   | Advanced Structures in Parallel Multipliers         | 12 |

|    | 2.2.1. | Baugh-Wooley Multiplier                             | 12 |

|    | 2.2.2. | 4:2 Compressor                                      | 15 |

|    | 2.2.3. | Hitachi's Multiplier                                | 17 |

|    | 2.2.4. | Inoue's Multiplier                                  | 17 |

|    | 2.3.   | Multiplier Power Reduction                          |    |

|    | 2.3.1. | Logic Level Multiplier Optimization                 |    |

|    | 2.4.   | Multipliers' Comparison                             | 19 |

| 3. | MULT   | IPLEXER-BASED MULTIPLICATION                        | 21 |

|    | 3.1.   | Introduction to the Algorithm                       | 21 |

|    | 3.2.   | Multiplexer Based Multipliers                       | 23 |

|    | 3.2.1. | Circuit Structure                                   | 23 |

|    | 3.2.2. | Comparison of Various Multipliers                   | 25 |

|    | 3.2.3. | Modification for Two's Complement Numbers           | 27 |

| 4. | DESIG  | N OF DIGITAL BLOCKS                                 | 28 |

|    | 4.1.   | Full Adder Design                                   |    |

| <b>6. REF</b> | ERENCES                                       | 53 |

|---------------|-----------------------------------------------|----|

| 5. CONCLUSION |                                               |    |

| 4.5.          | Design of 64 x 64-bit Multiplier Block        |    |

| 4.4.          | Comparison of Multipliers' Simulation Results | 40 |

| 4.3.          | Carry Lookahead Design                        |    |

| 4.2.          | Multiplexer Design                            |    |

## LIST OF TABLES

| Table 2.1 Booth recoding                                                             | 12    |

|--------------------------------------------------------------------------------------|-------|

| Table 2.2 Explanations of the Booth recoding table                                   | 12    |

| Table 2.3 Pros and cons table for various multiplication algorithms                  | 20    |

| Table 3.1 Truth table for Z <sub>j</sub>                                             | 22    |

| Table 3.2 Number of gates and transistors for various types of circuits              | 26    |

| Table 3.3 Circuit complexity comparison of various multipliers                       | 26    |

| Table 3.4 Operation time comparison of various multipliers                           | 27    |

| Table 4.1 Truth table for the full-adder circuit                                     | 29    |

| Table 4.2 Simulated dynamic performance characteristics of one-bit full-adder        | 30    |

| Table 4.3 Simulated dynamic performance characteristics of 18-T one-bit full-adder   | 33    |

| Table 4.4 Truth table for 4-to-1 multiplexer                                         | 34    |

| Table 4.5 Simulated dynamic performance characteristics of 4-1 multiplexer           | 36    |

| Table 4.6 Simulated dynamic performance characteristics of two-bit CLA               | 39    |

| Table 4.7(a) Performance characteristics of simulated 4x4-bit multiplier blocks      | 41    |

| Table 4.7(b) Improvement table of 4x4-bit multiplexer-based multiplier over of       | other |

| multiplier types                                                                     | 42    |

| Table 4.8(a) Performance characteristics of simulated 8x8-bit multiplier blocks      | 43    |

| Table 4.8(b) Improvement table of 8x8-bit multiplexer-based multiplier over of       | other |

| multiplier types                                                                     | 44    |

| Table 4.9(a) Performance characteristics of simulated 16x16-bit multiplier blocks    | 45    |

| Table 4.9(b) Improvement table of 16x16-bit multiplexer-based multiplier over o      | other |

| multiplier types                                                                     | 46    |

| Table 4.10(a) Performance characteristics of simulated 32x32-bit multiplier blocks . | 47    |

| Table 4.10(b) Improvement table of 32x32-bit multiplexer-based multiplier over o     | other |

| multiplier types                                                                     | 48    |

## LIST OF FIGURES

| Figure 2.1 Digital multiplication flow                                               | 4   |

|--------------------------------------------------------------------------------------|-----|

| Figure 2.2 Partial product generation example                                        | 5   |

| Figure 2.3 Array partial product reduction                                           | 7   |

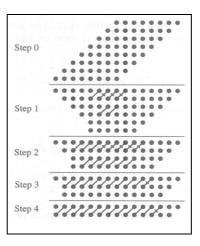

| Figure 2.4 Wallace tree partial product reduction                                    | 8   |

| Figure 2.5 An 8 x 8-bit Dadda multiplier example                                     | 9   |

| Figure 2.6 Unsigned multiplication                                                   | 13  |

| Figure 2.7 Two's complement multiplication                                           | 13  |

| Figure 2.8 Baugh-Wooley two's complement multiplication                              | 14  |

| Figure 2.9 Modified Baugh-Wooley two's complement multiplication                     | 15  |

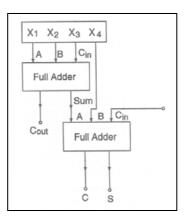

| Figure 2.10 4-to-2 compressor                                                        | 16  |

| Figure 2.11 Logic diagram of the 4-to-2 compressor (4W) unit                         | 16  |

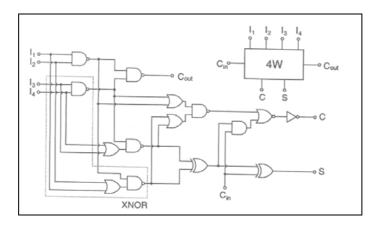

| Figure 2.12 Organization of Hitachi's multiplier                                     | 17  |

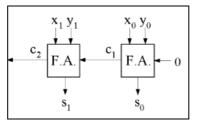

| Figure 3.1 Two-bit carry propagate adder                                             | 23  |

| Figure 3.2 Four-bit carry propagate adder                                            | 23  |

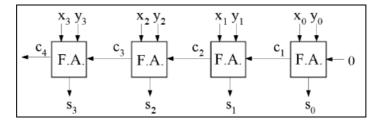

| Figure 3.3 Multiplexer-based multiplication algorithm                                | 24  |

| Figure 3.4 Multiplexer-based parallel multiplier                                     | 24  |

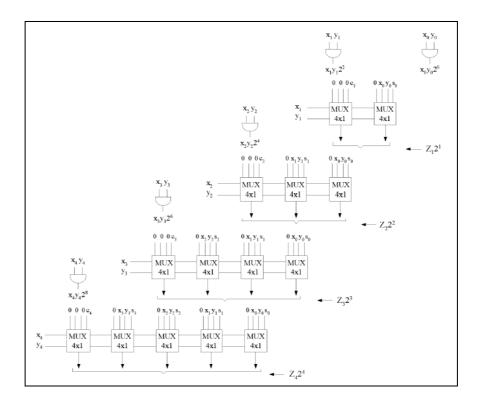

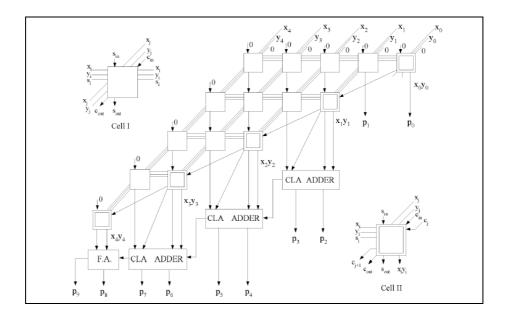

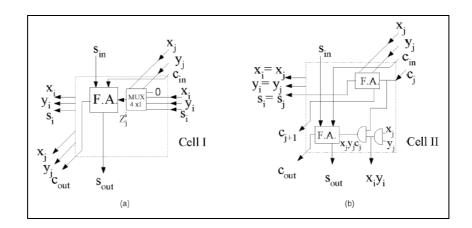

| Figure 3.5 Circuit structures of Cell-I and Cell-II blocks                           | 25  |

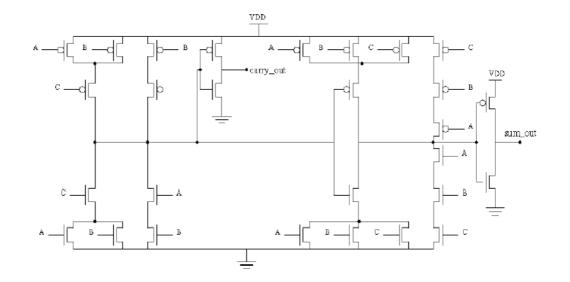

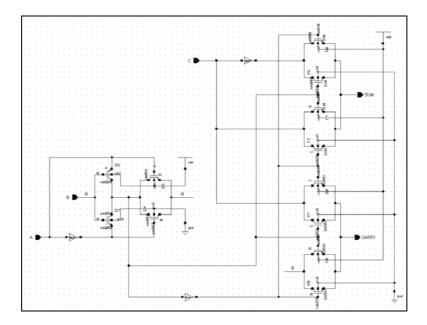

| Figure 4.1 Transistor-level schematic of conventional CMOS 28-T one-bit full-adder.  | 29  |

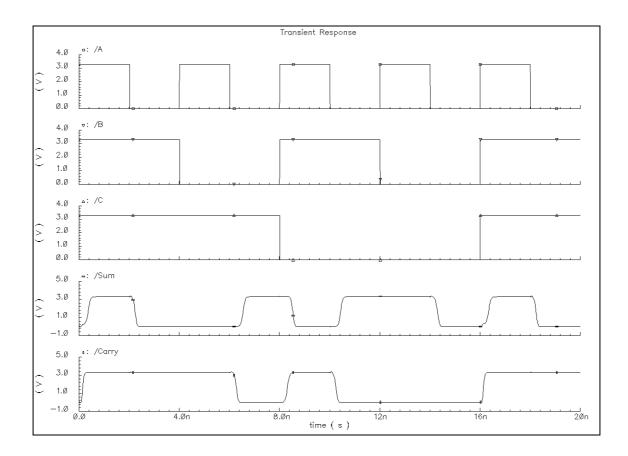

| Figure 4.2 Simulated input and output waveforms of the designed 28-T full-add        | ler |

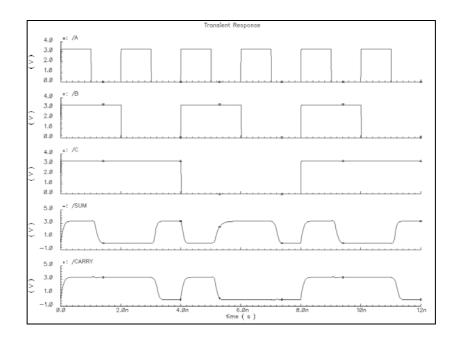

| circuit.                                                                             | 30  |

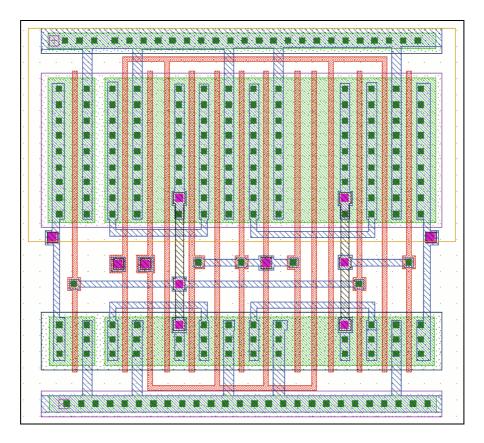

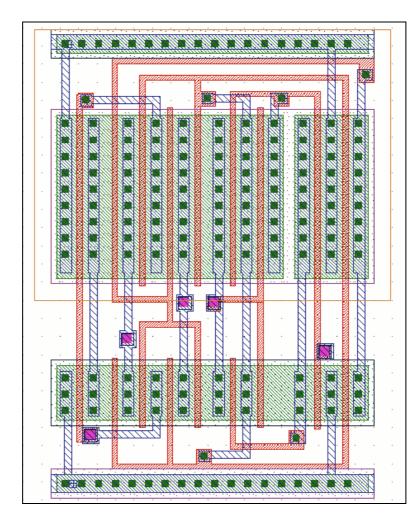

| Figure 4.3 Layout view of the designed one-bit full-adder                            | 31  |

| Figure 4.4 Transistor-level schematic of optimized 18-T CMOS full-adder circuit      | 32  |

| Figure 4.5 Simulated input and output waveforms of the designed optimized 18-T full- | -   |

| adder circuit                                                                        | 32  |

| Figure 4.6 Layout view of the designed 18-T one-bit full-adder                       | 33  |

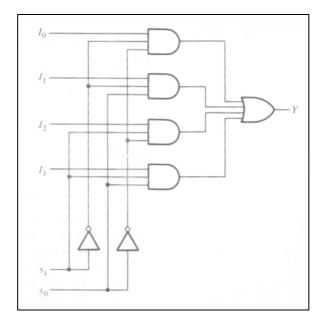

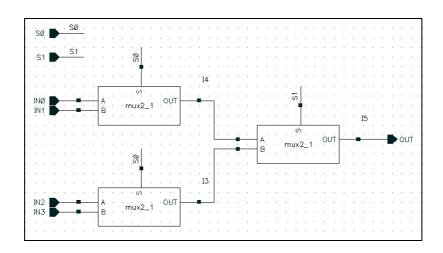

| Figure 4.7 Gate-level schematic of 4-1 multiplexer                                   | 34  |

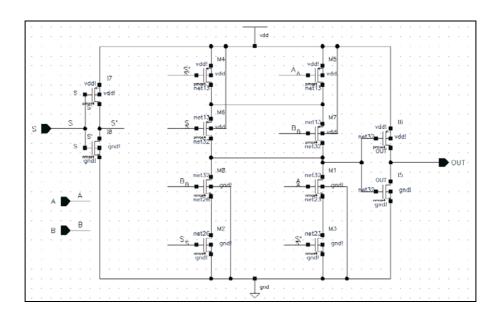

| Figure 4.8 Transistor-level schematic of 2-1 multiplexer                             | 35  |

| Figure 4.9 Schematic of 4-1 multiplexer                                     | 35 |

|-----------------------------------------------------------------------------|----|

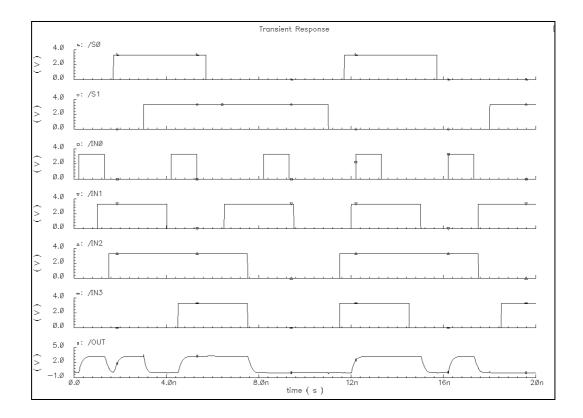

| Figure 4.10 Simulated input and output waveforms of the multiplexer circuit | 36 |

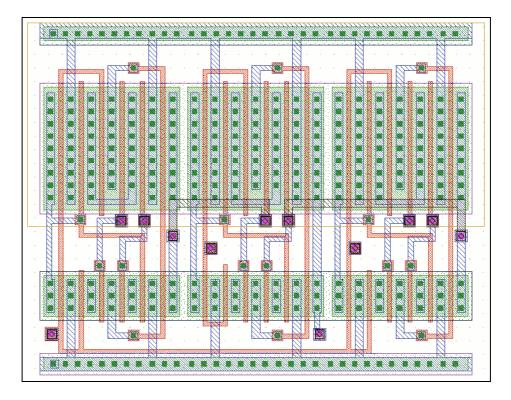

| Figure 4.11 Layout view of the designed 4-1 multiplexer                     | 37 |

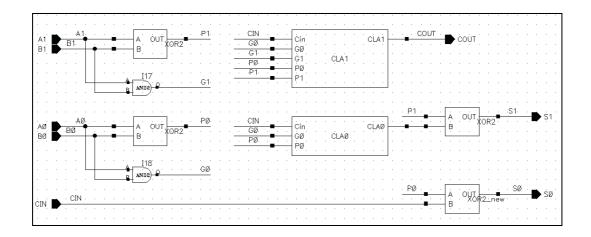

| Figure 4.12 Schematic view of the designed two-bit CLA circuit              | 39 |

| Figure 4.13 Simulated input and output waveforms of the two-bit CLA circuit | 39 |

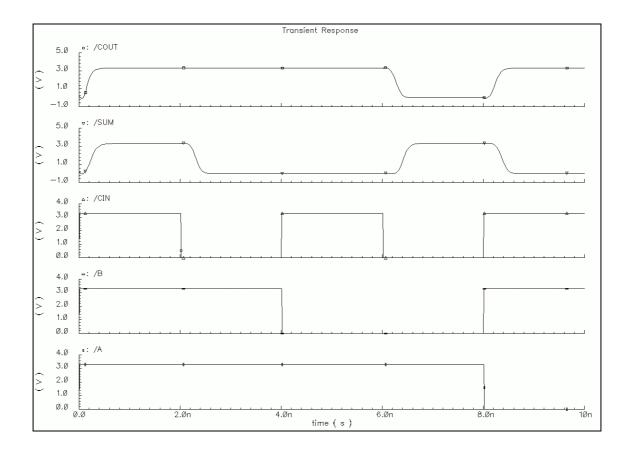

| Figure 4.14 Layout view of the designed CLA                                 | 40 |

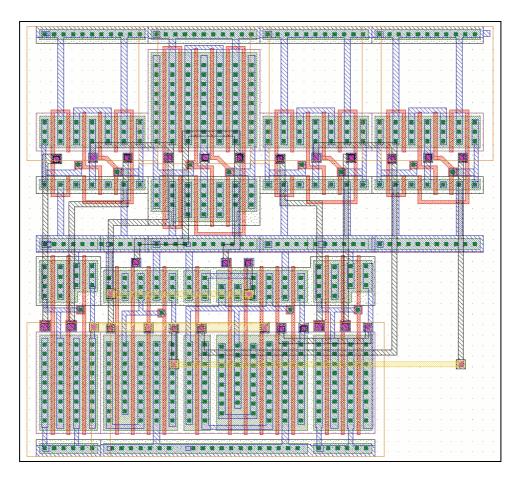

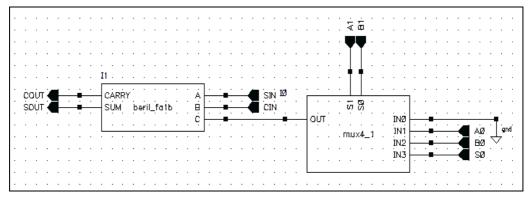

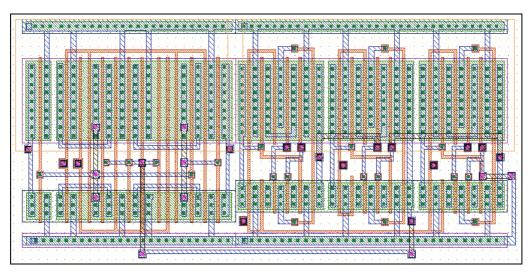

| Figure 4.15 Schematic view of the Cell-I Block                              | 49 |

| Figure 4.16 Layout view of the Cell-I Block                                 | 49 |

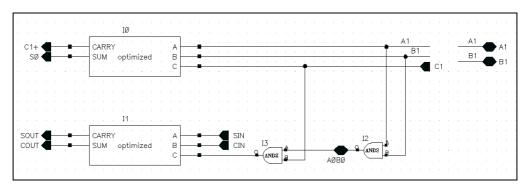

| Figure 4.17 Schematic view of the Cell-II Block                             | 49 |

| Figure 4.18 Layout view of the Cell-II Block                                | 50 |

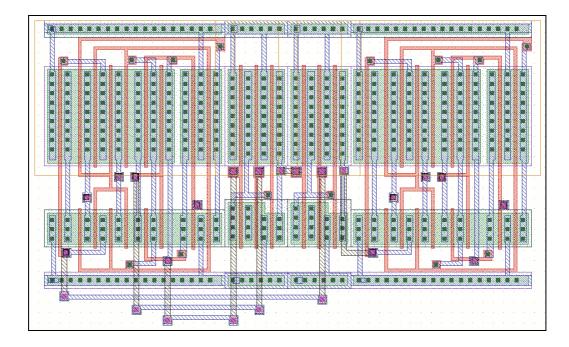

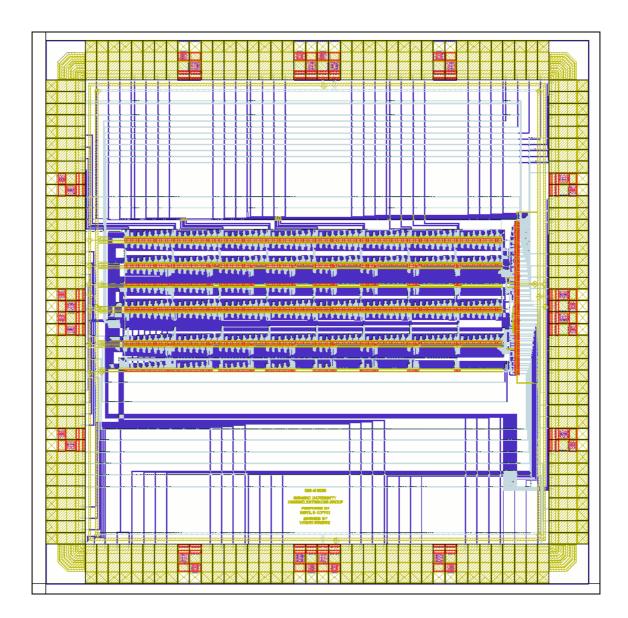

| Figure 4.19 Core layout of the 64 x 64–bit multiplier block                 | 50 |

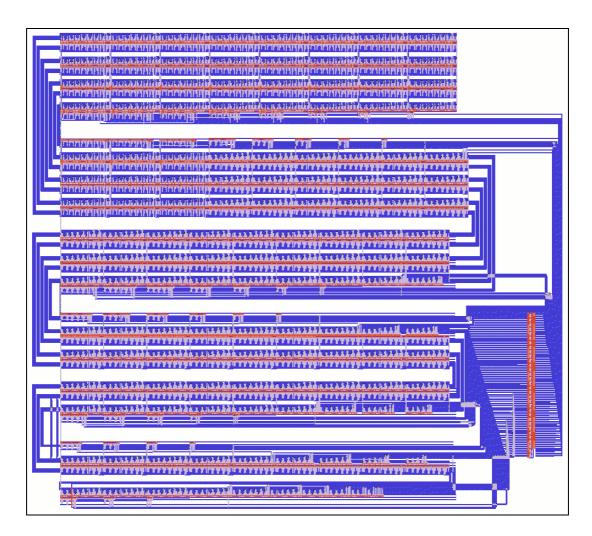

| Figure 4.20 Layout of 32 x 32-bit multiplier block                          | 51 |

# DESIGN AND REALIZATION OF A HIGH SPEED 64 X 64 – BIT MULTIPLIER FOR LOW POWER APPLICATIONS

by BERİL SEDA ÇİFTÇİ

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfillment of the requirements for the degree of Master of Science

> Sabancı University Spring 2003

# DESIGN AND REALIZATION OF A HIGH SPEED 64 X 64 – BIT MULTIPLIER FOR LOW POWER APPLICATIONS

APPROVED BY:

Assoc. Prof. Dr. Yaşar GÜRBÜZ

(Thesis Supervisor)

Assist. Prof. Dr. Ayhan BOZKURT

Assist. Prof. Dr. Erkay SAVAŞ

DATE OF APPROVAL:

© Beril Seda Çiftçi 2003 All Rights Reserved To my parents

#### ACKNOWLEDGEMENTS

I would like to thank my supervisor, Assoc. Prof. Yaşar Gürbüz, for his guidance, patience and encouragement throughout my research at Sabancı University. His contributions and helpful comments enabled me to study more efficiently. I also would like to thank my co-advisor, Assist. Prof. Ayhan Bozkurt, for his suggestions and help.

I am grateful to Tuğba Demirci for sharing her all design experience with me, answering my endless questions patiently and for her great friendship. Without her efforts, I could have never succeeded in the end.

It was a great pleasure to work with all colleagues at Microelectronics Group. I would like to thank Alper Emrah Üstünay, Aylin Ekşim, İhsan Çiçek, Mansoor Naseer and Mustafa Parlak for their valuable contributions, friendship and support.

I would like to present my thanks to four special friends, Fatma Tepiroğlu, Nihan Erol, Serdar Köroğlu and Verjin Karaoğlu, who have always been by my side whenever I need them, from the very first day we have known each other. I'm thankful for their unconditional love, trust and encouragement. I cannot imagine a life without them.

I also wish to acknowledge all the faculty members, graduate students and other individuals who have contributed to me during the period of my study at Sabancı University. Especially, I would like to thank Arif Volkan Vural, Ayça Çeşmelioğlu, Ekim Özaydın, Hacı Murat Özdemir, İpek Uzpeder, Özhan Öztürk, Sercan Uslu, Şenay Mihçin, Yeşim Müge Şahin and Zafer Gürel for their intimate friendship. Also, thanks to my late night workmates, Alper Gür, Ayşe Kıvılcım Coşkun, Didem Türker, Dilber Ece Gamsız, Erdinç Öztürk and Özkan Öztürk, who gave me the courage and support that I needed at the hardest aspects of my project.

Furthermore, I feel very lucky to have three precious friends in Sabancı University; I would like to thank Hakan Göl, Mustafa Kerem Darıcı and Nuri Mehmet Gökhan, for their invaluable friendship and for being my never-ending source of motivation.

Finally, I will forever be grateful to my parents for their unconditional endless love and for giving me the best of everything in the world. I would like to express my appreciation, especially to my mother, for all their sacrifices and efforts. Without their love and encouragement, all I could have achieved would be a complete failure.

# DESIGN AND REALIZATION OF A HIGH SPEED 64 X 64 – BIT MULTIPLIER FOR LOW POWER APPLICATIONS

### ABSTRACT

Wireless communication systems, including third generation cellular radio systems and wireless LANs, have become tremendously popular in recent years. These systems can be implemented using various platforms, like digital signal processors, ASICs and FPGAs. Most digital signal processing systems incorporate a multiplication unit to implement algorithms such as correlations, convolution, filtering and frequency analysis. These algorithms are used in applications such as finite impulse filters (FIR), infinite impulse filters (IIR), discrete cosine transforms (DCT) and fast Fourier transforms (FFT). Moreover, there has been a rapid increase in the popularity of portable and wireless electronic devices, like laptop computers, portable video players and cellular phones, which rely on embedded digital signal processors. Since the desire is to design digital systems for communication applications at best performance without power sacrifices, the need for high performance and low power multipliers is inevitable.

Since multiplication is one of the most critical operations in many computational systems, there have been many algorithm proposals in the literature to perform multiplication, each offering different advantages and having tradeoffs in terms of speed, circuit complexity, area and power consumption. This thesis focuses on an ASIC implementation of a multiplexer-based multiplication method, an efficient algorithm which is applicable to low power applications. Recently, it has been proved that the multiplexer-based multiplier outperforms the modified Booth multiplier both in speed and power dissipation by 13% to 26%, due to small internal capacitance. After analyzing the performance characteristics of conventional multiplier types, it is observed that the one designed using multiplexer-based multiplied numbers is small. In order to verify the superiorities of this algorithm, we performed an implementation, in which the bit size of the multiplicand and the multiplier is comparably large. Thus,

realization of a 64 x 64–bit multiplier block has been done in  $0.35\mu$  CMOS technology using Cadence Design Framework tools. The final multiplier structure operates at 12.8ns with an approximate dynamic power consumption of 1mW. Also, using the same algorithm, another block of 32-bit x 32-bit multiplier is designed and is sent for fabrication.

### ÖZET

Üçüncü nesil hücresel radyo sistemleri, kablosuz yerel bölge ağları gibi telsiz haberleşme sistemleri son yıllarda büyük önem kazanmıştır. Bu sistemler, sayısal işaret işlemciler, uygulamaya özgün tümdevreler (ASIC) ve alan-programlanabilir mantıksal kapı dizileri (FPGA) gibi ortamlar kullanılarak gerçekleştirilebilir. Temeli çarpma işlemine dayanan korelasyon, konvolüsyon, filtreleme ve frekans analizi gibi haberlesme algoritmalarının gerçeklenmesi amacıyla, sayısal işaret işlemcilerin çoğunda bir çarpma bloğu bulunur. Bu algoritmalar sonlu ve sonsuz dürtü yanıtlı süzgeçler, ayrık kosinüs dönüşümleri ve hızlı Fourier dönüşümleri gibi uygulamalarda yaygın olarak kullanılmaktadır. Bununla birlikte, tümleşik sayısal işaret işlemcilerle çalışan dizüstü bilgisayarlar, kablosuz video oynaticilari ve cep telefonları gibi tasınabilir elektronik tüketim mallarına olan rağbet hızla artmaktadır. Telekomünikasyon uygulamalarında hedef, güç tüketiminden ödün vermeden en yüksek performansta çalışan sayısal devre tasarımı gerçekleştirmek olduğundan, yüksek hızlı ve az güç tüketen çarpma devrelerine olan ihtiyaç kaçınılmazdır.

Çarpma, sayısal sistemlerin çoğunda yer alan en kritik işlemlerden biri olduğundan, tarihte çarpma işlemini gerçeklemeye yarayan ve farklı hız, alan, güç tüketimi ve devre karmaşıklığı özelliklerine sahip olan pek çok algoritma önerilmiştir. Bu tez, düşük güç tüketimli devreler için elverişli bir algoritma olan çoğullayıcı tabanlı çarpma yönteminin tümdevre (ASIC) uygulamasını içermektedir. Küçük iç kapasite özelliğinden dolayı, çoğullayıcı tabanlı çarpıcıların Booth çarpıcılarından hız ve güç tüketimi bağlamında %13 ila %26 oranında daha üstün olduğu teorik olarak kanıtlanmıştır. Klasik çarpma algoritmasıyla tasarlanmış devrelerin, özellikle küçük sayılarla işlem yaptığında, daha avantajlı olduğu görülmüştür. Bu algoritmanın üstünlüklerini doğrulamak ve diğer yapılarla kıyaslamak amacıyla, daha büyük sayılarla

çalışan bir uygulama ele alınmıştır. Bu amaçla, 64 x 64 - bitlik bir çarpma bloğunun tasarımı  $0.35\mu$  CMOS teknolojisinde Cadence tasarım programı kullanılarak gerçeklenmiştir. Elde edilen yapı 12.8ns'lik gecikme süresi ile çalışmakta olup statik güç tüketimi yaklaşık olarak 1mW olarak bulunmuştur. Ayrıca, üretim amacıyla yine aynı algoritma kullanılarak 32 x 32 – bitlik bir çarpma bloğu daha tasarlanmıştır.

## **TABLE OF CONTENTS**

| 1. | INTRC  | DUCTION                                             | 1  |

|----|--------|-----------------------------------------------------|----|

|    | 1.1.   | Design Considerations in Integrated Circuits        | 2  |

|    | 1.2.   | Why Low Power                                       | 2  |

|    | 1.3.   | Thesis Outline                                      | 3  |

| 2. | THEO   | RY OF MULTIPLICATION ALGORITHMS                     | 4  |

|    | 2.1.   | Multiplier Structure                                | 4  |

|    | 2.1.1. | Partial Product Generation                          | 5  |

|    | 2.1.2. | Partial Product Reduction                           | 6  |

|    | 2.1.2  | 2.1. Array Style Reduction                          | 7  |

|    | 2.1.2  | 2.2. Wallace Tree Partial Product Reduction         | 7  |

|    | 2.1.2  | 2.3. Partial Product Reduction using Booth Recoding | 10 |

|    | 2.2.   | Advanced Structures in Parallel Multipliers         | 12 |

|    | 2.2.1. | Baugh-Wooley Multiplier                             | 12 |

|    | 2.2.2. | 4:2 Compressor                                      | 15 |

|    | 2.2.3. | Hitachi's Multiplier                                | 17 |

|    | 2.2.4. | Inoue's Multiplier                                  | 17 |

|    | 2.3.   | Multiplier Power Reduction                          |    |

|    | 2.3.1. | Logic Level Multiplier Optimization                 |    |

|    | 2.4.   | Multipliers' Comparison                             | 19 |

| 3. | MULT   | IPLEXER-BASED MULTIPLICATION                        | 21 |

|    | 3.1.   | Introduction to the Algorithm                       | 21 |

|    | 3.2.   | Multiplexer Based Multipliers                       | 23 |

|    | 3.2.1. | Circuit Structure                                   | 23 |

|    | 3.2.2. | Comparison of Various Multipliers                   | 25 |

|    | 3.2.3. | Modification for Two's Complement Numbers           | 27 |

| 4. | DESIG  | N OF DIGITAL BLOCKS                                 | 28 |

|    | 4.1.   | Full Adder Design                                   |    |

| <b>6. REF</b> | ERENCES                                       | 53 |

|---------------|-----------------------------------------------|----|

| 5. CONCLUSION |                                               |    |

| 4.5.          | Design of 64 x 64-bit Multiplier Block        |    |

| 4.4.          | Comparison of Multipliers' Simulation Results | 40 |

| 4.3.          | Carry Lookahead Design                        |    |

| 4.2.          | Multiplexer Design                            |    |

## LIST OF TABLES

| Table 2.1 Booth recoding                                                             | 12    |

|--------------------------------------------------------------------------------------|-------|

| Table 2.2 Explanations of the Booth recoding table                                   | 12    |

| Table 2.3 Pros and cons table for various multiplication algorithms                  | 20    |

| Table 3.1 Truth table for Z <sub>j</sub>                                             | 22    |

| Table 3.2 Number of gates and transistors for various types of circuits              | 26    |

| Table 3.3 Circuit complexity comparison of various multipliers                       | 26    |

| Table 3.4 Operation time comparison of various multipliers                           | 27    |

| Table 4.1 Truth table for the full-adder circuit                                     | 29    |

| Table 4.2 Simulated dynamic performance characteristics of one-bit full-adder        | 30    |

| Table 4.3 Simulated dynamic performance characteristics of 18-T one-bit full-adder   | 33    |

| Table 4.4 Truth table for 4-to-1 multiplexer                                         | 34    |

| Table 4.5 Simulated dynamic performance characteristics of 4-1 multiplexer           | 36    |

| Table 4.6 Simulated dynamic performance characteristics of two-bit CLA               | 39    |

| Table 4.7(a) Performance characteristics of simulated 4x4-bit multiplier blocks      | 41    |

| Table 4.7(b) Improvement table of 4x4-bit multiplexer-based multiplier over of       | other |

| multiplier types                                                                     | 42    |

| Table 4.8(a) Performance characteristics of simulated 8x8-bit multiplier blocks      | 43    |

| Table 4.8(b) Improvement table of 8x8-bit multiplexer-based multiplier over of       | other |

| multiplier types                                                                     | 44    |

| Table 4.9(a) Performance characteristics of simulated 16x16-bit multiplier blocks    | 45    |

| Table 4.9(b) Improvement table of 16x16-bit multiplexer-based multiplier over o      | other |

| multiplier types                                                                     | 46    |

| Table 4.10(a) Performance characteristics of simulated 32x32-bit multiplier blocks . | 47    |

| Table 4.10(b) Improvement table of 32x32-bit multiplexer-based multiplier over o     | other |

| multiplier types                                                                     | 48    |

## LIST OF FIGURES

| Figure 2.1 Digital multiplication flow                                               | 4   |

|--------------------------------------------------------------------------------------|-----|

| Figure 2.2 Partial product generation example                                        | 5   |

| Figure 2.3 Array partial product reduction                                           | 7   |

| Figure 2.4 Wallace tree partial product reduction                                    | 8   |

| Figure 2.5 An 8 x 8-bit Dadda multiplier example                                     | 9   |

| Figure 2.6 Unsigned multiplication                                                   | 13  |

| Figure 2.7 Two's complement multiplication                                           | 13  |

| Figure 2.8 Baugh-Wooley two's complement multiplication                              | 14  |

| Figure 2.9 Modified Baugh-Wooley two's complement multiplication                     | 15  |

| Figure 2.10 4-to-2 compressor                                                        | 16  |

| Figure 2.11 Logic diagram of the 4-to-2 compressor (4W) unit                         | 16  |

| Figure 2.12 Organization of Hitachi's multiplier                                     | 17  |

| Figure 3.1 Two-bit carry propagate adder                                             | 23  |

| Figure 3.2 Four-bit carry propagate adder                                            | 23  |

| Figure 3.3 Multiplexer-based multiplication algorithm                                | 24  |

| Figure 3.4 Multiplexer-based parallel multiplier                                     | 24  |

| Figure 3.5 Circuit structures of Cell-I and Cell-II blocks                           | 25  |

| Figure 4.1 Transistor-level schematic of conventional CMOS 28-T one-bit full-adder.  | 29  |

| Figure 4.2 Simulated input and output waveforms of the designed 28-T full-add        | ler |

| circuit.                                                                             | 30  |

| Figure 4.3 Layout view of the designed one-bit full-adder                            | 31  |

| Figure 4.4 Transistor-level schematic of optimized 18-T CMOS full-adder circuit      | 32  |

| Figure 4.5 Simulated input and output waveforms of the designed optimized 18-T full- | -   |

| adder circuit                                                                        | 32  |

| Figure 4.6 Layout view of the designed 18-T one-bit full-adder                       | 33  |

| Figure 4.7 Gate-level schematic of 4-1 multiplexer                                   | 34  |

| Figure 4.8 Transistor-level schematic of 2-1 multiplexer                             | 35  |

| Figure 4.9 Schematic of 4-1 multiplexer                                     | 35 |

|-----------------------------------------------------------------------------|----|

| Figure 4.10 Simulated input and output waveforms of the multiplexer circuit | 36 |

| Figure 4.11 Layout view of the designed 4-1 multiplexer                     | 37 |

| Figure 4.12 Schematic view of the designed two-bit CLA circuit              | 39 |

| Figure 4.13 Simulated input and output waveforms of the two-bit CLA circuit | 39 |

| Figure 4.14 Layout view of the designed CLA                                 | 40 |

| Figure 4.15 Schematic view of the Cell-I Block                              | 49 |

| Figure 4.16 Layout view of the Cell-I Block                                 | 49 |

| Figure 4.17 Schematic view of the Cell-II Block                             | 49 |

| Figure 4.18 Layout view of the Cell-II Block                                | 50 |

| Figure 4.19 Core layout of the 64 x 64–bit multiplier block                 | 50 |

| Figure 4.20 Layout of 32 x 32-bit multiplier block                          | 51 |

### **1. INTRODUCTION**

Arithmetic circuits, like adders and multipliers, are essential components in the design of communication circuits in ASIC. Recently, an overwhelming interest has been seen in the problems of designing digital systems for communication systems and digital signal processing with low power at no performance penalty. To design low-power high-speed arithmetic circuits requires a combination techniques at four levels; algorithm, architecture, circuit and system levels. This thesis presents an ASIC implementation of a multiplication algorithm, which is suitable for high-performance and low-power applications.

In microprocessors, multiplication operation is performed in a variety of forms in hardware and software depending on the cost and transistor budget allocated for this particular operation. In the beginning stages of computer development, any complex operation was usually programmed in software or coded in the micro-code of the machine and some limited assistance was provided. Today, it's more likely to find full hardware implementation of the multiplication in order to satisfy the growing demand for speed and due to increasing cost of hardware.

Most digital signal processing (DSP) systems incorporate a multiplication unit to implement algorithms such as correlations, convolution, filtering and frequency analysis. In many DSP algorithms, the multiplier lies in the critical delay path and ultimately determines the performance of the algorithm. The speed of multiplication operation is of great importance in DSP as well as in the general processors today, especially since the media processing took off. In the past, multiplication was implemented generally with a sequence of addition, subtraction and shift operations. Recently, many multiplication algorithms have been invented and developed, each having pros and cons in different fields. The multiplier is a fairly large block of a computing system. The amount of circuitry involved is proportional to the square of its resolution; i.e. a multiplier of size n bits has  $O(n^2)$  gates [2]. For multiplication algorithms performed in DSP applications, latency and throughput are the two major constraints from delay perspective. Latency is the real delay of computing a function, a measure of how long after the inputs to a device are stable, is the final result available on outputs. Throughput is the measure of how many multiplications can be performed in a given period of time. Multiplier is not only a high-delay block but also a significant source of power dissipation. That's why, if one also aims to minimize power consumption, it is of great interest to identify the techniques to be applied to reduce delay by using various delay optimizations.

#### **1.1. Design Considerations in Integrated Circuits**

After guaranteeing correct digital functionality, the primary consideration for system designers has always been speed. A circuit is specified to operate at a particular delay, otherwise the entire system may not work; further reduction is beneficial but not strictly necessary. Other factors may have equal or greater importance than power dissipation; area of implementation and reliability issues are subjects which designer must take into account. It's worth to note that power reduction techniques are not necessarily negatively correlated to delay reduction. For example, one method to reduce delay in a circuit's critical path is to upsize the driving strength of gates, which results in increased power reduction. However, reducing interconnect capacitance, which is another way to lower delay, reduces both power and delay. Generally, great power savings can be achieved if delay is not an issue, but optimizing power without delay consideration is insignificant.

### 1.2. Why Low Power?

Power dissipation limitations come in two ways. The first is related to cooling considerations when implementing high performance systems. High-speed circuits dissipate large amounts of energy in a short amount of time, generating a great deal of

heat. This heat needs to be removed by the package on which integrated circuits are mounted. Heat removal may become a limiting factor if the package cannot sufficiently dissipate this heat or if the required thermal components are too expensive for the application.

The second failure of high-power circuits relates to the increasing popularity of portable electronic devices. Laptop computers, portable video players and cellular phones all use batteries as a power source. These devices provide a limited time of operation before they require recharging. To extend the battery life, low power operation is desirable in integrated circuits.

#### 1.3. Thesis Outline

This thesis focuses on an algorithm, called multiplexer based multiplication, which is suitable for high-speed and low-power applications. The algorithm, which is proposed by K. Pekmestzi, is symmetric so it's very applicable for binary multiplication, due to the interchangeability of the multiplicand and the multiplier. In theory, it is proven that the algorithm is comparably faster than recently proposed ones and much simpler than the others by means of circuit complexity. The implementation of this algorithm is performed by designing a 64-bit x 64-bit multiplier block in 0.35µ CMOS technology using Cadence Design Framework tools. Also, using the same algorithm, another block of 32-bit x 32-bit multiplier is designed and is sent for fabrication. The following chapters discuss the reason of using multiplexer-based multiplication algorithm as well as the design details of the blocks. In chapter 2, sequential multiplication basics, like forming the partial products and reducing the number of partial product bits through the use of high-radix methods, and various multiplication algorithms are introduced. The theory of multiplexer based multiplication algorithm and the architectural structure of designed multiplier is explained in Chapter 3. Chapter 4 presents design stages of the multiplier block, including the simulation results and layouts. Finally, in Chapter 5, conclusions are discussed.

### 2. THEORY OF MULTIPLICATION ALGORITHMS

In this chapter, we present a brief description of digital multipliers including their structure and relevant components. Some techniques, which have been developed to reduce the multiplier delay, are also discussed. Next, we go over power dissipation in CMOS circuits, along with some basic techniques, which can be applied to reduce power.

#### 2.1. Multiplier structure

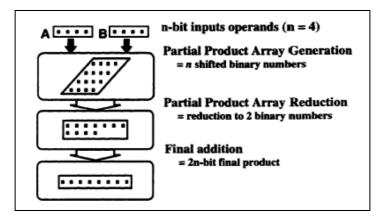

Digital multiplication is a series of bit shifts and bit additions, where two numbers, the multiplicand and the multiplier are combined into the result. Considering the bit representations of the multiplicand  $X = X_{n-1} \dots X_1 X_0$  and the multiplier  $Y = Y_{n-1} \dots Y_1 Y_0$ , in order to form the product, up to n shifted copies of the multiplicand are to be added for unsigned multiplication. The entire process consists of three steps, partial product generation, partial product reduction and final addition. Digital multiplication process flow is illustrated in Fig. 2.1

Figure 2.1 Digital multiplication flow [19]

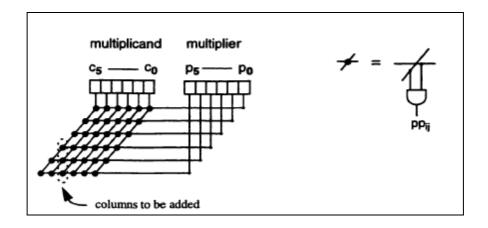

### 2.1.1 Partial Product Generation

In digital multiplication, as an initial step, one needs to generate n shifted copies of the multiplicand, which may be added in the coming stage. The value of the multiplier bit determines whether the shifted copy is to be added or not: if the i<sup>th</sup> bit  $(0 \le i \le n-1)$  of the multiplier is '1', then the shifted copy of the multiplicand is added. If the bit is '0', it's not added. A logical AND gate can implement this operation, by performing the function AND(x<sub>i</sub>y<sub>j</sub>)  $(0 \le i \le n-1 \land 0 \le y \le n-1)$ . The resulting values are called partial products. Fig.2.2 shows a trapezoidal structure, called *partial product array (PPA)*, where the partial product bits are arranged in columns to be added in order to form the product. This process is called *product array generation* [19].

Figure 2.2 Partial product generation example [19]

As noticed, all the bits are formed in parallel in the PPA, thus the static delay of each of the bits is equal. The width of the PPA is proportional to the size of the multiplicand whereas the height of the array is proportional to the size of the multiplier. The bits in a particular column will be added later on and some columns have more bits than others; middle bit positions require more additions than the low-order and highorder bit positions. Since carry bits from low-order positions result in a large number of bits to be added at the high-order bit positions, more additions will be necessary at the high-order positions than at the low-order ones [9].

#### 2.1.2. Partial Product Reduction

Efficient implementation of a digital multiplier depends on the method of the addition of partial product array bits. Since each shifted version of the multiplicand will give a delay proportional to the width of the multiplicand, the multiplier block will require a large amount of time to perform the operation if conventional adders were used to implement this addition. Hence, the partial products are reduced using a technique, called *carry-save addition*, which allows successive additions in one global step.

Considering the addition of two bits from two vectors, X and Y, where numerical bit vector representations are of the form  $X = x_{n-1}, x_{n-2}, ..., x_1, x_0$  and  $Y = y_{n-1}, y_{n-2}, ..., y_1, y_0$ , conventional full-adder can be used, which takes in three bits and outputs a sum and a carry bit, so the block adds two bits at a given position with the carry in from the previous bit position. Considering the case of adding two bit vectors, two bits are added at the lowest bit position and the carry is propagated to the next bit position. At the higher positions, two inputs and the carry bit are to be combined and a carry out is generated. This rippling technique of adding two n – bit numbers requires O(n) sequential bit additions, hence a delay of O(n). For the addition of three bit vectors of size n, X, Y and Z, this method can be used to add X and Y, then to add Zto the sum of X + Y; so the total number of bit additions of n shifted copies of an n – bit multiplicand is O(n) where the total delay is  $O(n^2)$ , assuming that the add operations are dependent on the previous ones since the output of earlier operations are inputs to later operations [6].

Even though the result comes from the combination of all operations, a certain amount of independence exists between each operation, considering the addition on a particular column. All the bits in a column must be added together along with the carry in bits coming from the previous column. Carry save addition influences that addition in separate columns can be performed independently. For example, in order to add three vectors of bits, full-adders can be used to perform the addition of three bits in each column. Except the lowest and the highest bit positions, the result is a carry and a sum bit in each bit position. So, the three bit vectors have been reduced to two bit vectors. Using carry save addition technique, a set of vectors, which are to be added together, can be reduced to two bit vectors. Carry save addition is one of the ways to make a multiplication faster than the conventional methods, considering the number of necessary additions.

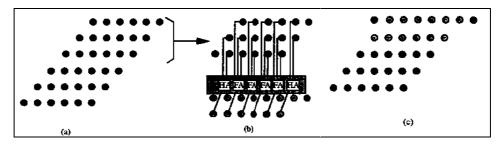

### 2.1.2.1. Array Style Reduction

There are several ways to implement the addition of partial product bits in the trapezoidal array. In this section, the simplest method, called *array partial product reduction*, will be described.

The trapezoidal PPA for a 6 x 6-bit multiplication is given in Fig. 2.3. The first three bit vectors are added using full-adders and the result is then combined with the remaining bits of PPA; thus three vectors are reduced to two vectors. While the trade-off of using slow components is obtaining a slow multiplier, the design benefits from the regularity, simplicity and efficiency it brings to the structure's layout, especially when it is considered that only short wires are needed for the interconnection of vertically, horizontally and diagonally adjacent full-adder cells. Although the delay of this block, which is a function of the number of rows, O(n), is a big improvement over the conventional addition method, it's possible to do better [19].

Figure 2.3 Array partial product reduction: The initial partial product is reduced to two bit vectors by using a row of carry-save adders and the resulting PPA is given [19]

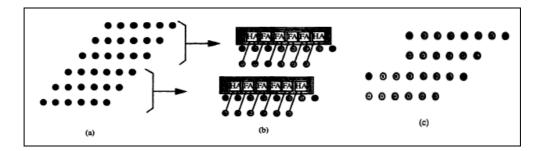

### 2.1.2.2. Wallace Tree Partial Product Reduction

In 1964, C.S. Wallace observed that it is possible to find a structure, which performs the addition operations in parallel; thus resulting in a less delay. In his historic paper, Wallace introduced a different way of parallel addition of the partial product bits using a tree of carry save adders, which is known as "Wallace Tree". In order to

perform the multiplication of two numbers with the Wallace method, partial product matrix is reduced to a two-row matrix by using a carry save adder and the remaining two rows are summed using a fast carry-propagate adder to form the product. Parallelizing carry save operations yields a delay proportional to the logarithm of the operand size n ( $O(\log_{3/2} n)$ ), which is significantly shorter than the array's sequential operations [6]. However, the disadvantage of Wallace trees is their irregular layout with respect to array structures. Moreover, this irregular layout results in greater wire loads. Also it's worth to note that the width of the final adder in a Wallace tree structure is approximately  $2n - \log_{3/2} n$  whereas the width of array architectures uses an adder having a width of n. In Fig 2.4, an example of 6-bit x 6-bit multiplication using Wallace tree partial product reduction method is shown. It can be noticed that parallelizing two carry save operations results in a smaller PPA after just one step [10].

Figure 2.4 Wallace tree partial product reduction [19]

Wallace's method was further refined by Dadda, who suggested an efficient addition of partial products. Dadda presented a concept of a counter structure, which takes a number of bits p in the same bit position (or so called in the same 'weight'), and outputs the number q, representing the count of ones at the input. He introduced various ways of reducing the partial products using such a counter, which is called Dadda's counter. The multiplication process for an 8-bit x 8-bit Dadda's multiplier is shown in Fig. 2.5, where each dot represents one bit product [18].

Figure 2.5 An 8 x 8-bit Dadda multiplier example [10]

In Dadda's multiplier, columns having more than six digits (or having tend to grow more than six digits due to carry bits) are reduced by using half and full-adders. A half adder takes two input digits and outputs one bit in the same column and one in the next more significant column, whereas a full-adder takes three inputs bits and outputs two digits; again one in the same, one in the next column. The arrangement of half and full-adders are done in such a way that no column in the first matrix will have more than six dots. In the second reduction matrix, the maximum number of digits in one column is four. In the coming stages, third matrix contains at most three digits and the fourth matrix has two digits per column. In order to find out the maximum number of digits in one column of the matrix, we start from the final two-row matrix and limit the height of each matrix no more than 1.5 times the height of its successor [10]. The delay of the matrix reduction process is proportional to log(n), since the number of matrices is logarithmically related to the number of bits in the words to be multiplied. In other words, the total delay of the multiplier is proportional to the logarithm of the word size, due to the addition process in the final two-row matrix, which can be implemented using a carry lookahead adder, which also has a logarithmic delay. There has been a great research for making faster parallel multipliers however, the efforts for inventing the fastest counter structure could not go beyond an architecture, which performs the summation of partial products faster than a full-adder [7].

### 2.1.2.3. Partial Product Reduction Using Booth Recoding

One of the best-known variations of the multiplication algorithm is the "Booth's Recoding Algorithm" described by Booth in 1951. The algorithm allows reducing the number of partial products, hence speeding up the multiplication process. The Booth's algorithm can be used for both sign magnitude and unsigned numbers. Before the explanation of Booth's algorithm, brief information about radix multiplication will be presented.

### **Radix multiplication**

For a given range of numbers to be represented, a higher representation radix leads to fewer digits. Thus, a digit at a time multiplication requires fewer cycles as we move to higher radices. That's why, high radix multiplication algorithms are studied for implementing hardware. A k-bit binary number can be formulated as a  $\lceil k/2 \rceil$ -digit radix-4 number and a  $\lceil k/3 \rceil$ -digit radix-8 number and so on. The use of high radix multiplication involves dealing with more than one bit of the multiplier in one cycle. Higher radix multipliers are designed to reduce the number of adders and hence the delay required to compute the partial sums. The best-known method is called *Booth recoding*, which a radix-4 multiplication scheme [9].

#### **Booth recoding technique**

Under certain conditions, when a bit in the multiplier is '0', a bench of carry save adders does not perform a useful function, because a '0' is added to the carry save result. Thus, the input bits are propagated to the output bits. These carry save adders can be removed from the multiplier structure in this case, resulting in power and delay settings. However, since it's not possible to know exactly which bits of the multiplier will be '0', the case, when all the multiplier bits are '1', has to be considered to maintain generality. Furthermore, in the largest delay case, for example in 4 x 4–bit multiplication, circuitry must be provided for the case when the multiplier is '1111', which results in a delay of four stages. Considering that multiplying by '1111' is the same as multiplying by '10000' and subtracting the multiplicand form the result, and knowing that multiplying by a power of two is simply a shift, the worst case delay has been reduced to 2-stages from 4-stages. This type of stage reduction is known as *Booth recoding* [2]. The theory of the Booth algorithm is explained below.

### **Modified Booth algorithm**

Consider two n-bit numbers X and Y to be multiplied. Y can be expressed as:

$$Y = -Y_{n-1}2^{n-1} + Y_{n-2}2^{n-2} + \dots + Y_02^0$$

(2.1)

$$Y = (-2 Y_{n-1} + Y_{n-2} + Y_{n-3}) 2^{n-2} + (-2 Y_{n-3} + Y_{n-4} + Y_{n-5}) 2^{n-4} + \dots + (-2Y_1 + Y_0 + Y_{-1}) 2^0$$

$$(2.2)$$

where  $Y_{-1} = 0$  and  $Y_{n-3}2^{n-2} - 2Y_{n-2}2^{n-4} = Y_{n-3}2^{n-3}$  have been used in the expression. Eq. (2.2) can be represented by

$$Y = \sum_{i=0}^{i=\frac{n}{2}-1} (-2Y_{2i+1} + Y_{2i} + Y_{2i-1}) \cdot 2^{2i} = \sum_{i=0}^{i=\frac{n}{2}-1} y_i \cdot 2^{2i}$$

(2.3)

Thus,

$$X \cdot Y = \left(-X_{n-1}2^{n-1} + \sum_{i=0}^{n-2} X_i \cdot 2^i\right) \left(-Y_{n-1}2^{n-1} + \sum_{j=0}^{n-2} Y_j \cdot 2^j\right)$$

(2.4)

$$X \cdot Y = \left( -X_{n-1} 2^{n-1} + \sum_{i=0}^{n-2} X_i \cdot 2^i \right) \left( \sum_{j=0}^{n-1} y_j \cdot 2^{2j} \right)$$

(2.5)

From the sequence of  $Y_{2i+1}$ ,  $Y_{2i}$  and  $Y_{2i-1}$ ,  $y_i$ , which can be -2, -1, 0, 1, 2 can be known. Therefore, the partial products of n-bit x n-bit multiplication can be reduced to the effective multiplication of n-bit x  $\frac{n}{2}$ -bit multiplication. Thus, the multiplication time is also reduced. The relation between  $Y_{2i+1}$ ,  $Y_{2i}$ ,  $Y_{2i-1}$  and  $y_i$  can be summarized in Table 2.1 and the explanations of the five possible multiples of the multiplicand are given in Table 2.2 [11].

Booth recoding necessitates the internal use of two's complement representation in order to efficiently perform subtraction of the partial products as well as additions. Since it is easy to implement, the algorithm is widely used for two's complement multiplication. The advantage of Booth algorithm is that it generates roughly one half of the partial products when compared to other multiplier implementations, however this benefit comes at the expense of increased hardware complexity.

| $Y_{2i+1}$ | $Y_{2i}$ | $Y_{2i-1}$ | Recoded digit $y_i$ | Operation on X |

|------------|----------|------------|---------------------|----------------|

| 0          | 0        | 0          | 0                   | 0 x X          |

| 0          | 0        | 1          | +1                  | +1 x X         |

| 0          | 1        | 0          | +1                  | +1 x X         |

| 0          | 1        | 1          | +2                  | +2 x X         |

| 1          | 0        | 0          | -2                  | -2 x X         |

| 1          | 0        | 1          | -1                  | -1 x X         |

| 1          | 1        | 0          | -1                  | -1 x X         |

| 1          | 1        | 1          | 0                   | 0 x X          |

Table 2.1 Booth recoding

| Recoded digit | Operation on X                                              |

|---------------|-------------------------------------------------------------|

| 0             | Add 0 to the partial product                                |

| +1            | Add X to the partial product                                |

| +2            | Shift left X one position and add it to the partial product |

| -1            | Add two's complement of X to the partial product            |

| -2            | Take two's complement of X and shift left one position      |

Table 2.2 Explanations of the Booth recoding table

# 2.2 Advanced Structures in Parallel Multipliers

# 2.2.1. Baugh-Wooley Multiplier

The Baugh-Wooley technique was developed to design direct multipliers for two's complement numbers. When multiplying 2's complement numbers directly, each of the partial products to be added is a signed number. Thus, each partial product has to be sign-extended to the width of the final product in order to form the correct sum by the CSA tree. According to the Baugh-Wooley approach, an efficient method of adding extra entries to the bit matrix is suggested to avoid having to deal with the negatively weighted bits in the partial product matrix [1]. In Fig.2.6 and Fig.2.7, PPA's of unsigned and two's complement multiplication of 5 x 5–bits are shown respectively.

|                  |           |           |              |              | $a_4$                 | $a_3$                 | $a_2$        | $a_1$     | $a_0$     |   |

|------------------|-----------|-----------|--------------|--------------|-----------------------|-----------------------|--------------|-----------|-----------|---|

|                  |           |           |              |              | <i>x</i> <sub>4</sub> | <i>x</i> <sub>3</sub> | $x_2$        | $x_1$     | $x_0$     |   |

|                  |           |           |              |              | $a_4 x_0$             | $a_{3}x_{0}$          | $a_{2}x_{0}$ | $a_1 x_0$ | $a_0 x_0$ | - |

|                  |           |           |              | $a_4 x_1$    | $a_{3}x_{1}$          | $a_2 x_1$             | $a_1 x_1$    | $a_0 x_1$ |           |   |

|                  |           |           | $a_4 x_2$    | $a_{3}x_{2}$ | $a_{2}x_{2}$          | $a_1 x_2$             | $a_0 x_2$    |           |           |   |

|                  |           | $a_4 x_3$ | $a_{3}x_{3}$ | $a_{2}x_{3}$ | $a_1 x_3$             | $a_0 x_3$             |              |           |           |   |

|                  | $a_4 x_4$ | $a_3 x_4$ | $a_{2}x_{4}$ | $a_1 x_4$    | $a_0 x_4$             |                       |              |           |           |   |

| $\overline{p_9}$ | $p_8$     | $p_{7}$   | $p_6$        | $p_5$        | $p_4$                 | $p_3$                 | $p_2$        | $p_1$     | $p_0$     | - |

Figure 2.6 Unsigned multiplication

|       |           |               |               |               | $a_4$                 | a3                    | $a_2$        | $a_1$     | $a_0$     |

|-------|-----------|---------------|---------------|---------------|-----------------------|-----------------------|--------------|-----------|-----------|

|       |           |               |               |               | <i>x</i> <sub>4</sub> | <i>x</i> <sub>3</sub> | $x_2$        | $x_1$     | $x_0$     |

|       |           |               |               |               | $-a_{4}x_{0}$         | $a_{3}x_{0}$          | $a_{2}x_{0}$ | $a_1 x_0$ | $a_0 x_0$ |

|       |           |               |               | $-a_{4}x_{1}$ | $a_3 x_1$             | $a_2 x_1$             | $a_1 x_1$    | $a_0 x_1$ |           |

|       |           |               | $-a_{4}x_{2}$ | $a_{3}x_{2}$  | $a_{2}x_{2}$          | $a_1 x_2$             | $a_0 x_2$    |           |           |

|       |           | $-a_{4}x_{3}$ | $a_{3}x_{3}$  | $a_{2}x_{3}$  | $a_1 x_3$             | $a_0 x_3$             |              |           |           |

|       | $a_4 x_4$ | $-a_{3}x_{4}$ | $-a_2x_4$     | $-a_1x_4$     | $-a_0 x_4$            |                       |              |           |           |

| $p_9$ | $p_8$     | $p_7$         | $p_6$         | $p_5$         | $p_4$                 | $p_3$                 | $p_2$        | $p_1$     | $p_0$     |

Figure 2.7 Two's complement multiplication

Here is how the algorithm works. Knowing that the sign bit in two's complement numbers has a negative weight, the entry  $a_4\overline{x}_0$  the term can be written in terms of  $-a_4x_0$ .

$$-a_4 x_0 = a_4 (1 - x_0) - a_4 = a_4 \overline{x}_0 - a_4 \tag{2.6}$$

Hence, the term  $-a_4x_0$  is replaced with  $a_4\overline{x}_0$  and  $-a_4$ . If  $a_4$  is used instead of  $-a_4$ , the column sum increases by  $2a_4$ . Thus,  $-a_4$  must be inserted in the next higher column in order to compensate the effect of  $2a_4$ . The same is done for  $a_4\overline{x}_1$ ,  $a_4\overline{x}_2$ , and  $a_4\overline{x}_3$ . In each column,  $a_4$  and  $-a_4$  cancel each other out. The  $p_8$  column gets a  $-a_4$  entry, which is replaceable by  $\overline{a}_4 - 1$ . This can be repeated for all entries, yielding to the insertion of  $x_4$  in the  $p_4$  column, and  $\overline{x}_4 - 1$  in the  $p_8$  column. There are two -1's in

the eighth column now, which is equivalent to a -1 entry in  $p_9$  and that can be replaced with a 1 and a borrow into the non-existing tenth column.

Baugh-Wooley method increases the height of the longest column by 2, which may lead to a greater delay through the CSA tree. In the given example of Fig. 2.8, column height changes from 5 to 7, requiring an extra CSA level. Removing  $x_4$  from fourth column and writing two  $x_4$  entries in the third column, which has only four entries, can reduce the extra delay caused by the additional CSA level. Thus, the maximum number of entries in one column becomes 6, which can be implemented with three-level CSA tree.

Alternatively, all negatively weighted  $a_4x_i$  terms can be transferred to the bottom row, which leads to two negative numbers in the last two rows, where a subtraction operation from the sum of all the positive elements is necessary. Instead of subtracting  $a_4x$ , two's complement of *a* can be added  $x_4$  times. This method is known as the Modified Baugh-Wooley algorithm [9, 19].

|       |                      |                      |                      |                      | $a_4$                 | $a_3$                 | $a_2$        | $a_1$     | $a_0$     |

|-------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|--------------|-----------|-----------|

|       |                      |                      |                      |                      | <i>x</i> <sub>4</sub> | <i>x</i> <sub>3</sub> | $x_2$        | $x_1$     | $x_0$     |

|       |                      |                      |                      |                      | $a_4 x_0$             | $a_{3}x_{0}$          | $a_{2}x_{0}$ | $a_1 x_0$ | $a_0 x_0$ |

|       |                      |                      |                      | $a_4 \overline{x_1}$ | $a_{3}x_{1}$          | $a_{2}x_{1}$          | $a_1 x_1$    | $a_0 x_1$ |           |

|       |                      |                      | $a_4 \overline{x_2}$ | $a_{3}x_{2}$         | $a_{2}x_{2}$          | $a_1 x_2$             | $a_0 x_2$    |           |           |

|       |                      | $a_4 \overline{x_3}$ | $a_{3}x_{3}$         | $a_{2}x_{3}$         | $a_1 x_3$             | $a_0 x_3$             |              |           |           |

|       | $a_4 \overline{x_4}$ | $a_3 \overline{x_4}$ | $a_{2}x_{4}$         | $a_1 \overline{x_4}$ | $a_0 \overline{x_4}$  |                       |              |           |           |

|       | $a_4$                |                      |                      |                      | $a_4$                 |                       |              |           |           |

| 1     | $\overline{x_4}$     |                      |                      |                      | <i>x</i> <sub>4</sub> |                       |              |           |           |

| $p_9$ | $p_8$                | $p_7$                | $p_6$                | $p_5$                | $p_4$                 | $p_3$                 | $p_2$        | $p_1$     | $p_0$     |

Figure 2.8 Baugh-Wooley two's complement multiplication

|       |           |              |              |                      | $a_4$                 | a3                                   | $a_2$     | $a_1$     | $a_0$      |

|-------|-----------|--------------|--------------|----------------------|-----------------------|--------------------------------------|-----------|-----------|------------|

|       |           |              |              |                      | <i>x</i> <sub>4</sub> | <i>x</i> <sub>3</sub>                | $x_2$     | $x_1$     | <i>x</i> 0 |

|       |           |              |              |                      | $\overline{a_4 x_0}$  | <i>a</i> <sub>3</sub> x <sub>0</sub> | $a_2 x_0$ | $a_1 x_0$ | $a_0 x_0$  |

|       |           |              |              | $\overline{a_4 x_1}$ |                       | $a_2 x_1$                            |           |           |            |

|       |           |              | $a_4 x_2$    | $a_{3}x_{2}$         | $a_{2}x_{2}$          | $a_1 x_2$                            | $a_0 x_2$ |           |            |

|       |           | $a_{4}x_{3}$ | $a_3 x_3$    | $a_2 x_3$            | $a_1x_3$              | $a_0 x_3$                            |           |           |            |

|       | $a_4 x_4$ | $a_3 x_4$    | $a_{2}x_{4}$ | $a_1 x_4$            | $a_0 x_4$             |                                      |           |           |            |

| 1     |           |              |              | 1                    |                       |                                      |           |           |            |

| $p_9$ | $p_8$     | $p_{7}$      | $p_6$        | $p_5$                | $p_4$                 | $p_3$                                | $p_2$     | $p_1$     | $p_0$      |

Figure 2.9 Modified Baugh-Wooley two's complement multiplication

Modified form of the Baugh-Wooley method, shown in Fig. 2.9, is more preferable since it does not increase the height of the columns in the matrix. However, this type of multiplier is suitable for applications where operands with less than 16 bits are processed, like digital filters where small operands like 6, 8 or 12 bits are used. Baugh-Wooley scheme becomes slow and area consuming when operands are greater than or equal to 16-bits. So, different techniques are required in order to reduce the size of the array as well as maintaining the regularity.

### 2.2.2. 4:2 Compressor

In the '4-2 carry save module' structure, which is introduced by Weinberger in 1981, a complicated-interconnected combination of full-adder cells exist for performing the compression of partial products faster than counters. In fact, the structure compresses five partial product bits (four input bits and one carry–in bit) into three, however it acts as a compressor reducing the four bits into two, since carry-in and carry-out bits connect the adjacent 4:2 compressors [13]. Thus, the number of partial product bits is reduced by half in one stage, making the efficiency higher. The structure of 4:2 compressors is shown in Fig. 2.10.

Figure 2.10 4-to-2 compressor

Figure 2.11 Logic diagram of the 4-to-2 compressor (4W) unit

In the arrangement shown in Fig. 2.10, sum can be obtained via four XOR gate delays

$$S = \left[ \left[ \left( X_1 \oplus X_2 \right) \oplus X_3 \right] \oplus X_4 \right] \oplus C_{in}$$

(2.7)

which is identical to the result in the Wallace tree structure using 2-layer carry save adders, thus the equation can be rearranged as

$$S = \left[ \left( X_1 \oplus X_2 \right) \oplus \left( X_4 \oplus C_{in} \right) \right] \oplus C_{in}$$

(2.8)

In the circuit shown with Fig.2.11, the equations are obtained to be

$$C_{out} = I_1 \cdot I_2 + I_3 \cdot I_4$$

(2.9)

$$S = \left(I_1 I_2 + \overline{I_1} \overline{I_2}\right) \oplus \left(I_3 I_4 + \overline{I_3} \overline{I_4}\right) \oplus C_{in}$$

(2.10)

$$C = I_1 \cdot I_2 \cdot I_3 \cdot I_4 + (I_3 \oplus I_2) \cdot (I_3 \oplus I_4) + [(I_1 \oplus I_2) \oplus (I_3 \oplus I_4)] C_{in}$$

(2.11)

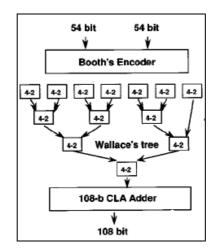

### 2.2.3. Hitachi's Multiplier

One of the best-performance multipliers, proposed by Ohkubo and Suzuki [13], is a 0.25µm 54 x 54-bit multiplier with an operation time of 4.4ns. The architecture consists of blocks performing Wallace tree and Booth's algorithms as well as a carry-lookahead adder, which is shown in Fig. 2.12. Booth's algorithm is used in order to save from chip area instead of reducing delay time, and by using Wallace tree operation time reduction is performed. Moreover, for further improvement, a new 4:2 compressor type is developed with pass transistor multiplexers so that critical path gate stages are reduced. This yields to reduction in the multiplication time of the multiplier by 14% [11].

Figure 2.12 Organization of Hitachi's multiplier [13]

# 2.2.4. Inoue's Multiplier

Among recently designed multipliers, the one published by Inoue [16] is one of the fastest. The novelty of this multiplier is the new design of the Booth encoder and Booth selector blocks for the generation of partial products, and the 4:2 compression unit. A simpler implementation of these blocks removes the need to use an XOR gate in the critical path. The regular Booth selector requires 18 transistors per bit for the implementation where the modified Booth selector necessitates 10 transistors per bit. Although for the 54-bit x 54-bit multiplier modification of the Booth selector yields 44% reduction in the transistor count, this modification does not give a significant change by means of transistor count in the overall multiplier, since the number of transistors that the Booth encoder consists of is approximately 1.2% of total architecture.

In his paper [16], Inoue observed the possible  $2^6$  implementations of the 4:2 compressor and among them he chose the one, which has the minimum number of transistors. Reducing the transistor count by 24% not only saves from layout area but also reduces the speed of the multiplier, approximately by 5% of the fastest possible implementation.

# 2.3. Multiplier Power Reduction

The design of digital CMOS has focused on delay reduction and power dissipation. In multipliers, delay increases as the size of the multiplier grows in terms of bits, but it can vary depending on the implementation. Power is proportional to the amount of circuitry of the multiplier and the way that it is connected to perform the multiplication. Since the amount of adder blocks is proportional to the square of the size of the number of bits  $(n^2)$ , multipliers tend to be fairly large, power consuming blocks.

Dynamic power consumption of digital CMOS circuits is expressed by Eq. (2.12). Static power consumption is neglected because which is relatively too small. The static power comes from the pull-up resistor. This would mean that in complementary CMOS circuits, only one device is conducting at a time. So, there's no need to calculate static power; only dynamic power exists since there is never a direct path between  $V_{DD}$  and GND in steady state.

$$P_{dyn} = V_{DD}^{2} f_{op} \sum_{n} \alpha_{n} C_{n} + V_{DD} \sum_{n} i_{sc}$$

(2.12)

n being the number of nodes and alpha is the number of switching activities. An equivalent equation can be expressed as

$$P_{dyn} = C_L V_{DD}^{2} f_{op} + t_{sc} V_{DD} I_{peak} f_{op} + V_{DD} I_{leakage}$$

(2.13)

In this equation,  $I_{peak}$  determined by the saturation current of the pmos and nmos transistors, which depend on their sizes, process technology, temperature, etc. and the ratio between input and output slopes. When load capacitance is small, power is dominated by Isc, short circuit current. Isc is less than 10% of total dynamic current under the condition of fast rising time and falling time. Therefore short circuit current is neglected for convenience of calculation. Because supply voltage and operation frequency are fixed when the application is specified, the power consumption is determined by node capacitance and transition activities (probability). In considering these two parameters, equivalent capacitance is defined in Eq (2.14). Using the principle of uniform distribution of delay time, the equivalent capacitance can be expressed as the driving load (C<sub>L</sub>). If it is only driving a capacitive load, then we can approximate that all the power is consumed in the act of switching. It is nontrivial to calculate the power via the resistance of the on transistor so use the output capacitance.

$$P_{dyn} = C_L \ V_{DD}^{\ 2} f_{op} \tag{2.14}$$

Typically, power and delay minimization techniques focus on the various subblocks inside a larger block and address power optimization of these blocks independently. However, an integrated approach may be more helpful since dependency of these blocks affect the overall power characteristics.

## 2.3.1. Logic Level Multiplier Optimization

Booth recoding suffers from the problem that unequal delay paths exist in the Booth partial product generator. One path goes from the multiplier through the Booth encoder and then to the Booth decoder, while paths from the multiplicand go directly to the Booth decoder. Since the Booth decoder is composed of two gates a glitch can result at the output of the Booth decoder due to this greater delay. One approach is to redesign the Booth encoder/decoders such that Booth encoder's logic depth is reduced and early arriving signal coming from the multiplicand has a greater delay through the decoder that inputs from the encoder. This balances the signal paths and allows reducing of glitches [2].

# 2.4. Multipliers' Comparison

In this chapter, we presented recently developed various multiplication algorithms. Generally, it is not possible to say that an exact architecture yields to greater cost-effectiveness, since the trade-off is design and technology dependent. The basic array multipliers, like the Baugh-Wooley scheme, consume low power and exhibit relatively good performances, however their use is limited with 16 bits. For operands of 16-bits and over, the modified Booth algorithm reduces the partial product's numbers by half. Thus, the speed of the multiplier is reduced. Due to the circuitry overhead in the Booth algorithm, its power dissipation is comparable to the Baugh-Wooley multiplier. Wallace's strategy for building carry save adder (CSA) trees is to combine the partial product bits as early as possible, whereas in Dadda's method, combination of partial products is performed at the latest stage. This method yields to a simpler CSA tree and a wider carry-propagate adder while the designs using Wallace's method are the fastest ones. However, a logarithmic depth reduction tree based on CSA's has an irregular structure that makes the design and layout more difficult. Moreover, connections and signal paths of varying lengths may lead to logical hazards and signal skew that have implications for both performance and power consumption. That's why; alternative reduction trees that are more suitable for VLSI implementation are of interest. A summary of pros and cons of the proposed algorithms, based on their theoretical attributes, is given below in Table 2.3 in terms of speed, circuit complexity, layout regularity and silicon area. A detailed simulation-based analysis of the algorithms, for both small-size and large-size multiplier blocks, will be presented in section 4.4. In the next chapter, we will introduce another multiplication algorithm called multiplexer based multiplication, which has both high-speed and low-power opportunity.

| Multiplier Type | Speed        | <b>Circuit Complexity</b> | Layout            | Area     |

|-----------------|--------------|---------------------------|-------------------|----------|

| Array           | Low / Medium | Simple                    | Regular           | Smallest |

| Booth           | High         | Complex                   | Irregular         | Medium   |

| Wallace         | Higher       | Medium                    | More irregular    | Large    |

| Dadda           | Higher       | Medium                    | Irregular         | Medium   |

| Hitachi         | Highest      | More complex              | Medium regularity | Largest  |

| Inoue           | Highest      | More complex              | Irregular         | Largest  |

Table 2.3 Pros and cons table for various multiplication algorithms

# **3. MULTIPLEXER BASED MULTIPLICATION**

In this chapter, a new multiplication technique, based on the synchronous computation of the partial sums of the operands, which is proposed by K.Z. Pekmestzi [15], is explained as an alternative to conservative multiplication methods. The algorithm is a different version of effective parallel multiplication, so one bit of the multiplier and the multiplicand are processed in each step. The multiplicand and the multiplier are interchangeable since the algorithm is symmetric. Parallel implementation of the algorithm results in a smaller circuit by means of area and it provides faster addition of partial products. Thus, its circuitry complexity is almost the same as the implementations based on Modified Booth's algorithm, but the multiplication time is considerably faster. These advantages are valid for both positive numbers and numbers in two's complement form.

# **3.1 Introduction to Algorithm**

Consider the multiplication of two n-bit numbers X and Y, where

$$X = x_{n-1} x_{n-2} \dots x_2 x_1 x_0 = \sum_{j=0}^{n-1} x_j 2^j$$

(3.1)

$$Y = y_{n-1}y_{n-2}\dots y_2 y_1 y_0 = \sum_{j=0}^{n-1} y_j 2^j$$

(3.2)

As derived in [15], based on these two equalities, the numbers  $X_{n-1}$  and  $Y_{n-1}$  can be defined as

$$X_{n-1} = x_{n-2}x_{n-3}\dots x_2 x_1 x_0 = \sum_{j=0}^{n-2} x_j 2^j \text{ and } X = X_{n-1} + 2^{n-1} x_{n-1}$$

(3.3)

$$Y_{n-1} = y_{n-2}y_{n-3}\dots y_2y_1y_0 = \sum_{j=0}^{n-2} y_j 2^j \text{ and } Y = Y_{n-1} + 2^{n-1}y_{n-1}$$

(3.4)

Thus, the product P of X and Y can be written as

$$P = X \cdot Y \tag{3.5}$$