# POWER AMPLIFIER IMPROVEMENT TECHNIQUES/CIRCUITS IN 0.35 MICRON SIGE HBT TECHNOLOGY FOR 5 GHz WIRELESS LAN BAND

by CANAN KAVLAK

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfillment of the requirements for the degree of Master of Science

> Sabanci University August, 2006

# POWER AMPLIFIER IMPROVEMENT TECHNIQUES/CIRCUITS IN 0.35 MICRON SiGe HBT TECHNOLOGY FOR 5 GHz WIRELESS LAN BAND

APPROVED BY:

| Assist. Prof. İbrahim TEKİN<br>(Dissertation Supervisor) |                    |

|----------------------------------------------------------|--------------------|

| Assist. Prof. Ayhan BOZKURT                              |                    |

| Fatih ÜSTÜNER, PhD<br>(Chief Scientist, EMC Section Lead | er, TÜBİTAK-UEKAE) |

| Assist. Prof. Mehmet KESKİNÖZ                            |                    |

| Assoc. Prof. Yaşar GÜRBÜZ                                |                    |

|                                                          |                    |

DATE OF APPROVAL:

© Canan KAVLAK 2006

All Rights Reserved

# POWER AMPLIFIER IMPROVEMENT TECHNIQUES/CIRCUITS IN 0.35 MICRON SIGE HBT TECHNOLOGY FOR 5 GHz WIRELESS LAN BAND

Canan KAVLAK

EECS, MS Thesis, 2006

Thesis Supervisor: Assist. Prof. Dr. İbrahim Tekin

Keywords: IEEE, 802.11a, WLAN, RF IC, SiGe, BiCMOS, HBT, power amplifier,

Wilkinson power combiner

#### Abstract

In this thesis, a 5 GHz radio frequency power amplifier for IEEE 802.11a WLAN applications is designed, the ideas of on-chip power combining and using transmission lines as an RF on-chip choke are tested and layouts are drawn. The power amplifier employs SiGe HBT's in AMS 0.35 µm BiCMOS process and it is designed to operate in Class A mode with a supply voltage of 3 Volts. Since the power amplifier is the final block and the final amplification stage of the transmitter chain in a wireless system, it must produce enough RF power to overcome the channel losses. At the same time, the power produced by the power amplifier should obey the power levels dictated by the operating standard. Therefore, in this work much consideration is given to design a power amplifier which provides enough output power for IEEE 802.11a WLAN standard. The power amplifier is designed to operate in Class A, and the bias points are chosen accordingly in order to preserve linearity. After the design of a single stage power amplifier, different versions of the circuit are designed and layouts are drawn. To decrease the dye area and the parasitic losses, the inductor which is used as the RF choke is replaced with capacitively loaded transmission lines. Moreover, in order to improve the linearity and obtain higher output power levels, two single stage power amplifiers are combined via on-chip Wilkinson power combiner made of lumped elements. Simulations are performed in ADS and Cadence environments in a parallel fashion

# 0.35 MİKRON SiGe HBT TEKNOLOJİSİ İLE, 5 GHz KABLOSUZ İLETİŞİM BANDINDA GUÇ AMFİSİ GELİŞTİRME TEKNİKLERİ VE DEVRELERİ

Canan KAVLAK

EECS, Yükseklisans Tezi, 2006

Tez Danışmanı: Yrd. Doç. Dr. İbrahim Tekin

## Anahtar Kelimeler: IEEE, 802.11a, WLAN, RF IC, SiGe BiCMOS, HBT, güç

kuvvetlendiricisi, Wilkinson güç birleştiricisi

### Özet

Bu tezde, 802.11a WLAN uygulamaları için yüksek frekans bir güç kuvvetlendiricisi AMS'in 0.35 µm SiGe BiCMOS teknolojisiyle 5 GHz frekansinda tasarlanmış ve serimi yapılmıştır. Bunun yanında, tümleşik güç birleştirici yöntemi ve iletim hattını tümleşik endüktans olarak kullanma fikri test edilmiştir. Bu güç kuvvetlendiricisi tasarımında AMS'in 0.35 µm BiCMOS prosesinde bulunan SiGe HBT'ler ver alıp, kuvvetlendirici 3 Volt kaynak voltajı ile Sınıf A'da çalışacak şekilde tasarlanmıştır. Güç kuvvetlendiricisi, gönderici hattındaki son yükseltici blok olduğu için, kanal kayıplarını aşabilmek için yeterli miktarda yüksek frekans çıkış gücü oluşturabilmelidir. Aynı zamanda, üretilen çıkış gücü, çalıştırma standardının öngördüğü çıkış gücü seviyelerini aşmamalıdır. Bu sebepten dolayı, bu çalışmada IEEE 802.11a standardı için yeterli seviyelerde güç üretebilen bir kuvvetlendirici tasarlamaya özen gösterilmiştir. Sınıf A'da çalıştırılmak üzere tasarlanan güç kuvvetlendiricisinin kutuplama noktalari bu doğrultuda seçilmiş ve doğrusallık korunmuştur. Tek sıralı güç kuvvetlendiricisi tasarlandıktan sonra, aynı devrenin değişik versiyonları tasarlanıp test edilmiştir. Kırmık boyutunu küçültmek ve parazitik kayıpları azaltmak için, RF choke görevi gören endüktans devreden çıkartılıp yerine kapasitif yüklenmiş iletim hattı yerleştirilmiştir. Doğrusallığı ve çıkış gücünü arttırmak içinse, iki tek sıralı güç kuvvetlendiricisi tümleşik Wilkinson güç birleştiricisi ile birleştirilmiştir. Simülasyonlar ADS ve Cadence ortamlarında es zamanlı olarak yapılmıştır.

#### ACKNOWLEDGEMENTS

First and foremost I would like to thank my thesis supervisor Asst. Prof. İbrahim Tekin for his guidance, support and for keeping me motivated all the time. It was a great honor for me to have the chance to work with him for two years. I certainly could not come this far without his assistance. Moreover, I appreciate his patience and encouragement during the long laboratory hours.

I also specially thank Asst. Prof. Ayhan Bozkurt and Assoc. Prof. Yaşar Gürbüz for their help in answering my questions. I would also like to thank my dissertation members, Asst. Prof. Mehmet Keskinöz and Dr. Fatih Üstüner for spending their invaluable time to review my thesis.

Next, I would like to thank my friends in my research group, Mehmet Kaynak, Onur Esame, Arzu Ergintav and Nilüfer Tonga for their invaluable assistance throughout the preparation of my dissertation. Several people outside my research group were also of great assistance to me, including Yalçın Yamaner and Ülkühan Güler. With their friendship, I overcame this process with much enjoyment and great moral support.

Last but not least, I would like to thank my family for their endless support in every step I take. With their unconditional love and moral support, I accomplished this dissertation.

# **TABLE OF CONTENTS**

| 1 | INTR | ODUCTION1                                                            |

|---|------|----------------------------------------------------------------------|

| 2 | BAC  | GROUND4                                                              |

|   | 2.1  | IEEE WLAN 802.11a Standard Specifications4                           |

|   | 2.2  | Architecture of an IEEE 802.11a WLAN Transceiver                     |

|   | 2.3  | Power Amplifier Background10                                         |

|   |      | 2.3.1 Introduction                                                   |

|   |      | 2.3.2 Power Amplifier Performance Parameters                         |

|   |      | 2.3.3 Power Amplifier Classes                                        |

| 3 | PA D | ESIGN METHODOLOGY                                                    |

|   | 3.1  | Design Roadmap                                                       |

|   | 3.2  | Device I-V curves                                                    |

|   | 3.3  | Load Pull                                                            |

|   | 3.4  | Matching Network Design                                              |

|   |      | 3.4.1 Output Matching                                                |

|   |      | 3.4.2 Input Matching                                                 |

|   | 3.5  | Overall Class A Single Stage PA Schematic                            |

|   | 3.6  | Wilkinson Power Combiner/Splitter Design                             |

|   | 3.7  | Microstrip Line/Coplanar Waveguide Equivalent Model of RF Choke . 40 |

|   |      | 3.7.1 Theoretical Foundation                                         |

|   |      | 3.7.2 Capacitively Loaded Microstrip Line Example                    |

|   |      | 3.7.3 Capacitively Loaded CPW Example                                |

| 4 | NUM  | ERICAL RESULTS                                                       |

|   | 4.1  | Introduction                                                         |

|   | 4.2  | Single Stage PA Performance Analyzes                                 |

|   |      | 4.2.1 Cadence Simulation Results                                     |

|   |      | 4.2.2 Final Schematic and Layout                                     |

|   |      | 4.2.3 WLAN 802.11a Spectrum Measurements                             |

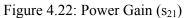

|   | 4.3  | Wilkinson Power Combined PA Topology                                 |

|      | 4.4   | RF Choke Alternative (Transmission Line Structures) |  |

|------|-------|-----------------------------------------------------|--|

| 5    | CON   | CLUSIONS AND FUTURE WORK                            |  |

| REFE | ERENC | ES                                                  |  |

| APPE | ENDIX |                                                     |  |

|      | Appe  | ndix A                                              |  |

|      | Appe  | ndix B                                              |  |

# LIST OF FIGURES

| Figure 2.1: OFDM PHY frequency channel plan for the United States                 | 6    |

|-----------------------------------------------------------------------------------|------|

| Figure 2.2: Transmit spectrum mask                                                | 8    |

| Figure 2.3: Block diagram of an IEEE 802.11a transmitter                          | 9    |

| Figure 2.4: Block diagram of an IEEE 802.11a receiver                             | 9    |

| Figure 2.5: Block diagram of an RF transceiver                                    | 10   |

| Figure 2.6: Basic topology of a power amplifier                                   | 11   |

| Figure 2.7: 1 dB compression characteristics                                      | 13   |

| Figure 2.8: Corruption of the desired signal due to nearby interferers            | 14   |

| Figure 2.9: Third Order Intercept Point                                           | 14   |

| Figure 2.10: Error Vector Magnitude representation                                | 15   |

| Figure 2.11: General power amplifier model                                        | 16   |

| Figure 2.12: I-V characteristics of a transistor                                  | 17   |

| Figure 2.13: Class A Optimal Bias Point                                           | 18   |

| Figure 2.14: Q point of Class A, AB, B and C PAs                                  | 19   |

| Figure 2.15: Summary of Class A, AB, B and C conduction angles                    | 20   |

| Figure 2.16: Maximum theoretical efficiency of an ideal amplifier as a function   | n of |

| conduction angle                                                                  | 21   |

| Figure 2.17: Class E amplifier                                                    | 22   |

| Figure 2.18: Class F amplifier                                                    | 22   |

| Figure 3.1: PA design roadmap                                                     | 24   |

| Figure 3.2: This circuit generates I-V curves and computes optimal bias for Class | s A  |

| operation                                                                         | 25   |

| Figure 3.3: Transistor I-V curves                                                 | 26   |

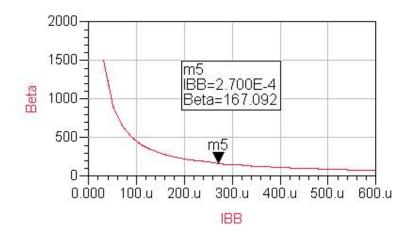

| Figure 3.4: Beta versus IBB at ICE which is specified by the marker m1            | 26   |

| Figure 3.5: Load Pull Setup in ADS                                                | 29   |

| Figure 3.6: Maximum PAE and Pout circles on the Smith Chart                       | 29   |

| Figure 3.7: Simulated load impedances                                             | 30   |

| Figure 3.8: Output matching network design using ADS Smith Chart utility          | 31   |

| Figure 3.9: Output matching network                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------|

| Figure 3.10: Input matching network design using ADS Smith Chart utility                                                  |

| Figure 3.11: Input matching network                                                                                       |

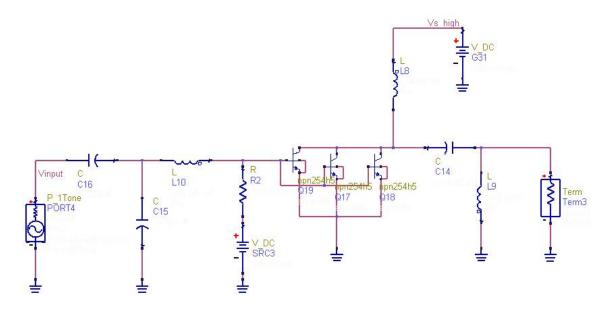

| Figure 3.12: Class A PA schematic with ideal elements in ADS                                                              |

| Figure 3.13: Single stage Class A output power and 1 dB compression point                                                 |

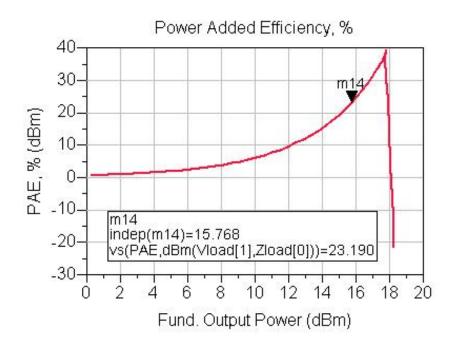

| Figure 3.14: Single stage Class A PAE curve                                                                               |

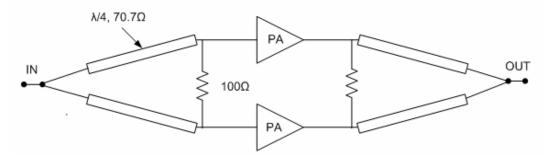

| Figure 3.15: In-phase power combining using Wilkinson power combiners                                                     |

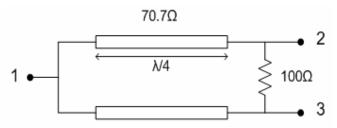

| Figure 3.16: Microstrip Wilkinson combiner                                                                                |

| Figure 3.17: "Pi" LC network model of a quarter wavelength transmission line                                              |

| Figure 3.18: Lumped element Equal split Wilkinson power divider at 5GHz center                                            |

| frequency                                                                                                                 |

| Figure 3.19: Simulated s <sub>11</sub> , s <sub>21</sub> and s <sub>31</sub> parameters of lumped element Wilkinson power |

| splitter model                                                                                                            |

| Figure 3.20: Short circuited transmission line                                                                            |

| Figure 3.21: Input impedance versus length                                                                                |

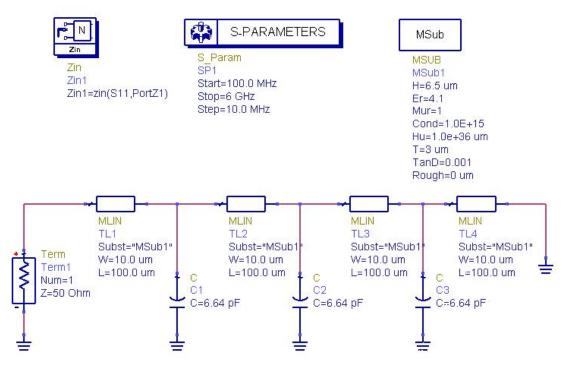

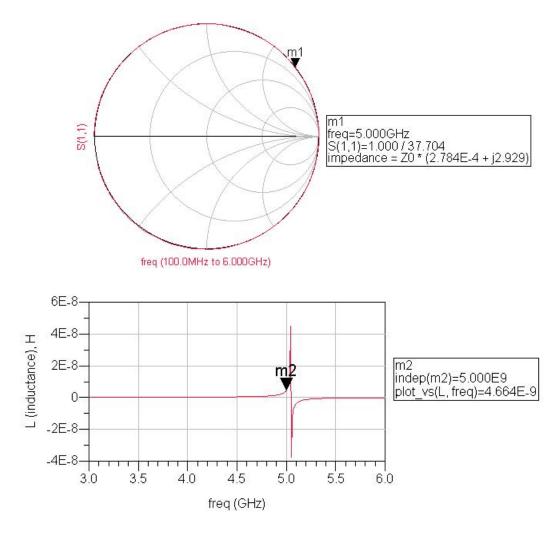

| Figure 3.22: Capacitively loaded microstrip line model                                                                    |

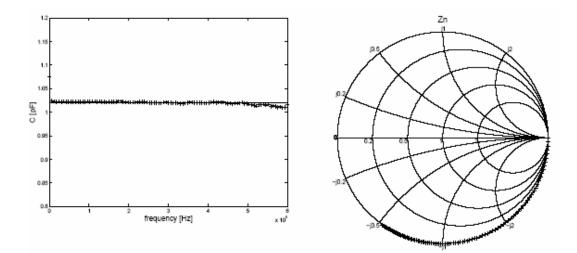

| Figure 3.23: Inductance of capacitively loaded microstrip line model                                                      |

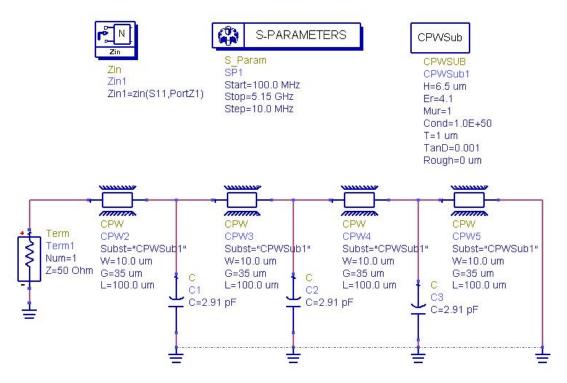

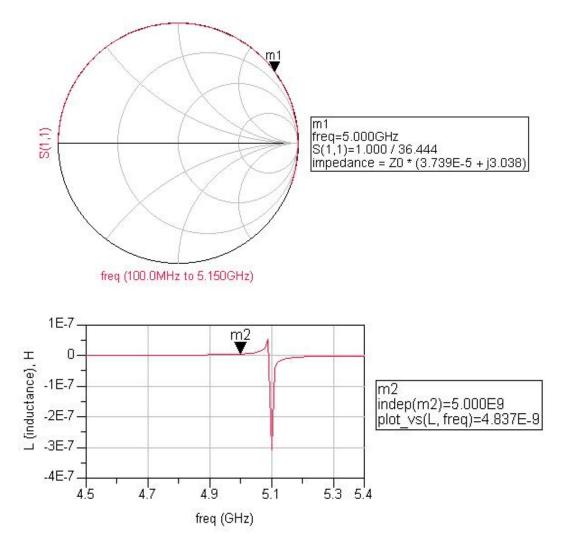

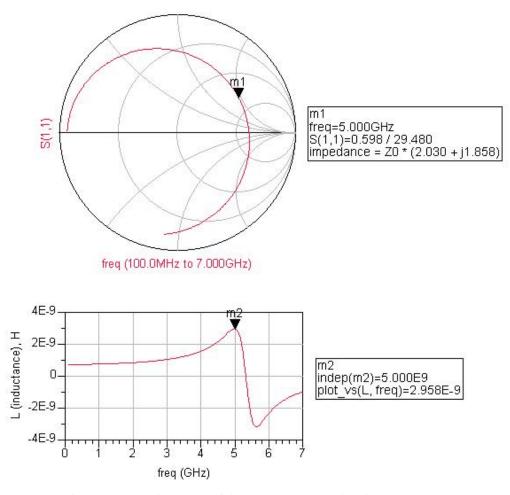

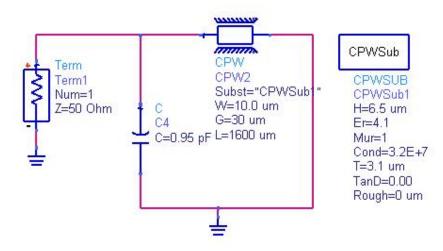

| Figure 3.24: Capacitively loaded coplanar waveguide model                                                                 |

| Figure 3.25: Inductance of capacitively loaded coplanar waveguide model                                                   |

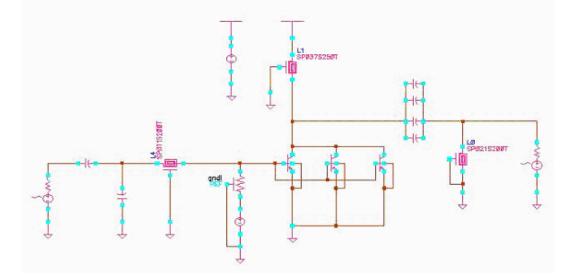

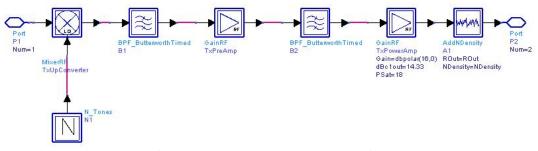

| Figure 4.1: Simulation setup of single stage PA circuit                                                                   |

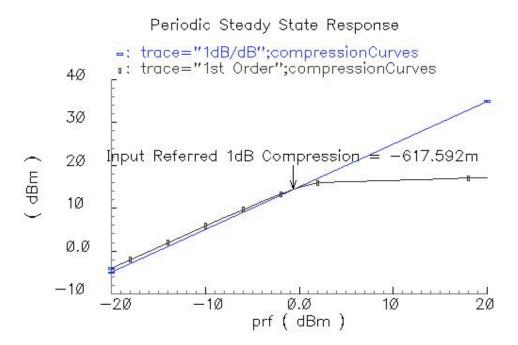

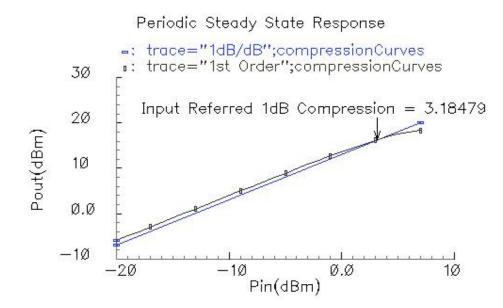

| Figure 4.2: Input referred 1 dB compression point (Gain=14.95 dB at 1 dB compression                                      |

| point)                                                                                                                    |

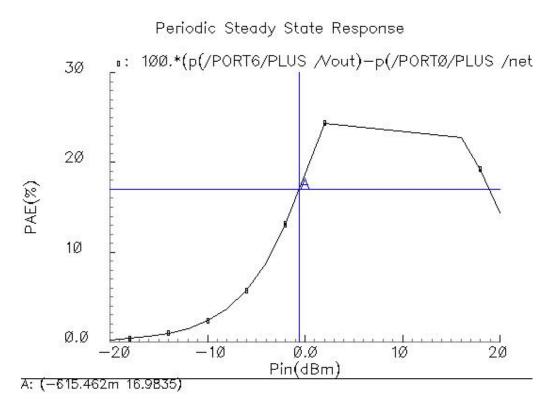

| Figure 4.3: Power Added Efficiency (PAE)                                                                                  |

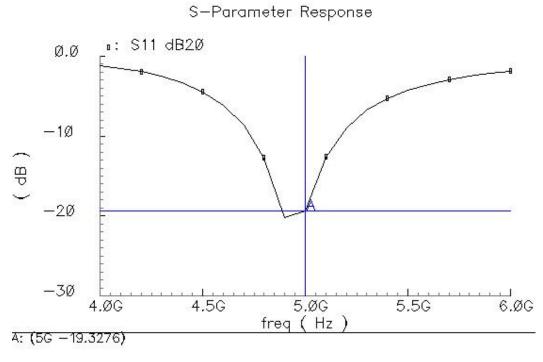

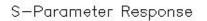

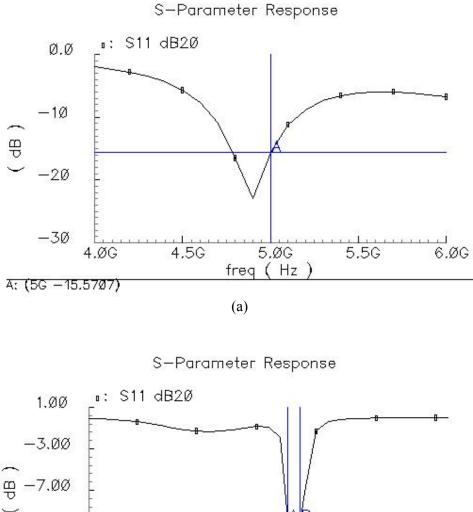

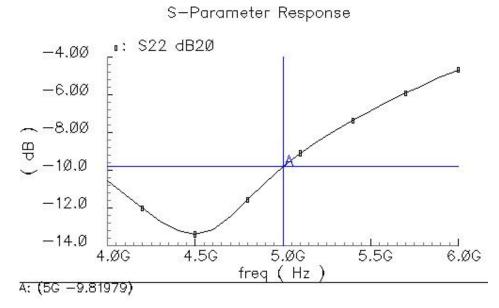

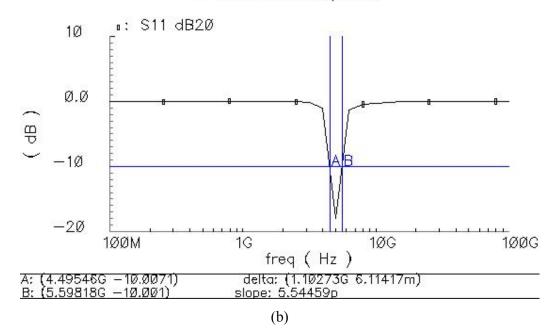

| Figure 4.4: (a) $s_{11}$ response (b) frequency bandwidth in which $s_{11}$ drops below -10 dB 52                         |

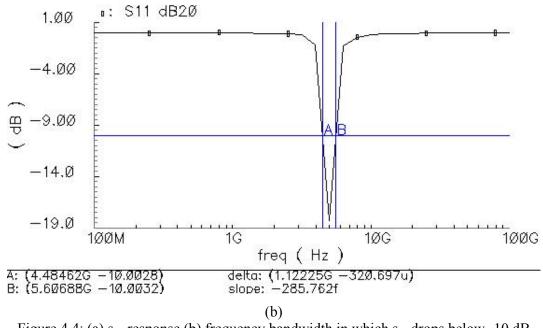

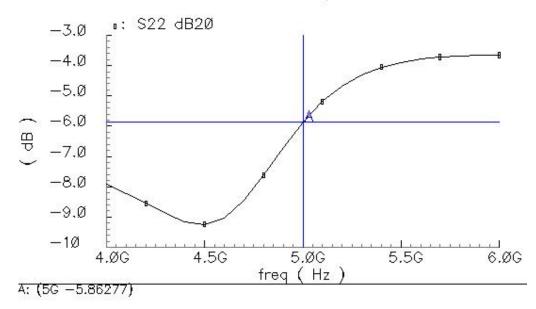

| Figure 4.5: s <sub>22</sub> response                                                                                      |

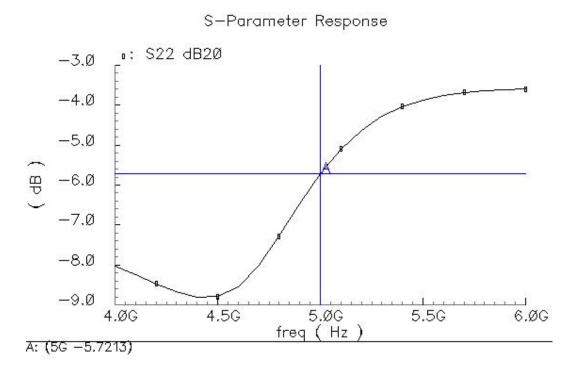

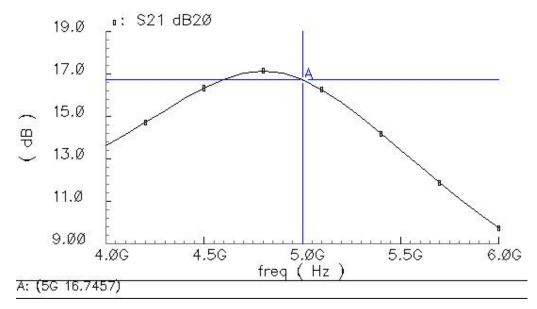

| Figure 4.6: Power gain                                                                                                    |

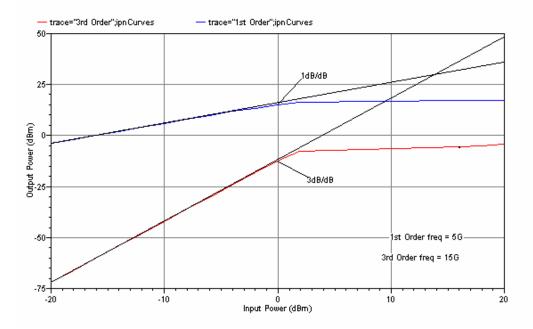

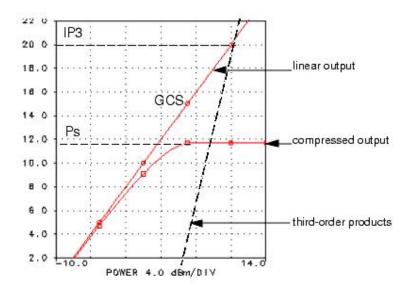

| Figure 4.7: Third Order Intercept point                                                                                   |

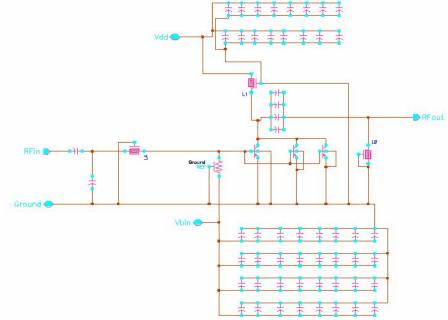

| Figure 4.8: Final schematic of single stage PA                                                                            |

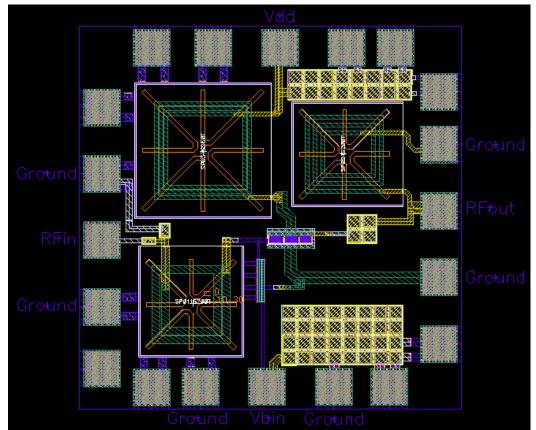

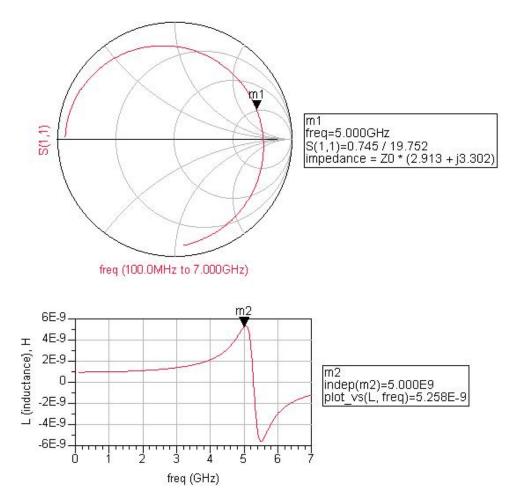

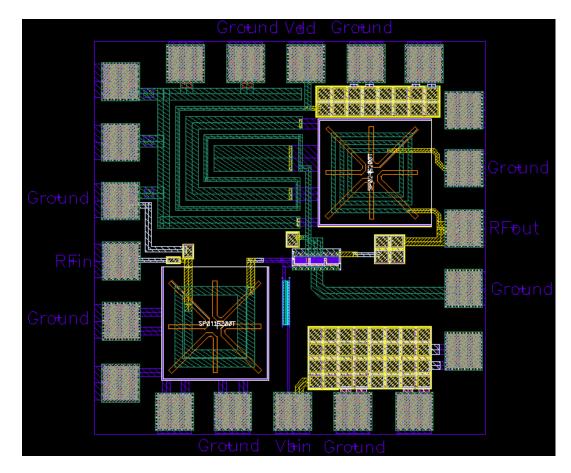

| Figure 4.9: Layout of the single stage PA                                                                                 |

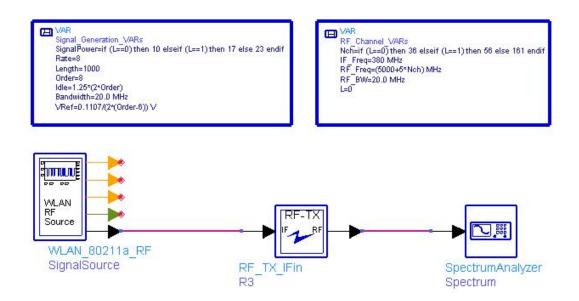

| Figure 4.10: WLAN 802.11a spectrum measurement setup                                                                      |

| Figure 4.11: WLAN 802.11a transmitter                                                                                     |

| Figure 4.12: Important PA metrics                                                                                         |

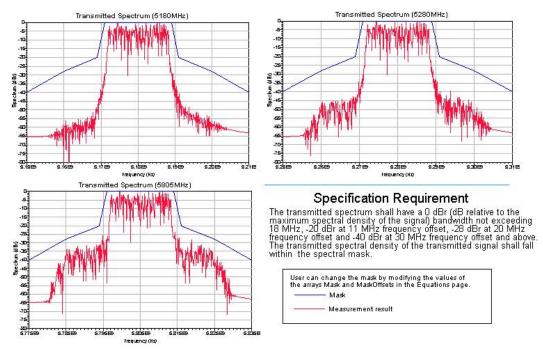

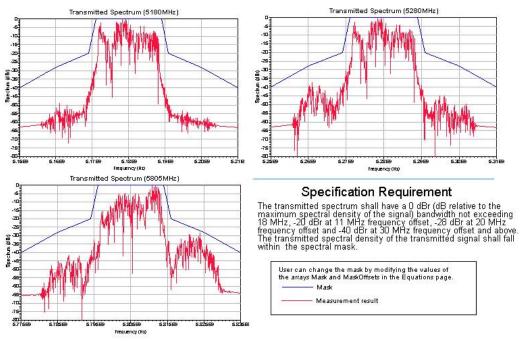

| Figure 4.13: 802.11a transmit spectrum mask measurement results for three different                                       |

| frequency bands of 802.11a standard                                                                                       |

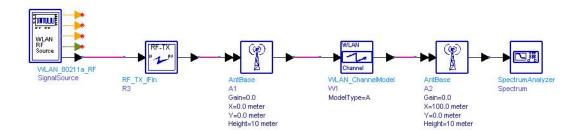

| Figure 4.14: ADS setup for the IEEE 802.11a transmit RF spectrum measurements in                            |

|-------------------------------------------------------------------------------------------------------------|

| the presence of WLAN channel model A                                                                        |

| Figure 4.15: 802.11a transmit spectrum mask measurement results in the presence of                          |

| WLAN channel model A                                                                                        |

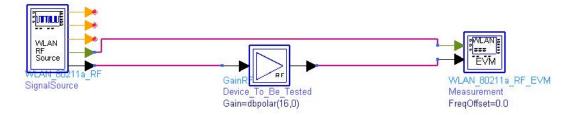

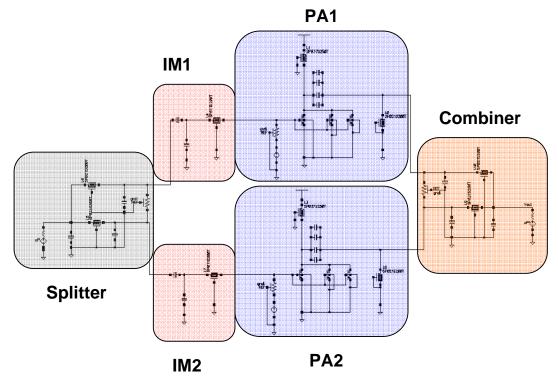

| Figure 4.16: ADS setup for the IEEE 802.11a PA EVM measurements                                             |

| Figure 4.17: PA EVM measurement results                                                                     |

| Figure 4.18: Combined power amplifier                                                                       |

| Figure 4.19: Input referred 1 dB compression point (Gain=13 dB at 1 dB compression                          |

| point)                                                                                                      |

| Figure 4.20: (a) $s_{11}$ response (b) $s_{11}$ in a logarithmic scale ( $s_{11}$ is below -10 between 4.59 |

| - 5.79 GHz bandwidth)                                                                                       |

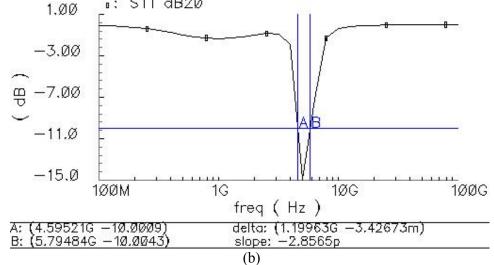

| Figure 4.21: s <sub>22</sub> response                                                                       |

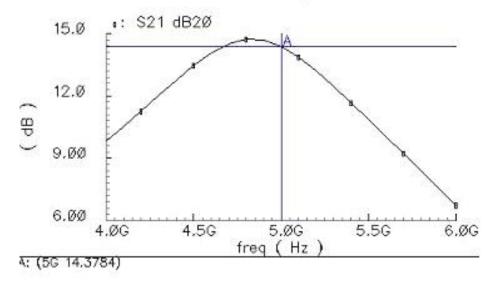

| Figure 4.22: Power Gain (s <sub>21</sub> )                                                                  |

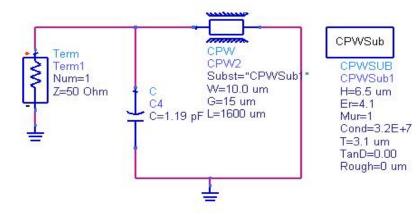

| Figure 4.23: Cadence test setup for testing the CPW structure                                               |

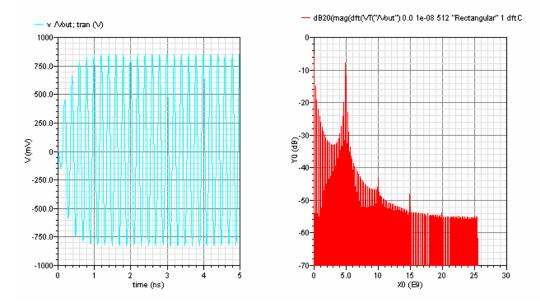

| Figure 4.24: Output voltage waveform and power spectrum at -10 dBm input power 67                           |

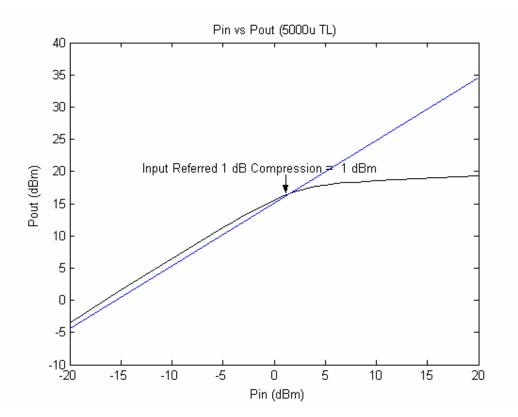

| Figure 4.25: Input referred 1 dB compression point (Gain=15.5 dB at 1 dB compression                        |

| point)                                                                                                      |

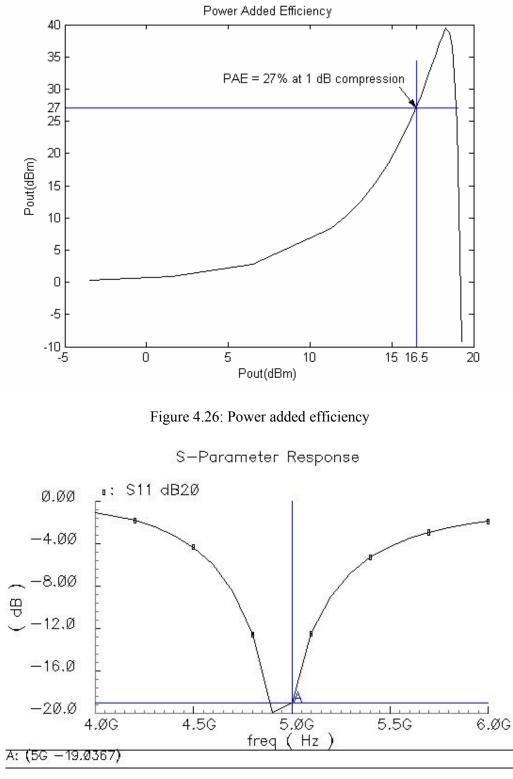

| Figure 4.26: Power added efficiency                                                                         |

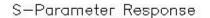

| Figure 4.27: (a) $s_{11}$ response (b) $s_{11}$ in a logarithmic scale ( $s_{11}$ is below -10 dB from 70   |

| 4.5 GHz to 5.6 GHz)                                                                                         |

| Figure 4.28: s <sub>22</sub> response                                                                       |

| Figure 4.29: Power Gain (s <sub>21</sub> )                                                                  |

| Figure 4.30: Modified CPW structure                                                                         |

| Figure 4.31: Inductance of the CPW structure in Figure 4.33                                                 |

| Figure 4.32: CPW structure                                                                                  |

| Figure 4.33: Inductance of the CPW Structure in Figure 4.35                                                 |

| Figure 4.34: Layout of the single stage PA with the CPW Structure in Figure 4.3575                          |

| Figure A.1: Delay and Doppler Spread and Carrier Phase Shift                                                |

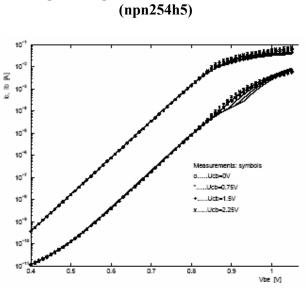

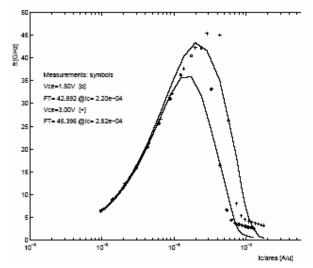

| Figure A.2: Gammel Plots of a bipolar transistor (npn254h5; 24µm emitter length) 86                         |

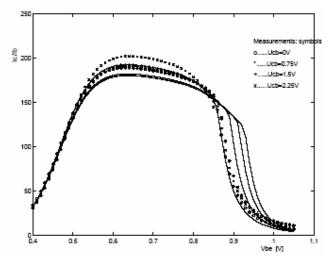

| Figure A.3: Beta plots of a bipolar transistor (npn254h5; 24µm emitter length) for a                        |

| typical wafer                                                                                               |

| Figure A.4: Ft plots of a bipolar transistor (npn254h5; 12µm emitter length) for a typical                  |

| wafer                                                                                                       |

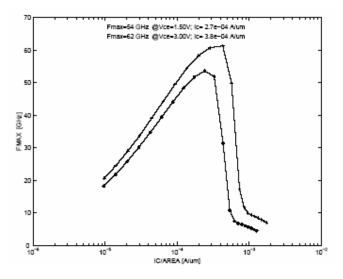

| Figure  | A.5: Fm | nax plots | of a | bipolar | transistor | (npn254h5; | 12µm | emitter | length) | for a |

|---------|---------|-----------|------|---------|------------|------------|------|---------|---------|-------|

| typical | wafer   |           |      |         |            |            |      |         |         | 87    |

# LIST OF TABLES

| Table 2.1: Transmit power levels for the United States    5                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2: Modulation types for different data rates    7                                                                                                                |

| Table 2.3: Allowed relative constellation error versus data rate    7                                                                                                    |

| Table 3.1: Optimal bias point values for Class A operation                                                                                                               |

| Table 3.2: Marker m1 bias point values, assuming Class A operation and AC current                                                                                        |

| limited to marker m2 value and AC voltage no higher than $VCE_{max} = 5.1V$                                                                                              |

| Table A.1: Model A, typical office environment with NLOS conditions and 50ns                                                                                             |

| average rms delay spread                                                                                                                                                 |

| Table A.2: Model B, typical large open space and office environments with NLOS                                                                                           |

| conditions and 100ns average rms delay spread                                                                                                                            |

| Table A.3: Model C, typical large open space environment with NLOS conditions and                                                                                        |

| 150ns average rms delay spread                                                                                                                                           |

|                                                                                                                                                                          |

| Table A.4: Model D, typical large open space environment with LOS conditions and                                                                                         |

| Table A.4: Model D, typical large open space environment with LOS conditions and 150ns average rms delay spread; a 10 dB spike at zero delay has been added resulting in |

|                                                                                                                                                                          |

| 150ns average rms delay spread; a 10 dB spike at zero delay has been added resulting in                                                                                  |

| 150ns average rms delay spread; a 10 dB spike at zero delay has been added resulting in<br>an rms delay spread of approximately 140ns                                    |

| 150ns average rms delay spread; a 10 dB spike at zero delay has been added resulting in<br>an rms delay spread of approximately 140ns                                    |

# LIST OF ABBREVIATIONS

| ADS    | Advanced Design System                            |

|--------|---------------------------------------------------|

| AMS    | Austria Micro Systems                             |

| BiCMOS | Bipolar Complementary Metal Oxide Semiconductor   |

| BPSK   | Binary Phase Shift Keying                         |

| CPW    | Coplanar Waveguide                                |

| FFT    | Fast Fourier Transform                            |

| HBT    | Heterojunction Bipolar Transistor                 |

| GI     | Guard Interval                                    |

| IC     | Integrated Circuit                                |

| I&Q    | Inphase and Quadrature                            |

| IEEE   | Institute of Electrical and Electronics Engineers |

| IFFT   | Inverse Fast Fourier Transform                    |

| LO     | Local Oscillator                                  |

| LOS    | Line of Sight                                     |

| NLOS   | Non Line of Sight                                 |

| OFDM   | Orthogonal Frequency Division Multiplexing        |

| QAM    | Quadrature Amplitude Modulation                   |

| QPSK   | Quadrature Phase Shift Keying                     |

| RF     | Radio Frequency                                   |

| SiGe   | Silicon Germanium                                 |

| UNII   | Unlicensed National Information Infrastructure    |

| WLAN   | Wireless Local Area Network                       |

## Chapter 1

#### **1** INTRODUCTION

The wireless local area network market has been growing rapidly for the past several years. The IEEE 802.11 WLAN standards have extended the frequency band from 2.4 GHz to 5 GHz bands in order to increase the data transmission rate. The new generation of 802.11a WLAN and HiperLAN/2 standards operating in the 5 GHz spectrum using OFDM are becoming popular due to high speed, greater system capacity and low interference [1]. Each of these standards requires a power amplifier as the final amplification block of the transmitter and each of them allow a specific maximum output power generated by the power amplifier.

IEEE 802.11a has different maximum output power levels depending on whether the transmission occurs in the lower (5.15 GHz-5.35 GHz) or the upper band (5.725 GHz-5.825 GHz). Typically, the required output power level for the IEEE 802.11a standard in 5.15-5.25 GHz, 5.25-5.35 GHz and 5.725-5.825 GHz bands is 40 mW, 200mW and 800 mW respectively [2].

Traditionally, power amplifier circuits at high frequencies have been implemented in III-V compound semiconductor technologies such as GaAs and InP [3]. However, RF Si ICs have recently demonstrated their competitive advantages for WLAN applications. SiGe BiCMOS technology is a silicon based technology that takes advantage of the maturity of silicon processing techniques and results into low cost elements. Recently, SiGe HBT power amplifiers are emerging as a contender for RF power amplifier applications at higher frequencies. However, SiGe devices capable of operating at 5 GHz have a low collector-emitter breakdown voltage, making it difficult to extract high output power from a single transistor [3]. Therefore, the solution to the difficulty of extracting high output power from a SiGe device operating at 5 GHz could be to use power combining techniques and to decrease losses such as conductor and dielectric substrate losses. In this thesis, two new ideas are tested and implemented to obtain higher output power. First idea is on-chip power combining using Wilkinson power combiner and the second idea is to decrease substrate losses of low Q-inductors by replacing them with transmission line inductor elements.

This thesis describes the design of a key RF block in the transmitter chain - the Power Amplifier and this work is based on SiGe BiCMOS process of AMS. We address the design of a 5 GHz PA for WLAN 802.11a applications. Our aim is to design a PA which produces enough output power for operating at the lowest frequency band of the IEEE 802.11a standard. This corresponds to 40 mW (16 dBm) output power for the 5.15 GHz-5.25 GHz frequency band. We start from the basic device I-V characteristics and designed the PA input/output matching and bias networks, accordingly. After the design of a single stage Class A PA suitable for IEEE 802.11a applications, the simulation results of the two different topologies deducted from the main PA topology are also performed. First topology to be simulated is the on-chip power combined PA circuit which utilizes a powerful technique to increase the output power and to improve the linearity. This method is tested in order to obtain higher output powers for the upper frequency bands of the IEEE 802.11a standard. Other than the power combined PA circuit, the idea of replacing the low Q inductors with capacitive loaded transmission lines is also simulated and implemented. Layouts for the single stage PA and its new version with RF choke replaced with the transmission lines are also drawn in a die size of 977\*981  $\mu$ m<sup>2</sup> including RF and DC bias pads.

The material in this thesis is organized as follows: In Chapter 2, the general principles and specifications of the IEEE 802.11a WLAN standard are presented. Also in this chapter, transmitter and receiver chains of a 802.11a system are investigated and basic principles of power amplifiers are presented. Role of power amplifier in a transmitter chain, power amplifier design parameters and different classes of power amplifiers are all given in detail in Chapter 2. In Chapter 3, basic design procedure of a 5GHz Class A single stage power amplifier is given in detail. The device I-V characteristics, load pull simulations and input/output matching network design are all presented as part of the PA design roadmap. Chapter 3 also introduces the theoretical background of the two ideas implemented in this thesis; namely on-chip Wilkinson power combining technique and capacitively loaded transmission line equivalent model of low Q inductors. This chapter also includes some ADS simulation results of the implementation of these ideas. In Chapter 4, preliminary numerical results of a more

realistic simulation of three different PA circuits will be presented. First, the simulation results of the single stage power amplifier with AMS components and layout of this topology are presented. Then, the same simulations are performed for the on-chip power combined PA topology which is also implemented with AMS components. Finally the simulation results of the single stage PA design with the transmission line structure used as the RF choke are given along with the layout. At the end of Chapter 4, an analysis of how the technology used in the design affects the characteristics of the capacitively loaded transmission line structure is done. Finally, in Chapter 5 a brief conclusion of this thesis and future work are given.

### Chapter 2

#### 2 BACKGROUND

In this chapter, brief background information about the power amplifier basics is given. Chapter 2 starts with the IEEE WLAN 802.11a standard specifications which cover the frequency allocation, output power levels, error vector magnitude values and transmit spectrum masks. Afterwards the architecture of an IEEE WLAN 802.11a transceiver is presented. Both the receiver and the transmitter parts are investigated in detail. Finally different power amplifier classes (linear and nonlinear) are mentioned in the last subsection.

#### 2.1 IEEE WLAN 802.11a Standard Specifications

IEEE 802.11 or Wireless Fidelity (Wi-Fi) denotes a set of Wireless LAN standards developed by working group 11 of IEEE 802. These specifications define an over-the-air interface between a wireless client and a base station; or between two or more wireless clients. The 802.11 family currently includes three separate protocols that focus on encoding (a, b, g); other standards in the family are service enhancement and extensions, or corrections to previous specifications.

IEEE Std. 802.11a is a high speed Wireless Local Area Network (WLAN) standard designated in 1999. This standard operates at radio frequencies between 5 GHz and 6 GHz. As seen in Table 1, there are three frequency bands allocating the 5-6 GHz band for this standard; lower band: 5.15-5.25 GHz, middle band: 5.25-5.35 GHz and the upper band: 5.725-5.825 GHz. Each band has its own maximum output power limit dictated by the IEEE 802.11a standard. As also given in Table 1, three transmit power levels are specified: 40 mW, 200mW and 800mW. The upper band defines transmit

power levels suitable for bridging applications and the lower band specifies transmit power levels suitable for short range indoor home and small office environments. Using the 5 GHz band gives 802.11a the advantage of less interference, since 2.4 GHz band is heavily used. However, this high carrier frequency restricts the use of 802.11a to almost line of sight.

| Frequency Band (GHz)  | Maximum output power with up to 6 |  |  |

|-----------------------|-----------------------------------|--|--|

| Frequency Band (G112) | dBi antenna gain (dBm)            |  |  |

| 5.15-5.25             | 40 (2.5 mW/MHz)                   |  |  |

| 5.25-5.35             | 200 (12.5 mW/MHz)                 |  |  |

| 5.725-5.825           | 800 (50 mW/MHz)                   |  |  |

Table 2.1: Transmit power levels for the United States

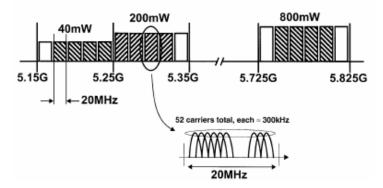

IEEE 802.11a standard has 12 non-overlapping channels, with a channel spacing of 20 MHz, as shown in Figure 2.1. Each channel is an OFDM modulated signal with consisting of 52 subcarriers. The basic principle of OFDM is to split a high data rate data stream into a number of lower rate streams that are transmitted simultaneously over a number of subcarriers. Because the symbol duration increases for the lower rate parallel subcarriers, the relative amount of dispersion in time caused by multipath delay spread is decreased. Intersymbol interference (ISI) is eliminated almost completely because the OFDM allows us to insert adequate guard interval between successive OFDM symbols.

As shown in Figure 2.1, the lower band contains four channels with channel numbers; 36, 40, 44, and 48 with center frequencies; 5180, 5200, 5220, and 5240 MHz respectively. Likewise, the middle band contains channels 52, 56, 60, and 64 with center frequencies; 5260, 5280, 5300, and 5320 MHz respectively. Finally, the upper band contains channels 149, 153, 157, and 161 with center frequencies; 5745, 5765, 5785, and 5805 MHz respectively.

Figure 2.1: OFDM PHY frequency channel plan for the United States

The IEEE 802.11a standard specifies an OFDM physical layer (PHY) that splits an information signal across 52 separate subcarriers to provide transmission of data at a rate of 6, 9, 12, 18, 24, 36, 48, or 54 Mbps. The 6, 12, and 24 Mbps data rates are mandatory in the IEEE 802.11a standard. From the 52 subcarriers, four are the pilot subcarriers that the system uses as a reference to disregard frequency or phase shifts of the signal during transmission. The remaining 48 subcarriers provide separate wireless pathways for sending the information in a parallel fashion. Since there are 64 possible subcarrier frequency slots in a 20 MHz channel in the IEEE 802.11a standard, the resulting subcarrier frequency spacing is 312.5 kHz.

The IEEE 802.11a standard system uses 52 subcarriers that are modulated using BPSK, QPSK, 16 QAM, or 64 QAM, as shown in Table 2. Depending on the data rate chosen, the binary serial signal is divided into groups (symbols) of one, two, four, or six bits and converted into complex numbers representing applicable constellation points. For example, if a data rate of 18 Mbps is chosen, the data bits are mapped to a QPSK constellation.

| Data Rate<br>(Mbits/sec) | Modulation |

|--------------------------|------------|

| 6                        | BPSK       |

| 9                        | BPSK       |

| 12                       | QPSK       |

| 18                       | QPSK       |

| 24                       | 16-QAM     |

| 36                       | 16-QAM     |

| 48                       | 64-QAM     |

| 54                       | 64-QAM     |

Table 2.2: Modulation types for different data rates

The IEEE 802.11a standard requires receivers to have a minimum sensitivity ranging between -82 dBm (at 6 Mbps data rate) and -65 dBm (at 54 Mbps data rate). The IEEE 802.11a standard also specifies maximum allowable Error Vector Magnitude (EVM) values for each data transmission rate, as shown in Table 3 [2].

| Data Transmission Speed (Mbps) | Allowable EVM (dB) |

|--------------------------------|--------------------|

| 6                              | -5                 |

| 9                              | -8                 |

| 12                             | -10                |

| 18                             | -13                |

| 24                             | -16                |

| 36                             | -19                |

| 48                             | -22                |

| 54                             | -25                |

Table 2.3: Allowed relative constellation error versus data rate

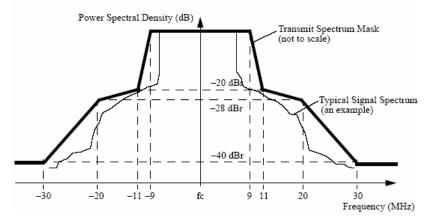

The transmitted spectral density of the transmitted signal should fall within the spectral mask, as shown in Figure 2.2.

Figure 2.2: Transmit spectrum mask

According to this transmit mask, the transmitted spectrum should have a 0 dBr bandwidth not exceeding 18 MHz, -20 dBr at 11 MHz frequency offset, -28 dBr at 20 MHz frequency offset and -40 dBr at 30 MHz frequency offset and above. The dBr unit is defined as the dB relative to the maximum spectral density of the signal.

# 2.2 Architecture of an IEEE 802.11a WLAN Transceiver

The spectral efficiency of the 802.11a standard comes at the expense of a more complicated transceiver with strict requirements on the radio performance. For example, the use of 64-QAM modulation requires a signal-to-noise ratio (SNR) of 30 dB, which is substantially greater than that required by the FSK modulation in Bluetooth and the QPSK modulation in 802.11b. This high SNR translates to stringent phase noise requirements for the frequency synthesizer and tight matching constraints for both the transmitter and receiver. OFDM, which is highly desirable because of its resilience to multipath interference, can substantially complicate the transmitter.

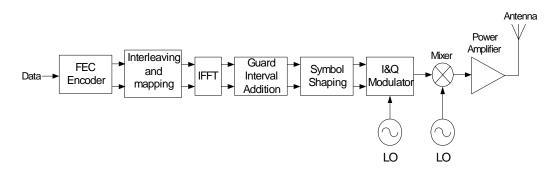

As shown in the Figure 2.3, data is first encoded using Forward Error Correction (FEC) encoder and then interleaved and mapped. After that, Inverse Fast Fourier Transform (IFFT) is applied and Guard Interval (GI) is added. After the symbol shaping is done, data is Inphase and Quadrature (I&Q) modulated and the then mixer is used to upconvert the signal to a specific frequency value with the help of the local oscillator

(LO). Finally the power amplifier is the last stage in the transmitter chain just before the antenna and it is used to increase the power level of the signal to be transmitted.

Figure 2.3: Block diagram of an IEEE 802.11a transmitter

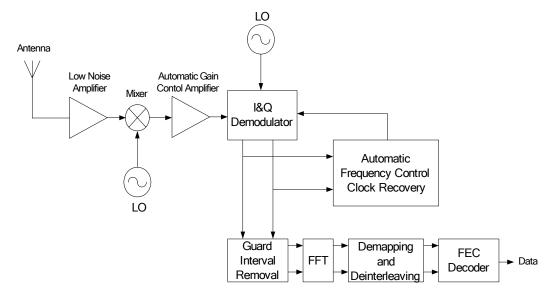

Figure 2.4 indicates the block diagram of an IEEE 802.11a receiver. The receiver topology looks like the reverse of the transmitter. First block is the Low Noise Amplifier (LNA) after the signal is captured with an antenna. The mixer follows the LNA to downconvert the signal. The mixer output is fed into an Automatic Gain Control Amplifier. Then I&Q demodulation takes place. Automatic Frequency Control Recovery is utilized after this block in order to achieve a flawless demodulation and after that GI is removed and Fast Fourier Transform (FFT) is applied. After demapping and deinterleaving stage, FEC decoder decodes the original data.

Figure 2.4: Block diagram of an IEEE 802.11a receiver

## 2.3 Power Amplifier Background

#### 2.3.1 Introduction

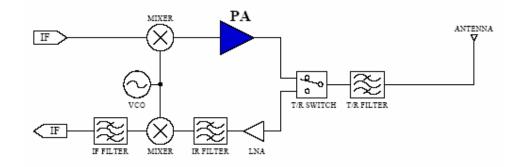

In any wireless communication system there is a transmitter part and in any transmitter one of the most challenging components is the Power Amplifier. Power Amplifier is the last amplification stage in the transmitter chain and it is a key part of the RF front end in any transmitter, as shown in Figure 2.5.

Figure 2.5: Block diagram of an RF transceiver

Power amplifier (PA) takes the signal to be transmitted and amplifies it to a proper level such that the transmitted signal overcomes the channel losses and receiver senses adequate power to recover the desired signal. That specific power level is determined by the communication system and for different applications the order of magnitude of the transmitted power varies. For example, while the transmitted power level is on the order of thousands of watts for satellite communications, this level drops to tens to hundreds of milliwatts for portable wireless communication devices. Even the generated output power levels differ greatly; the underlying principles of the power amplifier design are much the same.

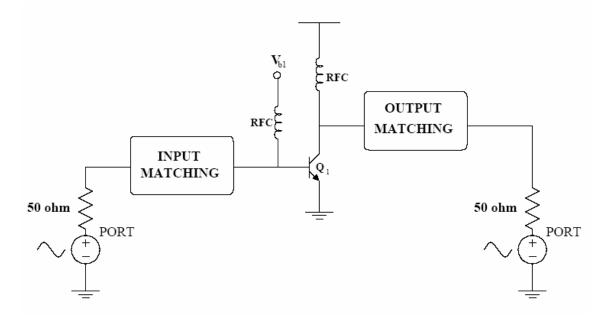

Because the power that should be sent to the transmitting antenna is often quite high, PA is the largest power consumer in most wireless communication systems. A major design requirement of a PA is how efficiently the PA converts the DC power into RF output power. A power amplifier usually consists of an active device, which is a transistor, input and output matching networks and some extra circuitry, like the bias network. Figure 2.6 shows the basic topology of a basic power amplifier.

Figure 2.6: Basic topology of a power amplifier

According to the target application of the PA; transistor type, class of operation and the matching circuit topologies are determined.

#### **2.3.2** Power Amplifier Performance Parameters

Some of the important terms and specifications of a PA are as follows:

## **Frequency of Operation**

The PA should be designed for a specific range of frequency in a narrowband application. Each communication standard specifies its own frequency range of operation and for this thesis the PA is designed at 5 GHz frequency and all of its parameters are simulated at 5 GHz. That is compatible with IEEE 802.11a WLAN standard which occupies the 5 GHz frequency band.

### **Output Power**

Output power is the amount of power that needs to be delivered to the transmitting antenna. As mentioned earlier, the output power levels of 802.11a transmitters are specified by the IEEE 802.11a standard. With upto 6 dBi antenna gain,

for the lower frequency band (5.15 GHz-5.25 GHz) the output power level should not exceed 40 mW; for the middle frequency band (5.25 GHz-5.35 GHz) the maximum output power level is 200 mW and for the upper frequency band (5.725 GHz- 5.825 GHz) this level is specified as 800 mW.

When considering power output, a common unit used is dBm, which is the output power in dB referenced to 1 mW. The output power in dB is given by

$$P_{dBm} = 10\log\frac{P}{0.001W}$$

(2.1)

where P is defined in Watts. In dB scale, the specified maximum output power levels for IEEE 802.11a standard are 16 dBm, 23 dBm and 29 dBm for the lower, middle and upper frequency bands respectively.

# **Power Gain**

PAs provide a certain level of power gain in order to boost the incoming signal to required levels. Power gain is defined as the ratio of the output power delivered to the load to the input power available from the source. It is desired that the power gain be flat over the frequency band, with a tolerance of  $\pm 0.5$  dB.

#### Efficiency

The measure of how much power a PA consumes while converting the DC power into RF power delivered to the load is a key performance parameter of a PA. This parameter is known as the PA's efficiency. Efficiency is most basically defined as the ratio of the "power delivered to the load" to the "power drawn from the source". The maximum efficiency is 1, or 100% since the PA is converting the DC supply power into RF power delivered to the load. This happens if there is no power consumed in the PA, which is only ideally possible.

There are variations of this metric that give more information about the PA. The most common efficiency metric used is the Power Added Efficiency (PAE). PAE is defined as

$$PAE = \frac{P_{RF_{OUT}} - P_{RF_{IN}}}{P_{DC}}$$

(2.2)

It is important to note that there is a tradeoff between efficiency and linearity. That is why nonlinear power amplifiers offer much higher efficiencies compared to their linear counterparts.

#### Linearity

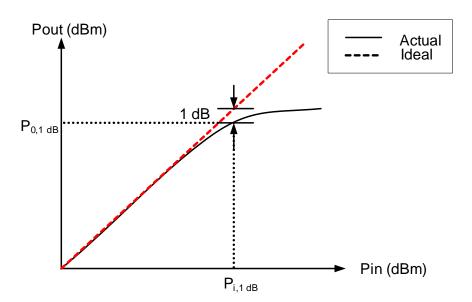

Input output relation of a PA must be linear in order to preserve signal integrity. It is desired that the PA operates with high linearity, meaning that the output power be linear with the input power. As the input power level increases, device gets closer to saturation point and eventually reaches the saturation point. This introduces harmonics in the output power spectrum. In order to measure linearity of a PA, 1 dB compression point and third order intercept points are used.

1 dB compression point can be defined both as input referred and output referred. For example, input referred 1 dB compression point is defined as the input power at which the linear gain of the amplifier is compressed by 1 dB [7]. The output referred 1 dB compression point is the sum of the input referred 1 dB compression point and the gain of the amplifier. Figure 2.7 shows a plot of the 1 dB compression point characteristics.

Figure 2.7: 1 dB compression characteristics

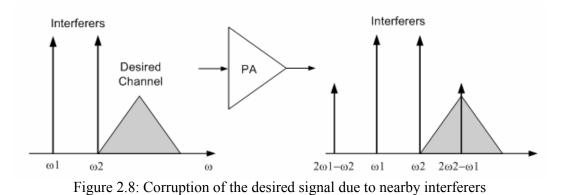

Third order intercept point is another useful metric for measuring linearity. When there are interferers very close to the fundamental frequency, the nonlinear behavior of the PA generates inter-modulation products. Third order intermodulation (IM3) product is the most important of the products, because it falls directly into the frequency band of interest as indicated in Figure 2.8.

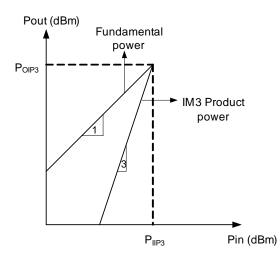

The amplitude of the IM3 product term increases in the order of cube of the fundamental amplitude. The third order intercept point is the extrapolated intersection of this IM3 product term and the fundamental power, as shown in Figure 2.9.

Figure 2.9: Third Order Intercept Point

In general, modulation schemes can be separated into two basic categories: constant envelope and non-constant envelope. In the constant envelope modulation schemes, there is no symbol information contained in the transmitted signal amplitude, therefore a linear relationship between the input and the output is not required. In the non-constant envelope case, there is symbol information contained in the transmitted signal amplitude. As a result, extremely linear power amplifiers are required for nonconstant envelope modulation techniques, while the linearity can be traded for efficiency in constant envelope modulation schemes. There are a variety of well established linearization techniques, such as feedback techniques, predistortion technique, feedforward technique, etc. The linearization methods will not be covered in this thesis.

# **Error Vector Magnitude (EVM)**

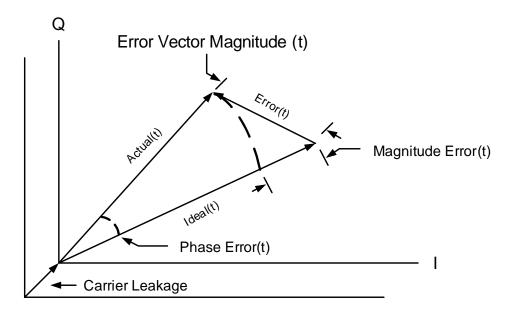

EVM represents the distance between the measured and expected carrier magnitude and phase at some point in time after it has been compensated in timing, amplitude, frequency, phase and DC offset. Figure 2.10 shows the error vector magnitude representation as the phase and magnitude difference between the actual and ideal carriers. For IEEE 802.11a, the error vector between the vector representing the transmitted signal and the vector representing the error-free modulated signal defines modulation accuracy. The magnitude of the error vector is called error vector magnitude (EVM).

Figure 2.10: Error Vector Magnitude representation

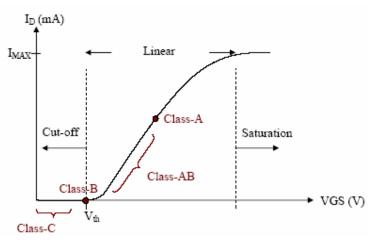

#### 2.3.3 Power Amplifier Classes

Although there are many different classes, in general PAs can be categorized into two groups; linear and non-linear (switching mode) amplifiers. In the former category of PAs, the active device (transistor) acts as a current source, while in the latter category device acts as a switch. Class A, B, AB and C amplifiers fall into linear amplifier category where the output amplitude of the signal is a linear function of the input signal amplitude. For this type of amplifiers the voltage and current waveforms through and across the transistor are full or partial sinusoids. On the other hand, class D, E and F are some of the switching mode PA types. These types of amplifiers can achieve high efficiency levels, but very nonlinear performances.

Brief background information about different classes of PAs will be presented in the next subsections. However, Class A will be emphasized more than other classes.

#### **Linear Power Amplifiers**

Linear PA generally refers to a PA which operates at a constant gain and needs to preserve amplitude information. For this type of amplifiers, the active device operates in its amplifying region. The amplifying region is the saturation region for FET devices, while it is the forward active region for bipolar devices.

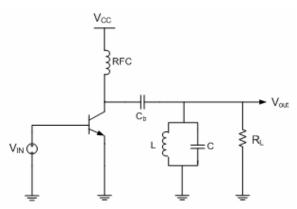

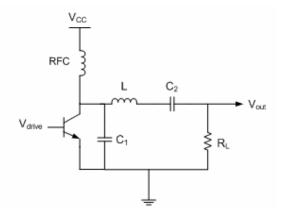

There are four types of PAs, distinguished primarily by bias conditions that may be termed "linear"; Class A, AB, B, and C. All may be understood by studying the single model given in Figure 2.11. In this figure,  $R_L$  is the load into which the output power is delivered. The inductor named, RFC is used as an RF choke to feed DC power to the collector. Likewise,  $C_b$  is a DC blocking capacitance, which is used to prevent any DC dissipation in the load. The LC network is used as an output matching network [5].

Figure 2.11: General linear power amplifier model

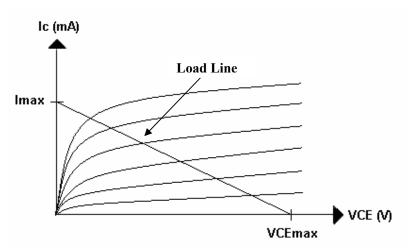

The design of linear PAs depends on the load line theory. This theory states that the maximum power that can be supplied by a transistor to a load is determined by the supply voltage and the maximum current passing through the transistor. As shown in Figure 2.12, load line is defined as the line drawn between the two specific points on the transistor I-V curve. These points are the knee point where the maximum collector current ( $I_{max}$ ) during AC operation is obtained and the  $I_c=0$ ,  $V_{CE,max}$  point, where the maximum allowed  $V_{CE}$  value is located. Load line technique is used to find the optimal bias point for different classes of linear PAs, i.e. for each class, a different optimal bias point should be chosen on the load line.

Figure 2.12: I-V characteristics of a transistor

To utilize the maximum current and voltage swing of the transistor, an optimum load resistance value,  $R_{opt}$ , would need to be selected, and simply this resistance is the ratio:

$$R_{opt} = \frac{V_{DC}}{\left(\frac{I_{\max}}{2}\right)} = \frac{2V_{DC}}{I_{\max}}$$

(2.3)

This equation is derived from the fact that the current swings over its maximum linear range (zero to Imax), that is with an amplitude of  $I_{max}/2$  and the voltage swings over its maximum linear range of zero to  $2V_{DC}$  [6].

This means that power amplifiers can deliver maximum power to a load given by  $R_{opt}$ . Since the transmitting antenna is acting as a 50  $\Omega$  load, this  $R_{opt}$  resistance is then transformed to 50  $\Omega$  by a matching network.

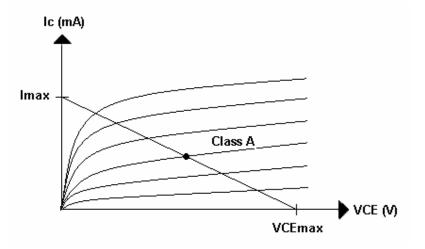

The most linear PAs are those in which the active device is always conducting current. This type is known as Class A power amplifiers. To design a Class A PA, it is important to make sure that the active device conducts current for the entire input sinusoid cycle. The input bias voltage is set such that the device remains in its amplification region all the time. As mentioned earlier, the class of operation is determined by the operating point on the load line which is obtained from the I-V characteristics of the transistor. For a Class A operation, the transistor should be biased at the center of the load line to maximize the output voltage and current swings as shown in Figure 2.13. This shows that the transistor is in the active region at all times.

Figure 2.13: Class A Optimal Bias Point

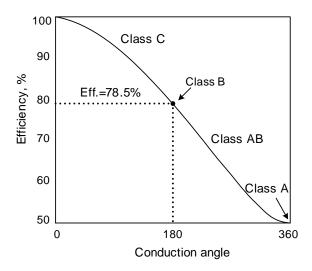

Conduction angle,  $\alpha$ , is defined as the time for which the transistor is conducting. For Class A operation, since the transistor is conducting all the time, the conduction angle is  $2\pi$ .

The linearity of Class A PAs is perfect as the input and output waveforms are preserved without any distortion but the maximum efficiency of a Class A PA is only 50%. However, an efficiency of about only 30% can be attained from a fully Class A PA implementation. This is mainly because, in real life, it is usually not possible to get a peak voltage swing as the active device leaves its amplification region and enters the resistive (this corresponds to saturation region for bipolar devices and linear region for FET devices) region.

For Class B operation, amplifier is biased at the threshold voltage of the transistor, such that the device is shut off half of every cycle. Because the transistor is conducting only half of every cycle, the conduction angle is  $\pi$ . The most practical of Class B amplifiers are push-pull configurations of two transistors. The peak current and maximum output voltage for Class B amplifier are same as for the Class A amplifier,

but the theoretical efficiency is about 78% for Class B amplifies. In practice, efficiency drops to 50% or less. However, linearity is worsened in these types of amplifiers. In conclusion, distortion is accepted in exchange for a significant improvement in linearity with the Class B amplifier.

Class AB amplifier, as its name suggests conducts somewhere between 50% (as Class B amplifiers) and 100% (as Class A amplifiers) of a cycle, depending on the bias level chosen. Accordingly, its efficiency and linearity are intermediate between those of a Class A and Class B amplifier. The conduction angle for Class AB amplifiers is  $\pi < \alpha < 2\pi$ .

Class C amplifiers are biased in such a way that the transistor conducts less than half the time. Consequently, the conduction angle is  $\alpha < \pi$ . Class C amplifiers offer efficiencies approaching 100%, but both power-handling capability and power gain approach zero at the same time. This class of amplifiers sacrifices linear operation to improve the efficiency. Also, it is actually difficult to design and construct Class C amplifiers with bipolar devices.

Figure 2.14: Q point of Class A, AB, B and C PAs

In sum, Class A, AB, B and C PAs fall into the linear PA category. Each class is biased at a different quiescent point as shown in Figure 2.15. For the Class A operation, the transistor should be biased at the center of the load line, while for the Class B operation transistor is biased at the threshold voltage,  $V_{th}$ . As the name suggested, for the Class AB operation, transistor should be biased between the Class A and Class B bias points. The corresponding conduction angles for each linear type PA is given in Figure 2.15.

Figure 2.15: Summary of Class A, AB, B and C conduction angles

Figure 2.16 summarizes the maximum theoretical efficiency as a function of conduction angle for different kinds of linear power amplifiers. As seen from this figure, maximum theoretical efficiency (100%) can be achieved with the Class C operation where the conduction angle varies between zero to  $\pi$ . Class B operation can reach theoretical efficiencies up to 78.5%, where the conduction angle is between  $\pi$ . Class A operation is the least efficient of all, where the maximum theoretical efficiency that can be reached is only 50% with a conduction angle of  $2\pi$ . Class AB mode has efficiency and conduction angle values between those of Class A and Class B modes. Theoretically, any efficiency value can be reached between 78.5% and 100% for Class AB operation.

Figure 2.16: Maximum theoretical efficiency of an ideal amplifier as a function of conduction angle

#### Non-Linear (Switching mode) Power Amplifiers

Switching mode amplifiers are used in applications where efficiency is the primary concern. They are driven with a large amplitude signal which turns the device ON or OFF, as a switch. There are various kinds of switching mode amplifiers, but Class D, E and F are the most common configurations. For high efficiency RF applications, Class D and Class E configurations have received the most attention.

Among several classes of switching mode PAs, the Class E configuration is the most suitable for RF operation. Figure 2.17 shows a Class E PA topology. The RFC provides a DC path to the supply and approximates an open circuit at RF. Under ideal conditions, the voltage of the switch transistor drops to zero and has zero slope just as the transistor turns on and conducts current. This ensures that neither voltage nor current exists simultaneously in the circuit [7]. Therefore, the theoretical peak efficiency of the Class E PA is 100%.

Figure 2.17: Class E amplifier

Class-F amplifiers employ harmonic resonators at the output to shape the drain waveforms. Figure 2.18 shows the Class F topology.

Figure 2.18: Class F amplifier

The harmonic traps are designed in such a way that the voltage waveform resembles a square wave and the current wave resembles a half sine wave. Both the voltage and current waveforms do not exist simultaneously, thus achieving good efficiency. With higher harmonics, the efficiency can be improved up to 100%, but linearity is severely worsened.

# **Chapter 3**

## **3** PA DESIGN METHODOLOGY

In this chapter, basic design procedure of a 5GHz Class A power amplifier is given in detail. This chapter starts with a basic design roadmap to be followed during a PA design. Then in the consequent subsections; the device I-V characteristics, load pull simulations and input/output matching network design are presented. Our main contribution in this thesis is to increase the output power and improve the linearity performance by using on-chip power combining technique and also to decrease conductor/substrate losses by replacing the low Q inductors by their transmission line equivalents. Therefore, the theory of Wilkinson Power Combiner and Transmission line equivalent model of low Q inductors, along with their simulation results in ADS environment are also presented in the last two subsections of this chapter.

## 3.1 Design Roadmap

The design starts with determining the requirements and device selection. As a rough approximation, device I-V curves are plotted and to support the current; number and size of the transistors are decided. In this PA design our main requirement is to obtain 40 mW output power to obey the 802.11a standard power specifications for the lowest frequency band. Power amplification in RF frequencies can be accomplished by using any one of many different devices; BJT, MOSFET, GaAs MESFET, HBT, etc. In this thesis, the PA is designed in AMS 0.35µm SiGe BiCMOS HBT technology and high voltage npn Bipolar transistors available in this process are used as the active device. The transistors are symbolized as npn <2><5><4>h5 HBT and the numbers refer to the number of collector, base and emitter contacts, respectively. Active

components are usually limited to 2 or 3 transistors in signal path, therefore in order to obtain enough output power (40 mW), 3 of these high voltage transistors are paralleled. Moreover, in order to maximize the output power, transistor sizes are also set to the maximum limit specified by the process, which corresponds to an emitter length of 96µm.

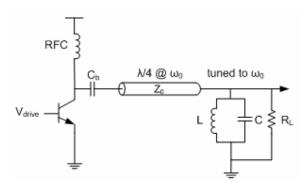

Figure 3.1 presents the design steps to be followed after the technology is chosen.

Figure 3.1: PA design roadmap

As seen in Figure 3.1, the first step in the design roadmap is to obtain device I-V curves which are used to determine the optimum bias points for the certain class of operation. After the DC operating points are determined from the device I-V curves, the next step will be to determine the optimum output impedance for maximum power. Load pull simulations are essential in terms of determining the optimum load impedance at the transistor array output, because load pull data gives a simple target area on the Smith Chart to base the strategy for suitable matching network design. Therefore, the optimum load impedance is determined from load pull simulations and then an output matching network is designed to transform 50  $\Omega$  load to the optimum load impedance at the transistor output. The following step is to design the input

matching network for gain (complex conjugate) match. Then the overall performance of the PA design is tested via simulation tools; ADS and Cadence. Finally, the circuit layout is drawn and post layout simulations are performed and performances are compared.

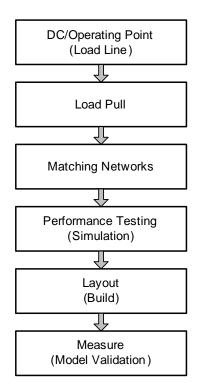

#### 3.2 Device I-V curves

After the technology is selected, the first step in designing a PA is to determine the I-V characteristics of the active device.

As mentioned earlier, AMS's high voltage npn Bipolar transistors are used with their emitter length set to the allowed maximum level, which is 96  $\mu$ m. Three transistors are connected in parallel in order to increase the total emitter length and transistor sizes are maximized in order to deliver required output power. The BJT curve tracer shown in Figure 3.2 generates transistor I-V curves by sweeping base current (IBB) and collector-emitter voltage (VCE).

Figure 3.2: This circuit generates I-V curves and computes optimal bias for Class A operation

I-V curves of three bipolar transistors are given in Figure 3.3, where VCE-IC curves are generated for different IBB values. The maximum collector current during AC operation is set by moving marker m2 to the knee of the I-V curve as shown in Figure 3.3. Then the maximum allowed VCE,  $VCE_{max}$  is specified as 5.1V. After that, load line is drawn between marker m2 and the (IC=0,  $VCE=VCE_{max}$ ) points. The

optimal bias point values are determined from this load line. Load line method is a useful priori design method to use as a starting point for the design process.

Device IV Curves and Load Line

Figure 3.3: Transistor I-V curves

For Class A operation, the center of the load line should be chosen as the bias point. Therefore, marker 1 (m1) is set to the center of the load line. As seen in Figure 3.3, the optimal VCE is 3V and IBB is 270  $\mu$ A for the Class A operation. At this biasing point (m1), transistor's DC current gain (beta) is about 167, as seen in Figure 3.4.

Figure 3.4: Beta versus IBB at ICE which is specified by the marker m1

ADS also generates the optimal Class A bias point values as a result of device I-V curves. As given in Table 3.1, optimal VCE is 3V and optimal ICE is 46.38 mA. Table 3.2 shows the output power and efficiency levels that can be reached at the bias point, m1. In case the transistors are loaded with the Rload value given in Table 3.2, and other bias conditions are satisfied, an efficiency of 35% and an output power of 16.76 dBm can be obtained. These are preliminary results based on linear approximations.

| Output Power at Optimal Bias (dBm) | 16.87  |

|------------------------------------|--------|

| Rload at Optimal Bias (ohm)        | 45.282 |

| DC to RF Efficiency (%)            | 35     |

| Optimal VCE (V)                    | 3      |

| Optimal ICE (mA)                   | 46.38  |

| DC Power Consumption (mW)          | 139.1  |

Table 3.1: Optimal bias point values for Class A operation

| Output power (dBm)        | 16.76  |

|---------------------------|--------|

| Rload (ohm)               | 44.082 |

| DC to RF Efficiency (%)   | 35     |

| DC Power Consumption (mW) | 135.3  |

Table 3.2: Marker m1 bias point values, assuming Class A operation and AC current limited to marker m2 value and AC voltage no higher than  $VCE_{max} = 5.1V$

In the next subsection, transistors are biased at point m1 by applying a 3V DC bias voltage to the collector and by ensuring that the bias current is  $270 \ \mu$ A.

#### 3.3 Load Pull

Load pull is varying or pulling the load impedance seen by a device under test (DUT) and measuring the performance of the DUT. This technique is important for nonlinear devices where the operating point may change with power level. In our case, we performed load pull analyzes by varying the load impedance of a power amplifier in order to obtain the optimal load impedance for maximum output power.

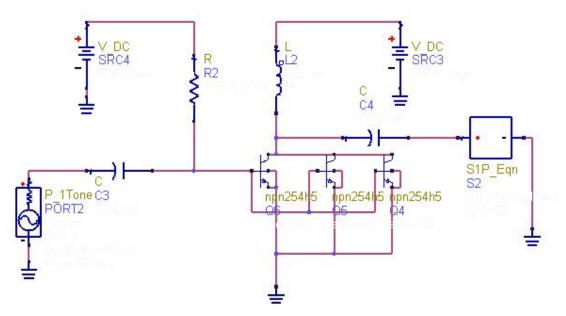

After the bias conditions are satisfied, load pull simulations are performed in order to obtain more realistic load impedance values for maximum power transfer. The load pull setup shown in Figure 3.5 performs one tone load pull simulations. As a result, the output power and PAE are found at each fundamental frequency.

In the Figure 3.5, the capacitors connected to the base and the collector are for DC blocking and they have a capacitance of 30 pF. The inductor at the collector is an RF choke with an inductance of 5 nH, which is used to feed DC power to the collector. The resistor connected to the base is for biasing purposes and finally the output is terminated with variable load impedance. RF choke has a comparatively large inductance in order to act as an open circuit at high frequencies (by showing high impedance at RF), thus isolates RF signals from DC signals. The impedance of the RF choke used in this design can be calculated from a basic equation:

$$Z_L = wL$$

, where  $w = 2 * \pi * f$  (3.1)

Since the operating frequency is 5GHz, the impedance of the RF choke at 5 GHz is:

$$Z_L = wL = (2 * \pi * 5 * 10^9) * (5 * 10^{-9}) = 157\Omega$$

(3.2)

On the other hand, DC blocking capacitors act as short circuit at high frequencies and as open circuit at DC. This is possible by showing very low impedance at RF. At 5 GHz, the impedance of the DC blocking capacitors used in this design (30 pF) is calculated as follows:

$$Z_C = \frac{1}{wC} \tag{3.3}$$

$$Z_{C} = \frac{1}{wC} = \frac{1}{(2*\pi*5*10^{9})*(30*10^{-12})} = 1\Omega$$

(3.4)

Figure 3.5: Load Pull Setup in ADS

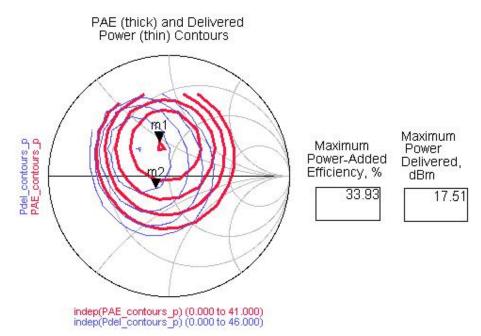

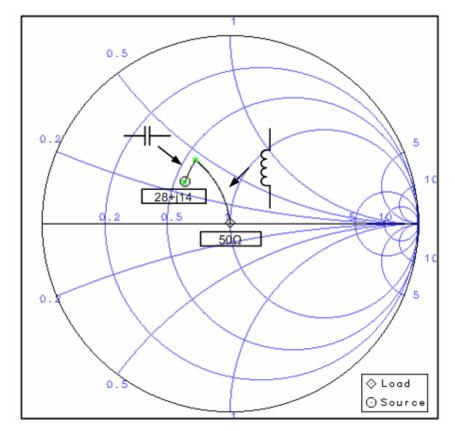

Load pull setup shown in Figure 3.5 generates power and efficiency circle at each load impedance and this results in concentric circles on the Smith Chart. Figure 3.6 shows the maximum PAE (33.93%) and output power (17.51 dBm) that can be obtained from this circuit. The target area on the Smith Chart for obtaining maximum power added efficiency and maximum output power can also be determined from the same figure.

Figure 3.6: Maximum PAE and Pout circles on the Smith Chart

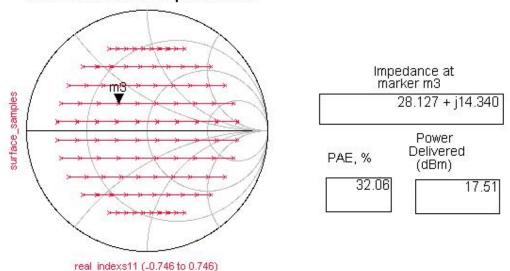

According to the target area on the Smith Chart indicated in Figure 3.6, the best point on the Smith Chart should be chosen as the optimum load impedance. As seen in Figure 3.7, each point on the Smith Chart represents different load impedance values and among these points, point m3 is chosen as the optimum load impedance. Impedance at marker m3 is 28.127 + j14.34 and with this load impedance, 32.06% PAE and 17.51 dBm output power could be obtained.

Simulated Load Impedances

Figure 3.7: Simulated load impedances

### 3.4 Matching Network Design

In an RF or microwave system, the terminal impedances are all designed to be  $50\Omega$  by convention. Thus the antenna is modeled as a  $50\Omega$  resistor. Since PA drives the antenna, some conversion must take place between the PA output and the antenna, in order to ensure desired power levels to be obtained at the antenna. This conversion process is accomplished by designing a matching network which converts the optimum load impedance, found from load pull simulations, to  $50\Omega$  antenna. The matching network consists of passive, ideally lossless components such as capacitors and inductors. The output and input matching network design will be mentioned in the following subsections.

## 3.4.1 Output Matching

After the optimum load impedance is determined from the load pull simulations, the next step is to design an output matching network. This network should transform the desired load impedance, which is 28.127 + j14.34 to  $50\Omega$  antenna impedance. The best way to design ideally lossless matching networks is to equip LC matching networks. The design of the matching network is done in ADS's Smith Chart Utility as shown in Figure 3.8. During the matching network design; inductive and capacitive losses are taken into account.

Figure 3.8: Output matching network design using ADS Smith Chart utility

The output matching network which transforms the optimum load impedance, 28.127 + j14.34 to  $50\Omega$  is given in Figure 3.9.

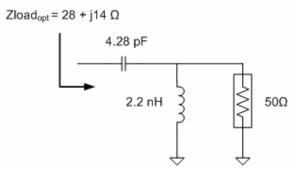

Figure 3.9: Output matching network

### 3.4.2 Input Matching

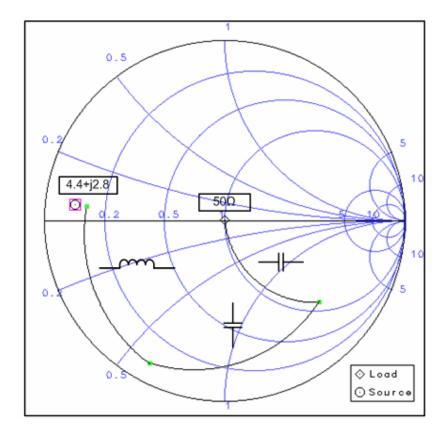

Bipolar devices show significant dependency between output power and input load. Therefore, input matching is a crucial part of the PA design. After the desired output load impedance is matched to 50  $\Omega$ , such that maximum power is transferred to the antenna, the next step is the design of the input matching network.

Basic design issue is to satisfy the conjugate match principle at the input for maximum power transfer. This principle is to show the conjugate match of s11 to the transistor input in order to obtain a gain match at the output. Accordingly, s11 is 4.4 - j2.8 at 5GHz when the optimum load impedance is shown to the output port. In order to obtain an input match, the complex conjugate of s11, which is 4.4 + j2.8, should be shown to the input. This is very low impedance since the transistors are connected in parallel. As such a large transistor array has very low input impedance, a matching network with a highest possible quality factor is necessary. Since we are using AMS's SiGe process, from AMS's library of thick metal inductors, we seek to use the inductor model with the highest Q at 5GHz. Therefore we choose the inductor model SP011S200T which has an inductance of 1.05 nH and a quality factor of 11.8 at 5GHz.

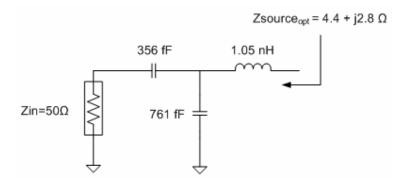

Again using ADS's Smith Chart Utility, an LC network is designed which matches 50  $\Omega$  to 4.4 + j2.8, as shown in Figure 3.10. Figure 3.11 shows this matching circuit, which consists of two capacitors, one in parallel and one in series, and a single inductor connected in series.

Figure 3.10: Input matching network design using ADS Smith Chart utility

Figure 3.11: Input matching network

# 3.5 Overall Class A Single Stage PA Schematic

After output and input matching network design, the overall single stage PA circuit which is operated in Class A is shown in Figure 3.12. DC blocking capacitors are integrated into the matching circuitry and the bias conditions are satisfied via the resistor connected to the base and the RFC connected between the collector and the DC

voltage source. All of the components are ideal elements taken from the ADS library and the circuit is designed to operate at 5GHz.

Figure 3.12: Class A PA schematic with ideal elements in ADS

This single stage Class A PA circuit provides 15.8 dBm output power at the 1 dB compression point, as given in Figure 3.13. The input power at 1 dB compression point is -3.5 dBm and at this point PAE is about 23%, which is an expected result of Class A operation. Maximum PAE is about 40% as shown in Figure 3.14.

Figure 3.13: Single stage Class A output power and 1 dB compression point

Figure 3.14: Single stage Class A PAE curve

As seen from the Figure 3.13, single stage PA provides an output power level very close to the IEEE 802.11a specified maximum output power level, which is 16 dBm (40 mW). However, our main goal is to obtain higher output power levels at 5GHz and to achieve this goal, the on-chip power combining technique is used, where two single stage Class A PAs are combined. This technique is described in detail in the following section.

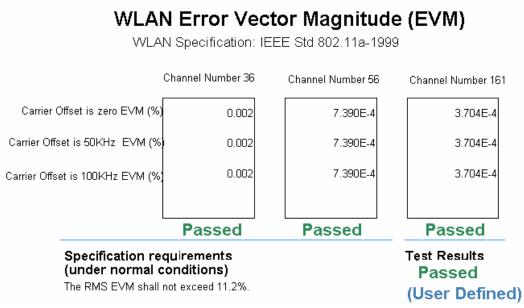

#### 3.6 Wilkinson Power Combiner/Splitter Design

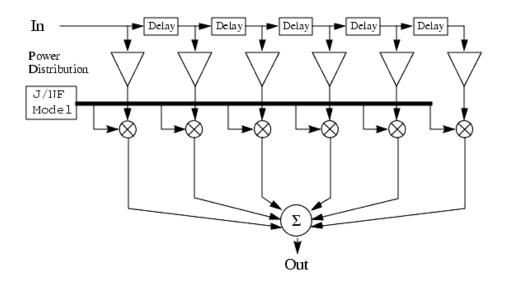

The first idea to be tested in this thesis is combining two single stage Class A PAs via power combining techniques in order to increase the output power and improve the linearity performance. Out of many power combining techniques, Wilkinson power combiner method is utilized. In Figure 3.15, two power amplifiers are combined via on-chip Wilkinson power combiners.

Figure 3.15: In-phase power combining using Wilkinson power combiners

A classical microstrip Wilkinson power splitter consists of two quarter wave microstrip line segments with characteristic impedance  $Z_0 * \sqrt{2}$  at the operating center frequency  $f_0$  and a  $2 * Z_0$  lumped resistor connected between the two ports, as shown in Figure 3.16. Wilkinson power combiners can be interpreted as 2:1 impedance transformers, which transform each 50 $\Omega$  input to 100 $\Omega$ , where the two are paralleled. The function of the isolation resistance is to terminate any odd mode signals.

Figure 3.16: Microstrip Wilkinson combiner

The S parameters for such a three port network are given by the matrix [8]:

$$[S] = \frac{-1}{\sqrt{2}} \begin{bmatrix} 0 & j & j \\ j & 0 & 0 \\ j & 0 & 0 \end{bmatrix}$$

(3.5)

The figures of merit of a Wilkinson power combiner are the return loss at ports 1 and 2 ( $RL_1$  and  $RL_2$ ), the coupling between ports 1 and 2 ( $CP_{12}$ ) and isolation between ports 2 and 3 ( $IL_{23}$ ).

$$RL_1 = -20\log|S_{11}| \tag{3.6}$$

$$RL_2 = -20\log|S_{22}| \tag{3.7}$$

$$CP_{12} = -20\log|S_{21}| \tag{3.8}$$

$$IL_{23} = -20\log|S_{23}| \tag{3.9}$$

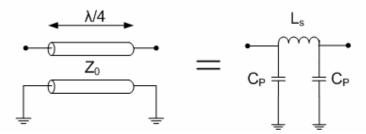

Ideally, return loss and isolation should approach negative infinity at the center frequency and the coupling should be very close to 3dB. Therefore, Wilkinson power splitter provides low loss, equal split, matching at all ports and high isolation between output ports [9]. In fact, at RF frequencies the quarter wave transmission line sections can have unrealistic dimensions. Thus, at higher frequencies the classical microstrip realization can be replaced with its lumped element counterpart, as given in Figure 3.17. Lumped element Wilkinson power splitter is obtained by replacing both quarter wave transmission line sections with their equivalent lumped element "Pi" LC network model at the design center frequency  $f_0$ .

Figure 3.17: "Pi" LC network model of a quarter wavelength transmission line

The inductance and capacitance values associated with the "Pi" LC equivalent network can be found from the below equations:

$$L_{s} = \frac{Z_{0}}{2*\pi*f_{0}}$$

(3.10)

$$C_{P} = \frac{1}{2*\pi * f_{0} * Z_{0}}$$

(3.11)

At 5GHz center frequency,  $L_S$  and  $C_P$  values are found for two way equal Wilkinson power divider from the below equations.

$$L_{\rm s} = \frac{50\sqrt{2}}{2^*\pi^*5^*10^9} = 2.25 \text{ nH}$$

(3.12)

$$C_P = \frac{1}{2^* \pi^* 5^* 10^9 * 50\sqrt{2}} = 450 \text{ fF}$$

(3.13)

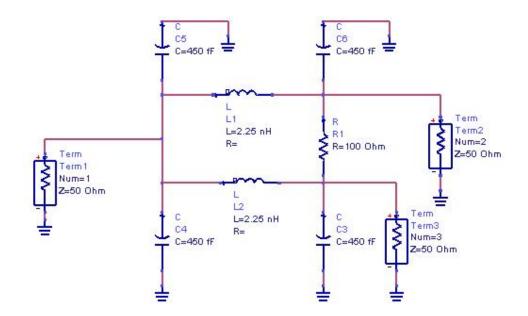

From the above equations, we obtain  $C_P = 450$  fF and  $L_S = 2.25$  nH at 5GHz. With these capacitance and inductance values, a lumped element equal 2-way Wilkinson power splitter at a center frequency of 5GHz is obtained as shown in the Figure 3.18.

Figure 3.18: Lumped element Equal split Wilkinson power divider at 5GHz center frequency

The lumped element Wilkinson power splitter exhibits perfect isolation at the input port and equal power division at the output ports. These can be seen from  $s_{11}$ ,  $s_{21}$  and  $s_{31}$  plots in Figure 3.19, obtained via ADS tool.

At 5 GHz,  $s_{11}$  drops down to -65 dB, when simulated with ideal elements. Likewise,  $s_{21}$  and  $s_{31}$  values are -3 dB as expected, indicating that the power is equally divided into two at 5 GHz. However, it should be noted that a Wilkinson divider/combiner is not a broadband device. Typical frequency bandwidths do not exceed 20% of the center frequency.

Figure 3.19: Simulated  $s_{11}$ ,  $s_{21}$  and  $s_{31}$  parameters of lumped element Wilkinson power splitter model

In the upcoming sections, this Wilkinson power splitter configuration will be used to combine two single stage Class A power amplifiers in order to obtain higher output power levels and better 1 dB compression values, therefore to improve the linearity.

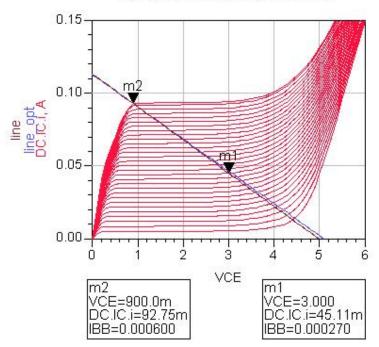

## 3.7 Microstrip Line/Coplanar Waveguide Equivalent Model of RF Choke

In this section the idea of using capacitively loaded microstrip transmission lines instead of low Q inductors will be discussed. The purpose of doing such a replacement is to reduce conductor and substrate losses, while shrinking the die area.

First, the performance simulations of capacitively loaded microstrip lines are performed in ADS environment. Then, the same simulations are done, again in ADS, for capacitively loaded coplanar waveguide. But, before discussing the ADS simulations for two different configurations, brief background information about the transmission line theory will be given.

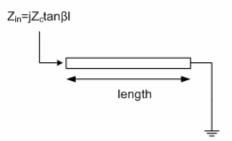

## 3.7.1 Theoretical Foundation

Input impedance of any transmission line is given by the formula:

$$Z_{in} = Z_c \frac{Z_L + jZ_c \tan\beta l}{Z_c + jZ_L \tan\beta l}$$

(3.14)

where  $Z_c$  is the characteristic impedance of the line,  $Z_L$  is the load impedance, 1 is the length and  $\beta$  is the propagation constant.

Figure 3.20: Short circuited transmission line

If the line is terminated with short circuit as in Figure 3.20, load impedance would be zero, i.e.  $Z_L=0$  and the input impedance expression takes the form:

$$Z_{in} = jZ_c \tan\beta\ell \tag{3.15}$$

where  $\beta = \frac{2\pi}{\lambda}$  and  $\beta \ell$  defines the electrical length of the line.

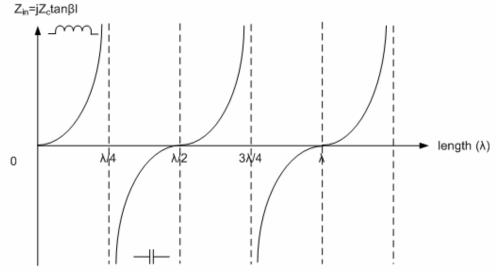

As the length of the line is changed, it can either be used as an inductor or a capacitor, as shown in Figure 3.21. This is the idea behind using a microstrip line with a

certain length as an RF choke inductor. The length of the line is adjusted in such a way that it shows a big inductance.

Figure 3.21: Input impedance versus length

At 5 GHz, the wavelength is:

$$\lambda = \frac{c}{f} = \frac{3*10^8}{5*10^9} = 6cm \tag{3.16}$$