# AN EFFICIENT H.264 INTRA FRAME CODER HARDWARE DESIGN

by ESRA ŞAHİN

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfillment of the requirements for the degree of Master of Science

> Sabancı University Spring 2006

# AN EFFICIENT H.264 INTRA FRAME CODER HARDWARE DESIGN

### APPROVED BY:

| Assist. Prof. Dr. İlker Hamzaoğlu |  |

|-----------------------------------|--|

| (Thesis Supervisor)               |  |

|                                   |  |

| Assist. Prof. Dr. Ayhan Bozkurt   |  |

|                                   |  |

|                                   |  |

| Assist. Prof. Dr. Hasan Ateş      |  |

DATE OF APPROVAL:

© Esra Şahin 2006

All Rights Reserved

#### AN EFFICIENT H.264 INTRA FRAME CODER HARDWARE DESIGN

Esra Şahin

EECS, Master Thesis, 2006

Thesis Supervisor: Assist. Prof. Dr. İlker Hamzaoğlu

#### ABSTRACT

H.264 / MPEG-4 Part 10, a recently developed international standard for video compression, offers significantly better video compression efficiency than previous international standards. Since it is impossible to implement a real-time H.264 video coder using a state-of-the-art embedded processor alone, in this thesis, we developed an efficient FPGA-based H.264 intra frame coder hardware for real-time portable applications targeting level 2.0 of baseline profile.

We first designed a high performance and low cost hardware architecture for realtime implementation of entropy coding algorithms, context adaptive variable length coding and exp-golomb coding, used in H.264 video coding standard. The hardware is implemented in Verilog HDL and verified with RTL simulations using Mentor Graphics Modelsim. We then designed a high performance and low cost hardware architecture for real-time implementation of intra prediction algorithm used in H.264 video coding standard. This hardware is also implemented in Verilog HDL and verified with RTL simulations using Mentor Graphics Modelsim.

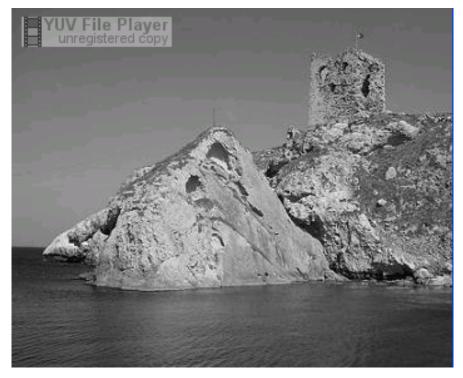

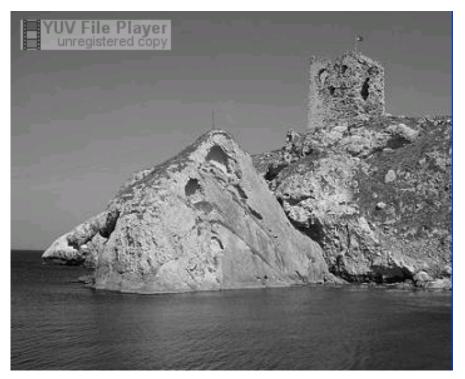

We then designed and implemented the top-level H.264 intra frame coder hardware. The hardware is implemented by integrating intra prediction, mode decision, transform-quant and entropy coding modules. The H.264 intra frame coder hardware is verified to be compliant with H.264 standard and it can code 35 CIF (352x288) frames per second. The hardware is first verified with RTL simulations using Mentor Graphics Modelsim. It is then verified to work at 71 MHz on a Xilinx Virtex II FPGA on an ARM Versatile Platform development board. The bitstream generated by the H.264 intra frame coder hardware for an input frame is successfully decoded by H.264 Joint Model (JM) reference software decoder and the decoded frame is displayed using a YUV Player tool for visual verification.

#### ETKİN BİR H.264 İNTRA ÇERÇEVE KODLAYICI DONANIM TASARIMI

Esra Şahin

EECS, Yüksek Lisans Tezi, 2006

Tez Danışmanı: Yard. Doç. Dr. İlker Hamzaoğlu

### ÖZET

Yakın tarihte geliştirilmiş uluslararası bir standart olan H.264 / MPEG4 Part 10, kendinden önceki standartlara göre belirgin şekilde daha iyi sıkıştırma verimi sunmaktadır. H.264 video kodlayıcısının son teknoloji gömülü işlemcilerle gerçek zamanlı uygulamasının imkansız olması nedeniyle bu tez çalışmasında taşınabilir uygulamalar için taban profilinin 2.0 düzeyini hedefleyen FPGA tabanlı H.264 intra çerçeve kodlayıcı donanımı geliştirilmiştir.

Öncelikle, H.264 standardında kullanılan entropy kodlamasi algoritması icin gerçek zamanlı çalışan yüksek performanslı ve düşük maliyetli bir donanım mimarisi Verilog HDL kullanılarak tasarlanmıştır. Tasarımın doğrulama işlemi Mentor Graphics Modelsim benzetim programı kullanılarak "RTL" benzetimleri ile gerçekleştirilmiştir. Daha sonra, H.264 standardında kullanılan intra tahmin algoritması için gerçek zamanlı çalışan düşük maliyetli bir donanım mimarisi tasarlanmıştır. Bu donanım da yine Verilog HDL kullanılarak gerçekleştirilmiş ve Mentor Graphics Modelsim benzetim programı kullanılarak gerçekleştirilmiş ve Mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı kullanılarak mentor Graphics Modelsim benzetim programı benzetim benzetim benzetim benzetim benzetim benzetim benzetim benzetim benzetim benzetim benzeti

Daha sonra, H.264 intra çerçeve kodlayıcı donanımı tasarlanmış ve gerçekleştirilmiştir. Donanım intra tahmin, moda karar verme, dönüşüm-nicemleme ve entropy kodlamasi modülleri entegre edilerek gerçekleştirilmiştir. Kodlayıcı donanımının H.264 standardıyla tamamen uyumlu olduğu doğrulanmıştır. Kodlayıcı saniyede 35 CIF (352x288) çerçevesini kodlayabilmektedir. Tasarım, Mentor Graphics Modelsim benzetim programı kullanılarak "RTL" benzetimleri ile doğrulanmıştır. Daha sonra, donanımın 71MHz hızla çalışması "ARM Versalite Platform" geliştirme ortamında doğrulanmıştır. H.264 intra çerçeve kodlayıcı donanımı ile bir girdi çerçeve için oluşturulan "bitstream" H.264 Joint Model (JM) şifre çözücü ile başarılı bir biçimde çözülmüş ve şifresi çözülen çerçeve "YUV Player" programı kullanılarak görsel anlamda doğrulanmıştır.

To My Mother and Father, and to My Sister Esin...

#### ACKNOWLEDGEMENTS

I would like to express my deep appreciation to my supervisor, Assist. Prof. Dr. Ilker Hamzaoglu, for his skills, enthusiasm, unconditional support, guidance and patience during the process of this thesis. I appreciate very much for his suggestions, detailed reviews and invaluable advices. I feel myself privileged as his student.

I also want to thank Assist. Prof. Dr. Yucel Altunbasak, who played an important role in initiating H.264 research project at Sabanci University; Assist. Prof. Dr. Hasan Ates, for his excellent help with particular issues; and Assist. Prof. Dr. Ayhan Bozkurt, who participiated in my thesis jury.

Thanks also my partners in H.264 research project, Ozgur Tasdizen, Mehmet Guney, and Sinan Yalcin, for valuable discussions and feedback throughout the project.

Special thanks due to my family. This thesis is dedicated with love and gratitude to my parents and my sister for their constant support and encouragement for going through my tough periods with me.

I am indebted to Yasin Erdogan, whose part in my own success is so vast I can not measure.

My warmest thanks go to Serkan Oktem for his friendship.

Finally, my acknowledgements go to Sabanci University for supporting our H.264 research project.

# TABLE OF CONTENTS

| ABSTRACT                                                     | iv   |

|--------------------------------------------------------------|------|

| ÖZET                                                         | v    |

| ACKNOWLEDGEMENTS                                             | vii  |

| TABLE OF CONTENTS                                            | viii |

| LIST OF FIGURES                                              | xi   |

| LIST OF TABLES                                               | xiii |

| ABBREVIATIONS                                                | xiv  |

| CHAPTER 1                                                    | 1    |

| INTRODUCTION                                                 | 1    |

| 1.1 Motivation                                               | 1    |

| 1.2 Thesis Organization                                      | 6    |

| CHAPTER 2                                                    | 7    |

| HARDWARE ARCHITECURES FOR H.264 INTRA PREDICTION ALGORITHM . | 7    |

| 2.1 H.264 Intra Prediction Algorithm Overview                | 7    |

| 2.2 Proposed Hardware Architecture                           | 18   |

| 2.2.1 Intra Prediction Hardware for Search & Mode Decision   | 19   |

| 2.2.1.1 Proposed Hardware for 4x4 Luma Prediction Modes      | 22   |

| 2.2.1.2 Proposed Hardware for 16x16 Luma Prediction Modes    | 28   |

| 2.2.1.3 Proposed Hardware for 8x8 Chroma Prediction Modes    | 38   |

| 2.2.1.4 Implementation Results                               | 42   |

| 2.2.2 Intra Prediction Hardware for Coder                    | 44   |

| 2.2.2.1 Proposed Hardware for 4x4 Luma Prediction Modes      | 47   |

| 2.2.2.2 Proposed Hardware for 16x16 Luma Prediction Mode                   | 52 |

|----------------------------------------------------------------------------|----|

| 2.2.2.3 Proposed Hardware for 8x8 Chroma Prediction Modes                  | 54 |

| 2.2.2.4 Implementation Results                                             | 56 |

| CHAPTER 3                                                                  | 57 |

| HARDWARE ARCHITECTURES FOR H.264 ENTROPY CODER                             | 57 |

| 3.1 H.264 Context-based Adaptive Variable Length Coding (CAVLC)            | 58 |

| 3.1.1 H.264 CAVLC Algorithm Overview                                       | 59 |

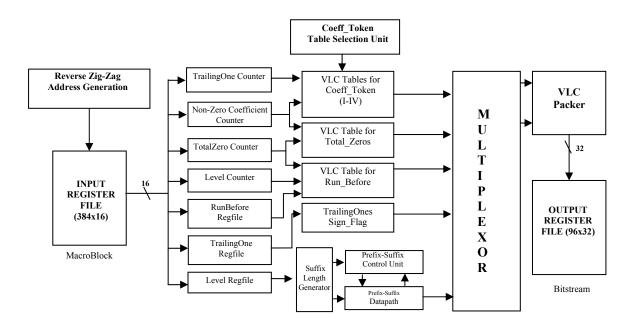

| 3.1.2 Proposed Hardware Architecture                                       | 63 |

| 3.1.2.1 VLC Counters and Reverse Zig-zag Ordering                          | 63 |

| 3.1.2.2 CAVLC Hardware for Generating Coeff_Token                          | 64 |

| 3.1.2.3 CAVLC Hardware for Encoding Level                                  | 67 |

| 3.1.2.4 VLC Packer                                                         | 69 |

| 3.1.3 Implementation Results                                               | 70 |

| 3.2 H.264 Exponential-Golomb Variable Length Entropy Coding                | 71 |

| 3.2.1 Exponential-Golomb Variable Length Entropy Coding Algorithm Overview | 71 |

| 3.2.1.1 Exponential-Golomb Codes                                           | 71 |

| 3.2.1.2 Sequence Syntax Elements                                           | 73 |

| 3.2.1.2 Picture Syntax Elements                                            | 74 |

| 3.2.1.3 Slice Syntax Elements                                              | 74 |

| 3.2.1.4 Macroblock Syntax Elements                                         | 75 |

| 3.2.2 Proposed Hardware Architecture                                       | 81 |

| 3.2.3 Implementation Results                                               | 82 |

| CHAPTER 4                                                                  | 83 |

| TOP LEVEL H.264 INTRA FRAME CODER HARDWARE                                 | 83 |

| 4.1 Proposed Hardware Architecture                                         | 83 |

| 4.1.1 Search & Mode Decision Hardware                                      | 85 |

| 4.1.2 Coder Hardware                                                       | 92 |

| 4.1.3 Implementation Results | 96  |

|------------------------------|-----|

| CHAPTER 5                    | 98  |

| CONCLUSIONS AND FUTURE WORK  | 98  |

| 5.1 Conclusions              | 98  |

| 5.2 Future Work              | 99  |

| REFERENCES                   | 100 |

# LIST OF FIGURES

| Figure 1.1 H.264 Encoder Block Diagram                                   | 2  |

|--------------------------------------------------------------------------|----|

| Figure 1.2 H.264 Intra Frame Coder Block Diagram                         | 4  |

| Figure 2.1 A 4x4 Luma Block and Neighboring Pixels                       | 8  |

| Figure 2.2 4x4 Luma Prediction Modes                                     | 9  |

| Figure 2.3 Examples of Real Images for 4x4 Luma Prediction Modes         | 9  |

| Figure 2.4 Prediction Equations for 4x4 Luma Prediction Modes            | 12 |

| Figure 2.5 16x16 Luma Prediction Modes                                   | 13 |

| Figure 2.6 Examples of Real Images for 16x16 Luma Prediction Modes       | 13 |

| Figure 2.7 Prediction Equations for 16x16 Luma Prediction Modes          | 15 |

| Figure 2.8 Prediction Equations for 8x8 Chroma Prediction Modes          | 18 |

| Figure 2.9 Intra Prediction Hardware for Search & Mode Decision          | 20 |

| Figure 2.10 Organized Prediction Equations for 4x4 Luma Prediction Modes | 25 |

| Figure 2.11 Datapath for 4x4 Luma Prediction Modes                       |    |

| Figure 2.12 Organized Prediction Equations for 16x16 Luma Plane Mode     | 36 |

| Figure 2.13 Datapath for 16x16 Luma Prediction Modes                     | 37 |

| Figure 2.14 Organized Prediction Equations for 8x8 Luma Plane Mode       | 40 |

| Figure 2.15 Intra Prediction Hardware for Coder                          | 46 |

| Figure 2.16 Organized Prediction Equations for 4x4 Luma Prediction Modes | 50 |

| Figure 2.17 Datapath for 4x4 Luma Prediction Modes                       | 51 |

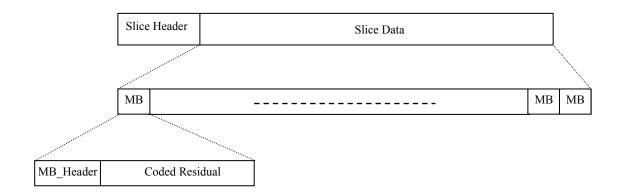

| Figure 3.1 Slice Syntax                                                  | 57 |

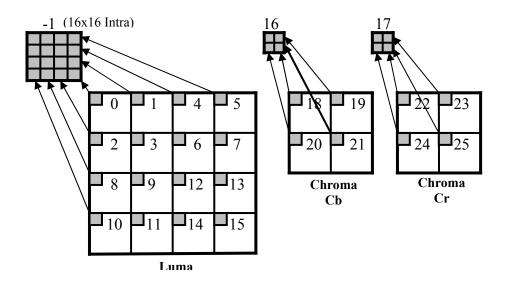

| Figure 3.2 Coding Order of Blocks in a Macroblock                        | 59 |

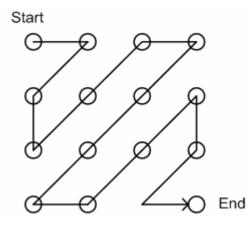

| Figure 3.3 Zig-zag scan for a 4x4 luma block                             | 60 |

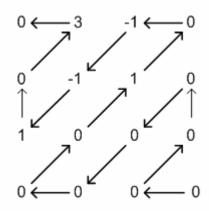

| Figure 3.4 Example of coding a 4x4 block by CAVLC                        |    |

| Figure 3.5 CAVLC Block Diagram                                           | 63 |

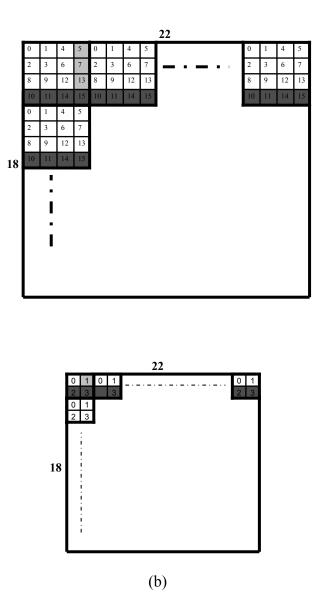

| Figure 3.6 Macroblocks in a CIF Frame (a) Luma, (b) Chroma Cb and Cr     | 66 |

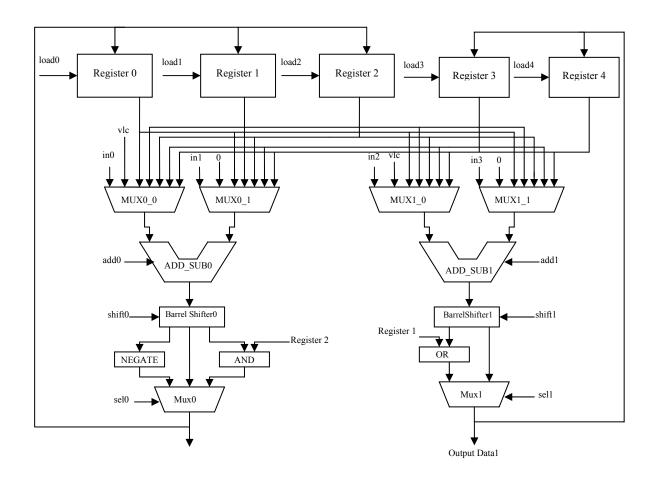

| Figure 3.7 Datapath for Coding Level Prefix and Level Suffix             | 68 |

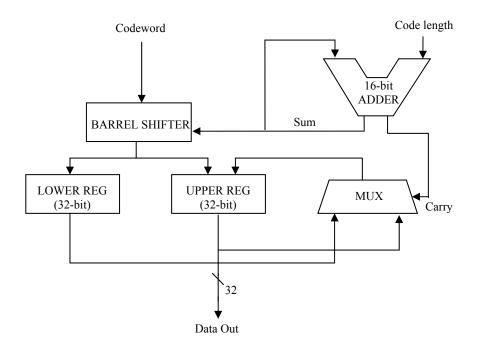

| Figure 3.8 VLC Packer Datapath                                           | 69 |

| Figure 3.9 Current and neighboring 4x4 luma blocks                       | 78 |

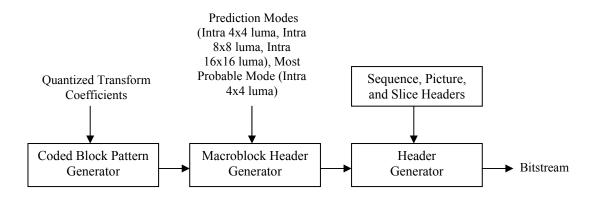

| Figure 3.10 Block Diagram of Header Generation Hardware                  | 81 |

| Figure 4.1 H.264 Intra Frame Coder Block Diagram                         | 83 |

| Figure 4.2 H.264 Intra Frame Coder Block Diagram                         | 84 |

| Figure 4.3 Block Diagram of Search & Mode Decision Hardware              | 86 |

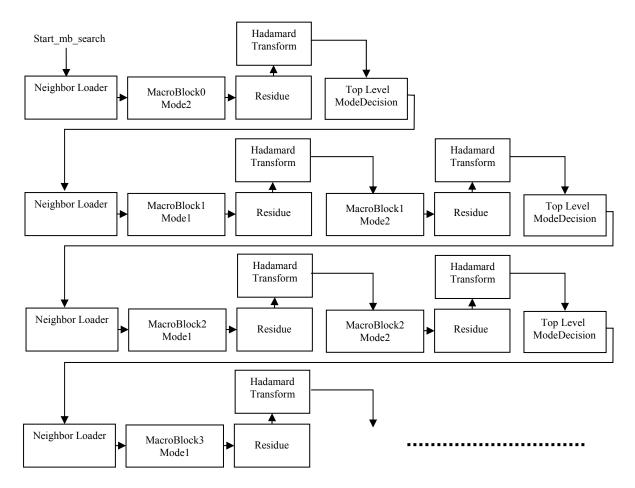

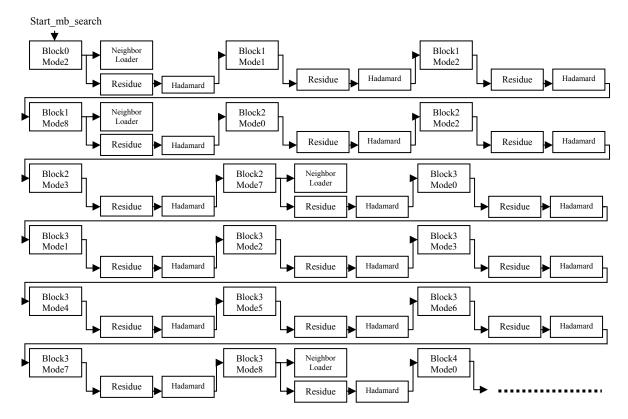

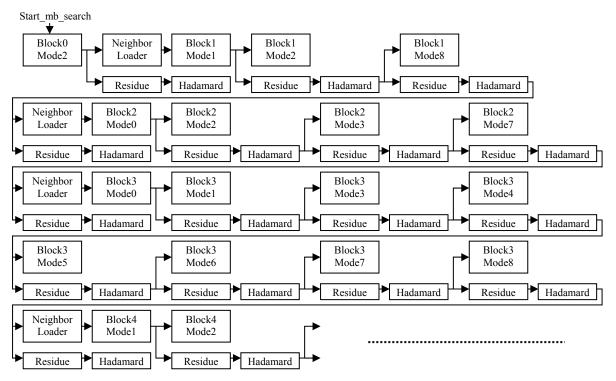

| Figure 4.4 Schedule for 16x16 Luma Prediction Modes                 | 87 |

|---------------------------------------------------------------------|----|

| Figure 4.5 Initial Schedule for 4x4 Luma Prediction Modes           | 88 |

| Figure 4.6 Final Schedule for 4x4 Luma Prediction Modes             | 89 |

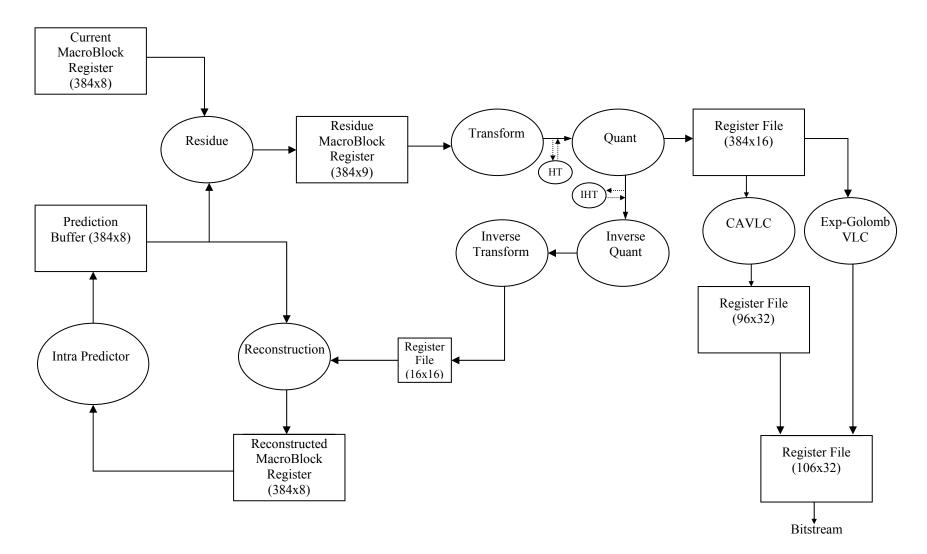

| Figure 4.7 Block Diagram of Coder Hardware                          | 93 |

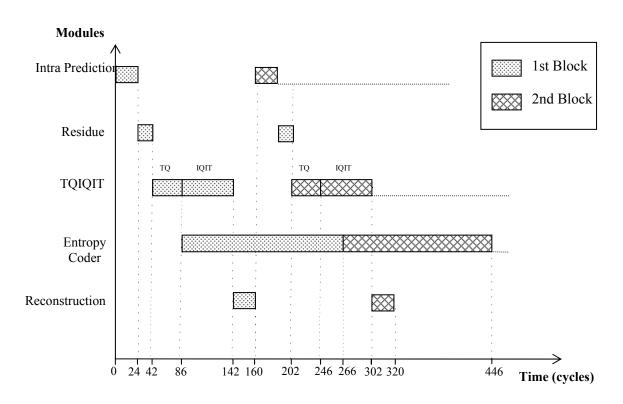

| Figure 4.8 Coder Hardware Scheduling for 4x4 Intra Modes            | 94 |

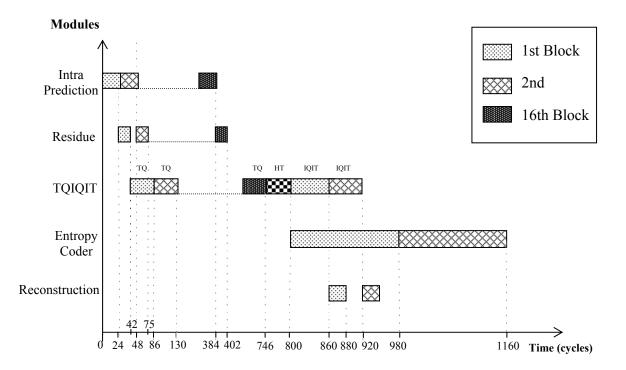

| Figure 4.9 Coder Hardware Scheduling for 16x16 Intra Modes          | 95 |

| Figure 4.10 Visual Verification of H.264 Intra Frame Coder Hardware | 97 |

## LIST OF TABLES

| Table 2.1 Availability of 4x4 Luma Prediction Modes                                       |

|-------------------------------------------------------------------------------------------|

| Table 2.2 Availability of 16x16 Luma Prediction Modes                                     |

| Table 2.3 Availability of 8x8 Chroma Prediction Modes    16                               |

| Table 2.4 Clock Cycles Required for Performing Available 4x4 Luma Prediction Modes 26     |

| Table 2.5 Clock Cycles Required for Performing Available 16x16 Luma Prediction Modes37    |

| Table 2.6 Clock Cycles Required for Performing Available 8x8 Chroma Prediction Modes41    |

| Table 2.7 Clock Cycles Required for Performing Available 16x16 Luma Prediction Modes42    |

| Table 2.8 Clock Cycles Required for Performing Available 8x8 Chroma Prediction Modes43    |

| Table 2.9 Clock Cycles Required for Performing Available 4x4 Luma Prediction Modes 43     |

| Table 2.10 Clock cycles required for performing the selected 4x4 Luma Prediction Modes 51 |

| Table 2.11 Clock Cycles Required for Performing Selected 16x16 Luma Prediction Modes53    |

| Table 2.12 Clock Cycles Required for Performing Selected 8x8 Chroma Prediction Modes 55   |

| Table 3.1 Macroblock Syntax Elements   58                                                 |

| Table 3.2 VLC Table for Coeff_Token    61                                                 |

| Table 3.3 Thresholds for determining whether to increment SuffixLength                    |

| Table 3.4 Exp-Golomb codewords   72                                                       |

| Table 3.5 Sequence Syntax Elements    73                                                  |

| Table 3.6 Picture Syntax Elements   74                                                    |

| Table 3.7 Macroblock Syntax Elements    75                                                |

| Table 3.8 Specification of CodedBlockPatternChroma                                        |

| Table 3.9 Macroblock types for I slices    77                                             |

| Table 3.10 Predictive coding of a 4x4 luma prediction mode    79                          |

|                                                                                           |

| Table 3.11 Exp-Golomb codes for 8x8 chroma prediction modes       80                      |

## **ABBREVIATIONS**

| ARM                                      | Advanced RISC Machines                                                                                                                                                                                                      |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASIC                                     | Application Specific Integrated Circuit                                                                                                                                                                                     |

| AVC                                      | Advanced Video Coding                                                                                                                                                                                                       |

| CABAC                                    | Context-Adaptive Binary Arithmetic Coding                                                                                                                                                                                   |

| CAVLC                                    | Context Adaptive Variable Length Coding                                                                                                                                                                                     |

| CIF                                      | Common Intermediate Format                                                                                                                                                                                                  |

| CODEC                                    | Coder, Decoder Pair                                                                                                                                                                                                         |

| CPU                                      | Central Processing Unit                                                                                                                                                                                                     |

| DFF                                      | D Flip Flop                                                                                                                                                                                                                 |

| DSP                                      | Digital Signal Processor                                                                                                                                                                                                    |

| DVD                                      | Digital Versatile Disc                                                                                                                                                                                                      |

| FPGA                                     | Field Programmable Gate Array                                                                                                                                                                                               |

| HDL                                      | Hardware Description Language                                                                                                                                                                                               |

| ISDN                                     | Integrated Services Digital Network                                                                                                                                                                                         |

|                                          |                                                                                                                                                                                                                             |

| ISO/IEC                                  | International Standards Organization, International Electrotechnical                                                                                                                                                        |

| ISO/IEC                                  | International Standards Organization, International Electrotechnical<br>Commission                                                                                                                                          |

| ISO/IEC<br>ITU-T                         | -                                                                                                                                                                                                                           |

|                                          | Commission                                                                                                                                                                                                                  |

|                                          | Commission<br>International Telecommunications Union, Telecommunications                                                                                                                                                    |

| ITU-T                                    | Commission<br>International Telecommunications Union, Telecommunications<br>Standardization Sector                                                                                                                          |

| ITU-T<br>JVT                             | Commission<br>International Telecommunications Union, Telecommunications<br>Standardization Sector<br>Joint Video Team                                                                                                      |

| ITU-T<br>JVT<br>LCD                      | Commission<br>International Telecommunications Union, Telecommunications<br>Standardization Sector<br>Joint Video Team<br>Liquid Crystal Display                                                                            |

| ITU-T<br>JVT<br>LCD<br>MB                | Commission<br>International Telecommunications Union, Telecommunications<br>Standardization Sector<br>Joint Video Team<br>Liquid Crystal Display<br>Macroblock                                                              |

| ITU-T<br>JVT<br>LCD<br>MB<br>MPEG        | Commission<br>International Telecommunications Union, Telecommunications<br>Standardization Sector<br>Joint Video Team<br>Liquid Crystal Display<br>Macroblock<br>Motion Picture Experts Group                              |

| ITU-T<br>JVT<br>LCD<br>MB<br>MPEG<br>NAL | Commission<br>International Telecommunications Union, Telecommunications<br>Standardization Sector<br>Joint Video Team<br>Liquid Crystal Display<br>Macroblock<br>Motion Picture Experts Group<br>Network Abstraction Layer |

| QCIF | Quadrature Common Intermediate Format  |

|------|----------------------------------------|

| QP   | Quantization Parameter                 |

| SAD  | Sum of Absolute Difference             |

| SATD | Sum of Absolute Transformed Difference |

| SRAM | Static Random Access Memory            |

| UMC  | United Microelectronic Corporation     |

| VCL  | Video Coding Layer                     |

| VGA  | Video Graphics Array                   |

| VLC  | Variable-Length Coding                 |

## **CHAPTER 1**

### **INTRODUCTION**

#### 1.1 Motivation

Video compression systems are used in many commercial products, from consumer electronic devices such as digital camcorders, cellular phones to video teleconferencing systems. These applications make the video compression hardware devices an inevitable part of many commercial products. To improve the performance of the existing applications and to enable the applicability of video compression to new real-time applications, recently, a new international standard for video compression is developed. This new standard, offering significantly better video compression efficiency than previous video compression standards, is developed with the collaboration of ITU and ISO standardization organizations. Hence it is called with two different names, H.264 and MPEG4 Part 10.

H.264 video coding standard has a much higher coding efficiency potential (capable of saving up to %50 bit rate at the same level of video quality) than the previous standards. Due to its high coding efficiency and due to its flexibility and robustness to different communication environments, in the near future, H.264 is expected to be widely used in many applications such as digital TV, DVD, video transmisson in wireless networks, and video conferencing over the internet.

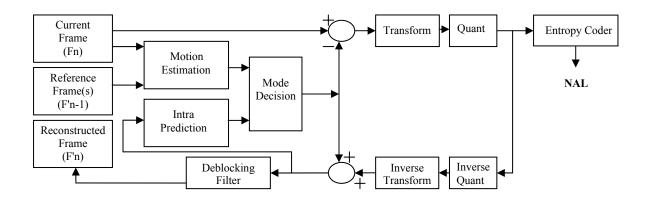

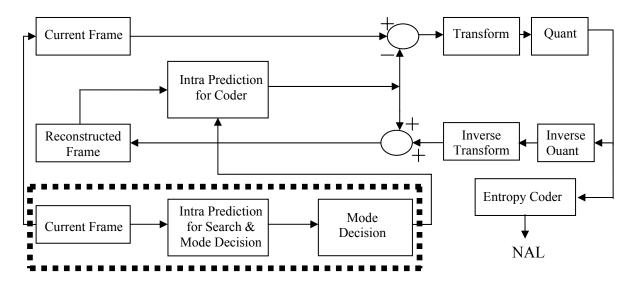

The video compression efficiency achieved in H.264 standard is not a result of any single feature but rather a combination of a number of encoding tools. The top-level block diagram of an H.264 Encoder is shown in Figure 1.1.

Figure 1.1 H.264 Encoder Block Diagram

The H.264 standard includes a Video Coding Layer (VCL), which efficiently represents the video content, and a Network Abstraction Layer (NAL), which formats the VCL representation of the video and provides header information in a manner suitable for transportation by particular transport layers or storage media [1].

As shown in Figure 1.1, an H.264 encoder has a forward path and a reconstruction path. The forward path is used to encode a video frame by using intra and inter predictions and to create the bit stream. The reconstruction path is used to decode the encoded frame and to reconstruct the decoded frame. Since a decoder never gets original images, but rather works on the decoded frames, reconstruction path in the encoder ensures that both encoder and decoder use identical reference frames for intra and inter prediction. This avoids possible encoder – decoder mismatches [1, 3, 4].

Forward path starts with partitioning the input frame into MBs. Each MB is encoded in intra or inter mode depending on the mode decision. In both intra and inter modes, the current MB is predicted from the reconstructed frame. Intra mode generates the predicted MB based on spatial redundancy, whereas inter mode, generates the predicted MB based on temporal redundancy. Mode decision compares the required amount of bits to encode a MB and the quality of the decoded MB for both of these modes and chooses the mode with better quality and bit-rate performance. In either case, intra or inter mode, the predicted MB is subtracted from the current MB to generate the residual MB. Residual MB is transformed using 4x4 and 2x2 integer transforms. Transformed residual data is quantized and quantized transform coefficients are re-ordered in a zig-zag scan order. The reordered quantized transform coefficients are entropy encoded. The entropy-encoded coefficients together with header information, such as MB prediction mode and quantization step size, form the compressed bit stream. The compressed bit stream is passed to network abstraction layer (NAL) for storage or transmission [1, 3, 4].

Reconstruction path begins with inverse quantization and inverse transform operations. The quantized transform coefficients are inverse quantized and inverse transformed to generate the reconstructed residual data. Since quantization is a lossy process, inverse quantized and inverse transformed coefficients are not identical to the original residual data. The reconstructed residual data are added to the predicted pixels in order to create the reconstructed frame. A deblocking filter is applied to reduce the effects of blocking artifacts in the reconstructed frame [1, 3, 4].

Since it is impossible to implement a real-time H.264 video coder using a state-ofthe-art embedded processor alone, in this thesis, we developed an efficient FPGA-based H.264 intra frame coder hardware for real-time portable applications targeting level 2.0 of baseline profile.

H.264 intra frame coder is a competitive alternative to JPEG2000 for still image compression, in terms of both coding efficiency and encoder/decoder complexity [2, 11, 12, 13]. The rate-distortion performance of H.264 intra frame coder using CABAC and R-D optimized mode decision is about the same as that of JPEG2000 with default optimized settings. The use of CAVLC for entropy coding results in about 0.5 dB loss in coding efficiency, and with low-complexity mode decision (R-D optimization turned off) there is an additional loss which is less than 0.5 dB. Without R-D optimized mode decision, the computational complexity of the H.264 encoder is similar to that of JPEG2000 encoder; but the decoding complexity of H.264 is much lower than that of JPEG2000. Moreover, H.264 coding algorithm is easier to implement in hardware, due to its use of block-based processing, which reduces the memory requirements and allows for a pipelined approach.

Another application area for H.264 intra frame coder is in motion picture production, editing and archiving, where video frames are coded as I-frames only to allow for random access to each individual picture. For such applications, H.264 is shown to be superior to Motion-JPEG2000, especially at lower resolutions [2, 11, 12, 13].

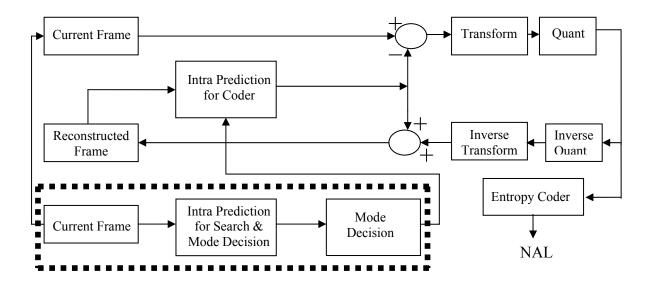

The block diagram of the proposed H.264 intra frame coder hardware is shown in Figure 1.2.

Figure 1.2 H.264 Intra Frame Coder Block Diagram

The intra prediction algorithm used in H.264 reduces spatial redundancies by exploiting the spatial correlation between adjacent blocks in a given picture. Each picture is divided into 16×16 pixel MBs and each MB is composed of luma and chroma components. Intra prediction module predicts the pixels in a MB using the pixels in the available neighboring blocks. For the luma component of a MB, a 16x16 predicted luma block is formed either by performing intra predictions for each 4x4 luma block in the MB or by performing intra prediction modes for a 16x16 luma block. For the chroma components of a MB, a predicted 8x8 chroma block is formed for each 8x8 chroma component by performing intra prediction for the MB. There are four prediction modes for each chroma component. Additional information for intra prediction algorithm and the proposed hardware for intra prediction are given in Chapter 2.

Context Adaptive Variable Length Coding (CAVLC) algorithm encodes transformed and quantized residual luminance and chrominance data. CAVLC uses multiple tables for a syntax element. It adapts to the current context by selecting one of these tables for a given syntax element based on the already transmitted syntax elements. Information other than the residual data is coded using Exp-Golomb code words [3, 4, 5]. Additional information for entropy coding algorithm and the proposed hardware for entropy coding are given in Chapter 3.

Transform algorithm is based on a 4x4 integer transform. The algorithm does not include any floating point operations; it only uses integer addition and binary shift operations. In this way, a possible drift between encoder and decoder is avoided. H.264 is the first standard to attain exact equality of decoded video content from all decoders [3, 4, 5]. Detailed information about transform algorithm and the proposed hardware for transform are given in [6].

The quantization algorithm uses a non-uniform quantizer. Quantization parameter can take a value between 0-51. The quantization step size doubles for an increment of 6 in quantization parameter. That means an increment of 1 in quantization parameter results in 12.2% increment in quantization step size. The quantization algorithm requires an integer multiplication [8, 9, 10]. Detailed information about quantization algorithm and the proposed hardware for quantization are given in [6].

The mode decision algorithm compares the 4x4 and 16x16 predictions and selects the best luma prediction mode for the MB. 4x4 prediction modes are generally selected for highly textured regions while 16x16 prediction modes are selected for flat regions. Each 8x8 chroma component of an intra coded MB is predicted from previously encoded and reconstructed chroma samples above and/or to the left and both chroma components always use the same prediction mode. The mode decision algorithm compares the 8x8 predictions and selects the best chroma prediction mode for the MB. Mode decision algorithm implemented in the proposed mode decision hardware is the same as the algorithm implemented in the JM Software when there is no Rate-Distortion optimization [4]. Additional information for mode decision algorithm and the proposed hardware for mode decision are given in Chapter 4.

## **1.2 Thesis Organization**

The rest of the thesis is organized as follows.

Chapter 2 explains intra prediction hardware designed as part of H.264 intra frame coder hardware. First, it introduces intra prediction algorithm used in H.264 / MPEG4 Part 10 video coding standard. Then it describes the designed hardware in detail and the implementation results are given.

Chapter 3 explains entropy coding hardware designed as part of H.264 intra frame coder hardware. First, it introduces entropy coding algorithm used in H.264 / MPEG4 Part 10 video coding standard. Then it describes the designed hardware in detail and the implementation results are given.

Chapter 4 explains the top-level intra frame coder hardware. The modules used in the intra frame coder hardware and their scheduling are explained.

Chapter 5 presents the conclusions and the future work.

### **CHAPTER 2**

# HARDWARE ARCHITECURES FOR H.264 INTRA PREDICTION ALGORITHM

The video compression efficiency achieved in H.264 standard is not a result of any single feature but rather a combination of a number of encoding tools. As it is shown in the top-level block diagram of an H.264 encoder in Figure 1.1, one of these tools is the intra prediction algorithm used in the baseline profile of H.264 standard [3, 4, 5]. Intra prediction algorithm generates a prediction for a MB based on spatial redundancy. H.264 intra prediction algorithm achieves better coding results than the intra prediction algorithms used in the previous video compression standards. However, this coding gain comes with an increase in encoding complexity which makes it is an exciting challenge to have a real-time implementation of intra prediction for H.264 video coding.

#### 2.1 H.264 Intra Prediction Algorithm Overview

Intra prediction algorithm predicts the pixels in a MB using the pixels in the available neighboring blocks. For the luma component of a MB, a 16x16 predicted luma block is formed by performing intra predictions for each 4x4 luma block in the MB and by performing intra prediction for the 16x16 MB. There are nine prediction modes for each 4x4 luma block and four prediction modes for a 16x16 luma block. A mode decision algorithm is then used to compare the 4x4 and 16x16 predictions and select the best luma

prediction mode for the MB. 4x4 prediction modes are generally selected for highly textured regions while 16x16 prediction modes are selected for flat regions.

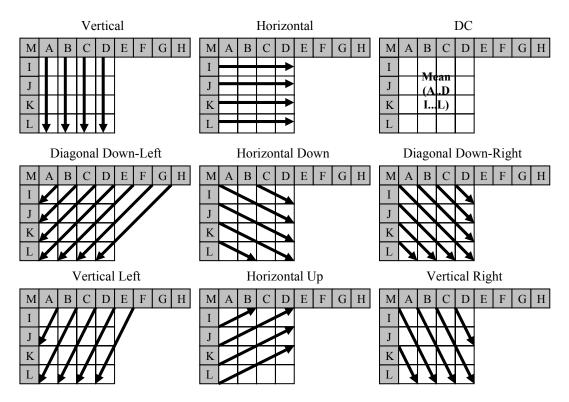

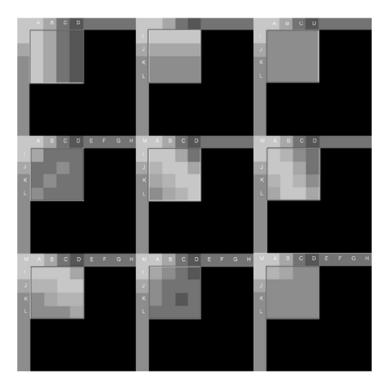

There are nine 4x4 luma prediction modes designed in a directional manner. A 4x4 luma block consisting of the pixels a to p is shown in Figure 2.1. The pixels A to M belong to the neighboring blocks and are assumed to be already encoded and reconstructed and are therefore available in the encoder and decoder to generate a prediction for the current MB. Each 4x4 luma prediction mode generates 16 predicted pixel values using some or all of the neighboring pixels A to M as shown in Figure 2.2. The examples of each 4x4 luma prediction mode for real images are given in Figure 2.3. The arrows indicate the direction of prediction in each mode. The predicted pixels are calculated by a weighted average of the neighboring pixels A-M for each mode except Vertical and Horizontal modes.

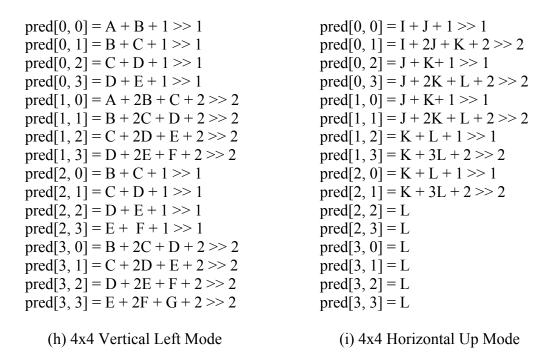

The prediction equations used in each 4x4 luma prediction mode are shown in Figure 2.4 where [y,x] denotes the position of the pixel in a 4x4 block (the top left, top right, bottom left, and bottom right positions of a 4x4 block are denoted as [0, 0], [0, 3], [3, 0], and [3, 3], respectively) and pred[y,x] is the prediction for the pixel in the position [y,x].

| М | Α | В | С | D | Е | F | G | Η |

|---|---|---|---|---|---|---|---|---|

| Ι | a | b | c | d |   |   |   |   |

| J | e | f | g | h |   |   |   |   |

| Κ | i | j | k | 1 |   |   |   |   |

| L | m | n | 0 | р |   |   |   |   |

Figure 2.1 A 4x4 Luma Block and Neighboring Pixels

DC mode is always used regardless of the availability of the neighboring pixels. However, it is adopted based on which neighboring pixels A-M are available. If pixels E, F, G and H have not yet been encoded and reconstructed, the value of pixel D is copied to these positions and they are marked as available for DC mode. The other prediction modes can only be used if all of the required neighboring pixels are available [4, 5]. Available 4x4 luma prediction modes for a 4x4 luma block depending on the availability of the neighboring 4x4 luma blocks are given in Table 2.1.

Figure 2.2 4x4 Luma Prediction Modes

Figure 2.3 Examples of Real Images for 4x4 Luma Prediction Modes

| pred[0, 0] = A | pred[0, 0] = I |

|----------------|----------------|

| pred[0, 1] = B | pred[0, 1] = I |

| pred[0, 2] = C | pred[0, 2] = I |

| pred[0, 3] = D | pred[0, 3] = I |

| pred[1, 0] = A | pred[1, 0] = J |

| pred[1, 1] = B | pred[1, 1] = J |

| pred[1, 2] = C | pred[1, 2] = J |

| pred[1, 3] = D | pred[1, 3] = J |

| pred[2, 0] = A | pred[2, 0] = K |

| pred[2, 1] = B | pred[2, 1] = K |

| pred[2, 2] = C | pred[2, 2] = K |

| pred[2, 3] = D | pred[2, 3] = K |

| pred[3, 0] = A | pred[3, 0] = L |

| pred[3, 1] = B | pred[3, 1] = L |

| pred[3, 2] = C | pred[3, 2] = L |

| pred[3, 3] = D | pred[3, 3] = L |

|                |                |

(a) 4x4 Vertical Mode

(b) 4x4 Horizontal Mode

pred[y,x] = (A + B + C + D + I + J + K + L + 4) >> 3(If the left and the top neighboring pixels are available)

pred[y,x] = (I + J + K + L + 2) >> 2(Else If only the left neighboring pixels are available)

pred[y,x] = (A + B + C + D + 2) >> 2(Else If only the top neighboring pixels are available)

pred[y,x] = 128(Else //If the left and the upper neighboring pixels are not available)

(c) 4x4 DC Mode

| pred[0, 0] = A + 2B + C + 2 >> 2 |

|----------------------------------|

| pred[0, 1] = B + 2C + D + 2 >> 2 |

| pred[0, 2] = C + 2D + E + 2 >> 2 |

| pred[0, 3] = D + 2E + F + 2 >> 2 |

| pred[1, 0] = B + 2C + D + 2 >> 2 |

| pred[1, 1] = C + 2D + E + 2 >> 2 |

| pred[1, 2] = D + 2E + F + 2 >> 2 |

| pred[1, 3] = E + 2F + G + 2 >> 2 |

| pred[2, 0] = C + 2D + E + 2 >> 2 |

| pred[2, 1] = D + 2E + F + 2 >> 2 |

| pred[2, 2] = E + 2F + G + 2 >> 2 |

| pred[2, 3] = F + 2G + H + 2 >> 2 |

| pred[3, 0] = D + 2E + F + 2 >> 2 |

| pred[3, 1] = E + 2F + G + 2 >> 2 |

| pred[3, 2] = F + 2G + H + 2 >> 2 |

| pred[3, 3] = G + 3H + 2 >> 2     |

| (d) 4x4 Diagonal Down Left Mod | e |

|--------------------------------|---|

|--------------------------------|---|

| pred[0, 0] = A + 2M + I + 2 >> 2 |

|----------------------------------|

| pred[0, 1] = M + 2A + B + 2 >> 2 |

| pred[0, 2] = A + 2B + C + 2 >> 2 |

| pred[0, 3] = B + 2C + D + 2 >> 2 |

| pred[1, 0] = M + 2I + J + 2 >> 2 |

| pred[1, 1] = A + 2M + I + 2 >> 2 |

| pred[1, 2] = M + 2A + B + 2 >> 2 |

| pred[1, 3] = A + 2B + C + 2 >> 2 |

| pred[2, 0] = I + 2J + K + 2 >> 2 |

| pred[2, 1] = M + 2I + J + 2 >> 2 |

| pred[2, 2] = A + 2M + I + 2 >> 2 |

| pred[2, 3] = M + 2A + B + 2 >> 2 |

| pred[3, 0] = J + 2K + L + 2 >> 2 |

| pred[3, 1] = I + 2J + K + 2 >> 2 |

| pred[3, 2] = M + 2I + J + 2 >> 2 |

| pred[3, 3] = A + 2M + I + 2 >> 2 |

(e) 4x4 Diagonal Down Right Mode

pred[0, 0] = M + A + 1 >> 1pred[0, 1] = A + B + 1 >> 1pred[0, 2] = B + C + 1 >> 1pred[0, 3] = C + D + 1 >> 1pred[1, 0] = I + 2M + A + 2 >> 2pred[1, 1] = M + 2A + B + 2 >> 2pred[1, 2] = A + 2B + C + 2 >> 2pred[1, 3] = B + 2C + D + 2 >> 2pred[2, 0] = M + 2I + J + 2 >> 2pred[2, 1] = M + A + 1 >> 1pred[2, 2] = A + B + 1 >> 1pred[2, 3] = B + C + 1 >> 1pred[3, 0] = I + 2J + K + 2 >> 2pred[3, 1] = I + 2M + A + 2 >> 2pred[3, 2] = M + 2A + B + 2 >> 2pred[3, 3] = A + 2B + C + 2 >> 2

(f) 4x4 Vertical Right Mode

pred[0, 0] = M + I + 1 >> 1pred[0, 1] = I + 2M + A + 2 >> 2pred[0, 2] = B + 2A + M + 2 >> 2pred[0, 3] = C + 2B + A + 2 >> 2pred[1, 0] = I + J + 1 >> 1pred[1, 1] = M + 2I + J + 2 >> 2pred[1, 2] = M + I + 1 >> 1pred[1, 3] = I + 2M + A + 2 >> 2pred[2, 0] = J + K + 1 >> 1pred[2, 1] = I + 2J + K + 2 >> 2pred[2, 2] = I + J + 1 >> 1pred[2, 3] = M + 2I + J + 2 >> 2pred[3, 0] = K + L + 1 >> 1pred[3, 1] = J + 2K + L + 2 >> 2pred[3, 2] = J + K + 1 >> 1pred[3, 3] = I + 2J + K + 2 >> 2

(g) 4x4 Horizontal Down Mode

Figure 2.4 Prediction Equations for 4x4 Luma Prediction Modes

| Availability of Neighboring       | Available 4x4 Luma            |

|-----------------------------------|-------------------------------|

| 4x4 Luma Blocks                   | Prediction Modes              |

| None available                    | DC                            |

| Left available, Top not available | Horizontal, DC, Horizontal Up |

| Top available, Left not available | Vertical Right, DC, Vertical  |

|                                   | Left, Diagonal Down-Left      |

| Both available                    | All Modes                     |

Table 2.1 Availability of 4x4 Luma Prediction Modes

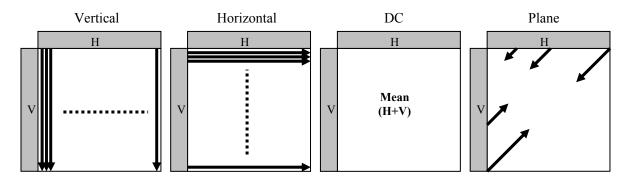

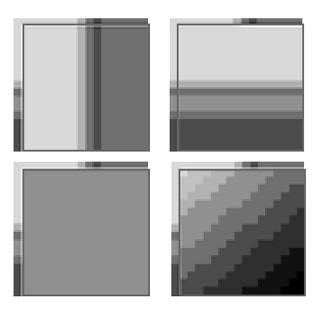

There are four 16x16 luma prediction modes designed in a directional manner. Each 16x16 luma prediction mode generates 256 predicted pixel values using some or all of the upper (H) and left-hand (V) neighboring pixels as shown in Figure 2.5. Vertical, Horizontal and DC modes are similar to 4x4 luma prediction modes. Plane mode is an approximation of bilinear transform with only integer arithmetic. The examples of each 16x16 luma prediction mode for real images are given in Figure 2.6. The prediction equations used in 16x16 luma prediction modes are shown in Figure 2.7 where [y,x] denotes the position of the pixel in a MB (the top left, top right, bottom left, and bottom right positions of a MB are

denoted as [0,0], [0,15], [15,0], and [15,15], respectively), *p* represents the neighboring pixel values and Clip1 is to clip the result into [0-255] range.

DC mode is always used regardless of the availability of the neighboring pixels. However, it is adopted based on which neighboring pixels are available. The other prediction modes can only be used if all of the required neighboring pixels are available [2, 3]. Available 16x16 luma prediction modes for a MB depending on the availability of the neighboring MBs are given in Table 2.2.

Figure 2.5 16x16 Luma Prediction Modes

Figure 2.6 Examples of Real Images for 16x16 Luma Prediction Modes

| Availability of Neighboring<br>16x16 Luma Blocks | Available 16x16 Luma<br>Prediction Modes |

|--------------------------------------------------|------------------------------------------|

| None available                                   | DC                                       |

| Left available, Top not available                | Horizontal, DC                           |

| Top available, Left not available                | Vertical, DC                             |

| Both available                                   | All Modes                                |

Table 2.2 Availability of 16x16 Luma Prediction Modes

| pred[y, 0] = $p[-1, 0]$   | pred[0, x] = p[0, -1]   |

|---------------------------|-------------------------|

| pred[y, 1] = $p[-1, 1]$   | pred[1, x] = p[1, -1]   |

| pred[y, 2] = $p[-1, 2]$   | pred[2, x] = p[2, -1]   |

| pred[y, 3] = $p[-1, 3]$   | pred[3, x] = p[3, -1]   |

| pred[y, 4] = $p[-1, 4]$   | pred[4, x] = p[4, -1]   |

| pred[y, 5] = $p[-1, 5]$   | pred[5, x] = p[5, -1]   |

| pred[y, 6] = $p[-1, 6]$   | pred[6, x] = p[6, -1]   |

| pred[y, 7] = $p[-1, 7]$   | pred[7, x] = p[7, -1]   |

| pred[y, 8] = $p[-1, 8]$   | pred[8, x] = p[8, -1]   |

| pred[y, 9] = $p[-1, 9]$   | pred[9, x] = p[9, -1]   |

| pred[y, 10] = $p[-1, 10]$ | pred[10, x] = p[10, -1] |

| pred[y, 11] = $p[-1, 11]$ | pred[11, x] = p[11, -1] |

| pred[y, 12] = $p[-1, 12]$ | pred[12, x] = p[12, -1] |

| pred[y, 13] = $p[-1, 14]$ | pred[14, x] = p[14, -1] |

| pred[y, 15] = $p[-1, 15]$ | pred[15, x] = p[15, -1] |

| $(0 \le y \le 15)$        | $(0 \le x \le 15)$      |

(a) 16x16 Vertical Mode (b) 16x16 Horizontal Mode

pred[y,x] = p[-1, x'] + p[y', -1] + 16 >> 5(x' = 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15) (y' = 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15)

(If the left and the upper neighboring pixels are available)

$$pred[y,x] = p[y', -1] + 8 >> 4$$

(y' = 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15)

(Else If the left neighboring pixels are available)

pred[y,x] = p[-1, x'] + 8 >> 4

(x' = 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15)

(Else If the top neighboring pixels are available)

pred[y,x] = 128

(Else //If the left and the upper neighboring pixels are not available)

(c) 16x16 DC Mode

pred[y,x] = Clip1 [((a + b \* (x - 3) + c \* (y - 3) + 16) >> 5] a = 16 \* (p[-1,15] + p[15,-1]) b = (5 \* H + 32) >> 6 c = (5 \* V + 32) >> 6  $H = \sum (x'+1)*(p[-1,8 + x'] + p[-1, 6 - x'])$  (x' = 0, 1, 2, 3, 4, 5, 6, 7)  $V = \sum (y'+1)*(p[8 + y',-1] + p[6 - y',-1])$  (y' = 0, 1, 2, 3, 4, 5, 6, 7) (d) 16x16 Plane Mode

Figure 2.7 Prediction Equations for 16x16 Luma Prediction Modes

For the chroma components of a MB, a predicted 8x8 chroma block is formed for each 8x8 chroma component by performing intra prediction for the MB. There are four 8x8 chroma prediction modes which are similar to 16x16 luma prediction modes. A mode decision algorithm is used to compare the 8x8 predictions and select the best chroma prediction mode for each chroma component of the MB. Both chroma components of a MB always use the same prediction mode. The prediction equations used in 8x8 chroma prediction modes are shown in Figure 2.8 where [y,x] denotes the position of the pixel in a MB (the top left, top right, bottom left, and bottom right positions of a MB are denoted as [0,0], [0,7], [7,0], and [7,7], respectively), *p* represents the neighboring pixel values and Clip1 is to clip the result into [0-255] range.

DC mode is always used regardless of the availability of the neighboring pixels. However, it is adopted based on which neighboring pixels are available. The other prediction modes can only be used if all of the required neighboring pixels are available [4, 5]. Available 8x8 chroma prediction modes for a MB depending on the availability of the neighboring MBs are given in Table 2.3.

Availability of Neighboring<br/>8x8 Chroma BlocksAvailable 8x8 Luma<br/>Prediction ModesNone availableDCLeft available, Top not availableHorizontal, DCTop available, Left not availableVertical, DCBoth availableAll Modes

Table 2.3 Availability of 8x8 Chroma Prediction Modes

| pred[y, 0] = $p[-1, 0]$ | pred[0, x] = p[0, -1]   |

|-------------------------|-------------------------|

| pred[y, 1] = $p[-1, 1]$ | pred[1, x] = p[1, -1]   |

| pred[y, 2] = $p[-1, 2]$ | pred[2, x] = p[2, -1]   |

| pred[y, 3] = $p[-1, 3]$ | pred[3, x] = p[3, -1]   |

| pred[y, 4] = $p[-1, 4]$ | pred[4, x] = p[4, -1]   |

| pred[y, 5] = $p[-1, 5]$ | pred[5, x] = p[5, -1]   |

| pred[y, 6] = $p[-1, 6]$ | pred[6, x] = p[6, -1]   |

| pred[y, 5] = $p[-1, 5]$ | pred[5, x] = $p[5, -1]$ |

| pred[y, 6] = $p[-1, 6]$ | pred[6, x] = $p[6, -1]$ |

| pred[y, 7] = $p[-1, 7]$ | pred[7, x] = $p[7, -1]$ |

| $(0 \le y \le 7)$       | $(0 \le x \le 7)$       |

(a) 8x8 Vertical Mode (b) 8x8 Horizontal Mode

pred[y, x] =  $(\sum p[x', -1] + \sum p[-1, y'] + 4) >> 3$ (If p[x', -1] with x' = 0..3, and p[-1, y'] and y' = 0..3 are available)

$pred[y, x] = (\sum p[x', -1] + 2) >> 2$ (Else If p[x', -1] with x' = 0..3 are available and p[-1, y'] and y' = 0..3 are not available)

pred[y, x] =  $(\sum p[-1, y'] + 2) >> 2$ (Else If p[-1, y'] and y' = 0..3 are available and p[x', -1] with x' = 0..3 are not available)

pred[y, x] = 128(Else //If p[x', -1] with x' = 0..3, and p[-1, y'] and y' = 0..3 are not available)  $(0 \le x \le 3)$  $(0 \le y \le 3)$ (c-1) 8x8 DC Mode  $pred[y, x] = (\sum p[x', -1] + 2) >> 2$ (If p[x', -1] with x' = 4..7 are available)  $pred[y, x] = (\sum p[-1, y'] + 2) >> 2$ (Else If p[-1, y'] and y' = 0..3 are available) pred[y, x] = 128(Else)  $(4 \le x \le 7)$  $(0 \le v \le 3)$ (c-2) 8x8 DC Mode pred[y, x] =  $(\sum p[-1, y'] + 2) >> 2$ (If p[-1, y'] and y' = 4..7 are available)  $pred[y, x] = (\sum p[x', -1] + 2) >> 2$ (Else If p[x', -1] with x' = 0..3 are available) pred[y, x] = 128(Else)  $(0 \le x \le 3)$  $(4 \le y \le 7)$ (c-3) 8x8 DC Mode pred[y, x] =  $(\sum p[x', -1] + \sum p[-1, y'] + 4) >> 3$ (If p[x', -1] with x' = 4..7, and p[-1, y'] and y' = 4..7 are available)

$pred[y, x] = (\sum p[x', -1] + 2) >> 2$ (Else If p[x', -1] with x' = 4..7 are available and p[-1, y'] and y' = 4..7 are not available)

pred[y, x] =  $(\sum p[-1, y'] + 2) >> 2$ (Else If p[-1, y'] and y' = 4..7 are available and p[x', -1] with x' = 4..7 are not available) pred[y, x] = 128 (Else //If p[x', -1] with x' = 4..7, and p[-1, y'] and y' = 4..7 are not available)

$$(4 \le x \le 7)$$

$(4 \le y \le 7)$

$$pred[y,x] = Clip1 [((a + b * (x - 3) + c * (y - 3) + 16) >> 5]$$

$$a = 16 *(p[-1,7] + p[7,-1])$$

$$b = (5 * H + 32) >> 6$$

$$c = (5 * V + 32) >> 6$$

$$H = \sum (x'+1)*(p[-1,4 + x'] + p[-1, 2 - x'])$$

$$(x' = 0, 1, 2, 3)$$

$$V = \sum (y'+1)*(p[4 + y', -1] + p[2 - y', -1])$$

$$(y' = 0, 1, 2, 3)$$

(d) 8x8 Plane Mode

Figure 2.8 Prediction Equations for 8x8 Chroma Prediction Modes

### 2.2 Proposed Hardware Architecture

In the previous video coding standards, prediction part and coding part (DCT/Q/IQ/IDCT/VLC) can be clearly separated. After prediction part finishes processing a MB, coding part starts coding this MB and prediction part starts processing the next MB. However, because of the intra prediction algorithm used in H.264 standard, after prediction of a MB, the next MB can not be predicted before corresponding reconstructed pixels at the output of the Transform/Quant/Inverse Quant/Inverse Transform are produced. The situation is even worse for 4x4 luma prediction modes. Prediction and mode decision of a 4x4 block cannot be performed until the previous 4x4 block is reconstructed. Therefore, the

prediction part must wait the coding part which makes the MB pipelining impossible and the design of a real-time intra frame coder hardware very costly.

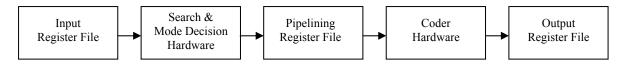

We, however, divided our proposed H.264 intra frame coder hardware into two main parts; the search & mode decision part and coder part. The search & mode decision hardware and the coder hardware work in a pipelined manner. After the first MB of the input frame is loaded to the input register file, search & mode decision hardware starts to work on determining the best mode for coding this MB. After search & mode decision hardware determines the best mode for the first MB, coder hardware starts to code the first MB using the selected best mode and search & mode decision hardware starts to work on the second MB. The entire frame is processed MB by MB in this order.

This is achieved by performing intra prediction in the search & mode decision hardware using the pixels in the current frame rather than the pixels in the reconstructed frame. However, intra prediction in the coder hardware is performed using the pixels in the reconstructed frame in order to be compliant with H.264 standard. Therefore, in this thesis, two different low-cost hardware architectures are designed for H.264 intra prediction algorithm, one for search & mode decision hardware and one for coder hardware. This makes the MB pipelining and therefore the implementation of a low-cost H.264 intra frame coder hardware possible at the expense of a small PSNR loss in the video quality.

## 2.2.1 Intra Prediction Hardware for Search & Mode Decision

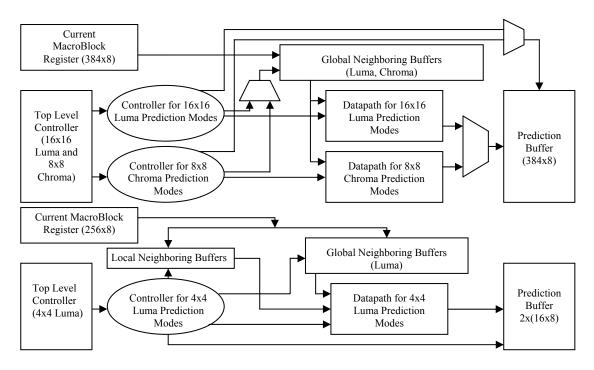

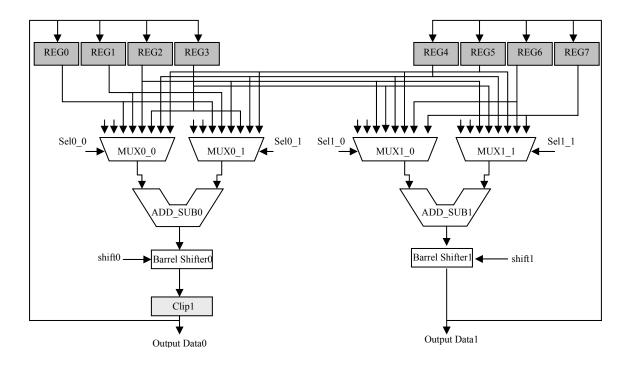

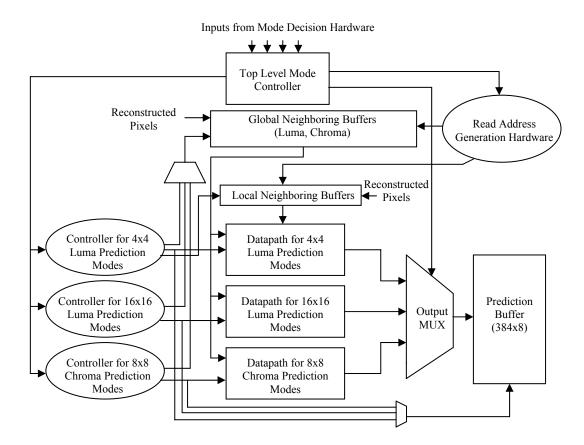

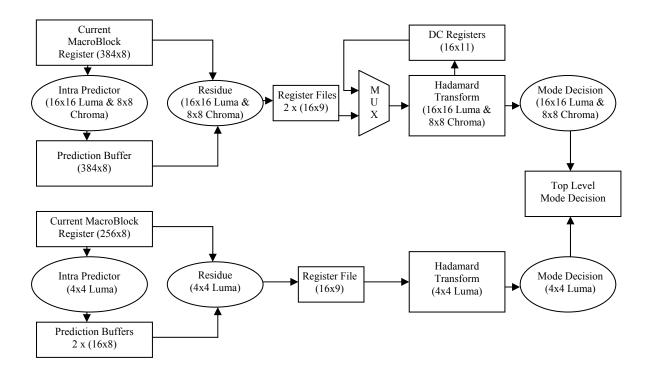

The block diagram of the proposed intra prediction hardware architecture for the search & mode decision part of the H.264 intra frame coder is shown in Figure 2.9. The proposed hardware generates the predicted pixels using available 16x16 and 4x4 luma prediction modes for luma and 8x8 chroma prediction modes for chroma components of a MB with different configurations. In the proposed hardware, there are two parts operating in parallel in order to perform intra prediction faster.

Figure 2.9 Intra Prediction Hardware for Search & Mode Decision

The upper part is used for generating the predicted pixels for the luma component of a MB using available 16x16 luma prediction modes and for generating the predicted pixels for the chroma components of a MB using available 8x8 chroma prediction modes. The size of register files that are used for the current MB and the prediction buffer is 384x8, because they are used for storing both luma and chroma components of the current and predicted MB respectively.

The lower part is used for generating the predicted pixels for each 4x4 block in the luma component of a MB using available 4x4 luma prediction modes. The lower part is more computationally demanding and it is the bottleneck in the intra prediction hardware for search & mode decision. The size of the current MB register file is 256x8, because it is used for storing only luma components of the current MB. The size of the prediction buffer is 16x8 since it is used for storing the predicted pixels for a 4x4 luma block.

Two local neighboring buffers, local vertical register file and local horizontal register file, are used to store the neighboring pixels in the previously coded and reconstructed neighboring 4x4 luma blocks in the current MB. After a 4x4 luma block in the current MB is coded and reconstructed, the neighboring pixels in this block are stored in the corresponding local register files.

Local vertical register file is used to store the neighboring pixels d, h, l, and p in the left-hand previously coded and reconstructed neighboring 4x4 luma blocks in the current MB. Local horizontal register file is used to store the neighboring pixels m, n, o, and p in the upper previously coded and reconstructed 4x4 luma blocks in the current MB. The proposed hardware uses this data to determine the neighboring pixels in the left-hand and upper previously coded neighboring 4x4 luma blocks in the current MB.

Six global neighboring buffers, three global vertical neighboring buffers and three global horizontal neighboring buffers, are used to store the neighboring pixels in the previously coded and reconstructed neighboring MBs of the current MB.

Global luma vertical register file is used to store the neighboring pixels d, h, l, and p in the 4x4 luma blocks 5, 7, 13 and 15 of the previously coded MB. The proposed hardware uses this data to determine the neighboring pixels in the left-hand previously coded neighboring MB of the 4x4 luma blocks 0, 2, 8, and 10 in the current MB. Global Cb vertical register file and global Cr vertical register file are used for the chroma Cb and chroma Cr components of the MBs.

Global luma horizontal register file is used to store the neighboring pixels m, n, o, and p in the luma blocks 10, 11, 14, and 15 of the previously coded MBs in the previously coded MB row of the frame. The proposed hardware uses this data to determine the neighboring pixels in the upper previously coded neighboring MB of the 4x4 luma blocks 0, 1, 4, and 5 in the current MB. Global Cb horizontal register file and global Cr horizontal register file are used for the chroma Cb and chroma Cr components of the MBs.

Instead of using one large external SRAM, we have used 8 internal register files to store the neighboring reconstructed pixels in order to reduce power consumption. The power consumption is reduced by accessing a small register file for storing and reading a reconstructed pixel instead of accessing a large external SRAM. In addition, we have disabled the register files when they are not accessed in order to reduce power consumption.

## 2.2.1.1 Proposed Hardware for 4x4 Luma Prediction Modes

After a careful analysis of the equations used in 4x4 luma prediction modes, it is observed that there are common parts in the equations and some of the equations are identical. The intra prediction equations are organized for exploiting these observations to reduce both the number of memory accesses and computation time required for generating the predicted pixels. The organized prediction equations for 4x4 luma prediction modes are shown in Figure 2.10. As it can be seen from the figure, (A + B), (B + C), (C + D), (D + E), (E + F), (F + G), (G + H), (J + K), (I + J), (M + I) and (M + A) are common in two or more equations, and some of the prediction equations (e.g. [(A + B) + (B + C) + 2] >> 2) are identical.

$$Pred[0, 0] = Pred[1, 0] = Pred[2, 0] = Pred[3, 0] = A$$

$$Pred[0, 1] = Pred[1, 1] = Pred[2, 1] = Pred[3, 1] = B$$

$$Pred[0, 2] = Pred[1, 2] = Pred[2, 2] = Pred[3, 2] = C$$

$$Pred[0, 3] = Pred[1, 3] = Pred[2, 3] = Pred[3, 3] = D$$

(a) 4x4 Vertical Prediction Mode

Pred[0, 0] = Pred[0, 1] = Pred[0, 2] = Pred[0, 3] = I Pred[1, 0] = Pred[1, 1] = Pred[1, 2] = Pred[1, 3] = J Pred[2, 0] = Pred[2, 1] = Pred[2, 2] = Pred[2, 3] = K Pred[3, 0] = Pred[3, 1] = Pred[3, 2] = Pred[3, 3] = L(b) 4x4 Horizontal Prediction Mode

pred[y,x] = [(A + B) + (C + D) + (I + J) + (K + L) + 4] >> 3(If the left and the top neighboring pixels are available)

Pred[y, x] = [(I + J) + (K + L) + 2] >> 2(Else If only the left neighboring pixels are available)

pred[y, x] = [(A + B) + (C + D) + 2] >> 2(Else If only the top neighboring pixels are available)

pred[y,x] = 128(Else //If the left and the top neighboring pixels are not available)

(c) 4x4 DC Prediction Mode

| Pred[0, 0]                           | = [(A + B) + (B + C) + 2] >> 2 |

|--------------------------------------|--------------------------------|

| Pred[0, 1] = Pred[1, 0]              | = [(C + D) + (B + C) + 2] >> 2 |

| Pred[0, 2] = Pred[1, 1] = Pred[2, 0] | = [(C + D) + (D + E) + 2] >> 2 |

| Pred[0, 3] = Pred[1, 2] = Pred[2, 1] | = [(E + F) + (D + E) + 2] >> 2 |

| Pred[3, 0]                           | = [(E + F) + (D + E) + 2] >> 2 |

| Pred[1, 3] = Pred[2, 2] = Pred[3, 1] | = [(E + F) + (F + G) + 2] >> 2 |

| Pred[2, 3] = Pred[3, 2]              | = [(G + H) + (F + G) + 2] >> 2 |

| Pred[3, 3]                           | = [(G + H) + (H + H) + 2] >> 2 |

(d) 4x4 Diagonal Down-Left Mode

| Pred[0, 2] = Pred[1, 3]              | = [(A + B) + (B + C) + 2] >> 2 |

|--------------------------------------|--------------------------------|

| Pred[0, 3]                           | = [(C + D) + (B + C) + 2] >> 2 |

| Pred[3, 0]                           | = [(J + K) + (K + L) + 2] >> 2 |

| Pred[2, 0] = Pred[3, 1]              | = [(J + K) + (I + J) + 2] >> 2 |

| Pred[1, 0] = Pred[2, 1] = Pred[3, 2] | = [(M + I) + (I + J) + 2] >> 2 |

| Pred[0, 0] = Pred[1, 1] = Pred[2, 2] |                                |

| = Pred[3, 3]                         | = [(M + I) + (M + A) + 2] >> 2 |

| Pred[0, 1] = Pred[1, 2] = Pred[2, 3] | = [(A + B) + (M + A) + 2] >> 2 |

(e) 4x4 Diagonal Down-Right Mode

| Pred[3, 0]              | = [(I + J) + (J + K) + 2] >> 2 |

|-------------------------|--------------------------------|

| Pred[2, 0]              | = [(I + J) + (M + I) + 2] >> 2 |

| Pred[1, 0] = Pred[3, 1] | = [(M + A) + (M + I) + 2] >> 2 |

| Pred[1, 1] = Pred[3, 2] | = [(M + A) + (A + B) + 2] >> 2 |

| Pred[1, 2] = Pred[3, 3] | = [(B + C) + (A + B) + 2] >> 2 |

| Pred[1, 3]              | = [(B + C) + (C + D) + 2] >> 2 |

| Pred[0, 1] = Pred[2, 1] | = [(A + B) + 1] >> 1           |

| Pred[0, 3]              | = [(C + D) + 1] >> 1           |

| Pred[0, 0] = Pred[2, 1] | = [(M + A) + 1] >> 1           |

| Pred[0, 2] = Pred[2, 3] | = [(B + C) + 1] >> 1           |

(f) 4x4 Vertical Right Mode

| Pred[3, 1]              | = [(K + L) + (J + K) + 2)] >> 2 |

|-------------------------|---------------------------------|

| Pred[2, 1] = Pred[3, 3] | = [(I + J) + (J + K) + 2] >> 2  |

| Pred[1, 1] = Pred[2, 3] | = [(I + J) + (M + I) + 2] >> 2  |

| Pred[0, 1] = Pred[1, 3] | = [(M + A) + (M + I) + 2] >> 2  |

| Pred[0, 2]              | = [(M + A) + (A + B) + 2] >> 2  |

| Pred[0, 3]              | = [(B + C) + (A + B) + 2] >> 2  |

| Pred[0, 0] = Pred[1, 2] | = [(M + I) + 1] >> 1            |

| Pred[1, 0] = Pred[2, 2] | = [(I + J) + 1] >> 1            |

| Pred[2, 0] = Pred[3, 2] | = [(J + K) + 1] >> 1            |

| Pred[3, 0]              | = [(K + L) + 1] >> 1            |

(g) 4x4 Horizontal Down Mode

| Pred[1, 0]              | = [(A + B) + (B + C) + 2] >> 2 |

|-------------------------|--------------------------------|

| Pred[1, 1] = Pred[3, 0] | = [(C + D) + (B + C) + 2] >> 2 |

| Pred[1, 2] = Pred[3, 1] | = [(C + D) + (D + E) + 2] >> 2 |

| Pred[1, 3] = Pred[3, 2] | = [(E + F) + (D + E) + 2] >> 2 |

| Pred[3, 3]              | = [(E + F) + (F + G) + 2] >> 2 |

| Pred[0, 0]              | = [(A + B) + 1] >> 1           |

| Pred[0, 1] = Pred[2, 0] | = [(B + C) + 1] >> 1           |

| Pred[0, 2] = Pred[2, 1] | = [(C + D) + 1] >> 1           |

| Pred[0, 3] = Pred[2, 2] | = [(D + E) + 1] >> 1           |

| Pred[2, 3]              | = [(E + F) + 1] >> 1           |

(h) 4x4 Vertical Left Mode

$$\begin{array}{ll} Pred[0, 1] &= [(I + J) + (J + K) + 2] >> 2\\ Pred[0, 3] = Pred[1, 1] = [(J + K) + (K + L) + 2)] >> 2\\ Pred[1, 3] = Pred[2, 1] = [(L + L) + (K + L) + 2)] >> 2\\ Pred[1, 2] = Pred[2, 0] = [(K + L) + 1] >> 1\\ Pred[0, 0] &= [(I + J) + 1] >> 1\\ Pred[0, 2] = Pred[1, 0] = [(J + K) + 1] >> 1\\ Pred[2, 2] = Pred[2, 3] = Pred[3, 0] = Pred[3, 1]\\ &= Pred[3, 2] = Pred[3, 3] = L \end{array}$$

(i) 4x4 Horizontal Up Mode

Figure 2.10 Organized Prediction Equations for 4x4 Luma Prediction Modes

The proposed hardware first calculates the results of the common parts in all the 4x4 luma prediction modes and stores them in temporary registers. It, then, calculates the results of the prediction equations using the values stored in these temporary registers. If both the left and top neighboring blocks of a 4x4 luma block are available, 12 common parts are calculated in the preprocessing step and this takes 8 clock cycles. The neighboring buffers are only accessed during this preprocessing. Therefore, they are disabled after the preprocessing for reducing power consumption.

The proposed hardware calculates the results of the identical prediction equations only once and stores them in temporary registers. It, then, determines the results of identical prediction equations by reading the values stored in these temporary registers, instead of calculating the same equations again.

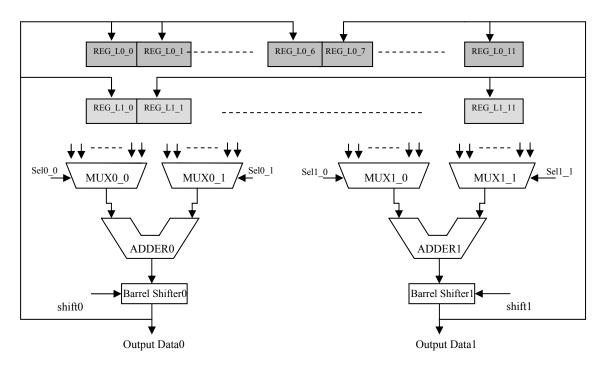

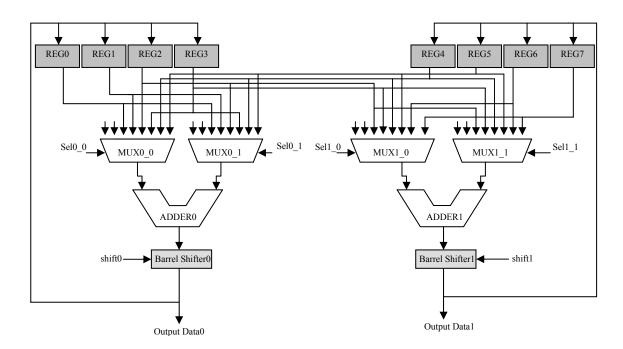

The proposed datapath for generating predicted pixels for a 4x4 luma block using all 4x4 luma prediction modes is shown in Figure 2.11. Level0 (L0) registers are used to store the results of the common parts in the equations of all the 4x4 luma prediction modes. Level1 (L1) registers are used to store the results of the identical prediction equations used in all the 4x4 luma prediction modes. If both the left and top neighboring blocks of a 4x4 luma block are available, it takes 165 clock cycles to generate the predicted pixels for that 4x4 block using available 4x4 luma prediction modes. Clock cycles required for preprocessing and performing available 4x4 luma predictions based on the availability of neighboring 4x4 luma blocks for a 4x4 luma block are given in Table 2.4.

Figure 2.11 Datapath for 4x4 Luma Prediction Modes

| Preprocessing & Available Modes | Clock Cycles /<br>4x4 Luma Block |

|---------------------------------|----------------------------------|

| Preprocessing                   | 8                                |

| Vertical                        | 17                               |

| Horizontal                      | 17                               |

| DC                              | 19                               |

| Diagonal Down-Left Mode         | 18                               |

| Diagonal Down-Right Mode        | 18                               |

| Vertical Right                  | 17                               |

| Horizontal Down                 | 17                               |

| Vertical Left                   | 17                               |

| Horizontal Up                   | 17                               |

Table 2.4 Clock Cycles Required for Performing Available 4x4 Luma Prediction Modes

(a) Top and Left Neighboring 4x4 Luma Blocks are available

| Preprocessing & Available Modes | Clock Cycles /<br>4x4 Luma Block |

|---------------------------------|----------------------------------|

| Preprocessing                   | 8                                |

| Vertical                        | 17                               |

| DC                              | 18                               |

| Diagonal Down-Left Mode         | 18                               |

| Vertical Left                   | 17                               |

(b)Top Neighboring 4x4 Luma Block is available

| Preprocessing & Available Modes | Clock Cycles/4x4<br>Luma Block |

|---------------------------------|--------------------------------|

| Preprocessing                   | 5                              |

| Horizontal                      | 17                             |

| DC                              | 18                             |

| Horizontal Up                   | 18                             |

(c) Left Neigboring 4x4 Luma Block is available

| Preprocessing & Available Modes | Clock Cycles/4x4<br>Luma Block |

|---------------------------------|--------------------------------|

| Preprocessing                   | -                              |

| DC                              | 17                             |

(d) Top and Left Neighboring 4x4 Luma Blocks are not available

Since the order of the equations used in a 4x4 luma prediction mode is not important for functional correctness, the equations are ordered to keep the inputs of the adders the same for as many consecutive clock cycles as possible. This avoids unnecessary switching activity and reduces the power consumption.

#### 2.2.1.2 Proposed Hardware for 16x16 Luma Prediction Modes

After a careful analysis of the equations used in 16x16 luma prediction modes, it is observed that Vertical, Horizontal and DC mode equations can directly be implemented using adders and shifters, however the equations used in Plane mode can be organized to avoid using a multiplier and to reduce computation time required for generating the predicted pixels. The organized prediction equations for Plane mode are shown in Figure 2.12. A similar organization for the Plane mode prediction equations is given in [7, 8]. However, our hardware design is different than their design and it is a more cost-effective solution for portable applications.

a = (p[-1,15] + p[15,-1]) << 4, b = [(H << 2) + (H + 32)] >> 6c = [(V << 2) + (V + 32)] >> 6C0 = [a - (7 \* b) - (7 \* c) + 16]

pred[0, 0] = Clip1 [(C0) >> 5] pred[0, 1] = Clip1 [(C0 + b) >> 5] pred[0, 2] = Clip1 [(C0 + 2b) >> 5] pred[0, 3] = Clip1 [(C0 + 3b) >> 5]pred[1, 0] = Clip1 [(C0 + c) >> 5]

pred[1, 1] = Clip1 [((C0 + c) + b) >> 5] pred[1, 2] = Clip1 [((C0 + c) + 2b) >> 5]pred[1, 3] = Clip1 [((C0 + c) + 3b) >> 5]

pred[2, 0] = Clip1 [(C0 + 2c) >> 5] pred[2, 1] = Clip1 [((C0 + 2c) + b) >> 5] pred[2, 2] = Clip1 [((C0 + 2c) + 2b) >> 5]pred[2, 3] = Clip1 [((C0 + 2c) + 3b) >> 5]

pred[3, 0] = Clip1 [(C0 + 3c) >> 5] pred[3, 1] = Clip1 [((C0 + 3c) + b) >> 5] pred[3, 2] = Clip1 [((C0 + 3c) + 2b) >> 5]pred[3, 3] = Clip1 [((C0 + 3c) + 3b) >> 5]

## C1 = [a - (3 \* b) - (7 \* c) + 16] = C0 + 4b

| pred[0, 4] = Clip1 [(C1) >> 5]<br>pred[0, 5] = Clip1 [(C1 + b) >> 5]<br>pred[0, 6] = Clip1 [(C1 + 2b) >> 5]<br>pred[0, 7] = Clip1 [(C1 + 3b) >> 5]                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pred[1, 4] = Clip1 [(C1 + c) >> 5]<br>pred[1, 5] = Clip1 [((C1 + c) + b) >> 5]<br>pred[1, 6] = Clip1 [((C1 + c) + 2b) >> 5]<br>pred[1, 7] = Clip1 [((C1 + c) + 3b) >> 5]     |

| pred[2, 4] = Clip1 [(C1 + 2c) >> 5]<br>pred[2, 5] = Clip1 [((C1 + 2c) + b) >> 5]<br>pred[2, 6] = Clip1 [((C1 + 2c) + 2b) >> 5]<br>pred[2, 7] = Clip1 [((C1 + 2c) + 3b) >> 5] |

| pred[3, 4] = Clip1 [(C1 + 3c) >> 5]<br>pred[3, 5] = Clip1 [((C1 + 3c) + b) >> 5]                                                                                             |

| pred[3, 5] = Clip1[((C1 + 3c) + b) >> 5]   |

|--------------------------------------------|

| pred[3, 6] = Clip1 [((C1 + 3c) + 2b) >> 5] |

| pred[3, 7] = Clip1 [((C1 + 3c) + 3b) >> 5] |

# C2 = [a - (7 \* b) - (3 \* c) + 16] = C0 + 4c

| pred[4, 0] = Clip1 [(C2) >> 5]      |

|-------------------------------------|

| pred[4, 1] = Clip1 [(C2 + b) >> 5]  |

| pred[4, 2] = Clip1 [(C2 + 2b) >> 5] |

| pred[4, 3] = Clip1 [(C2 + 3b) >> 5] |

|                                     |

pred[5, 0] = Clip1 [(C2 + c) >> 5] pred[5, 1] = Clip1 [((C2 + c) + b) >> 5] pred[5, 2] = Clip1 [((C2 + c) + 2b) >> 5]pred[5, 3] = Clip1 [((C2 + c) + 3b) >> 5]

pred[6, 0] = Clip1 [(C2 + 2c) >> 5] pred[6, 1] = Clip1 [((C2 + 2c) + b) >> 5] pred[6, 2] = Clip1 [((C2 + 2c) + 2b) >> 5]pred[6, 3] = Clip1 [((C2 + 2c) + 3b) >> 5]

pred[7, 0] = Clip1 [(C2 + 3c) >> 5] pred[7, 1] = Clip1 [((C2 + 3c) + b) >> 5] pred[7, 2] = Clip1 [((C2 + 3c) + 2b) >> 5]pred[7, 3] = Clip1 [((C2 + 3c) + 3b) >> 5]

# C3 = [a - (3 \* b) - (3 \* c) + 16] = C0 + 4c + 4b

| pred[4, 4] = Clip1 [(C3) >> 5]<br>pred[4, 5] = Clip1 [(C3 + b) >> 5]<br>pred[4, 6] = Clip1 [(C3 + 2b) >> 5]<br>pred[4, 7] = Clip1 [(C3 + 3b) >> 5]                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pred[5, 4] = Clip1 [(C3 + c) >> 5]<br>pred[5, 5] = Clip1 [((C3 + c) + b) >> 5]<br>pred[5, 6] = Clip1 [((C3 + c) + 2b) >> 5]<br>pred[5, 7] = Clip1 [((C3 + c) + 3b) >> 5]     |

| pred[6, 4] = Clip1 [(C3 + 2c) >> 5]<br>pred[6, 5] = Clip1 [((C3 + 2c) + b) >> 5]<br>pred[6, 6] = Clip1 [((C3 + 2c) + 2b) >> 5]<br>pred[6, 7] = Clip1 [((C3 + 2c) + 3b) >> 5] |

| pred[7, 4] = Clip1 [(C3 + 3c) >> 5]<br>pred[7, 5] = Clip1 [((C3 + 3c) + b) >> 5]<br>pred[7, 6] = Clip1 [((C3 + 3c) + 2b) >> 5]                                               |

| pred[7, 4] = Clip1[(C3 + 3c) >> 5]         |

|--------------------------------------------|

| pred[7, 5] = Clip1 [((C3 + 3c) + b) >> 5]  |

| pred[7, 6] = Clip1 [((C3 + 3c) + 2b) >> 5] |

| pred[7, 7] = Clip1 [((C3 + 3c) + 3b) >> 5] |

# C4 = [a + (1 \* b) - (7 \* c) + 16] = C0 + 8b

| pred[0, 8] = Clip1 [(C4) >> 5]       |

|--------------------------------------|

| pred[0, 9] = Clip1 [(C4 + b) >> 5]   |

| pred[0, 10] = Clip1 [(C4 + 2b) >> 5] |

| pred[0, 11] = Clip1 [(C4 + 3b) >> 5] |

|                                      |

pred[1, 8] = Clip1[(C4 + c) >> 5]pred[1, 9] = Clip1[((C4 + c) + b) >> 5]pred[1, 10] = Clip1[((C4 + c) + 2b) >> 5]pred[1, 11] = Clip1 [((C4 + c) + 3b) >> 5]

pred[2, 8] = Clip1 [(C4 + 2c) >> 5]pred[2, 9] = Clip1 [((C4 + 2c) + b) >> 5]pred[2, 10] = Clip1 [((C4 + 2c) + 2b) >> 5]pred[2, 11] = Clip1[((C4 + 2c) + 3b) >> 5]

| pred[3, 8] = Clip1 [(C4 + 3c) >> 5]         |

|---------------------------------------------|

| pred[3, 9] = Clip1 [((C4 + 3c) + b) >> 5]   |

| pred[3, 10] = Clip1 [((C4 + 3c) + 2b) >> 5] |

| pred[3, 11] = Clip1 [((C4 + 3c) + 3b) >> 5] |

# C5 = [a + (5 \* b) - (7 \* c) + 16] = C0 + 12b

| pred[0, 12] = Clip1 [(C5) >> 5]<br>pred[0, 13] = Clip1 [(C5 + b) >> 5]<br>pred[0, 14] = Clip1 [(C5 + 2b) >> 5]<br>pred[0, 15] = Clip1 [(C5 + 3b) >> 5]                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pred[1, 12] = Clip1 [(C5 + c) >> 5]<br>pred[1, 13] = Clip1 [((C5 + c) + b) >> 5]<br>pred[1, 10] = Clip1 [((C5 + c) + 2b) >> 5]<br>pred[1, 11] = Clip1 [((C5 + c) + 3b) >> 5]     |

| pred[2, 12] = Clip1 [(C5 + 2c) >> 5]<br>pred[2, 13] = Clip1 [((C5 + 2c) + b) >> 5]<br>pred[2, 14] = Clip1 [((C5 + 2c) + 2b) >> 5]<br>pred[2, 15] = Clip1 [((C5 + 2c) + 3b) >> 5] |

| pred[3, 12] = Clip1 [(C5 + 3c)>> 5]<br>pred[3, 13] = Clip1 [((C5 + 3c) + b) >> 5]<br>pred[3, 14] = Clip1 [((C5 + 3c) + 2b) >> 5]<br>pred[3, 15] = Clip1 [((C5 + 3c) + 3b) >> 5]  |

C6 = [a + (1 \* b) - (3 \* c) + 16] = C0 + 8b + 4c

pred[4, 8] = Clip1 [(C6)>> 5] pred[4, 9] = Clip1 [(C6 + b) >> 5]pred[4, 10] = Clip1 [(C6 + 2b) >> 5]pred[4, 11] = Clip1 [(C6 + 3b) >> 5]pred[5, 8] = Clip1 [(C6 + c) >> 5]pred[5, 9] = Clip1 [((C6 + c) + b) >> 5]pred[5, 10] = Clip1 [((C6 + c) + 2b) >> 5]pred[5, 11] = Clip1 [((C6 + c) + 3b) >> 5]pred[6, 8] = Clip1 [(C6 + 2c) >> 5]pred[6, 9] = Clip1 [((C6 + 2c) + b) >> 5]pred[6, 10] = Clip1[((C6 + 2c) + 2b) >> 5]pred[6, 11] = Clip1[((C6 + 2c) + 3b) >> 5]pred[7, 8] = Clip1 [(C6 + 3c) >> 5]pred[7, 9] = Clip1 [((C6 + 3c) + b) >> 5]pred[7, 10] = Clip1[((C6 + 3c) + 2b) >> 5]pred[7, 11] = Clip1 [((C6 + 3c) + 3b) >> 5]

# C7 = [a + (5 \* b) - (3 \* c) + 16] = C0 + 12b + 4c

| pred[4, 12] = Clip1 [(C7) >> 5]<br>pred[4, 13] = Clip1 [(C7 + b) >> 5]<br>pred[4, 14] = Clip1 [(C7 + 2b) >> 5]<br>pred[4, 15] = Clip1 [(C7 + 3b) >> 5]                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pred[5, 12] = Clip1 [(C7 + c) >> 5]<br>pred[5, 13] = Clip1 [((C7 + c) + b) >> 5]<br>pred[5, 10] = Clip1 [((C7 + c) + 2b) >> 5]<br>pred[5, 11] = Clip1 [((C7 + c) + 3b) >> 5]     |

| pred[6, 12] = Clip1 [(C7 + 2c) >> 5]<br>pred[6, 13] = Clip1 [((C7 + 2c) + b) >> 5]<br>pred[6, 14] = Clip1 [((C7 + 2c) + 2b) >> 5]<br>pred[6, 15] = Clip1 [((C7 + 2c) + 3b) >> 5] |

| pred[7, 12] = Clip1 [(C7 + 3c) >> 5]        |

|---------------------------------------------|

| pred[7, 13] = Clip1[((C7 + 3c) + b) >> 5]   |

| pred[7, 14] = Clip1 [((C7 + 3c) + 2b) >> 5] |

| pred[7, 15] = Clip1 [((C7 + 3c) + 3b) >> 5] |

C8 = [a - (7 \* b) + (1 \* c) + 16] = C0 + 8c

| pred[8, 0] = Clip1 [(C8) >> 5]<br>pred[8, 1] = Clip1 [(C8 + b) >> 5]<br>pred[8, 2] = Clip1 [(C8 + 2b) >> 5]<br>pred[8, 3] = Clip1 [(C8 + 3b) >> 5]                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|