# Dependability Assessment of NAND Flash-memory for Mission-critical Applications

Michele Fabiano

Michele.Fabiano@polito.it Michele.Fabiano@gmail.com

Submitted in total fulfillment of the requirements of the degree of Doctor of Philosophy

February 2013

Faculty of Computer Engineering Department of Control and Computer Engineering Politecnico di Torino

Herewith declare that I have produced this paper without the prohibited assistance of third parties and without making use of aids other than those specified; notions taken over directly or indirectly from other sources have been identified as such. This thesis has not previously been presented in identical or similar form to any other Italian or foreign examination board. The thesis work was conducted from 01/2009 to 01/2013 under the supervision of Prof. Paolo Prinetto at Politecnico di Torino.

## **About the author**

Michele Fabiano received the Bachelor Science (BS) and Master Science (MS) degree in computer science and information engineering from the Universita' degli Studi di Napoli "Federico II", Napoli (Italy), in 2008.

During this PhD activity, he was Visiting Scientist at the European Space Research and Technology Centre (ES-TEC), Nordwijk (Netherlands), where he worked on the faulttolerant oriented design of high performance NAND flashbased architectures in the On Board Computers and Data Handling Section.

He is currently working as Embedded HW/SW Engineer at ASML, Veldhoven (Netherlands).

His major research interests are the development of real-time embedded systems, implementation of VLSI for digital signal processing, and development of parallel processing software for automated code generation.

## LIST OF PUBLICATIONS

### ISI journals (accepted for publication)

**Fabiano M.**, Furano G., *NAND Flash Storage Technology for Missioncritical Space Applications*, accepted for publication on IEEE Aerospace and Electronic Systems Magazine (AESS).

### ISI journals (revisions being processed)

Di Carlo S., **Fabiano M.**, Indaco M., Prinetto P., *Design and Optimization of Adaptable BCH Codecs for NAND Flash Memory*, revisions being processed on Elsevier Microprocessors and Microsystems (MICPRO).

## **Chapters in edited books**

Caramia M., Di Carlo S., **Fabiano M.**, Prinetto P., *Design Issues and Challenges of File Systems for Flash Memories*, Flash Memory, Edited by Igor Stievano, Published by InTech, pp. 28 (pp. 3 – 30) ISBN 978-9-5330-7272-2.

### **IEEE Conference papers**

Zambelli C., Indaco M., Fabiano M., Di Carlo S., Prinetto P., Olivo P., and Bertozzi D., *A Cross-Layer Approach to the Reliability-Performance Trade-Off in MLC NAND Flash Memories*, on Proceedings of Design, Automation and Test in Europe (DATE) 2012, pages 881–886, 12<sup>th</sup> – 16<sup>th</sup> March 2012, Dresden (Germany).

#### **IEEE Conference papers (continued)**

Di Carlo S., **Fabiano M.**, Piazza R., Prinetto P., *Exploring Modeling and Testing of NAND Flash memories*, Proceedings of 8th IEEE East-West Design & Test Symposium (EWDTS) 2010, 17<sup>th</sup> – 20<sup>th</sup> September 2010, St. Petersburg (Russia).

Di Carlo S., **Fabiano M.**, Piazza R., Prinetto P., *EDACs and Test Integration Strategies for NAND Flash memories*, Proceedings of 8th IEEE East-West Design & Test Symposium (EWDTS) 2010, 17<sup>th</sup> – 20<sup>th</sup> September 2010, St. Petersburg (Russia).

Caramia M., **Fabiano M.**, Miele A., Piazza R., Prinetto P., *Automated synthesis of EDACs for FLASH Memories with User-Selectable Correction Capability*, Proceedings of IEEE High-Level Design Validation and Test (HLDVT) 2010, 11<sup>th</sup> – 12<sup>th</sup> June 2010, Anaheim, California (USA) ISSN: 1552-6674, Print ISBN: 978-1-4244-7805-7.

Caramia M., Di Carlo S., **Fabiano M.**, Prinetto P., *FLARE: a Design Environment for Space Applications*, Proceedings of IEEE High-Level Design Validation and Test (HLDVT) 2009, 4<sup>th</sup> – 6<sup>th</sup> November 2009, San Francisco (USA) ISSN: 1552-6674, Print ISBN: 978-1-4244-4823-4.

Caramia M., Di Carlo S., **Fabiano M.**, Prinetto P, *Exploring Design Dimensions in Flashbased Mass-memory Devices*, Proceedings of 4<sup>th</sup> International Workshop on Software Support for Portable Storage (IWSSPS) 2009, 15<sup>th</sup> October 2009, Grenoble (France), pp. 43 – 48.

Caramia M., Di Carlo S., **Fabiano M.**, Prinetto P., *Flash-memories in Space Applications: Trends and Challenges*, Proceedings of 7<sup>th</sup> IEEE East-West Design & Test Symposium (EWDTS) 2009, 18<sup>th</sup> – 21<sup>st</sup> September 2009, Moscow (Russia), pp. 429 – 432.

#### **IEEE Conferences Posters**

Di Carlo S., **Fabiano M.**, Indaco M., and Prinetto P., *ADAGE: An Automated Synthesis tool for Adaptive BCH-based ECC IP-Cores*, IEEE International Test Conference (ITC) 2012, Anaheim CA, November 4-9, 2012, pp. 15

#### **Conferences without Proceedings**

**Fabiano M.**, Furano G. and Magistrati G., *NAND Flash Storage Technology for Mission-critical Space Applications*, in Single Event Effects (SEE) Symposium, April 3-5, 2012, NASA, San Diego

## **CONTENTS**

| List of | ligures                                      | ix  |

|---------|----------------------------------------------|-----|

| List of | Tables                                       | xii |

| 1 Int   | oduction                                     | 1   |

| 1.1     | Mission-critical applications                | 3   |

|         | 1.1.1 An example: the space environment      | 3   |

| 1.2     | Thesis organization                          |     |

| 2 De    | endability of NAND Flash Memory: An Overview | 9   |

| 2.1     | Flash memory issues and challenges           | 10  |

|         | 2.1.1 Technology                             | 10  |

|         | 2.1.2 Architecture                           | 12  |

|         | 2.1.2.1 Examples of NAND Flash Architecture  | 13  |

|         | 2.1.3 Address translation and boot time      | 16  |

|         | 2.1.4 Garbage collection                     | 17  |

|         | 2.1.5 Memory wearing                         | 17  |

|         | 2.1.6 Bad block management                   | 18  |

|         | 2.1.7 Error correcting codes                 | 18  |

|         | 2.1.8 Testing                                | 19  |

| 2.2     | Using flash-memory as Hard Disk (HD)         | 19  |

| 2.3     | Flash-memory Reliability Screening           | 21  |

|         | 2.3.1 Data Retention ( <i>detrapping</i> )   | 21  |

|         | 2.3.2 Endurance ( <i>trapping</i> )          | 22  |

| 3 Ma    | leling and Testing NAND Flash memory         | 25  |

| 3.1     | NAND Flash Disturbances                      | 26  |

|         | 3.1.1 Program Disturbances                   | 27  |

|         | 3.1.2 Read Disturbances                      | 30  |

|         | 3.1.3 Over-Erase Disturbance (OED)           | 32  |

|         | 3.1.4 Over-Program Disturbance (OPD)         | 32  |

| 3.2     | NAND Flash Circuit Level Modeling            | 32  |

|         | 3.2.1 Intra-cell Faults                      | 33  |

|   |      | 3.2.2    | Inter-cells Faults                                                          | 33 |

|---|------|----------|-----------------------------------------------------------------------------|----|

|   | 3.3  | A Com    | prehensive Fault Model for NAND flash                                       | 34 |

|   |      | 3.3.1    | The BF&D Extended Test Algorithm                                            | 36 |

|   |      | 3.3.2    | Algorithm Complexity                                                        | 37 |

|   | 3.4  | To test  | or not to test: an important remark                                         | 37 |

| 4 | Adaj | ptable E | Error Correcting Codes Design for NAND Flash memory                         | 39 |

|   | 4.1  | Backgi   | round and related works                                                     | 41 |

|   | 4.2  | Optim    | ized Architectures of Programmable Parallel LFSRs                           | 45 |

|   | 4.3  | BCH C    | Code Design Optimization                                                    | 48 |

|   |      | 4.3.1    | The choice of the set of polynomials                                        | 48 |

|   |      | 4.3.2    | Shared Optimized Programmable Parallel LFSRs                                | 52 |

|   | 4.4  | Adapta   | able BCH Encoder                                                            | 54 |

|   | 4.5  | Adapta   | able BCH Decoder                                                            | 55 |

|   |      | 4.5.1    | Adaptable Syndrome Machine                                                  | 56 |

|   |      | 4.5.2    | Adaptable Berlekamp Massey Machine                                          | 59 |

|   |      | 4.5.3    | Adaptable Chien Machine                                                     | 60 |

|   | 4.6  | Experi   | mental Results                                                              | 62 |

|   |      | 4.6.1    | Automatic generation framework                                              | 62 |

|   |      | 4.6.2    | Experimental setup                                                          | 64 |

|   |      | 4.6.3    | Performance evaluations                                                     | 66 |

|   |      | 4.6.4    | Synthesis Results                                                           | 68 |

|   | 4.7  | A Cros   | ss-Layer Approach for New Reliability-Performance Trade-Offs in Multi Level |    |

|   |      |          | ILC) NAND Flash Memories                                                    |    |

|   | 4.8  | Conclu   | lsions                                                                      | 71 |

| 5 | Soft | ware Ma  | anagement of NAND Flash memory: Issues and Challenges                       | 75 |

|   | 5.1  | File sy  | stems for flash memories                                                    | 76 |

|   |      | 5.1.1    | Flash file systems in the technical and scientific literature               | 78 |

|   |      |          | 5.1.1.1 eNVy                                                                | 78 |

|   |      |          | 5.1.1.2 Core flash file system (CFFS)                                       |    |

|   |      |          | 5.1.1.3 FlexFS                                                              | 84 |

|   |      | 5.1.2    | Open source flash file systems                                              | 89 |

|   |      |          | 5.1.2.1 Yet Another Flash File System (YAFFS)                               | 89 |

|   |      | 5.1.3    | Proprietary FFS                                                             | 96 |

|   |      |          | 5.1.3.1 exFAT (Microsoft)                                                   | 96 |

|   |      |          | 5.1.3.2 XCFiles (Datalight)                                                 | 96 |

|   |      |          | 5.1.3.3 TrueFFS (M-Systems)                                                 | 96 |

|   |      |          |                                                                             |    |

|   |      |         | 5.1.3.4 ExtremeFFS (SanDisk)                                        |

|---|------|---------|---------------------------------------------------------------------|

|   |      |         | 5.1.3.5 OneFS (Isilon)                                              |

|   |      |         | 5.1.3.6 emFile (Segger Microcontroller Systems)                     |

|   | 5.2  | Compa   | arisons of the presented FFS                                        |

|   | 5.3  | FLARE   | a Design Environment for Flash-based Critical Applications          |

|   |      | 5.3.1   | FLARE Architecture                                                  |

|   |      |         | 5.3.1.1 System Configuration Management                             |

|   |      |         | 5.3.1.2 Flash Memory Simulator                                      |

|   |      |         | 5.3.1.3 Dependability Evaluation                                    |

|   |      |         | 5.3.1.4 Utilities                                                   |

|   |      | 5.3.2   | FLARE Technology Roadmap                                            |

|   |      | 5.3.3   | OSs                                                                 |

|   |      | 5.3.4   | Flash-memory Emulator                                               |

|   |      |         | 5.3.4.1 User Level Emulation                                        |

|   |      |         | 5.3.4.2 Kernel Level Emulation                                      |

|   |      | 5.3.5   | Workload                                                            |

|   |      | 5.3.6   | Interface                                                           |

|   |      | 5.3.7   | Core Functions: YAFFS and Partitioning                              |

|   |      | 5.3.8   | Fault Injector                                                      |

|   |      | 5.3.9   | Monitor and Control                                                 |

|   |      | 5.3.10  | Snapshots                                                           |

|   | 5.4  | Wear L  | eveling Strategies: An Example                                      |

|   |      | 5.4.1   | Circular Buffer Wear Leveling: Modeling and Lifetime Estimation 112 |

|   |      | 5.4.2   | Examples                                                            |

| _ |      |         |                                                                     |

| 6 | A Ca | se Stud | y: the Space Environment 117                                        |

|   |      | U       |                                                                     |

|   | 6.2  |         | Flash Memory Space-oriented Design                                  |

|   |      | 6.2.1   | Storage Capacity                                                    |

|   |      |         | Power Consumption                                                   |

|   |      | 6.2.3   | Mass and Volume                                                     |

|   |      | 6.2.4   | Performance                                                         |

|   |      | 6.2.5   | Lifetime and Reliability                                            |

|   |      | 6.2.6   | Radiation and Error Rates                                           |

|   |      | 6.2.7   | Wrap-up                                                             |

|   | 6.3  | Sentin  | el 2                                                                |

|   |      | 6.3.1   | Onboard Data Storage                                                |

|   |      | 6.3.2   | Storage capacity                                                    |

|   |      |         |                                                                     |

|    |       | 6.3.3     | Mass and volume                                              | 126 |

|----|-------|-----------|--------------------------------------------------------------|-----|

|    |       | 6.3.4     | Power consumption                                            | 126 |

|    |       | 6.3.5     | Performances                                                 | 126 |

|    |       | 6.3.6     | Lifetime and reliability                                     | 126 |

|    |       | 6.3.7     | Bit Error Rate (BER)                                         | 127 |

| A  | Reli  | ability ( | Overview                                                     | 131 |

|    | A.1   | Mean      | Time Between Failures (MTBF) and Mean Time To Failure (MTTF) | 131 |

|    | A.2   | Failure   | e Rate                                                       | 132 |

|    | A.3   | Failur    | re In Time (FIT)                                             | 132 |

|    | A.4   | Reliat    | pility Functions                                             | 133 |

|    | A.5   | An Exa    | ample                                                        | 133 |

| В  | Flas  | h-mem     | ory Dependability: Screening and Qualification               | 135 |

|    | B.1   | Screer    | ory Dependability: Screening and Qualification               | 135 |

|    |       | B.1.1     | Reliability Methodologies                                    | 136 |

|    |       | B.1.2     | Arrhenius plot (accelerated-temperature data retention)      | 137 |

|    |       | B.1.3     | An example: flash-memory                                     |     |

|    | B.2   | Failure   | e rate assessment                                            | 140 |

| С  | Prin  | ciples o  | of Error Correcting Codes                                    | 145 |

|    | C.1   | ECC P     | rinciples                                                    | 145 |

|    |       |           | Error Detection                                              |     |

|    |       | C.1.2     | Error Correction                                             | 148 |

|    |       | C.1.3     | Hamming bound                                                | 148 |

|    | C.2   | Bose-0    | Chaudhuri-Hocquenhem Codes Design Flow                       | 149 |

|    |       | C.2.1     | Design Requirements                                          | 149 |

|    |       | C.2.2     | Parameters Evaluation                                        | 150 |

|    |       | C.2.3     | Code Characterization                                        | 151 |

|    |       | C.2.4     | Shortened Codes                                              | 152 |

|    | C.3   | Error l   | Detecting and Correcting Codes: The actual trend             | 152 |

|    |       | C.3.1     | Examples                                                     | 153 |

|    | C.4   | Error o   | correcting techniques for future NAND flash memory           | 155 |

| D  | List  | of symł   | bols and acronyms                                            | 157 |

| Bi | bliog | aphy      |                                                              | 163 |

## LIST OF FIGURES

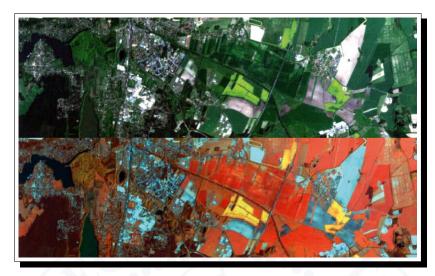

| 1.1  | Sentinel 2 (with courtesy of European Space Agency)                                       | 3  |

|------|-------------------------------------------------------------------------------------------|----|

| 1.2  | Simulated Sentinel-2 image (with courtesy of European Space Agency)                       | 4  |

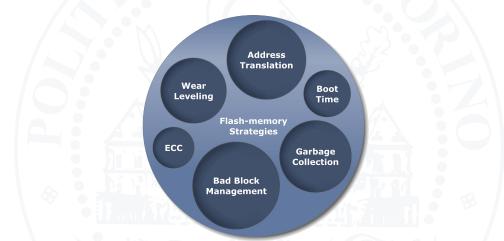

| 2.1  | A possible taxonomy of the management strategies for flash memories                       | 10 |

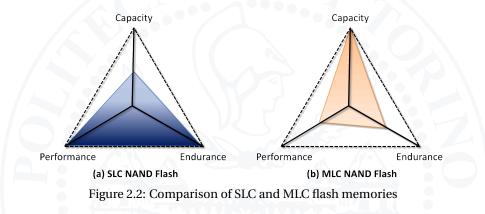

| 2.2  | Comparison of SLC and MLC flash memories                                                  | 11 |

| 2.3  | SLC NAND Block Architecture                                                               | 13 |

| 2.4  | A 256MB Single Plane 2KB-Page SLC NAND Flash Device                                       | 14 |

| 2.5  | A 512MB Dual Plane 2KB-Page SLC NAND Flash Device                                         | 14 |

| 2.6  | A 1GB Dual Plane 2KB-Page MLC NAND Flash Device                                           | 15 |

| 2.7  | A 2GB Dual Plane 4KB-Page MLC NAND Flash Device                                           | 15 |

| 2.8  | High-level Flash-based Hard Disk                                                          | 16 |

| 2.9  | (a) High-level and (b) low-level view of flash architecture                               | 20 |

| 2.10 | Charge Loss Mechanism in NAND Flash                                                       | 21 |

| 2.11 | Endurance in NAND Flash                                                                   | 23 |

| 3.1  | NAND Flash memory Organization                                                            | 27 |

| 3.2  | NAND Flash memories Program Disturbances                                                  | 28 |

| 3.3  | Program Disturbances in NAND Flash                                                        | 29 |

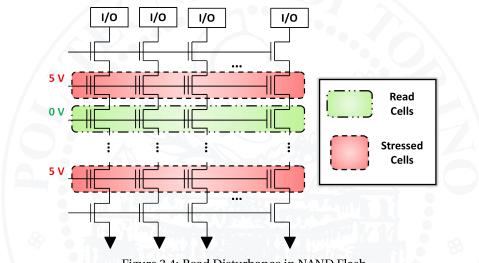

| 3.4  | Read Disturbance in NAND Flash                                                            | 30 |

| 3.5  | NAND Flash memory Intra-cell Faults                                                       | 33 |

| 3.6  | NAND Flash memory Inter-cells Faults                                                      | 34 |

| 3.7  | BF&D Extended Test Algorithm                                                              | 36 |

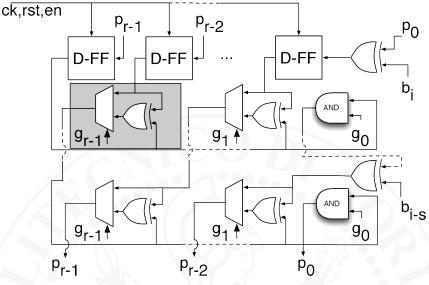

| 4.1  | Architecture of a <i>r</i> -bit PPLFSR with <i>s</i> -bit parallelism.                    | 44 |

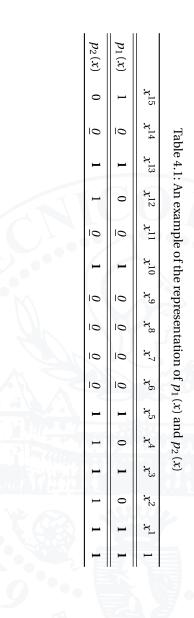

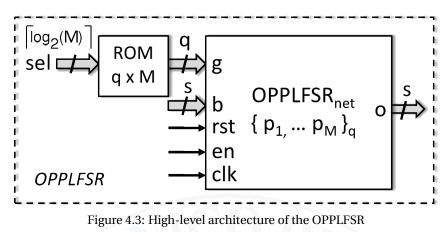

| 4.2  | Example of the resulting PPLFSR (a) and OPPLFSR (b) with 8-bit parallelism for $x^{15}$ , |    |

|      | $x^{14}$ and $x^{13}$ of $p_1(x)$ and $p_2(x)$                                            | 47 |

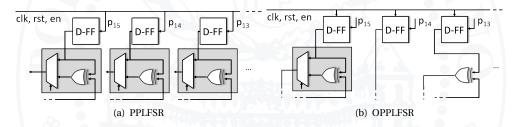

| 4.3  | High-level architecture of the OPPLFSR                                                    | 48 |

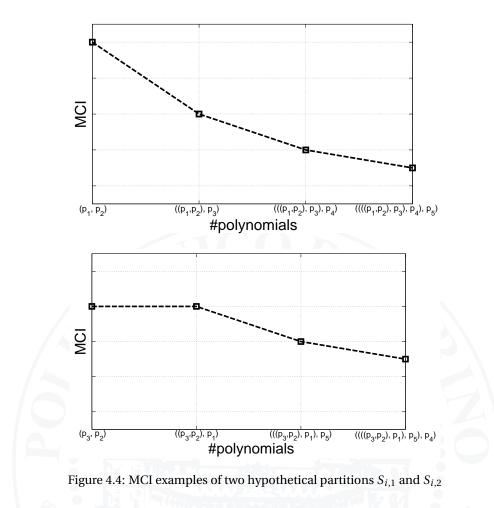

| 4.4  | MCI examples of two hypothetical partitions $S_{i,1}$ and $S_{i,2}$                       | 50 |

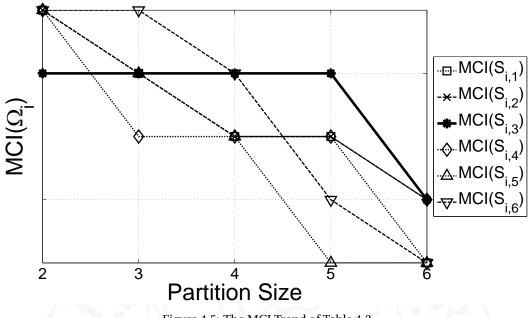

| 4.5  | The MCI Trend of Table 4.2                                                                | 52 |

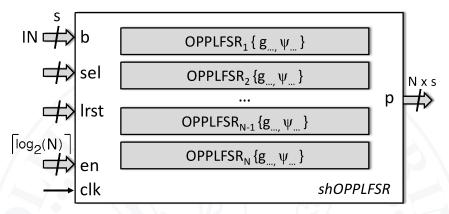

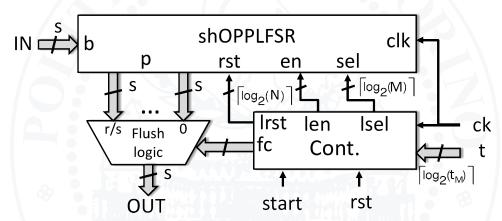

| 4.6  | The shOPPLFSR architecture is composed by multiple OPPLFSRs                               | 53 |

| 4.7  | High-level architecture of the adaptable encoder highlighting the three main building     |    |

|      | blocks and their main connections.                                                        | 54 |

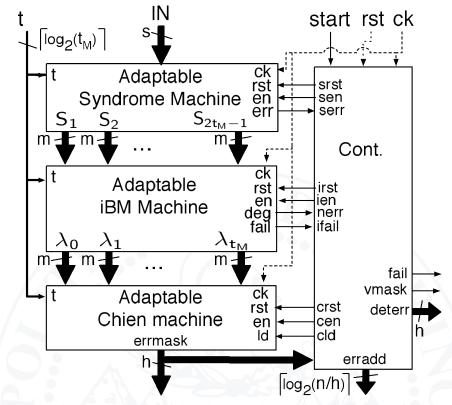

| 4.8  | High-level architecture of the adaptable decoder, highlighting the four main building               |     |

|------|-----------------------------------------------------------------------------------------------------|-----|

|      | blocks: the adaptable syndrome machine, the adaptable iBM machine, the adaptable                    |     |

|      | Chien machine, and the controller in charge of managing the overall decoding process                | 56  |

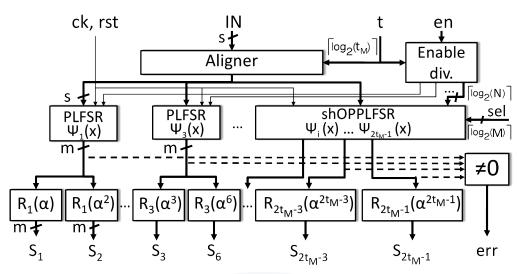

| 4.9  | Architecture of the adaptable Syndrome Machine                                                      | 57  |

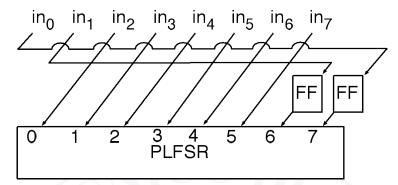

| 4.10 | Example of the schema of a byte aligner for $t = 2$ and $s = 8$                                     | 58  |

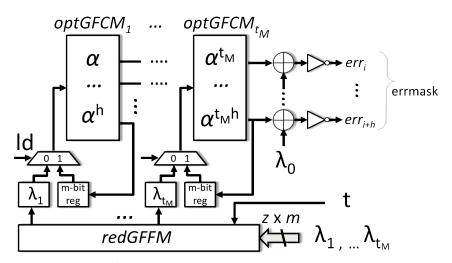

| 4.11 | Architecture of the proposed parallel adaptable Chien Machine with parallelism equal                |     |

|      | to <i>h</i>                                                                                         | 61  |

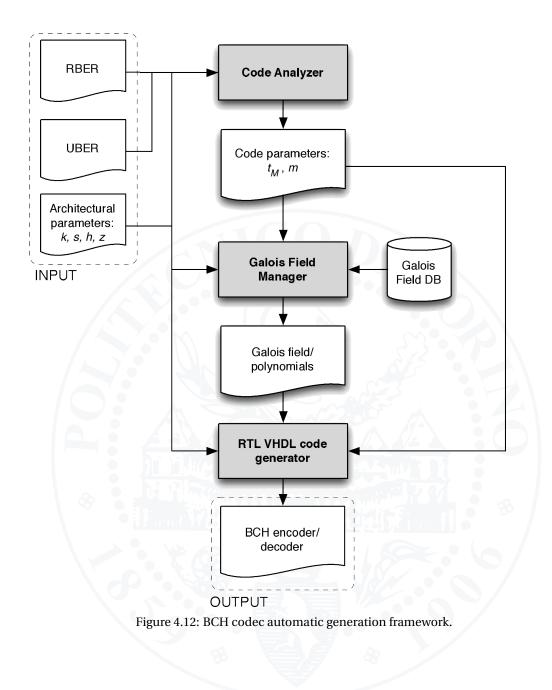

| 4.12 | BCH codec automatic generation framework                                                            | 63  |

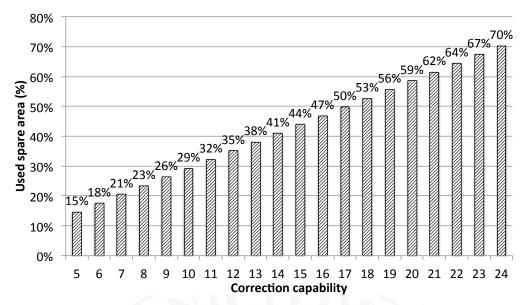

| 4.13 | Percentage of spare area dedicated to parity bits while changing the correction capa-               |     |

|      | bility of the adaptable codec of Arch. 2 and Arch. 3                                                | 68  |

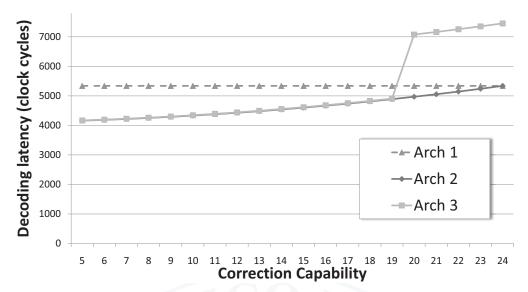

| 4.14 | Worst case decoding latency for the three architectures considered                                  | 69  |

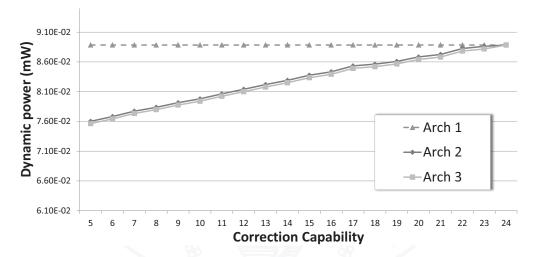

| 4.15 | Worst case dynamic power consumption of the three decoders for the three consid-                    |     |

|      | ered architectures. Power is expressed in mW                                                        | 70  |

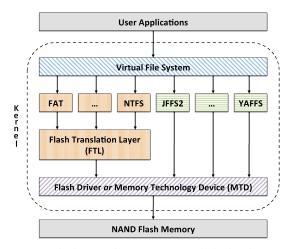

| 5.1  | Flash Translation Layer and Flash File Systems                                                      |     |

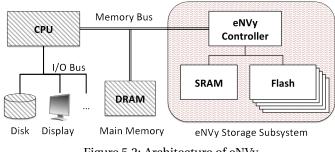

| 5.2  | Architecture of eNVy                                                                                |     |

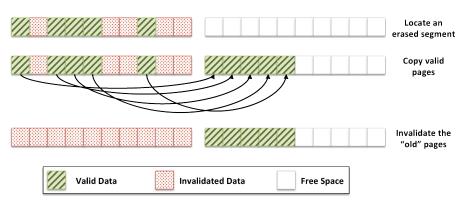

| 5.3  | Steps of the eNVy cleaning process                                                                  | 80  |

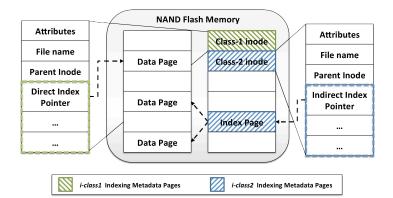

| 5.4  | An example of direct ( <i>i-class1</i> ) and indirect ( <i>i-class2</i> ) indexing for a NAND flash | 82  |

| 5.5  | Flexible Cell Programming                                                                           | 84  |

| 5.6  | The layout of flash blocks in FlexFS                                                                | 85  |

| 5.7  | An example of Data Migration                                                                        | 85  |

| 5.8  | An example of Dynamic Allocation                                                                    | 87  |

| 5.9  | An example of Wearing Rate Control                                                                  |     |

| 5.10 | The YAFFS Architecture                                                                              | 90  |

| 5.11 | An Example of YAFFS Operations                                                                      | 91  |

| 5.12 | An example of Tnode tree for data file                                                              | 93  |

| 5.13 | An high-level overview of FLARE Design Environment                                                  | 101 |

| 5.14 | A detailed view of FLARE Architecture                                                               | 104 |

| 5.15 | A view of the partitioning process (Source Navigator)                                               | 108 |

|      | A view of the FLARE design environment                                                              |     |

| 5.17 | A view of the FLARE design environment (2)                                                          | 111 |

|      | A possible graphical report                                                                         |     |

| 5.19 | A 1GB MLC NAND flash device                                                                         | 112 |

| 5.20 | A 4GB Dual Plane MLC NAND flash device                                                              | 114 |

| 6.1  | Sentinel 2 (with courtesy of European Space Agency)                                                 | 123 |

| 6.2  | Architecture of the Sentinel 2 MMFU [129]                                                           | 125 |

| B.1  | Arrhenius Diagram of a Floating Gate device                                                         | 138 |

|      |                                                                                                     |     |

|      |                                                                                                     |     |

| B.2  | A possible survival function S(t) for flash-memory           |

|------|--------------------------------------------------------------|

| C.1  | General Encoding/Decoding structure of Error Correcting Code |

| C.2  | A "0000" codeword after a single-bit error                   |

| C.3  | Generic case Codeword                                        |

| C.4  | The wrong "0001" read codeword                               |

| C.5  | BCH Code Design Flow                                         |

| C.6  | Examples of Raw BER and Uncorrected BER                      |

| C.7  | ECC Example for point "Large Block"                          |

| C.8  | Uncorrected BER for different Error Correcting Codes (ECCs)  |

|      | 512B-ECC16 protecting a 2KB page 154                         |

| C.10 | 1KB-ECC16 protecting a 2KB page                              |

## LIST OF TABLES

| 1.1 | NAND Vs NOR flash-memory 2                                                            |

|-----|---------------------------------------------------------------------------------------|

| 1.2 | Operations Voltage for Flash Memories                                                 |

| 2.1 | NAND SLC Vs MLC                                                                       |

| 3.1 | NAND Flash Memory Disturbances                                                        |

| 3.2 | NAND Flash Memories Circuit Level Faults                                              |

| 4.1 | An example of the representation of $p_1(x)$ and $p_2(x)$                             |

| 4.2 | An example of $\Omega_i$                                                              |

| 4.3 | Characteristics of the analyzed architectures                                         |

| 4.4 | Worst case Parity Bits and Encoding/Decoding Latency. $sh_{poly}$ denotes the maximum |

|     | number of minimal polynomials shared in the shOPPLFSR of the syndrome machine . 67    |

| 4.5 | Synthesis Results                                                                     |

| 4.6 | Minimal polynomials expressed with the corresponding hexadecimal string of coeffi-    |

|     | cients                                                                                |

| 4.7 | Generator polynomial expressed with the corresponding hexadecimal string of coef-     |

|     | ficients                                                                              |

| 5.1 | Comparison among the strategies of the presented FFS                                  |

| 5.2 | Performance comparison among the presented FFS                                        |

| 6.1 | Comparison of DRAM and NAND flash technology                                          |

| 6.2 | Sentinel 2 MMFU Requirements                                                          |

| 6.3 | MMFU Storage Features                                                                 |

| B.1 | Charge Loss Mechanisms and Related Activation Energy                                  |

| B.2 | Main parameters adopted for flash-memory screening and qualification                  |

| B.3 | Reliability Data                                                                      |

| C.1 | The Hamming distance between pairs of codewords of 4-bit code                         |

| C.2 | BCH code properties                                                                   |

Flash memory is a technology that doesn't depend on Moore's Law...this technology should go at least 10 generations!

Gordon Knight, CEO of Nanochip

## **INTRODUCTION**

#### **Contents of this chapter**

1.1 Mission-critical applications

1.2 Thesis organization

lash memory, thanks to the advances in the manufacturing processes, is continuously reducing its typical feature size. E.g., 20nm NAND flash devices are currently available [85]. These advances are producing enormous gains in speed, single chip array sizes, and consequent reduction in power consumption, both in absolute and relative (watt/bit) terms.

The current market provides two major types of flash-memory: NOR and NAND flashmemory. NOR flash-memory is for EEPROM replacement and is more suitable for program execution. NAND flash-memory is more suitable for storage systems [22, 66]. They both exploit the Floating Gate (FG) transistor, but they differ in the way of performing operations and in the interconnections among cells<sup>1</sup>. Table 1.1 briefly sums up the main characteristic of these types of flash-memory.

The main NAND flash merit is the high speed programming/erasing, while the main demerits are the slow random access and the impossibility of byte-programming. At the opposite, the main NOR flash merit is the high speed random access and the possibility

<sup>&</sup>lt;sup>1</sup>e.g., NAND flash adopts FN-Tunneling effect for program/erase operations and are much denser than NOR flash

#### 1. INTRODUCTION

|      | Standby/<br>Active<br>Power | Cost<br>per<br>bit | R/W/E Speed  | Capacity | Erase<br>Cycles | Code<br>Execu-<br>tion | Interface |

|------|-----------------------------|--------------------|--------------|----------|-----------------|------------------------|-----------|

| NAND | Med/Low                     | Low                | Med/High/Med | High     | 10 <sup>5</sup> | Hard                   | I/O-like  |

| NOR  | Low/Med                     | High               | High/Low/Low | Low      | $10^{4}$        | Easy                   | SRAM-like |

Table 1.1: NAND Vs NOR flash-memory

of byte-programming. However, NOR flash suffers of slow programming/erasing.

This document addresses only NAND flash-memories. They are increasingly used for data storage both in consumer electronics (e.g., USB flash drives, Solid State Drive (SSD), digital cameras, MP3 players) and mission critical applications, thanks to their:

- compactness: NAND flash are much more compact than magnetic HDs;

- performance: they are faster than a common magnetic HD (e.g., Read/Write/Erase about μs/μs/ms), providing a higher data throughput;

- **power consumption**: there is no physical movement on the disk (i.e., there are no mechanical parts)<sup>2</sup>;

- shock-resistance: the resistance to shocks is much higher than magnetic HDs;

NAND flash is the most suitable solution for embedded applications. Although actual magnetic HD are moving toward higher sizes, in order to leverage the yield costs (e.g., 1TB for about 120\$), embedded applications usually do not need such a huge memory. E.g., an embedded application like a mobile phone can ask around 16/32GB HD. Applying a magnetic HDs to such a system has two main difficulties: (i) there is no physical space where a magnetic HD can fit; (ii) nowadays it can be really tough or even not possible to find a magnetic HD with that size.

These motivations and many others are pushing for an extensive use of NAND flash memory as mass-memory devices. However, NAND flash research and literature in the mission-critical environment is not as established as in the commercial applications. Mission-critical applications and hi-rel electronics are struggling in keeping the pace with those advances, for multiple reasons.

<sup>&</sup>lt;sup>2</sup> the lack of mechanical parts, in turn, implies also an higher reliability

#### **1.1 Mission-critical applications**

It is a matter of fact that NAND flash memory devices are well established in consumer market. However, it is not true that the same architectures adopted in the consumer market are suitable for mission critical applications like space [16, 18]. In fact, USB flash drives, digital cameras, MP3 players are usually adopted to store "less significant" data which are not changing frequently (e.g., MP3s, pictures, etc.). Therefore, in spite of NAND flash's drawbacks, a modest complexity is usually needed in the logic of commercial flash drives [16]. On the other hand, mission critical applications have different reliability requirements from commercial scenarios. Moreover, they are usually playing in a hostile environment (e.g., the space) which contributes to worsen all the issues [17].

#### **1.1.1** An example: the space environment

Thanks to the experience at the European Space Research and Technology Centre (ES-TEC) in Noordwijk, we can provide an example w.r.t. the critical space environment. Fig. 1.1 shows Sentinel-2. It is the first space mission with a flash-based mass-memory device.

Figure 1.1: Sentinel 2 (with courtesy of European Space Agency)

Sentinel-1 is already flying, while Sentinel-2 will fly soon. Once they both are opera-

tional, this pair of satellites will provide global coverage every five days, delivering highresolution optical imagery for Global Monitoring for Environment and Security (GMES) land and emergency services. Fig 1.2 shows an example of a land monitoring image.

Figure 1.2: Simulated Sentinel-2 image (with courtesy of European Space Agency)

The specific requirements for an avionic application (e.g., Sentinel-2) must determine the final choice of memory used and European Space Agency's duty is to provide new workarounds to known reliability problems to go from (low performance) failure immune systems to (high performance) failure tolerant systems.

Several studies and researches revealed Samsung NAND flash memory to be more suitable than other flash memory to the use in the space environment [62, 100, 101, 102, 119]. However, the choice of a particular technology presents several issues.

The tremendous advances in the manufacturing processes strongly affect the applicability of the studies cited above to the modern mission-critical applications. We need clever solutions to minimize the cost related to upscreening and ruggedisation operations of newer technologies, by exploiting the previous ones.

Space usually incorrectly refers to flash-memory as Non Volatile RAM (NVRAM). Since NAND flashes are not NVRAM, they have different failure modes from Random Access Memory (RAM). Furthermore, space applications have always dealt with RAMs and not often with NAND flash. Therefore, the true risk is that the common fault tolerant techniques (e.g., ECC) of RAMs will be applied to devices (i.e., NAND flash) which have completely different failure modes. As a consequence, proper fault tolerant strategies are needed.

Each space mission usually provides an ad-hoc solution. Therefore, we need to explore technology-independent techniques to minimize changes with technology and to avoid the rebuilding of the solutions from scratch.

Each mission is usually provided with proprietary solution from external contractors. It is needed a powerful framework to properly validate, verify and, generally speaking, evaluate the proposed solutions. This environment is still missing for NAND flash memory for space applications, because of the marginal and non-critical use of NAND flash in this field. However, this framework is already under development within this PhD activity [17].

#### 1.2 Thesis organization

This thesis presents the results of 3 years of research in the dependability assessment of NAND flash memory for mission critical applications. We aim at providing practical valuable guidelines, comparisons and tradeoffs among the huge number of dimensions of fault tolerant methodologies for NAND flash applied to critical environments. We hope that such guidelines will be useful for our ongoing research and for all the interested readers. The thesis is organized as follows.

### **Chapter 2**

#### Dependability of NAND Flash Memory: An Overview

Chapter 2 introduces the main issues related to the dependability assessment of NAND flash devices. From a technological standpoint, all NAND flash are not created equal and may differ in cell types, architecture, performance, timing parameters, command set, etc. However, they respect the following general organization. A NAND flash-memory is usually partitioned into blocks. Each block has a fixed number of pages and each page has a fixed size. A block is the smallest unit for erase operations, while read and write operations are done in terms of pages. Therefore, a page can be erased only if its whole corresponding block is erased. In other words, the space already written cannot be overwritten unless it is erased from the flash-memory device. This is one of the main challenging aspects of flash-memories. Moreover, flash-memory wears out after a certain number of erasure cycles. If the erasure cycles of a block exceed this number, it becomes a "bad block" and is not reliable for storing data anymore.

#### **Chapter 3**

#### Modeling and Testing NAND Flash memory

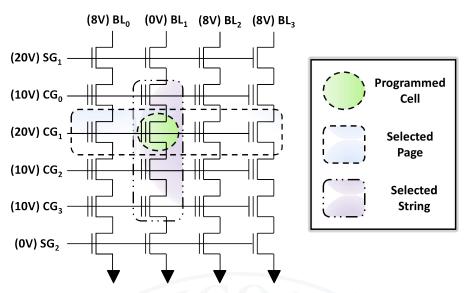

NAND flash operations rely on FN-Tunneling, which is based on probabilistic concepts. It is not possible to determine exactly how many electrons will enter the Floating Gate (FG), but there is a certain probability<sup>3</sup> that a well-defined number of them will do it. FN-Tunneling requires high voltages to work properly (see Table 1.2).

|             | V <sub>CG</sub>     | VD     | Vs     | VB     |  |

|-------------|---------------------|--------|--------|--------|--|

| Programming | 20V                 | Ground | Ground | Ground |  |

| Reading     | 5V+V <sub>B</sub>   | ~1V    | 0V     | 0V     |  |

| Erasing     | -10V+V <sub>B</sub> | 4-6V   | Float  | 0V     |  |

Table 1.2: Operations Voltage for Flash Memories

Such voltages highly stress each cell of the NAND memory. In particular, they affect the quality of the oxide of each cell, which in turn causes disturbances during read, write and erase operations.

Chapter 3 presents a complete overview of disturbances, modeling and testing of NAND flash, in conjunction with a novel comprehensive fault model and the related testing algorithm.

#### **Chapter 4**

### Error Correcting Codes for NAND flash memory

Fault tolerance mechanisms are systematically applied to increase reliability and endurance of these devices. In particular, since most available parts are COTS, redundancy must be built into the system to ensure its data integrity during operating lifetime. Redundancy, for example, can be built around multi-chip-modules (MCM), which contains duplicates of one die installed in a single package. Furthermore, proper ECCs are needed. Since independent and manufacturer studies showed NAND flash to have random failures, Bose-Chaudhuri-Hocquenhem (BCH), Perfect Difference Cyclic Set, Low Density Parity Check (LDPC) and similar codes may be a suitable choice. However, each ECC is made of several design dimensions. Choosing the most suitable ECC for a specific mission is always a tradeoff among such dimensions.

<sup>&</sup>lt;sup>3</sup>refer to Schroedinger and Heisenberg equations

Chapter 4 presents an adaptable Bose-Chaudhuri-Hocquenhem (BCH) based design for NAND flash memory. It can dynamically adapt the correcting capability to the specific condition of the memory. The number of parity bits and the decoding complexity are therefore adapted depending on how many errors have to be corrected. An automatic design environment supports the generation of such a architecture. These are two of the most important topics of our ongoing research.

#### Chapter 5

#### Software Management of NAND Flash memory: Issues and Challenges

When using a NAND flash as HD, the file management is a challenging issue to address. In fact, flash memories manage data in a completely different manner if compared to magnetic HDs. Operating Systems (OSs) address this issue with two main approaches: (i) block-device emulation, and (ii) Flash File System (FFS). These methodologies are alternatively adopted for compatibility and performance reasons respectively.

Chapter 5 introduces the main software strategies for tackling NAND flash issues. We propose an overall comparison among several FFSs and we present the novel FLash AR-chitecture Evaluator (FLARE) design environment, one of the most important topic of our ongoing research.

#### Chapter 6

#### A Case Study: the Space Environment

The most critical remark is that, although NAND flash memories provide so many advantages and are a pivotal component in consumer electronics, their use in mission-critical applications (e.g., space) is still under research.

Most of the commercial NAND flash would be deficient in respect of their ability to operate successfully and survive in the space avionics physical environment. For example, commercial systems and components do not often have adequate operating temperature ranges, packaging or radiation harness performance. The availability of fully qualified space memories is not an option for cost, availability, long lead or performance reasons. Commercial Off The Shelves (COTS) NAND flashes need to be adopted. Since most of them are not able to successfully operate and survive in the critical environment, they request additional cost (i.e., upscreening, protection, redundancy, etc.). However, the most recent studies point out that: (a) TID tend to become less significant because of the very thin high-k oxides; (b) latch-up mechanisms are becoming less severe in terms of survivability of the device but more widespread due to the physical (3D) stacking of the bare chips; thus, in spite of a lower bias voltage, latch-up is still an issue for some devices; (c) in modern NAND flash, SEE are becoming more and more similar to SEFI, thus most SEE can be assimilated to new classes of SEFI errors. We therefore need strategies to tackle them at digital level to increase memory failure tolerance.

All issues are worsened by the aggressive scaling down of NAND flash. They are effectively accelerating Moore's Law, with a scaling factor 2 each 2 years. E.g., 20nm NAND flash devices are currently available [85].

#### Appendixes A, B and C

Appendix A provides a generic overview of the main reliability concepts. Appendix B presents the most important issues related to the screening and qualification process of NAND flash memory. Appendix C overviews the ECCs design dimensions and issues.

#### Conclusions

In conclusion, the proposed dependability assessment of NAND flash-based architectures requires both exploring a huge number of design dimensions and evaluating a huge amount of trade-offs among all such dimensions. Moreover, the reliability requirements of critical applications (e.g., space) are much higher than other common applications (e.g., consumer). Therefore, proper methodologies and techniques are needed to accomplish these strict requirements. We hope that this PhD activity will represent a critical contribution to a thorough understanding of the architectural design of NAND flash device within critical environments (e.g., space avionics).

We will try to introduce the concepts required to understand each topic within each chapter. However, topics are usually related among each other. Therefore, some concepts will be re-introduced, when required, in the next chapters.

Unknown

# DEPENDABILITY OF NAND FLASH MEMORY: AN OVERVIEW

#### Contents of this chapter

At least my pencil never crashes!

- 2.1 Flash-memory issues and challenges

- 2.2 Using flash-memory as Hard Disk (HD)

- 2.3Flash-memory Reliability Screening

he increasing demand for high-speed storage capability both in consumer electronics (e.g., USB flash drives, digital cameras, MP3 players, solid state harddisks, etc.) and mission critical applications, makes NAND flash memories a rugged, compact alternative to traditional mass-storage devices such as magnetic harddisks.

The NAND flash technology guarantees a non-volatile high-density storage support that is fast, shock-resistant and very power-economic. At higher capacities, however, flash storage can be much more costly than magnetic disks, and some flash products are still in short supply. Furthermore, the continuous downscaling allowed by new technologies introduces serious issues related to yield, reliability, and endurance of these devices [34, 59, 60, 64, 65, 91, 96]. Several design dimensions, including flash memory technology, architecture, file management, dependability enhancement, power consumption, weight and physical size, must be considered to allow a widespread use of flash-based devices in the realization of high-capacity mass-storage systems [17].

This chapter introduces the main concepts related to the dependability assessment of NAND flash devices. In particular, Section 2.1 presents the most important design dimensions to address when dealing with flash-memory, Section 2.2 explains how to use NAND flash-memory as hard-disks, while Section 2.3 addresses the most recurring concepts and figures of NAND flash data-sheets.

#### 2.1 Flash memory issues and challenges

Although flash memories are a very attractive solution for the development of high-end mass storage devices, the technology employed in their production process introduces several reliability challenges [59, 65, 96]. The so called Flash Translation Layer (FTL) and the native Flash File System (FFS)<sup>1</sup> have to address these problems with proper strategies and methodologies in order to efficiently manage the flash memory device. Fig. 2.1 shows a possible partial taxonomy of such strategies that will be discussed in the sequel of this section [47].

Figure 2.1: A possible taxonomy of the management strategies for flash memories

#### 2.1.1 Technology

The target memory technology is the first parameter to consider when designing a flashbased mass-memory device [18]. The continuous technology downscaling strongly af-

<sup>&</sup>lt;sup>1</sup>refer to Section 2.2 for more details about FTL and FFS

fects the reliability of the flash memory cells, while the reduction of the distance among cells may lead to several types of cell interferences [64, 91].

From the technology standpoint, two main families of flash memories do exist: (i) NOR flash memories and (ii) NAND flash memories. A deep analysis of the technological aspects of NOR and NAND flash memories is out of the scope of this document<sup>2</sup>. Both technologies use floating-gate transistors to realize non-volatile storing cells. However, the NAND technology allows denser layout and greater storage capacity per unit of area. It is therefore the preferred choice when designing mass-storage systems, and it will be the only technology considered in this document.

NAND flash memories can be further classified based on the number of bit per cell the memory is able to store. Single Level Cell (SLC) memories store a single bit per cell, while Multi Level Cell (MLC) memories allow to store multiple bits per memory cell. Fig. 2.2 shows a comparison between SLC and MLC NAND flash memories [72] considering three main characteristics: capacity, performance and endurance.

The MLC technology offers higher capacity compared to the SLC technology at the same cost in terms of area. However, MLC memories are slightly slower than SLC memories. MLC memories are more complex, cells are closer, there are multiple voltage references and highly-dependable analog circuitry is requested [13]. The result is an increased Bit Error Rate (BER) that reduces the overall endurance and reliability [90], thus requiring proper error correction mechanisms at the chip and/or FTL/FFS level.

Consumer electronic products, that continuously demand for increased storage capacity, are nowadays mainly based on MLC NAND flash memories, while mission-critical applications that require high reliability mainly adopt SLC memories [141].

<sup>&</sup>lt;sup>2</sup> the reader may refer to [60] for additional information

The interested reader may refer to [24, 34] for more detailed comparisons between SLC and MLC technology. Table 2.1 provide some additional figures about these two technologies.

|     | Features      |               |              | Architecture |              | Reliability     |     |    | Array Operations |      |                |              |

|-----|---------------|---------------|--------------|--------------|--------------|-----------------|-----|----|------------------|------|----------------|--------------|

|     | Bits<br>/cell |               | Bus<br>width |              | Page<br>size | Pages<br>/block | NOP |    | Endu-<br>rance   |      |                |              |

| SLC | 1             | 3.3V,<br>1.8V |              | 1 or<br>2    | 2,112B       | 64+             | 1   | 1  | <10 <sup>5</sup> | 25us |                | 1.5 –<br>2ms |

| MLC | 2+            | 3.3V          | x8           | 2+           | 4,314B+      | 128+            | 4+  | 4+ | <10 <sup>4</sup> | 50us | 600 -<br>900us | 2ms          |

Table 2.1: NAND SLC Vs MLC

Although some entries of the table may not be familiar to the reader, they will be addressed shortly in the sequel of this chapter.

#### 2.1.2 Architecture

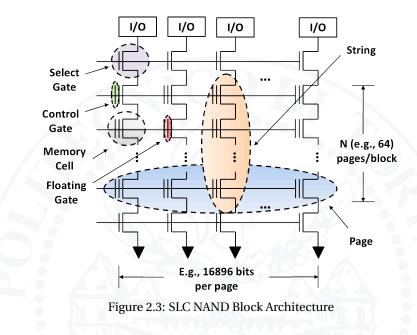

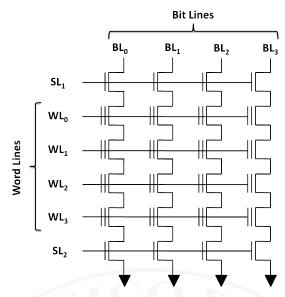

The hardware architecture of a NAND flash memory is usually a hierarchical structure organized into cells, pages, blocks and planes.

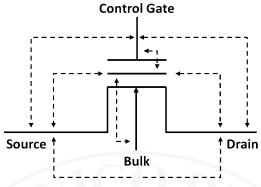

**Memory cells** A memory cell is characterized by the so called Floating Gate (FG) inside which electrons can be kept. According to the particular technology chosen, the memory cell can store either 1 bit (i.e., SLC) or 2 bits (i.e., MLC). They will have either  $2^1$  (i.e., "0", "1") or  $2^2$  (i.e., "00", "01", "10", "11") voltage reference levels respectively.

**Pages** A page groups a fixed number of memory cells. It is the smallest storage unit when performing read and programming operations<sup>3</sup>. Each page includes a data area where actual data are stored and a spare area. The spare area is typically used for system level management, although there is no physical difference from the rest of the page. Pages already written with data must be erased prior to write new values. A typical page size can be 2KB plus 64B spare, but the actual trend is to increase the page size up to 4KB+128B and to exploit the MLC technology.

<sup>&</sup>lt;sup>3</sup>MLC-based devices may allow the so called Partial Page Programming (PPP), which is the ability of programming only a part of the page; a limited Number Of PPP (NOP) per page is allowed; PPP provides more flexibility, but increases the possibility of the so called program disturbances (refer to Chapter 3 for more details about disturbances);

**Blocks** A block is a set of pages. It is the smallest unit when performing erase operations. Therefore, a page can be erased only if its corresponding block is totally erased. A block typically contains 64 pages, with a trend to increase this number to 128 pages per block, or even more. Since flash memories wear out after a certain number of erasure cycles (endurance), if the erasure cycles of a block exceed this number, the block cannot be considered anymore reliable for storing data. A typical value for the endurance of an SLC flash memory is about  $10^6$  erasure cycles.

Fig. 2.3 shows the organization of a 128KB+4KB SLC NAND flash-memory block [34]. In this example, we have 2KB+64B per page and 64 pages per block.

**Planes** Finally, blocks are grouped into planes. A flash memory with *N* planes can read-/write and erase *N* pages/blocks at the same time [34].

#### 2.1.2.1 Examples of NAND Flash Architecture

For sake of completeness, we provide a few examples of NAND flash devices. Examples includes both SLC and MLC technology [34].

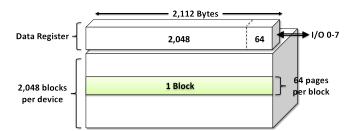

**256MB Single Plane SLC NAND Device** Fig. 2.4 provides the first basic example of a single plane 256MB NAND flash device.

#### 2. DEPENDABILITY OF NAND FLASH MEMORY: AN OVERVIEW

Figure 2.4: A 256MB Single Plane 2KB-Page SLC NAND Flash Device

Each page is 2KB+64B long. SLC technology is used. A data register able to store a full page is provided, and an 8-bit data bus (i.e., I/O 0-7) is used to access stored information.

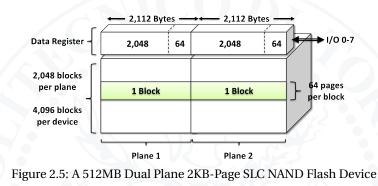

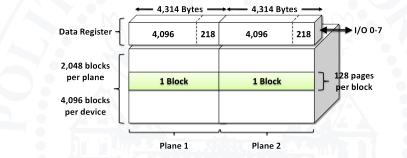

**512MB Dual Plane SLC NAND Device** Fig. 2.5 shows an example of a 512MB dual plane SLC NAND flash memory architecture.

The double capacity w.r.t. Fig. 2.4 is accomplished by adding an additional plane<sup>4</sup>. Each plane can store 256MB with pages of 2KB+64B. A data register able to store a full page is provided for each plane, and an 8-bit data bus (i.e., I/O 0-7) is used to access stored information. Doubling the planes basically doubles the operations throughput by allowing:

- Read/Write two pages of different planes at the same time;

- Erase two blocks of different planes at the same time;

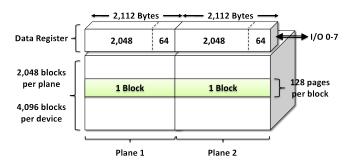

**1GB Dual Plane MLC NAND Device** Fig. 2.6 shows an example of a 1GB dual plane NAND flash device.

<sup>&</sup>lt;sup>4</sup>Plane 1 and plane 2 are addressing the even- and odd-numbered blocks respectively

Figure 2.6: A 1GB Dual Plane 2KB-Page MLC NAND Flash Device

The doubled capacity w.r.t. Fig. 2.5 is accomplished by adopting a MLC technology with 2-bit per cell. In order to indicate this change in a simple way, Fig. 2.6 presents a doubled number of pages (i.e., 128). The smart reader would note that the capacity is doubled, while the area is the same of Fig. 2.5.

**2GB Dual Plane 4KB-Page MLC NAND Device** Fig. 2.7 shows a an example of a 2GB dual plane NAND flash device.

Figure 2.7: A 2GB Dual Plane 4KB-Page MLC NAND Flash Device

The double capacity w.r.t. Fig. 2.6 is accomplished by adopting a page 4KB+218B long. Each plane can store 1GB with pages of 4KB+218B. Data registers are growing accordingly, while an 8-bit data bus (i.e., I/O 0-7) is still used to access stored information.

**Note** Several variations of this basic architecture can be produced, with main differences in performance, timing and available set of commands [34]. To allow interoperability among different producers, the Open NAND Flash interface (ONFi) Workgroup is trying to provide an open specification (ONFi specification) to be used as a reference for future designs [104]. To March 11, 2013, Samsung and Toshiba are not member of

the ONFi Workgroup. E.g., Samsung is moving toward legacy solutions like the One-NAND<sup>™</sup>technology [114]. OneNAND will not be addressed in the sequel of this document.

#### 2.1.3 Address translation and boot time

Each page of a flash is identified by both a logical and physical address. Logical addresses are provided to the user to identify a given data with a single address, regardless if the actual information is moved to different physical locations to optimize the use of the device. The *address translation* mechanism that maps logical addresses to the corresponding physical addresses must be efficient to generate a minor impact on the performance of the memory. The address translation information must be stored in the non-volatile memory to guarantee the integrity of the system. However, since frequent updates are performed, a translation lookup table is usually stored in a (battery-backed) RAM (Fig. 2.8), while the flash memory stores the metadata to build this table. The size of the table is a trade-off between the high cost of the RAM and the performance of the storage system.

Figure 2.8: High-level Flash-based Hard Disk

Memories with a large page size require less RAM, but they inefficiently handle small writes. In fact, since an entire page must be written into the flash with every flush, larger pages cause more unmodified data to be written for every (small) change. Small page sizes efficiently handles small writes, but the resulting RAM requirements can be unaffordable. At the FTL and at the FFS level, the translation table can be implemented both at the level of pages or blocks thus allowing to trade-off between the table size and the granularity of the table [47].

#### 2.1.4 Garbage collection

Data stored in a page of a flash memory cannot be overwritten unless an erasure of the full block is performed. To overcome this problem, when the content of a page must be updated, the new data are usually saved in a new free page. The new page is marked as *valid* while the old page is marked as *invalid*. The address translation table is then updated to allow the user to access the new data with the same logical address. This process introduces several challenges both at the FTL and at the FFS level.

At a certain point, free space is going to run out. When the amount of free blocks is less than a given threshold, invalidated pages must be erased in order to free some space. The only way to erase a page is to erase the whole block it belongs to. However, a block selected for erasure may contain both valid and invalid pages. As a consequence, the valid pages of the block must be copied into other free pages. The old pages can be then marked as invalid and the selected block can be erased and made available for storage.

This cleaning activity is referred to as *garbage collection*. Garbage collection decreases the flash memory performance and therefore represents a critical aspect of the design of a native flash file system. Moreover, as described in the next subsection, it may impact on the endurance of the device. The key objective of an efficient garbage collection strategy is to reduce garbage collection costs and evenly erase all blocks.

Flexible cleaning algorithms [137], greedy policies, aging functions [28] or periodical collection approaches [130] can be adopted to minimize the cleaning cost.

#### 2.1.5 Memory wearing

As previously introduced, flash memories wear out after a certain number of erasure cycles (usually between  $10^4$  and  $10^5$  cycles). If the number of erasures of a block exceeds this number, the block is marked as a *bad block* since it cannot be considered anymore reliable for storing data. The overall life time of a flash memory therefore depends on the number of performed erasure cycles. *Wear leveling* techniques [21, 23, 28, 35, 112] are used to distribute data evenly across each block of the entire flash memory, trying to level and to minimize the number of erasure cycles of each block. The alternative is to consider higher capacity flash-memory devices, taking care of the resulting drawbacks in terms of weight and volume [20].

There are two main wear leveling strategies: dynamic and static wear leveling. The *dynamic* wear leveling only works on those data blocks that are going to be written, while

the *static* wear leveling works on all data blocks, including those that are not involved in a write operation. Active data blocks are in general wear-leveled dynamically, while static blocks (i.e., blocks where data are written and remain unchanged for long periods of time) are wear-leveled statically. The dynamic and static blocks are usually referred as *hot* and *cold* data, respectively. In MLC memories it is important to move cold data to optimize the wear leveling. If cold data are not moved then the related pages are seldom written and the wear is heavily skewed to other pages. Moreover, every read to a page has the potential to disturb data on other pages in the same block. Thus continuous read-only access to an area can cause corruption, and cold data should be periodically rewritten [77].

Wear leveling techniques must be strongly coupled with garbage collection algorithms at the FTL and at the FFS level. In fact, the two tasks have in general conflicting objectives and the good trade-off must be found to guarantee both performance and endurance. The interested reader may refer to [21] for a comparative analysis of the most used wear leveling algorithms.

#### 2.1.6 Bad block management

As discussed in the previous sections, when a block exceeds the maximum number of erasure cycles, it is marked as a *bad block*. Bad blocks can be detected also in new devices as a result of blocks identified as faulty during the end of production test.

Bad blocks must be detected and excluded from the active memory space. In general, simple techniques to handle bad blocks are commonly implemented. An example is provided by the Samsung's XSR (Flash Driver) and its Bad Block Management scheme [111]. The flash memory is initially split into a reserved and a user area. The reserved blocks in the reserved area represent a *Reserve Block Pool* that can be used to replace bad blocks. Samsung's XSR basically remaps a bad block to one of the reserved blocks so that the data contained in a bad block is not lost and the bad block is not longer used.

#### 2.1.7 Error correcting codes

Fault tolerance mechanisms and in particular Error Correcting Code (ECC) are systematically applied to NAND flash devices to improve their level of reliability. ECCs are costefficient and allow detecting or even correcting a certain number of errors. ECCs have to be fast and efficient at the same time. Several ECC schema have been proposed based on linear codes like Hamming codes [84] or Reed-Solomon (RS) codes [115, 127]. Among the possible solutions, Bose-Chaudhuri-Hocquenhem (BCH) codes are linear codes widely adopted with flash memories [33, 45, 67, 81]. They are less complex than other ECCs, providing also a higher code efficiency. Moreover, manufacturers' and independent studies [42, 48, 138] have shown that flash memories tend to manifest non-correlated bit errors. BCH are particularly efficient when errors are randomly distributed, thus representing a suitable solution for flash memories.

The choice of the characteristics of the ECC is a trade-off between reliability requirements and code complexity, and strongly depends on the target application (e.g. consumer electronics vs mission-critical applications) [18].

ECC can be implemented both at the software-level, or resorting to hardware facilities. Software implemented ECC allow to decouple the error correction mechanisms from the specific hardware device. However, the price to pay for a software-based ECC solution is a drastic performance reduction. For this reason, available file systems tend to delegate the code computation tasks to a dedicate hardware limiting the amount of operations performed in software, at the cost of additional resources (e.g., hardware, power consumption, etc.) and reduced flexibility.

The interested reader may refer to Appendix C for more details about ECCs and BCH. Furthermore, Chapter 4 is addressing the design and the practical implementation of an adaptable BCHs for NAND flash-memory.

#### 2.1.8 Testing

Flash-memory testing is quite different from testing other kinds of memory. In fact, flash-memory experiences disturbances or faults not conforming to any of the traditionally known fault models used in testing RAMs. Firstly, we need specific fault models to properly represent the most frequent physical defects. Then, we are able to devise efficient test algorithms to test them [18].

Chapter 3 about testing flash-memory is thoroughly addressing such a peculiar issue.

#### 2.2 Using flash-memory as Hard Disk (HD)

Among the different issues to consider when designing a flash-based mass-storage system, the file management represents a challenging problem to address [47]. In fact, flash memories store and access data in a completely different manner if compared to magnetic disks. This must be considered at the OS level to grant existing applications an efficient access to the stored information. Two main approaches are pursuit by OSs and flash memory designers: (i) block-device emulation, and (ii) development of native file systems optimized to operate with flash-based devices [22, 47]. Both approaches try to address the issues discussed in Section 2.1.

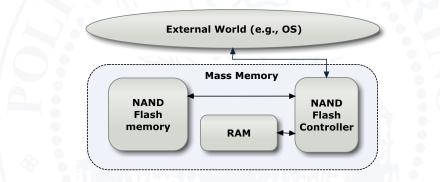

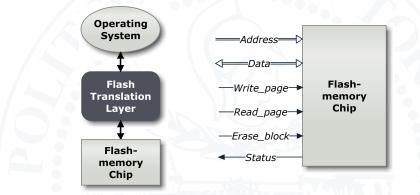

*Block-device emulation* refers to the development of a hardware/software layer able to emulate the behavior of a traditional block device such as a hard-disk, allowing the OS to communicate with the flash using the same primitives exploited to communicate with magnetic-disks. This layer is usually referred as Flash Translation Layer (FTL). Fig. 2.9 (left) shows a very high-level view of a FTL. The FTL "translates" the typical system calls (e.g., open, read, write) of the OS into the proper sequence of commands for the specific flash-memory chip. Fig. 2.9 (right) shows an example of the low-level commands a flash-memory chip [113].

Figure 2.9: (a) High-level and (b) low-level view of flash architecture

The main advantage of this approach is the possibility of reusing available file systems (e.g., FAT, NTFS, ext2) to access the information stored in the flash, allowing maximum compatibility with minimum intervention on the OS. However, traditional file systems do not take into account the specific peculiarities of the flash memories, and the emulation layer alone may be not enough to guarantee maximum performance.

The alternative to the block-device emulation is to exploit the hardware features of the flash device in the development of a *native Flash File System* (FFS). An end-to-end flash-friendly solution can be more efficient than stacking a file system designed for the characteristics of magnetic hard-disks on top of a device driver designed to emulate disks using flash memories [52]. For efficiency reasons, this approach is becoming the preferred solution whenever embedded NAND flash memories are massively exploited [7, 132, 133].

The literature is rich of strategies involving block-device emulation [22, 23, 61, 66, 75]. [47] offers a comprehensive comparison of available native FFS. Furthermore, Chapter 5 discusses how to properly address the issues of using NAND flash memories as massmemory devices from the software standpoint.

#### 2.3 Flash-memory Reliability Screening

We think it is worthy to briefly introduce a pair of concepts that will often recur during our discussions: the *data retention* and the *endurance* of a NAND flash device.

#### 2.3.1 Data Retention (detrapping)

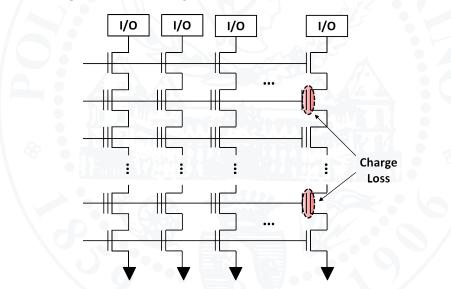

A flash-memory basically works on a Floating Gate (FG) transistor [59]. The programming operation inject electrons in the FG, while the erase operation does the opposite operation. However, as we can imagine, the FG is subject to wearing and damages [34]. Therefore, as Fig. 2.10 shows, charge loss can occur.

Figure 2.10: Charge Loss Mechanism in NAND Flash

This phenomenon is usually referred as *de-trapping*. It basically causes a shift of the threshold voltage  $V_{th}$ , which in turn effectively disturbs the value measured by the sense

amplifiers during read operations.

The *data retention* refers to the ability to maintain stored data between the time of writing and subsequent reading of the stored information. For NAND flash, the data retention time is usually referred as detrapping time  $t_{det}$  (i.e., the time needed by "enough" electrons to exit the FG).

Companies usually state in the data-sheets of their flash-memory that, e.g.,

"(...) Reliable CMOS Floating-Gate Technology (...) Data Retention: 10 Years..." [113].

Since, for obvious reasons of time-to-market, it is not feasible to test the flash-memory for 10 years, accelerated strategies are performed [13]. The interested reader may refer to Appendix B for more information about the screening process of NAND flash-memory.

It is important to point out that the memory cell is <u>not damaged</u>. The block, to which the cell/page belongs to, can be cycled (i.e., erased and re-programmed). In order to improve data retention, it is advisable:

- limiting Program/Erase (P/E) Cycles of a block requiring a high retention;

- limiting read operations as much as possible to reduce the Read Disturbance (RD)<sup>5</sup>;

Therefore, leveling the operations is the most suitable solution for improving the data retention. This is why wear leveling techniques play a fundamental role for accomplishing a high level data retention for our NAND flash device.

#### 2.3.2 Endurance (*trapping*)

Cycling (i.e., continuously performing Program/Erase operations) has the inconvenient side effect of *trapping* electrons in the dielectric [34, 59]. This phenomenon, as Fig. 2.11 shows, causes an irreversible shift of the threshold voltage  $V_{th}$ .

From a circuitry logic standpoint, it can be observable as a failed program or erase operation. The cell is actually <u>physically damaged</u> and cannot be repaired. Therefore, we have to retire the block to which the cell/page belongs to, by marking it as a bad block.

In their data-sheets, companies usually refer to the *endurance* as the number of P/E cycles after which a block of their flash-memory cannot store data in a reliable mode anymore. E.g., Samsung states that their (old) K9XXG08UXM has:

<sup>&</sup>lt;sup>5</sup>refer to Chapter cha:Testing-NAND-Flash-memory for more details about RD

Figure 2.11: Endurance in NAND Flash

"(...) Endurance: 5K Program/Erase Cycles (with 4bit/512byte ECC)..." [113]

In order to improve the endurance of each block, it is advisable:

- checking that program/erase operations did not fail (i.e., SR0 = pass/fail flag set by P/E operations);

- if the program set *SR*0 = *f ail*, moving valid data of current block *A* to another block and, then, marking the old block as *bad*;

- leveling the wearing of each block of the memory (i.e., Wear Leveling);

- using ECCs both for protecting data and for metadata (i.e., ECCs on the spare area);

Therefore, wear leveling techniques and ECCs to user/spare data are the most suitable methodologies for improving NAND flash endurance.

# **SUMMARY**

This chapter introduced the main concepts related to the dependability assessment of NAND flash devices.

NAND flash-memory experiences phenomena not conforming to any of the traditionally known technology. Therefore, we addressed the peculiar issues and challenges of NAND flash.

Using NAND flash-memory as an hard-disk implies to develop either a Flash Translation Layer (FTL) or a Flash File System (FFS). Both methodologies have to implement specific strategies (e.g., wear leveling, ECC) to address the issues discussed above. The complexity of the applied strategies is strictly related with the complexity of the target application. E.g., although they are based on the same technology, a MP3 player will <u>not</u> require the same dependability of a Solid State Drive (SSD) for space applications. Data retention and endurance are pivotal recurring concepts in NAND flash (data-sheets). Wear leveling techniques and ECCs play a fundamental role for accomplishing high levels of data retention and endurance.

The problem with troubleshooting is that trouble shoots back.

Unknown

# **MODELING AND TESTING NAND FLASH MEMORY**

# Contents of this chapter

3.1NAND Flash Disturbances

3.2NAND Flash Circuit Level Modeling

3.3A Comprehensive Fault Model and Test Algorithm for NAND flash

3.4To test or not to test: an important remark

lash-memory testing is quite different from testing other kinds of memory. During read/write/erase operations, flash memories can experience disturbances or faults that do not conform to any of the traditionally known fault models used in testing RAMs [18]. The rationale of flash-memory lies in the Floating Gate (FG) transistor<sup>1</sup>. It is basically a completely insulated metal layer in which electrons can be trapped thanks to the *tunneling* effect. However, this layer is intrinsically not perfectly reliable and leads to problems in terms of *data retention* and *endurance*<sup>2</sup>. Therefore, the reliability issues of NAND flash memory are due to two main reasons: (i) the technology of the FG; (ii) the strong scaling down of technology. The high dependence on technology implies an high complexity of the testing process. Furthermore, the cost-per-cell pushes for a continuous scaling down of technology, which has the side effect of reduc-

<sup>&</sup>lt;sup>1</sup> a detailed dissertation about FG-based devices is out of the scope of this chapter. The interested reader may refer to [59, 60, 64, 143] for more detailed information about this topic

<sup>&</sup>lt;sup>2</sup>refer to Section 2.3 for more details

ing the overall endurance and reliability [18, 90]. A complete technology-independent test is therefore needed.

Literature is rich of approaches for NOR flash-memory. A first possible approach is to adopt a functional/logical model of NOR flashes. [27, 30, 65, 93, 94, 96]. However, the alternative is to model flashes with a defect-based approach [70]. However, both approaches usually propose test algorithm(s) related to their models.

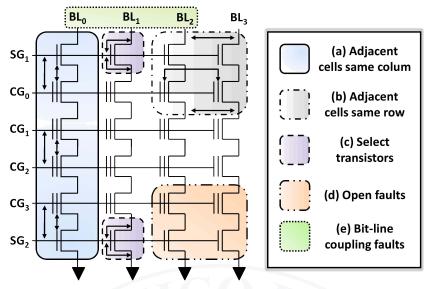

Literature about NAND is not as rich as NOR flash. Although these approaches can be extended to NAND flash memories, other methodologies were addressed. [95] provides a simplified list of fault models for NAND flash memories, according to technological assumptions, and the related test algorithm. [58] presents a possible Bridging Fault (BF) model for NAND flash memories.

All these approaches lack considering all the realistic possible permanent faults. Section 3.1 is a complete analysis of the possible disturbances of NAND flash-memory. The principles of the main operations are discussed too. Section 3.2 addresses the modeling of NAND flash from a circuit level standpoint. Section 3.3 proposes a comprehensive fault model and the related test algorithm which is able to test all the possible fault models of NAND flash independently on the specific technology. Finally, Section 3.4 presents some useful remarks about testing NAND flash devices.

# 3.1 NAND Flash Disturbances

Disturbances are faulty behaviors resulting from the FG technology [59]. As a consequence, they do belong to flash memories, but not to the other memories. The most significant ones are derived from [59] and include: (i) program disturbance faults; (ii) Read Disturbance (RD) faults; (iii) Over-Erase Disturbance (OED) and Over-Program Disturbance (OPD) faults<sup>3</sup>.

All these disturbances are able to modify the original value stored inside a cell into another one.

**Reference NAND Organization** In the sequel, we will refer to the basic organization of Fig.3.1 to explain the main operations of NAND flash-memory and the related issues.

<sup>&</sup>lt;sup>3</sup>Erase disturbance faults (i.e., disturbance faults on erase operations) are considered within NOR testing as Wordline Erase Disturbance (WED) and Bit-line Erase Disturbance (BED) [92], but they are usually excluded from NAND testing [97]; they will not be considered in the sequel of this chapter

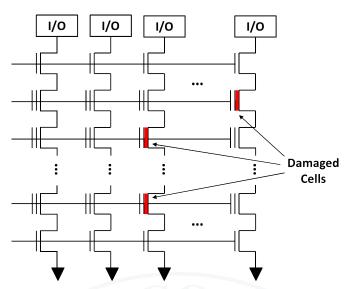

Figure 3.1: NAND Flash memory Organization

Word-Line (WL) is the horizontal line. Bit-Line (BL) is the vertical line. Control gates are connected to WL. BL connects drains together and basically represent data bus. Select Line<sub>1</sub> (SL<sub>1</sub>) and Select Line<sub>2</sub> (SL) connects drains and sources to power supply and to common ground respectively. The voltage combination applied to WL and BL define an operation (i.e., read, erase or program).

During program and erase operations, high voltages are applied to the WL and the BL. Therefore, disturbances along them are more critical in flash memory w.r.t. RAMs [139].

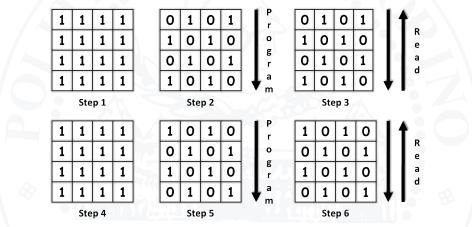

#### 3.1.1 Program Disturbances

The state of an erased cell is logically "1". Programming a single NAND flash-memory cell consists into logically writing a "0". Erasing a cell, means logically writing a "1" again.

Unlike NOR and RAMs are *random* access memory, NAND flash memory are referred as *sequential* access memory. This means that, in order to access (to read and write) a cell, we need to "pass" through the others, stressing them.

Fig. 3.2 shows the programming a single cell C11.