brought to you by TCORE

111

# Single-Piece State-Space Behavioral Models for IC Output Buffers

C. Siviero, I. S. Stievano, P. Savi, I. A. Maio, F. G. Canavero

Dipartimento di Elettronica, Politecnico di Torino Corso Duca degli Abruzzi 24, 10129, Torino, Italy igor.stievano@polito.it

*Abstract*— In this paper enhancements of parametric behavioral models for the output buffers of digital ICs are explored. A model based on a single-piece structure, which offers improved accuracy in describing state transition events for arbitrary load conditions, is proposed. This model exploits the potentiality of local-linear state-space parametric relations. These relations can be effectively estimated from input-output port responses only, and provide better stability properties and improved efficiency.

# I. INTRODUCTION

The modeling of the input and output buffers of digital Integrated Circuits (IC) is a key issue in signal integrity and electromagnetic compatibility simulations. Behavioral models are the best solution of this modeling problem [1], [2], as they offer the accuracy and efficiency needed to tackle the distortion effects and the complexity of real digital systems. Behavioral models based on nonlinear parametric relations and identification method, in particular, are now well developed and provide very good accuracy as well as the ability to include high-order and susceptibility effects [3].

The aim of this work is to explore an enhancement of parametric behavioral models for digital IC output buffers, that further improves their accuracy and robustness, while preserving their advantages. To this end, the development of behavioral models defined by a single-piece structure, *i.e.*, by a relation holding for both logic states, is addressed. The present behavioral models for output buffers are based on a two-piece structure, where two separate submodels contain the information on the behavior in the two logic states. The use of a single-piece structure can add information on the behavior during state transitions, improving the accuracy and robustness of the model in describing state switching events. Recently, a single-piece model for IC output buffers has been proposed (e.g., see [4]). This model is based on a sophisticate continuous-time neural network structure and has outstanding accuracy performance. In order to minimize the cost of estimating the model parameters and the model run time, in this work nonlinear parametric relations based on the state-space representation are exploited. These relations are a recent advancement in parametric modeling and offer improved efficiency for multiple input/output variables as well as better stability properties, *i.e.*, improved robustness. They are well suited to enable enhanced and compact behavioral models with a single-piece structure.

#### II. IC OUTPUT BUFFER MODELS

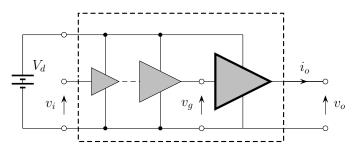

In this Section, the behavioral modeling of IC output buffers and its main issues are shortly reviewed. IC output buffers (simply drivers in the following) are circuits composed of a cascade of inverter stages interfacing IC internal logic with external interconnects. The typical driver structure is sketched in Fig. 1 along with the relevant electrical variables.

A behavioral driver model is a relation between the output variables  $v_o$  and  $i_o$ . In order to describe the operation in the two logic states and the switching between them, this relation must also change according to the value of a control variable. In standard behavioral models, the control variable is taken into account by means of a two-piece structure:

$$i_{o} = w_{H}(t)i_{H}(v_{o}, \frac{dv_{o}}{dt}) + w_{L}(t)i_{L}(v_{o}, \frac{dv_{o}}{dt})$$

(1)

where  $i_H$  and  $i_L$  are submodels accounting for the device behavior in the logic High and Low state, respectively. The time-varying functions  $w_H(t)$  and  $w_L(t)$  provide the transition between the two submodels  $i_H$  and  $i_L$ , *i.e.*, the switching between the two logic states. The physical meaning of the two-piece assumption and the easy estimation of the model parameters from the port waveforms are the main strengths of this model structure.

The main elements defining a driver model based on (1) are the structure of the equation itself (piecewise) and the relations used to generate the submodels  $i_H$  and  $i_L$ . Submodels  $i_H$  and  $i_L$  can be obtained from either simplified equivalent circuit representations (*e.g.*, see IBIS [1]) or from parametric relations and identification methods. Models based on parametric

Fig. 1. Typical IC output buffer (dashed box) and its main electrical variables. Voltage  $v_i$  is the control voltage applied by the IC logic core,  $v_o$  and  $i_o$  are the circuit output voltage and currents, respectively. The bold triangle symbol indicates the last inverter stage and  $v_g$  its input voltage.

relations, in particular, are today well established and proved to be very accurate, efficient and flexible [2]. Therefore, in order to further enhance IC driver models, different model structures and improved parametric relations are considered.

Two-piece models exploit information on the behavior of the driver in the two logic states only. The information on the behavior during logic state transitions is confined in the weighting functions of the model. On the other hand, single-piece models can be more accurate in describing state transitions, because they can include additional information on the device behavior in intermediate states [5]. Concerning the parametric relations, only input/output parametric relation have been exploited up to now. Recently, state-space relations have been proposed which can be more efficient and robust than the input/output relations. The objective of this work, therefore, is to verify the feasibility and the performance of a single-piece model exploiting state-space parametric relations.

#### **III. SINGLE-PIECE MODELS**

Different single-piece models can be devised to relate the port variables of the drivers. Here, we focus on a model defined by a static and a dynamic part:

$$i_o = i_{os}(v_o, v_g) + i_d(v_o, v_g)$$

(2)

where  $i_{os}$  is the DC output characteristic of the driver and  $i_d$  is a dynamic model accounting for the difference between the actual response and the static one. In order to include any DC contribution of  $i_o$  into  $i_{os}$ , the dynamic part is null for constant  $v_o$  and  $v_g$  waveforms. This kind of representation, in which the static and dynamic parts are splitted, has been already exploited in the two-piece models [2]. Its main advantage is a facilitated estimation of the parameters of the dynamic part, as the information on the static behavior is completely contained in the static part.

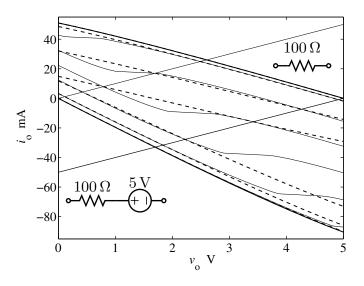

As an example, in Fig. 2 the DC output current of a driver (dashed lines) and the DC output characteristic of a twopiece (solid thin lines) model are compared. The weighting functions of the model (1) are computed by the two-waveform method [5]. As it was expected, the static characteristic of the two-piece model and the actual one are similar near the load lines (straight lines of Fig. 2) only. These lines correspond to the loads used in the computation of the weighting functions  $w_H$  and  $w_L$  of (1). In contrast, the static part  $i_{os}(v_o, v_g)$  of the single-piece model (2), reproduce the actual DC output curves, thus eliminating the error of the two-piece model on the DC contribution in the intermediate states.

In order to obtain a driver output model, a control variable defining the logic state of the model and driving the switching process must also be defined. For the sake of simplicity, here we assume that all the internal variables of the driver are accessible. The most natural control variable for model (2) is the driver last stage input voltage  $v_g$ . For  $v_g = V_d$  and  $v_g = 0$  the DC characteristic of the Low and High logic states are selected, whereas intermediate  $v_g$  values lead to intermediate states. In our model, the role of coefficients  $w_H$  and  $w_L$  of

the two-piece models is played by a suitable  $v_g(t)$  waveform. In actual operation,  $v_g(t)$  is decided by the circuits preceding the last stage and by the backward transmission properties of the last stage. However, the backward transmission of inverter stages is weak, and it has been verified that  $v_g(t)$  weakly depends on the driven loads. The backward transmission is, therefore, neglected and the input voltage  $v_g$  of the last stage that is observed when the driver is connected to a reference resistor (a  $100 \Omega$  resistor in the modeling example of Sec.V) is used as a control waveform. In conclusion, the proposed model is defined by (2) and by a function  $v_{gr}(t)$ , *i.e.*, the reference input voltage of the last stage, that controls the logic state and the state switching.

# IV. STATE-SPACE PARAMETRIC MODELS

Several modeling methods based on state-space parametric relation have been proposed recently. In this paper, a method based on Locally-Linear State-Space (LLSS) equations is exploited [6]. This method is based on the approximation of the complex dynamic behavior of a nonlinear dynamic system by means of the composition of locally linear state-space models. The operating domain of the system is partitioned into smaller domains where the system behavior is approximated by a linear state-space equation. Even if this idea has been already investigated in the literature, the implementation of [6] has several strengths. Mainly, the model parameters are obtained from the input/output port responses only via an optimization procedure and the different domains are authomatically computed during model estimation.

As an example, a LLSS representation for  $i_d(v_o, v_g)$  of (2) is defined by the following discrete-time state-space equation:

Fig. 2. Solid-line curves: DC output current of an example CMOS driver  $(v_g \text{ parameter})$ ; dashed lines: DC output current of a two-piece model of the driver; straight solid lines: load lines of the two loads (indicated) used to compute the weighting functions of the two-piece model. The driver and two-piece model curves intersect along the load lines only.

$$\begin{cases} \mathbf{x}(k+1) = \sum_{i=1}^{s} p_i(\phi(k)) \left( \mathbf{A}_i \mathbf{x}(k) + \mathbf{b}_i \mathbf{u}(k) + \mathbf{o}_i \right) \\ i_H(k) = \mathbf{c}^T \mathbf{x}(k) + \mathbf{d} \mathbf{u}(k) \end{cases}$$

(3)

where k is the discrete-time variable; vector  $\mathbf{x}$  collects the internal states, **u** the input variables  $v_o$  and  $v_q$ , and  $p_i(\cdot)$  is the weighting coefficient of the i-th local model. Each local model is defined by the state matrix  $A_i$  and by the vectors  $\mathbf{b}_i$  and  $\mathbf{o}_i$ . The argument of the weights, *i.e.*, the scheduling vector  $\phi(k)$ , corresponds to the operating point of the system and it is in general a function of both the input and the state variables. Among all the possible choices for  $p_i(\phi(k))$ , a common solution in local linear modeling, that is also used in [6], amounts to defining the weights as normalized radial basis functions depending on the input sequence  $\mathbf{u}(k)$  only. The radial functions vary between zero and one and their sum is forced to be one at each operating point of the system. It is worth to remark that, under some specific assumptions, the above parametrized state-space equation can arbitrarily approximate any nonlinear dynamic system [6].

Since the computation of the model parameters of (3), *i.e.*, the local model matrices and the parameters defining the weights, requires the solution of a nonlinear non-convex approximation problem, a modified version of the Levenberg-Marquardt (LM) iterative method is proposed in [6]. The basic version of the LM algorithm has been suitably modified to handle the non-uniqueness of a state-space representation that may cause ill-conditioning of the matrices during the model estimation. In addition, the parameter initialization is carried out by means of a deterministic procedure, thus avoiding the dependence of the estimated model on the initial guess of the parameters. Besides, the initial guess of the matrices defining the local models are set equal to the matrices of a single global stable linear model. The parameters of the global linear model are computed by means of the application of an efficient subspace identification method [7]. The latter subspace method also provides the automatic computation of the number of internal state variables, *i.e.*, the size of vector x of (3). The initial radial weighting functions  $p_i$  are distributed uniformly over the range of the input sequence.

In the proposed implementation of the algorithm, during the training no additional constraints are included to enforce model stability. The model stability is verified a posteriori and the device models obtained so far by using the proposed approach have been verified to be stable.

LLSS models designed as outlined in this Section have additional strengths. Mainly, the state-space nature of this class of representations facilitates the modeling of devices with multiple inputs. Besides, they have been proven to be effective for the characterization of the strongly nonlinear behavior of real devices, possibly with high-order dynamical effects. Finally, LLSS models that have a relatively small size (a few local models are usually sufficient for the modeling problem at hand), leading to efficient model implementations.

## V. NUMERICAL EXAMPLE

In this Section, the single-piece model and the LLSS ideas introduced in the two previous sections are tested on a modeling example. The example involves the four-inverter-stage CMOS driver defined in [8], pag. 492, for which a Device Level (DL) model is available. The responses of this DL model are used as reference for both the estimation of the model parameters and the assessment of the accuracy of the obtained models. This DL model is for a slightly dated CMOS technology, nevertheless it is still representative of current drivers and it is public. Besides, the state transition of this driver are difficult to describe by means of traditional two-piece models.

For the example driver, a traditional two-piece model with parametric input/output submodels and a single-piece model with an LLSS dynamic part are generated. The traditional model has been generated as described in [2] and turns out to have a dynamic order equal two and both the parametric submodels  $i_H$  and  $i_L$  defined by six basis functions. On the contrary, the parameters of the single-piece model are estimated from the response of the driver when its last stage is driven by the  $v_{gr}(t)$  waveform defined in Sec. III and it feeds a transmission line load (LC line,  $Z_o = 50 \Omega$ , 3ns time delay and 10pF capacitor load). The transmission line reflections excite the output port dynamic behavior. This allows to estimate  $i_d$ parameters via a standard algorithm by using  $v_{gr}$ ,  $v_{oe}$  and the difference current:

$$i_{de}(t) = i_{oe}(t) - i_{os}(v_{oe}(t), v_{qr}(t))$$

(4)

where  $v_{oe}(t)$  and  $i_{oe}(t)$  are the output driver waveforms recorded in the switching experiment with the transmission line load. The mapping  $i_{os}$  is approximated by a sum of 20 sigmoidal functions and the obtained LLSS dynamic model is composed of two linear state-space submodels with 7 internal state variables.

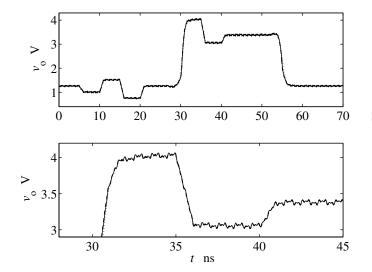

The properties and performance of the single-piece model obtained have been verified. A cumulative test is carried out by driving a 50  $\Omega$  SSTL termination series connected to a supplemental disturbing voltage source. The modeled device applies a High logic pulse lasting 25ns and the disturbing source applies a signal with large level variations and a small amplitude white noise component. The voltage responses obtained by using the modeled driver and its single- and two-piece models are shown in Fig. 3 and 4.

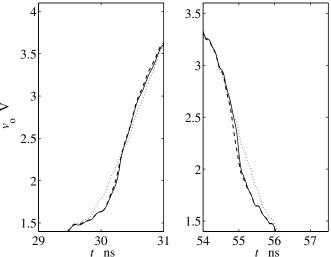

The waveform of the bottom panel of Fig. 3 demonstrates the ability of the single-piece model to perform as well as the two-piece model in describing driver operation in fixed logic state. The edge part of the responses, shown in Fig. 4, demonstrate the key feature expected from a single-piece model, *i.e.*, its ability to describe state transitions for arbitrary loads. The edges predicted by the single-piece model, in fact, are in good agreement with the driver response, whereas the edges predicted by the two-piece model are less accurate. This confirms that the proposed model improves the accuracy of two-piece models.

Fig. 3. Voltage responses of a test circuit composed of a driver and a noisy SSTL load (see Sec.IV). Solid line: reference; dashed line: single-piece LLSS model; dotted line: two-piece model. Top panel: complete waveform; bottom panel: close-up for the operation in High logic state.

For an additional performance evaluation, the stability of the single-piece LLSS models is assessed by means of an analysis of the eigenvalues of the linearized model as suggested in [9]. This analysis confirms that the obtained models are locally stable, thus avoiding possible spurious dynamics for any excitation or load condition.

Finally, the implementation and efficiency issues are addressed. Two-piece models require the implementation of two dynamic submodels, two v-i curves and two switching functions of time. In contrast, the proposed single-piece model requires the implementation of a dynamic part, one v-i 2D mapping and one switching function of time. The dynamic LLSS part has a complexity comparable to the one of the submodels composing two-piece models. Besides, it can be even simpler than the submodels of two-pieces models, if multiple input and output variables are involved. The v-i mapping can be critical from the efficiency point of view, however effective implementations can be obtained via sigmoidal expansions as in this study. In conclusion, the numerical efficiencies of single-piece and two-piece models are comparable. Indeed the run times of the models developed for this example are similar.

### VI. CONCLUSIONS

The feasibility of a single-piece model is addressed by developing a model composed of the output DC characteristic of the last driver stage and of a LLSS dynamic relation. The logic state of this model is controlled by a variable that mimics the input voltage of the last driver stage.

Fig. 4. Edges of the waveforms of Fig.3 that correspond to state transition of the modeled device. Solid line: reference; dashed line: single-piece LLSS model; dotted line: two-piece model.

The obtained model benefits of the advantages of state-space based relations and turns out to be more accurate in describing state transition events. On the other hand, the single-piece model studied in this work has low estimation cost and is almost as simple as current two-piece models. It has the potential to be used in large scale simulation for electromagnetic compatibility and signal integrity.

#### REFERENCES

- [1] I/O Buffer Information Specification (IBIS) Ver. 4.1, on the web at http://www.eigroup.org/ibis/ibis.htm, Jan. 2004.

- [2] I. S. Stievano, I. A. Maio, F. G. Canavero, "Mπlog, Macromodeling via Parametric Identification of Logic Gates," *IEEE Trans. on Advanced Packaging*, Vol. 27, No. 1, pp. 15-23, Feb. 2004.

- [3] I. S. Stievano, E. Vialardi, F. G. Canavero, "Behavioral Macromodels of Digital Integrated Circuits for RF Immunity Prediction," *18th Intenational Zurich Symposium on Electromagnetic Compatibility*, Munich, Germany, Sept. 24-28, 2007.

- [4] Y. Cao, R. Ding, Q. Zhang, "State-space Dynamic Neural Network Technique for High-Speed IC Applications: Modeling and Stability Analysis," *IEEE Trans. on Microwave Theory and Technique*, Vol. 54, No. 6, June 2006.

- [5] I.A. Maio, I. S. Stievano, P. Savi, F. G. Canavero, "Single and Multi-Piece Behavioral Models of IC Output Buffers," *Proc of 2006 Electronics System integration Technology Conference, ESTC*, Dresden, Germany, pp. 209-214, Sept. 5-7, 2006.

- [6] V. Verdult, L. Ljung, M. Verhaegen, "Identification of composite local linear state-space models using a projected gradient serch," *Int. Journal* of Control, Vol. 65, No. 16/17, pp. 1385–1398, 2002.

- [7] M. Verhaegen, "Identification of the deterministic part MIMO state space models given in innovations form from input-output data," *Automatica* Vol. 30, pp. 71–74, 1994.

- [8] J. M. Rabaey, "Digital Integrated Circuits: a Design Perspective," Prentice Hall Electronics and VLSI series, 2003.

- [9] C. Alippi, V. Piuri, "Neural Modeling of Dynamic Systems with Nonmeasurable State Variables", *IEEE Trans. on Instrumentation and Measurement*, Vol. 48, No. 6, pp. 1073–1080, Dec. 1999.