# Software and Hardware Implementation of the RSA Public Key Cipher

Volume 1(1)

Paul Brady B.Sc(Eng), Hons. Dip. E.E.

Submitted to the National Institute for Higher Education, Dublin for the degree of Master of Engineering

This research was carried out under the supervision of Dr. T. Curran in the School of Electronic Engineering at the National Institute for Higher Education, Dublin and at the National Microelectronics Research Centre, Cork.

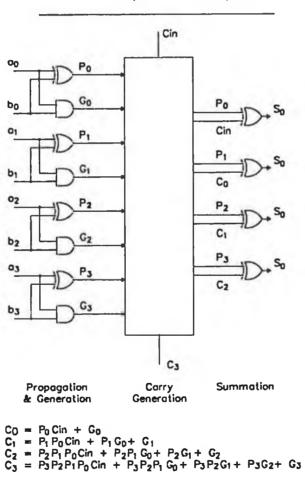

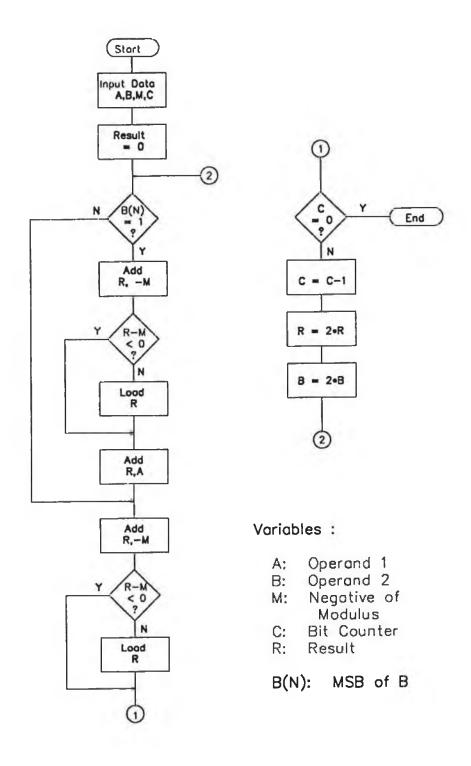

This thesis is based on the candidates own work

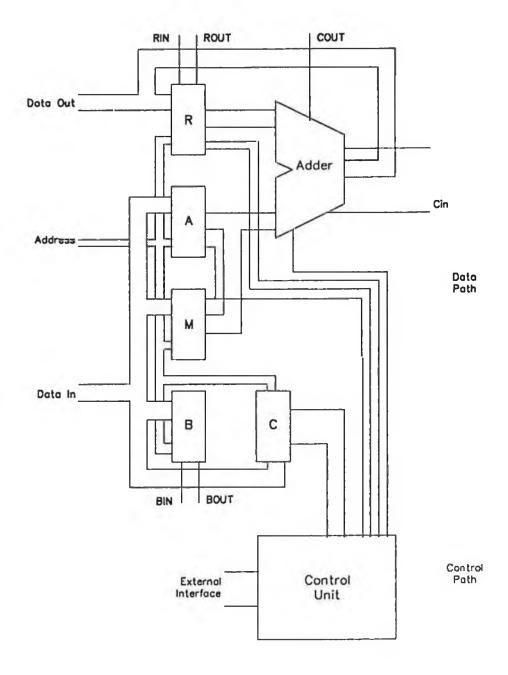

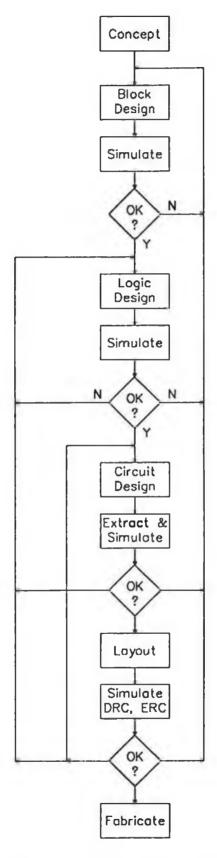

September 1988

## **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to

Dr. Tommy Curran for his expert advice, guidance and for his infinite patience.

Dr. Sverre Lidholm for his invaluable assistance.

Ericssons and the N.B.S.T for financial support of this project

The staff and postgraduate students at the N.M.R.C and N.I.H.E Dublin.

I would also like to thank all the people who helped me in this endeavour either directly or indirectly.

## Contents

| 0. ABSTRACT                                     | i  |

|-------------------------------------------------|----|

| 1. INTRODUCTION                                 | 1  |

| 1.1 General                                     | 1  |

| 1.2 Cryptography                                | 2  |

| 1.3 Security of Cryptographic Systems           | 3  |

| 1.4 Cryptographic Systems                       | 5  |

| 1.4.1 Public Key Systems                        | 5  |

| 1.4.2 Conventional Systems                      | 6  |

| 1.4.2.2 Transposition Ciphers                   | 7  |

| 1.4.2.3 Product Cipher                          | 8  |

| 1.4.2.3.1 The Data Encryption Standard          |    |

| (DES)                                           | 8  |

| 1.5 Key Management                              | 9  |

| 1.6 Implementing Ciphers                        | 10 |

| 1.7 Objectives                                  | 11 |

| 2. PUBLIC KEY SYSTEMS                           | 15 |

| 2.1 Introduction                                | 15 |

| 2.2 Public Key Ciphers                          | 17 |

| 2.2.1 The Knapsack Problem                      | 18 |

| 2.2.2 The RSA Cipher                            | 22 |

| 2.3 Comparison of Public Key Ciphers            | 26 |

| 2.4 Microprocessor Implementation of RSA Cipher | 27 |

| 2.4.1 Modular Exponentiation                    | 28 |

| 2.4.1.1 Results                                 | 30 |

| 3. MODULAR MULTIPLICATION METHODS               | 34 |

| 3.1 Introduction                                | 34 |

| 3.2 Multiplication                              | 35 |

| 3.3 Reduction Modulo N                          | 36 |

| 3.3.1 Division by repeated shift and subtract   | 37 |

| 3.3.2 Division using KNUTHs algorithm           | 40 |

| 3.3.3 Division using reciprocals.               | 43 |

| 3.4 Blakelys Algorithm.                         | 45 |

| 3.5 Encryption Time.                            | 46 |

| 3.6 Observations                                | 48 |

| 3.7 Possible solutions.                         | 49 |

| 4. KEY GENERATION                              | 62 |

|------------------------------------------------|----|

| 4.1 Introduction                               | 62 |

| 4.2 Security of the RSA cipher                 | 62 |

| 4.3 Choice of Key size                         | 63 |

| 4.4 Choice of Primes.                          | 64 |

| 4.5 Generation of random numbers.              | 65 |

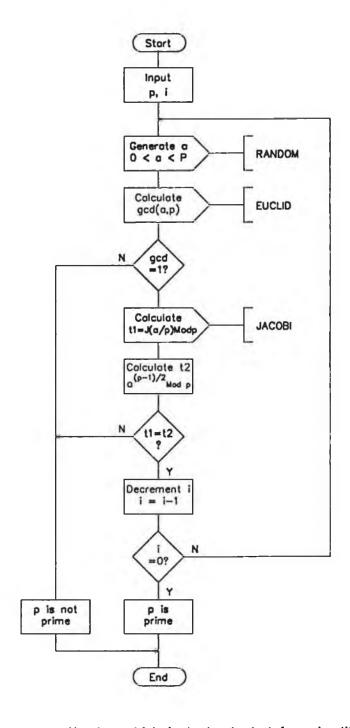

| 4.6 Primality Testing                          | 66 |

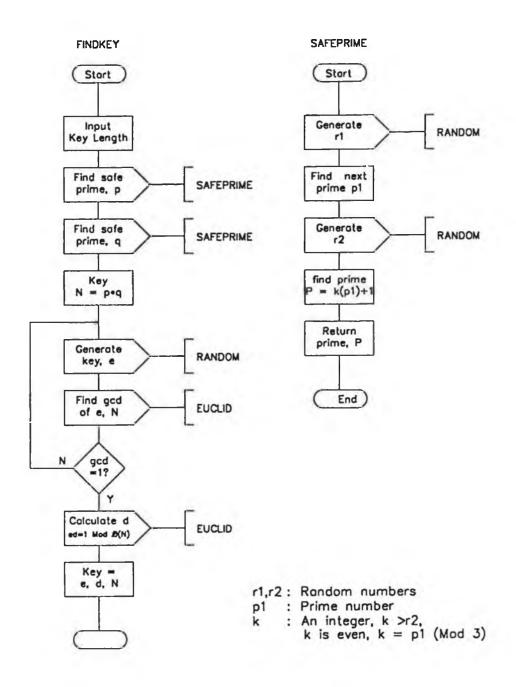

| 4.7 Generating keys.                           | 68 |

| 4.9 Effect of Key Generation on encryption.    | 68 |

| 4.10 Microprocessor Implementation.            | 69 |

| 5. HARDWARE MULTIPLICATION                     | 73 |

| 5.1 Introduction                               | 73 |

| 5.2 Hardware Multipliers                       | 74 |

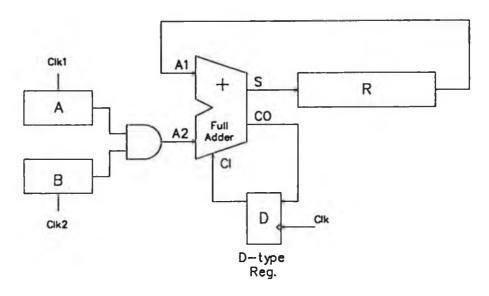

| 5.2.1 Serial Multipliers                       | 74 |

| 5.3.2 Serial/Parallel Multiplier               | 75 |

| 5.3.2.1 Horners Method                         | 76 |

| 5.3.2.2 Right to Left Factorisation            | 76 |

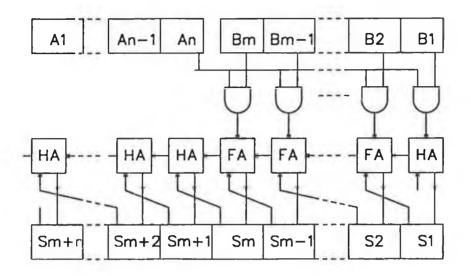

| 5.3.3 Parallel Multiplier                      | 77 |

| 5.3 Speed and space comparison of multipliers. | 78 |

| 5.4 Choice of multiplier.                      | 79 |

| 5.5 Modular Multipliers.                       | 81 |

| 5.6 Implementation.                            | 83 |

| 5.6.1 Discrete Hardware                        | 83 |

| 5.6.2 Bit Slice Devices                        | 84 |

| 5.6.3 Application Specific Integrated Circuits |    |

| (ASICS)                                        | 84 |

| 5.6.3.1 Gate Array                             | 85 |

| 5.6.3.2 Standard Cell                          | 85 |

| 5.6.3.3 Full Custom                            | 86 |

| 5.7 Choice of implementation method.           | 86 |

| 6. SEMI-CUSTOM IMPLEMENTATION                  | 93 |

| 6.1 Design Criteria                            | 93 |

| 6.2 Design Process                             | 93 |

| 6.2.1 Concept                                  | 93 |

| 6.2.2 Block Design                             | 94 |

| 6.2.3 Logic Design                             | 94 |

| 6.2.4 Circuit Design                           | 95 |

| 6.2.5 Lavout                                   | 96 |

| 6.2.6 Fabrication                    | 97  |

|--------------------------------------|-----|

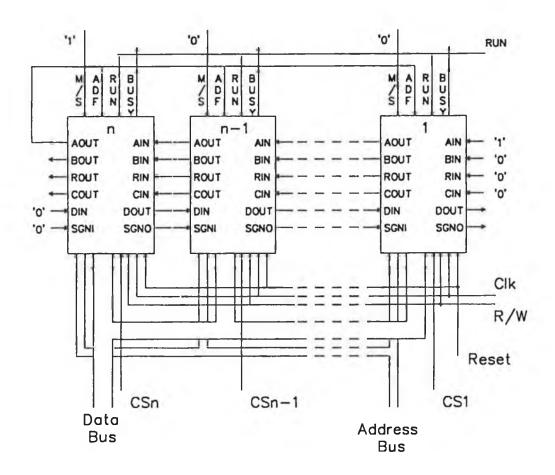

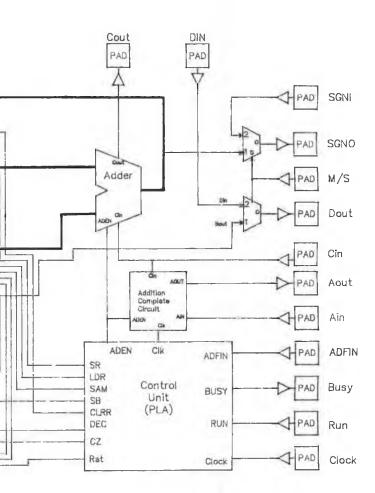

| 6.3 System Overview                  | 98  |

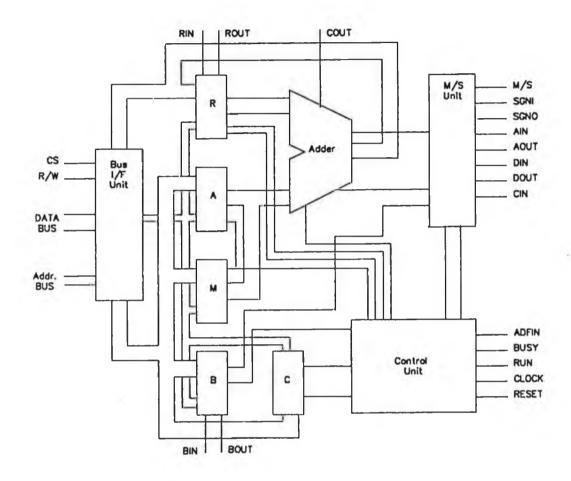

| 6.3 System design                    | 99  |

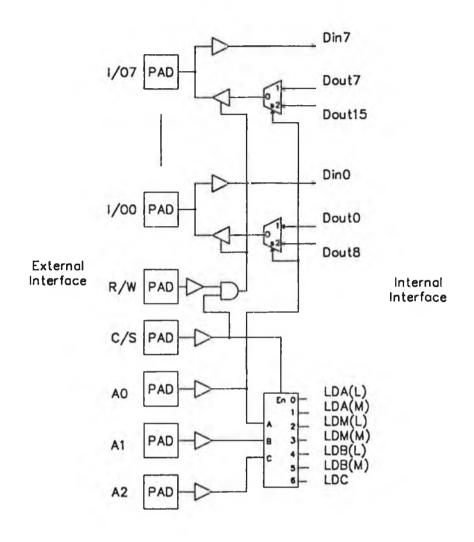

| 6.3.1 Interface Unit                 | 100 |

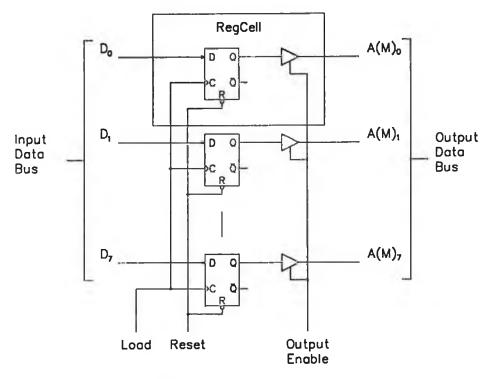

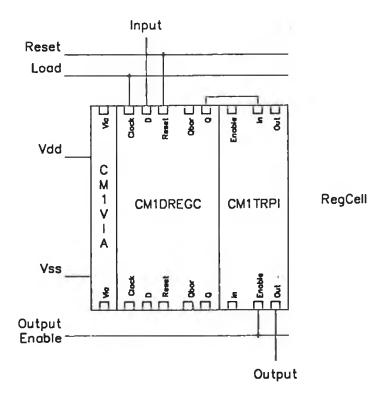

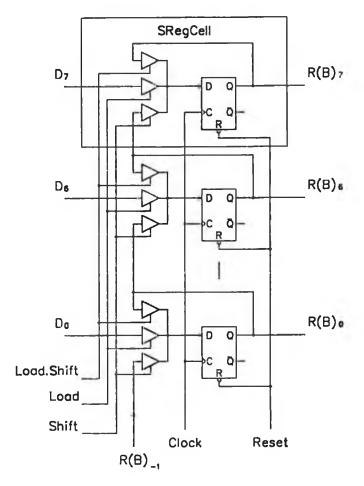

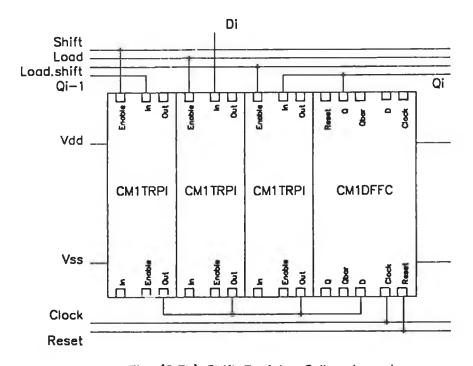

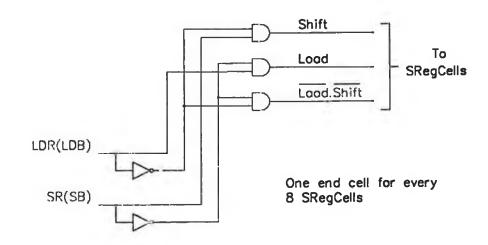

| 6.3.2 Storage Unit                   | 101 |

| 6.3.3 Computation Unit.              | 103 |

| 6.3.4 Cascade and Master/Slave Unit. | 104 |

| 6.3.5 Control Unit                   | 106 |

| 6.4 Device Performance               | 108 |

| 6.5 Encryption using the MMD         | 109 |

| 6.6 Further Enhancements             | 110 |

| 7. CONCLUSION                        | 127 |

| REFERENCES                           | 131 |

## **Abstract**

Title: Software and Hardware Implementation of the RSA

Public Key Cipher.

Author: Paul Brady

Cryptographic systems and their use in communications are presented. The advantages obtained by the use of a public key cipher and the importance of this in a commercial environment are stressed. Two two main public key ciphers are considered.

The RSA public key cipher is introduced and various methods for implementing this cipher on a standard, non-dedicated, 8 bit microprocessor are investigated. The performance of the different algorithms are evaluated and compared. Various ways of increasing the performance are considered. The limitations imposed by the performance on the practical use of the cipher are discussed.

The importance of the key to the security of the cipher is assessed. Different forms of attack are mentioned and a procedure for generating keys, which minimise the probability of a sucessful attack is presented. This procedure is implemented on a minicomputer. Use of the method on personal computers or microprocessors is examined.

Methods for performing multiplication in hardware, with particular emphasis on the use of these methods in modular multiplication, are detailed. An algorithm for performing part of the encryption function in hardware and the hardware necessary for it is described. Different methods for implementing the hardware are discussed and one is choosen. A description of the hardware unit is given.

The design and development of an application specific integrated circuit (ASIC) to perform key elements of the encryption function is described. The various stages of the design process are detailed. The results expected from this device and its integration into the overall encryption scheme are presented.

## 1.INTRODUCTION

#### 1.1 GENERAL

The use of cryptography to protect confidential information has a long history. The Romans are certainly known to have used simple ciphers and one exists today which is attributed to Julius Caesar. Leonardo DaVinci is said to have used mirror writing to protect his ideas. Further details of the users of encryption throughout history and the methods that they used can be found in KAHN(1).

Until recently the main users of cryptography were the military. Commercial institutions did not, in general, consider it necessary to resort to encryption to protect information. Any use of cryptography by commercial institutions did not usually consider the security of the code or cipher being used. The main objective was to deter the casual eavesdropper, and not to secure against a determined attack by experience cryptanalysts.

This attitude of commercial organisations towards cryptography has undergone a sudden and dramatic change in recent years. There are two major factors which have influenced this change. The first is the advent of worldwide telecommunications network, and the second is the increased use of electronic media to transfer and store information. Electronic information transmitted over the public telecommunications network must travel by cable, radio or microwave links, all of which are vulnerable to eavesdropping. Access to computers can now be obtained by **v**irtually anyone with a terminal and modem, introducing the risk that confidential data may be exposed even when it is not in transit. The increasing use of electronic funds transfer has highlighted the problem not only of security but of authentication. Security in this case is insufficient, it is not enough to know that the data has not been altered between sender and receiver, it is necessary to verify that the data originated where it claims. Equally important is that the sender of the data cannot later disown it.

Traditional means of protecting data usually involve physical protection of the data itself, for example in a safe or with a trusted courier. The increased use of electronic storage renders this approach less effective. Information stored on magnetic disk or tapes can be physically protected by restricting access to the devices, however, when these devices are on line, or when information is in transit to or from such devices, it is vulnerable. Ways of protecting data both in storage and in transit are many but the method that is most widespread is the use of cryptography.

#### 1.2 CRYPTOGRAPHY

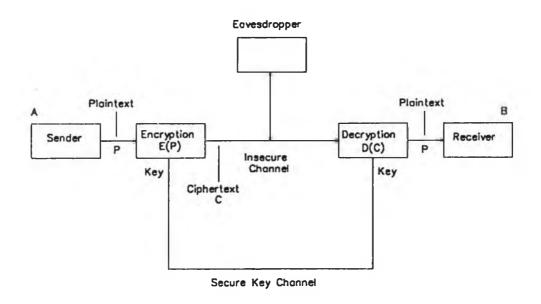

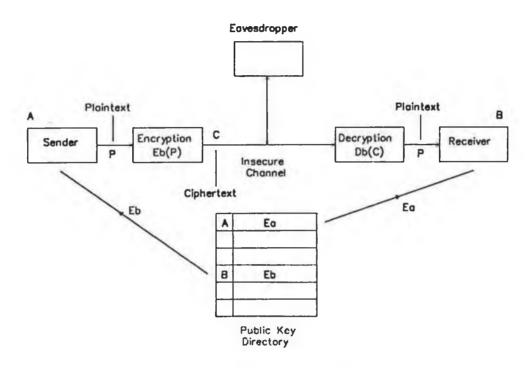

The problem that cryptography seeks to address is that of a sender A who wishes to send a plaintext message P to a recipient B over an insecure channel. To do this A first encrypts the plaintext, using a transformation E, to produce ciphertext C. This ciphertext is now transmitted over the insecure channel. The intended recipient B then decrypts the ciphertext, using a transformation D, to produce the plaintext P again. This process of encryption and decryption is shown in Fig.(1.1) and can be described by the equations:

C = E(P)

P = D(C)

The transformations E and D must therefore have the property that D(E(P)) = P to allow B to decipher the message. In most cipher systems the general transformations are known but the specific transformations, which are determined by the encryption and decryption keys are not.

The function of the eavesdropper, shown in Fig.(1.1) is to recover the plaintext without knowing the decryption key D. Eavesdroppers can be classified into two categories passive and active. A passive eavesdropper can listen to and record, but he cannot alter, the data passing through the insecure channel. An active eavesdropper can dynamically alter data passing through the channel. He can

therefore prevent data from reaching the intended recipient or he can record messages and send them to B at some later time. The active form of eavesdropping is particularly dangerous in electronic funds transfer where messages crediting an account could be recorded and replayed many times while messages debiting an account could be prevented from reaching their destination. this illustrates the need for verification, not only of the sender, but of the message itself. Message authentication can be achieved by inserting some non-repeating information, such as the date or a message number, into the message prior to encryption.

To recover the plaintext without knowing the decryption key D the eavesdropper, or cryptanalyst, must use the information available to him. The worst situation for the cryptanalyst is if he has a large amount of ciphertext, a general knowledge of the encryption method used and some information regarding the message. knowledge may only extend as far as knowing the language in which the message was written or the probability of occurrence of certain words and phrases. This form of attack is the weakest and is known as a ciphertext only attack. If the cryptanalyst knows some plaintext and the corresponding ciphertext, e.g press releases which are intercepted in encrypted form which are released later, he has more information with which to work. This form of attack is described as a known plaintext attack. The most favourable situation for the cryptanalyst is when he can submit messages for encryption and obtain the corresponding ciphertext. This is called a chosen plaintext attack. To be considered secure an encryption system must withstand each of these attacks.

#### 1.3 SECURITY OF CRYPTOGRAPHIC SYSTEMS

The security of a cipher can best be described in terms of the resources required by the cryptanalyst to determine the decryption key. Cryptographic systems can be either absolutely (or unconditionally) secure or they can be computationally secure. Absolute security implies that, regardless of the resources available to the cryptanalyst,

he has insufficient information to obtain the decryption key and hence the plaintext. With computationally secure systems, however, it is possible to obtain the decryption key provided that sufficient resources are available. The designer of a computationally secure system must ensure that encryption and decryption are fast and inexpensive but that cryptanalysis would require more computational resources than would be possible to obtain. Computers are becoming more powerful and less expensive all the time, so it is necessary to include a very large margin in the system to allow for future developments. Even with this large margin computationally secure systems eventually become insecure, thus information which must remain secure for a long period of time e.g government archives should not be encrypted using such a system. All practical cryptographic systems are computationally secure.

With few exceptions it is not possible to prove that a cryptographic system is secure. A system is considered if it has withstood concerted secure a attack experienced cryptanalysts for an extended period of time. This attack would be undertaken under the most favourable conditions possible. This process of testing the security of a system is known as certification. The only cipher that can be proven to be absolutely secure is the one time pad. In this cipher the plaintext is encrypted using a random key which is the same length as the plaintext. This system is absolutely secure as the key is random and never repeats thus concealing totally the statistical properties of the plaintext. This cipher is not in widespread use as the management of keys makes it impractical. To exchange a plaintext message the sender and receiver must first agree on a key which is the same length as the plaintext. As this key exchange requires a secure channel this channel could be used to transfer the plaintext instead. The use of such a system is therefore limited to high security diplomatic links where total security is vital and cost is not a factor.

#### 1.4 CRYPTOGRAPHIC SYSTEMS

Cryptographic systems fall into two main categories, conventional or single key systems, and public or two key systems. In a conventional system the encipherment and the decipherment key are the same, or one can be easily obtained from the other. Two people who wish to exchange information thus share a common key. Each pair of users therefore requires a different key and the number of keys required for large numbers of user-pairs quickly becomes unmanageable, i.e for N user pairs the number of keys is  $(N^2-N)/2$ . Before contact is made between two users it is necessary that they both receive a key and this can be time consuming for once off or infrequent communication.

## 1.4.1 Public Key Systems

In public key systems the encipherment key E and the decipherment key D are different and D cannot easily be obtained from E. It is therefore possible to make E public while ensuring that D remains secret. The public keys of many users could be published regularly as in a telephone directory. Any person who wishes to send secure information to a user A need only look up A's public key in the directory and use it to encrypt the message. The only person who can now read the message is A as only he knows the secret decryption key. Contact between user- pairs can now be established without the need for a secure key exchange and, if there are N users the number of key pairs required is also N. The reduced key management problem of public key ciphers make them attractive for use in a commercial environment where the number of contacts is large and constantly changing.

The idea of public key ciphers was introduced by DIFFIE and HELLMAN(2) in 1976. They did not however give a practical example of such a system. This paper was soon followed by two papers, one by MERKLE and HELLMAN(3) and another by RIVEST, SHAMIR and ADLEMAN(4), both of which described practical public key cryptosystems. These two systems were based on a mathematical concept known as a

trapdoor function. A trapdoor function is a transformation that is essentially one way unless some secret information, is known. Consider the use of the trapdoor, transformation in a cryptographic system. The trapdoor function is the encryption key which converts the plaintext ciphertext. Now to anyone, without the transformation is information, this irreversible. secret information is thus the decryption key. The method proposed by Merkle and Hellman is based on the knapsack problem while that proposed by Rivest, Shamir and Addleman, and hence known as the RSA method, is based on the difficulty of factoring large numbers. These two methods are the basis of public key cryptography.

## 1.4.2 Conventional Systems

Unlike public key cryptography, which is of recent origin conventional encryption systems have a much longer history. This has led to the development of a large number of cipher systems being developed. However, along with this development there has been a parallel increase in methods of cryptanalysis of such ciphers. The two main groups into which most ciphers fall are, substitution and transposition ciphers.

#### 1.4.2.1 Substitution Ciphers

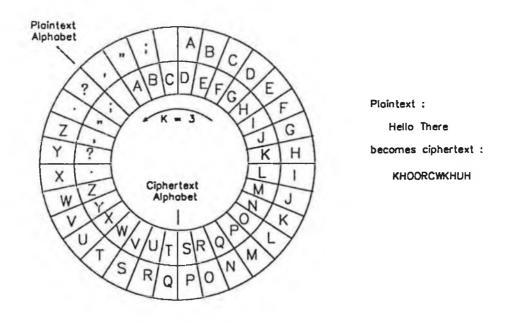

In a substitution cipher each character in the plaintext is replaced by a character from an alternative alphabet. The simplest substitution cipher is the Caesar cipher, named after its reputed inventor Julius Caesar. In this cipher, shown in Fig.(1.2), the alternative alphabet is simply the regular alphabet shifted by three places e.g A becomes D etc. The security of such a system is very low as once the method of encryption is known it is a simple matter to cryptanalyse the ciphertext. Variations of this in which the alternative alphabet differs are similarly prone to cryptanalysis. One method of solution is to simply try all possible keys, of which there are only twenty six, the second method is to attempt a statistical attack. A

statistical attack relies on the fact that certain letters in English appear more often than others e.g E,A. With sufficient ciphertext it is possible to create a table of probabilities and match them with standard English. The use of a large alphabet in a substitution cipher increases its security as the number of possible keys increases. A substitution cipher can also be easily broken by a known plaintext attack.

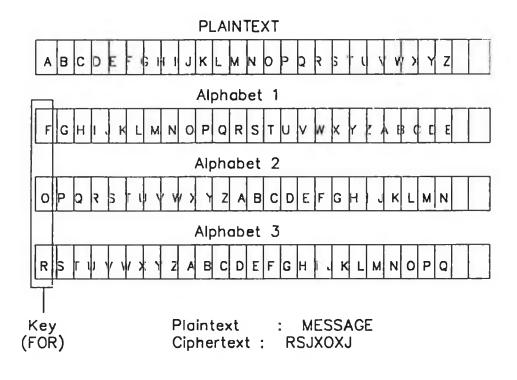

To increase the security of a substitution cipher more than one alternative alphabet can be used, under the control of a key. This is known as a polyalphabetic cipher, Fig. (1.4) and is much more difficult to solve, as the probability distribution of letters is now much flatter and resemble standard English. Given sufficient ciphertext, however, it is possible to solve such a cipher using a method developed by KASISKI(5). This method is based on determining the length of key by looking for repetitions in the ciphertext. The longer therefore, the more difficult it is to solve. To increase the apparent keylength multiple encryption can be used e.g if the plaintext is encrypted twice, using keys whose lengths are relatively prime to each other the apparent key length is the product of the individual keylengths. As the key length increases the amount of ciphertext required and the time needed to solve the cipher increase, thus affording an increasing level of security.

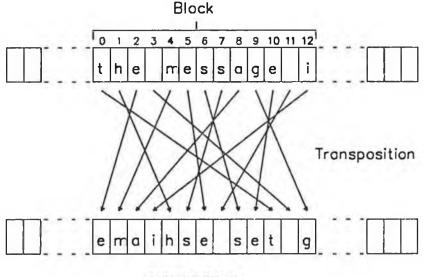

## 1.4.2.2 Transposition Ciphers

In a transposition cipher the plaintext is split into fixed length blocks and the letters are rearranged under the control of a key, as shown in Fig. (1.3). The size of the block must be large to prevent the cryptanalyst from trying all possible keys to obtain meaningful plaintext. A transposition cipher can also be defeated by a statistical attack. In this method the frequency of occurrence of common letter pairs e.g TH, QU, IN is used to obtain will transformations which reunite such pairs. transposition cipher is completely vulnerable to a known plaintext attack.

## 1.4.2.3 Product Cipher

Transposition and substitution ciphers do not possess adequate security for practical use. They can however be used together to produce a much stronger cipher known as a product cipher. A product cipher is of the form ST where S is a simple substitution cipher on a large alphabet and T is the transposition of bits within a fixed length block. Repeated encipherment using a different substitution key each time produces a strong cipher. One such cipher is the DES, or Data Encryption Standard (6).

## 1.4.2.3.1 The Data Encryption Standard (DES)

The National Bureau of Standards in the U.S.A issued a requirement for an encryption scheme which could be used as an encryption standard by the Federal authorities. result was a product cipher developed by IBM and it is this which is now the Data Encryption Standard. This cipher uses a combination of transposition and substitution to achieve a very high level of security. This cipher, uses a 56 bit key to perform 16 rounds of encryption on a 64 bit block. Each round of encryption is a combination of substitution and transposition. The DES cipher is considered computationally secure as the only known way of solving it is to search all possible keys. With  $2^{56}$  , or approximately possible keys such a search is computationally infeasible at present. However with the speed and power of computers increasing all the time the life of the DES will be short lived, by 1990 it is believed that the DES will be insecure.

The selection of a standard by the U.S government and the subsequent availability of inexpensive and secure encryption methods has helped the use of encryption to become more widespread. The DES algorithm is available in the form of a single integrated circuit which can be easily added to new or existing products (18)The setting up of a standard also ensures widespread acceptance of the method

by commercial organisations and thus enables a large number of users to communicate with each other.

#### 1.5 KEY MANAGEMENT

The DES is a secure and easily implementable cipher but it is prone to the same problem of key management that is common to all conventional cryptosystems. The problem of key management is two fold. The first is caused by the need for each user to store secretly all the keys it uses. This is a major problem for large commercial organisations with many contacts as the number of keys that must be securely stored is large. The second problem is one of contact initiation. A user A wishing to communicate securely with a user B has first to establish a secret key. This requires a secure channel, e.g a courier. The setting up of this key introduces a large time delay before the two users can communicate. Also if the requirement was only for a single secure transaction this could be accomplished using the secure key channel and the cipher need not be used.

Public key ciphers, which will be discussed in more detail chapter 2 do not suffer from distribution problem. The public key of all users can be published or held in a public database. This removes the need for each user to maintain a large collection of secret keys, the only key that must be stored is the users secret decryption key. A user who now wishes to establish a secure communication channel with another user need only look up that users public key. This abolishes the need for an expensive and time consuming secure key channel.

Despite this lack of a key distribution problem public key ciphers have not yet gained widespread acceptance. There are several reasons for this. Public key ciphers, in general involve a more complex process than conventional ciphers and they are therefore slower. This reduces the transmission rate that can be obtained over a channel and rules them out for applications in which high speed communication is essential. Due to the complexity of the public key encryption process no single chip solution is commercially available at present. This makes the inclusion

of a such a cipher into a new or existing product much more difficult than with DES.

Another problem with public key ciphers is that due to their relative youth there are still doubts regarding their security. Conventional ciphers such as DES have undergone extensive attacks by cryptanalysts for an extended period of time. This is the only sure way of testing the security of a system. Public key ciphers being relatively new have such a period of extensive undergone Conventional ciphers, such as DES are based on understood principles so the prospect of finding a hidden flaw in such a system is quite small. One public key cipher, the RSA method, has received extensive attention since it was proposed in 1978 and has resisted attempts to render it insecure. This system is now being proposed as a federal standard (7). If it is accepted semiconductor manufacturers may produce single chip implementations of the cipher. This would enable it to be introduced into products as easily as DES. The problem of key management would thus be greatly reduced.

## 1.6 IMPLEMENTING CIPHERS

Methods of implementing ciphers vary according to the application. Where speed is not a problem encryption and decryption algorithms can be written in a high level programming language. This could be used, for example, before and after long term storage of computer files. This would remove the need for secure storage of For higher speed applications backups etc. microprocessor, programmed in a low level language, can be used. For higher speeds hardware assisted microprocessors hardware can be used. Cipher dedicated implemented in software can be rendered insecure if the programme itself is violated. The ideal encryption device is therefore a single chip VLSI device on which the secret key is stored, perhaps on EPROM, so that is is never available outside the chip.

#### 1.7 OBJECTIVES

The objectives of this thesis are two fold. The first is an investigation into methods of implementing the RSA public key cipher on a standard microprocessor. The results of this investigation will determine whether such a system is practically viable. The second part is an investigation into the possible uses of hardware to improve the speed and security of the cipher.

Various methods of hardware encryption are considered and a solution is chosen. The means of implementing this system are described and ways of testing it are discussed.

Chapter 2 will discuss public key ciphers. Methods for producing public key ciphers are described with particular attention being paid to the RSA method. Different encryption schemes are compared and the advantages and of each method is discussed. disadvantages determining the security of each and the possible means of attacking the systems are examined. The importance of the key to the security is described and the different levels of security obtainable with different key lengths tabulated for the RSA method. Implementation of the RSA method, in general, and of modular exponentiation, particular is considered.

Chapter 3 investigates ways of performing modular multiplication, which is a vital part of the RSA scheme, using a standard eight bit microprocessor. Several schemes are described and flowcharts for each are given. A detailed timing analysis of each method is performed and graphs of the relative performance of each are produced. From this timing analysis the time to encrypt blocks of data of different lengths is calculated and graphed. The practical uses of such a system are discussed and ways of improving the performance of the system are considered.

Chapter 4 considers the problem of key generation in detail. The importance of the proper choice of key, and the implications of key choice for security are discussed. A practical key generation scheme, for use on a personal computer or a mainframe, is detailed with the aid of flowcharts. The expected execution time of the programme,

and the effect of this on the overall encryption scheme are Ways considered. of implementing the key algorithm in a low level language, for use on microprocessor are discussed.

Chapter 5 details methods for performing multiplication in hardware with particular emphasis on the use of these in modular multiplication. These methods compared and the advantages and disadvantages of each noted. The tradeoffs inherent in each choice are considered. A method is chosen for implementation and the reasons for the choice are given. Various ways implementing this choice are discussed and one is chosen.

Chapter 6 describes the design and development of the hardware unit. The various stages of the design process are described and the results expected are mentioned. A description of the hardware unit is given and the test performed to estimate its performance are given. Testing of the completed unit is examined. The effect of the hardware unit on the encryption process, in terms of the time taken to encrypt various block sizes is discussed.

Chapter 7 is a summary of the result achieved by this research. The implications of these results are considered and possible commercial applications are suggested. Further improvements and refinements are considered and the effect of continuing advances is speculated upon.

Fig. 1.1 Cryptography in communication

Fig. 1.2 Caesar cipher

## **PLAINTEXT**

CIPHERTEXT

Key = (2 4 8 12 1 7 5 11 6 10 0 3 9)

Fig. (1.3) Transposition Cipher

Fig. (1.4) Polyalphabetic Substitution Cipher

## 2. PUBLIC KEY SYSTEMS

#### 2.1 INTRODUCTION

The concept of a public key system was first introduced by DIFFIE and HELLMAN (2) in 1976. They considered the problem of key distribution, which is a major disadvantage of conventional cryptosystems and limits their widespread use in commercial environments. Their approach was to find cryptosystems which would remove the need for a secure channel to exchange keys. This would eliminate the time consuming and expensive process of establishing a secure channel between two parties. Two alternatives were suggested, public key distribution and public key ciphers.

Public key distribution allows two users A and B to establish a key, which can then be used in a conventional encryption algorithm, by communicating over an insecure channel. This insecure channel can be the channel over which the conventional cryptosystem will be used. An eavesdropper listening in on the key establishment procedure must not be able to obtain sufficient information to make it computationally feasible to find the key. DIFFIE and HELLMAN give an example of a public key distribution system which will be repeated here to clarify the procedure.

A user, i, who wishes to be included in the public key distribution scheme must first generate a random number,  $r_i$  from a finite field GF(N) i.e a positive integer less than N. This number is kept secret but the user publishes the key,  $K_i$ , which is obtained from  $r_i$  by the following relationship:

$$K_i = a mod N$$

where a is a fixed primitive element of GF(N). Two users, i and j, who wish to initiate secure communication arrive at a common key,  $K_{ij}$  using the

information available in the public directory. For user i,

$$K_{ij} = a \xrightarrow{r_i r_j} \mod N$$

$$= (a \xrightarrow{r_j} \mod N) \xrightarrow{r_i} \mod N$$

$$= (K_j) \xrightarrow{r_i} \mod N$$

where  $r_i$  is known only to user i and  $K_j$  is obtained from the public directory. User j arrives at the same key by calculating,

$$K_{ij} = a^{r_i r_j} \mod N$$

$$= (K_i)^{r_j} \mod N$$

whereas in this case  $r_j$  is known only to user j and  $K_i$  is obtained from the public key. Users i and j have thus arrived at a common key without the need for a secure key channel.

The security of this method relies on the difficulty of calculating logarithms in a finite field GF(N). For a cryptanalyst to determine  $K_{ij}$  it is necessary that he know  $r_i$  or  $r_j$ . These are not available directly as each user has kept their r number secret. The eavesdropper must therefore obtain  $r_i$  (or  $r_j$  from the corresponding  $K_i$ . Now

$$K_i = a^{r_i} \mod N$$

therefore

$$r_i = log_a (K_i) \mod N$$

The system will be insecure if logarithms are computationally easy to calculate. The fastest algorithm, which is applicable for any value of N, is attributed to KNUTH(8) and has a run time which is  $O(N^{0.5})$ . Thus for large N (>10 $^{50}$ ) this is computationally infeasible. Faster algorithms are available; POHLIG and HELLMAN(10), ADDLEMAN(11) but these are generally dependent on some

property of the generator a or the modulus N. The choice of a and N should be so as to defeat or slow down these algorithms.

#### 2.2 PUBLIC KEY CIPHERS

A public key cipher, fig. 2.1, differs from in that the encryption conventional ciphers and decryption keys different and it are not computationally feasible to calculate the decryption key if the encryption key is known. In a system of this kind the encryption key can be made public. A user, A, who wishes to communicate privately with another user B, obtains B's encryption key from the public directory and uses it to encrypt the message. B can reply by obtaining A's encryption key from the public directory. As each user keeps his decryption key secret only he can decrypt the message, however anyone with access to the public directory can send secure information to another party without the need for a prior agreement on keys.

In a public key system the encryption algorithm, E, and the decryption algorithm, D, must have the following properties:

- D(E(P)) = P

- . E, D form a distinct pair.

- . It is computationally infeasible to calculate D from  ${\tt E}$

- . It is easy to encrypt and decrypt data if E an D are known.

The first property ensures that each encryption key has an inverse, thus allowing the user to decrypt the ciphertext. The second property ensures that each encryption key has a unique decryption key. The third property makes it possible to publish E without compromising the security of the system, while the fourth minimises the work necessary for encryption and decryption.

Diffie and Hellman in their original paper did not propose a practical scheme for implementing a public key

cipher. However soon after MERKLE and HELLMAN(3), and RIVEST, SHAMIR and ADLEMAN(4) proposed practical public key ciphers. The cipher proposed by Merkle and Hellman is based on the knapsack problem while that proposed by Rivest, Shamir and Adleman, and hence known as the RSA method is based on modular exponentiation and the difficulty of factoring large numbers.

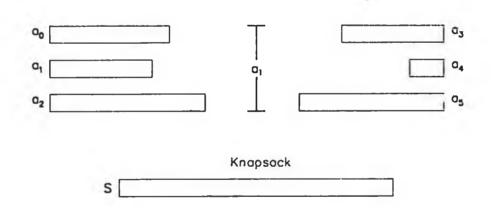

## 2.2.1 The Knapsack Problem

The knapsack problem, see Fig.(2.2), is an old arithmetic problem and can be described as follows. Given a positive integer C and a vector of elements  $A = \{a_1, a_2, \ldots, a_n\}$  the knapsack problem is to find a subset of A that sums to C i.e.

$$C = A.M = \sum_{i=1}^{n} a_i m_i$$

where  $M = \{m_1, \ldots, m_n\}$  is a binary vector. The knapsack problem appears in many commercial applications. For example a freight company wishing to maximise the value of cargo carried by boat, truck or air, and given a finite storage space and a collection of cargo, is faced with solving the knapsack problem.

The difficulty of solving a given knapsack varies depending on the elements of A. If the elements of A are superincreasing i.e if each element a, is greater by one unit than the sum of all previous a,'s, the solution is not difficult and such a knapsack is called an easy knapsack. The simplest example of an easy knapsack is one based on the binary sequence  $A = \{1, 2, 4, 8, \ldots\}$  and in this instance the solution is trivial. The binary vector M is simply the binary representation of C. knapsacks are easy to solve, the generalised knapsack problem is known to belong to the class of problems known as NP-complete which can not be solved in polynomial time on a deterministic machine. The best known algorithm for attributed knapsack problem is solving the

SCHROEPPEL(12) and takes  $O(2^{n/2})$  in time and  $O(2^{n/4})$  in memory. This information does not help greatly in determining how the knapsack problem can be used in developing a public key cipher as it tells us that at best a solution to the knapsack problem is trivial while at worst it is computationally infeasible, for large n.

To make use of the knapsack problem as a public key cipher Merkle and Hellman constructed a trapdoor by taking an easy knapsack and transforming it into a hard knapsack. Anyone not possessing the secret trapdoor information would find it computationally infeasible to solve the knapsack, however, with the trapdoor information the problem can be converted to an easy knapsack and quickly solved.

To construct a trapdoor knapsack it is first necessary to form an easy knapsack by choosing a set of elements  $A = \{a_1 \dots a_n\}$  such that A is superincreasing i.e

$$a_i > \sum_{j=1}^{i-1} a_j$$

Then choose two large numbers, a modulus, r and, a multiplier, s that are relatively prime i.e gcd(r,s) = 1. Use these numbers to calculate the hard knapsack B =  $\{b_1, \ldots, b_n\}$  where  $b_i$  is:

$$b_i = s.a_i \mod r$$

The elements of b are not superincreasing and thus B is a hard knapsack. This hard knapsack B =  $\{b_1, \ldots, b_n\}$  constitutes the users public key. All other information, particularly s,r,A should remain secret. The decryption key d, which is the multiplicative inverse modulo r of s i.e ds 1 (mod r), can be calculated and should also be kept secret.

A user X who wishes to send a secure message  $M = \{m_1 \dots m_k\}$ , where  $m_i$  is a binary digit, to user Y first breaks the message into n bit blocks. These blocks are then encrypted using Y's public key producing the

ciphertext C where

$$C = M.B = \sum_{i=1}^{n} m_i b_i$$

where  $B = \{b_1, \ldots, b_n\}$  is the public encryption key of Y. The ciphertext can now be transmitted to Y over an insecure channel. On receipt of the ciphertext, C, user Y retrieves the plaintext by applying his secret decryption key d:

$$dC = d \sum_{i=1}^{n} m_i b_i = \sum_{i=1}^{n} dm_i b_i$$

However,

$$db_i \equiv dsa_i \equiv a_i \pmod{r}$$

as,

$$ds \equiv 1 \pmod{r}$$

Thus

$$dC = \sum_{i=1}^{n} m_i a_i \pmod{r}$$

and the problem is to recover  $m_i$ . This is now an easy knapsack problem as the set  $A = \{a_1, \ldots, a_n\}$  is superincreasing.

The following simple example illustrates the method:

$$A = \{ 1,3,5,10 \}$$

$r = 23$

$s = 9$

The easy knapsack  $A = \{ 1,3,5,10 \}$  is transformed into the hard knapsack B.

$$B = A.s \mod r$$

= (9 mod 23,3\*9 mod 23,5\*9 mod 23,10\*9 mod 23)

= (9, 4, 22, 21)

this is the users encryption key which can be published in a directory or a public database. The decryption key can be calculated by solving

$$ds \equiv 1 \pmod{r}$$

$$d*9 \equiv 1 \pmod{23}$$

using Euclids algorithm, resulting in d=18. This key should not be disclosed. To encrypt a message  $M=7=(0111)_2$  to form ciphertext C use

$$C = B.M = 9 + 4 + 22 = 35 = (100011)_{2}$$

The ciphertext can be decrypted by using the secret key d to form the simple knapsack E.

$$E = dC = 18*35 \pmod{23} = 9$$

This simple knapsack (E,A) can be solved to give M. Such a knapsack can be solved in linear time.

The security of the knapsack cipher system relies on difficulty of solving hard knapsacks. As mentioned previously the fastest known algorithm can solve an nth order knapsack in time  $O(2^{n/2})$ . For this to computationally infeasible it is recommended that n be greater than 100. If n is 100 then the time taken to solve the hard knapsack, assuming that a single operation takes one microsecond, is approximately 109 seconds or years. However a large number of processors working in parallel would reduce this time considerably and this would have to be considered when choosing n.

The choice of A, r and s is also important to the security of the cipher. These should be chosen from a sufficiently large set so that a direct search is not computationally feasible. For n=100 Merkle and Hellman recommend that the numbers be chosen from the following ranges:

$$2^{201}$$

+1  $\leq$  r  $\leq$   $2^{202}$  -1

$2 \leq$  d  $\leq$  r - 2

$1 \leq$   $a_1 \leq$   $2^{100}$

$2^{100}$  +1  $\leq$   $a_2 \leq$   $2*2^{100}$

$$3*2^{100} +1 \le a_3 \le 4*2^{100}$$

: : : (2<sup>i-1</sup> -1)2<sup>100</sup> +1  $\le a_i \le 2^{i-1}.2^{100}$

This ensures that each parameter is can have one of  $2^{100}$  possible values thus defeating a direct search. Note that as each element of the public key B is less than r they will require 202 bits each for their representation. Thus the public key of each user will require approximately 20k bits of storage. An n bit message M when encrypted will require  $202 + \log_2(100)$  or 209 bits to represent it. The message is therefore expanded by a factor of 2.09. If the ciphertext is to be transmitted over a bandlimited channel this will result in a halving of transmission rate when compared with unencrypted transmission.

## 2.2.2 The RSA Cipher

The RSA public key cipher is based on modular exponentiation and the difficulty of factoring large numbers. To encrypt a plaintext message, M, it is first divided into blocks and then raised to the eth power modulo N, where e and N are the encryption keys of the user i.e

$$C = M^e \mod N$$

The size of the plaintext block should be such that M is always less than N. To recover the plaintext from the ciphertext, the ciphertext C is raised to the  $d^{\text{th}}$  power modulo N where d is the users decryption key i.e

$$M = C^d \mod N$$

Note that as all arithmetic is performed modulo N there is no data expansion from plaintext to ciphertext.

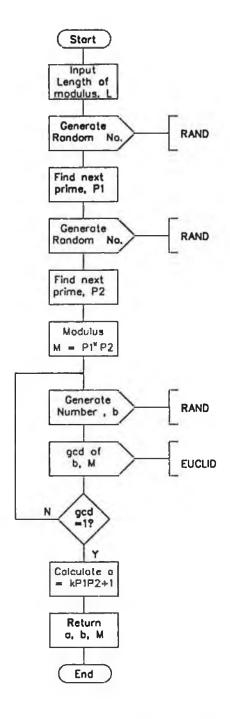

To make use of this method in a public key cipher the key parameters e,d,N have to be carefully chosen. Rivest, Shamir and Adleman recommend the following procedure for their selection.

First choose two large prime numbers p and q. There are restrictions necessary when choosing such primes to ensure that the cipher is resistant to cryptanalysis. These restrictions and the procedures for choosing large primes will be described in a later chapter. These primes must be chosen from a large enough set that a direct search is computationally infeasible. The modulus N is the product of these two primes:

$$N = pq$$

The encryption key, e, can now be chosen to be a large random number that is relatively prime to  $\emptyset(N)$  where  $\emptyset(N)$  is the Euler totient function of N:

$$gcd(e, \emptyset(N)) = 1$$

where gcd is the greatest common divisor. The Euler totient function of an integer, N, is the number of integers less than N and relatively prime to N. For a prime number the Euler totient function is one less than the prime number itself so

$$\mathcal{A}(N) = \mathcal{A}(pq) = (p-1)(q-1)$$

This is the users encryption key and it can be published, along with N , in a public directory or database. The decryption key, d, can be calculated as the multiplicative inverse of e modulo  $\mathcal{B}(N)$ . Such a number exists and is unique as e is relatively prime to  $\mathcal{B}(N)$ . the decryption key is therefore given by:

ed

$$\equiv 1 \pmod{\mathscr{O}(N)}$$

This equation can be solved using Euclids algorithm to find d. This is the decryption key of the user and it should not be made public. Note that due to the nature of the cipher e and d are interchangeable and either one can be made public retaining the other to use as a decryption key.

To test the validity of the RSA cipher it is necessary to prove that decryption of an encrypted message will yield the original plaintext i.e

$$D(E(M)) = M$$

where D denotes the decryption function and E the encryption function. For the RSA cipher

$$E(M) = C = M^e \text{ Mod } N$$

and

$$D(E(M)) = D(C) = C^d \text{ Mod } N = (M^e \text{ Mod } N)^d \text{ Mod } N$$

$$= M^{ed} \text{ Mod } N$$

but

$$ed = 1 \pmod{\mathscr{O}(N)}$$

=>  $ed = k\mathscr{O}(N)+1$ , for some integer k. thus  $k\mathscr{O}(N)$

D(E(M)) = M.M

Now for any integer, a, relatively prime to O(N) Eulers generalisation of Fermats theorem states that :

Mod N

$\mathcal{Q}(N)$  a = 1 ( Mod N ) , for any integer a. therefore  $D\left(E\left(M\right)\right) = M \ (\text{Mod } N)$

and as M is less than N :

$$D(E(M)) = M$$

Thus it is seen that the functions described in the RSA method do perform encryption and decryption.

As an example of the use of the RSA cipher consider the following example, note that the numbers involved here are too small for a practical cipher but the method is the same.

Choose p and q , the random primes to be:

$$p = 53, q = 61$$

Hence the modulus N is 53 \* 61 = 3233 and  $\emptyset(N)$  the Euler totient function of N, is 52 \* 61 = 3172. To choose e we select a number in the required range and check to see if it is relatively prime to  $\emptyset(N)$ . If it is not another number must be used. let d = 279, which is relatively prime to 3172, this can be proven using Euclids algorithm. To find the encryption key e we need to solve the equation:

$$d * 279 = 1 \pmod{3172}$$

this can again be solved using Euclids algorithm. This results in a value for e of 71. To encrypt the message RENAISSANCE we first assign numbers to each letter say A = 00....Z = 25 and then divide the message into 4 digit blocks. This gives

$$M = (1704 1300 0818 1800 1302 0426)$$

To encrypt this message each block is raised to the power of 71 modulo 3172 giving the ciphertext C

$$C = (3106\ 0100\ 0931\ 2691\ 1984\ 2927)$$

To recover the plaintext message M the same procedure is carried out with d=279 as the exponent.

The security of the RSA cipher relies on the difficulty of finding d when e and N are known. As d is the multiplicative inverse of e modulo  $\mathcal{O}(N)$  it is necessary to determine  $\mathcal{O}(N)$ .  $\mathcal{O}(N)$  is formed by subtracting one from each of the prime divisors of N and forming their product i.e

$$\mathcal{O}(N) = (p-1)(q-1) = 1 + N - p - q$$

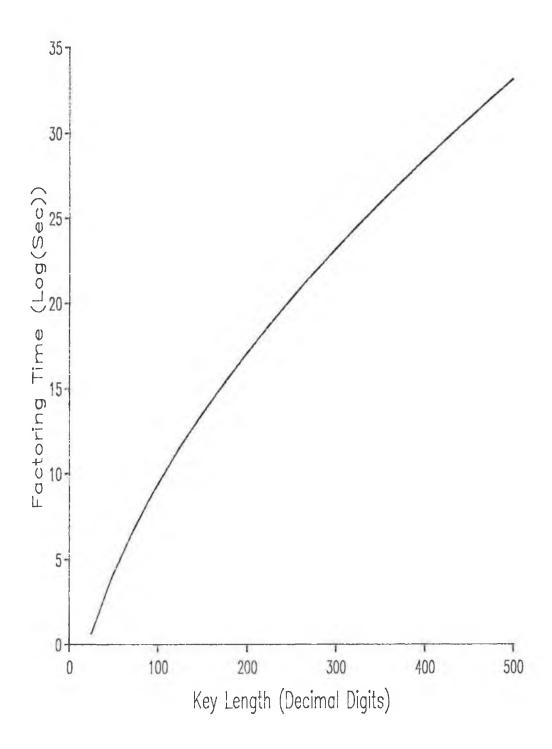

If p and q are known  $\emptyset(N)$  can be calculated and the decryption key d can also be found. The problem therefore reduces to finding the prime factors p, q of N. Factoring a number into its prime factors is easy when N is small but becomes increasingly more difficult as N increases.

Various factoring algorithms have been suggested and KNUTH(8) describes some of these in detail. The fastest known algorithm for factorisation attributed to SCHROEPPEL and detailed in KNUTH(8, pp. 380-384) has a runtime of the order of  $n^r$  where r is:

$$(Ln(N) * Ln(Ln(N)))^{1/2}$$

Even with this algorithm the time required to factor N, for large N, is excessive. A table of the time required to factor N for various sizes of N and assuming that one microsecond is given in Fig. (2.3). operation takes one From this table it can be seen that for N greater than 10<sup>100</sup> calculating the prime factors is computationally infeasible. To protect against future increases speed and power of computers Rivest, Shamir and Adleman recommend choosing N to be  $O(10^{200})$  i.e 200 digits. This would require approximately 3.8\*109 years to factor. This should provide a secure cipher for a long time regardless of progress in computer technology. Other methods of attack are possible (Rivest, Shamir, Adleman (4)) but these are all believed to be equivalent to factoring N and thus would require the same computational resources.

## 2.3 COMPARISON OF PUBLIC KEY CIPHERS

The knapsack method and the RSA method are the main contenders in the field of public key cryptography. cipher has the advantage that encryption and decryption are fast as only modular multiplication and addition are required. The RSA method is more complex requiring modular exponentiation and this consuming. The public key size required for a knapsack cipher is approximately 20k bits whereas for the RSA the key memory required is about 1.2k bits. The RSA cipher does not expand the data from plaintext to ciphertext as the plaintext and ciphertext space are the same. This allows the RSA to be used to authenticate messages by forming digital signatures. The knapsack cipher does expand the data and thus it can be used for secrecy

authentication but not both. The ability of the user of an RSA system to choose the level of security is also an advantage. There has been doubts cast on the security of the knapsack cipher,(4)which undermines confidence in the method. The RSA method has, so far, remained secure, providing the keys are chosen properly. This confidence in the RSA method and the advantages that a public key cipher provide when compared to a conventional cipher has led to it being proposed as a national standard in the U.S.A ( ZIMMERMANN(7) ). The main difficulty with the RSA cipher is the complexity of the encryption and decryption process. Using dedicated hardware the DES cipher, conventional cipher, has a throughput in the megabits/sec To be successful in a commercial environment the RSA method must attain a speed comparable to or at least the same order as the DES. The objective of this report is to investigate ways of implementing the RSA cipher.

#### 2.4 MICROPROCESSOR IMPLEMENTATION OF RSA CIPHER

The first objective is to investigate the implementation of the RSA cipher on a microprocessor. This would be an inexpensive and flexible method of implementation that would have many commercial applications. If it is possible to produce a programme that will enable a reasonable throughput rate it could be included in many devices already utilising microprocessors providing a high level of security for a small cost.

The choice of an 8 bit microprocessor for use in implementing the RSA cipher is based mainly on power, cost the availability of a development system. and microprocessor in common use in the N.I.H.E is the MC6809 from Motorola. This is considered one of the most powerful 8 bit microprocessors due to its flexible methods and its use of a hardware multiplier. Development systems for this microprocessor were readily available in college, consisting of VAX based assemblers simulators, and real time emulators. The suitability of and the time delay incurred processor purchase of development systems should an alternative be

motivated the use of the MC6809 in the RSA cipher. implementation of the As all bit microprocessors are basically similar the results obtained this microprocessor should be immediately applicable to other microprocessors.

### 2.4.1 Modular Exponentiation

basis the RSA cipher of is modular encryption exponentiation. As the and decryption algorithms are similar we need only consider one or the other. The objective therefore is to find ways calculating C where

$C = M^e \text{ Mod } N$

where N,e,M are of the order of 200 decimal digits or 600 bits. This calculation must be performed on an 8 bit microprocessor.

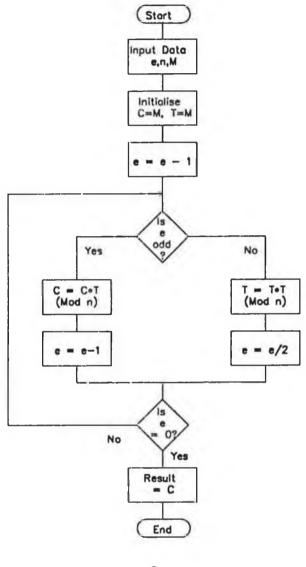

To calculate Me, M could simply be multiplied by itself e times. This requires e multiplications. However not all of the partial products are necessary. Consider the case when e is a power of two say e = 16. This would require 16 multiplications if the simple method above is used. The number of multiplications can be dramatically reduced by squaring each partial product i.e forming M,  $M^2$ ,  $M^4$ ,  $M^8$ ,  $M^{16}$ . This has reduced the number multiplications to 4 and in general only  $Log_2(e)$ multiplications are required if e is a power of 2. This method can be expanded to include any arbitrary e by using the following algorithm, known as exponentiating by repeated squaring and multiplying. This method is an extension of the binary method described by KNUTH (8, pp.441-443) to numbers of arbitrary radix. This method is described below:

First Multiplication:

Let the result C be equal to M. This carries out the first multiplication so reduce e by one. A temporary variable T is needed to hold the partial product and this should be initialised to M also.

- : If e is odd : Let C = C \* T and reduce e by one.

- : If e is even : Let  $T = T^2$  and divide e by two.

- : Repeat until e is zero.

To demonstrate the method consider the example  $M^{37}$ .

```

First C = M, T = M, e = 36

Then e is even: T = T^2 = M^2, e = 18

e is even: T = T^2 = M^4, e = 9

e is odd: C = C*T = M.M^4, e = 8

e is even: T = T^2 = M^8, e = 4

e is even: T = T^2 = M^{16}, e = 2

e is even: T = T^2 = M^{32}, e = 1

e is odd: C = C*T = M^5.M^{32}, e = 0

```

The number of multiplications necessary to calculate  $M^{37}$  is thus 7 which is a large reduction on the 37 required by the direct method.

To calculate the number of multiplications required for arbitrary e consider the binary representation of e,  $(e_0...e_k)$ . To test if e is odd or even it is only necessary to determine whether  $e_0$ , the least significant bit, is one or zero. A zero would imply that e is even, a that it is odd. In the squaring and multiplying method described above if e is even we calculate  $T^2$  and divide e by 2 whereas if e is odd we calculate C\*T and decrease e by one. Reducing an odd number by one results in an even number. Therefore an odd number is equivalent to an even number followed by an extra multiplication (C\*T) in the above method. The number of times that e can be divided by two is  $log_2(e)$ . The total number of multiplications required is  $log_2(e) + D$  where D is the number of extra multiplications required because e is odd. Dividing by two, in binary, is equivalent to

shifting right by one bit, thus the number of times that e can be odd is equal to the number of ones in the binary representation of e or the Hamming weight of e. Therefore the total number of multiplications is given by:

$$NM = log_2(e) + w(e)$$

where w(e) is the Hamming weight of e. The worst case condition is when e contains all ones in which case  $w(e) = \log 2(e)$  and the number of multiplications required is:

$$NM_{max} = 2*log_2(e)$$

A flowchart describing this exponentiation method is shown in Fig(2.4).

#### 2.4.1.1 Results

A programme was written in MC6809 assembly language to implement the algorithm described in Fig.(2.4). While it may be possible to compress the programme further the times given below represent an approximate run time which would not be significantly altered by variations in programming techniques. The MC6809 is an 8 bit microprocessor therefore all calculations are performed on 8 bit bytes. The worst case time to encrypt a message M using a key (e,N) in which e and N can be represented by  $N_{\rm B}$  bytes is (20):

$$T_e = 53 + 2583(N_B) + 2432(N_B)^2 + 32(N_B)T_{Mod}[N_B]$$

cycles

where  $T_{\mbox{Mod}}[N_{\mbox{B}}]$  is the number of cycles required to calculate the product of two  $N_{\mbox{B}}$  byte numbers modulo a third  $N_{\mbox{B}}$  byte number.

A cycle is one microsecond on the standard 1MHz microprocessor. Various methods for performing modular multiplication and the resulting overall encryption will now be discussed.

Fig. 2.1 Public Key Cipher

Find the set of a<sub>1</sub>,s that will sum to S i.e. fill the knapsack

Fig. 2.2 The Knapsack problem

Fig (23) Factoring time for various key lengths

$C = M^e \pmod{n}$

# Variables:

Exponent e: Modulus n:

T: Temporary variable

C: Result

M: Operand

Fig. 2.4 Modular Exponentiation

# 3. Modular Multiplication Methods

## 3.1 INTRODUCTION

exponentiation requires that modular Modular multiplications be performed. In the RSA public key cipher it is necessary to calculate the product AB (mod N) where A, B, N are positive integers of the order of 100 decimal digits or 330 bits. Calculations on numbers of this size cannot be performed directly on a standard microprocessor whose word size is much smaller than this, typically 8 or It is thus necessary to consider calculations as multiple precision calculations. It convenient to use the word size of the computer as the radix for all calculations thus a 336 bit number becomes a 42 digit number on an 8 bit microprocessor such as the MC6809. It is considered that the multiplication of two single digit numbers to form a double precision result is a primitive operation of the microprocessor.

To form the product C = AB (Mod N) two approaches are possible. The first forms the product C = AB and then reduces this modulo N to complete the calculation. This entails the use of memory to store the double length result prior to its reduction. The second method achieves the reduction modulo N simultaneously with the formation of the product AB. This removes the need to store a double length result as the product is a single length number, however such methods are generally slower than the former methods.

The reduction of an m digit number C modulo N where N is an  $N_{\rm B}$  digit number is the remainder when C is divided by N and is therefore less than N. Multiple precision division and subtraction are thus needed for reduction. The process of performing modular multiplication is one of multiple precision multiplication of two single length numbers to provide a double length result followed by multiple precision division and subtraction to reduce this number modulo N.

## 3.2 MULTIPLICATION

The conventional 'pen and paper' method for forming multiple precision products is known as the sum of products method. In this method the first operand is multiplied by each digit of the second operand forming a number of partial products. These partial products are then shifted and added to obtain the result. As an example consider multiplying 814639 by 462115:

Multiplicand: 814639 Multiplier: <u>x 462115</u> 4073195 814639 814639

Result: 376456301485

When implementing this method on a computer it is more efficient in both time and memory to add the partial products as they are produced instead of storing each result and adding when all partial products are obtained.

In the general case for numbers of arbitrary radix consider the product of  $A = (a_0, \ldots a_{t-1})_r$  and  $B = (b_0, \ldots b_{s-1})_r$  where the  $a_i$ 's and  $b_i$ 's are digits in radix r. The radix r is usually chosen as the word length of the computer being used e.g r = 256 for an 8 bit microprocessor such as the MC6809. The product of A and B is therefore:

$$A*B = \sum_{i=0}^{t-1} (a_i r^i) \qquad \sum_{j=0}^{s-1} (b_j r^j)$$

This can be written as :

$$A*B = \sum_{i=0}^{t-1} P_i + r^i \sum_{j=0}^{s-1} (a_i b_j r^j)$$

where  $P_i$  is the partial product. It can be seen from this that s\*t single precision multiplications are required along with multiple precision additions.

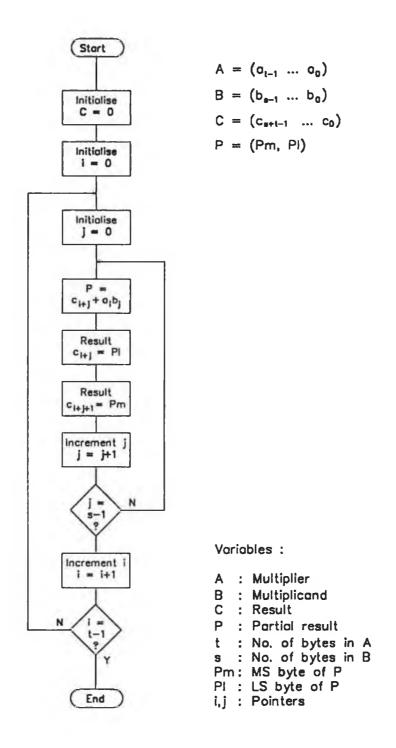

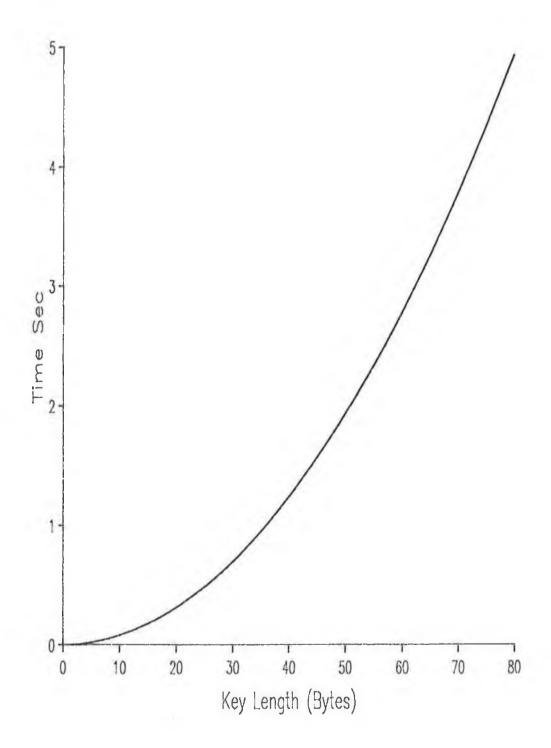

This algorithm was implemented in assembly language on the MC6809 microprocessor and a flowchart describing the programme is shown in Fig.(3.1a). The digits of the multiple digit numbers A and B were stored in successive memory locations. A pointer to the operands and the number of digits contained in each was also kept. This facilitates the addressing and manipulation of the operands. The time taken to calculate the product is given below.

$$T_{\text{mult}} = 62 + 11(s+t) + s(45 + 49t)$$

cycles

=  $62 + 56s + 11t + 49st$  cycles

In the RSA public key cipher s and t will tend to be the same as all multiplication is done modulo N, thus the maximum value for either operand is N. If  $N_{\rm B}$  is the number of digits in N then and if s = t =  $N_{\rm B}$  then the multiplication time is :

$$T_{\text{mult}}[N_{\text{B}}] = 62 + 67(N_{\text{B}}) + 49(N_{\text{B}})^2$$

cycles

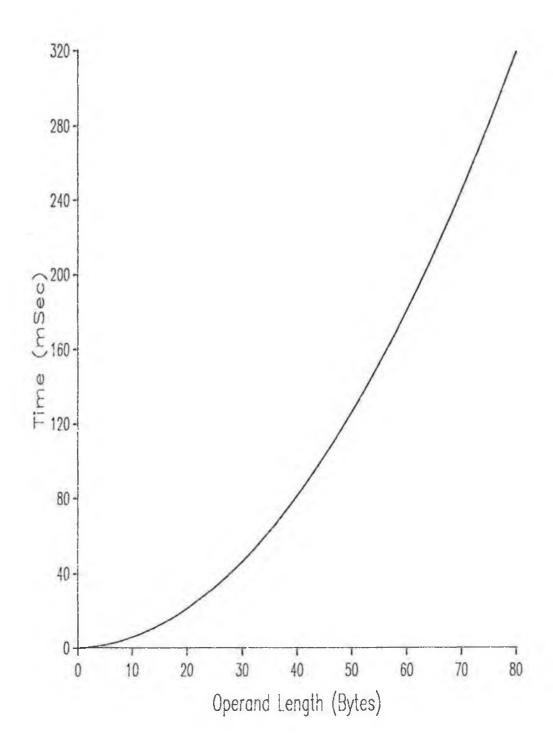

The time taken to multiply numbers of differing precision is shown in Fig.(3.1b). In this case a clock cycle is taken as being equal to 1 microsecond as in the standard MC6809. The area of particular interest, to the RSA cipher, in this figure is the multiplication of numbers in the 40 to 80 byte range as this provides a significant level of security. It can be seen that a multiplication of this size takes from 80 to 320 milliseconds.

# 3.3 REDUCTION MODULO N

To represent a number C in modular form it is necessary to find an integer R such that:

$$C = R \pmod{N}$$

Therefore C = Q.N + R where Q is some integer. This is equivalent to dividing C by N to obtain a quotient Q and a remainder. Reduction modulo N is thus very similar to

division except that in this case it is the remainder and not the quotient that is of interest. It is therefore necessary to consider ways to implement multiple precision division. Three methods are considered:

- 1. Division by repeated shift and subtract.

- 2. Division using KNUTHs algorithm.

- The calculation of reciprocals and its use in division.

# 3.3.1 Division by repeated shift and subtract

The shift and subtract method of division is similar to the familiar 'pen and paper' division in common use. In this the quotient is obtained one digit at a time and the divisor is subtracted from the divisor at decreasing levels of significance until the calculation is complete. Two types of division using this method can be defined, restoring or non-restoring division. In restoring division, if a trial subtraction is unsuccessful i.e the partial remainder is less than zero the partial remainder is restored to its previous value, the divisor is shifted another trial subtraction is made. non-restoring division, however, if a trial subtraction is unsuccessful the partial remainder is not restored instead the next trial becomes an addition. This has the advantage that it is not necessary to retain an unmodified version of the partial remainder or to perform an additional addition to restore the remainder. Non-restoring division can easily be implemented when twos complement numbers are being used, however, when dealing with unsigned integers the restoring method is preferred. This can be described as shown below:

Let the dividend C be (  $c_{m-1}c_{m-2}...c_0$  )<sub>2</sub> and let the divisor N be (  $d_{n-1}d_{n-2}...d_0$  )<sub>2</sub> where  $c_i$  and  $d_i$  are binary digits then the algorithm is :

From the divisor N form an m bit number by adding m-n trailing zeros.

$$N = (d_{n-1}d_{n-2}..d_00_{m-n}0_{m-n-1}...0_1)_2$$

2. Subtract the divisor N from the dividend  ${\tt C}$  to form the partial remainder.

$$C = C - N$$

If the partial remainder is negative the quotient bit is zero otherwise it is one. As the quotient is not required in this application it is not necessary to store it.

3. If the partial remainder is negative then restore it by adding N.

$$C = C + N$$

- 4. The divisor is now shifted one bit to the right and steps (2) to (4) are repeated.

- 5. The algorithm ends when the divisor has been shifted m-n times.

As an example of this method consider dividing  $(11001001)_2$  by  $(111)_2$ .

| 111 | 11001001<br>111<br>1111                                                         | : remainder is negative => Q5=0 |

|-----|---------------------------------------------------------------------------------|---------------------------------|

|     | 1100<br>_111                                                                    | : restore partial remainder     |

|     | 101                                                                             | : remainder is positive => Q4=1 |

|     | $   \begin{array}{r}     1011 \\     \underline{111} \\     100   \end{array} $ | : remainder is positive => Q3=1 |

|     | 1000<br>_111<br>_1                                                              | : remainder is positive => Q2=1 |

|     | $   \begin{array}{r}     10 \\     \underline{111} \\     1011   \end{array} $  | : remainder is negative => Q1=0 |

101 : restore partial remainder

111

1110 : remainder is negative => Q0=0

101 : restore partial remainder

Therefore  $(11001001)_2/(111)_2 = (11100)_2$  plus a remainder of  $(101)_2$  or :

$$(11001001)_2 \equiv (101)_2 \pmod{(111)_2}$$

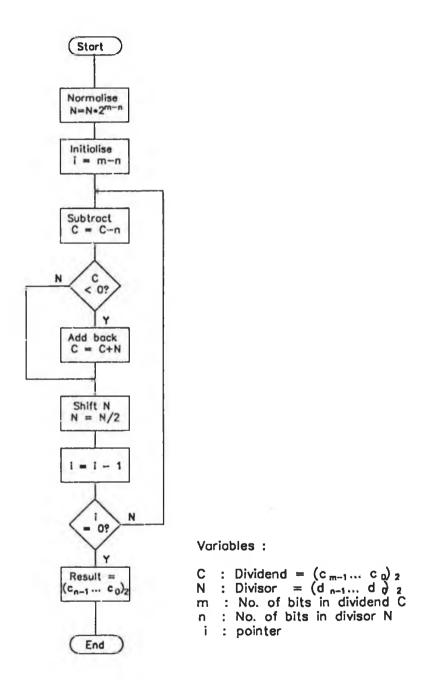

This algorithm was implemented in assembly language on an MC6809 microprocessor. A flow chart of this algorithm is given in Fig. (3.2a). The run time of the algorithm was:

$$T_{D1} = 638 + 486 (N_C - N_B) + 208 (N_C - N_B)^2 + 8 (N_C - N_B + 1) [105 + 123 (N_C - N_B)]$$

=

$$1478 + 2310 (N_C - N_B) + 1192 (N_C - N_B)^2$$

where  $N_C$  is the number of bytes in the dividend C and  $N_B$  is the number of bytes in the divisor or modulus N. The dividend will in the case of the RSA cipher contain a maximum of twice as many digits as the divisor (it is the product of two  $N_B$  digit numbers) thus  $N_C$  =  $2N_B$  therefore,

$$T_{D1} = 1478 + 2310 (N_B) + 1192 (N_B)^2$$

A table and graph showing the variation of the division time  $T_{\rm D1}$  for differing values of  $N_{\rm B}$  is shown in Fig.(3.2b). As in the case of multiplication we are particularly interested in the range from 40 digits to 80 digits and it can be seen that reduction of an integer of this size takes from 2 to 8 seconds. It is again noted that one clock cycle is of 1 microsecond duration.

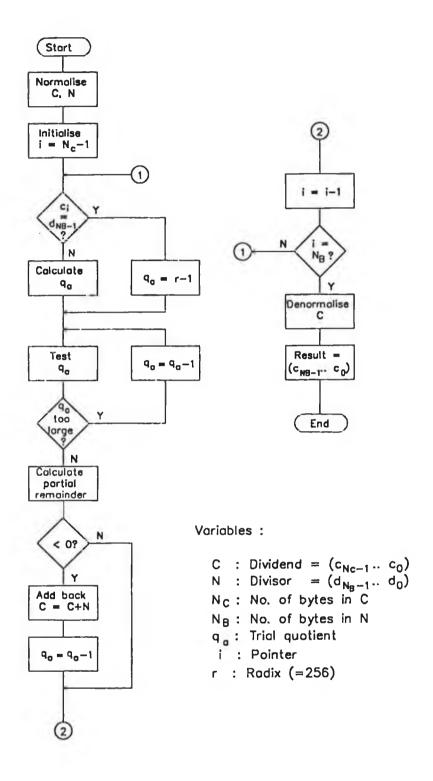

# 3.3.2 Division using KNUTHs algorithm

The disadvantage of the previous method is that it does not utilise the power of the microprocessor efficiently. The algorithm deals with bits at a time whereas the microprocessor can more readily deal with bytes. An algorithm which can be used with computers of arbitrary radix is KNUTHs(8) algorithm. The purpose of this algorithm is to approximate the 'pen and paper' method of division. Consider the case of an  $N_C$  digit dividend  $C = (c_{NC-1}....c_0)_r$  divided by an  $N_B$  digit divisor  $N = (d_{NB-1}...d_0)_r$ . The first step is to divide the divisor into the most significant  $(N_B+1)$  digits of the dividend to obtain a quotient digit q and a partial remainder P.

$$(d_{NB-1}..d_0)_r$$

$$(c_{NC-1}...c_{NC-NB-1})_{p}$$

P is always less than N so the next step uses  $P*r + c_{NC-NB-2}$ , where r is the radix, as the dividend. The result of this is to shift P left by one digit and to add the next most significant digit of the dividend to it. This is similar to the shift in the previous shift and subtract method.

The difficulty arises in finding the quotient digit q. This can not be obtained directly as it involves a multiple precision division. An approximation to q, call it  $q_a$ , can be obtained from the leading digits of the divisor and the dividend. Thus

$$q_a = int \left[ \frac{c_{Nc-1}b + c_{Nc-2}}{d_{NB-1}} \right]$$

where int denotes the integer part of. If  $q_a$  is larger than r it can be replaced by (r-1), the largest single digit number. The accuracy of this approximation to q will determine how useful the method is. KNUTH(x pp. 255-260) shows that if the dividend is first normalised so that its most significant digit is greater than half the radix then

$\mathbf{q}_{\mathrm{a}}$  will always be greater than  $\mathbf{q}$  but never more than two greater i.e

$$q \leqslant q_a \leqslant q+2$$

(if  $c_{Nc-1} > int(r/2)$ )

The trial quotient can thus be obtained by dividing a double digit number by a single digit number to obtain a single digit approximation  $q_a$ . Many microprocessors include such an instruction in their instruction set but unfortunately the MC6809 does not. This is not a great disadvantage as such a division can be carried out rapidly using the shift and subtract method described previously. When  $q_a$  is calculated it is multiplied by the divisor N and subtracted from the dividend.

The complete algorithm is thus :

1. Normalise: Ensure that the most significant digit of the divisor is greater than half the radix. Multiply the dividend by the same factor. This can be accomplished by:

$$N = int \left[r/(d_{NB-1}+1)\right] *N, C = int \left[r/(d_{NB-1}+1)\right] *C$$

Note that although the normalisation will not affect the quotient it will affect the remainder and as it is the remainder which is important in this application the result will have to be denormalised.

- 2. Initialise : set a pointer  $i=N_C-1$ , the most significant digit of the dividend.

- 3. Calculate trial quotient  $\mathbf{q}_a$  . This is obtained from the most significant digits of the dividend and the divisor.

$$q_a = \inf \left[ \frac{c_i b + c_{i-1}}{d_{NB-1}} \right]$$

4. Test  $q_a$ . Determine if  $q_a$  is too large. The following test is a quick method of determining if  $q_a$  is too large. It will determine all cases when  $q_a$  is two

greater than q and most of the cases when  $q_a$  is one greater than q.

if

$$q_a d_{NB-2} > (c_i b + c_{i-1}) - q_a d_{NB-1} r + c_{i-3}$$

then

$$q_a = q_a - 1$$

5. Calculate partial remainder. Multiply  $\mathbf{q}_{a}$  by N and subtract from most significant digits of C.

$$P_i = (c_i...c_{i-NB}) - q_aN$$

The partial remainder can be stored in the most significant digits of C i.e.

$$(c_i...c_{i-NB}) = P_i$$

6. Restore. If  $q_a$  is one greater than q and is not detected by step (4)  $P_i$  will be negative. Reduce  $q_a$  by one and restore the partial remainder by adding N to it.

$$P_i = P_i + N$$

- 7. Decrement pointer i. Repeat steps (3) to (7) until  $i = N_B$

- 8. Denormalise the remainder to obtain the required result. The remainder is stored in the  $\rm N_{\rm B}$  least significant digits of C.

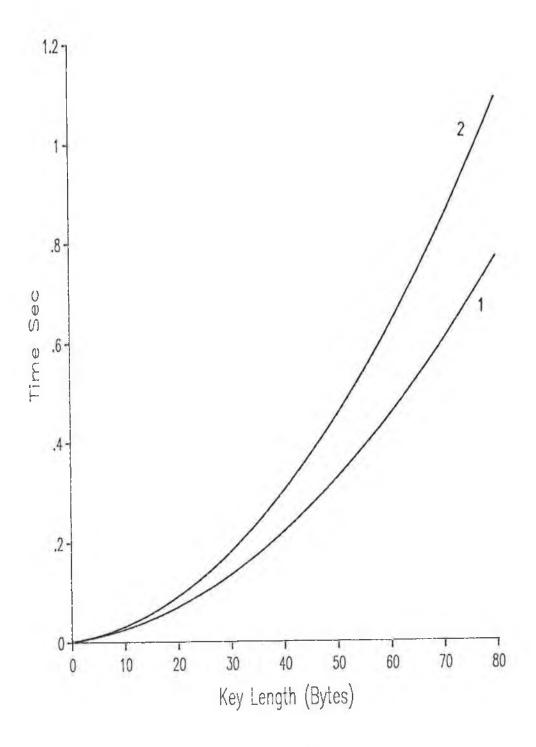

A flow chart describing this algorithm is shown in Fig.(3.3a). The algorithm was implemented on the MC6809 microprocessor and the run time was as follows:

$$T_{D2} = 827 + 561N_B + (N_C - N_B + 1) \left[ 701 + 103 (N_C - N_B) \right]$$

Again as in the previous case if  $N_{\text{C}} = 2N_{\text{B}}$  the total worst case run time is:

$$T_{D2} = 1528 + 1365(N_B) + 103(N_B)^2$$

cycles

A table and graph showing the division time for varying block lengths is shown in Fig.(3.3b). The time taken to divide numbers in the 40 to 80 digit range is from 200ms to 800ms.

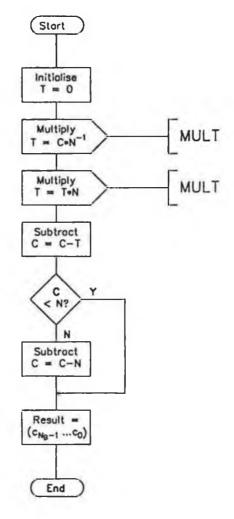

# 3.3.3 Division using reciprocals.

If the reciprocal of a number can be found then a quotient can be formed by taking the reciprocal of the divisor and multiplying the result by the dividend.

$$quotient = \begin{array}{c} \frac{Dividend}{}{Divisor} = \begin{bmatrix} Dividend & 1 \\ & \star & \\ & Divisor \end{bmatrix}$$

This method is especially useful when the divisor is common to many multiplications. In this case the divisor can be precalculated thus saving time. In the RSA method the divisor which is the modulus N will remain constant throughout the exponentiation process which will require many modular multiplications and thus divisions by N. Two methods of obtaining an approximation to the reciprocal of a number were considered. These are:

1. Divide  $2^K$  by the number N, whose reciprocal is required, to get a K place approximation to 1/N. The division in this case can be carried out by any means available such as the shift and subtract method described previously or KNUTHs algorithm. The binary point is assumed to be to the left of the most significant bit.

#### 2. Newtons Method.

This requires some initial approximation  $X_0$  to the reciprocal 1/N and then to use the iterative algorithm:

$$x_{j+1} = 2x_j - Dx_j^2$$

This algorithm converges rapidly, at a quadratic rate, to 1/N if the initial approximation to 1/N was 'good'. If  $X_0$  is not sufficiently close to 1/N the method may converge only slowly, if at all.

The speed of the algorithm chosen to calculate the reciprocal is not a limiting factor as it will only be calculated once per exponentiation. The first method was chosen using the shift and subtract division algorithm as it avoids the problem of convergence and it had already been coded.

The implementation of the shift and subtract reciprocal algorithm on the MC6809 is essentially the same as that of the division programme with the exception that in this case it is the quotient and not the remainder that is of interest and this must be stored. The flowchart for this algorithm is thus the same as for the division programme and can be seen in Fig. (3.2a). The time required to calculate the reciprocal is:

$$T_R = 1447 + 174(N_C) + 424(N_C)^2$$

cycles.

where  $N_C$  is the number of bytes in the dividend. Having calculated the reciprocal it is necessary to find the quotient and the remainder. The product  $C^*N^{-1}$  needs to be calculated. As C is typically  $2N_B$  bytes long and  $N^{-1}$  is  $N_B$  bytes long this would involve a long multiplication yielding a result of  $3(N_B)$  bytes in length. This level of accuracy is not required, only integer accuracy is necessary, thus the multiplication can be considered as the multiplication of two  $(N_B)$  byte numbers. This product should then be multiplied by the divisor N and subtracted from C to obtain the remainder. Two multiple precision multiplications are performed.

This algorithm, a flow chart of which is shown in Fig.(3.4a), was implemented on the MC6809 microprocessor. The run time of the algorithm is:

$$T_{D3} = 240 + 101(N_B) + 2(T_{Mult}[N_B])$$

cycles.

where  $N_B$  is the number of bytes in the divisor, N, and  $T_{Mult}[N_B]$  is the time taken to multiply two  $N_B$  byte numbers to form a  $2\,(N_B)$  byte product using the algorithm described previously. A table showing the run time for various lengths of operands is shown in Fig.(3.4b).

## 3.4 BLAKELYS ALGORITHM.

The methods discussed so far have performed the modular multiplication in two steps. The first step multiplied the two operands together forming a double length product. This product was then reduced by dividing it by the modulus and keeping the remainder. It is possible to perform the modular multiplication directly and an algorithm to do this was described by BLAKELY(9).

Blakelys algorithm is similar to the conventional bitwise integer multiplication algorithm. In this method the following steps are carried out:

- 1. Initialise the result to zero.

- 2. Test the most significant bit of the first operand. If it is one add the second operand to the result.

- 3. Shift the result one bit to the left.

- Repeat for successively less significant bits of the first operand. Stop when all the bits have been tested.

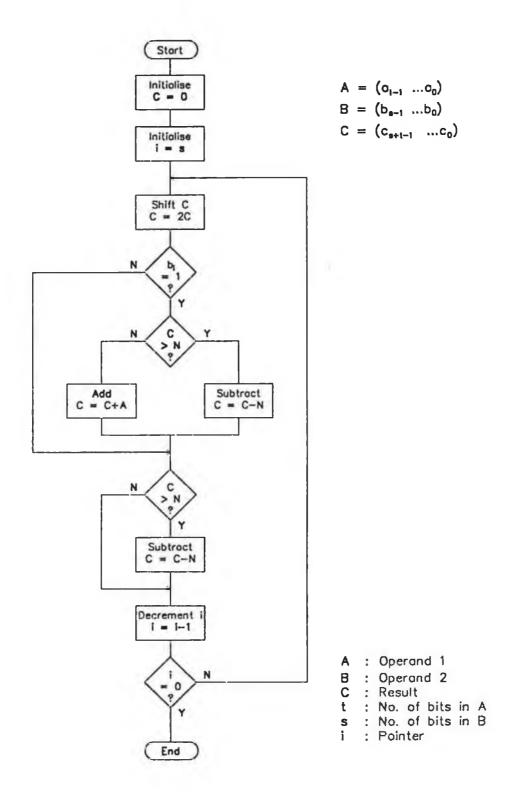

The modular multiplication algorithm developed by Blakely modifies this basic algorithm to provide modular multiplication. To do this it is necessary to test the result after every addition or left shift. If the result is greater than the required modulus subtract the modulus from the result and continue. The reduction is thus performed along with the multiplication. The algorithm is therefore:

- 1. Initialise the result to zero.

- Test the most significant bit of the first operand.If it is one add the second operand to the result.

- 3. If the result is greater than the modulus N subtract N from the result.

- 4. Shift the result to the left by one bit.

- 5. If the result is greater than N, subtract N from the result.

- 6. Repeat steps 2 to 6 for successively less significant bits of the first operand. Stop when all the bits have been tested.

A flowchart of this algorithm appears in Fig.(3.5a). A programme utilising this algorithm was written for the MC6809 and the run time is given as follows:

$$T_B = 66 + 197(N_B) + 768(N_B)^2$$

cycles.

where  $N_{\rm B}$  is the number of bytes in the modulus. A table showing the run time of this programme for various values of  $N_{\rm B}$  is given in Fig.(3.5b).

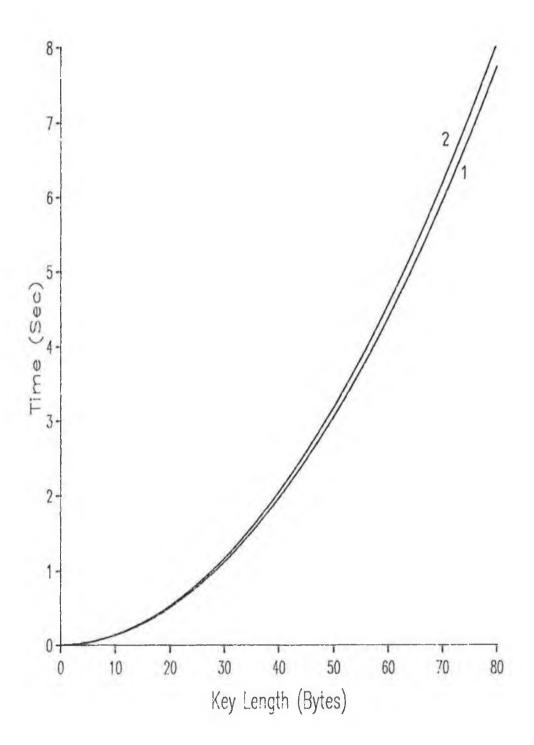

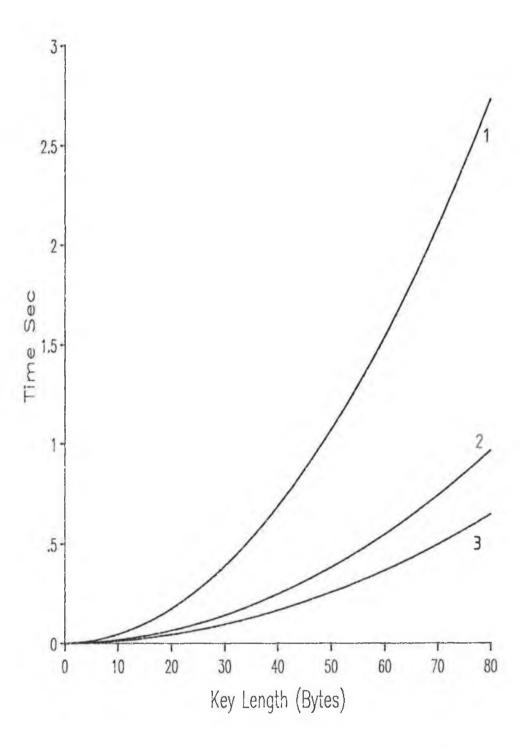

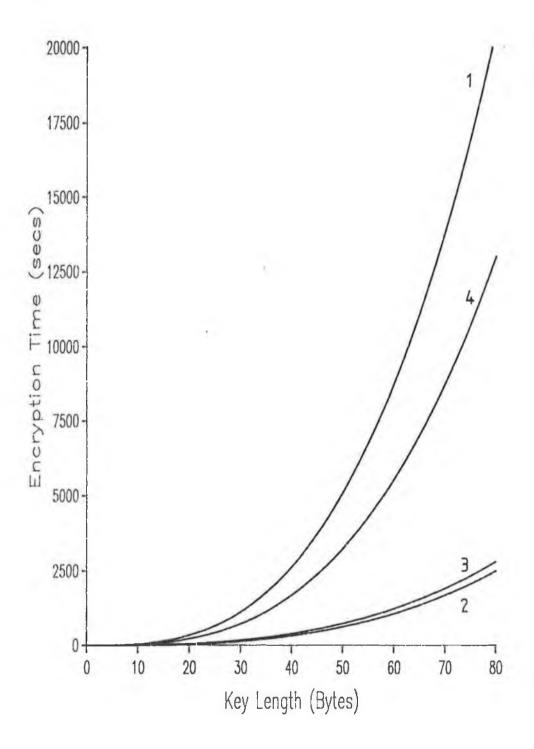

#### 3.5 ENCRYPTION TIME.

Various methods for performing modular multiplication have been described. It is now necessary to determine overall encryption times using each of these methods. The encryption algorithm is of the form:

$$C = M^e \mod N$$

C is the required ciphertext, M is the plaintext, e is the encryption key and N is the modulus. The length of C,M,e,N will be  $N_{\rm B}$  bytes where  $N_{\rm B}$  is of the order of 40 bytes or

more. The exponentiation algorithm has a run time of :

$$T_e = 53 + 2583(N_B) + 2432(N_B)^2 + 32(N_B)T_{Mod}[N_B]$$

cycles

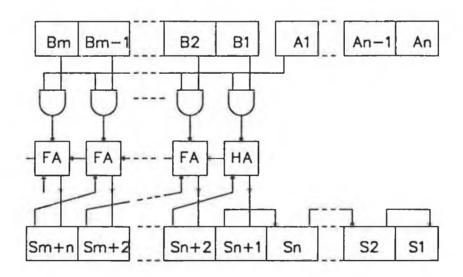

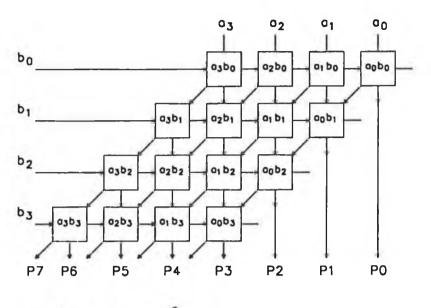

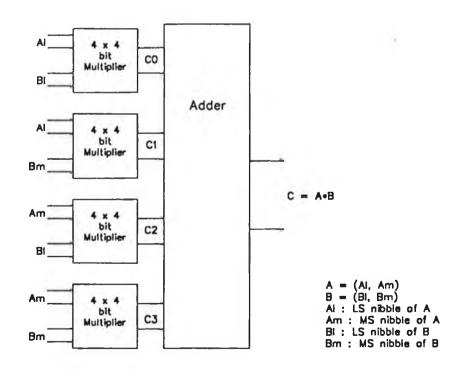

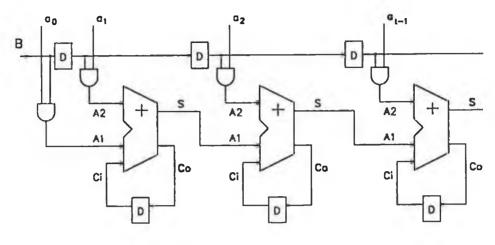

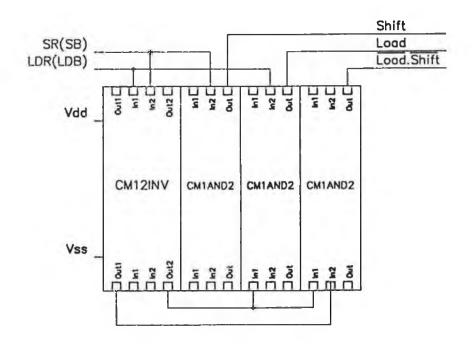

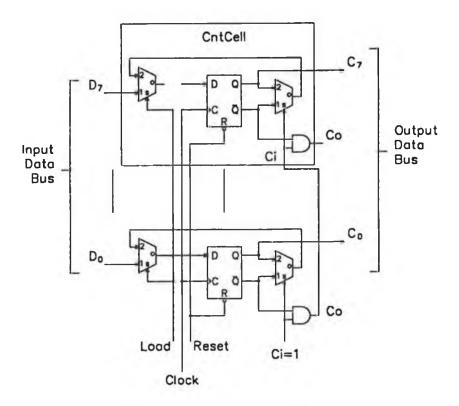

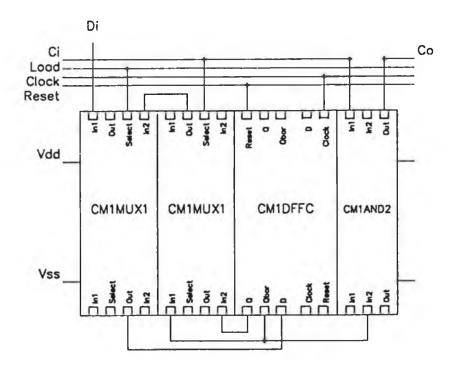

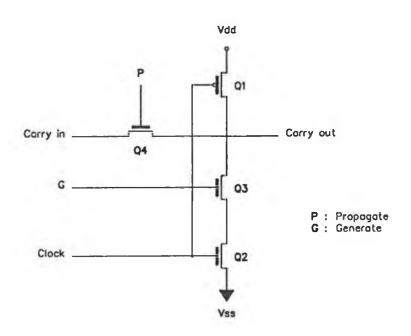

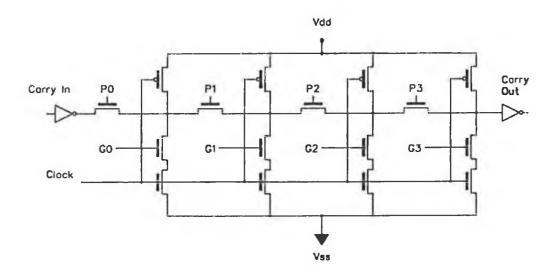

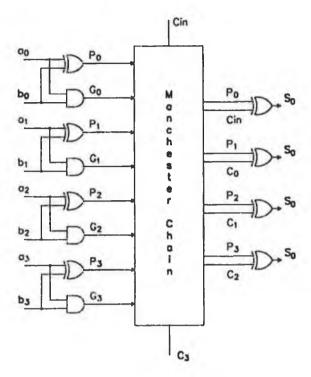

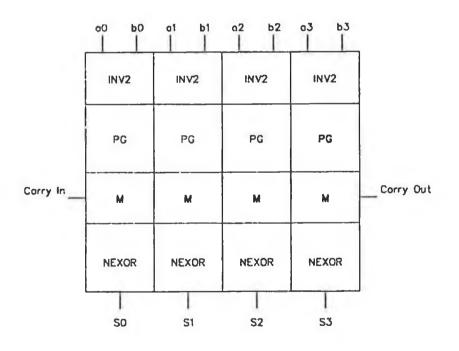

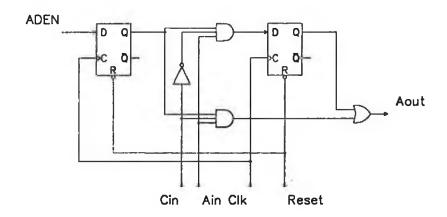

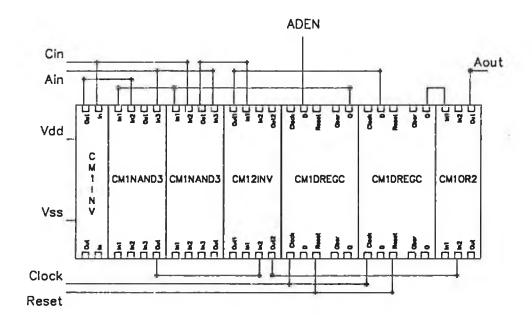

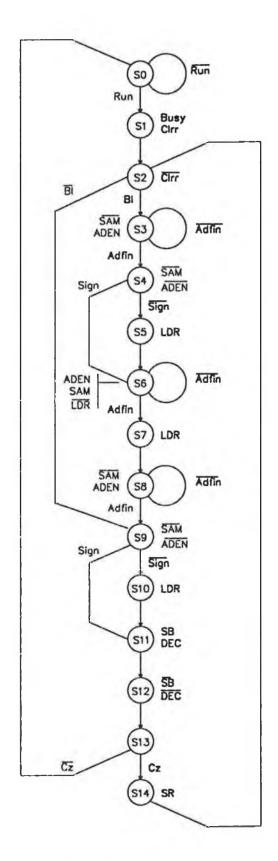

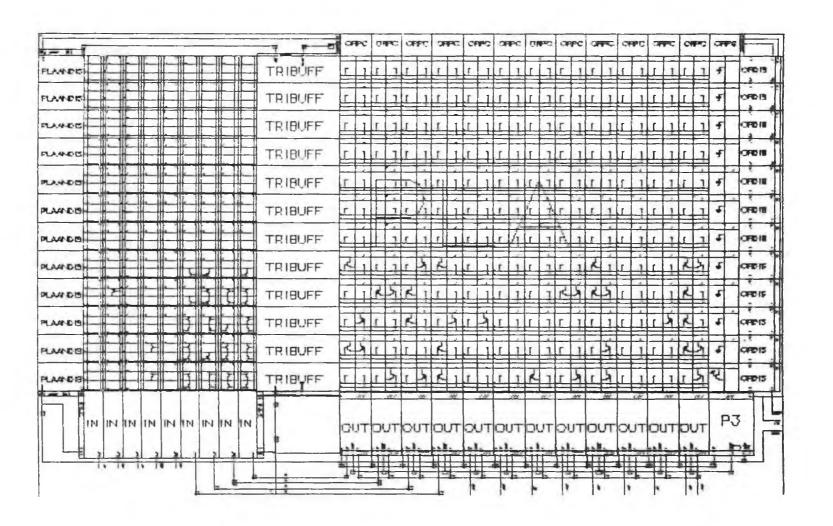

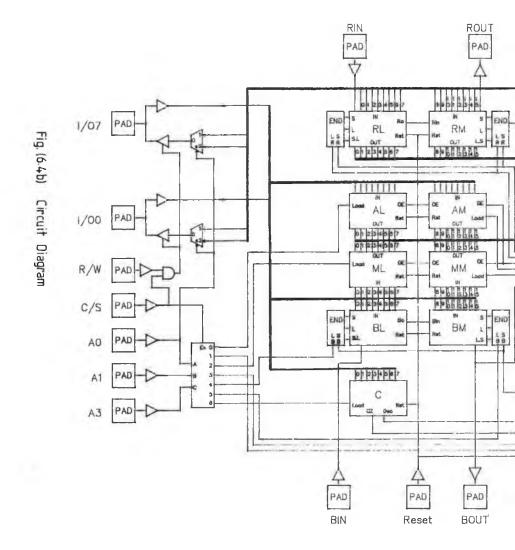

where  $T_{\mbox{Mod}}[N_{\mbox{B}}]$  is the time required to form the product of two  $N_{\mbox{B}}$  byte numbers modulo a third  $N_{\mbox{B}}$  byte number. Four methods of calculating such a product have been discussed: