# Single Event Effects (SEE) Testing of Embedded DSP Cores within Microsemi RTAX4000D Field Programmable Gate Array (FPGA) Devices

Christopher E Perez Melanie D. Berg Mark R. Friendlich MEI Technologies in support of NASA/GSFC August 2011

### **Outline**

- Motivation

- Device under test

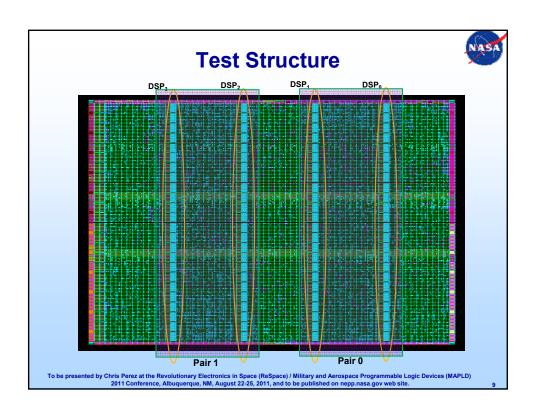

- Design of test structure

- Test setup

- Test results

- Conclusions

To be presented by Chris Perez at the Revolutionary Electronics in Space (ReSpace) / Military and Aerospace Programmable Logic Devices (MAPLD)

### **Motivation**

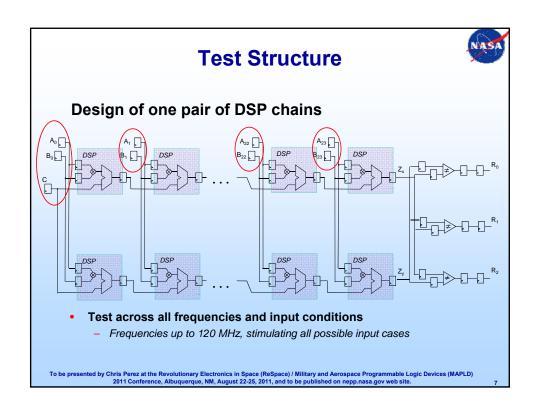

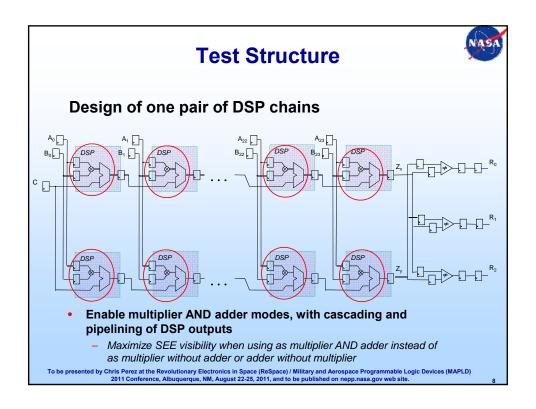

- Accurately characterize DSP core single-event effect (SEE) behavior

- Test DSP cores across a large frequency range and across various input conditions

- Isolate SEE analysis to DSP cores alone

- Interpret SEE analysis in terms of single-event upsets (SEUs) and single-event transients (SETs)

- Provide flight missions with accurate estimate of DSP core error rates and error signatures

To be presented by Chris Perez at the Revolutionary Electronics in Space (ReSpace) / Military and Aerospace Programmable Logic Devices (MAPLD) 2011 Conference, Albuquerque, NM, August 22-25, 2011, and to be published on nepp.nasa.gov web site.

Powice Under Test

Microsemi RTAX-DSP FPGAs

Output

# DSP Blocks 18x18 bit multiplier with 41-bit accumulator Option to register inputs and ouputs for up to 125 MHz operation Configure as one 18x18 multiplier or two 9x9 multipliers Cascading, arithmetic shift, and feedback capabilities SEU hardened by TMR of input and output registers SET mitigated by guard-gate at output of combinatorial logic with delay chain set to 750 ps delay SET mitigated by guard-gate at output of combinatorial logic with delay chain set to 750 ps delay To be presented by Chris Perez at the Revolutionary Electronics in Space (RSpace) / Miltray and Aerospace Programmable Logic Devices (MAPLD) 2011 Conference, Albuquerque, NM, August 22-25, 2011, and to be published on nepp.nasa gov web site.

## NASA

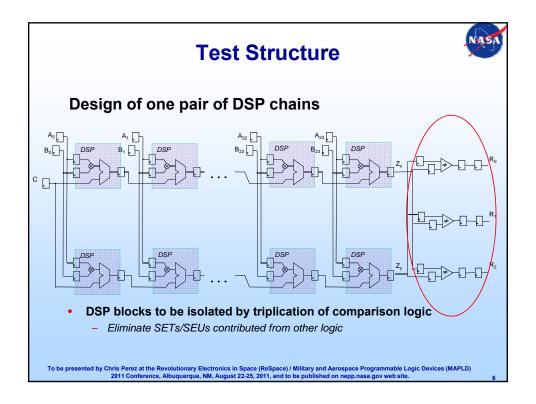

### **Error Conditions**

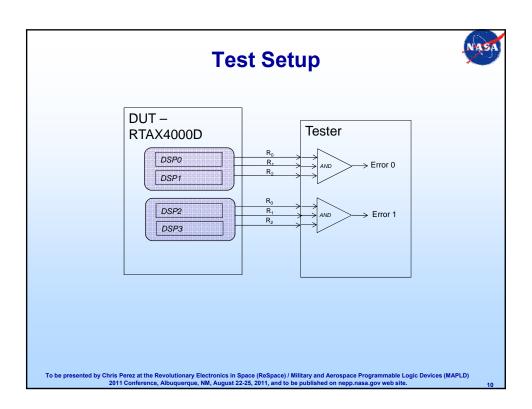

- SEU in any DSP block within a chain results in single-cycle upset at output of that chain

- Assume Z<sub>x</sub>, Z<sub>v</sub> are outputs of paired chains

- If Z<sub>x</sub> /= Z<sub>y</sub>, then within last 24 cycles, SEU occurred in one of 24 DSPs in chain X or in chain Y

- Comparison logic for  $Z_x$ ,  $Z_y$  is triplicated, producing output flags  $R_0$ ,  $R_1$ ,  $R_2$  all set high when  $Z_x$  /=  $Z_y$

- Flags R<sub>0</sub>, R<sub>1</sub>, R<sub>2</sub> are compared in tester, and when all set high, SEU detected in one of 48 DSPs within pair

- All other outcomes of R<sub>0</sub>, R<sub>1</sub>, R<sub>2</sub> are ignored as they don't represent SEUs in DSPs

To be presented by Chris Perez at the Revolutionary Electronics in Space (ReSpace) / Military and Aerospace Programmable Logic Devices (MAPLD) 2011 Conference, Albuquerque, NM, August 22-25, 2011, and to be published on nepp.nasa.gov web site.

**Example DSP Upset** Logic analyzer screenshot of actual SEU in DUT DSP cores captured by tester system Sampling clock is 2X frequency of maximum DSP operating frequency Intronix LogicPort Logic Analyzer - C: Wocuments and Settings Lab 1 Nesktop \ Test\_Data \ LBNL\_05\_2011 \ Mctel\_RTAX4000D \ logicport \ RTAX4000D\_DSP. File Options Setup Acquisition View Help Waveforms State List Notes 📴 🗅 🖫 🖨 🚻 🕸 🔡 🕨 📭 🔳 🗜 🐺 🔰 🕀 🔾 🎕 🦞 Buffer Position: ▼ 500MHz ▼ Logic Threshold Pre-Trigger Buffer Wire ID TMRO\_0 TMR1 0 D1 Π TMR2 0 TMR0 1 0 TMR1 1 0 TMR2 1 D5 0 NONZERO\_0 NONZERO 1 D7

### **Test Setup**

- A<sub>i</sub>, B<sub>i</sub>, C are all selected by separate 2-bit inputs

- 00 selects 0

- 01 selects +1

- 10 selects -1

- 11 selects a counter

- For first round of testing, A<sub>i</sub>, B<sub>i</sub> set to counter for all cases, C remained variable

- Test matrix:

| 1 MHz     | 15 MHz    | 30 MHz    | 60 MHz    | 120 MHz   |

|-----------|-----------|-----------|-----------|-----------|

| C=0       | C = 0     | C = 0     | C = 0     | C = 0     |

| 1 MHz     | 15 MHz    | 30 MHz    | 60 MHz    | 120 MHz   |

| C = +1    |

| 1 MHz     | 15 MHz    | 30 MHz    | 60 MHz    | 120 MHz   |

| C = -1    |

| 1 MHz     | 15 MHz    | 30 MHz    | 60 MHz    | 120 MHz   |

| C = count |

**Test Parameters**

- Heavy Ion Testing at LBNL

- Energy: 15 MeV

- Fluence: up to 4.0E+7, OR until significant number of upsets observed

- Fluxes

- 2.0E+5 to 2.3E+5 : Ne

9.7E+4 to 1.1E+5 : Ar

7.0E+4 to 1.0E+5 : Cu

- Angles of incidence tested : 0°, 45°, and 60°

- Effective LETs tested: 3.94 to 29.94 MeV·cm²/mg

o be presented by Chris Perez at the Revolutionary Electronics in Space (ReSpace) / Military and Aerospace Programmable Logic Devices (MAPLD)

14

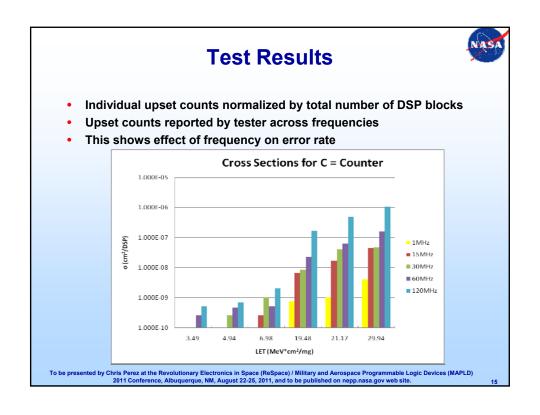

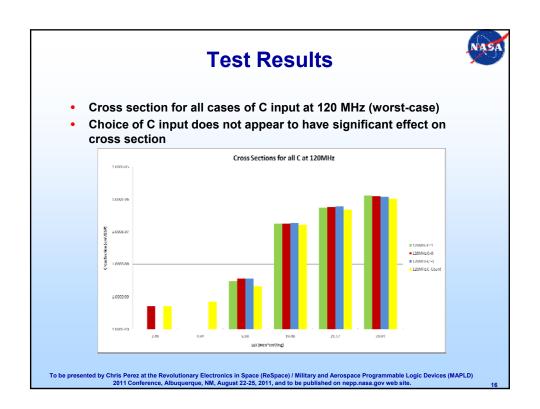

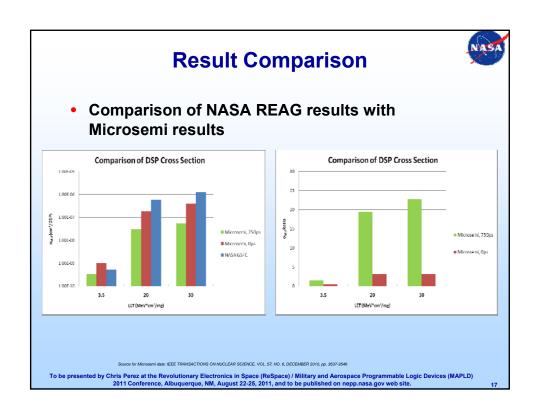

### **Test Analysis**

- Cross sections show similar characteristics as results obtained by Rezgui et. Al., although appear 10X higher for case of multipliers at 120MHz with 750ps guard gate delay

- Surprisingly, cross sections more closely match results obtained by Rezgui et. Al. for case of multipliers at 120MHz with 0ps guard gate delay

- Are SETs effectively being filtered by delay chain of 750ps and guard-gate?

### **Test Analysis**

NASA REAG SEE Model for FPGAs

$$P(fs)_{error} \propto P_{Configuration} + P(fs)_{functionalLogic} + P_{SEFI}$$

Probability for Design Specific system SEU: Probability for Configuration SEU SEU SEU SEU Probability for Functional logic Single Event Functional Interrupt

For RTAX-DSP target device...

$$P(f_s) \propto P(f_s)_{SET o SEU} \propto \sum_{i=1}^{41} P_{gen}(i) \times P_{prop}(i) \times \tau_{width}(i) \times f_s$$

$P_{configuration} \rightarrow 0 \quad P_{SEFI} \rightarrow 0 \quad P_{DFFSEU} \rightarrow 0$

To be presented by Chris Perez at the Revolutionary Electronics in Space (ReSpace) / Military and Aerospace Programmable Logic Devices (MAPLD) 2011 Conference, Albuquerque, NM, August 22-25, 2011, and to be published on nepp.nasa.gov web site.

### **Test Analysis**

- · Test results show that model is satisfied

- As frequency increases, transients more likely to be captured within setup-hold time window around clock edge

$$f_s \uparrow \Rightarrow P(f_s) \uparrow$$

Higher LETs imply transients more likely to propagate thru several levels of combinatorial logic to output registers

$$LET \uparrow \Rightarrow P_{prop} \uparrow \Rightarrow P(f_s) \uparrow$$

Higher LETs imply transients more likely to be generated within combinatorial logic of DSP block

$$LET \uparrow \Rightarrow P_{gen} \uparrow \Rightarrow P(f_s) \uparrow$$

Threshold LET seems higher than expected with SET mitigation via filtration by delay chain and guard gate design

To be presented by Chris Perez at the Revolutionary Electronics in Space (ReSpace) / Military and Aerospace Programmable Logic Devices (MAPLD)

20

### **Next Steps**

- Future testing to validate expected cross section saturation and threshold LET

- May limit testing to worst-case conditions (120 MHz) to increase data points

- Test at higher LETs to gather more data points and to observe if any potential DSP functional interrupts or global functional interrupts

- Test at all other input conditions (A<sub>i</sub>, B<sub>i</sub> coefficients set static instead of dynamic)

To be presented by Chris Perez at the Revolutionary Electronics in Space (ReSpace) / Military and Aerospace Programmable Logic Devices (MAPLD) 2011 Conference, Albuquerque, NM, August 22-25, 2011, and to be published on nepp.nasa.gov web site.

..

### **Acknowledgements/Closing**

- RTAX-DSP FPGA devices remain good choice for designers of DSP algorithms targeting FPGAs for space

- All upsets observed appear to stem from transient capture at output registers of DSP cores

- I'd like to thank Melanie Berg, Mark Friendlich, Hak Kim for their expertise, assistance during test planning, design, execution, and analysis

- Questions?

To be presented by Chris Perez at the Revolutionary Electronics in Space (ReSpace) / Military and Aerospace Programmable Logic Devices (MAPLD)

22