Todd C. MacLeod NASA Marshall Space Flight Center

NASA, Marshall Space Flight Center, Huntsville, AL 35812 Tel: (256) 544-2018 Email: todd.macleod@.nasa.gov

W. Herb Sims NASA Marshall Space Flight Center

Kosta A. Varnavas NASA Marshall Space Flight Center

Fat D. Ho University of Alabama Huntsville

INITIAL RESULTS FROM ON-ORBIT TESTING OF THE FRAM MEMORY TEST EXPERIMENT ON

## THE FASTSAT MICRO-SATELLITE OUTLINE

- 1. Introduction

- 2. Radiation Environment in Space

- 3. Effects of Radiation on Electronics

- 4. NASA's Efforts to Mitigate Radiation Effects on Electronics

- 5. Overview of the FASTSAT Satellite

- 6. Overview of the Memory Test Experiment

- 7. Initial Results from the Memory Test Experiment

- 8. Conclusions

## INTRODUCTION

- NASA is planning on going beyond Low Earth orbit with manned exploration missions

- The radiation environment for most Low Earth orbit missions is harsher than at the Earth's surface but much less harsh than deep space

- Development of new electronics is needed to meet the requirements of high performance, radiation tolerance, and reliability

- The need for both Volatile and Non-volatile memory has been identified

- Emerging Non-volatile memory technologies (FRAM, C-RAM, M-RAM, R-RAM, Radiation Tolerant FLASH, SONOS, etc.) need to be investigated for use in Space missions

- An opportunity arose to fly a small memory experiment on a high inclination satellite (FASTSAT)

- An off-the-shelf 512K Ramtron FRAM was chosen to be tested in the experiment

- Early NASA Manned missions used very simple and large feature size integrated circuits which were much less susceptible to radiation effects

- Unmanned deep space missions rely on redundant radiation tolerant electronics that have low mass efficiency and are low performance

- The Shuttle and Space Station rely on redundant older technology with Error Detection and Correction

- The three common ways to deal with radiation impacts to electronic systems in space are:

- Use radiation hardened devices that can operate in the planned environment

- Use Triple Module Redundancy (TMR). Three copies of each functional box and a voting system

- Use extensive Error Detection and Correction algorithms

- Projects usually use a combination of each of these methods

- The Problem with the three methods are:

- Most radiation hardened devices are high power, high weight, low performance

- Shielding helps to reduce the impact of lower energy particles but actually hurts with very high energy radiation

- The radiation is more likely to interact with High-Z materials and create worse secondary particles

- TMR increases weight, power, complexity and may introduce its own failure modes

- EDAC is useful for correcting small numbers of bit flips but it can't handle a swarm of errors

## **Radiation Environment in Space**

## The Radiation Environment

### Space Radiation affects all spacecraft.

- Spacecraft electronics have a long history of power resets, safing, and system failures due to:

- Long duration exposures,

- Unpredictable solar proton activity,

- Ambient galactic cosmic ray environment.

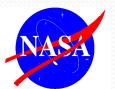

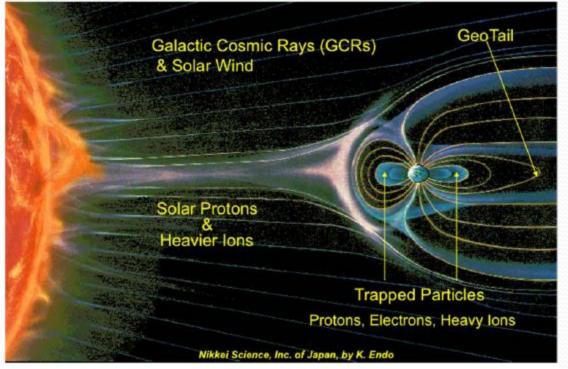

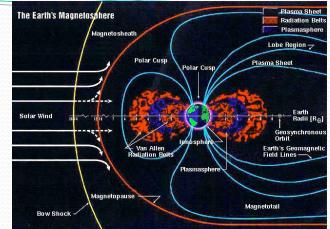

## **Space Environment Radiation Sources**

The main sources of energetic particles that are of concern to spacecraft designers are:

- protons and electrons trapped in the Van Allen belts,

- heavy ions trapped in the Earth's magnetosphere,

- cosmic ray protons and heavy ions of multiple elements, and

- protons and heavy ions from solar flares.

## South Atlantic Anomaly

NASA

outer zone

## **Maximum Energies of Particles**

| Particle Type                     | Maximum Energy* |

|-----------------------------------|-----------------|

| Trapped Electrons                 | 10s of MeV      |

| Trapped Protons &<br>Heavier Ions | 100s of MeV     |

| Solar Protons                     | 100s of MeV     |

| Solar Heavy Ions                  | GeV             |

| Galactic Cosmic Rays              | TeV and beyond! |

\* For engineering applications

Six ground-based experiments have reported a total of 22 events >10<sup>20</sup> eV (super-Greisen-Zatsepin-Kuzmin (GZK) events) during the last 40 years:

This corresponds to a flux of about one event per km<sup>2</sup> per century.

### **Radiation Effects on Electronics**

### Long-Term Electronic Damage Mechanisms:

### Total Ionizing Dose (TID) Damage

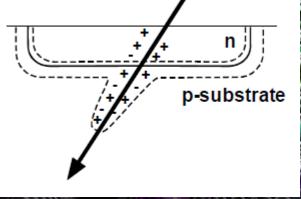

- Radiation causes lattice ionization, generating migratory carrier traps.

- Traps can permanently collect near interfaces, causing leakage currents and increased threshold voltage shifts.

- Multiplied by millions, leakage currents can cripple a device.

### Enhanced Low Dose Rate Sensitivity (ELDRS):

- Affects linear bipolar devices.

- Damage often done in unpowered mode.

## **Radiation Effects on Electronics**

## Short-Term Electronic Damage Mechanisms:

### Transient Ionization Effects

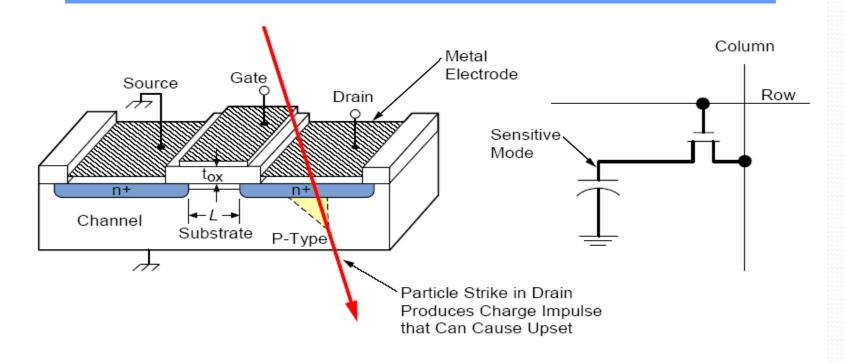

- High energy particles ionize the surrounding atoms, generating charges that propagate and collect. In digital circuitry, this can result in a Single Event Effect (SEE). Many types of SEEs have been characterized:

- Single-Event Upsets (SEU): transient state changes of memory or register bits caused by a single ion interaction.

- Single-Event Latch up (SEL): high energy ion or proton forces a latched state that is held until power cycled. If the state causes high current flow, permanent damage can occur.

- Single-Event Transient (SET): charge collected from an ionization event results in a spurious signal propagating through the circuit.

- Single-Event Induced Burnout (SEB): occurs in power MOSFETs when ionization causes the breakdown voltage to be exceeded and high current risks destroying the device.

- Single-Event Gate Rupture (SEGR): occurs in power MOSFETs when a heavy ion hits the gate region while a high voltage is applied to the gate, causing a short through the gate oxide and permanent device destruction.

### Pad/Launch

- Galactic Cosmic Rays in Upper Atmosphere

- Atmospheric Neutrons

### In-Space

- Trapped Particles

- Galactic Cosmic Rays

- Solar Particle Events

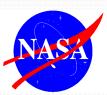

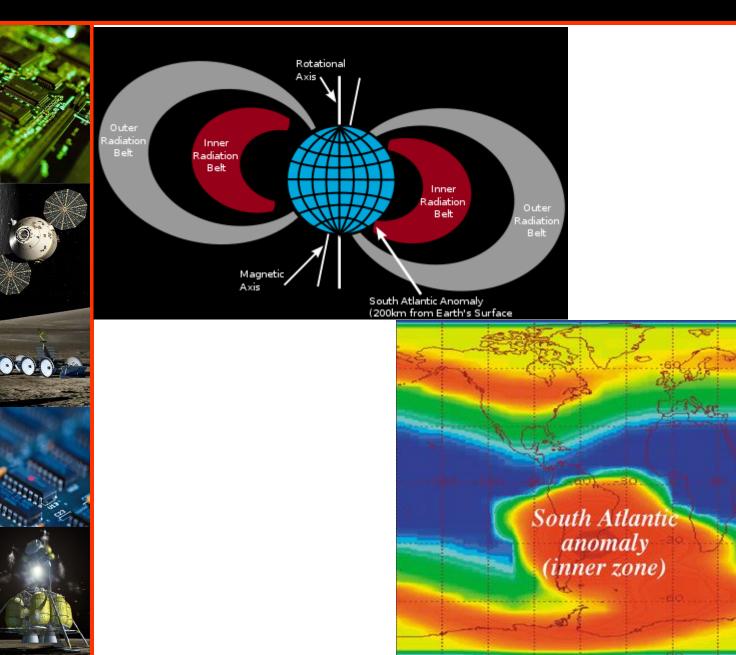

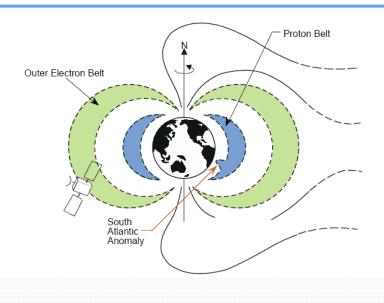

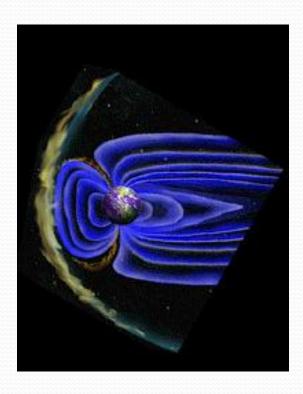

•The trapped radiation belts have two distinct regions

- •The outer Electron belt

- •The inner Proton belt •Because of the interaction of the Earth's magnetic field, the spin of the Earth and the Solar Wind, The Proton belt comes closest to the surface in

the South Atlantic

•The South Atlantic Anomaly (SAA) is a large source of single event upsets in Low Earth Orbit spacecraft

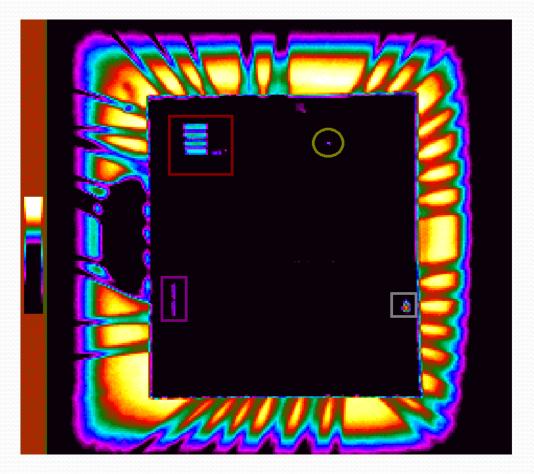

#### Trapped Radiation Belts around Earth

Radiation effects are not evenly distributed for Low earth Orbits

Data shows that most upsets occur in the South Atlantic Anomaly or near the Poles

This is because of the increased Proton flux in the SAA and the Galactic Cosmic Ray (GCR) increase near the poles

GCR increase near the pole because they are charge particles which tend to not cross magnetic field lines. At the poles the magnetic field lines are perpendicular to the Earth so the GCRs can strike the upper atmosphere

## **Radiation Effects on Electronics**

## Summary of Radiation Types

| Radiation Source        | Particle Type                                              | Primary Effects                        |

|-------------------------|------------------------------------------------------------|----------------------------------------|

| Trapped radiation belts | Electrons<br>Protons                                       | Ionization damage;<br>Ionization, SEE. |

| Galactic Cosmic Rays    | High-energy, heavy,<br>charged particles                   | SEE                                    |

| Solar Flares            | Electrons<br>Protons<br>Lower-energy, charged<br>particles | lonization<br>lonization, SEE<br>SEE   |

## **Radiation Effects**

- Total Ionizing Dose

- Single Event Effects (SEE)

- SEU Single event upsets

- SEL Single event latchups

- Displacement Damage

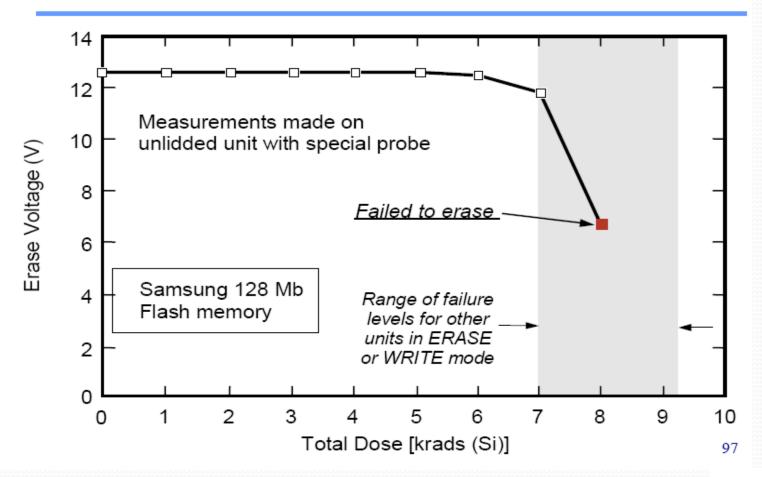

## Total Ionizing Dose (TID)

- Measured in rads

- Radiation Absorbed Dose

- SI unit is the gray (Gy);

- 1 Gy = 100 rads = 1 J/kg

- Typical part tolerance

- COTS 5-20Krad

- Foundry plays an important role.

- Rad Tolerant 100Krad

- Rad Hardened 1Mrad

## Single Event Effects (SEEs)

- SEE is caused by a single high-energy particle disrupting charge flow/storage in electronic circuits.

- Galactic cosmic rays.

- Solar flare events.

- High energy protons in belts.

- Roughly four types of SEE

- Single-event upset (SEU) a soft error.

- Single-event latchup (SEL) a soft or hard error.

- Single-event burnout (SEB) a hard failure.

- Single-event functional interrupt (SEFI) soft/hard error.

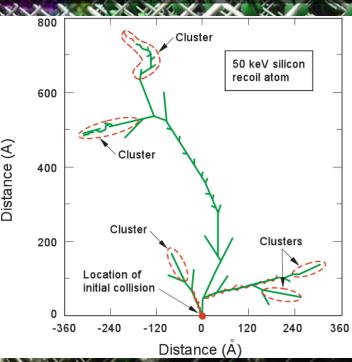

## **Displacement Damage**

- Crystal lattice deformed by particle interactions.

- Particles:

- Protons, electrons, neutrons.

- Mobility of carriers, especially minority, affected by DD.

- Sensitive parts:

- Bipolar

- Optical components (LEDs, optocouplers).

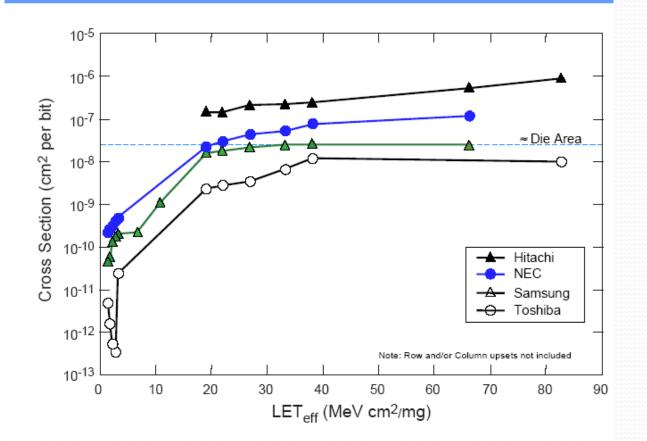

### Upset Mechanism for DRAMs

Single-Event Upset in 64-Mb DRAMs

### **Flash Memories**

- The error rate observed can suddenly jump during a Solar flare event

- The proton flux can increase by a factor of one hundred in a few hours

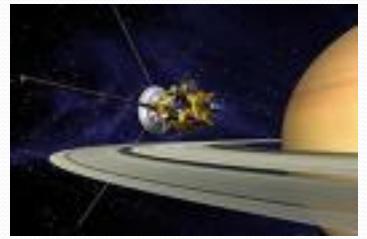

- The Memory errors detected by the Cassini spacecraft increased by a factor of 15

- The memory error rate hit 150 per hour

### Cassini SSR Errors During Solar Flare

# NASA Efforts to Mitigate Radiation Effects on Electronics

## NASA Efforts to Mitigate Radiation Effects on Electronics

### Radiation Effects & Analysis Group

•Located at NASA Goddard Space Flight Center, Greenbelt Maryland – Manager Ken LaBel

### • Electronics Radiation Characterization (ERC) project

•Run at GSFC and Jet Propulsion Laboratory

•Provides radiation evaluation of cross-cutting technologies

•Examples: COTS, emerging microelectronics, photonics

Provides guidelines for technology usage

•Example: optocoupler usage

•Supports radiation-specific issues to provide increased reliability and reduced costs

•Example: radiation test methods

### •Space Radiation Physics Office (SRPO)

Characterizes the radiation environment

# Advanced Avionics and Processor Systems Project

UAH

**Exploration Technology Development Program**

Advanced Avionics and Processor Systems (AAPS) for Space Exploration

-0.00

The Advanced Avionics and Processor Systems (AAPS) project expands the current state-of-the-art in spacecraft avionics components and processor systems to develop high performance devices for long duration exposure to the space and lunar environments.

- The specific project goals of the AAPS project are to foster technology development efforts in radiation-hardened electronics possessing these associated capabilities:

- improved Total Ionization Dose (TID) tolerance,

- reduced Single Event Upset (SEU) rates,

- increased threshold for Single Event Latch-up (SEL),

- increased sustained processor performance,

- increased processor efficiency,

- increased speed of dynamic reconfigurability,

- reduced operating temperature range's lower bound,

- increased the available levels of redundancy and reconfigurability, and

- increased the reliability and accuracy of radiation effects modeling.

- Through recent NASA reorganizations, The AAPS project is now part of Exploration Technology Development and Demonstration program

- The level of funding is uncertain but likely reduced

## AAPS Tasks

## AAPS tasks:

- Model of Radiation Effects on Electronics (MREE),

- Lead Center: MSFC

- Participants: Vanderbilt University

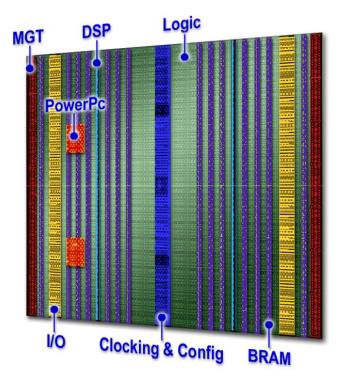

- Single Event Effects (SEE) Immune Reconfigurable Field Programmable Gate Array (FPGA) (SIRF),

- Lead Center: GSFC

- Participants: AFRL, Xilinx

- Radiation Hardened High Performance Processors (HPP),

- Lead Center: GSFC

- Participants: LaRC, JPL, Multiple US Government Agencies

- Reconfigurable Computing (RC),

- Lead Center: MSFC

- Silicon-Germanium (SiGe) Integrated Electronics for Extreme Environments.

- Lead Center: LaRC

- Participants: Georgia Tech. leads multiple commercial and academic participants.

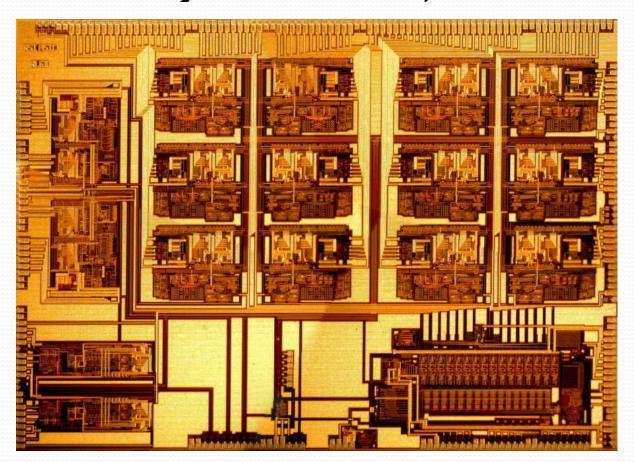

- Radiation-Hardened Volatile and Non-Volatile Memory

- Lead Center: MSFC

- Participants: LaRC, Multiple Vendors

## HPP Accomplishments

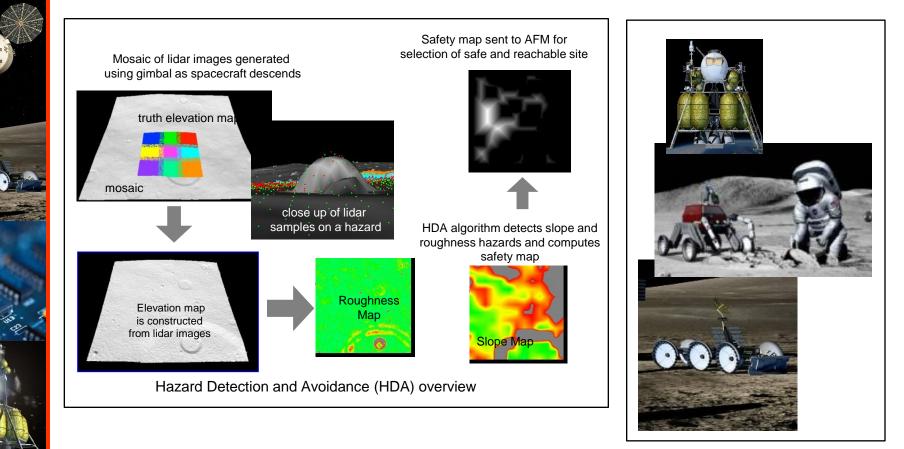

### Objective:

- Assess performance and susceptibilities of high-performance processor options

- Focus on HyperX (Hx) and Tilera options

- Recommend high performance processor for ALHAT (and other) capabilities

- Assess options for (ultra) low-power embedded processors for LSS, EVA capabilities

## SIRF Accomplishments

### Key Status /Accomplishment/Deliverable/Milestone

- FX1 engineering prototype component was fabricated and is under test

- The FX1 chip has been successful in achieving its goals

- No functional anomalies have been found at all\

- The design-hardened chip should run at full commercial speed

- Customers are strongly urging Xilinx and AFRL to come out with a product quickly

- Program will likely proceed to productization with only minor changes to FX1

The SIRF program is lead and majority funded by the Air Force Research Laboratory

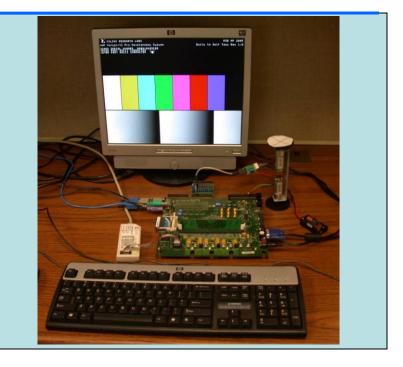

## **Reconfigurable Computing Accomplishments**

### Objective:

Radiation-Hardened Electronics for Space Environments (AAPS) Reconfigurable Computing (RC) task Demonstration #1 was to show basic manual reconfiguration of the test hardware into three substantially different computing resources.

#### Key Accomplishments

Basic concepts of RC were showcased at MSFC. Coupled with the demo was an informative slideshow with background information, a description of goals and activities of the demonstration itself, and plans for future research and demonstrations of progressively more complex RC concepts and capabilities. This concentrated on very basic demo manual reconfiguration of the test hardware into three substantially different computing resources. These were: microprocessor, digital signal processor and motor control/feedback setups.

#### Significance:

- Establishes a foundation for RC upon which further demonstrations of internal reconfiguration, external reconfiguration, and fault recognition functions will build.

- Provides crucial publicity of RC efforts within NASA and the technical community at large; weighs heavily in efforts to garner significant technical and fiscal support for RC.

### Shown: Hardware for RC Demo #1

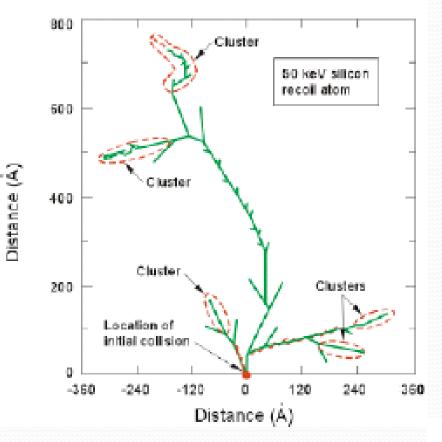

### MREE Accomplishments

#### Objective:

Develop a revised model for estimating radiation effects on spacecraft electronics.

Motivation for this Task:

- The paradigm used in CREME96 and other models of that generation do not account for the feature sizes and complexities of modern electronic components. Key Accomplishment/Deliverable/Milestone:

- > 27 February 2009

- Completed Maturation Plan

- > 31 March 2009

- Selected Revised Cosmic Ray Model

- > 2 April 2009

- Charge transport and collection models defined

- 1 June 2009

• Legacy CREME96 Model On-line at Vanderbilt Significance:

- Well defined plan for maturing the revised model

- Selected the most accurate galactic cosmic ray model by comparison with an extensive database.

- Developed a model for charge transport and collection by a microelectronic circuit following an ionizing particle strike that approximates a full TCAD calculation

- Put CREME96 on line at Vanderbilt University in order to preserve access to it after the NRL host goes down.

CRÈME-MC Device Model from the Vanderbilt WWW Site

https://creme-mc.isde.vanderbilt.edu/

# SiGe Accomplishments

# "SiGe Integrated Electronics for Extreme Environments"

### Scope:

Develop and Demonstrate Extreme Environment Electronic Components Required for Distributed Architecture Lunar / Martian Robotic / Vehicular Systems Using <u>SiGe Technology</u>

### Extreme Environment Requirements: (e.g., Lunar)

- +120C (day) to -180C (night) + cycling

- radiation (TID + SEE tolerant, SEL immune)

### Accomplishments:

- develop mixed-signal electronics with proven wide T + radiation capability

- deliver compact modeling tools for circuit design (design suite)

- deliver SiGe mixed-signal circuit components (component library)

- <u>deliver</u> robust packaging for ICs (integrated multi-chip module)

- <u>deliver</u> a SiGe Remote Electronics Unit (REU) sensor interface prototype

- demonstrate device + circuit + package reliability per NASA specs

- develop a robust infusion path for NASA mission insertion (TRL-6)

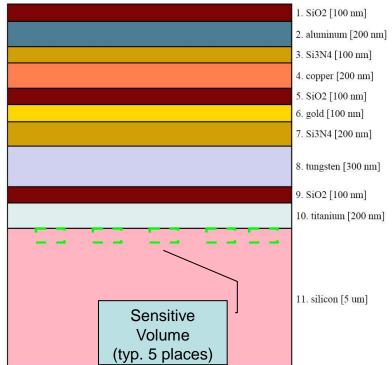

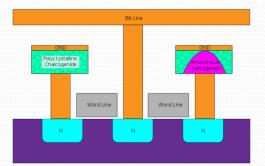

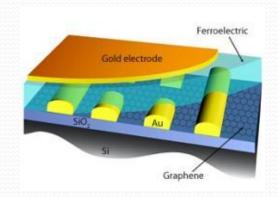

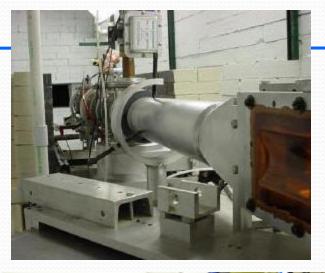

•The Radiation Hardened Memory project conducts research and development into radiation tolerant volatile and non-volatile memory devices in support of NASA's Exploration Technology Development Program

•We have laboratories at Marshall Space Flight Center and at Langley Research Center for testing memory devices

•We characterize memory devices for performance, temperature effects, and radiation effects

- Technologies that have been tested include

- •Ferroelectric memory

- •Phase Change memory

- Silicon-on-Insulator based memory

- SONOS Memory

- •Rad Hard SRAM

### **Radiation Hardened Memory Accomplishments**

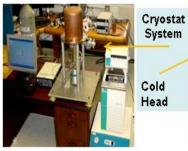

### Objective: Characterize and develop volatile and nonvolatile radiation tolerant memory

The Memory Test Laboratory was completed and started testing memory devices. It has the capability of characterizing several different memory technologies. It can also perform thermal testing at high temperatures and extremely low temperatures with the use of a helium cryostat. This facility is now online and has started testing Silicon-On-Insulator technology and Phase Change memory devices

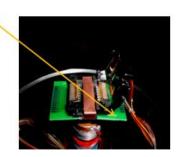

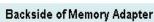

#### Pictures from LaRC Memory Test Lab

#### Electronics Board Sockets for Memory Devices

**Thermally Conducting Adapter** for Memory Devices

Thermally Conducting Memory Characterization Set-up Arrangement on Top of Cold Head

# **Overview of the FASTSAT Satellite**

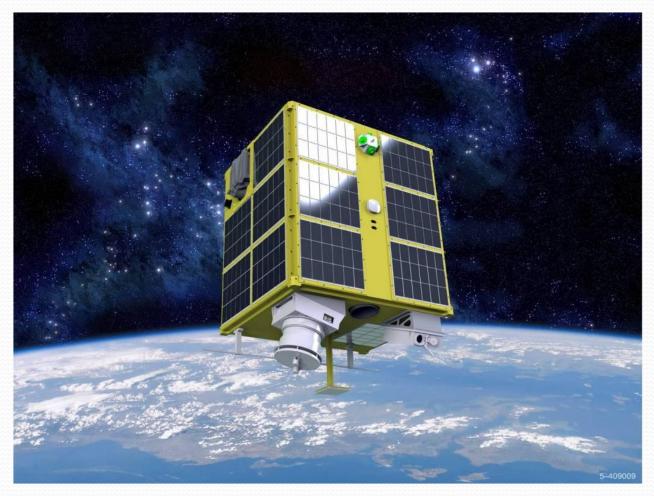

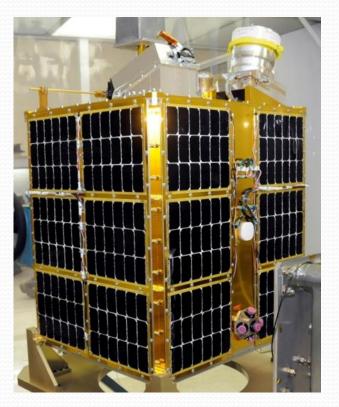

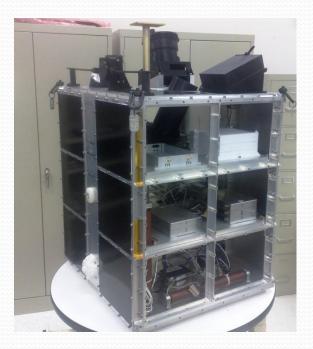

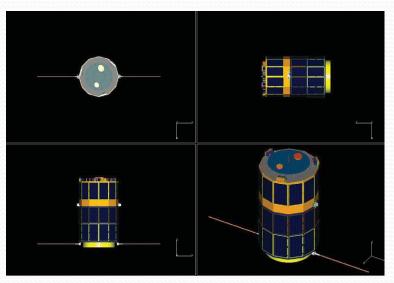

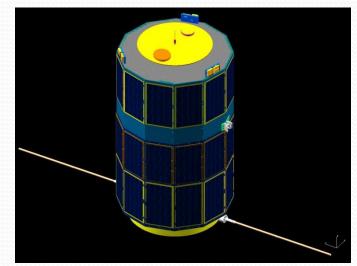

- Fast and Affordable Science and Technology SATellite (FASTSAT)

- The FASTSAT Satellite is a NASA developed low cost high capability satellite bus

- It was developed in a short amount of time (approximately 18 months)

- It can support a wide variety of payloads

- The first mission is a joint Department of Defense and NASA mission with six separate payloads

- The orbit for the first mission is approximately 600 kilometer circular altitude with an inclination of approximately 75 Degrees

- The first launch was November 19, 2010

- The satellite is approximately 36" in each dimension and weighs approximately 250 pounds

- The satellite bus was designed and developed at Marshall Space Flight Center in Huntsville Alabama in conjunction with the Von Braun Center for Science and Innovation and Dynetics Inc.

- The hardware consists of mostly off the shelf parts with some custom designs

- The FASTSAT Satellite is designed to provide a bus for a wide variety scientific and technology payloads

- It can provide a platform for optical, RF, and other instruments as well as deploying up to 3 cubesats

- The satellite is 3 axis stabilized and provides approximately 1 degree attitude accuracy

- The design principle was to keep it simple

- No mechanisms (except for separation ring)

- No moving parts

- Body mounted solar panels

- No reaction wheels (all magnetic torque rods)

- Fixed patch antennas

- Flexible Payload mounting locations

- Simple data and power interfaces

- The FASTSAT Satellite was launched on November 19, 2010 aboard a Minotaur IV rocket from Kodiak Launch Complex on Kodiak Island, Alaska

- It continues to successfully operate

# **Overview of the Memory Test Experiment**

•The RF communication system required a custom design to interface the flight computer to the transmitter

•The opportunity presented itself to include a new memory technology device for space environment testing

•An off-the-shelf 512K Ramtron

Ferroelectric RAM was chosen because of immediate availability and ease of integrating with the existing circuit

•The device is not used for any functions of FASTSAT.

•Failure of the device will not affect other operation of FASTSAT and its payloads

### • FM24C512

#### • 512Kbit Ferroelectric Nonvolatile RAM

- Organized as 65,536 x 8 bits

- High Endurance 10 Billion Read/Writes

- 45 year Data Retention

- NoDelay<sup>™</sup> Writes

- Advanced High-Reliability Ferroelectric Process

#### Fast Two-wire Serial Interface

- Up to 1 MHz Maximum Bus Frequency

- Supports Legacy Timing for 100 kHz & 400 kHz

- Low Power Operation

- 5V Operation

- 250 uA Active Current (100 kHz)

- 120 uA Standby Current

#### • Industry Standard Configuration

- Industrial Temperature -40°C to +85°C

- 8-pin "Green"/RoHS EIAJ SOIC Package

### Memory Test Experiment Operations

•A random number is generated by the flight computer during each power up and sent to the communications board to be used in telemetry encoding

•The first 8 bits is stored in each memory location in the FRAM device

- •Every 6 minutes the microcontroller on the communications card reads each memory cell and compares it to the reference pattern

- •For each non-matching cell, the address and time is stored and down linked later.

- •Each time the flight computer is reset a new test pattern is stored

### Memory Test Experiment Operations

- •The data is be transmitted to the ground within 24 hours of being recorded

- •The data is sent to the National Space Science and Technology Center.

- •NASA and University of Alabama Huntsville personnel will analyze the data

- •The detected errors will be categorized into several categories

- 1. Error in writing to the memory cell (Silicon or Ferroelectric)

- 2. One time error in reading memory cell (Silicon)

- 3. Change of state of memory cell (Ferroelectric)

- 4. Permanent pinned state of memory cell (Silicon or Ferroelectric)

- The position of the satellite at the time of the error will be calculated to determine the radiation environment

- Space Weather data will be obtained to identify and unusual solar activity

- The position of the memory cell on the chip will be identified to understand any clustering of errors

### Memory Test Experiment Operations

•The categorized detected errors have the following characteristics:

- 1. Error in writing to the memory cell (Silicon or Ferroelectric)

- The first read after write is a mismatch and it never changes

- 2. One time error in reading memory cell (Silicon)

- The initial read matches the test pattern then a single read mismatches and the subsequent read matches

- 3. Change of state of memory cell (Ferroelectric)

- The initial read matches the test pattern then a read mismatches and the subsequent read mismatch

- 4. Permanent pinned state of memory cell (Silicon or Ferroelectric)

- The bit is always in one state no matter what is written to it

- This data will be used to determine the radiation effect characteristics of the ferroelectric material as compared to the silicon material.

- This data will be used to determine if existing designs of ferroelectric memory offer the needed radiation tolerance for NASA missions

Radiation Testing the Memory Test Experiment for the Fast and Affordable Science and Technology Satellite at Indiana University.

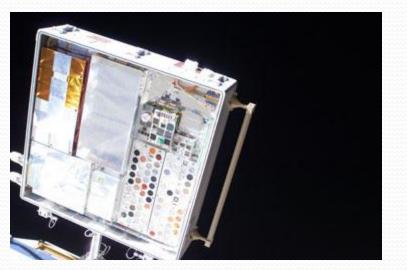

• The Memory Test Experiment (MTE) was tested under proton radiation at Indiana University. The test was conducted to verify the FASTSAT avionics. The MET is incorporated into the telemetry board of the FASTSAT avionics. The test consisted of putting the avionics boards into the proton beam and testing them with power on and off. Energy levels were up to 200 KeV with the dose of 115 rads. The telemetry board passed the radiation testing and no errors were recorded Telemetry in the ferroelectric memory devices. Board

### **Other Space Tests of Ferroelectric Memory**

•The FERRO experiment was an experiment developed by the Naval Postgraduate School in Monterey California

> •This experiment was to test ferroelectric capacitors to determine the effect of space radiation this was part of the Advanced Photovoltaic And Electronic Experiments (APEX) Mission

It is launched into a 195 Km by 1377 Km orbit at 70 degrees inclination on August 3, 1994

•A undetected software error caused the data gathered not to be transmitted for the experiment

### **Other Space Tests of Ferroelectric Memory**

•The Ferroelectric Reflectarray Critical Components Experiment (F-Recce) was developed by NASA Glenn Research Center

•This experiment will provide data on the long-duration performance of critical components associated with Glenn's novel Reflectarray Antenna--an antenna that can redirect its main beam without physically repositioning itself

•F-RECCE was launched on the Shuttle on May 16, 2011 as part of the Materials on the International Space Station Experiment (MISSE-8)

•The Ferroelectric Relectarray was developed by Robert Romanofsky and Felix Miranda of NASA

### **Other Space Tests of Ferroelectric Memory**

•The NPSAT1 is a satellite developed by the Naval Postgraduate School in Monterey California

It was scheduled to be launched in December 2009 but has been delayed to no earlier than January 2012

The satellite uses two rad-hard UTMC80C196KD micro-controllers that contain 8k ferroelectric RAM

The Principal Investigator is Rudolf Panholzer

# Initial Results FROM ON-ORBIT TESTING OF THE FRAM MEMORY TEST EXPERIMENT ON THE FASTSAT MICRO-SATELLITE Initial Data from the Memory Test Experiment Experiment

### Initial Data Results

• The Good News

- The Good News

- There have been no single or multi-bit errors detected by the Memory Test Experiment as of July 24, 2011

- The Good News

- There have been no single or multi-bit errors detected by the Memory Test Experiment as of July 24, 2011

- The Bad News

- The Good News

- There have been no single or multi-bit errors detected by the Memory Test Experiment as of July 24, 2011

- The Bad News

- There have been no single or multi-bit errors detected by the Memory Test Experiment as of July 24, 2011

- Comparison of FeRAM error results with other memory on the FASTSAT Satellite

- The main flight computer has a Applied Micro Circuits Corporation Power PC PPC405GPr Embedded Processor with 128 MB of SDRAM

- The computer has an embedded Error Detection and Correction process that corrects all single bit errors every 15.2 micro-seconds

- The processor also detects (but does not correct) all 2-bit errors every 15.2 micro-seconds

- The telemetry down-linked from the satellite does not report EDAC corrections or 2-bit error detections

- No computer lock-ups or other effects have been reported as arising from memory errors. This could be because only single bit errors have occurred or (more likely) that multi-bit errors have occurred, but not in data that would crash the computer (For example: It is hard to tell if one bit is flipped in an image file)

- Comparison of FeRAM error results with other memory on the FASTSAT Satellite

- The Remote Data Acquisition (RDAQ) Modules act as I/O controllers for all sub-systems

- The RDAQs were designed by NASA personnel and use an embedded micro-controller with SDRAM

- The RDAQs were radiation tested in an accelerator at Indiana University and successfully passed all radiation tests

- There have been at least 3 instances where an RDAQ (8 RDAQs on FASTSAT) has locked up (likely due to a Single Event Upset due to radiation)

- This shows that the lower energy proton testing on the ground does not always replicate the effects seen in the full spectrum of energies seen in space

# Conclusions

- Radiation effects on spacecraft is significant and becoming worse with miniaturization of components

- NASA's new exploration missions need to handle the radiation environments of deep space

- Ferroelectric based memory has shown radiation tolerance in testing on Earth and in space

- The Memory Test Experiment has demonstrate the radiation impacts on a ferroelectric memory device in a high inclination Low Earth Orbit

- Data analysis will try to determine if any future detected errors are caused by the ferroelectric material or the other silicon parts within the device

# Acknowledgements

- Thanks to the National Space Science and Technology Center, Huntsville Alabama for providing the equipment and laboratories for testing

- Thanks to the FASTSAT project team for allowing this experiment to be incorporated into the satellite

# References

- Harsh Environments: Space Radiation Environment, Effects, and Mitigation, *Richard H. Maurer, Martin E. Fraeman, Mark N. Martin, and David R. Roth* Johns Hopkins APL Technical Digest, Volume 28, Number 1, 2008

- Observations of radiation in the space radiation environment and its effect on commercial off-the-shelf electronics in low-Earth orbit, Craig I. Underwood, *Phil. Trans. R. Soc. Lond. A*, 2003,193-197

- Space Radiation Effects on Microelectronics, Sammy Kayali, NASA GSFC, 2009

- Radiation Hardness Assurance (RHA) for Space Systems, Christian Poivey, *EPFL Space Center*, *June 2009*

- Overview of the Naval Postgraduate School Small Satellite, NPSAT1 Prater, D Sakoda, LA Grant, 22nd AIAA International Communications Satellite Systems Conference & Exhibit 2004