NASA/TM-2010-216834

# Fault Injection and Monitoring Capability for a Fault-Tolerant Distributed Computation System

Wilfredo Torres-Pomales, Amy M. Yates, and Mahyar R. Malekpour Langley Research Center, Hampton, Virginia Since its founding, NASA has been dedicated to the advancement of aeronautics and space science. The NASA scientific and technical information (STI) program plays a key part in helping NASA maintain this important role.

The NASA STI program operates under the auspices of the Agency Chief Information Officer. It collects, organizes, provides for archiving, and disseminates NASA's STI. The NASA STI program provides access to the NASA Aeronautics and Space Database and its public interface, the NASA Technical Report Server, thus providing one of the largest collections of aeronautical and space science STI in the world. Results are published in both non-NASA channels and by NASA in the NASA STI Report Series, which includes the following report types:

- TECHNICAL PUBLICATION. Reports of completed research or a major significant phase of research that present the results of NASA programs and include extensive data or theoretical analysis. Includes compilations of significant scientific and technical data and information deemed to be of continuing reference value. NASA counterpart of peerreviewed formal professional papers, but having less stringent limitations on manuscript length and extent of graphic presentations.

- TECHNICAL MEMORANDUM. Scientific and technical findings that are preliminary or of specialized interest, e.g., quick release reports, working papers, and bibliographies that contain minimal annotation. Does not contain extensive analysis.

- CONTRACTOR REPORT. Scientific and technical findings by NASA-sponsored contractors and grantees.

- CONFERENCE PUBLICATION. Collected papers from scientific and technical conferences, symposia, seminars, or other meetings sponsored or co-sponsored by NASA.

- SPECIAL PUBLICATION. Scientific, technical, or historical information from NASA programs, projects, and missions, often concerned with subjects having substantial public interest.

- TECHNICAL TRANSLATION. Englishlanguage translations of foreign scientific and technical material pertinent to NASA's mission.

Specialized services also include creating custom thesauri, building customized databases, and organizing and publishing research results.

For more information about the NASA STI program, see the following:

- Access the NASA STI program home page at <u>http://www.sti.nasa.gov</u>

- E-mail your question via the Internet to <u>help@sti.nasa.gov</u>

- Fax your question to the NASA STI Help Desk at 443-757-5803

- Phone the NASA STI Help Desk at 443-757-5802

- Write to: NASA STI Help Desk NASA Center for AeroSpace Information 7115 Standard Drive Hanover, MD 21076-1320

NASA/TM-2010-216834

# Fault Injection and Monitoring Capability for a Fault-Tolerant Distributed Computation System

Wilfredo Torres-Pomales, Amy M. Yates, and Mahyar R. Malekpour Langley Research Center, Hampton, Virginia

National Aeronautics and Space Administration

Langley Research Center Hampton, Virginia 23681-2199

August 2010

### Acknowledgments

The system described in this report originated from an initial experiment concept developed in collaboration with Dr. Oscar R. González and Dr. W. Steven Gray of Old Dominion University. We are grateful for their productive discussions in the development of system requirements.

We would like to thank Sandra V. Koppen and Truong X. Nguyen for their contributions to the definition of the system configuration for fault-injection experiments in a HIRF environment.

The work described here was made possible by the support from Eric G. Cooper, Associate Principal Investigator for NASA's IVHM Project.

The work performed by Old Dominion University as part of this research collaboration is funded by the NASA Langley Research Center under grant NNX07AD52A.

The use of trademarks or names of manufacturers in this report is for accurate reporting and does not constitute an official endorsement, either expressed or implied, of such products or manufacturers by the National Aeronautics and Space Administration.

Available from:

NASA Center for AeroSpace Information 7115 Standard Drive Hanover, MD 21076-1320 443-757-5802

# Abstract

The Configurable Fault-Injection and Monitoring System (CFIMS) is intended for the experimental characterization of effects caused by a variety of adverse conditions on a distributed computation system running flight control applications. A product of research collaboration between NASA Langley Research Center and Old Dominion University, the CFIMS is the main research tool for generating actual fault response data with which to develop and validate analytical performance models and design methodologies for the mitigation of fault effects in distributed flight control systems. Rather than a fixed design solution, the CFIMS is a flexible system that enables the systematic exploration of the problem space and can be adapted to meet the evolving needs of the research. The CFIMS has the capabilities of system-under-test (SUT) functional stimulus generation, fault injection and state monitoring, all of which are supported by a configuration capability for setting up the system as desired for a particular experiment. This report summarizes the work accomplished so far in the development of the CFIMS concept and documents the first design realization.

# **Table of Contents**

| List of Figures                                                                                      | vii |

|------------------------------------------------------------------------------------------------------|-----|

| List of Tables                                                                                       | Х   |

| 1. Introduction                                                                                      | 1   |

| 2. Concept for a Configurable Fault-Injection and Monitoring Capability                              |     |

| 2.1. SUT Functional Stimulation and Monitoring                                                       |     |

| 2.2. Fault Injection                                                                                 |     |

| 2.3. State Monitoring                                                                                |     |

| 2.4. System Configuration                                                                            | 10  |

| 3. Overview of the ROBUS-2 Communication System                                                      |     |

| 3.1. System Structure                                                                                |     |

| 3.2. Distributed Coordination                                                                        |     |

| 3.3. Redundancy Management                                                                           |     |

| 3.4. Operational Modes                                                                               |     |

| 3.4.1. Clique Preservation                                                                           |     |

| 3.4.2. Self-Test                                                                                     |     |

| 3.4.3. Clique Detection                                                                              |     |

| 3.4.4. Clique Join                                                                                   |     |

| 3.4.5. Clique Initialization                                                                         |     |

| 3.5. ROBUS Messages                                                                                  |     |

| 3.6. Point-to-Point Communication                                                                    |     |

| 3.7. Communication Patterns                                                                          |     |

| 3.7.1. Collective Diagnosis                                                                          |     |

| 3.7.2. Schedule Update                                                                               |     |

| 3.7.3. PE Broadcast                                                                                  |     |

| 3.7.4. Accusation Exchange                                                                           |     |

| 3.7.5. Synchronization Preservation                                                                  |     |

| 3.7.6. Local Diagnosis Acquisition                                                                   |     |

| <ul><li>3.7.7. Synchronization Acquisition</li><li>3.7.8. Collective Diagnosis Acquisition</li></ul> |     |

| 3.7.9. Initial Diagnosis                                                                             |     |

| 3.7.10. Initial Synchronization                                                                      |     |

| 3.8. Communication between PEs and BIUs                                                              |     |

| 5.6. Communication octiveen i Es and Dios                                                            |     |

| 4. Overview of the Configurable Fault-Injection and Monitoring System                                | 27  |

| 4.1. Initial Application                                                                             | 27  |

| 4.2. Execution Platform                                                                              |     |

| 4.2.1. Reconfigurable SPIDER Prototyping Platform 1                                                  |     |

| 4.2.2. Reconfigurable SPIDER Prototyping Platform 2                                                  |     |

| 4.3. Initial Configurable Fault Injection and Monitoring System                                      |     |

| 4.3.1. SUT Function Testing.                                                                         |     |

| 4.3.1.1. PE Synchronization                                                                          |     |

| 4.3.1.2. Application Testing                                                                         |     |

| 4.3.2. Fault Injection                                                                               |     |

| 4.3.2.1. Mapping the OTH Fault Modes to Component Fault Modes                                        |     |

| 4.3.2.2. Design Approach                                                                             |     |

| 4.3.2.3. Current Design                                                                              |     |

| 4.3.3. State Monitoring                                                                              |     |

| 4.3.4. Round Control                                                                                        |      |

|-------------------------------------------------------------------------------------------------------------|------|

| 4.3.5. Data Collection                                                                                      |      |

| 4.3.6. System Configuration                                                                                 |      |

|                                                                                                             |      |

| 5. Hardware Controller Coordination Protocol                                                                |      |

| 5.1. Normal Run Modes                                                                                       |      |

| 5.2. Stop Scenarios                                                                                         | 54   |

|                                                                                                             |      |

| 6. Data Links                                                                                               |      |

| 6.1. Word-Mode Communication Unit<br>6.2. Packet-Mode Communication Unit                                    |      |

| 6.3. Multiple-Access Controller                                                                             |      |

| 0.5. Wultiple-Access Controller                                                                             |      |

| 7. Test Control Messages                                                                                    |      |

| 7.1. Round Control                                                                                          |      |

| 7.2. Function Testing                                                                                       |      |

| 7.2.1. PE Synchronization                                                                                   |      |

| 7.2.2. Application Testing                                                                                  |      |

| 7.3. Fault Injection                                                                                        |      |

| 7.4. State Monitoring                                                                                       |      |

| 8. Fault Injectors                                                                                          | 75   |

| 8.1. Common Architecture                                                                                    |      |

| 8.2. Fail-Silent Fault Injector                                                                             |      |

|                                                                                                             | ,,,, |

| 9. PE-BIU Node                                                                                              |      |

| 9.1. PE Setup Unit                                                                                          |      |

| 9.2. Processing Element                                                                                     |      |

| 9.2.1. Main Functions                                                                                       |      |

| 9.2.2. Operational Modes                                                                                    |      |

| 9.2.3. Organization and Error Checks                                                                        |      |

| 9.3. Embedded Node Monitor                                                                                  | 85   |

| 10. RMU Node                                                                                                |      |

|                                                                                                             |      |

| <ol> <li>Hardware Processes of the Primary Test Controller.</li> <li>11.1. PTC Round Controller.</li> </ol> |      |

|                                                                                                             |      |

| 11.2. SPIDER Function Tester<br>11.2.1. Function Timer                                                      |      |

| 11.2.1. Function Timer                                                                                      |      |

| 11.3. Primary Fault-Injection Controller                                                                    |      |

| 11.4. PE-BIU State Monitor                                                                                  |      |

| 11.5. SPIDER Health Monitor                                                                                 |      |

| 11.6. Test Control Links                                                                                    |      |

| 11.7. Software Interface                                                                                    |      |

|                                                                                                             |      |

| 12. Hardware Processes of the Secondary Test Controller                                                     |      |

| 12.1. STC Round Controller                                                                                  |      |

| 12.2. Secondary Fault-Injection Controller                                                                  |      |

| 12.3. RMU State Monitor                                                                                     |      |

| 12.4. Health Monitor                                                                                        |      |

| 12.6. Software Interface                                                                                    |      |

|                                                                                                             |      |

| 13. Test Control Software                                                                                   |      |

|                                                                                                             |      |

| 13.1. Test Execution and Data Management          |  |

|---------------------------------------------------|--|

| 13.2. Data Management Software                    |  |

| 13.3. Test Execution Software                     |  |

| 14. Final Remarks                                 |  |

| Appendix A. Test Specification File               |  |

| Appendix B. Data Collected During Round Execution |  |

| B.1. Round Control                                |  |

| B.2. Round Timer                                  |  |

| B.3. Function Timer                               |  |

| B.4. Function Monitors                            |  |

| B.5. PE-BIU State Monitors                        |  |

| B.6. RMU State Monitors                           |  |

| Appendix C. Test Control Software Pseudo-Code     |  |

| C.1. PTC Data Management Software                 |  |

| C.2. STC Data Management Software                 |  |

| C.3. PTC Test Execution Software                  |  |

| C.4. STC Test Execution Software                  |  |

| References                                        |  |

| Acronyms and Abbreviations                        |  |

# List of Figures

| Figure 1.1: SPIDER topology and services                                                              | 2  |

|-------------------------------------------------------------------------------------------------------|----|

| Figure 2.1: Main components and information flows in the configurable fault injection and monitoring  |    |

| capability                                                                                            |    |

| Figure 2.2: Application-level view of the SUT configured as the flight controller                     |    |

| Figure 2.3: High-level view of the CFIMS functions                                                    |    |

| Figure 2.4: Faultload generation and propagation of fault manifestations                              | 7  |

| Figure 3.1: ROBUS topology                                                                            | 12 |

| Figure 3.2: Generic top-level node structure for BIUs and RMUs                                        |    |

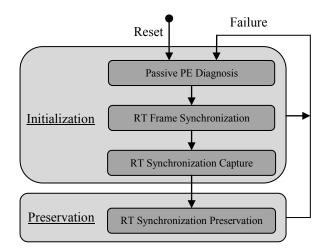

| Figure 3.3: Major operational mode transitions for ROBUS nodes                                        |    |

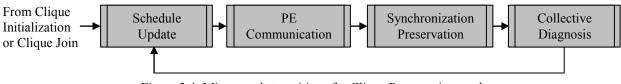

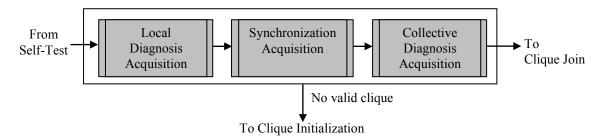

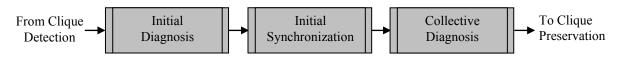

| Figure 3.4: Minor mode transitions for Clique Preservation mode                                       | 16 |

| Figure 3.5: Minor modes transitions for Clique Detection mode                                         | 17 |

| Figure 3.6: Minor modes transitions for Clique Initialization mode                                    | 17 |

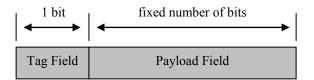

| Figure 3.7: ROBUS Message format                                                                      | 18 |

| Figure 3.8: Generic point-to-point communication path                                                 | 18 |

| Figure 3.9: Timing for synchronous communication                                                      | 19 |

| Figure 3.10: Message flow graph for the Collective Diagnosis protocol                                 | 20 |

| Figure 3.11: Message flow graph for the Schedule Update protocol                                      | 20 |

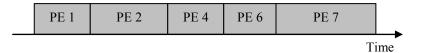

| Figure 3.12: Example of an access pattern during the PE Broadcast service                             | 21 |

| Figure 3.13: Message flow graph for the PE Broadcast protocol                                         | 21 |

| Figure 3.14: Message flow graph for the Accusation Exchange protocol                                  | 21 |

| Figure 3.15: Message flow graph for the Synchronization Preservation protocol                         | 22 |

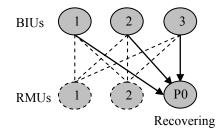

| Figure 3.16: Message flow in a 3x3 system with a recovering RMU executing Local Diagnosis Acquisition | 22 |

| Figure 3.17: Message flow graph for Synchronization Preservation with the Synchronization Capture     |    |

| processes                                                                                             | 23 |

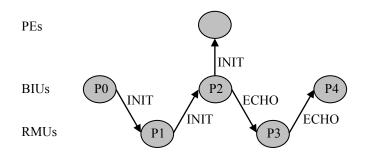

| Figure 3.18: Message flow graph for the Initial Diagnosis protocol                                    | 23 |

| Figure 3.19: Message flow graph for the Initial Synchronization protocol                              |    |

| Figure 3.20: Message exchange pattern between a BIU and its attached PE in Clique Preservation mode   | 25 |

| Figure 4.1: Concept for initial SUT configuration                                                     |    |

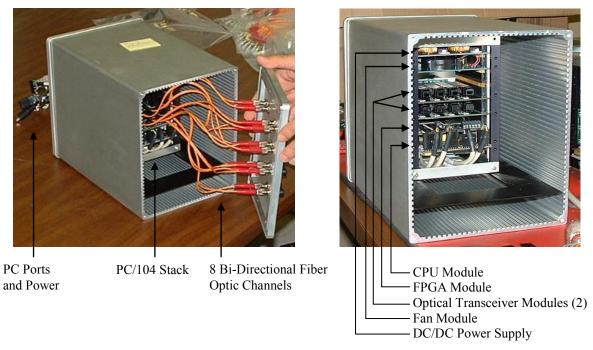

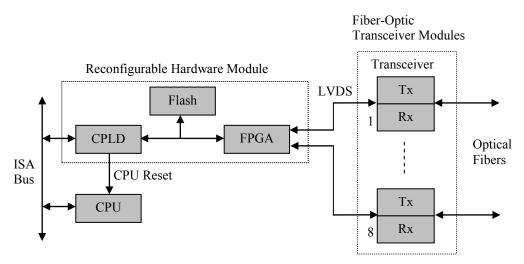

| Figure 4.2: RSPP1 Node                                                                                | 29 |

| Figure 4.3: Interconnection of the main physical design components on an RSPP1 Node                   | 30 |

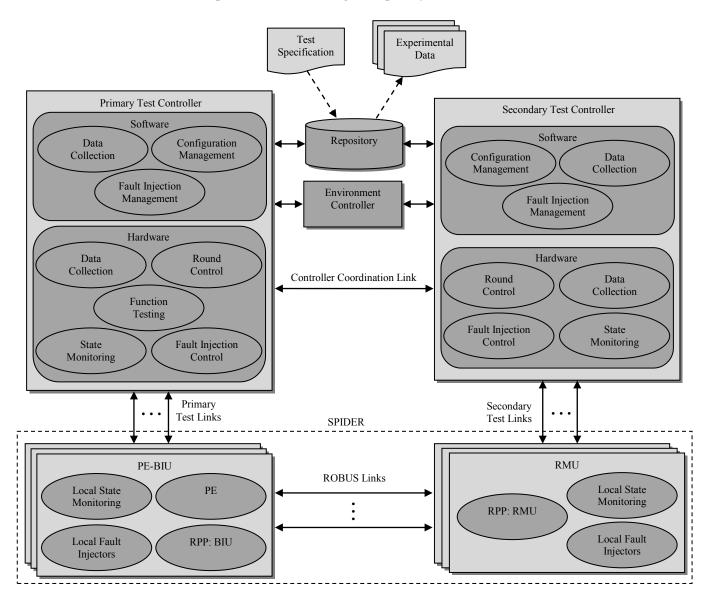

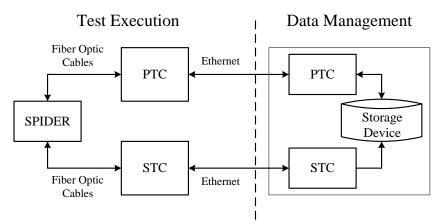

| Figure 4.4: High-level architectural view of the CFIMS and SUT                                        | 32 |

| Figure 4.5: Major-mode transition graph for a Processing Element                                      | 35 |

| Figure 4.6: Message flow graph for the RCI agreement protocol                                         | 35 |

| Figure 4.7: Mode transitions for Function Timer                                                       | 36 |

| Figure 4.8: Message flow pattern for testing ROBUS fault effects on PE messages                       | 37 |

| Figure 4.9: Dataflow graph for a node state monitoring lane                                           | 45 |

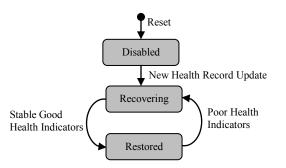

| Figure 4.10: State transition diagram for node condition assessment                                   | 45 |

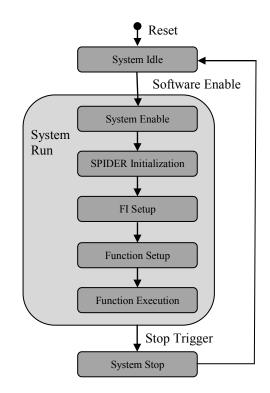

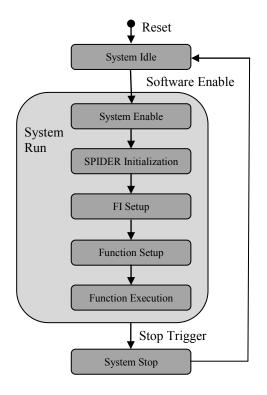

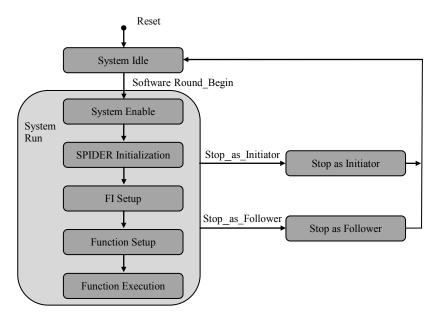

| Figure 4.11: Major mode transition diagram for CFIMS                                                  | 46 |

| Figure 5.1: Major mode transition diagram for the CFIMS                                               |    |

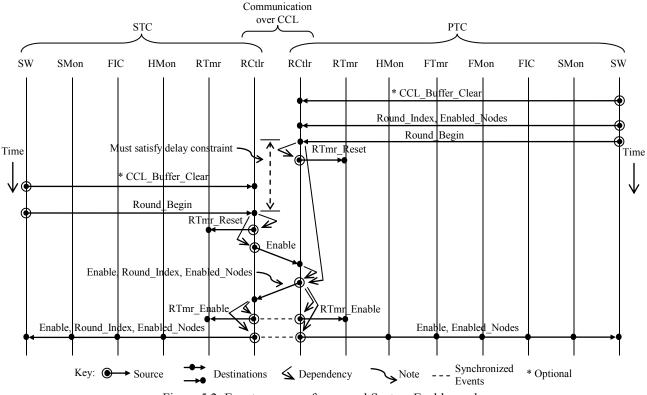

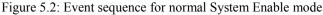

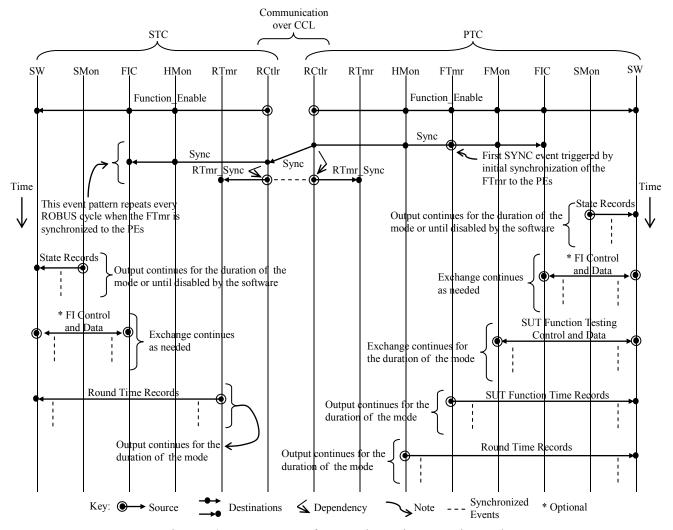

| Figure 5.2: Event sequence for normal System Enable mode                                              | 50 |

| Figure 5.3: Event sequence for normal SPIDER Initialization mode                                      | 51 |

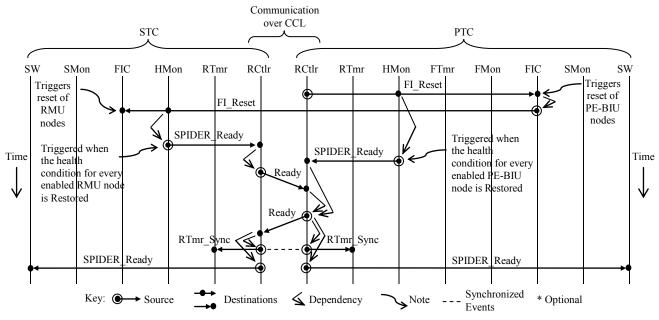

| Figure 5.4: Event sequence for normal Fault Injection Setup mode                                      | 52 |

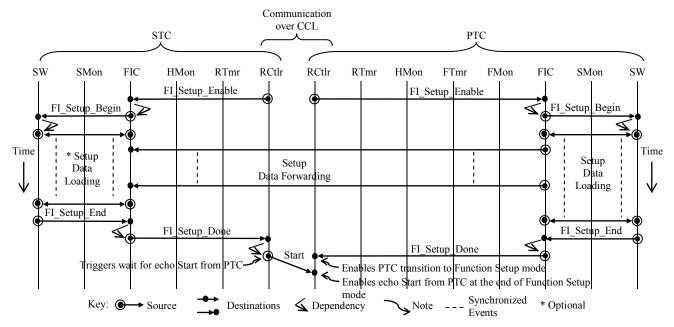

| Figure 5.5: Event sequence for normal Function Setup mode                                             | 52 |

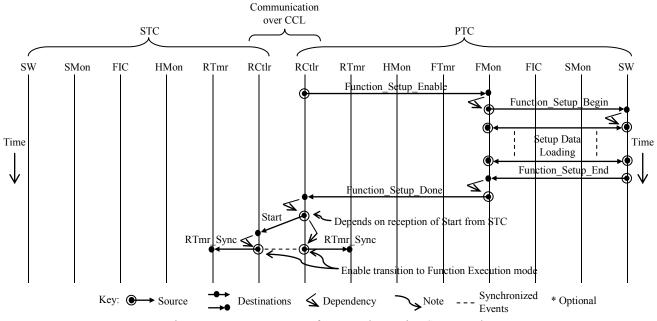

| Figure 5.6: Event sequence for normal Function Execution mode                                         | 53 |

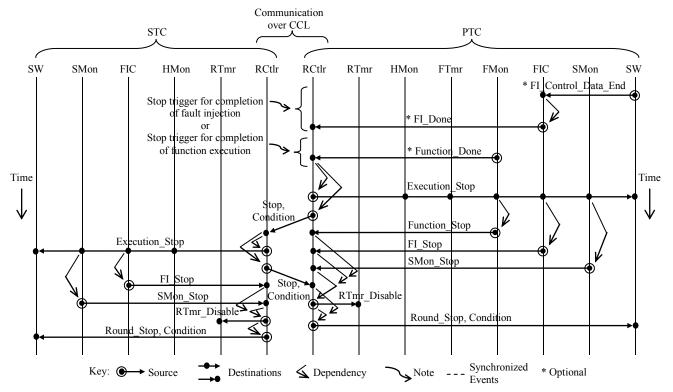

| Figure 5.7: Event sequence for System Stop on completion of PTC fault injection or function execution | 54 |

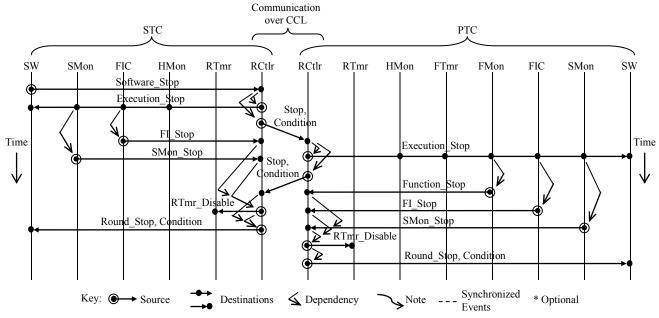

| Figure 5.8: Event sequence for System Stop on STC software stop                                       | 55 |

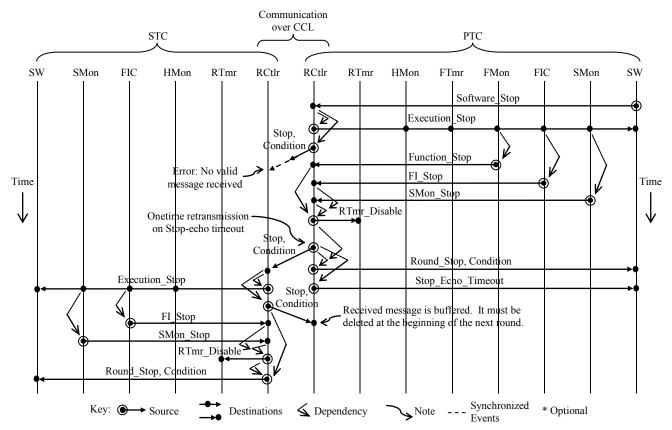

| Figure 5.9: Event sequence for System Stop on PTC software stop and with initiator Stop message error | 55 |

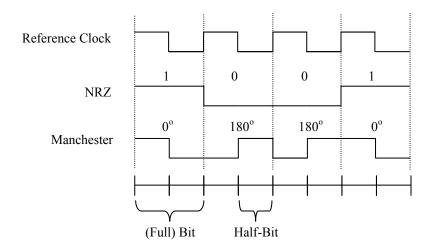

| Figure 6.1: Manchester encoding of NRZ data bits                                                      | 59 |

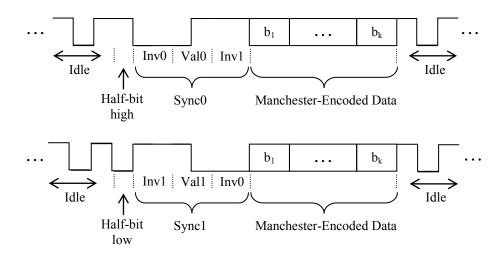

| Figure 6.2: Signaling structure for the transmission of a data word (with Sync0 and Sync1)            |    |

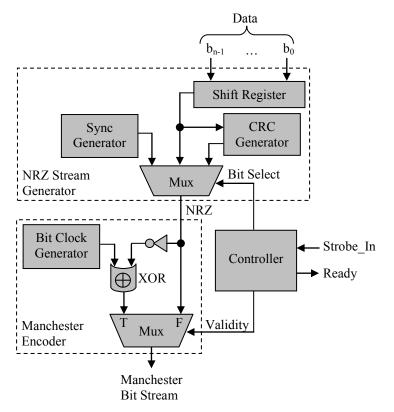

| Figure 6.3: Block diagram for the word-mode transmitter                                               |    |

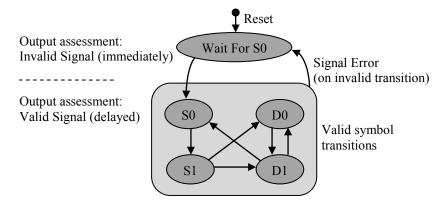

| Figure 6.4: Simplified state diagram for WMCU Waveform Monitor                                        |    |

| Figure 6.5: Block diagram for the Word-Mode Receiver                                                  |    |

|                                                                                                       |    |

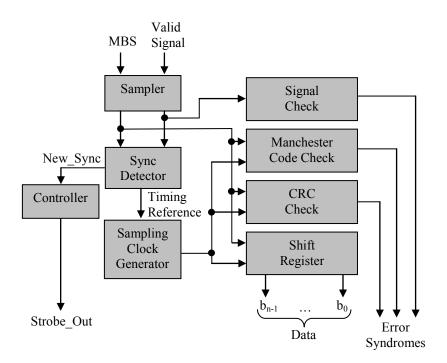

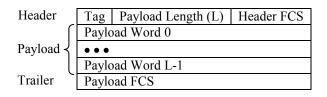

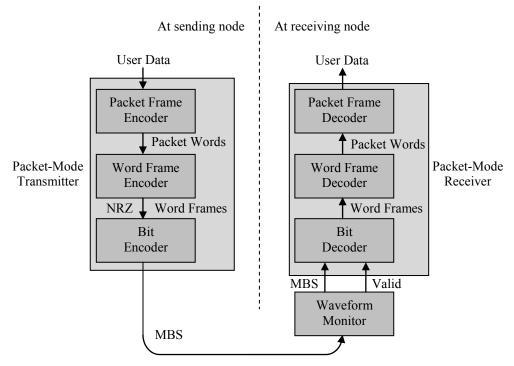

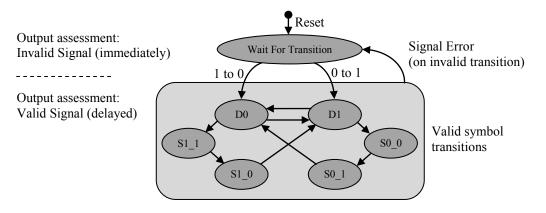

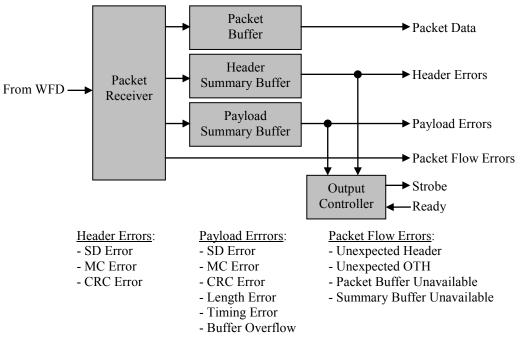

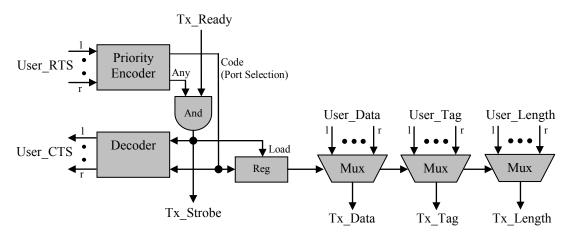

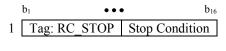

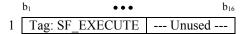

| Figure 6.7: Packet frame format64Figure 6.8: Block diagram for the packet-mode data link65Figure 6.9: Simplified state diagram for PMCU waveform monitor65Figure 6.10: Block diagram for the Packet Frame Decoder and list of packet error checks66Figure 6.11: Block diagram for the PMCU Multiple-Access Controller67Figure 7.1: TCL packet format for TCMs68Figure 7.2: TCM format: RC_ENABLE69Figure 7.3: TCM format: RC_READY and RC_START70Figure 7.4: TCM format: RC STOP70 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.9: Simplified state diagram for PMCU waveform monitor                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 6.10: Block diagram for the Packet Frame Decoder and list of packet error checks                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 6.11: Block diagram for the PMCU Multiple-Access Controller       67         Figure 7.1: TCL packet format for TCMs       68         Figure 7.2: TCM format: RC_ENABLE       69         Figure 7.3: TCM format: RC_READY and RC_START       70                                                                                                                                                                                                                              |

| Figure 7.1: TCL packet format for TCMs                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 7.2: TCM format: RC_ENABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 7.3: TCM format: RC_READY and RC_START                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Eigure 7.4: TCM format: DC STOD                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 7.4. TCWI Iomaa. RC_STOP                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 7.5: TCM format: SF_SETUP                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 7.6: TCM format: SF_EXECUTE                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 7.7: TCM format: SYNC PE TIME                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 7.8: TCM format: SYNC_ROUND_TIME                                                                                                                                                                                                                                                                                                                                                                                                                                            |

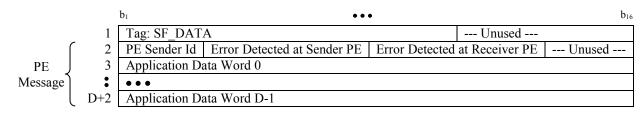

| Figure 7.9: TCM format: SF DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

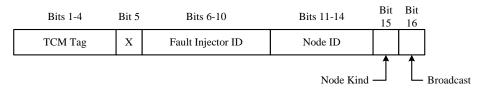

| Figure 7.10: Format of first TCM Payload Word for FI_RESET, FI_FAULT, FI_ACTIVATION,                                                                                                                                                                                                                                                                                                                                                                                               |

| FI EXECUTE, and FI FIRE                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 7.11: TCM format: FI RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 7.12: TCM format: FI EXECUTE                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 7.13: TCM format: FI FAULT, FI ACTIVATION, and FI FIRE                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 7.14: TCM format: FI FIRE for current CFIMS                                                                                                                                                                                                                                                                                                                                                                                                                                 |

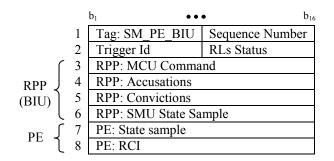

| Figure 7.15: TCM format: $S\overline{M}$ PE BIU                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 7.16: TCM format: SM RMU                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

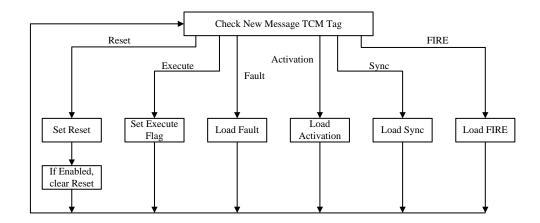

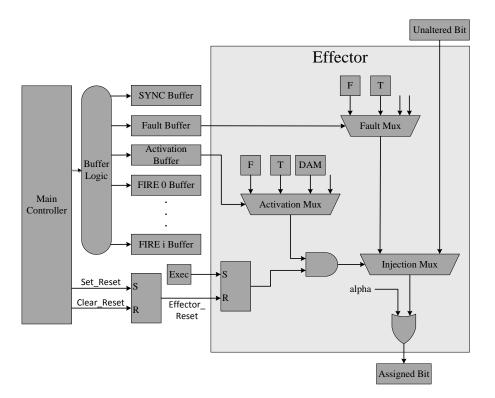

| Figure 8.1: Local Fault Injector State Machine                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 8.2: Local Fault Injector Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                      |

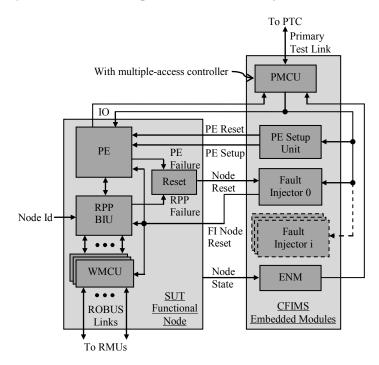

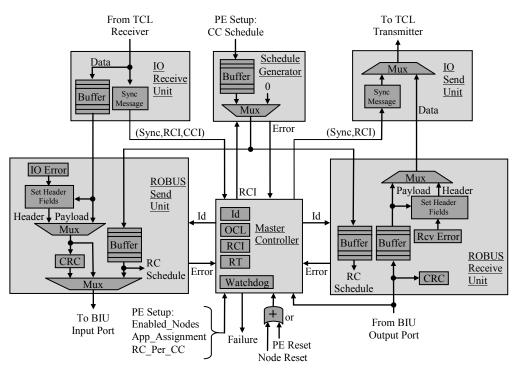

| Figure 9.1: Block diagram for a PE-BIU node                                                                                                                                                                                                                                                                                                                                                                                                                                        |

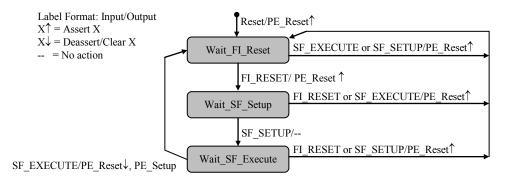

| Figure 9.2: Mode transition diagram for the PE Setup Unit                                                                                                                                                                                                                                                                                                                                                                                                                          |

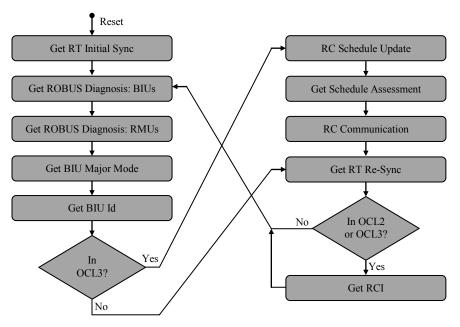

| Figure 9.3: Major-mode transition diagram for the PE                                                                                                                                                                                                                                                                                                                                                                                                                               |

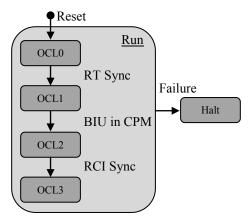

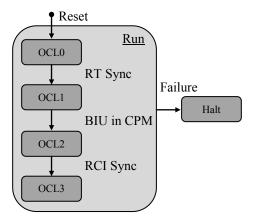

| Figure 9.4: Minor-mode transition diagram for the PE                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 9.5: Block diagram for Processing Element                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 9.6: Block diagram for the Embedded Node Monitor                                                                                                                                                                                                                                                                                                                                                                                                                            |

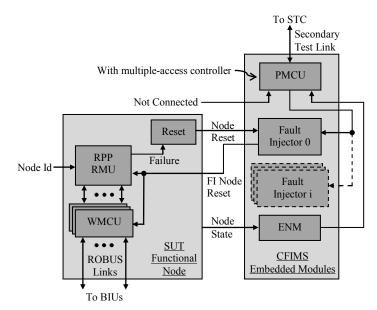

| Figure 10.1: Block diagram for RMU node                                                                                                                                                                                                                                                                                                                                                                                                                                            |

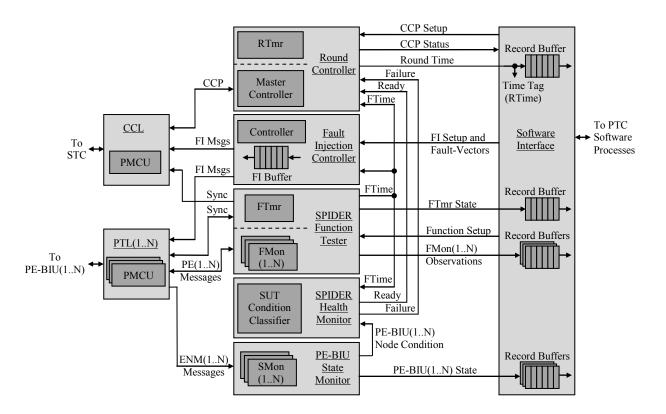

| Figure 11.1: Block diagram for the Hardware Processes of the Primary Test Controller                                                                                                                                                                                                                                                                                                                                                                                               |

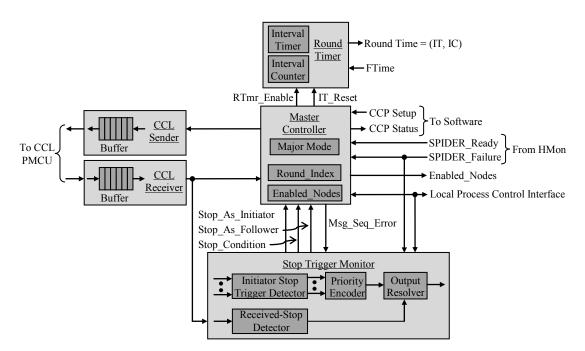

| Figure 11.2: Block diagram for the PTC Round Controller                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 11.3: Major mode transition graph for the Master Controller of the PTC RCtlr                                                                                                                                                                                                                                                                                                                                                                                                |

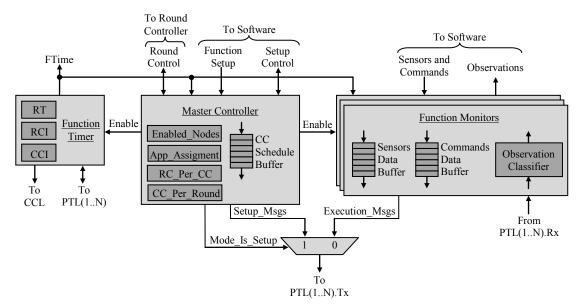

| Figure 11.4: Top-level block diagram for SPIDER Function Tester                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 11.5: Mode transition graph for the Function Timer                                                                                                                                                                                                                                                                                                                                                                                                                          |

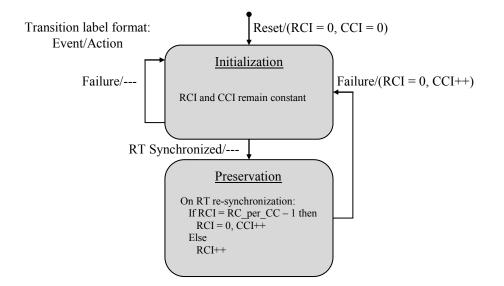

| Figure 11.6: Policy rules for managing the values of RCI and CCI                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 11.7: Block diagram for the Function Timer                                                                                                                                                                                                                                                                                                                                                                                                                                  |

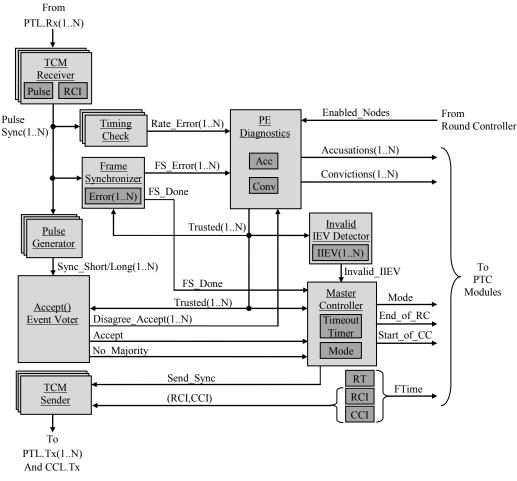

| Figure 11.8: Example sync pulses and corresponding Accept() Event Voter response for $\Pi_{\text{SP,P3IO,RCV}} = 2$                                                                                                                                                                                                                                                                                                                                                                |

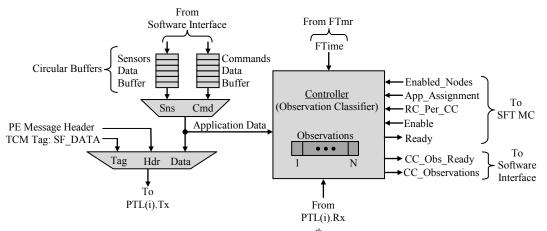

| Figure 11.9: Block Diagram for the i <sup>th</sup> Function Monitor                                                                                                                                                                                                                                                                                                                                                                                                                |

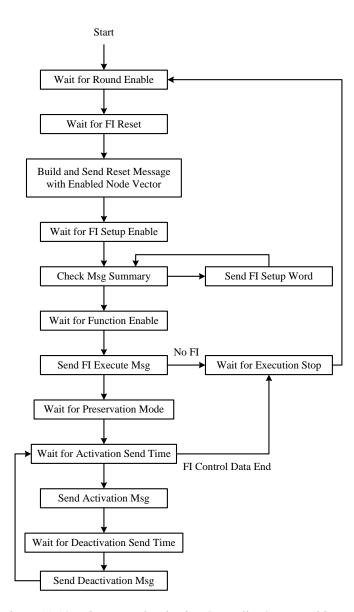

| Figure 11.10: Primary Fault Injection Controller State Machine                                                                                                                                                                                                                                                                                                                                                                                                                     |

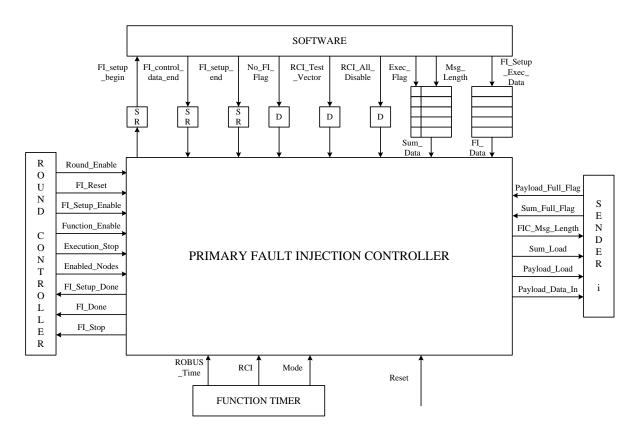

| Figure 11.11: Primary Fault Injection Controller Interface Architecture                                                                                                                                                                                                                                                                                                                                                                                                            |

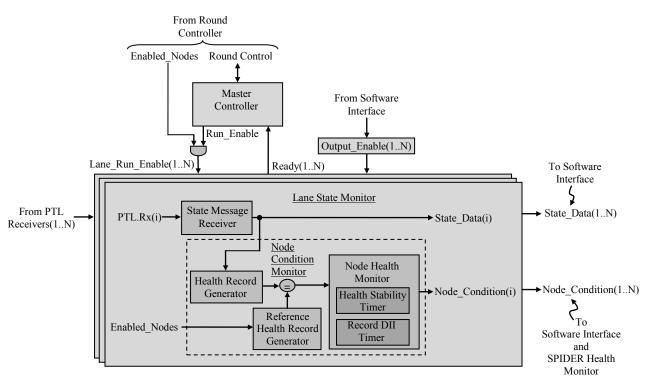

| Figure 11.12: Block Diagram for the PE-BIU State Monitor                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 11.13: Transition diagram for state-based node health assessment                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 11.14: Block diagram for the PTC Software Interface module                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 12.1: Block diagram for the Hardware Processes of the Secondary Test Controller                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 12.2: Block diagram for the STC Round Controller                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 12.3: Secondary Fault Injection Controller Interface Architecture                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 12.4: Secondary Fault Injection Controller Relay State Machine                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 12.5: Secondary Fault Injection Controller Control Signal State Machine                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 12.6: Block diagram for the STC Software Interface                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 13.1: Separation of the Test Execution and Data Management Software                                                                                                                                                                                                                                                                                                                                                                                                         |

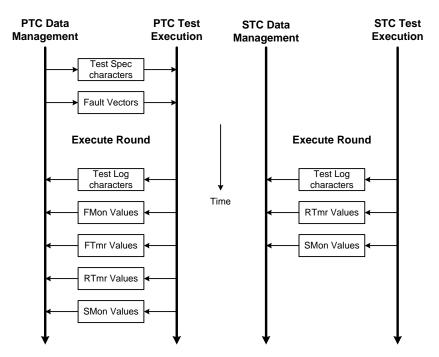

| Figure 13.2: Test Execution and Data Management Software Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                             |

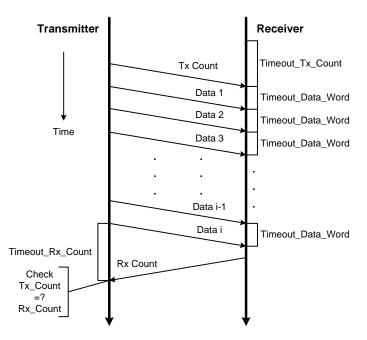

| Figure 13.3: Test Execution and Data Management Software Data Transmission Protocol                                                                                                                                                                                                                                                                                                                                                                                                |

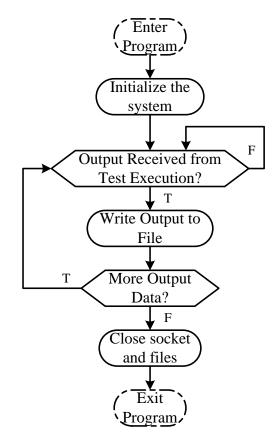

| Figure 13.4: PTC and STC Data Management Software High Level Program Flow                           | 118 |

|-----------------------------------------------------------------------------------------------------|-----|

| Figure 13.5: PTC and STC Test Execution Software High Level Program Flow                            | 119 |

| Figure 13.6: PTC Test Execution Software CCP State Machine                                          |     |

| Figure 13.7: PTC and STC Test Execution Software Check for Stop Subset of CCP State Machine         |     |

| Figure 13.8: STC Test Execution Software CCP State Machine                                          |     |

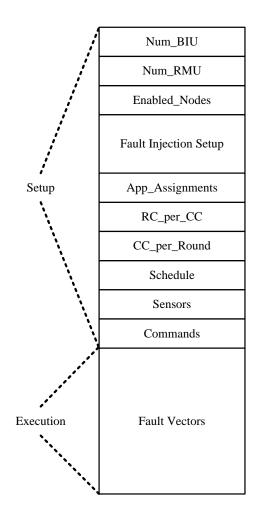

| Figure A.1: Test Specification File Format                                                          |     |

| Figure A.2: Test Specification File Setup Line Format                                               |     |

| Figure A.3: Enabled Nodes Format                                                                    |     |

| Figure A.4: Example of Fault Injection Section of Test Specification file with multiple fault types |     |

| Figure A.5: Test Specification File Example.                                                        |     |

|                                                                                                     |     |

# List of Tables

| Table 2.1: Detectability-based fault model for one-to-one communication                                                | 8   |

|------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2: Omissive-Transmissive Hybrid fault model for one-to-many communication                                      | 9   |

| Table 4.1: Defined observations for the communication path from sender FMon <sub>i</sub> to receiver FMon <sub>i</sub> | 38  |

| Table 4.2: Detectability-based fault manifestation at the receiver as a function of source node and link fault         |     |

| types                                                                                                                  | 39  |

| Table 4.3: OTH fault classification based on Node Type and Link Type outputs                                           | 40  |

| Table 6.1: Definition of WMCU waveform symbols                                                                         | 62  |

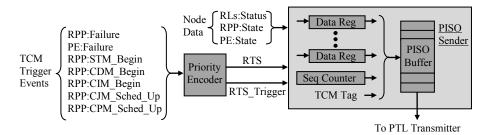

| Table 7.1: TCM Sources                                                                                                 |     |

| Table 7.2: TCM Tags                                                                                                    | 69  |

| Table A.1: Test Specification File Setup Section Labels                                                                | 126 |

| Table B.1: Round Controller Status Word                                                                                | 129 |

| Table B.2: Round Stop Conditions                                                                                       | 130 |

| Table B.3: Collected Function Timer Data                                                                               | 131 |

| Table B.4: Observation codes for a Function Monitor                                                                    | 132 |

| Table B.5: Main state record content for a PE-BIU State Monitor Lane                                                   | 133 |

| Table B.6: Main state record content for an RMU State Monitor Lane                                                     | 139 |

|                                                                                                                        |     |

# 1. Introduction

The system described in this report, henceforth referred to as the Configurable Fault-Injection and Monitoring System (CFIMS), is intended for the experimental characterization of effects caused by a variety of adverse conditions on a distributed computation system running flight control applications. The CFIMS is a product of collaborative research between NASA Langley Research Center (LaRC) and Old Dominion University (ODU) in support of NASA's goal of developing technologies to improve the intrinsic safety of aircraft [NASA06, Shin08]. The research is being performed under the organizational framework of the Aviation Safety Program's Integrated Vehicle Health Management (IVHM) research thrust, which aims to develop tools, technologies and techniques to mitigate hazardous events during flight [IVHM08]. The NASA-ODU collaboration is focused on developing theoretical tools to analyze the relationship between the design features of a representative computational platform and the performance of a flight control system implemented using the platform and operating in harsh environments [Gray08, Gray10, Chávez10].

The distributed computation platform selected for this research is the Scalable Processor Independent Design for Extended Reliability (SPIDER) developed at Langley Research Center under a previous research effort [Miner02, Torres05A]. SPIDER is a concept for a family of general-purpose fault-tolerant architectures that provides a flexible set of design solutions capable of satisfying a wide range of performance and reliability requirements, while preserving a consistent interface to applications. SPIDER has a combination of attributes not found in existing architectures:

- Product family solution adaptable to many different applications;

- Suitable for safety-critical aircraft functions;

- Supports the Integrated Modular Avionics (IMA) architectural concept (i.e., the ability to host many functions of mixed criticality on the same computational platform) [ARINC651];

- Redundancy management decoupled from applications (i.e., the fault tolerance and redundancy management functions required by the applications are handled by the computational platform itself);

- Customizable redundancy management strategy according to the requirements of the applications (i.e., different fault tolerance and redundancy management strategies can be concurrently supported for different applications);

- Byzantine-fault resilience (i.e., the ability to tolerate arbitrary fault manifestations) [Driscoll03];

- Function migration capability (i.e., the ability to dynamically move functions across a network to different computing resources);

- Ability to survive or quickly recover from massive correlated transient upsets;

- Implemented using mostly off-the-shelf hardware and software;

- Support for dissimilar processors;

- Handles part obsolescence (i.e., the design can evolve to accommodate obsolescence of processors and low-level communication hardware);

- High reliability-to-cost ratio; and

- Design assurance based on Formal Methods (i.e., algorithms and design are formally proven correct) [Butler02]

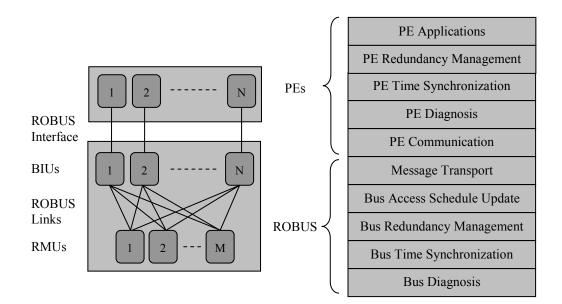

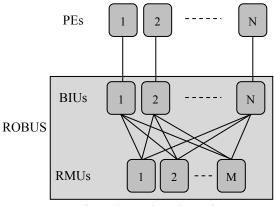

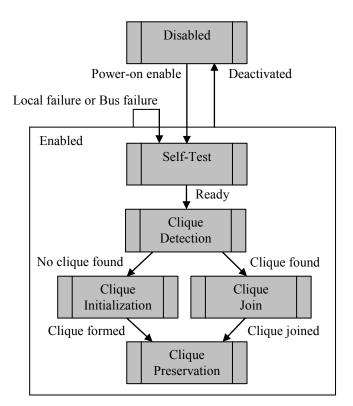

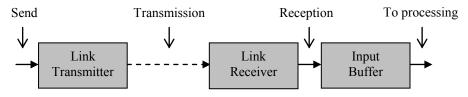

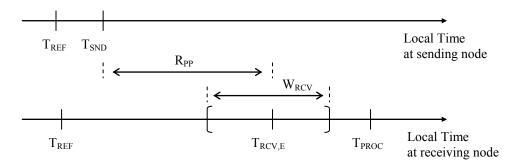

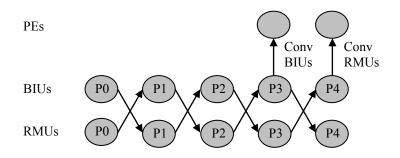

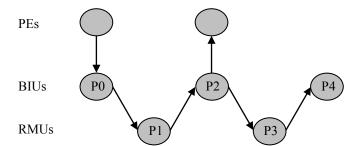

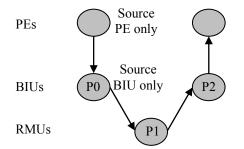

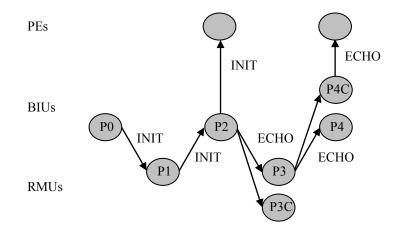

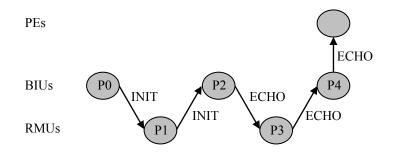

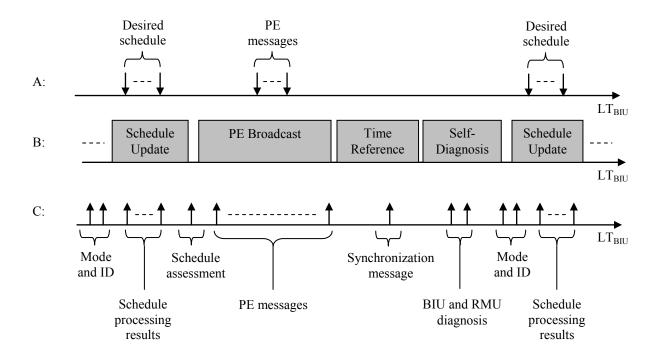

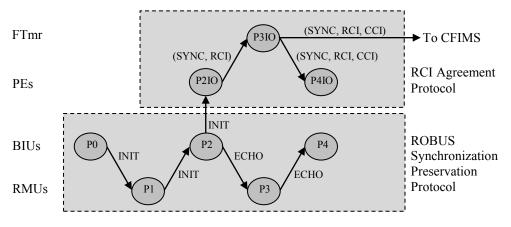

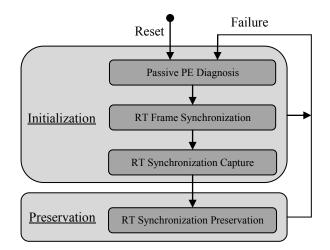

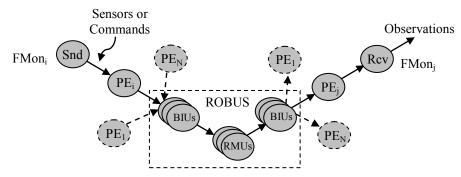

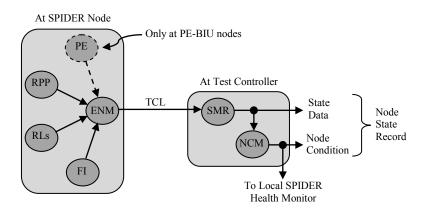

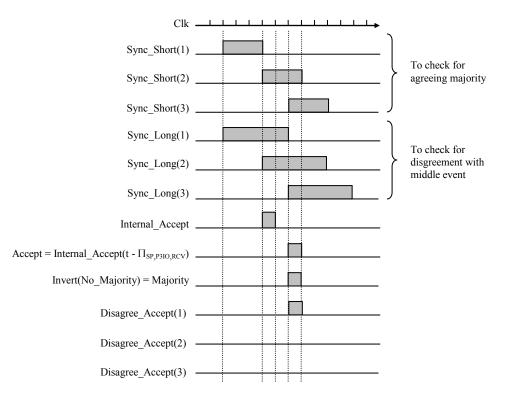

Figure 1.1 illustrates the SPIDER topology and main system services. The architecture consists of processing elements (PEs) executing the applications and other high-level system functions, and the ROBUS (Robust Bus) communication system, which provides basic services as the foundation for higher-level functions. The data network has a redundant active-star topology with the Bus Interface Units (BIUs) serving as the access ports and the Redundancy Management Units (RMUs) providing connectivity as network hubs. All the communication interfaces are bi-directional. The links between BIUs and RMUs form a complete bipartite graph in which each node is directly connected to every node of the opposite kind. A PE can be collocated and tightly coupled at the physical level to its corresponding BIU (i.e., they can share a fault-containment region (FCR)) [Lala91], or they can be physically independent components.

Figure 1.1: SPIDER topology and services

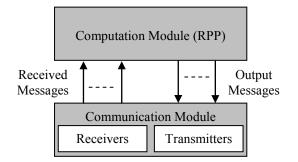

ROBUS implements basic distributed agreement protocols at the level they are most effective (i.e., in hardware) and is intended to reduce the computational burden on the PEs by providing a simple communication system abstraction for what is an inherently complex distributed processing problem. ROBUS-2, an instance of ROBUS, is a time-division multiple access (TDMA) broadcast data communication system (i.e., a data bus) with media access control by means of a time-indexed communication schedule. ROBUS-2 provides guaranteed fault-tolerant services to the attached PEs in the presence of a bounded number of internal faults. These services include message broadcast (Byzantine Agreement), dynamic communication schedule update, time reference (clock synchronization), and distributed diagnosis (group membership). ROBUS-2 also features fault-tolerant startup and restart

capabilities. ROBUS-2 tolerates internal as well as PE faults and incorporates a dynamic selfreconfiguration capability driven by the internal diagnostic system. ROBUS-2 consists of customdesigned hardware-based ROBUS Protocol Processors (RPPs) implementing the ROBUS-2 functionality, and a lower-level physical communication network consisting of full-duplex data links [Stallings94] interconnecting the RPPs (see ROBUS Links in Figure 1.1). Additional information about ROBUS-2 can be found in [Torres05A] and [Torres05B]. For completeness, Section 3 of this report provides an overview of ROBUS-2. The VHDL [Armstrong93] source code for the ROBUS-2 RPP is publicly available on the Internet with an open-source license agreement [R2PP].

In the NASA-ODU research collaboration, the range of adverse events to be considered are those characteristic of environmental threats like high-energy particle radiation [Taber93, Zhang08, Zhang09] and electromagnetic interference (EMI) from sources such as lightning and high-intensity radiated fields (HIRF) [Fuller95, Gray00, González01]. These environments have the potential to cause random fault manifestations in individual avionics components and to generate simultaneous system-wide faults that can overwhelm existing resource management mechanisms [Gray08, Hess97]. A flight control system using SPIDER will be subjected to physical and simulated faults in controlled laboratory conditions [Arlat89, Arlat03, Hsueh97, Torres08A] while gathering data suitable for characterizing fault effects at the control system level and at the computation platform level. The CFIMS is a critical element of the research effort as the means to generate experimental data for the development and validation of performance models for operation in adverse conditions.

The purpose of this report is to summarize the work accomplished so far in the development of the CFIMS concept and to document the design of its first realization. The next section describes the general concept for the CFIMS capability. That is followed by an overview of the ROBUS-2 design. After a high-level description for the current CFIMS, the report provides a description of the CFIMS hardware and software elements. A summary and remarks about future work conclude the report.

# 2. Concept for a Configurable Fault-Injection and Monitoring Capability

Relative to the primary goals of the NASA-ODU collaboration, the CFIMS is the main research tool for generating actual fault response data with which to develop and validate analytical performance models and design methodologies for the mitigation of fault effects. It is expected that achieving the project goals will involve a combination of systematic exploration of the problem space and an iterative process of model refinement involving experimentation and data analysis. Given the uncertainty about how this research will evolve, putting together a-priori a comprehensive list of well-defined design requirements for the CFIMS is a difficult (if not impossible) task with a high likelihood for an unfavorable outcome. Thus, rather than a fixed design solution, we envision a flexible system that can be adapted to meet the evolving needs of the research. The CFIMS should be an enabling tool that allows the investigators to focus on the research problem without being hampered by system limitations due to prior design choices.

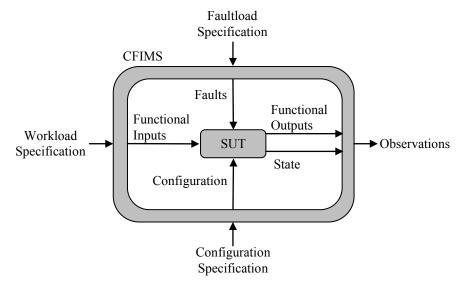

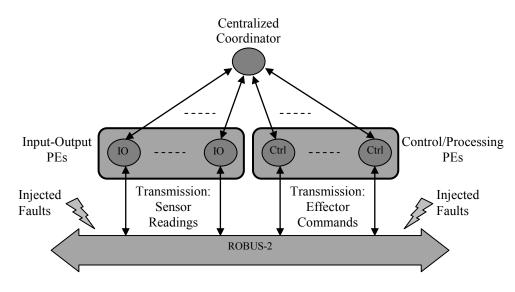

With this aim in mind, the first step in the development was to define a concept that captured the essence of what is needed. Figure 2.1 shows a graphical depiction of the concept. The central element is the system under test (SUT), which is a configurable version of SPIDER with added functionality to support simulated fault injection and state monitoring. The CFIMS controls the environment within which the SUT operates. The capabilities of the CFIMS include functional stimulation of the SUT, fault injection, and state monitoring, all of which are supported by a configuration capability for setting up the system as desired for a particular experiment. An experiment is defined by the specifications of the SUT will be subjected. Basically, the purpose of an experiment is to gather observations about the response of the SUT when operating under conditions determined by the specifications of the configuration, workload and faultload.

Figure 2.1: Main components and information flows in the configurable fault injection and monitoring capability

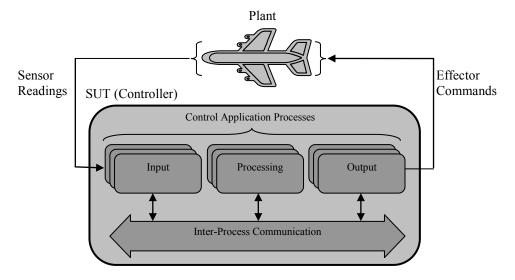

In general, the SUT is a distributed computation system executing an application. Figure 2.2 illustrates the role of the SUT in a flight control system and shows a generic SUT functional architecture at the application level consisting of a set of intercommunicating processes. The definition of the

application processes and the inter-process communication, as well as their mapping to the resources of the computation platform, are determined by the configuration specification. In SPIDER, all the application processes run on the PEs, which also handle the communication among the processes by leveraging the lower level services provided by ROBUS.

Figure 2.2: Application-level view of the SUT configured as the flight controller

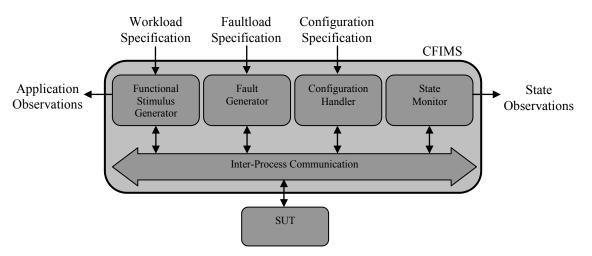

Figure 2.3: High-level view of the CFIMS functions

At a high level, the CFIMS can be viewed as a distributed set of intercommunicating processes (or modules) as illustrated in Figure 2.3 where the SUT is depicted as an external communicating process. The modularization of the CFIMS affords a reduction in the complexity of the development by containing most design changes within individual functional modules and limiting the interaction between modules to clearly defined interfaces. The function of the Configuration Handler process is to setup the system, including the CFIMS and the SUT, as indicated in the configuration specification. This configuration capability is one of the features that allow us to adapt the system to changing requirements. The Functional Stimulus Generator process is responsible for implementing the plant functionality to be

controlled by the application processes running on the SUT as shown in Figure 2.2. The Functional Stimulus Generator also has the capability to monitor the behavior of the application and generate observations for post-test analysis. The Fault Generator process injects faults into the SUT according to the faultload specification. The injected faults can be actual physical faults at the hardware level or simulated faults with similar manifestations. The State Monitor process collects state data from the SUT and outputs another stream of observations for post-test analysis. The following subsections elaborate on the desired features for the SUT and the CFIMS.

### 2.1. SUT Functional Stimulation and Monitoring

This aspect of the system determines the application implemented by the SUT and the CFIMS. As previously described, the type of application of interest is a closed-loop flight control system with the SUT performing the role of the controller and the CFIMS implementing the controlled object (or plant). However, given that the SUT is a general purpose computer and that there may be circumstances in which we may want to have a very simple application layer and focus on the fault effects on the lower level services of the computation platform, it is advantageous to conceptualize the function performed by the SUT as a generic application consuming inputs and generating outputs. The CFIMS provides the workload for the SUT, receives the generated functional outputs, and gathers observations about the response to injected faults.

In general, the mechanisms for testing (or "exercising") the function of the SUT should be scalable and flexible to accommodate a wide range of sizes of the computation platform, applications with various degrees of complexity, and fine precision for the specification of functionality for the system response monitors. There should also be mechanisms to allow various degrees of precision in the coordination between the function testing activities, the injection of faults, and the collection of application and state observations. The CFIMS should also provide the means to easily correlate the data in the output observation streams.

#### 2.2. Fault Injection

In the NASA-ODU collaborative research, only physical hardware faults (i.e., faults involving the physical parts of the system) are of interest. For the purpose of this research, it is assumed that software and design faults are not significant factors in the behavior of the SUT. In essence, a (physical hardware) fault is a physical event that causes a malfunction (i.e., a deviation from correct operation) in a system component. A system is composed of a collection of components organized such that their interaction generates a behavior implementing the function described in the system specification [Avizienis04]. The components of a system are themselves systems that implement lower-level functions.

The CFIMS fault injection capability is intended to force anomalous behavior on the components of the SUT. It is expected that for every SUT function and state monitoring setup, there will be many injection rounds with a variety of fault patterns, some of which may target multiple nodes, sometimes simultaneously. The fault injection configuration is likely to be the configuration that will change most often and the one to require the most flexible and precise solution for specification and execution of a test. Following the terminology in [Arlat03], some of the desired properties for a fault injection capability to assess the effectiveness of a fault-tolerant system include the following:

Reachability: the degree to which the possible fault locations can actually be reached by the means of injection;

- Controllability: the ability to control the location and time at which faults are injected (i.e., the precision with which faults can be injected);

- Repeatability: the ability to repeat fault injection experiments with high accuracy;

- Reproducibility: the ability to reproduce results in a statistical sense (which does not imply highly accurate fault repeatability); and

- Non-intrusiveness: the ability to avoid or minimize the impact of the fault injection instrumentation on the behavior of the SUT.

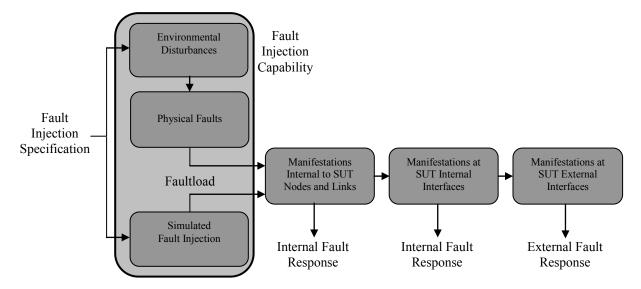

The injection of faults will normally be seen as the main independently controlled variable in an experiment. Figure 2.4 illustrates in concept the elements of the CFIMS fault injection capability for the generation of a faultload based on the injection specification and how the manifestations of the injected faults propagate and can be observed (and analyzed) at various SUT abstraction levels. In the CFIMS, application-level observations will capture fault manifestations at the external SUT interfaces, and the state monitoring capability will gather observations about fault manifestations within the SUT. As shown in Figure 2.4, the fault injection capability supports injection of physical and simulated faults. Physical fault injection will be effected indirectly by controlling the characteristics of environmental disturbances, including high-energy particle radiation and high intensity electromagnetic fields, generated in controlled laboratory conditions [Clough96, FAA93, Taber93, Torres08A]. In general, fault injection based on particle radiation has high reachability, but controllability and repeatability are low [Arlat03, Karlsson95]. Electromagnetic radiation also has very low controllability and repeatability, and in addition, reachability is lower than with particle radiation. Thus, in general, these environments are not the most effective for achieving the desirable attributes for a fault injection capability intended for a thorough characterization of effects. Nevertheless, these environments are representative of the types of conditions experienced by operational systems and that makes the experimental results immediately applicable to the goals of the NASA IVHM project. The data from experiments in these environments can be used to characterize the bounds of the relevant fault space, which can then be methodically explored in detail with simulated fault injections.

Figure 2.4: Faultload generation and propagation of fault manifestations

In general, the system fault space can be large and complex when measured in terms of the possible fault locations with respect to the actual smallest physical parts that make up the system. A strong determining factor for the complexity of a fault effects analysis is the selection of the components that constitute the smallest units of failure relevant to the analysis. In the SPIDER-based distributed SUT, the nodes and their communication links are the smallest recognized entities in the distributed interaction protocols, including resource management and agreement protocols. The system nodes and links are natural boundaries that can be leveraged in the definition of the minimum component granularity for fault effects analyses.

At their highest structural level, every SUT node is composed of a communication component and a computation component (see Section 3 in this report and [Torres05A]). The communication component of a node manages all the messaging interfaces to other nodes. The computation component performs all the local data processing according to the definition of the distributed protocols and the system application. A goal in the design of the SPIDER fault-tolerant system is to contain the internal propagation of faults and errors to allow the delivery of correct services at the external interfaces. As part of a node's error handling capability, the communication and computation components perform acceptance checks (e.g., CRC checks [Stallings94] or time of arrival checks [Torres05A]) on received messages with the intent of impeding the propagation of errors from other FCRs and minimize the likelihood that such errors corrupt the state of the receiving node. It is possible to significantly reduce the fault space to be analyzed by focusing on the manifestations of a transmitting node's behavior as perceived by a receiving node taking into consideration the results of error checks at the receiving node. The space of all possible faults that can occur at a transmitting node and its communication link can be mapped to a simple classification by leveraging the concept of error detectability (which is related to the property of integrity, i.e., the absence of improper state alteration) [Avizienis04, Paulitsch05] to establish equivalence relations on the manifestations at a receiver. The fault classes in this model for communication between a sending node and a receiving node are labeled Good, Omissive and Transmissive (GOT). Alternatively, the classes can be respectively labeled Correct, Detected and Undetected (CDU) (see [Torres08B]). In this GOT/CDU model, the fault categories are defined as shown in Table 2.1, where correctness is determined by the system specification. This fault model for one-toone communication can be used through composition to study the propagation of errors and error detection in a large distributed system network.

| Fault Mode              | Description                                                                              |

|-------------------------|------------------------------------------------------------------------------------------|

| Good/Correct            | The receiver accepts a correct message (i.e., there is no fault or fault manifestation). |

| Omissive/Detected       | The receiver detects a missing message or rejects an incorrect message.                  |

| Transmissive/Undetected | The receiver accepts an incorrect message.                                               |

Table 2.1: Detectability-based fault model for one-to-one communication

A fault model better suited to the analysis of properties in distributed agreement protocols is the omissive-transmissive hybrid (OTH) model [Azadmanesh00, Torres08B, Weber06], which adds the concept of consistency of perception to the definition of the fault categories. In this model, the smallest system component is a sending node and its transmission links to all the nodes receiving messages from it (i.e., the observers). The receivers either agree on their observations (i.e., their observations are symmetric) or they do not (i.e., their observations are asymmetric). The fault categories in this model are defined in Table 2.2. The OTH model allows a further reduction in complexity by minimizing the fault

space to a small set of categories that are relevant to the analysis of distributed agreement properties.

| Fault Mode                      | Description                                                       |

|---------------------------------|-------------------------------------------------------------------|

| Correct                         | All observers receives the same correct message.                  |

| Omissive Symmetric              | Each observer declares the message invalid, either because the    |

|                                 | message was not received or it was detectably incorrect.          |

| Transmissive Symmetric          | Each observer accepts the same incorrect message.                 |

| Strictly Omissive Asymmetric    | Some observers receive the same correct message and others        |

|                                 | declare the message invalid, either because they do not receive a |

|                                 | message or declare invalid their received message.                |

|                                 | Some observers accept the same incorrect message and others       |

| Single-Data Omissive Asymmetric | declare the message invalid, either because they do not receive a |

|                                 | message or declare invalid their received message.                |

| Transmissive Asymmetric         | The observers have other patterns of disagreeing observations.    |

Table 2.2: Omissive-Transmissive Hybrid fault model for one-to-many communication

An enhancement to the OTH model is to add the dimension of time duration to the fault categories. With the concept of persistence of a fault, each OTH category can be subdivided by fault duration categories defined according to the particular conditions of the problem at hand (e.g., transient and permanent duration). We refer to this classification as the Detectability, Consistency and Persistence (DCP) fault model.

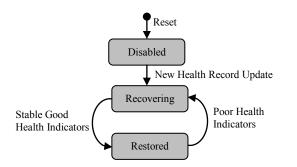

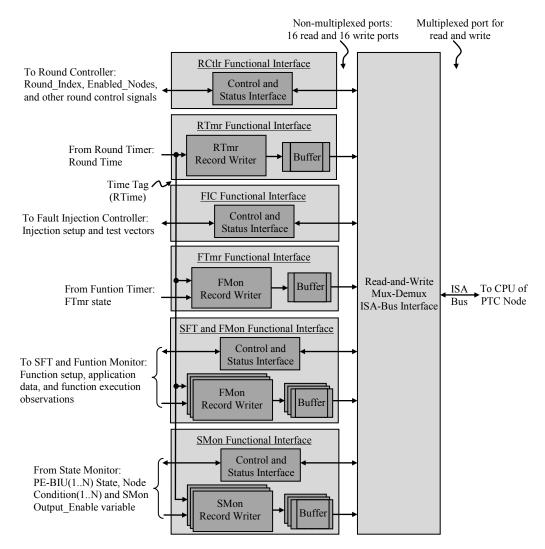

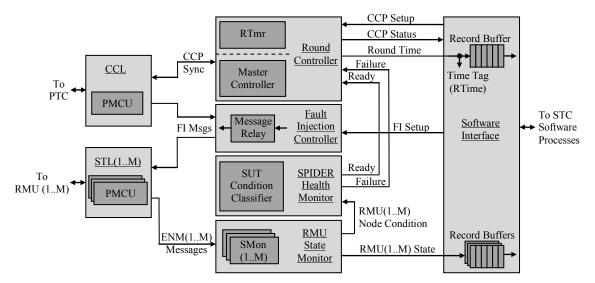

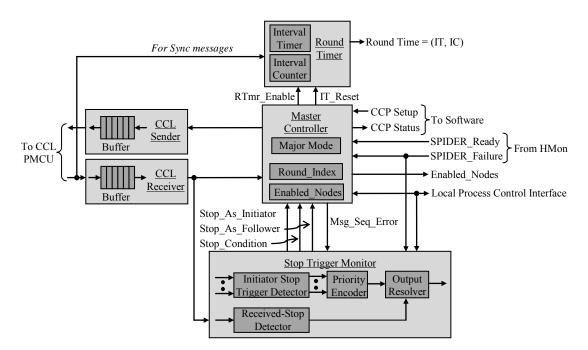

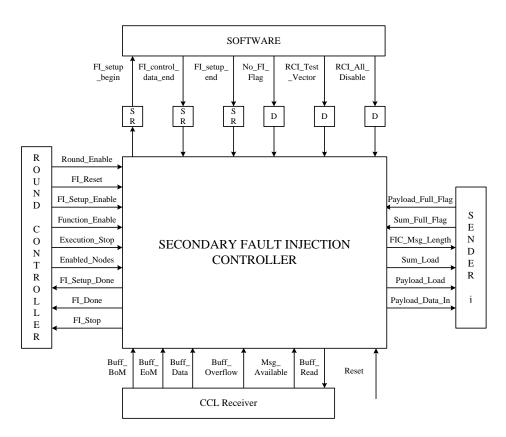

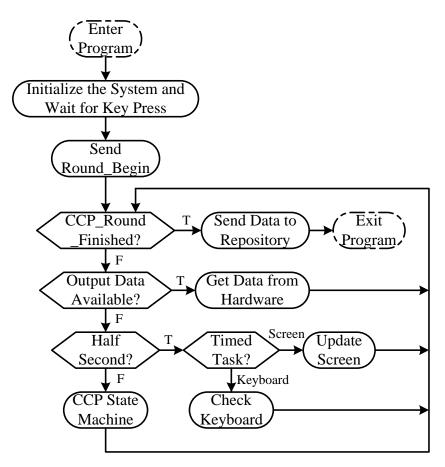

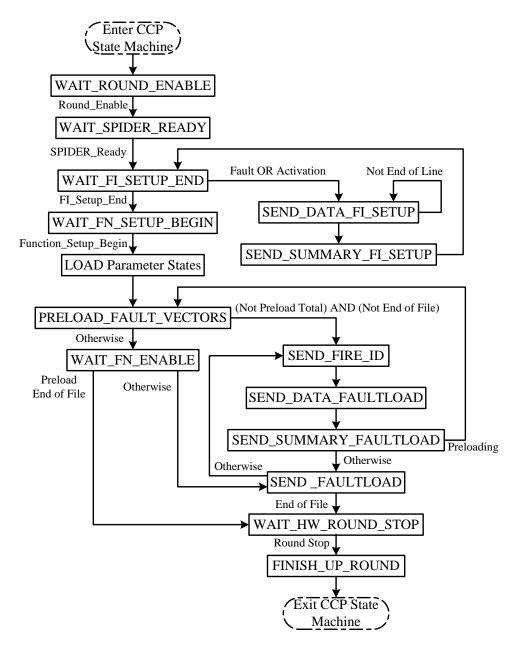

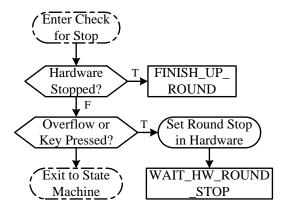

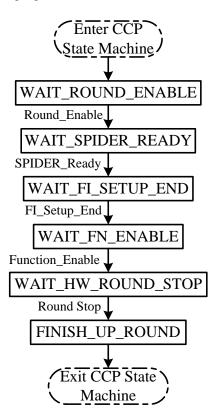

A peculiarity of these observer-based fault models is that the classification of any given physical fault is not absolute but relative to the states of the observers, which normally change during system operation. This may limit the achievable reduction in the fault space complexity.