## MODELING OF SONOS MEMORY CELL ERASE CYCLE

## THOMAS A. PHILLIPS<sup>a</sup>, TODD C. MACLEOD<sup>a</sup>, and FAT DUEN $HO^b$

<sup>a</sup>National Aeronautics and Space Administration, Marshall Space Flight Center, Huntsville, Alabama, 35812, U.S.A. <sup>b</sup>The University of Alabama in Huntsville, Department of Electrical and Computer Engineering, Huntsville, Alabama 35899, U.S.A.

## ABSTRACT

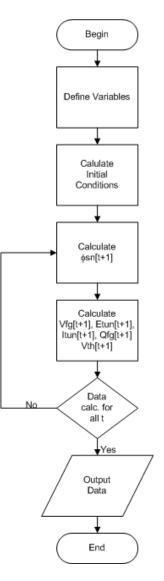

Silicon-oxide-nitride-oxide-silicon (SONOS) nonvolatile semiconductor memories (NVSMS) have many advantages. These memories are electrically erasable programmable read-only memories (EEPROMs). They utilize low programming voltages, endure extended erase/write cycles, are inherently resistant to radiation, and are compatible with high-density scaled CMOS for low power, portable electronics. The SONOS memory cell erase cycle was investigated using a nonquasi-static (NQS) MOSFET model. The SONOS floating gate charge and voltage, tunneling current, threshold voltage, and drain current were characterized during an erase cycle. Comparisons were made between the model predictions and experimental device data.

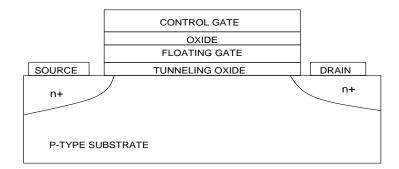

Figure 1: SONOS Device Layout

Figure 2: ERASE Model Flow Chart